## **Computer Structures: Principles and Examples**

Daniel P. Siewiorek Carnegie-Mellon University

**C. Gordon Bell** Digital Equipment Corporation

Allen Newell Carnegie-Mellon University

### McGraw-Hill Book Company

New York⊐St. Louis⊐San Francisco⊐Auckland⊐Bogotá⊐Hamburg⊐ Johannesburg⊐London⊐Madrid⊐Mexico⊐Montreal⊐New Delhi⊐ Panama⊐Paris⊐São Paulo⊒Singapore⊐Sydney⊐Tokyo⊐Toronto This book was set in Caledonia by Black Dot, Inc. The editors were Charles E. Stewart and James E. Vastyan; the production supervisor was Joe Campanella. New drawings were done by Fine Line Illustrations, Inc. Von Hoffmann Press, Inc., was printer and binder.

Library of Congress Cataloging in Publication Data

Main entry under title:

Computer structures.

(McGraw-Hill computer science series) Bibliography: p. Includes index. 1. Computer architecture—Addresses, essays, lectures. I. Siewiorek, Daniel P. II. Bell, C. Gordon. III. Newell, Allen. QA76.9.A73C65 621.3819'5 80-27926 ISBN 0-07-057302-6 AACR 1

### **Computer Structures: Principles and Examples**

Copyright © 1982 by McGraw-Hill, Inc. All rights reserved. Chapters 9, 10, 11, 40, 43, and 48 are from *Computer Structures: Readings and Examples* by C. Gordon Bell and Allen Newell, copyright © 1971 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

1234567890VHVH8987654321

See Acknowledgments on pages 915–920. Copyrights included on this page by reference.

Computer Structures: Principles and Examples

### **McGraw-Hill Computer Science Series**

Allen ANATOMY OF LISP Bell and Newell COMPUTER STRUCTURES: READINGS AND EXAMPLES Donovan SYSTEMS PROGRAMMING Feigenbaum and Feldman COMPUTERS AND THOUGHT Gear COMPUTER ORGANIZATION AND PROGRAMMING Givone INTRODUCTION TO SWITCHING CIRCUIT THEORY Goodman and Hedetniemi INTRODUCTION TO THE DESIGN AND ANALYSIS OF ALGORITHMS Hamacher, Vranesic, and Zaky COMPUTER ORGANIZATION Hamming INTRODUCTION TO APPLIED NUMERICAL ANALYSIS Haves COMPUTER ARCHITECTURE AND ORGANIZATION Hellerman DIGITAL COMPUTER SYSTEM PRINCIPLES Hellerman and Conroy COMPUTER SYSTEM PERFORMANCE Kain AUTOMATA THEORY: MACHINES AND LANGUAGES Katzan MICROPROGRAMMING PRIMER Kohavi SWITCHING AND FINITE AUTOMATE THEORY Liu elements of discrete mathematics Liu INTRODUCTION TO COMBINATORIAL MATHEMATICS MacEwen INTRODUCTION TO COMPUTER SYSTEMS: USING THE PDP-11 AND PASCAL Madnick and Donovan OPERATING SYSTEMS Manna MATHEMATICAL THEORY OF COMPUTATION Newman and Sproull principles of interactive computer graphics Nilsson problem-solving methods in artificial intelligence Rice MATRIX COMPUTATIONS AND MATHEMATICAL SOFTWARE Rosen PROGRAMMING SYSTEMS AND LANGUAGES Salton AUTOMATIC INFORMATION ORGANIZATION AND RETRIEVAL Siewiorek, Bell, and Newell COMPUTER STRUCTURES: PRINCIPLES AND EXAMPLES Stone INTRODUCTION TO COMPUTER ORGANIZATION AND DATA STRUCTURES Stone and Siewiorek INTRODUCTION TO COMPUTER ORGANIZATION AND DATA STRUCTURES: PDP-11 EDITION Tonge and Feldman COMPUTING: AN INTRODUCTION TO PROCEDURES AND PROCEDURE-FOLLOWERS Tremblay and Bunt AN INTRODUCTION TO COMPUTER SCIENCE: AN ALGORITHMIC APPROACH Tremblay and Bunt AN INTRODUCTION TO COMPUTER SCIENCE: AN ALGORITHMIC APPROACH, Short Edition Tremblay and Manohar DISCRETE MATHEMATICAL STRUCTURES WITH APPLICATIONS TO COMPUTER SCIENCE Tremblay and Sorenson AN INTRODUCTION TO DATA STRUCTURES WITH APPLICATIONS Tucker PROGRAMMING LANGUAGES Watson TIMESHARING SYSTEM DESIGN CONCEPTS Wiederhold DATABASE DESIGN Winston THE PSYCHOLOGY OF COMPUTER VISION

#### McGraw-Hill Advanced Computer Science Series

Davis and Lenat KNOWLEDGE-BASED SYSTEMS IN ARTIFICIAL INTELLIGENCE Feigenbaum and Feldman COMPUTERS AND THOUGHT Kogge THE ARCHITECTURE OF PIPELINED COMPUTERS Lindsay, Buchanan, Feigenbaum, and Lederberg APPLICATIONS OF ARTIFICIAL INTELLIGENCE FOR ORGANIC CHEMISTRY: THE DENDRAL PROJECT Nilsson PROBLEM-SOLVING METHODS IN ARTIFICIAL INTELLIGENCE Watson TIMESHARING SYSTEMS DESIGN CONCEPTS Winston THE PSYCHOLOGY OF COMPUTER VISION

Wulf, Levin, and Harbison HYDRA/C.MMP: AN EXPERIMENTAL COMPUTER SYSTEM

To Brigham, Laura, Nora, and Paul ,

## Contents in Brief

Preface

### Part 1 FUNDAMENTALS

|         |    | Section 1<br>ABSTRACTION AND NOTATION           | 3   |

|---------|----|-------------------------------------------------|-----|

| CHAPTER | 1  | Computer Classes and Evolution                  | 4   |

| CHAPTER | 2  | Levels and Abstractions                         | 9   |

| CHAPTER | 3  | PMS Notation                                    | 17  |

| CHAPTER | 4  | An Introduction to ISPS                         | 23  |

|         |    | Section 2                                       |     |

|         |    | THE COMPUTER SPACE                              | 33  |

| CHAPTER | 5  | Function and Performance                        | 39  |

| CHAPTER | 6  | Structure                                       | 62  |

|         | CO | Section 3<br>MPUTERS OF HISTORICAL SIGNIFICANCE | 96  |

| CHAPTER | 7  | The Manchester Mark 1                           | 107 |

| CHAPTER | 8  | Structural Levels of the PDP-8                  | 110 |

| CHAPTER | 9  | Design of the B 5000 System                     | 129 |

| CHAPTER | 10 | One-Level Storage System                        | 135 |

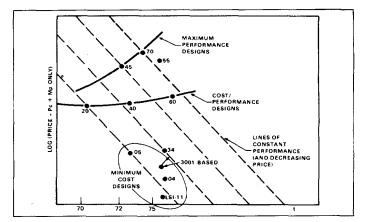

## Part 2 REGIONS OF COMPUTER SPACE

|            | Section 1<br>MICROPROGRAM-BASED PROCESSORS                                          | 151 |

|------------|-------------------------------------------------------------------------------------|-----|

| CHAPTER 11 | Microprogramming and the Design of the<br>Control Circuits in an Electronic Digital |     |

|            | Computer                                                                            | 158 |

| CHAPTER 12 | Microprogramming the IBM System/360                                                 |     |

|            | Model 30                                                                            | 164 |

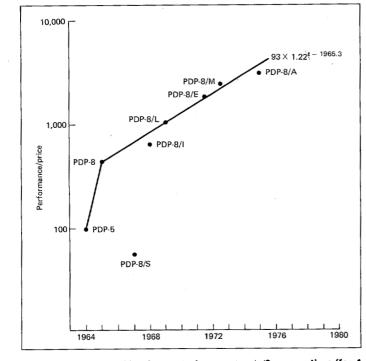

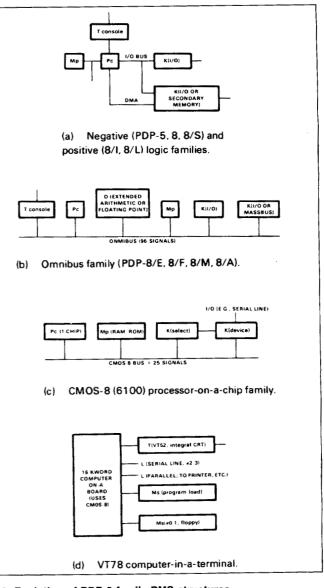

| CHAPTER 13 | Bit-Sliced Microprocessor of the Am2900                                             |     |

|            | Family: The Am2901/2909                                                             | 168 |

| CHAPTER 14 | The Am2903/2910                                                                     | 186 |

| CHAPTER 15 | A PDP-8 Implemented from AMD                                                        |     |

|            | Bit-Sliced Microprocessors                                                          | 219 |

| MEMOR                    | Section 2<br>Y HIERARCHIES AND MULTIPLE PROCESSES                                  | 227 |

|--------------------------|------------------------------------------------------------------------------------|-----|

| CHAPTER 16<br>CHAPTER 17 | Burroughs' B6500/B7500 Stack Mechanism<br>An Outline of the ICL 2900 Series System | 244 |

| CHAPIER II               | Architecture                                                                       | 251 |

|                          | Section 3                                                                          |     |

| CON                      | CURRENCY: SINGLE-PROCESSOR SYSTEMS                                                 | 260 |

| CHAPTER 18               | The IBM System/360 Model 91: Machine                                               |     |

|                          | Philosophy and Instruction-Handling                                                | 300 |

| CHAPTER 19               | An Efficient Algorithm for Exploiting                                              |     |

|                          | Multiple Arithmetic Units                                                          | 293 |

| CHAPTER 20               | The Illiac IV System                                                               | 306 |

| CHAPTER 21               | A Productive Implementation of an                                                  | 017 |

|                          | Associative Array Processor: STARAN                                                | 317 |

|                          | Section 4                                                                          |     |

|                          | MULTIPLE-PROCESSOR SYSTEMS                                                         | 332 |

| CHAPTER 22               | The C.mmp/Hydra Project: An                                                        |     |

|                          | Architectural Overview                                                             | 350 |

| CHAPTER 23               | Pluribus: An Operational Fault-Tolerant                                            |     |

|                          | Multiprocessor                                                                     | 371 |

|                          |                                                                                    |     |

|                          | Section 5<br>NETWORKS                                                              | 387 |

|                          |                                                                                    |     |

| CHAPTER 24               | The Interface Message Processor for the                                            |     |

|                          | ARPA Computer Network                                                              | 402 |

| CHAPTER 25               | ALOHA Packet Broadcasting: A Retrospect                                            | 416 |

| CHAPTER 26               | Ethernet: Distributed Packet Switching for                                         | 400 |

|                          | Local Computer Networks                                                            | 429 |

|                          | Section 6                                                                          |     |

|                          | FAULT-TOLERANT SYSTEMS                                                             | 439 |

| CHAPTER 27               | The STAR (Self-Testing And Repairing)                                              |     |

|                          | Computer: An Investigation of the Theory                                           |     |

|                          | and Practice of Fault-Tolerant Computer                                            |     |

|                          | Design                                                                             | 448 |

| CHAPTER 28               | Fault-Tolerant Design of Local ESS                                                 |     |

|                          | Processors                                                                         | 459 |

| CHAPTER 29               | The Tandem 16: A Fault-Tolerant                                                    |     |

|                          | Computing System                                                                   | 470 |

|                          |                                                                                    |     |

xiii

vii

|            | Section 7<br>LANGUAGE-BASED COMPUTERS   | 486 |

|------------|-----------------------------------------|-----|

| CHAPTER 30 | The SYMBOL Computer                     | 489 |

| CHAPTER 31 | A Dual-Processor Desk-Top Computer:     |     |

|            | The HP 9845A                            | 508 |

| CHAPTER 32 | The IBM System/38                       | 533 |

|            | Section 8<br>PERSONAL COMPUTING SYSTEMS | 547 |

| CHAPTER 33 | Alto: A Personal Computer               | 549 |

# Part 3 COMPUTER CLASSES

|            | Section 1                                   |     |

|------------|---------------------------------------------|-----|

|            | MONOLITHIC MICROCOMPUTERS                   | 581 |

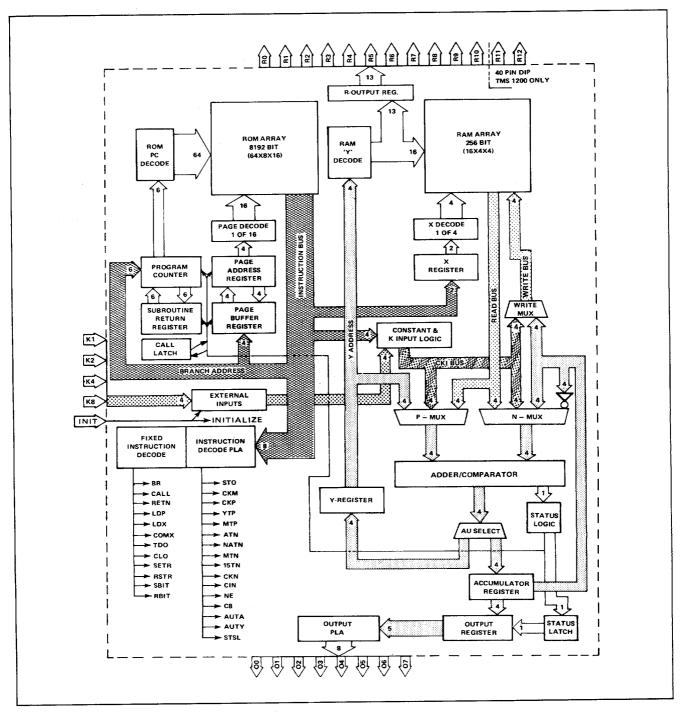

| CHAPTER 34 | TMS1000/1200: Chip Architecture and         |     |

|            | Operation                                   | 587 |

| CHAPTER 35 | PIC1650: Chip Architecture and Operation    | 602 |

|            | Section 2                                   |     |

|            | MICROCOMPUTERS                              | 610 |

| CHAPTER 36 | Trends in Microcomputers                    | 612 |

| CHAPTER 37 | Intel Microprocessors: 8008 to 8086         | 615 |

|            | Section 3                                   |     |

|            | MINICOMPUTERS                               | 647 |

| CHAPTER 38 | A New Architecture for Mini-Computers:      |     |

|            | The DEC PDP-11                              | 649 |

| CHAPTER 39 | Implementation and Performance              |     |

|            | Evaluation of the PDP-11 Family             | 666 |

|            | Section 4                                   |     |

|            | MAXICOMPUTERS                               | 680 |

| CHAPTER 40 | The Structure of System/360, Part I:        |     |

|            | Outline of the Logical Structure            | 695 |

| CHAPTER 41 | The Structure of System/360, Part II:       |     |

|            | System Implementations                      | 711 |

| CHAPTER 42 | VAX-11/780: A Virtual Address Extension to  |     |

|            | the DEC PDP-11 Family                       | 716 |

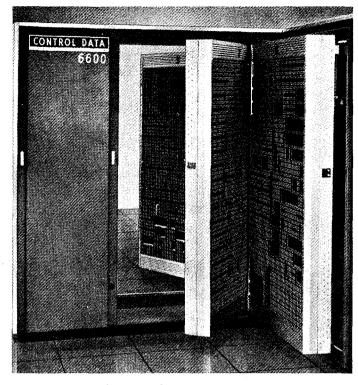

| CHAPTER 43 | Parallel Operation in the Control Data 6600 | 730 |

|            |                                             |     |

| CHAPTER 44 | The CRAY-1 Computer System           | 743     |

|------------|--------------------------------------|---------|

| CHAPTER 45 | The TI ASC: A Highly Modular and     |         |

|            | Flexible Super Computer Architecture | <br>753 |

## Part 4

# FAMILY RANGE, COMPATIBILITY, AND EVOLUTION

|              | Section 1<br>MICROCOMPUTER FAMILIES                                             | 765 |

|--------------|---------------------------------------------------------------------------------|-----|

|              | Section 2                                                                       |     |

|              | MINICOMPUTER FAMILIES                                                           | 766 |

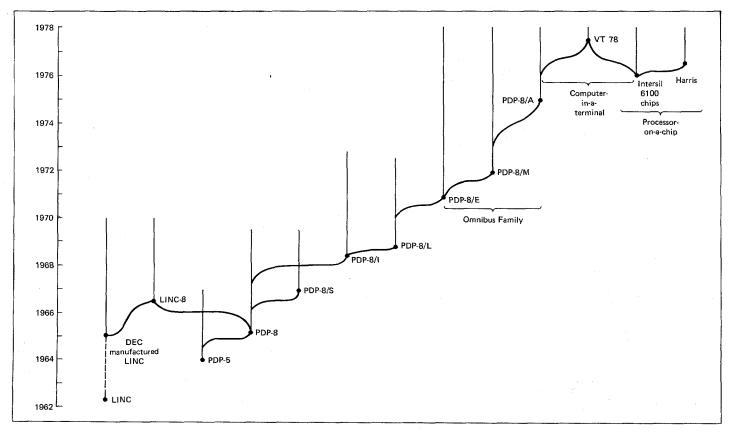

| CHAPTER 46   | The PDP-8 Family                                                                | 767 |

| CHAPTER 47   | The Evolution of the PDP-11                                                     | 776 |

|              | Section 3<br>EVOLUTION OF HP CALCULATORS                                        | 785 |

| CHAPTER 48   | The HP Model 9100A Computing                                                    |     |

|              | Calculator                                                                      | 787 |

| CHAPTER 49   | The HP 9810/20/30 Series                                                        | 801 |

| CHAPTER 50   | Hewlett-Packard Calculator Architectures                                        | 824 |

| EV           | Section 4<br>VOLUTION OF BURROUGHS COMPUTERS                                    | 828 |

|              | Section 5                                                                       |     |

| TH           | he system/360 and system/370 family                                             | 829 |

| CHAPTER 51   | Architecture of the IBM System/370                                              | 830 |

| CHAPTER 52   | The IBM System/360, System/370, 3030,<br>and 4300: A Series of Planned Machines |     |

|              | That Span a Wide Performance Range                                              | 856 |

| F            | Section 6<br>EVOLUTION OF CDC/CRAY COMPUTERS                                    | 893 |

|              |                                                                                 |     |

| Bibliography |                                                                                 | 894 |

| Acknowledg   | gments                                                                          | 915 |

| Index        |                                                                                 | 921 |

|              |                                                                                 |     |

## **Contents**<sup>1</sup>

Preface

xiii

### Part 1 FUNDAMENTALS

|         |             | Section 1<br>ABSTRACTION AND NOTATION                                                                                                                                                                   | 3          |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| CHAPTER | 1           | Computer Classes and Evolution                                                                                                                                                                          | 4          |

|         | 2           | Levels and Abstractions                                                                                                                                                                                 | 9          |

|         | 3           | PMS Notation                                                                                                                                                                                            | 17         |

|         | 4           | An Introduction to ISPS                                                                                                                                                                                 |            |

|         |             | Mario R. Barbacci                                                                                                                                                                                       | 23         |

|         |             | Section 2                                                                                                                                                                                               |            |

|         |             | THE COMPUTER SPACE                                                                                                                                                                                      | 33         |

| CHAPTER | 5           | Function and Performance                                                                                                                                                                                | 39         |

|         | 6           | Structure                                                                                                                                                                                               | 62         |

|         |             | Section 3                                                                                                                                                                                               |            |

|         | CON         | THEFT AND                                                                                                                                                           | 00         |

|         | CO          | MPUTERS OF HISTORICAL SIGNIFICANCE                                                                                                                                                                      | 96         |

| CHAPTER | CO)<br>7    | MPUTERS OF HISTORICAL SIGNIFICANCE<br>The Manchester Mark 1                                                                                                                                             | 96         |

| CHAPTER |             |                                                                                                                                                                                                         | 96<br>107  |

| CHAPTER |             | The Manchester Mark 1                                                                                                                                                                                   |            |

| CHAPTER | 7           | The Manchester Mark 1<br>S. H. Lavington                                                                                                                                                                |            |

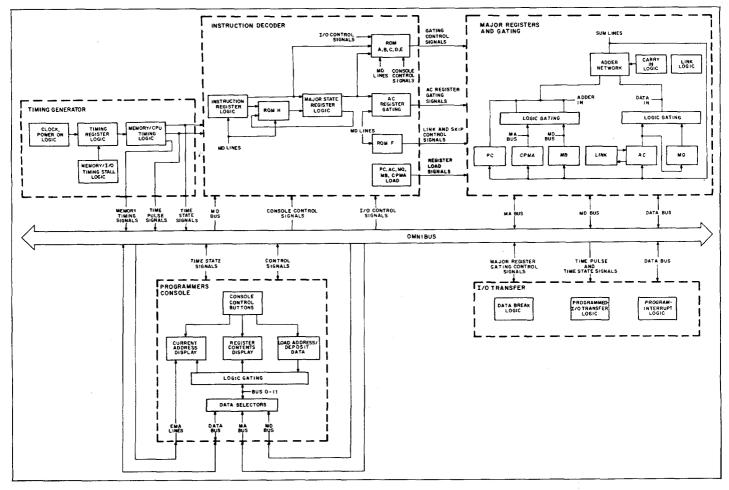

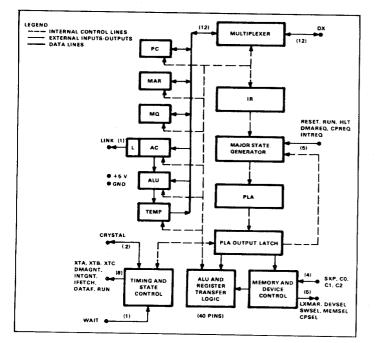

| CHAPTER | 7           | The Manchester Mark 1<br>S. H. Lavington<br>Structural Levels of the PDP-8                                                                                                                              |            |

| CHAPTER | 7           | The Manchester Mark 1<br>S. H. Lavington<br>Structural Levels of the PDP-8<br>C. Gordon Bell, Allen Newell, and                                                                                         | 107        |

| CHAPTER | 7<br>8      | The Manchester Mark 1<br>S. H. Lavington<br>Structural Levels of the PDP-8<br>C. Gordon Bell, Allen Newell, and<br>Daniel P. Siewiorek                                                                  | 107        |

|         | 7<br>8      | The Manchester Mark 1<br>S. H. Lavington<br>Structural Levels of the PDP-8<br>C. Gordon Bell, Allen Newell, and<br>Daniel P. Siewiorek<br>Design of the B 5000 System                                   | 107<br>110 |

|         | 7<br>8<br>9 | The Manchester Mark 1<br>S. H. Lavington<br>Structural Levels of the PDP-8<br>C. Gordon Bell, Allen Newell, and<br>Daniel P. Siewiorek<br>Design of the B 5000 System<br>William Lonergan and Paul King | 107<br>110 |

## Part 2 REGIONS OF COMPUTER SPACE

|            | Section 1<br>MICROPROGRAM-BASED PROCESSORS                                                      | 151 |

|------------|-------------------------------------------------------------------------------------------------|-----|

| CHAPTER 11 | Microprogramming and the Design of the<br>Control Circuits in an Electronic Digital<br>Computer |     |

|            | M. V. Wilkes and J. B. Stringer                                                                 | 158 |

| 12         | Microprogramming the IBM System/360<br>Model 30                                                 |     |

|            | Helmut Weber                                                                                    | 164 |

| 13         | Bit-Sliced Microprocessor of the Am2900<br>Family: The Am2901/2909                              |     |

|            | Advanced Micro Devices, Inc.                                                                    | 168 |

| 14         | The Am2903/2910                                                                                 |     |

|            | Advanced Micro Devices, Inc.                                                                    | 186 |

| 15         | A PDP-8 Implemented from AMD                                                                    |     |

|            | Bit-Sliced Microprocessors                                                                      |     |

|            | Michael Tsao                                                                                    | 219 |

| 39         | Implementation and Performance                                                                  |     |

|            | Evaluation of the PDP-11 Family                                                                 |     |

|            | Edward A. Snow and Daniel P. Siewiorek                                                          | 666 |

| 34         | TMS1000/1200: Chip Architecture and                                                             |     |

|            | Operation                                                                                       |     |

|            | Texas Instruments, Inc.                                                                         | 581 |

| 48         | The HP Model 9100A Computing Calculator                                                         |     |

|            | Richard E. Monnier, Thomas E. Osborne, and                                                      |     |

|            | David S. Cochran                                                                                | 787 |

| <b>4</b> 9 | The HP 9810/20/30 Series                                                                        | 801 |

<sup>1</sup>This is a "virtual" contents, which means that because many of the computers are relevant to more than one part and section, we have used *italic type* for chapter numbers and titles to indicate a nonsequential mapping for computers placed out of "physical" order. The reader might read (reference) the book according to the virtual order. See the preface for further discussion.

ix

### x Contents

| 31         | A Dual-Processor Desk-Top Computer: The<br>HP 9845A<br>William D. Eads, Jack M. Walden, and                        |            |

|------------|--------------------------------------------------------------------------------------------------------------------|------------|

|            | Edward L. Miller                                                                                                   | 508        |

| MEMOR      | Section 2<br>Y HIERARCHIES AND MULTIPLE PROCESSES                                                                  | 227        |

| CHAPTER 10 | One-Level Storage System                                                                                           |            |

|            | T. Kilburn, D. B. G. Edwards, M. J. Lanigan,<br>and F. H. Sumner                                                   | 135        |

| 9          | Design of the B 5000 System                                                                                        |            |

|            | William Lonergan and Paul King                                                                                     | 129        |

| 16         | Burroughs' B6500/B7500 Stack Mechanism                                                                             | 244        |

| 17         | E. A. Hauck and B. A. Dent<br>An Outline of the ICL 2900 Series System                                             | 244        |

| 14         | Architecture                                                                                                       |            |

|            | J. L. Keedy                                                                                                        | 251        |

| 42         | VAX-11/780: A Virtual Address Extension to                                                                         |            |

|            | the DEC PDP-11 Family                                                                                              | 716        |

| 20         | W. D. Strecker<br>The IBM/System 38                                                                                | 716<br>533 |

| 32         |                                                                                                                    | 000        |

| CON        | Section 3<br>CURRENCY: SINGLE-PROCESSOR SYSTEMS                                                                    | 260        |

| CHAPTER 18 | The IBM System/360 Model 91: Machine<br>Philosophy and Instruction-Handling<br>D. W. Anderson, F. J. Sparacio, and |            |

|            | R. M. Tomasulo                                                                                                     | 300        |

| 19         | An Efficient Algorithm for Exploiting<br>Multiple Arithmetic Units                                                 |            |

|            | R. M. Tomasulo                                                                                                     | 293        |

| 20         | The Illiac IV System                                                                                               |            |

|            | W. J. Bouknight, Stewart A. Denenberg,<br>David E. McIntyre, J. M. Randall,                                        |            |

|            | Amed H. Sameh, and Daniel L. Slotnick                                                                              | 306        |

| 21         | A Productive Implementation of an                                                                                  |            |

|            | Associative Array Processor: STARAN                                                                                |            |

|            | Jack A. Rudolph and Kenneth E. Batcher                                                                             | 317        |

| 43         | Parallel Operation in the Control Data 6600                                                                        | 730        |

| 44         | James E. Thornton<br>The CRAY I Computer System                                                                    | 730        |

| 44         | The CRAY-1 Computer System<br>Richard M. Russell                                                                   | 743        |

| 45         | The TI ASC: A Highly Modular and                                                                                   |            |

|            | Flexible Super Computer Architecture                                                                               |            |

|            | W.J. Watson and L. C. Dean                                                                                         | 753        |

|            | Section 4<br>MULTIPLE-PROCESSOR SYSTEMS                                                                            | 332        |

| CHAPTER 22 | The C.mmp/Hydra Project: An<br>Architectural Overview<br>Henry H. Mashburn                                         | 350        |

| John G. Robinson, F. Stanley Skowronski,<br>and Eric W. Wolf 37<br>43 Parallel Operation in the Control Data 6600<br>James E. Thornton 75<br>21 A Productive Implementation of an                                                                                                                                                                                                                                                                                                                                                                                | 71<br>30 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Associative Array Processor: STARAN<br>Jack A. Rudolph and Kenneth E. Batcher 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17       |

| Section 5<br>NETWORKS 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87       |

| CHAPTER 24 The Interface Message Processor for the<br>ARPA Computer Network<br>F. E. Heart, R. E. Kahn, S. M. Ornstein,<br>W. D. Courseher and D. C. Walder                                                                                                                                                                                                                                                                                                                                                                                                      | 02       |

| 25 ALOHA Packet Broadcasting: A Retrospect<br>R. Binder, N. Abramson, F. Kuo, A. Okinaka,                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16       |

| 26 Ethernet: Distributed Packet Switching for<br>Local Computer Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70       |

| Section 6<br>FAULT-TOLERANT SYSTEMS 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39       |

| CHAPTER 27 The STAR (Self-Testing And Repairing)<br>Computer: An Investigation of the Theory<br>and Practice of Fault-Tolerant Computer<br>Design                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| Algirdas Avizienis, George C. Gilley,<br>Francis P. Mathur, David A. Rennels,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48       |

| Algirdas Avizienis, George C. Gilley,<br>Francis P. Mathur, David A. Rennels,<br>John A. Rohr, and David K. Rubin 4<br>23 Pluribus: An Operational Fault-Tolerant<br>Multiprocessor<br>Daivd Katsuki, Eric S. Elsam,<br>William F. Mann, Eric S. Roberts,<br>John G. Robinson, F. Stanley Skowronski, and                                                                                                                                                                                                                                                        | 48<br>71 |

| Algirdas Avizienis, George C. Gilley,<br>Francis P. Mathur, David A. Rennels,<br>John A. Rohr, and David K. Rubin 4:<br>23 Pluribus: An Operational Fault-Tolerant<br>Multiprocessor<br>Daivd Katsuki, Eric S. Elsam,<br>William F. Mann, Eric S. Roberts,<br>John G. Robinson, F. Stanley Skowronski, and<br>Eric W. Wolf 3:<br>28 Fault-Tolerant Design of Local ESS<br>Processors                                                                                                                                                                             |          |

| Algirdas Avizienis, George C. Gilley,         Francis P. Mathur, David A. Rennels,         John A. Rohr, and David K. Rubin       44         23       Pluribus: An Operational Fault-Tolerant         Multiprocessor       Daivd Katsuki, Eric S. Elsam,         William F. Mann, Eric S. Roberts,       John G. Robinson, F. Stanley Skowronski, and         Eric W. Wolf       37         28       Fault-Tolerant Design of Local ESS         Processors       W. N. Toy         29       The Tandem 16: A Fault-Tolerant         Computing System       State | 71       |

|         |             | Section 7<br>LANGUAGE-BASED COMPUTERS                                                               | 486         |

|---------|-------------|-----------------------------------------------------------------------------------------------------|-------------|

| CHAPTE  | r <b>30</b> | The SYMBOL Computer:<br>SYMBOL: A Large Experimental System<br>Exploring Major Hardware Replacement |             |

|         |             | of Software                                                                                         |             |

|         |             | William R. Smith, Rex Rice, Gilman D.                                                               |             |

|         |             | Chesley, Theodore A. Laliotis, Stephen F.                                                           |             |

|         |             | Lundstrom, Myron A. Calhoun, Lawrence D.<br>Gerould, and Thomas G. Cook                             | 400         |

|         |             | SYMBOL: A Major Departure from Classic                                                              | 489         |

|         |             | Software Dominated von Neumann                                                                      |             |

|         |             | Computing Systems                                                                                   |             |

|         |             | R. Rice and W. R. Smith                                                                             | 502         |

|         | <b>4</b> 9  | The HP 9810/20/30 Series                                                                            | 801         |

|         | 31          | A Dual-Processor Desk-Top Computer: The HP 9845A                                                    |             |

|         |             | William D. Eads, Jack M. Walden, and                                                                |             |

|         |             | Edward L. Miller                                                                                    | 508         |

|         | 32          | The IBM System/38:                                                                                  |             |

|         |             | A High-Level Machine                                                                                |             |

|         |             | S. H. Dahlby, G. G. Henry, D. N. Reynolds,                                                          |             |

|         |             | and P. T. Taylor                                                                                    | 533         |

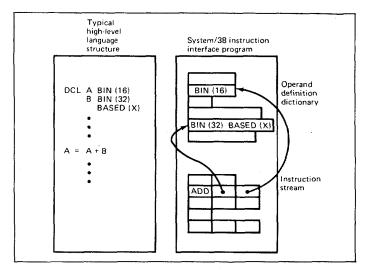

|         |             | Object-Oriented Architecture                                                                        |             |

|         |             | K. W. Pinnow, J. G. Ranweiler, and<br>J. F. Miller                                                  | 537         |

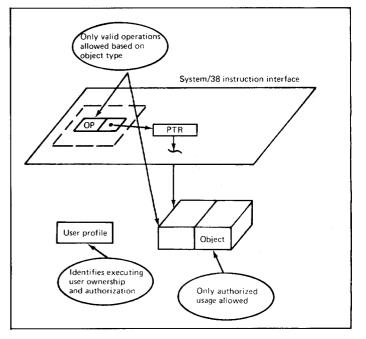

|         |             | Addressing and Authorization                                                                        | 007         |

|         |             | V. Berstis, C. D. Truxal, and J. G. Ranweiler                                                       | 540         |

|         |             | Hardware Organization of the System/38                                                              | • 10        |

|         |             | R. L. Hoffman and F. G. Soltis                                                                      | 544         |

|         |             | Section 8<br>PERSONAL COMPUTING SYSTEMS                                                             | 547         |

| CHAPTER | 34          | TMS1000/1200: Chip Architecture and                                                                 |             |

|         |             | Operation                                                                                           |             |

|         |             | Texas Instruments, Inc.                                                                             | 587         |

|         | <b>4</b> 8  | The HP Model 9100A Computing Calculator                                                             |             |

|         |             | Richard E. Monnier, Thomas E. Osborne, and                                                          |             |

|         |             | David S. Cochran                                                                                    | 787         |

|         | <b>49</b>   | The HP 9810/20/30 Series                                                                            | 801         |

|         | 31          | A Dual-Processor Desk-Top Computer: The<br>HP 9845A                                                 |             |

|         |             | William D. Eads, Jack M. Walden,                                                                    | <b>2</b> 00 |

|         | 22          | and Edward L. Miller                                                                                | 508         |

|         | 33          | Alto: A Personal Computer<br>C. P. Thacker, E. M. McCreight,                                        |             |

|         |             | B. W. Lampson, R. F. Sproull, and                                                                   |             |

|         |             | D. R. Boggs                                                                                         | 549         |

|         |             |                                                                                                     | 010         |

# Part 3 COMPUTER CLASSES

|            |                                                          | فنبياب المستعورين |

|------------|----------------------------------------------------------|-------------------|

|            | Section 1<br>MONOLITHIC MICROCOMPUTERS                   | 581               |

| CHAPTER 34 | TMS1000/1200: Chip Architecture and Operation            |                   |

|            | Texas Instruments, Inc.                                  | 587               |

| 35         | PIC1650: Chip Architecture and Operation                 |                   |

|            | Frank M. Gruppuso                                        | 602               |

|            | Section 2<br>MICROCOMPUTERS                              | 610               |

| CHAPTER 36 | Trends in Microcomputers                                 |                   |

|            | F. Faggin                                                | 612               |

| 37         | Intel Microprocessors: 8008 to 8086                      |                   |

|            | Stephen P. Morse, Bruce W. Ravenel,                      |                   |

|            | Stanley Mazor, and William B. Pohlman                    | 615               |

| 49         | The HP 9810/20/30 Series                                 | 801               |

| 31         | A Dual-Processor Desk-Top Computer: The<br>HP 9845A      |                   |

|            | William D. Eads, Jack M. Walden, and                     |                   |

|            | Edward L. Miller                                         | 508               |

|            | Section 3<br>MINICOMPUTERS                               | 647               |

| CHAPTER 8  | Structural Levels of the PDP-8                           |                   |

|            | C. Gordon Bell, Allen Newell, and                        |                   |

|            | Daniel P. Siewiorek                                      | 110               |

| 15         | A PDP-8 Implemented from AMD Bit-Sliced                  |                   |

|            | Microprocessors                                          |                   |

|            | Michael Tsao                                             | 219               |

| <b>4</b> 6 | The PDP-8 Family                                         |                   |

|            | C. G. Bell and J. E. McNamara                            | 767               |

| 38         | A New Architecture for Mini-Computers:<br>The DEC PDP-11 |                   |

|            | G. Bell, R. Cady, H. McFarland, B. Delagi,               |                   |

|            | J. O'Laughlin, R. Noonan, and W. Wulf                    | 649               |

| 39         | Implementation and Performance                           |                   |

|            | Evaluation of the PDP-11 Family                          |                   |

|            | Edward A. Snow and Daniel P. Siewiorek                   | 666               |

| 47         | The Evolution of the PDP-11                              |                   |

|            | C. G. Bell and J. C. Mudge                               | 776               |

| 49         | The HP 9810/20/30 Series                                 | 801               |

| 31         | A Dual-Processor Desk-Top Computer: The<br>HP 9845A      |                   |

|            | William D. Eads, Jack M. Walden, and                     |                   |

|            | Edward L. Miller                                         | 508               |

| 32         | The IBM System/38                                        | 533               |

|            | Section 4<br>MAXICOMPUTERS                  | 680 |

|------------|---------------------------------------------|-----|

| CHAPTER 40 | The Structure of System/360, Part I:        |     |

|            | Outline of the Logical Structure            |     |

|            | G. A. Blaauw and F. P. Brooks, Jr.          | 695 |

| 41         | The Structure of System/360, Part II:       |     |

|            | System Implementations                      |     |

|            | W. Y. Stevens                               | 711 |

| 42         | VAX-11/780: A Virtual Address Extension to  |     |

|            | the DEC PDP-11 Family                       |     |

|            | W. D. Strecker                              | 716 |

| 43         | Parallel Operation in the Control Data 6600 |     |

|            | James E. Thornton                           | 730 |

| 44         | The CRAY-1 Computer System                  |     |

|            | Richard M. Russell                          | 743 |

| 45         | The TI ASC: A Highly Modular and            |     |

| 20         | Flexible Super Computer Architecture        |     |

|            | W. J. Watson and L. C. Dean                 | 753 |

|            |                                             |     |

## Part 4 FAMILY RANGE, COMPATIBILITY, AND EVOLUTION

|            | Section 1<br>MICROCOMPUTER FAMILIES                                          | 765 |

|------------|------------------------------------------------------------------------------|-----|

| CHAPTER 37 | Intel Microprocessors: 8088 to 8086                                          |     |

|            | Stephen P. Morse, Bruce W. Ravenel,<br>Stanley Mazor, and William B. Pehlman | 615 |

|            | Section 2                                                                    |     |

|            | MINICOMPUTER FAMILIES                                                        | 766 |

| CHAPTER 46 | The PDP-8 Family                                                             |     |

|            | C. G. Bell and J. E. McNamara                                                | 767 |

| 47         | The Evolution of the PDP-11                                                  |     |

|            | C. G. Bell and J. C. Mudge                                                   | 776 |

|            | Section 3                                                                    |     |

|            | EVOLUTION OF HP CALCULATORS                                                  | 785 |

| CHAPTER 48 | The HP Model 9100A Computing                                                 |     |

|            | Calculator                                                                   |     |

|            | Richard E. Monnier, Thomas E. Osborne,                                       | -   |

|            | and David S. Cochran                                                         | 787 |

| 49         | The HP 9810/20/30 Series:                                                    |     |

|            | A New Series of Programmable Calculators                                     | 001 |

|            | Richard M. Spangler                                                          | 801 |

|                 | Model 10 Maintains Compatibility, Expands<br>Capability                     |             |

|-----------------|-----------------------------------------------------------------------------|-------------|

|                 | Curtis D. Brown and Jack M. Walden<br>Interactive Model 20 Speaks Algebraic | 803         |

|                 | Language                                                                    |             |

|                 | Rex L. James and Francis J. Yockey                                          | 805         |

|                 | BASIC-Language Model 30 Can Be                                              |             |

|                 | Calculator, Computer, or Terminal                                           |             |

|                 | Richard M. Spangler                                                         | 810         |

|                 | 9800 Processor Incorporates 8-MHz                                           |             |

|                 | Microprocessor                                                              | 014         |

|                 | Henry J. Kohoutek                                                           | 814         |

|                 | Versatile Input/Output Structure Welcomes                                   |             |

|                 | Peripheral Variety                                                          | 817         |

|                 | Gary L. Egan                                                                | 011         |

| 31              | A Dual-Processor Desk-Top Computer:<br>The HP 9845A                         |             |

|                 | William D. Eads, Jack M. Walden, and                                        | F00         |

| <b>2</b> 0      | Edward L. Miller                                                            | 508         |

| 50              | Hewlett-Packard Calculator Architectures                                    | 824         |

|                 | Thomas E. Osborne                                                           | 024         |

|                 | Section 4                                                                   |             |

| I               | EVOLUTION OF BURROUGHS COMPUTERS                                            | 828         |

| CHAPTER 9       | Design of the B 5000 System                                                 |             |

| CHAPTER 9       | William Lonergan and Paul King                                              | 129         |

| 16              |                                                                             | 140         |

| 10              | E. A. Hauck and B. A. Dent                                                  | 244         |

|                 | E. A. Huuck und D. A. Den                                                   | <b>4</b> 11 |

| נ               | Section 5<br>THE SYSTEM/360 AND SYSTEM/370 FAMILY                           | 829         |

| CHAPTER 51      | Architecture of the IBM System/370                                          |             |

| CHAPTER JI      | Richard P. Case and Andris Padegs                                           | 830         |

| 52              |                                                                             | 000         |

| 02              | and 4300: A Series of Planned Machines                                      |             |

|                 | That Span a Wide Performance Range                                          |             |

|                 | C. G. Bell, A. Newell, M. Reich, and                                        |             |

|                 | D. Siewiorek                                                                | 856         |

|                 |                                                                             |             |

|                 | Section 6<br>EVOLUTION OF CDC/CRAY COMPUTERS                                | 893         |

| CHAPTER 43      | Parallel Operation in the Control Data 6600                                 |             |

|                 | James E. Thornton                                                           | 730         |

| 44              | The CRAY-1 Computer System                                                  |             |

|                 | Richard M. Russell                                                          | 743         |

|                 |                                                                             |             |

| Bibliography    |                                                                             |             |

| Acknowledgments |                                                                             |             |

| Index           |                                                                             | 921         |

|                 |                                                                             |             |

|                 |                                                                             |             |

## Preface

When Computer Structures: Readings and Examples was originally published by Gordon Bell and Allen Newell in 1971, the concept of computer structures was just emerging. The book focused on the historical evolution of technology, instruction sets, and uniprocessors. Two new notations were introduced to provide more concise descriptions of instruction sets (ISP, for instructionset processor) and uniprocessor structures (PMS, for processor-memory-switch).

In the last decade, the scene has changed dramatically. Technological advances have led to a virtual explosion in the number of computer types and installations. Minicomputers and calculators, still relatively new computer applications in 1971, are the basis of industries today. Entirely new types, such as microprocessors and maxicomputers with vector data-types, now command sizable markets of their own. Techniques such as microprogramming, networks, multiprocessors, and fault tolerance were infrequently applied in 1971; a decade later, these concepts are essential in almost all the new systems.

The 1971 edition of *Computer Structures* introduced the concept of a design space, with each computer structure representing a point in that space. This edition embraces and expands the computer space concept and reflects changes in several dimensions which have since either received common acceptance or been replaced by other dimensions with significantly more impact on the structure's performance.

The number of addresses per instruction is an example of a dimension where common acceptance has developed. Contemporary instruction sets are based on general-register organizations with multiple-byte or -word instructions. The variable-length instruction format enables the computer to assign the largest number of op codes and address bits into a 1-word instruction. Early instruction-set design often meant wasted memory if the instructions were too wide. Too short an instruction could require excess instructions to perform an otherwise simple task. A good instruction-set encoding can increase program density by over 50 percent. With the creation of a large number of instruction sets, designers of new instruction sets have been able to integrate the best features of their predecessors.

Networks are an example of where new dimensions are emerging. Variations in network performance due to instructionset design are negligible compared to variations in network performance due to operating systems, network topology, network protocol, media bandwidth, etc.

This book emphasizes computer space dimensions with numerous and quantitative subdimensions. Each alternative value for a dimension represents a design alternative. These values and their interactions with other dimensions are illustrated by real machines.

All the machines discussed in this book have actually been constructed and evaluated. The papers, wherever possible, are written by the specific machine architects or people closely associated with the architectures. Several of the machines are presented in elaborate detail, enabling the reader to appreciate the design complexities encountered and design methodologies employed by the architects. Many of these papers have been written specifically for this book. In favoring depth over breadth, the book is not able to discuss all important architectures (nor even all major manufacturers). However, the architectures that are included were carefully selected to uniformly cover the major design principles of computer structures.

The proliferation of computer structures and the emergence of computer families have provided quantitative as well as descriptive data for the book. Wherever possible, data, models, and/or trends are derived from the actual computer structures.

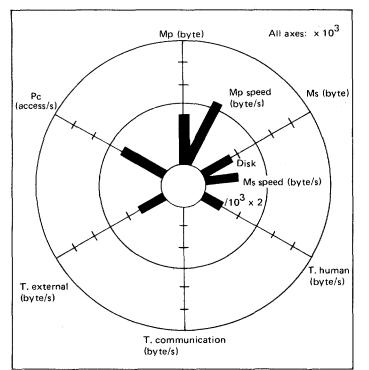

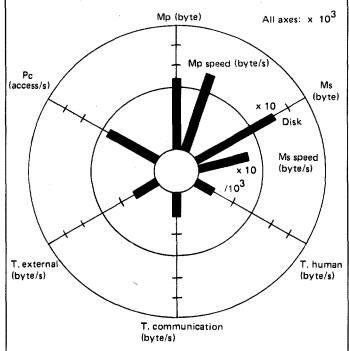

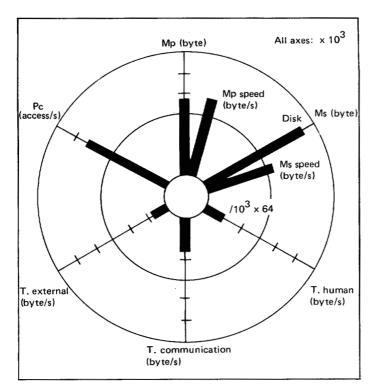

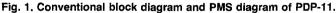

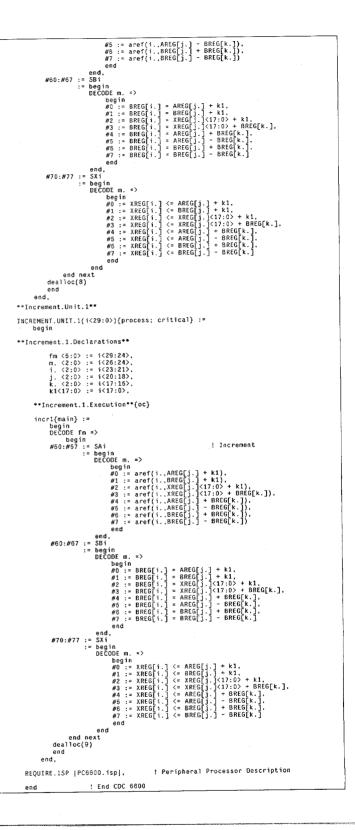

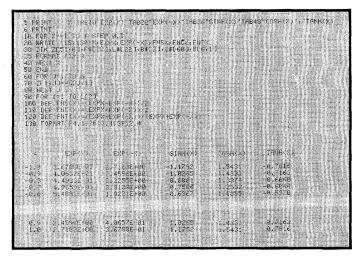

Three notations help to summarize information about the computer structures: ISP, PMS, and Kiviat graphs. An updated version of the original ISP language-ISPS-has been used to formally describe a growing number of major computer architectures. A simulator has been utilized for debugging (e.g., running diagnostic programs written for the hardware implementations of the machines) and data collection (e.g., implementationindependent measures of benchmarks). ISPL, a predecessor of ISPS, was used in the Army-Navy Military Computer Family (MCF) project to evaluate alternative architectures.<sup>1</sup> Several research projects based on formal machine descriptions have also developed, including the generation of microcode, assemblers, diagnostics, and compilers. Since a complete ISPS description of a contemporary machine can be over 50 pages long, we have chosen to provide subsets of the full ISPS descriptions for all but the very simple architectures. These ISPS descriptions are complete except that only a subset of each machine's instruction set is described. All the ISPS descriptions that appear in this book have been compiled and simulated.

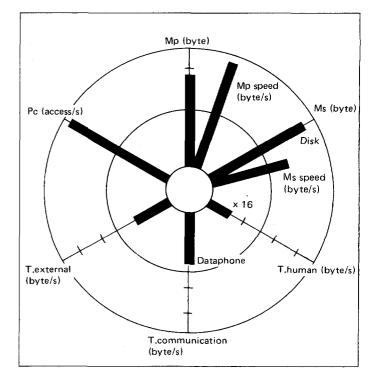

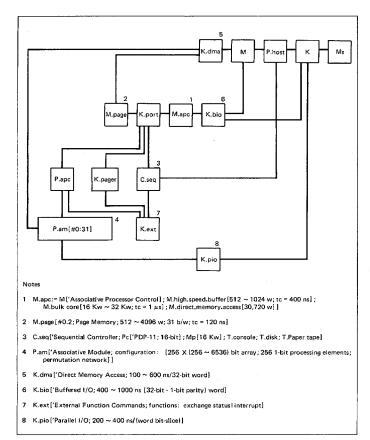

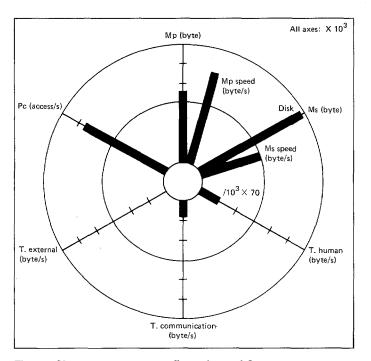

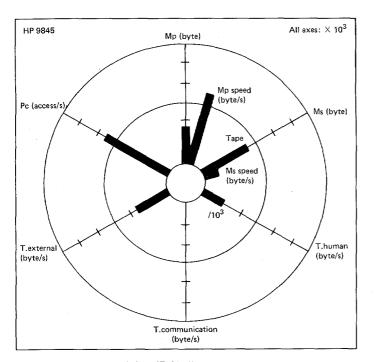

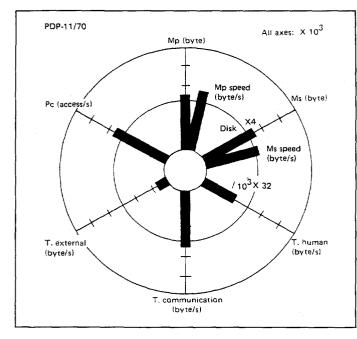

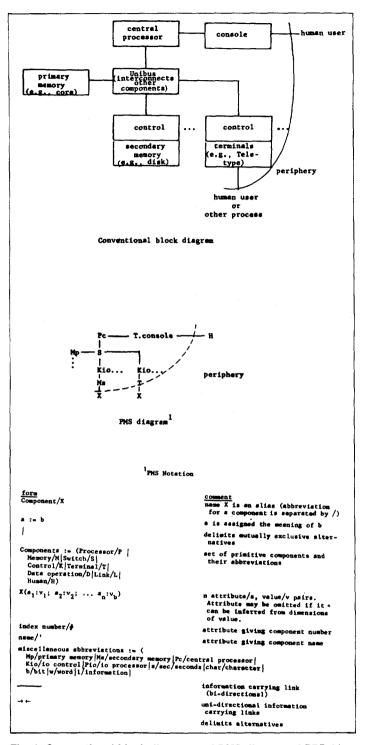

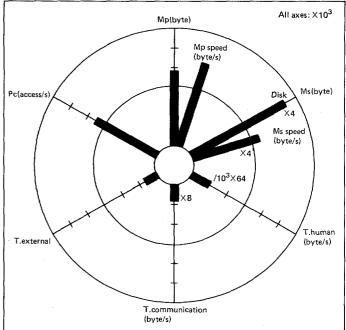

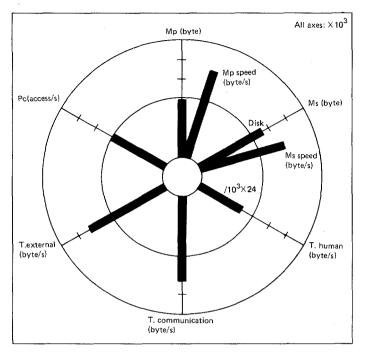

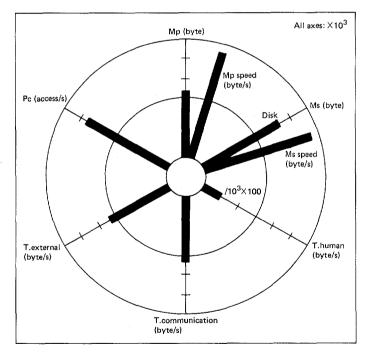

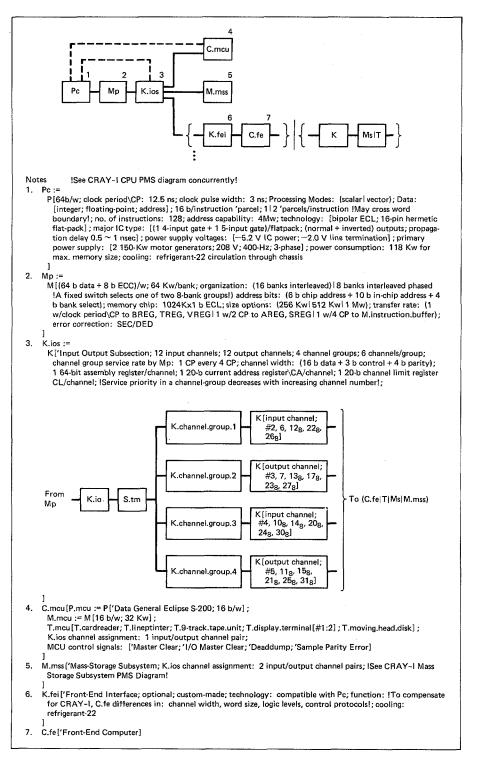

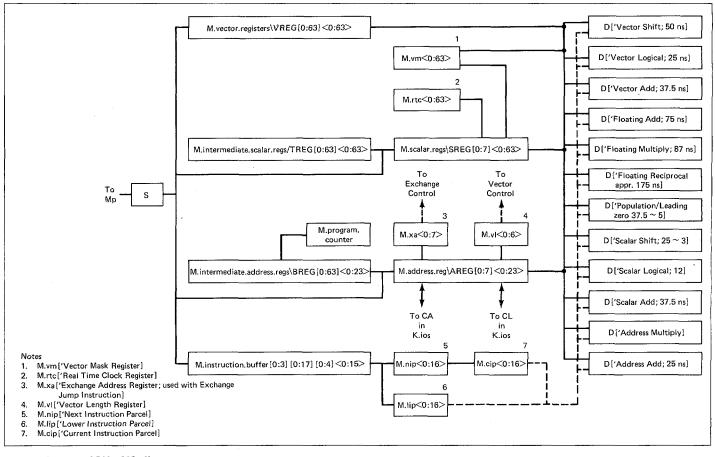

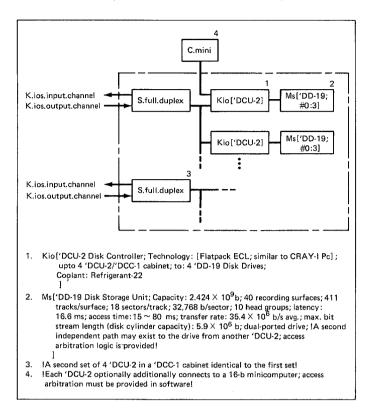

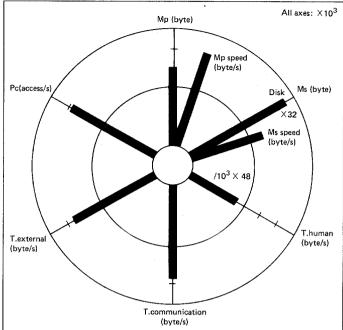

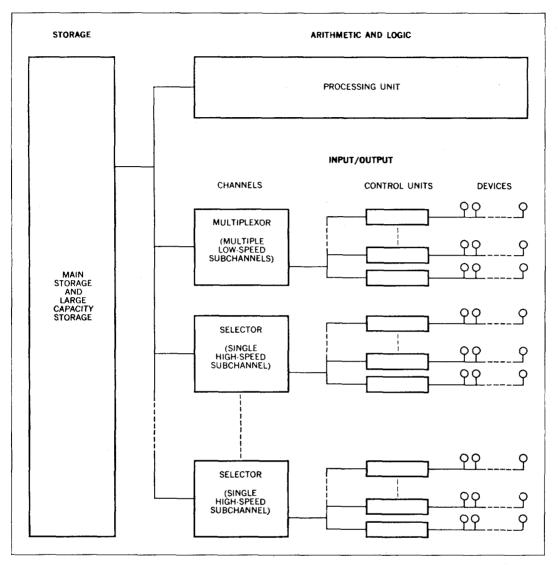

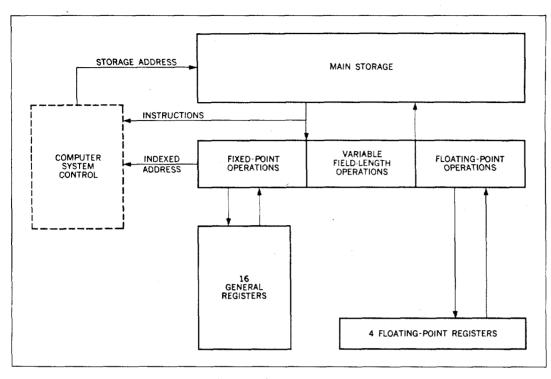

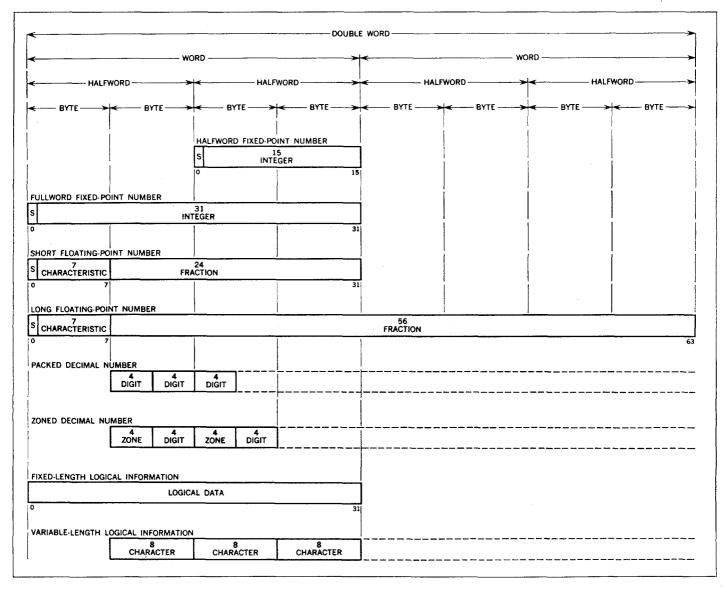

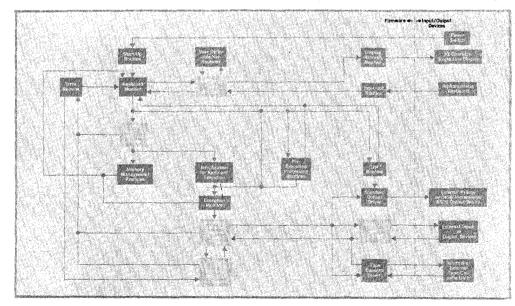

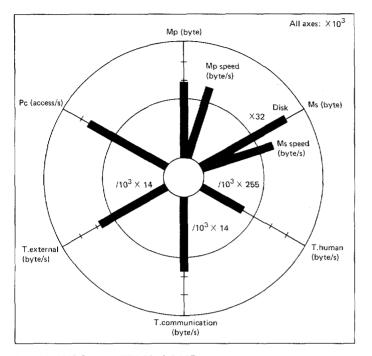

The PMS notation for describing the information flow rate of computer structures has been simplified and made more readable. System performance is provided by Kiviat graphs, which display six major system parameters.

It is hoped that this book will serve as an educational resource for three professional groups: the computer engineer, who de-

<sup>1"</sup>Military Computer Architectures: A Look at the Alternatives," special issue of *Computer*, vol. 10, no. 10, October 1977.

xiii

signs physical computer systems; the computer scientist, who is concerned primarily with the programming level and with various abstract views of information processing; and the electrical engineer, who sees computer systems as part of a larger technology.

This book presents design choices, structural variations, and systematic analysis, which can be especially useful for the computer engineer charged with designing a new computer system or subsystem. The student of computer engineering who approaches this book with a working knowledge of logic design should find it possible to realize many of the systems described at the next lower levels of logic structure.

For the computer scientist, the levels of computer structure discussed in this book offer significant insight into the physical devices that underlie computer science. Even if the computer scientist does not carry through the design in terms of the lower logic levels, it will still be possible to incorporate the upper levels of computer structure.

The electrical engineer need not study every example in this book. A sampling, plus the overview presented in the first three chapters, is appropriate to give insight into the elaborate growth accompanying the basic digital technology created within electrical engineering.

The book is divided into four parts:

- 1. Fundamentals

- 2. Regions of Computer Space

- 3. Computer Classes

- 4. Family Range, Compatibility, and Evolution

Part 1 provides an introduction to ISP, PMS, and Kiviat graph notation, sketches the dimensions of the computer space, and provides a discussion of several historically significant machines. Part 2 examines several of the computer space dimensions, contrasting the alternative values for each dimension. Examples of actual computer structures provide a comparative taxonomy of design choices.

Part 3 contains detailed descriptions of computer structures organized by size: monolithic microcomputer, microcomputer, minicomputer, and maxicomputer. Each class has a common set of applications and goals. On the basis of ISP, PMS, and Kiviat graph notations, the structures are compared and contrasted and trends are described.

Part 4 deals with computer families, which comprise several structures implementing a common design goal and frequently employing a common ISP. Extensive data are provided for the comparison of closely related systems, and several alternative analyses are presented, including a discussion of the impact on the system of individual design tradeoffs, such as those presented in Part 2.

This book has both a physical and a "virtual" table of contents. The physical order of the chapters presents the material in a logical progression. If covered in a sequential fashion, the material in this book would span three one-semester courses. Therefore, a "virtual" table of contents, relating chapters by topic, has been provided. The instructor or student can utilize the virtual table of contents to focus on particular subsets of the material and formulate logically independent courses.

This book can be used either as a primary text or as a reference text in a computer architecture course beyond the elementary level. It can also support digital-system design courses ranging from the register-transfer level through the system organization level. Each of the sections of Part 2 given in the virtual table of contents, suitably augmented by selected introductory material from Part 1, would be sufficient for a quarter-length course on individual topics (e.g., microprogramming, memory hierarchies, concurrency, multiple-processors, networks, fault tolerance, language-based computers, and personal computing). Each section also provides sufficient detail to assign programming and/or design projects based on the principles discussed. Semesterlength courses can be developed by combining related sections (e.g., multiple-processors and networks, or language-based computers and personal computing systems). A subset of Part 3 on computer classes could form the basis of a course on instructionset design and evolution. Part 4 provides source material for an advanced course on computer families, including evolution and computer family planning for range and/or compatibility. The family evaluation methodology presented in Part 4 could be extended to other computer families. The January 1978 special issue on computer architecture of the Communications of the Association for Computing Machinery is an excellent supplement to Part 4.

This book can be used in both the curriculum for undergraduate programs in computer science prepared by the ACM Committee on Curriculum in Computer Science (C<sup>3</sup>S) and the IEEE's Curriculum in Computer Science and Engineering (CSE). This book provides material for the hardware portions of the ACM/C<sup>3</sup>S courses as illustrated in Table 1. [Austing et al. 1979].

For the extensive IEEE/CSE curriculum, with its emphasis on hardware, this book can be used for all computer organization courses, as well as for actual design examples for the digital logic courses. Table 2 on page xvi illustrates how portions of this text support the various topics included in IEEE/CSE courses.

The authors of this book wish to acknowledge a deep debt of gratitude to our many colleagues in the computing profession. Without their contributions and assistance this book could not have been written. We are especially grateful to the authors of papers who shared their design insights with us and to those authors who took time from busy schedules to write chapters specifically for this book. Our thanks also to individuals in various organizations who kindly responded to our numerous requests for information. A special debt is owed Digital Press for providing extensive excerpts from *Computer Engineering: A DEC View of*

|                    |        |                                                     | Specific topics<br>covered by                                 |                                       |

|--------------------|--------|-----------------------------------------------------|---------------------------------------------------------------|---------------------------------------|

| Level              | Course | e                                                   | "Computer Structures"                                         | Example chapters                      |

| Elementary level   | CS-4   | Introduction to Computer<br>Organization            | Basic logic design examples                                   | Chap. 2; Chap. 8; Chap. 15            |

|                    |        |                                                     | Hardware implementation of<br>instruction fetch, execute      | Chap. 8                               |

|                    |        |                                                     | Data flow and block diagram<br>of simple processor            | Chap. 8                               |

|                    |        |                                                     | Microprogramming                                              | Part 2, Sec. 1                        |

|                    |        |                                                     | I/O, interrupts                                               | Part 1, Sec. 2                        |

| Intermediate level | CS-6   | Operating Systems and<br>Computer Architecture I    | I/O, interrupts, addressing, microprograming                  | Part 1, Sec. 2; Part 2, Sec.          |

|                    |        |                                                     | Stacks, displays, reentrant programs                          | Part 1, Sec. 2; Chap. 16;<br>Chap. 17 |

|                    |        |                                                     | Memory management,<br>paging, segmentation,<br>virtual memory | Part 2, Sec. 2                        |

|                    |        |                                                     | Process management                                            | Part 2, Sec. 2                        |

| Advanced level     | CS-10  | Operating Systems and                               | -                                                             |                                       |

|                    |        | Computer Architecture II                            | I/O, interrupts, addressing                                   | Part 1, Sec. 2                        |

|                    |        | -                                                   | Concurrent processes                                          | Part 2, Sec. 2                        |

|                    |        |                                                     | Protection                                                    | Part 2, Sec. 2                        |

|                    |        |                                                     | Pipelining, parallelism                                       | Part 2, Sec. 3                        |

|                    |        |                                                     | Networks                                                      | Part 2, Sec. 5                        |

|                    |        |                                                     | Distributed systems                                           | Part 2, Sec. 4                        |

| Special topics     |        | Telecommunications/Networks,<br>Distributed Systems | Networks                                                      | Part 2, Sec. 5                        |

|                    |        | -                                                   | Distributed systems                                           | Part 2, Sec. 4                        |

### Table 1 ACM Committee on Curriculum in Computer Science

Hardware Design, by C. G. Bell, J. C. Mudge, and J. E. McNamara.

We are deeply indebted to Gary Leive for his many hours of writing, compiling, simulating, debugging, and formatting the many ISPs in the book. Over 9,400 lines of ISP were produced, of which only about a third appear here. A similar debt is owed Vittal Kini, who assembled the PMS diagrams and checked them for consistency. Jin Kim and Michael Tsao spent many hours assembling the artwork that had to be photographed.

Comments from several reviewers were particularly helpful. Lloyd Dickman provided a comprehensive review of the manuscript. Robert Sproull and John Wakerly offered substantial comments, as did Robert Stanton of IBM on the S/360-S/370 material. A careful editing of Part 1 was done by Eleanor Dickman.

The patience and encouragement of colleagues and students alike—especially Angel Jordan and Joe Traub—were deeply appreciated. In addition we would like to thank those we worked with at McGraw-Hill, particularly Richard Mickey, the copy editor, who worked long hours carefully preparing the manuscript for production. The patience and diligence of Mrs. Dorothy Josephson, who typed and retyped the many manuscript drafts and letters is worthy of special note. Finally, the support and understanding of our families and wives—Karon, Gwen, and Noel—were an essential ingredient in the completion of this book.

> Daniel P. Siewiorek C. Gordon Bell Allen Newell

1

### Reference

Austing et al. [1979].

| Course                                                                 | Topics covered by<br>"Computer Structures"                                                                     | Example chapters                      |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Switching Theory and Digital Logic:<br>DL-1 and DL-2                   | Programmable controllers; use of PLAs, ROMs                                                                    | Part 3, Sec. 1                        |

| Microprocessor Systems: DL-3                                           | Developments in LSI<br>Microprocessor architecture<br>Common microprocessors:<br>Calculator chips, bit slices, | Part 3, Secs. 1 and 2; Part 2, Sec. 1 |

|                                                                        | and monolithic microprocessors                                                                                 |                                       |

| Introduction to Computer                                               | Computer units                                                                                                 |                                       |

| Organization: CO-1                                                     | Microprogramming                                                                                               | Part 2, Sec. 1                        |

|                                                                        | Memory hierarchy                                                                                               | Part 2, Sec. 2                        |

|                                                                        | Input/output                                                                                                   | Part 1, Sec. 2                        |

|                                                                        | System structure                                                                                               | -                                     |

|                                                                        | Single-processor                                                                                               | Part 3                                |

|                                                                        | Multiprocessor                                                                                                 | Part 2, Sec. 4                        |

|                                                                        | Networks                                                                                                       | Part 2, Sec. 5                        |

|                                                                        | Evaluation                                                                                                     | Chap. 5                               |

|                                                                        | System examples                                                                                                | Chap 27                               |

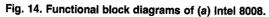

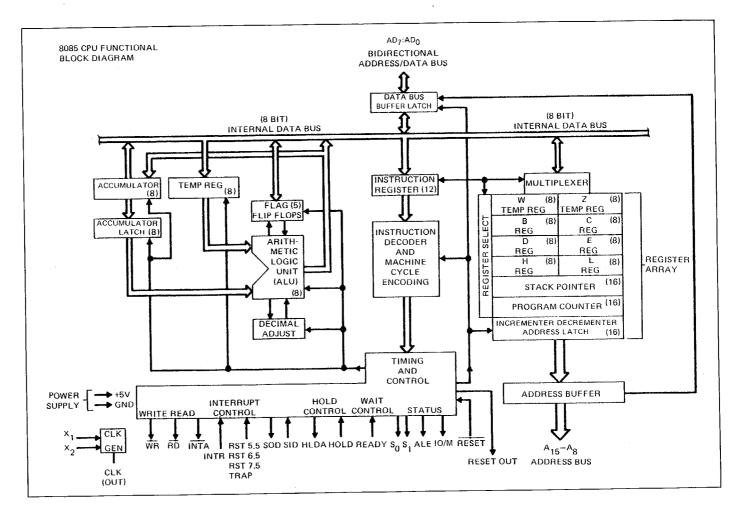

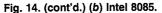

|                                                                        | Intel 8080<br>PDP-8                                                                                            | Chap. 37<br>Chap. 8                   |

|                                                                        | PDP-11                                                                                                         | Chap. 38                              |

|                                                                        | IBM \$/360 and \$/370                                                                                          | Chaps. 40, 41, 51, 52                 |

|                                                                        | CDC-6600                                                                                                       | Chap. 43                              |

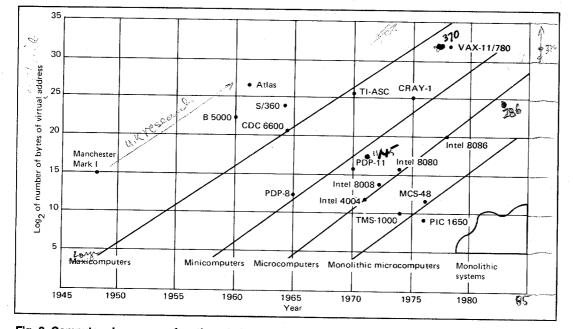

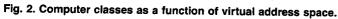

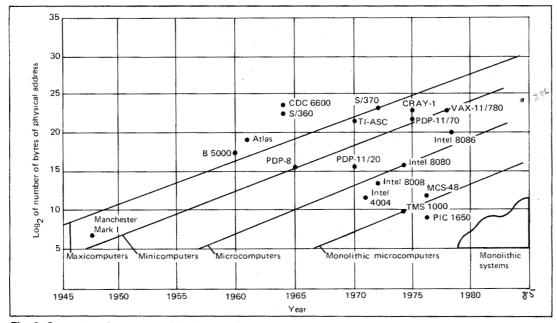

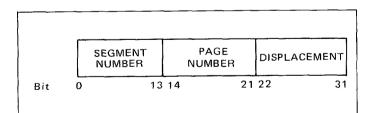

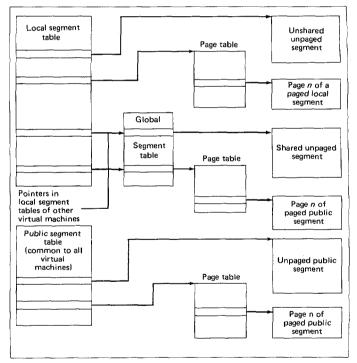

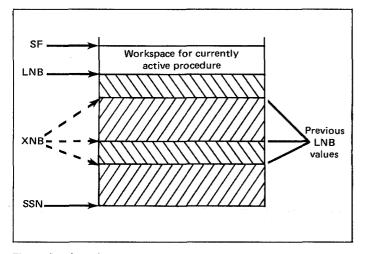

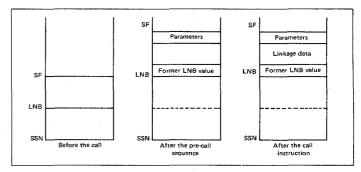

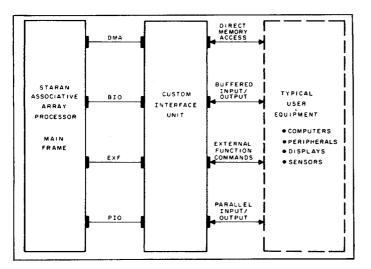

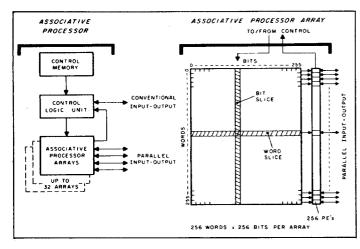

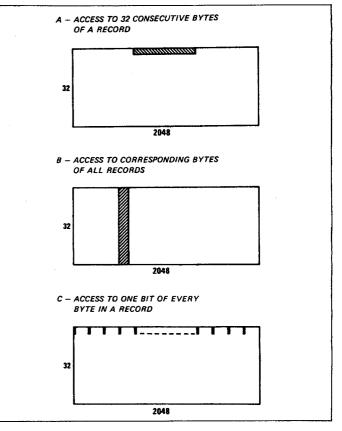

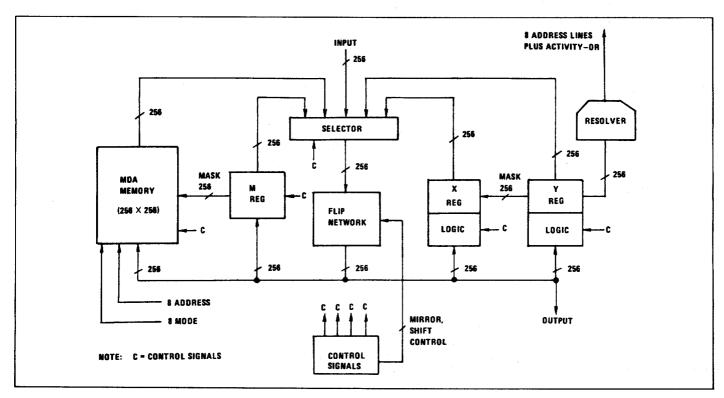

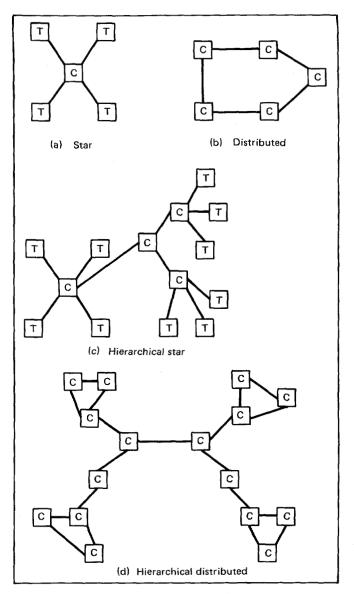

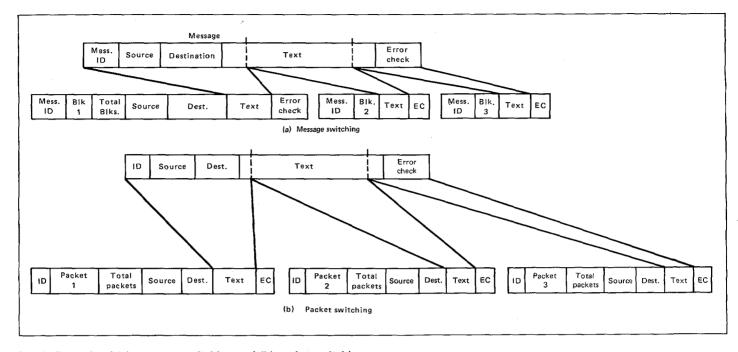

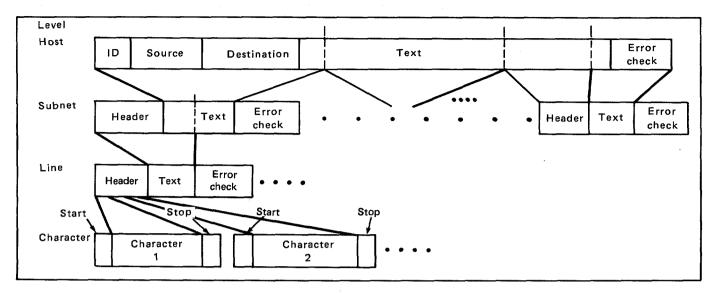

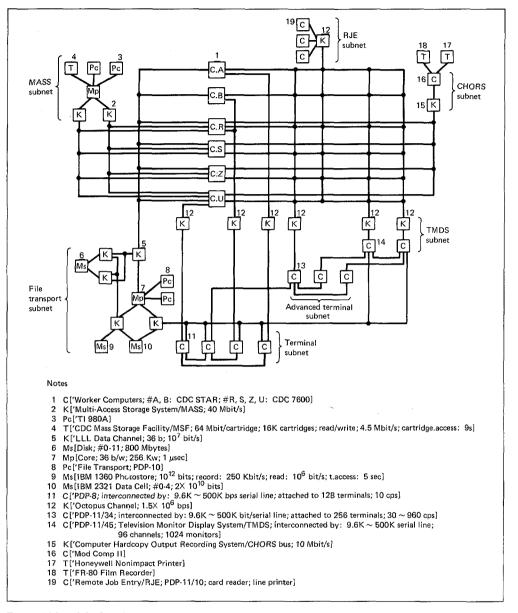

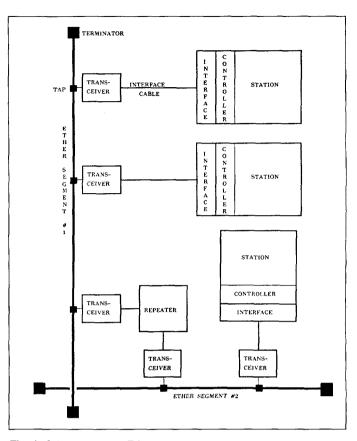

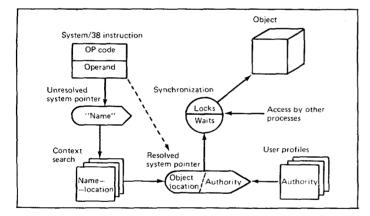

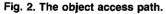

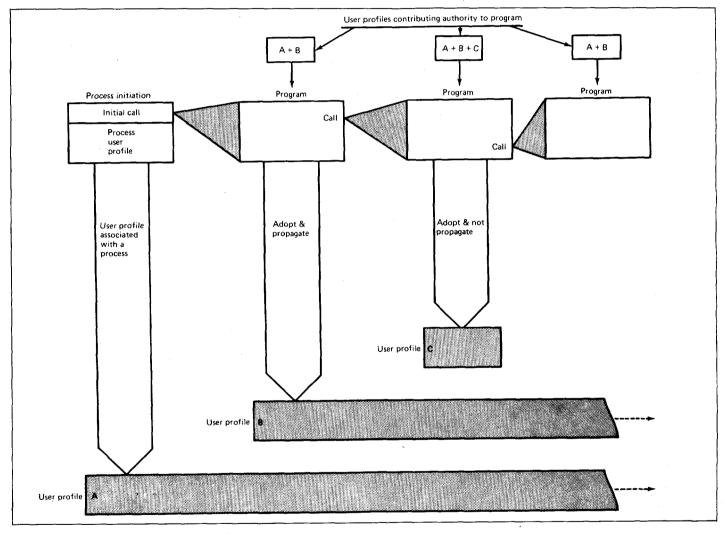

|                                                                        | Illiac IV                                                                                                      | Chap. 20                              |