#### CHAPTER 3 MODULES

Dick Best, Russ Doane, John McNamara

Before applying the views of computer systems, technology, packaging, and manufacturing, expressed in the previous chapters to the DEC computers discussed in the following chapters, a brief review of printed circuit module technology is in order. Module technology is important because modules were DEC's first products, and because the progress in semiconductor technology that has formed the major element of the technology push driving the computer industry is evident in module technology in a scale convenient for close examination and understanding.

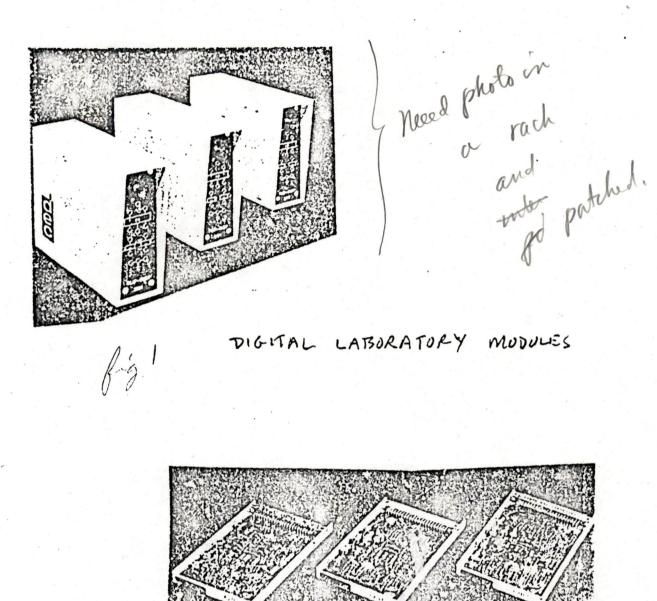

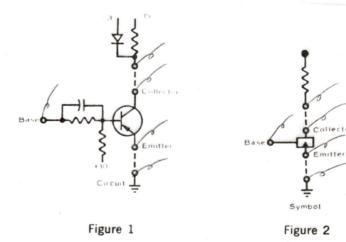

The first modules produced by DEC were called "Digital Laboratory Modules" and were intended to sit on an engineer's work bench and be interconnected with simple cords equipped with banana plugs. As shown in Figure 1, the modules were mounted in aluminum cases 1-3/4 by 4-1/2 by 7 inches in size, and all of the logical signals were brought out to the front of the case, where they appeared on miniature banana jacks mounted in a schematic diagram of the logical function performed by the module. The modules were offered in three speed ranges with compatible signal levels. The three speed ranges were 500 KHz, 5 MHz, and 10 MHz.

The Digital Laboratory Module product line was supplemented by the Digital Systems Modules. These modules, samples of which are shown in Figure 2, were

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 2

identical to the Laboratory Modules in circuitry, signal levels, and speed range, but had a different packaging scheme. The System Module packaging was designed for rack mounting and used 22-pin Amphenol connectors at the backs of the modules rather than banana plugs at the front. The System Module mounting method was chosen for the PDP-1 computer.

The circuits used in both module series were based on the M.I.T. Lincoln Laboratory TX-2 computer circuits. All of the TX-2 basic circuits were used, except those gates which used emitter followers. The emitter follower gates were not short circuit proof, and it was felt that misplaced patch cords in Laboratory Module configurations or slipping scope probes in System Module configurations would cause a high fatality rate for those circuits.

A brief review of some of the circuits follows to indicate how much present day logic design differs from logic design of twenty years ago. Today designers deal with ALUs and microprocessors as units, whereas twenty years ago, single gates were units.

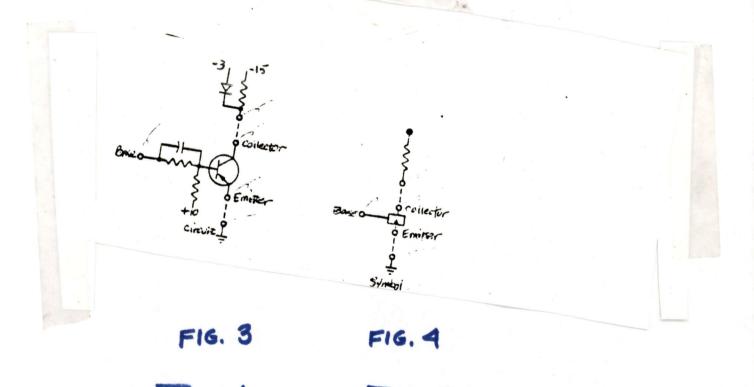

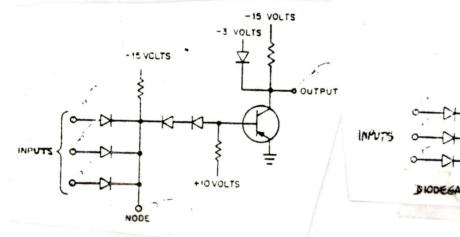

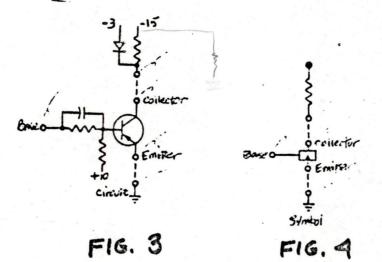

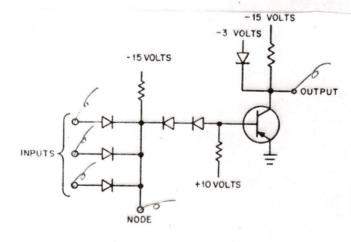

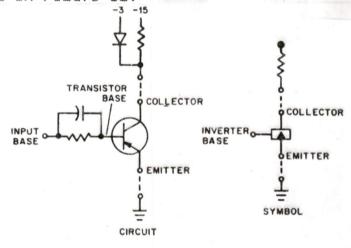

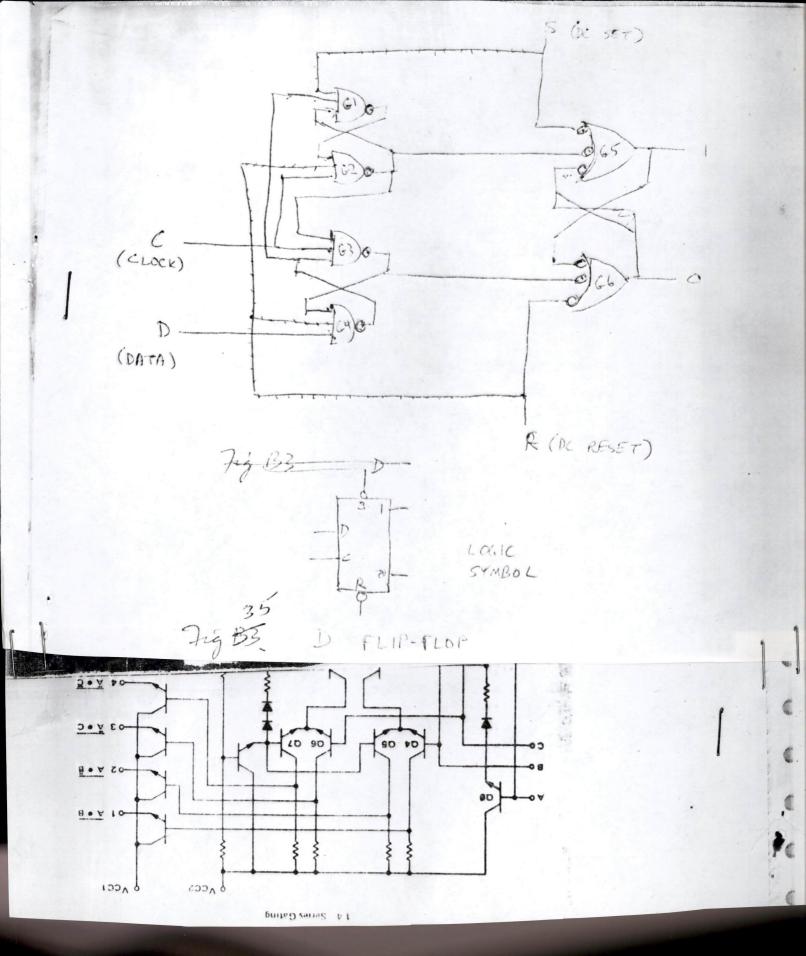

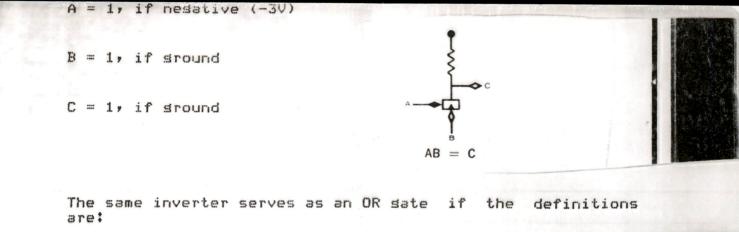

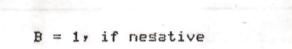

In the early module designs, most logical operations were performed using saturating PNP germanium transistors, as described in Chapter 3. While the use of transistors in radios and television sets relies on the linear relationship between base current and emitter/collector current to provide the amplification of radio frequency and audio frequency signals, the use of transistors in computer circuits (except those using ECL) relies primarily on the behavior of transistors in either the saturated state or the cut-off state. The use of transistors in such circuits can best be appreciated from the simple example shown in Figure 3.

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 3

Figure 3 is a schematic of an inverter. If the base lead is brought to a sufficiently negative voltage, the resulting base current will saturate the transistor, effectively connecting the emitter to the collector. If, on the other hand, the base is grounded, no base current flows, no emitter/collector current will flow, and the transistor will be in the cut-off state. The collector would then assume the voltage of the negative voltage source, were it not for the "clamp diode" which limits the voltage of the collector to -3 volts.

Inverter (Se hematic)

Inverter (Symbolic)

Edited 3/17/78

page 4

R. Best, R. Doane, J. McNamara

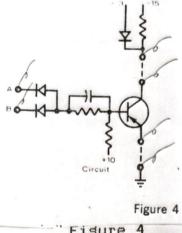

To simplify the logic drawings, a symbolic drawing like that in Figure 4, was customarily used to represent this circuit. Note that neither Figure 3 nor Figure 4 shows the emitter directly connected to ground or the collector directly connected to the negative supply. Rather, a dotted line is shown. This is because Laboratory Modules and System Modules often used a series connection of up to three inverter gates between the negative supply and ground to accomplish various logical functions. This practice would seem strange by today's standards because today's transistors use silicon and each saturated transistor has a 0.7 volt voltage drop across it. In Laboratory Modules and System Modules, germanium transistors were used, and these had only about a 0.1 volt voltage drop.

The Digital Laboratory Modules and the Digital System Modules used a dual polarity logic system employing both levels and pulses. The logical voltage levels were -3 volts and ground. Correspondence between the logic state, ONE or ZERO, and the voltage levels of -3 and ground were indicated at each point in the logic diagram by a diamond. The diamond defined the necessary voltage level for the action desired. A solid diamond denoted that a -3 volt level was an assertion , and a hollow diamond indicated that a ground level was an assertion.

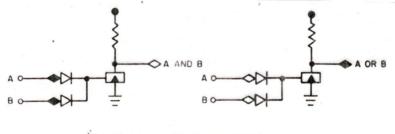

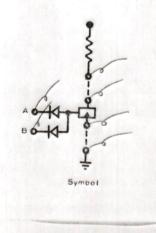

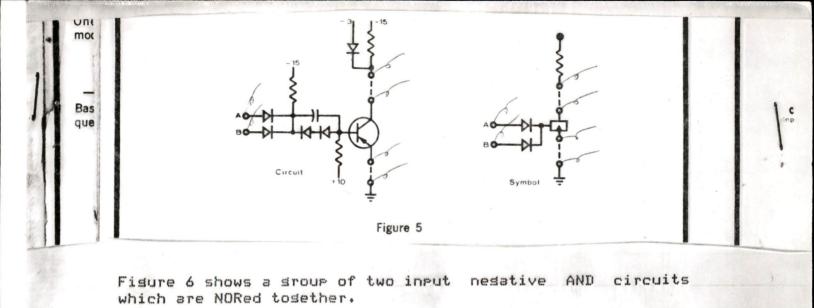

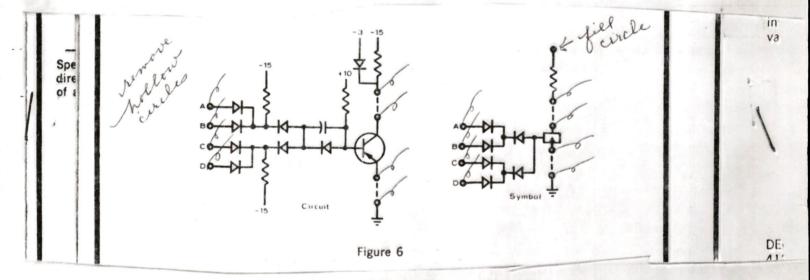

Series arrangements of inverters, while useful, were not sufficient to provide all logical functions. A more general arrangement was to add diodes to the circuit of Figure 3 to form NAND gate or NOR gates, as shown in Figures 5 and 6.

Figs 5\$6 tube sufflied.

R. Best, R. Doane, J. McNamara

Edited 3/17/78

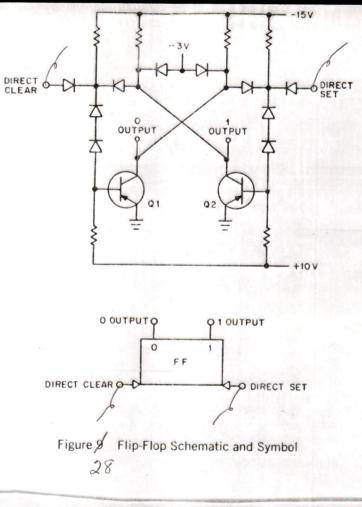

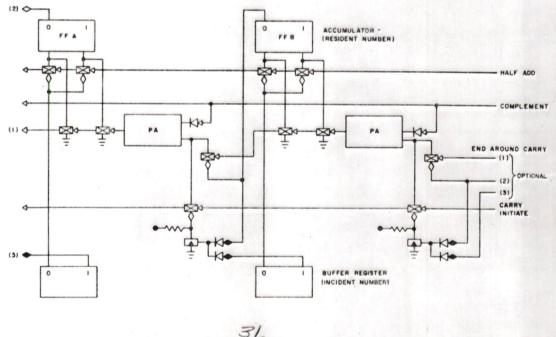

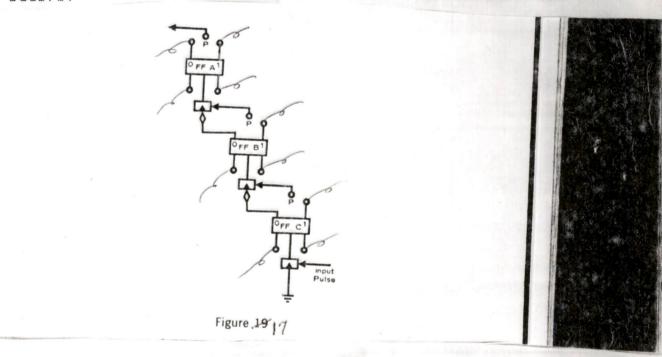

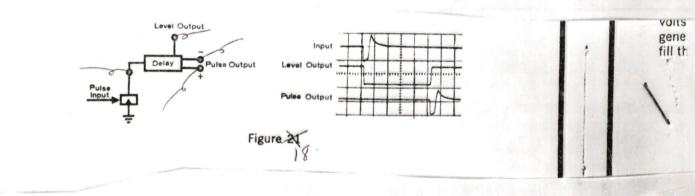

Except for very small amounts of delay, the inputs and outputs of these circuits changed simultaneously, thus no information was stored. The storage of information was accomplished by bi-stable devices called "flip-flops" whose state was controlled by the application of pulses. Before discussing the construction of flip-flops, therefore, it is necessary to briefly describe the generation of pulses.

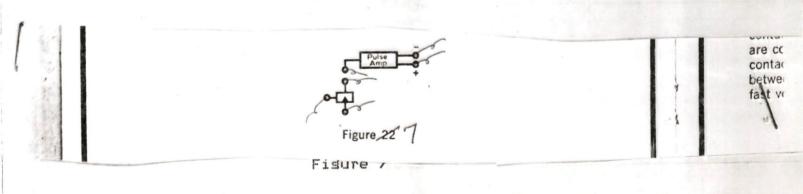

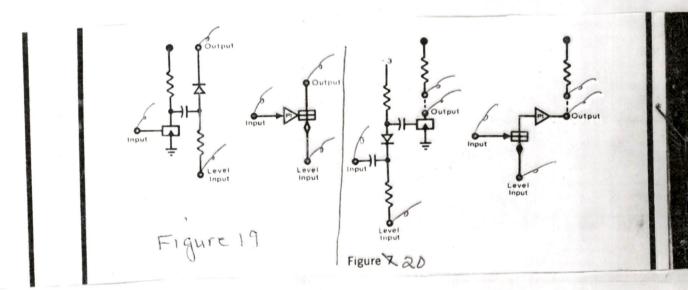

Pulses, which were used both in NAND/NOR circuits like those in Figures 5 and 6 and for controlling flip-flops, were generated by pulse amplifiers. Pulse amplifiers were very powerful logical elements because they not only amplified and standardized the shapes of pulses, but they also gated pulses. This latter feature meant that when the same logical gating was to be done on a whole register of flip-flops, it could often be done once, at the pulse amplifier which drove the register. The pulse amplifier would typically be arranged to operate in response to a pulse or level change and produce an output via a pulse transformer. The pulse transformer had both terminals of its secondary winding available so that either positive or negative pulses (ground to -3 volts and back to ground) was represented in the logic drawings by a solid triangle, and a positive pulse (-3 volts to ground and back to -3 volts) was represented by a hollow triangle.

The use of pulses is emphasized a great deal in the following discussion because the concept of gating a pulse at the source and using the gated pulse to transfer data from register to register on a parallel basis used an absolute minimum of logic. This method was referred to as "East Coast" logic, while "West Coast" logic used gating at each bit position to do parallel

page 5

\_\_\_\_

Chapter 3 page 6

R. Best, R. Doane, J. McNamara

Edited 3/17/78

tranfers. These distinctions seem strange in the 1970's when gates are much cheaper than "a dime a dozen", but in the late 1950's and early 1960's much of computer design involved this level of component reduction ingenuity.

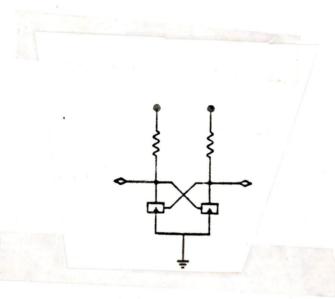

## F16. 7

Basic FLir-FLOP

Returning to the discussion of gates and flip-flops, a primative flip-flop can be obtained by interconnecting two grounded emitter inverters as shown in Figure 7. When one inverter is cut-off, its output is negative. This holds the

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 7

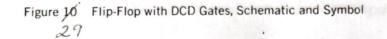

other inverter on, which in turn holds the first inverter off. If an additional inverter circuit is added to the circuit of Figure 7, the circuit of Figure 8 is obtained. The application of a negative pulse to the input of the additional inverter changes the state of the flip-flop. In the actual implementations of DEC Laboratory Module flip-flops, buffer amplifiers were added to the outputs to permit a single flip-flop to drive the inputs of many other gates. The buffer amplifiers also provided delays at the outputs of the flip-flops such that the output did not change until after the activating pulse was over. This permitted the state of the flip-flop to be sensed while the flip-flop was being pulsed, a necessary feature for the simple implementation of shift registers, counters, and adders.

FIG. 8 Flip-Flop @ INVERTER

Chapter 3 page 8 R. Best, R. Doane, J. McNamara Edited 3/17/78

Collections of the inverters, gates, and flip-flops just described were packaged in appropriate quantities (i.e. as many as would fit within the size and pin contraints) and sold as Laboratory Modules and System Modules. There were a relatively small number of module types available in the Laboratory Module Series. For example, in the first product line, the 100 Series:

| 103 | 6 | Inverters                                   |

|-----|---|---------------------------------------------|

| 110 | 2 | 6-input negative diode NOR's                |

| 201 | 1 | buffered flip-flop                          |

| 302 |   | one-shot                                    |

| 402 | 1 | clock pulse generator                       |

| 406 | 1 | crystal clock                               |

| 410 | 1 | Schmitt trigger circuit pulse generator     |

| 501 | 3 | level standardizers                         |

| 602 | 2 | pulse amplifiers                            |

| 550 | 1 | tube pulser (15 volt 100 nanosecond pulses) |

| 667 |   | level amplifiers (0 to -15 volts)           |

| 801 | 1 | relay                                       |

By contrast, there were many System Module types developed. With their higher packing density, lower cost, and fixed backplane wiring, they were used for computers, memory testers, and other complex systems of logic.

It is interesting to note that a large percentage of the modules on the above list were used for the generation and conditioning of the pulses and levels used in the relatively small number of logic circuits. Reference to a present day IC catalog would reveal very few pulsing and clocking circuits and a great many logic circuits. The emphasis on pulses was one of economy, as noted previously.

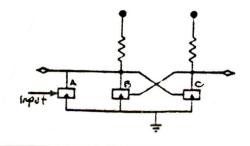

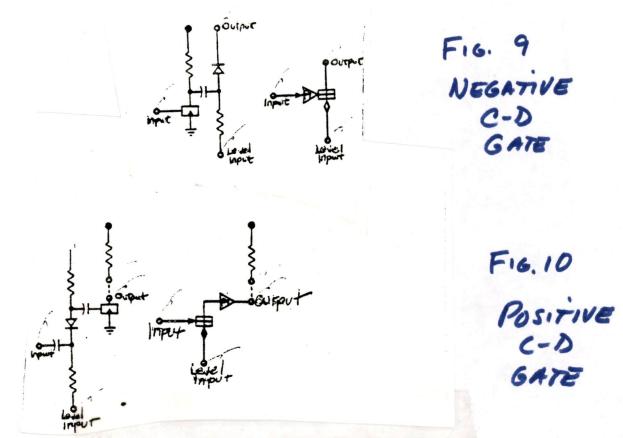

In 1960 DEC began building modules with slightly different circuitry than that described above. While transistor inverters, buffered delayed flip-flops, and their associated pulse logic were the best choice for 5 and 10 MHz logic, C-D (capacitor-diode) gates and unbuffered flip-flops were found preferable for

| Chap | oter 3   |        |           |         |       |         |     |       |      | page    | 9   |

|------|----------|--------|-----------|---------|-------|---------|-----|-------|------|---------|-----|

| R. E | Best, R. | Doane, | , J. McNa | mara    |       |         |     |       | Edit | ed 3/17 | /78 |

| low  | speed    | logic  | because   | greater | logic | density | and | lower | cost | could   | be  |

| achi | eved.    |        |           |         |       |         |     |       |      |         |     |

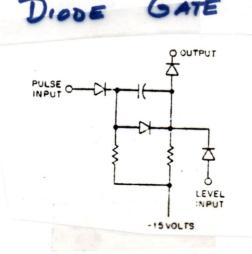

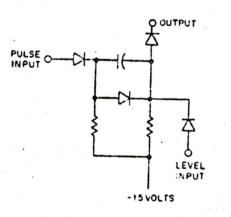

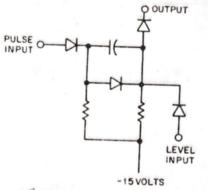

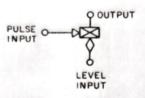

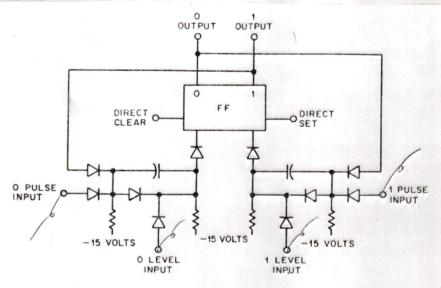

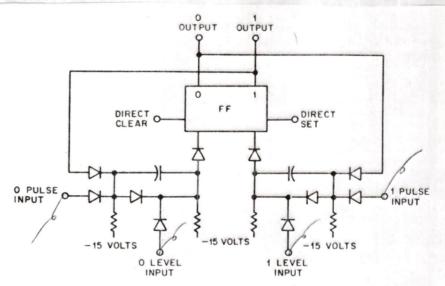

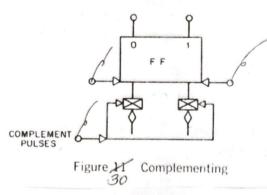

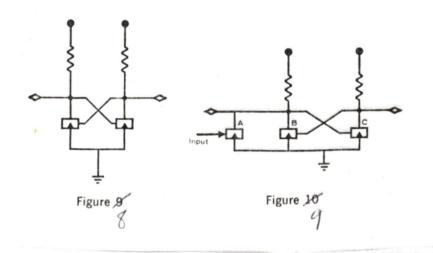

A negative capacitor-diode gate is illustrated in Figure 9. With both the level input and the pulse input at ground for sufficent time to allow the capacitor charge to reach three volts, a negative level change or a negative pulse at the pulse input will cause a positive pulse to appear at the output. Such gates could drive the direct set input of any flip-flop which required a positive pulse, and were built into some unbuffered flip-flop inputs to be used for shifting and counting. tthe importance of the losic

The significant aspect of the logic was that

It was quite easy to so from basic losi resister transfer level structures

to the Ja logica/diagrams using the initial systems modules . The If we - Assuming there is a basic A ) In the PDP-1, the Addumulator was the basic store resister the second g in which all arithmetic re operations were carried out, tosether with operatndy that eminated from memory and were held in the Memory Matter Buffer resister, MB.

Fisure \_\_\_\_shows a simp the simplified and del detailed

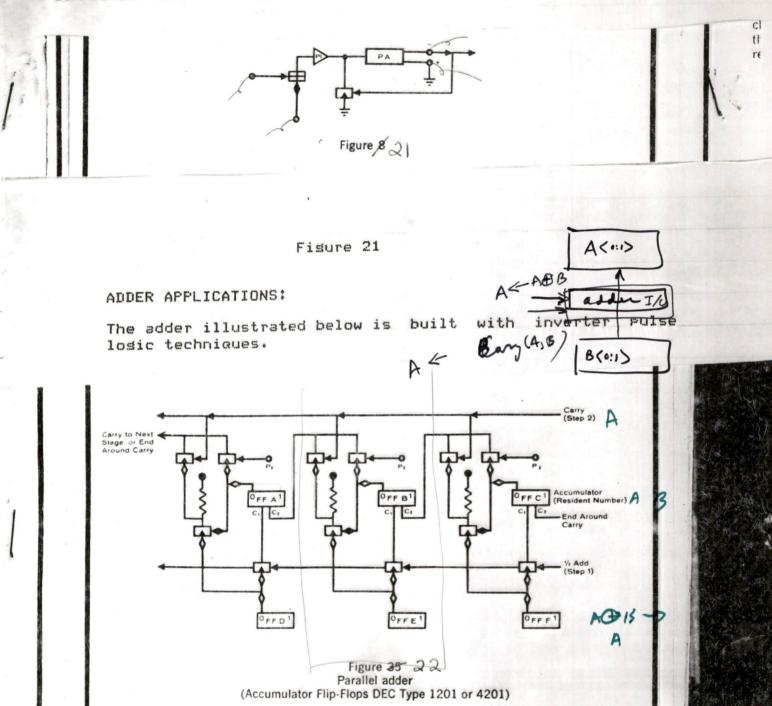

Figure 2 shows the interconnection of the two resistert both in simplified form and with all the resister transfer commands that & could be siven by the control section of the computer s which effe effect operations on the resisters (in this case just the AC). Note: there are 5 basic five five opertations can be carried out on the accumulator (the there were

PDP-1

corresponding Fisure D' shows the losic diagram for 1 bit of the accumulator and MB for the operations The first operatin to clear the WAC is carried out siven in the 🖌 resister transfer diagram.. by just & pulsing connecting a pulse amplifer to all 18 bits of the a AC & and Complementing the

the via AC is carried out by connecting a transistor to ground connecenting a transitor of one of the complementeing the inputs, & and short emitting a negative pulse. Addition is done the a two step processs: fist, the MB and AC is siden half added to the AC using the exclusive or operation where the AC is complemented if the corresponding MB bit is a one; second, the carry operation is given. Carry is slightly more complex and

consists

-to the next but

A carry at a given bit position is initiated if the AC is 0 (it had been a 1 of and

MB is 1 and the AC is 0 (corresponding on to an ititial condition of two 1s before the half add. Once a carry is started at a digit, it Genetit and eminates from the carry proposate line, pe, flip flops carry proposate signal, P2 P; -a carry will continue to propsate if each bit of the AC is a 1. A In this ways a Luca the propogate output, P2 ( a pulse ) In a simlar way, a one can be added to the accumulator by simpy pulsing the least signifcant

disit of the AC and having it proposate along all the disits that are one,

complemnting the each disity of the AC as propagates from from digit to digit.

Here, the relation ship between a one is emitted pulse is emitted from

inserted into the carry propste input, c2. the carry proposste liner P2, if a o sulse is

les anjulifier for revoking operation d because the buffered flip flops privided by Th

r

the put interest of the state

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 10

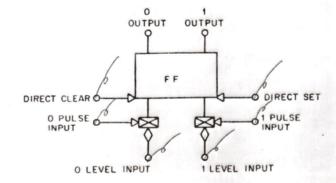

A positive capacitor-diode gate is illustrated in Figure 10. With the level input at -3 and the capacitor input at ground for a sufficient time to allow the charge on the capacitor to become stable, a negative level change or a negative pulse at the capacitor input will cause the transistor to conduct, grounding the output for an amount of time determined by the gate time constant or the input pulse width, whichever is shorter. Gates of this type were not cross-coupled to form flip-flops, but could be used to set and clear unbuffered flip-flops by momentarily grounding the correct flip-flop outputs in a fashion similar to the inverter gate that was added to Figure 7 to obtain Figure 8.

The principal advantages of the capacitor-diode gates were:

- 1) The level input to the gate was used to charge a capacitor and was isolated from the rest of the circuit by a diode. Thus, no DC load was presented to the circuit driving the level input of a C-D gate.

- 2) The resistor-capacitor time constant of the gate required that the conditioning level be present a certain amount of time before the pulse input occurred. This introduced a delay between the application of a new gate level and the time the gate was conditioned, and allowed the sampling of unbuffered flip-flop outputs at the same time that the flip-flop was being changed.

- 3) The resistor-capacitor combination differentiated level changes, permitting a level change to create a pulse.

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 11

The use of saturating MADT transistors and toroidal pulse transformers appeared to be nearing an operating limit at 10 MHz. The pulses needed to operate the circuits shown in the previous diagrams were 40% of the cycle time of 10 MHz logic, tightly constraining transformer recovery time and making it difficult to design circuits that were not excessively sensitive to repetition rate. Furthermore, gate delays were large enough to prevent some needed logic configurations from propagating within the 100 nanosecond interval implied by the 10 MHz rating.

A major break with previous circuit geometries appeared necessary. The use at IBM of non-saturating logic encouraged an exploration in that direction. The project was called the "VHF Logic" project because operation at 30 MHz or better (the bottom end of the VHF radio band) was the goal.

The complex 30 mHz flip-flops were packaged one to a module, so a great many interconnections were needed to implement logical functions. In systems designed for 30 MHz operation, the use of leads longer than a few centimeters was expected to require special care, hence the availability of a satisfactory transmission line hookup medium was felt to be an essential element for ease of use. A new solid wall coaxial cable had just been introduce, the 50 ohm impedance version of which was chosen to hook up the VHF modules. It appeared to have a strong enough center conductor for practical hookup between modules while not being too bulky for easy hand bending.

Due to the low impedance needed for the coaxial cable connections, substantial driving current was necessary to achieve adequately high signal voltages, and hence considerable power had to be dissipated. The ability to

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 12

drive a load at any point along the transmission line was deemed necessary for practical hookup, and 3 volt swings had to be available for compatibility with existing modules. These needs were met by choosing a 60 milliampere output current, producing a 1.5 volt swing on a double-terminated 50 ohm line and a 3 volt swing with a 50 ohm load when interfacing to existing slower logic. These voltage and current levels required the addition of heat sinks to the output transistors. This was accomplished by installing spring clips that fastened the cases of the transistors directly to the connector pins, exploiting the connectors as heatsinks and at the same time providing a minimum inductance connection from the transistor collector (common to the case) out of the module.

The VHF modules contained a novel delay line implementation which has reappeared in recent days in the ECL boards of the KL10 processor. Flip-flop feedback delay was provided by a 10 nanosecond stripline etched onto the printed circuit board. A meander pattern was selected with a degree of local coupling between the loops to achieve a seven to one delay to risetime ratio. Eoth the delayed and undelayed ends of this 50 ohm stripline were made available at the module pins. The undelayed outputs switched simultaneaously with the flip-flop outputs, allowing a subsequent gate to subtract a delayed flip-flop output from the undelayed complement output side of the flip-flop and produce a 10 nanosecond pulse when the flip-flop changed state.

The performance of the VHF modules was rated at 30 HMz, which was the limit of the module testers used on the production floor. Bench testing demonstrated 40 MHz capability with the promise of 50 MHz performance if adequate testing apparatus could be found. Risetimes were better than 1.

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 13

Modules delivered to customers were used to build satisfactory high performance systems, but the need for such high performance was not widespread. In addition, the product development cycle was by the standards of the time quite long (two years) and the enthusiasm for the VHF modules amongst the DEC engineers flagged, further attenuating product momentum. Despite their failure as a product, the VHF modules eventually made a contribution to computer progress. To produce timesharing systems, the PDP-6 needed a way of comparing relocated addresses at very high speed. A high speed register comparator was quickly designed using current mode logic similar to the VHF modules.

As a series of general purpose products for engineers to use, the cost of the VHF modules and the inconvenience of their wiring was too great. Further developments in general purpose logic modules were to lie in the opposite direction: cheaper, more compact, easier to use, and slower.

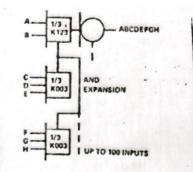

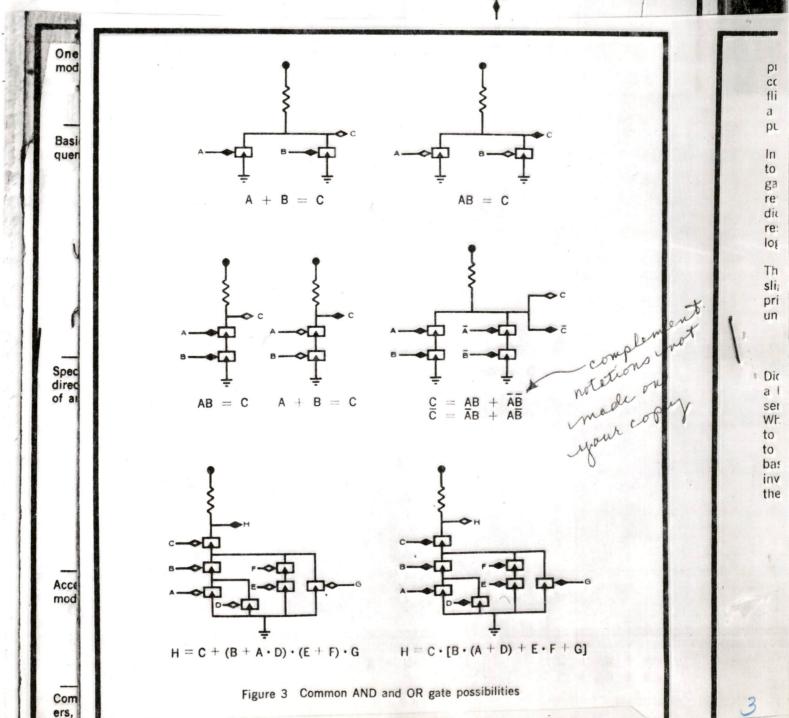

By 1964 the decreasing cost of semiconductors during the early 60's had caused the cost of System Module mounting hardware to become a significant portion of the total module cost. In response to this trend, a new type of module was developed which was a 2.5 by 5 inch printed circuit card with a color coded plastic handle. The printed circuit card provided its own mechanical support there was no metal frame around it as there had been in the System Module design. The new modules, called Flip-Chip modules, plugged into connector blocks that could support eight such modules.

The first series of the new modules was designated the "R-Series" and was identified by using red handles. The R-Series circuits were a reaction to the

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 14

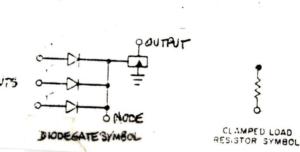

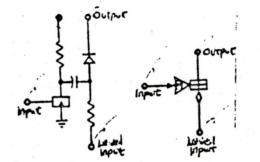

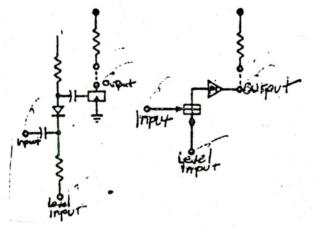

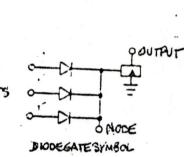

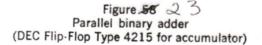

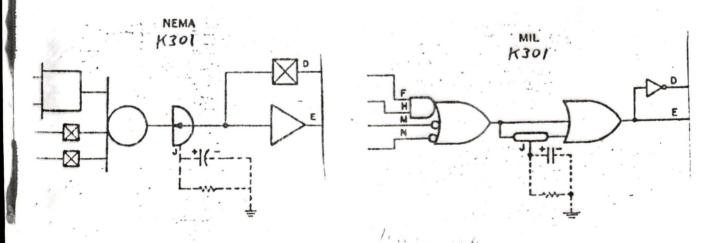

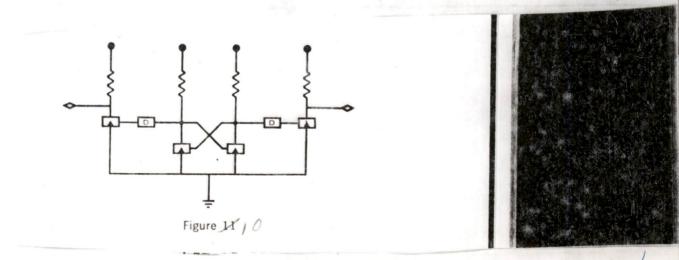

rather complicated set of usage rules developed for the previous products. The goal was to make these easy to use and inexpensive . Integrated circuits were not used because they were more expensive than discrete components and the computer industry had not yet decided on the type of integrated circuit to use. The building block for R-Series logic was the diode gate, a sample of which is shown in Figure 11. The other basic circuit was the DCD (diode-capacitor-diode) circuit shown in Figure 12. The DCD gate was used to provide standardized levels to active devices such as flip-flops and to produce the logical delay necessary to sense and change flip-flops at the same time.

F16. 11

FIG. 12 DCD GATE

R. Best, R. Doane, J. McNamara

Edited 3/17/78

A second series of the new modules was developed for the first PDP-8s. This series was called the S-Series, although it also had red handles. The S-Series modules used the same circuits as their R-Series counterparts, but with variations to the values of the load resistors and DCD gate storage capacitors to obtain greater speed.

The E-Series with blue handles was essentially the same as the 6000 series of 10 MHz System Modules, but repackaged on the new 2.5 inch by 5 inch cards, and used silicon transistors rather than germanium transistors. The new silicon transistors were a mixed blessing. While they had temperature sensitivity characteristics superior to those of the germanium transistors, and their voltage drop characteristics permitted the elimination of the bias resistor to +10 volts, they did not saturate as well as the germanium transistors. Because they did not saturate well, the voltage between the collector and the emitter in the saturated state was not as low as it was with germanium transistors. This meant that the series arrangement of three inverters discussed in conjunction with the dotted lines in Figure 4 could not be used. Instead, only two of the silicon transistor inverters could be connected in series if the output was intended to drive another inverter. The first computer to use the B-Series modules was the PDP-7.

Analog applications were the target market for the A-Series modules, which had amber handles. This series, still being manufactured today, includes analog multiplexers, operational amplifiers, sample and hold circuits, comparators, digital to analog converters, reference voltage supplies, analog to digital converters, and various accessory modules. The peak development rate for analog modules occurred in 1971 with 38 new types and declined to 5 new types

page 15

Chapter 3 page 16 R. Best, R. Doane, J. McNamara Edited 3/17/78

------in 1977.

While all of the preceding modules had been designed as user-arrangeable building blocks, the green handled G-Series was intended for modules that would only be sold as part of a system. For example, all of the DEC core memory circuits have been in the G-Series because a core memory system is sufficiently complex that a cookbook approach using a standard series of modules is not appropriate. The G-Series is still actively used today for circuits other than logic, generally in peripheral devices such as disks, tapes, and terminals.

Like the A Series and G Series, the W (white handle) Series is still manufactured, and is used to provide intput/output capability between Flip-Chip modules and other devices. Lamp drivers, relay drivers, solenoids drivers, level converters, and switch filters are included in this family, but the only modules used widely today are the W900-W999 modules which include cable termination modules and blank boards upon which the user can mount ICs and wire wrap them together.

While the W-Series provided a variety of interface capabilities, the circuitry used therein was still too fast for typical industrial applications. Computer-oriented logic, by its very nature, is high speed and provides noise immunity far below that required in small-scale industrial control systems located physically close to the process they control.

Unfortunately, industrial electrical noise is not predictable to the nearest order of magnitude. Thus, attempts to solve the problems with "high level Chapter 3 page 17

R. Best, R. Doane, J. McNamara

Edited 3/17/78

logic" whose voltage thresholds were merely a few times greater than computer-type logic levels did not work well.

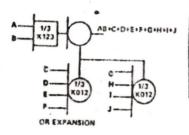

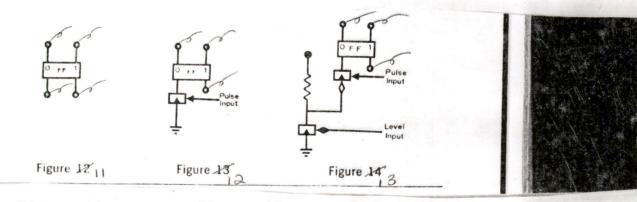

A new series of modules, the K-Series (with blac(K) handles), was developed which relied on a combination of voltage, current, and time thresholds to protect storage elements such as flip-flops and timers from false triggering. Since industrial controls typically interact with physically massive equipment, time thresholds are particularly attractive. There are four ways of exploiting these:

- 1) basic 100 Khz slow-down circuits everywhere

- 2) optional 5 KHz slow-down circuits available

- 3) transition-sensitive (edge-detecting) circuits provided with hysteresis to allow additional discrete capacitor loading when all else fails

- 4) replacement of the conventional monostable multivibrator or "one-shot" circuit by a timing circuit having both a low impedance and hysteresis at the input.

The hardware for the K-Series was specially designed to fit the NEMA (National Electrical Manufacturers Association) enclosures traditionally used with relay implemented industrial controls, but used the same connectors as the other Flip-Chip modules. Sensing and output terminals were provided with screw terminals and indicator lights, and appropriate arrangements were made to interface with 120 VAC devices. Wire wrap terminals were protected from external voltages but were available for oscilloscope probes. Magnetically latched reed relays and diode arrays that could be programmed by snipping out diodes were provided as memory elements that would retain data during power

Chapter 3 page 18 R. Best, R. Doane, J. McNamara Edited 3/17/78

failures.

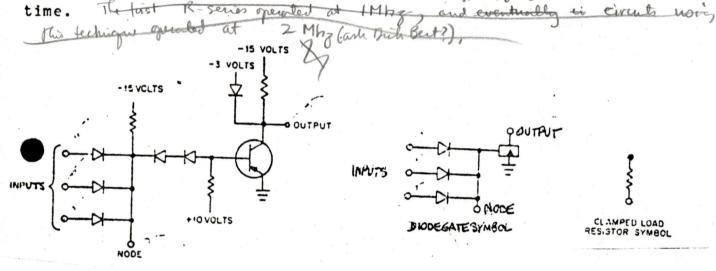

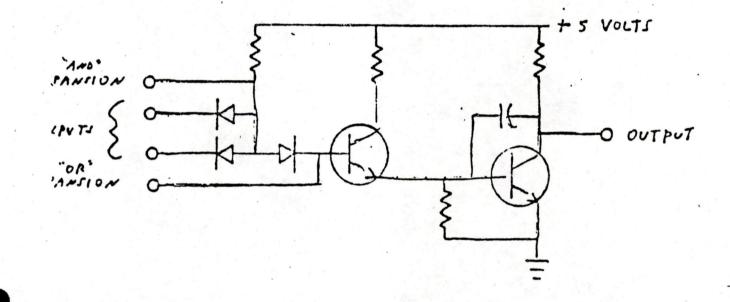

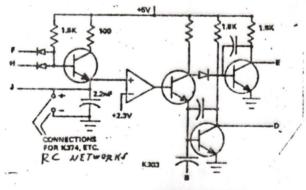

# FIG. 13 K-Series Circuit

Gating in early K-Series modules was accomplished with discrete diode-transistor circuits such as that shown in Figure 13. Other K-Series modules used integrated circuits for the logic functions. In these designs the inputs to the ICs were protected with filter/trigger circuits which filtered out the noise and then restored the fast rise-times required by the ICs. Outputs were protected from output-induced noise and converted to standard

gates.

Unlike other DEC modules, the K-Series modules were not directly useful for constructing computers or computer-like data processing subsystems due to their low speed and high cost. They did play an important part in bringing digital logic into industrial applications, and the noise protection techniques developed for these modules were useful in the design of the PDP-14 Industrial Controller (Chapter 6).

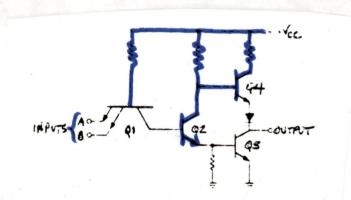

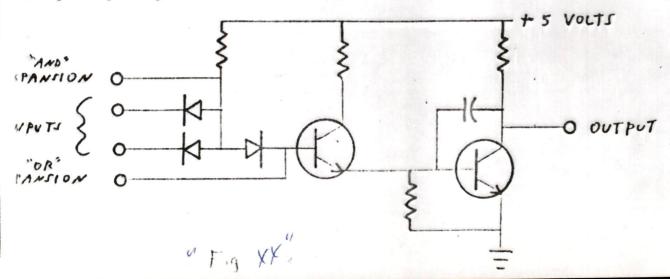

By 1967 the electronics world had settled on transistor-transistor-logic (TTL) as the technology of choice for integrated circuits and the cost for logic functions implemented in TTL ICs had dropped below that of discrete circuit implementations. With much more logic fitting into the same printed circuit board area, a single Flip-Chip card could now accommodate much more complicated functions. However, there were not enough connector pins available to get the necessary signals on and off the card. The answer to the problem was to keep the cards the same size, but to have etch and associated contacts on both sides of the printed circuit board. This increased the number of contacts from 18 to 36, and a new series with magenta handles (M-Series) was born. Subsequently, some G-Series and W-Series modules were also designed with ICs and double sided boards.

The advent of TTL brought the first power supply and signal level change in DEC's history. The -15 volt and +10 volt supplies were no longer required. Only a single +5 volt supply was needed to supply the logic signals which were now 0 and +3 volts. The packaging was kept consistant, however, as the old Chapter 3 page 20

R. Best, R. Doane, J. McNamara

Edited 3/17/78

single-sided modules could be plugged into the new connector blocks, and careful attention to pinning arrangements allowed double-sided module to be used in a single sided block at a sacrifice of some circuits.

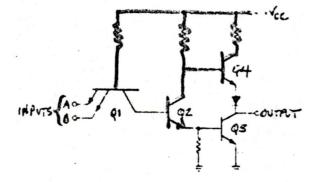

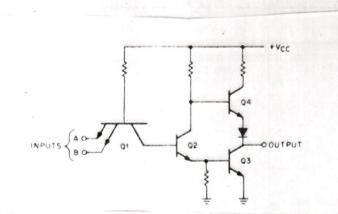

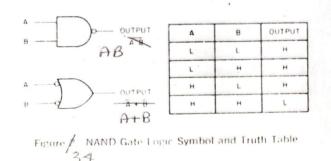

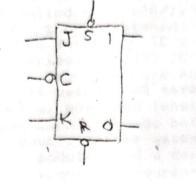

The basic TTL circuit is the NAND gate shown in Figure 14.

## FIG. 14 TTL NAND Circuit

The input of the TTL gate is a multiple emitter transistor. If either input is

R. Best, R. Doane, J. McNamara

------

Edited 3/17/78

\_\_\_\_\_

page 21

at or near ground (0 to 0.8 volts), Q1 becomes saturated, bringing the base voltage of Q2 low, turning off Q3 and turning on Q4 making the output high (+2.4 to +3.6 volts). If both inputs are high (above 2.0 Volts), Q2 has base current supplied to it through the collector diode of Q1, turning Q2 on. This in turn provides base current to Q3, saturating it and cutting off Q4, making the output low (0 to 0.4 volts).

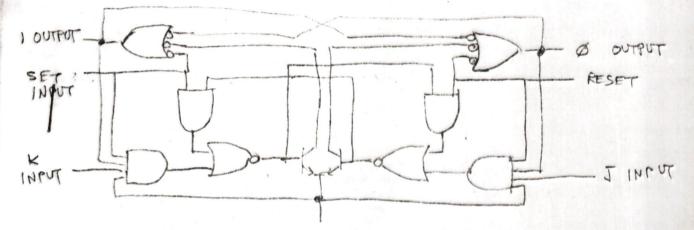

Like the transistor inverter circuits discussed in conjunctuion with System Modules, TTL NAND gates can be cross-connected to form flip-flops.

The first generation of M-Series modules were used in a redesign of the PDP-8 called the PDP-8/I. The circuits used in these modules used TTL integrated circuits which were called "7400 series" integrated circuits because of a growing tendency in the semiconductor industry to standardize part numbers for TTL circuits, calling a package of 4 NAND gates a 7400, a package of six inverters a 7404, etc. The KI10 processor used in the PDP-10 was designed from higher speed circuits using the 74H00 series of TTL integrated circuits. The 74H00 circuits were similar to the earlier 74 series, but were faster and used much more power. The first PDP-11 (the PDP-11/20) used both 7400 and 74H00 series ICs, as did the PDP-8/E. Both of these latter machines used 8.5 inch by 10.4 inch "extended quad" modules.

In 1970 an M-Series 18-bit machine, the PDP-15, was constructed. It was the last of a generation which started with the PDP-1 (System Modules), and grew through the PDP-7 and PDP-9 (B-Series modules). The PDP-15 and the PDP-11/45 used Schottky TTL, a circuitry with such rapid switching speeds that four-layer boards had to be used such that the inner layers of power and

Chapter 3page 22R. Best, R. Doane, J. McNamaraEdited 3/17/78

ground etch could provide shielding.

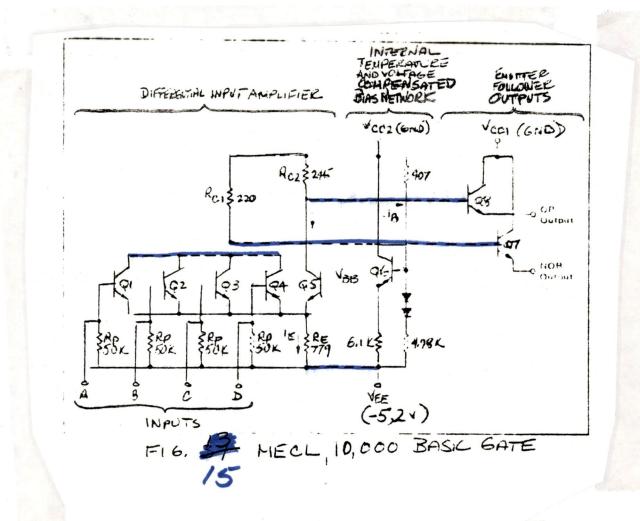

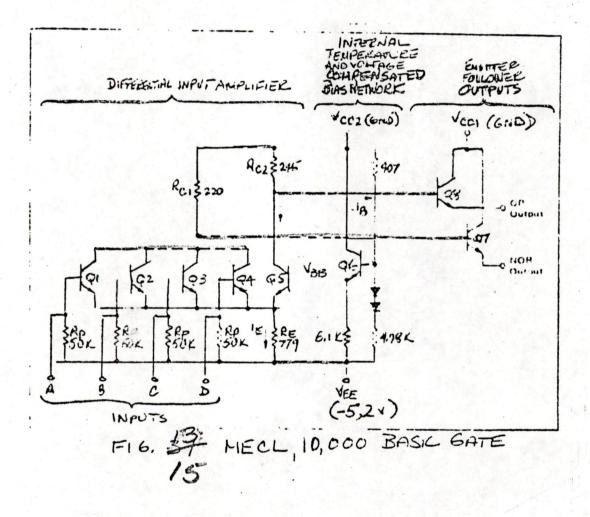

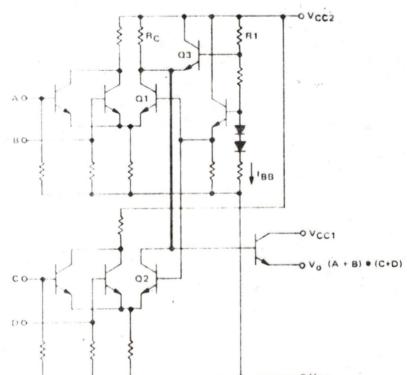

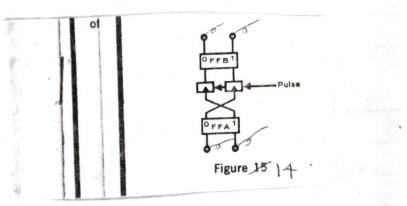

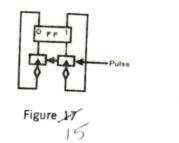

In 1972 work began on a new PDP-10 processor, the KL10. This used ECL current switching non-saturating logic from several vendors including the MECL (Motorola Emitter Coupled Logic) 10,000 series. This line of circuits is in some ways an integrated circuit version of the VHF modules. The basic gate is shown in Figure 15.

Chapter 3 page 23

R. Best, R. Doane, J. McNamara

Edited 3/17/78

Q6 has a temperature compensated internally generated reference voltage on its base of -1.3 volts. The outputs drive 50 ohm terrminated transmission lines returned to -2 volts. There is a complementary pair of outputs so that the circuit is both an OR and a NOR gate. At 25 degrees Celsius the upper level will between -0.81 and -0.96 volts, while the lower level will be between -1.65 and -1.85 volts. The circuits, like the Schottky circuits, are so fast that multi-layer boards are required. In addition, a great deal of care in signal line termination is required. As with the previous logic families studied, flip-flops can be created. The ECL master-slave flip-flops are quite complex, requiring 32 transistors and 7 diodes.

As the various module circuit technologies developed, not only could more logic functionality fit in a given space, but also the space provided on individual logic modules was increased. By 1973, the "hex" module (8.5 by 15.6 inches) was widely used, principally in the PDP-11 family. By 1977, DEC computers were using 12 by 15.6 inch "extended hex" modules.

An evolution in circuits has continued as the technology has changed. As integrated circuits have become more powerful by the reduction of the size of their active elements, each new computer introduced is smaller, faster, and generally lower cost than its predecessor. While only DEC examples have been mentioned here, the trend toward smaller, faster, and less costly computers has been true across all of the computer manufacturers.

The chart below shows the number of module types that were started each year from 1957 through 1977.

| Chapter 3                                                  |        | page 24 |

|------------------------------------------------------------|--------|---------|

| R. Best, R. Doane, J. McNamara                             | Edited | 3/17/78 |

|                                                            |        |         |

| Figures:                                                   |        |         |

|                                                            |        |         |

| 1. Photograph of Digital Laboratory Module                 |        |         |

| 2. Photograph of Digital System Module                     |        |         |

| 3. Schematic of an Inverter Used in Digital System Modules |        |         |

| 4. Symbolic Drawing of an Inverter                         |        |         |

| 5. OR Gate                                                 |        |         |

| 6. AND Gate                                                |        |         |

| 7. Flip-Flop                                               |        |         |

| 8. Flip-Flop With Inverter                                 |        |         |

| 9. Negative C-D Gate                                       |        |         |

| 10. Positive C-D Gate                                      |        |         |

| 11. Diode Gate                                             |        |         |

| 12. D-C-D Gate                                             |        |         |

| 13. K Series Circuit                                       |        |         |

| 14. TTL Circuit                                            |        |         |

| 15. ECL Circuit                                            |        |         |

CHAPTER MODULES Dick Best, Russ Doane, John McNamara

godinie.

Before applying the views of computer systems, technology, packaging, and manufacturing, expressed in the previous chapters to the DEC computers discussed in the following chapters, a brief review of printed circuit module technology is in order. Module technology is important because modules were DEC's first products, and because the progress in semiconductor technology that has formed the major element of the technology push driving the computer industry is evident in module technology in a scale convenient for close maination and understanding.

The first modules produced by DEC were called "Digital Laboratory Modules" and or be mounted in a scientist's equipad were intended to sit on an engineer's work bench and be interconnected with simple cords equipped with banana plugs. As shown in Figure 1, the modules (see Feg. 1) with housed were mounted in aluminum cases 1-3/4 by 4-1/2 by 7 inches in size, and all of the logical signals were brought out to the front of the case, where they appeared on miniature banana jacks mounted in a schematic diagram of the logical function performed by the module. The modules were offered in three speed ranges with compatible signal levels. The three speed ranges were 500 speeds with and KHz, 5 MHz, and 10 MHz bey added in \$959 Up to modules are monted in a single 10'rex 19"

The Digital Laboratory Module product line was supplemented by the Digital stems Modules. These modules, samples of which are shown in Figure 2, were

Which halds

relay calor mounting backplene which s

FIGURE 1 - LABORATORY AND SYSTEM MODULES

fig 2 DIGITAL SYSTEM MODULES

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 2

Intical to the Laboratory Modules in circuitry, signal levels, and speed range, but had a different packaging scheme. The System Module packaging was designed for rack mounting and used 22-pin Amphenol connectors at the backs of for sedued intervention the modules, rather than banane plugs at the front. The System Module mounting method was chosen for the PDP-1 computer so that op to 25 modules could be monted in ~ S'rix 19", mount wired mounting panel. Intervent

The circuits used in both module series were based on the M.I.T. Lincoln Laboratory TX-2 computer circuits. All of the TX-2 basic circuits were used, except those gates which used emitter followers. The emitter follower gates were not short circuit proof, and it was felt that misplaced patch cords in Laboratory Module configurations or slipping scope probes in System Module configurations would cause a high fatality rate for those circuits.

Dorief review of some of the circuits follows to indicate how much present day logic design differs from logic design of twenty years ago. Today arthmetic logic units (ALUCE), registers, designers deal with ALUS and microprocessors as units, whereas twenty years and individual flip flops ago, single gates, were units.

In the early module designs, most logical operations were performed using saturating PNP germanium transistors, as described in Chapter 3. While the use of transistors in radios and television sets relies on the linear relationship between base current and emitter/collector current to provide the amplification of radio frequency and audio frequency signals, the use of transistors in computer circuits (except those using ECL) relies primarily on the behavior of transistors in either the saturated state or the cut-off state. The use of transistors in such circuits can best be appreciated from the simple example shown in Figure 3. Chapter 3 page 3

R. Best, R. Doane, J. McNamara

Edited 3/17/78

Figure 3 is a schematic of an inverter. If the base lead is brought to a sufficiently negative voltage, the resulting base current will saturate the transistor, effectively connecting the emitter to the collector. If, on the other hand, the base is grounded, no base current flows, no emitter/collector current will flow, and the transistor will be in the cut-off state. The collector would then assume the voltage of the negative voltage source, were it not for the "clamp diode" which limits the voltage of the collector to -3

volts. The +10 volt bias voltage could be varied for marginal checking followy the timeofn circuits of cheater 3. The - 3 volt supply was generated on each module using 4 forward bias and docked relativel poorly from the to boostcally relativel roomly regulated -15 supply. volts. Lincoln TX-

(Se hemavie) Inverter (Se hemavie) (Symbolic)

Chapter 3 page 5 SEAC computer work.

Bared on the NBS Edited 3/17/78

R. Best, R. Doane, J. McNamara

Except for very small amounts of delay, the inputs and outputs of these circuits changed simultaneously, thus no information was stored. The storage of information was accomplished by bi-stable devices called "flip-flops" whose state was controlled by the application of pulses. Pefore discussing the construction of flip-flops, therefore, it is necessary to briefly describe the -generation of pulses which were the and equally important type of lugic & signal.

Insert 5,1 Pulses, which were used both in NAND/NOR circuits like those in Figures 5 and 6 and for controlling flip-flops, were generated by pulse amplifiers. Pulse amplifiers were very powerful logical elements because they not only amplified and standardized the shapes of pulses, but they also gated pulses. This latter feature meant that when the same logical gating was to be done on a whole register of flip-flops, it could often be done once, at the pulse amplifier ich drove the register. The pulse amplifier would typically be arranged to the operate in response to a pulse or level change and produce an output via a pulse transformer. The pulse transformer had both terminals of its secondary winding available so that either positive or negative pulses could be obtained depending upon which terminal was grounded. A negative pulse (ground to -3 volts and back to ground) was represented in the logic drawings by a solid triangle, and a positive pulse (-3 volts to ground and back to -3 volts) was represented by a hollow triangle. INSert A

notion of The use of pulses is emphasized a great deal in the following discussion because the concept of gating a pulse at the source and using the gated pulse to transfer data from register to register on a parallel basis used an absolute minimum of logic. This method was referred to as "East Coast" logic, while "West Coast" logic used gating at each bit position to do parallel

> and was in contrast to the othere forms of logic design using clockes and dual rank flip flops for register out put dela

Palaes were used for the computer clocks and for carrying out the register transfer operations among the registers. 5.1 A pulse, as it name implies, was a very well controlled. short event in which a logic signal is asserted. Pulses when by pulse amplifiers which were Generated I blocking oscillator circuits employing Insert A fim page 5 again, musically and and they to pulse transformers. I Pluse anglifiers were important because they to high energy(high fanord) produced, Standard, shaped pulses that which could be used to ischet gate a complete regester as a single, logical signal. Pulse signal Signals were normally distributed on dirsted pair wiring and could travel the (wathout degradation travel long distances needed in the early, large sized digital Systems (eg. (DP-1), without degradation. The Pulses "i'm Puta In foldation to the use of puls and qualifiers For the clock clocking, pulse ampliping your significant became woic course porto performed at the input determines the condition for register tranjer operations.

Chapter 3 page 6 R. Best, R. Doane, J. McNamara Edited 3/17/78 tranfers. These distinctions seem strange in the 1970's when gates are much cheaper than "a dime a dozen", but in the late 1950's and early 1960's much of computer design involved this level of component reduction ingenuity. hogical desig Even recent logical design texts englussive the need to minimize ligic and reduce the number of gates in a circuit system. where the schematic to conversion physical conversion was rathen In addition to the DEC logic, clucked sequentfal circuits and serial Bureau of Standardo based lugic alternatives, there was a concernabat. how logic was represented. Two logic design representations were used; "East Coast & logic" was idiagramatic runs and that typified in DEC'S Cogical design and regula tranzer diagrans; "west Coast Cogic" was based soldy or difference equations. "Gschwind (19\_)" described the DEC system effectively in his textbook.

F16. 7

Basic FLip-FLOP

Returning to the discussion of gates and flip-flops, a primative flip-flop can be obtained by interconnecting two grounded emitter inverters as shown in gure 7. When one inverter is cut-off, its output is negative. This holds the

Q A

Logical states and corresponding voltages for DEC dual polarity logic system

| <- Sames | ignal -> | <i>e</i> Jn rert | ed signal- |

|----------|----------|------------------|------------|

| A -0     | ¬A -◆    | -A-              | A-4        |

| 0 (-3)   | 1 (-3)   | 1 (0)            | 0 (0)      |

| 1 (0)    | 0 (0)    | 0 (-3)           | 1 (-3)     |

01

Fig. 4.1 Signal numing convention and signal levels through inverter (NOT gate) for DEC dual polarily logic system: convention

R. Best, R. Doane, J. McNamara

### Edited 3/17/78

he paralleled for the equivalent negated functions.

page 4

To simplify the logic drawings, a symbolic drawing like that in Figure 4, was sustomarily used to represent this circuit. Note that neither Figure 3 nor Figure 4 shows the emitter directly connected to ground or the collector directly connected to the negative supply. Rather, a dotted line is shown. This is because Laboratory Modules and System Modules often used, a series connection of up to three inverter gates between the negative supply and ground to accomplish various logical functions. This practice would seem strange by today's standards because today's transistors use silicon and each saturated transistor has a 0.7 volt voltage drop across it. In Laboratory Modules and System Modules, germanium transistors were used, and these had only about a 0.1 volt voltage drop.

Both series and parallel connections and be use to give logiced expressions while exclusive or fange The Digital Laboratory Modules and the Digital System Modules used a dual plarity logic system employing both levels and pulses. The logical voltage levels were -3 volts and ground. Correspondence between the logic state, ONE or ZERO, and the voltage levels of -3 and ground were indicated at each point in the logic diagram is a diamond. The diamond defined the necessary voltage level for the action desired. A solid diamond denoted that a -3 volt level was an assertion , and a hollow diamond indicated that a ground level was an two signals to names to one assertion. This convention gives physical signal, and if a given asserted signal, A, is passed though result is shown for signals fog Fig 4.1. m inverter, Series arrangements of inverters, while useful, were not sufficient to provide Down cost logic function equivalent to both the series and A more general arrangement was to add diodes to the all logical functions. circuit of Figure 3 to form NAND gate or NOR gates, as shown in Figures 5 and 6.

Figs 586 tube sufficial.

unapter 3

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page /

other inverter on, which in turn holds the first inverter off. If an itional inverter circuit is added to the circuit of Figure 7, the circuit of Figure 8 is obtained. The application of a negative pulse to the input of solut Benduitance the additional inverter changes the state of the flip-flop. In the actual implementations of DEC Laboratory Module flip-flops, buffer amplifiers were added to the outputs to permit a single flip-flop to drive the inputs of many other gates. The buffer amplifiers also provided delays at the outputs of the flip-flops such that the output did not change until after the activating pulse was over. This permitted the state of the flip-flop to be sensed while the flip-flop was being pulsed, a necessary feature for the simple implementation of shift registers, counters, and adders.

> sim<sup>eltenen</sup>data exchange between two regerters)

will be off

F16. 8

Flip-Flop @ INVERTER

R. Eest, R. Doane, J. McNamara Collections of the inverters, gates, and flip-flops just described were packaged in appropriate quantities (i.e. as many as would fit within the size and pin contraints) and sold as Laboratory Modules and System Modules. There were a relatively small number of module types available in the Laboratory Module Series. For example, Mr the first product line; the 100 Series:

Chapter 3

| 103  | 6 | Inverters                                   |

|------|---|---------------------------------------------|

| 110  | 2 | 6-input negative diode NOR's                |

| 201  |   | buffered flip-flop                          |

| 302  |   | one-shot                                    |

| 102  | 1 | clock pulse generator                       |

| 106  |   | crystal clock                               |

| 110. | 1 | Schmitt trigger circuit pulse generator     |

| 501  |   | level standardizers                         |

| 502  | 2 | pulse amplifiers                            |

| 50   |   | tube pulser (15 volt 100 nanosecond pulses) |

| 567  |   | level amplifiers (0 to -15 volts)           |

| 201  |   | relay                                       |

|      |   |                                             |

By contrast, there were many System Module types developed. With their higher Ocking density, lower cost, and fixed backplane wiring, they were used for computers, memory testers, and other complex systems of logic.

It is interesting to note that a large percentage of the modules on the above list were used for the generation and conditioning of the pulses and levels used in the relatively small number of logic circuits. Reference to a present day IC catalog would reveal very few pulsing and clocking circuits and a great many logic circuits. The emphasis on pulses was one of economy, as noted previously.

8.1 Inert

In 1960 DEC began building modules with slightly different circuitry than that described above. While transistor inverters, buffered delayed flip-flops, and their associated pulse logic were the best choice for 5 and 10 MHz logic, C-D (non-delayed)

page 8

Chapter 3 page 9 R. Eest, R. Doane, J. McNamara Edited 3/17/78 Low speed logic because greater logic density and lower cost could be

achieved.

FIG. 9 NEGATIVE C-D GATE

FIG. 10 POSITIVE C-D GATE

A negative capacitor-diode gate is illustrated in Figure 9. With both the level input and the pulse input at ground for sufficient time to allow the capacitor charge to reach three volts, a negative level change or a negative pulse at the pulse input will cause a positive pulse to appear at the output. Such gates could drive the direct set input of any flip-flop which required a softward positive pulse, and were built into some unbuffered flip-flop inputs to be used for shifting and counting. Note, here the charge of performing  $\bullet$  as the defent the direct set input of puffered flip-flop inputs to be

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 10

A positive capacitor-diode gate is illustrated in Figure 10. With the level input at -3 and the capacitor input at ground for a sufficient time to allow the charge on the capacitor to become stable, a negative level change or a negative pulse at the capacitor input will cause the transistor to conduct, grounding the output for an amount of time determined by the gate time constant or the input pulse width, whichever is shorter. Gates of this type were not cross-coupled to form flip-flops, but could be used to set and clear unbuffered flip-flops by momentarily grounding the correct flip-flop outputs in a fashion similar to the inverter gate that was added to Figure 7 to obtain Figure 8.

The principal advantages of the capacitor-diode gates were:

- The level input to the gate was used to charge a capacitor and was isolated from the rest of the circuit by a diode. Thus, no DC load was presented to the circuit driving the level input of a C-D gate.

- 2) The resistor-capacitor time constant of the gate required that the conditioning level be present a certain amount of time before the pulse input occurred. This introduced a delay between the application of a new gate-level and the time the gate was conditioned, and allowed the sampling of unbuffered flip-flop outputs at the same time that the flip-flop was being changed.

- 3) The resistor-capacitor combination differentiated level changes, permitting a level change to create a pulse.

4) The combunied system cost was significantly less than with the Impfered flip flops.

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 11

The use of saturating MADT transistors and toroidal pulse transformers appeared to be nearing an operating limit at 10 MHz. The pulses needed to operate the circuits shown in the previous diagrams were 40% of the cycle time (40 nansecond) of 10 MHz logic, tightly constraining transformer recovery time and making it difficult to design circuits that were not excessively sensitive to repetition rate. Furthermore, gate delays were large enough to prevent some needed logic configurations from propagating within the 100 nanosecond interval implied by the 10 MHz rating.

A major break with previous circuit geometries appeared necessary. The use at IBM of non-saturating logic encouraged an exploration in that direction. The project was called the "VHF Logic" project because operation at 30 MHz or better (the bottom end of the VHF radio band) was the goal.

The complex 30 mHz flip-flops were packaged one to a module, so a great many interconnections were needed to implement logical functions. In systems designed for 30 MHz op ation, the use of leads longer than a few centimeters was expected to require special care, hence the availability of a satisfactory transmission line hookup medium was felt to be an essential element for ease of use. A new solid wall coaxial cable had just been introduce, the 50 ohm impedance version of which was chosen to hook up the VHF modules. It appeared to have a strong enough center conductor for practical hookup between modules while not being too bulky for easy hand bending.

Due to the low impedance needed for the coaxial cable connections, substantial driving current was necessary to achieve adequately high signal Itages, and hence considerable power had to be dissipated. The ability to

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 12

drive a load at any point along the transmission line was deemed necessary for practical hookup, and 3 volt swings had to be available for compatibility with existing modules. These needs were met by choosing a 60 milliampere output current, producing a 1.5 volt swing on a double-terminated 50 ohm line and a 3 volt swing with a 50 ohm load when interfacing to existing slower logic. These voltage and current levels required the addition of heat sinks to the output transistors. This was accomplished by installing spring clips that fastened the cases of the transistors directly to the connector pins, exploiting the connectors as heatsinks and at the same time providing a minimum inductance connection from the transistor collector (common to the case) out of the module.

The VHF modules contained a novel delay line implementation which has appeared in recent days in the ECL boards of the KL10 processor. Flip-flop feedback delay was provided by a 10 nanosecond stripline etched onto the printed circuit board. A meander pattern was selected with a degree of local coupling between the loops to achieve a seven to one delay to risetime ratio. Eoth the delayed and undelayed ends of this 50 ohm stripline were made available at the module pins. The undelayed outputs switched simultaneaously with the flip-flop outputs, allowing a subsequent gate to subtract a delayed flip-flop output from the undelayed complement output side of the flip-flop and produce a 10 nanosecond pulse when the flip-flop changed state.

The performance of the VHF modules was rated at 30 HMz, which was the limit of the module testers used on the production floor. Bench testing demonstrated 40 MHz capability with the promise of 50 MHz performance if adequate testing paratus could be found. Risetimes were better than 1. hanosecond?

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 13

Modules delivered to customers were used to build satisfactory high performance systems, but the need for such high performance was not widespread. In addition, the product development cycle was by the standards of the time quite long (two years) and the enthusiasm for the VHF modules amongst the DEC engineers flagged, further attenuating product morentum. Despite their failure as a product, the VHF modules eventually made a contribution to computer progress. To produce timesharing systems, the PDP-6 needed a way of comparing relocated addresses at very high speed. A high speed register comparator was quickly designed using current mode logic similar to the VHF modules.

As a series of general purpose products for engineers to use, the cost of the VHF modules and the inconvenience of their wiring was too great. Further velopments in general purpose logic modules were to lie in the opposite direction: cheaper, more compact, easier to use, and slower.

Flip

By 1964 the decreasing cost of semiconductors during the early 60's had caused and the wiring of the modules the cost of System Module mounting hardware, to become a significant portion of Systen the total module cost. In response to this trend, a new type of module was developed which was a 2.5 by 5 inch printed circuit card with a color coded (see Feg. 10.2) plastic handle. The printed circuit card provided its own mechanical support there was no metal frame around it as there had been in the System Module  $\mathfrak{l}$ - Each connector had 18-pins . design. The new modules, called Flip-Chip modules, plugged into, connector blocks that could support eight such modules. The main advantage of the Flip-Clip modules was that antomatic wire wrapping seguipment, built by gardner - Denver lorp. The modules. Chapte This evolution is could be used to on inter wire (interconnect) The first series of the new modules was designated the "R-Series" and was entified by using red handles. The R-Series circuits were a reaction to the

Assented both in Part II (page 0) an charter o on the POP-10 (praseo

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 14

rather complicated set of usage rules developed for the previous products. The goal was to make these easy to use and inexpensive . Integrated circuits were not used because they were more expensive than discrete components and the computer industry had not yet decided on the type of integrated circuit to use. The building block for R-Series logic was the diode gate, a sample of which is shown in Figure 11. The other basic circuit was the DCD (diode-capacitor-diode) circuit shown in Figure 12. The DCD gate was used to provide standardized levels to active devices such as flip-flops and to produce the logical delay necessary to sense and change flip-flops at the same som POP-8

CLAMPED LOAD RESIGTOR SYMBOL

F16. 11

DIODE GATE

F16.12 DOT GATE

R. Best, R. Doane, J. McNamara

page 15

second series of the new modules was developed for the first PDP-8s. This series was called the S-Series, although it also had red handles. The S-Series modules used the same circuits as their R-Series counterparts, but with variations to the values of the load resistors and DCD gate storage capacitors to obtain greater speed that the IMbg R-Series - The Dith what this was?

The E-Series with blue handles was essentially the same as the 6000 series of 10 MHz System Modules, but repackaged on the new 2.5 inch by 5 inch cards, and used silicon transistors rather than germanium transistors. The new silicon transistors were a mixed blessing. While they had temperature sensitivity characteristics superior to those of the germanium transistors, and their voltage drop characteristics permitted the elimination of the bias resistor to +10 volts, they did not saturate as well as the germanium transistors. Pecause ey did not saturate well, the voltage between the collector and the emitter in the saturated state was not as low as it was with germanium transistors. This meant that the series arrangement of three inverters discussed in conjunction with the dotted lines in Figure 4 could not be used. Instead, only two of the silicon transistor inverters could be connected in series if the output was intended to drive another inverter. The first computer to use the B-Series modules was the PDP-7764 Me POP-10 process was based on ad Mended du B-ceim

Analog applications were the target market for the A-Series modules, which had amber handles. This series, still being manufactured today, includes analog multiplexers, operational amplifiers, sample and hold circuits, comparators, digital to analog converters, reference voltage supplies, analog to digital converters, and various accessory modules. The peak development rate for malog modules occurred in 1971 with 38 new types and declined to 5 new types

R. Best, R. Doane, J. McNamara

page 16

Edited 3/17/78

n 1977.

While all of the preceding modules had been designed as user-arrangeable building blocks, the green handled G-Series was intended for modules that would only be sold as part of a system. For example, all of the DEC core memory circuits have been in the G-Series because a core memory system is sufficiently complex that a cookbook approach using a standard series of modules is not appropriate. The G-Series is still actively used today for circuits other than logic, generally in peripheral devices such as disks, tapes, and terminals.

Like the A Series and G Series, the W (white handle) Series is still manufactured, and is used to provide intput/output capability between ip-Chip modules and other devices. Lamp drivers, relay drivers, solenoids drivers, level converters, and switch filters are included in this family, but the only modules used widely today are the W900-W999 modules which include cable termination modules and blank boards upon which the user can mount ICs and wire wrap them together.

While the W-Series provided a variety of interface capabilities, the circuitry used therein was still too fast for typical industrial applications. Computer-oriented logic, by its very nature, is high speed and provides noise immunity far below that required in small-scale industrial control systems located physically close to the process they control.

Unfortunately, industrial electrical noise is not predictable to the nearest order of magnitude. Thus, attempts to solve the problems with "high level

R. Best, R. Doane, J. McNamara

. . . . . . . .

page 17

Edited 3/17/78

logic" whose voltage thresholds were merely a few times greater than computer-type logic levels did not work well.

A new series of modules, the K-Series (with blac(K) handles), was developed which relied on a combination of voltage, current, and time thresholds to protect storage elements such as flip-flops and timers from false triggering. Since industrial controls typically interact with physically massive equipment, time thresholds are particularly attractive. There are four ways of exploiting these:

- 1) basic 100 Khz slow-down circuits everywhere

- 2) optional 5 KHz slow-down circuits available

- 3) transition-sensitive (edge-detecting) circuits provided with hysteresis to allow additional discrete capacitor loading when all else fails

- 4) replacement of the conventional monostable multivibrator or "one-shot" circuit by a timing circuit having both a low impedance and hysteresis at the input.

The hardware for the K-Series was specially designed to fit the NEMA (National Electrical Manufacturers Association) enclosures traditionally used with relay implemented industrial controls, but used the same connectors as the other Flip-Chip modules. Sensing and output terminals were provided with screw terminals and indicator lights, and appropriate arrangements were made to interface with 120 VAC devices. Wire wrap terminals were protected from external voltages but were available for oscilloscope probes. Magnetically latched reed relays and diode arrays that could be programmed by snipping out

Unupuer )

R. Best, R. Doane, J. McNamara

Edited 3/17/78

failures.

FIG. 13 K- Series Circuit

Gating in early K-Series modules was accomplished with discrete diode-transistor circuits such as that shown in Figure 13. Other K-Series modules used integrated circuits for the logic functions. In these designs the inputs to the ICs were protected with filter/trigger circuits which filtered out the noise and then restored the fast rise-times required by the ICs. • tputs were protected from output-induced noise and converted to standard

R. Best, R. Doane, J. McNamara

Edited 3/17/78

page 19

K-Series signals by circuits similar to those used in the discrete logic gates.

Unlike other DEC modules, the K-Series modules were not directly useful for constructing computers or computer-like data processing subsystems due to their low speed and high cost. They did play an important part in bringing digital logic into industrial applications, and the noise protection techniques developed for these modules were useful in the design of the PDP-14 Industrial Controller (Chapter 6).

By 1967 the electronics world had settled on transistor-transistor-logic (TTL) and the dual-in line package (DIP) as the technology of choice for integrated circuits and the cost for logic functions implemented in TTL ICs had dropped below that of discrete circuit implementations. With much more logic fitting into the same printed circuit board area, a single Flip-Chip card could now accommodate much more complicated functions. However, there were not enough connector pins available to get the necessary signals on and off the card. The answer to the problem was to keep the cards the same size, but to have etch and associated contacts on both sides of the printed circuit board. This increased the number of contacts from 18 to 36, and a new series with magenta handles (M-Series) was born. Subsequently, some C-Series and W-Series modules were also designed with ICs and double sided boards.

The advent of TTL brought the first power supply and signal level change in DEC's history. The -15 volt and +10 volt supplies were no longer required. Only a single +5 volt supply was needed to supply the logic signals which were 0 and +3 volts. The packaging was kept consistant, however, as the old Chapter 3 page 20

R. Best, R. Doane, J. McNamara

Edited 3/17/78

single-sided modules could be plugged into the new connector blocks, and eareful attention to pinning arrangements allowed double-sided module to be used in a single sided block at a sacrifice of some circuits.

The basic TTL circuit is the NAND gate shown in Figure 14.

# FIG. 14 TTL NAND Circuit

he input of the TTL gate is a multiple emitter transistor. If either input is

R. Best, R. Doane, J. McNamara

page 21

Edited 3/17/78

or near ground (0 to 0.8 volts), Q1 becomes saturated, bringing the base voltage of Q2 low, turning off Q3 and turning on Q4 making the output high (+2.4 to +3.6 volts). If both inputs are high (above 2.0 Volts), Q2 has base current supplied to it through the collector diode of Q1, turning Q2 on. This in turn provides base current to Q3, saturating it and cutting off Q4, making the output low (0 to 0.4 volts).

Like the transistor inverter circuits discussed in conjunctuion with System Modules, TTL NAND gates can be cross-connected to form flip-flops.

The first generation of M-Series modules were used in a redesign of the PDP-8 called the PDP-8/J. The circuits used in these modules used TTL integrated rcuits which were called "7400 series" integrated circuits because of a growing tendency in the semiconductor industry to standardize part numbers for TTL circuits, calling a package of 4 NAND gates a 7400, a package of six and the PDP-15 were and PDP-15 inverters a 7404, etc. The KI10 processor used in the PDP-10 was designed from higher speed circuits using the 74H00 series of TTL integrated circuits. The 74H00 circuits were similar to the earlier 74 series, but were faster and used much more power. The first PDP-11 (the PDP-11/20) used both 7400 and 74H00 series JCs, as did the PDP-8/E. Both of these latter machines used 8.5 inch by used general purpose andules nd Note 10.4 inch "extended quad" modules. More importantly when Not the earling DEC IC machines (i.e. 8/I, 8/L, KI 10, and PDP-15) had relatively low packing density since most interconnections were carried out on the backplane. The 8/E and 11/20 dized functionally specialized modules and interconnections were carried out on the & printed circuit etch of the module. the earlier DEC In 1970 on M-Series 18-bit machine, the PDP-15, was constructed. It was the last of a generation which started with the PDR-1 (System Modules), and grew through the PDP-7 and PDP-9 (B-Series modules). The PDA-15 and the PDP-11/45 Schottky TTL, a circuitry with such rapid switching speeds that four-layer boards had to be used such that the inner layers of power and

Chapter 3 page 22 R. Best, R. Doane, J. McNamara Edited 3/17/78 ·e.round etch could provide shielding. also the

In 1972 work began on a new PDP-10 processor, the KL10. This used ECL current switching non-saturating logic from several vendors including the MECL (Motorola Emitter Coupled Logic) 10,000 series. This line of circuits is in some ways an integrated circuit version of the VHF modules. The basic gate is shown in Figure 15.

R. Best, R. Doane, J. McNamara

11/40, 11/40 and

page 23

Edited 3/17/78 Q6 has a temperature compensated internally generated reference voltage on its base of -1.3 volts. The outputs drive 50 ohm terrminated transmission lines returned to -2 volts. There is a complementary pair of outputs so that the circuit is both an CR and a NOR gate. At 25 degrees Celsius the upper level will between -0.81 and -0.96 volts, while the lower level will be between -1.65 and -1.85 volts. The circuits, like the Schottky circuits, are so fast that multi-layer boards are required. In addition, a great deal of care in signal line termination is required. As with the previous logic families studied, flip-flops can be created. The ECL master-slave flip-flops are quite -

As the various module circuit technologies developed, not only could more logic functionality fit in a given space, but also the space provided on The number of pins per module hers also varied greatly ! dividual logic modules was increased. By 1973, the "hex" module/(8.5 by 15.6 the UAX-IV inches) was widely used, principally in the PDP-11 family, Ey 1977, DEC computers were using 12 by 15.6 inch "extended hex" modules....... further reduce the interconnection cost by placing more logic on a single bo module. 18.0

Lite wire, the DE for cost DEC system 2020 was based on extended her modules

complex, requiring 32 transistors and 7 diodes.

An evolution in circuits has continued as the technology has changed. As integrated circuits have become more powerful by the reduction of the size of their active elements, each new computer introduced is smaller, faster, and generally lower cost than its predecessor. While only DEC examples have been mentioned here, the trend toward smaller, faster, and less costly computers has been true across all of the computer manufacturers.

(Fra. 16 The chart below shows the number of module types that were started each year from 1957 through 1977.

Chapter 3 page 24 R. Best, R. Doane, J. McNamara Edited 3/17/78 Photos of Figures: need photo of system 1. Photograph of Digital Laboratory Module in a System 2. Photograph of Digital System Module 3. Schematic of an Inverter Used in Digital System Modules 4. Symbolic Drawing of an Inverter 5. OR Gate Signal naming convention and signal levels through inverter (NOT gote) for DEC dual polanty logic. 6. AND Gate (8.1 Register transfer representation of PDP-1 accumulator, AC. (8. V Logic diagram of POP-1 accumulator abit, AC<3>. 7. Flip-Flop 8. Flip-Flop With Inverter 9. Negative C-D Gate 9. Regardent

10. Positive C-D Gate <u>Photograph of 30 Hhs</u> flip flop

11. Diode Gate <u>10, 2 Photograph of Hip Chip modules</u>

A. D-C-D Gate <u>10, 2 Photograph of Hip Chip modules</u> used in POP- 7 and POP-8 13. K Series Circuit 14. TTL Circuit 15. ECL Circuit 15.1 Pholograph of super her modules the used in VAX-11/180. 16. Time line chart of the number of modules introduced each year at DEC

Flip chy s, d. - g. - ext. he

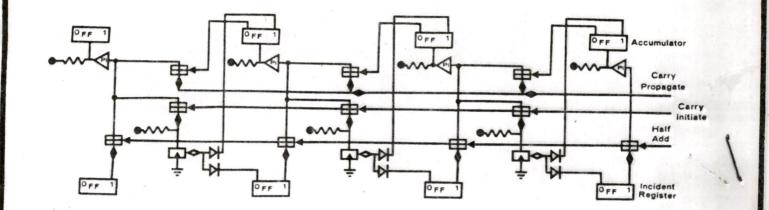

The adder illustrated below is built from negative C-D gates and unbuffered flip-flops.

Figure 23 Parallel binary adder (DEC Flip-Flop Type 4215 for accumulator)

This is also a two step add; a half add is followed by a carry.

VHF (See Russ Doane's insert.)

FLIP-CHIPS 1964 -

# STRATEGY AND PACKAGES:

25

Each year the cost of semiconductors decreased, causing the cost of the hardware used to house the semiconductors to be more significant. The answer was a 2.5 × 5 inch card with a labelled and color-coded plastic handle to be plugged into a connector block that can hold 8 such modules with sufficient insertion depth to support them. An added production gain was made by making 4 modules at once, and cutting the "quad" into "singles" after assembly.

THE CIRCUITS

#### R SERIES

The R-series (red handles) circuits were a reaction to the rather complicated set of usage rules developed for the specials products. The goal was to make these easy to use

#### VHF MODULES

Dick: Dick: too long? Need a diagram ?

- 3-2237

# USING EMITTER-COUPLED LOGIC (E C L)

The use of saturating MADT transistors with toroidal pulse transformers appeared to be near its limit at 10MHz in the 6000 Series. The pulses already needed to be 40% of the minimum time interval to achieve adequate "on" times, tightly constraining transformer recovery and making it difficult to design circuits that were not excessively sensitive to repetition rate. Series gating stacks had to be limited to two transistors for many purposes. Gate I delays were large enough to prevent some needed logic configurations from propagating within the 100ns interval implied by the 10MHz rating. Lhic

A major break with previous circuit geometries appeared necessary. The use at IBM of non-saturating logic encouraged an exploration in that direction. The project was dubbed "VHF Logic" because operation at 30MHz or better (the bottom end of the VHF radio band) was a goal.

Solid-wall co-ax had just been introduced, and the 50 ohm version of this product appeared to have a strong enough center conductor for practical hookup between modules while not being too bulky for easy hand bending. Since leads longer than a few centimeters were expected to require special care, the availability of a satisfactory transmission-line hookup medium was felt to be an essential element for ease of use, and the 50 ohm impedance level was therefore adopted. (Remember that in those days, each flip-flop was going to need its own separate module, imposing about 1cm of intermodule leadlength in addition to connector pins and any printed wiring length ().)

# POWER DISSIPATION

Due to the low impedance needed for practical co-ax hookup, considerable power had to be dissipated. Moreover, 3 volt swings had to be available for compatibility with existing modules. The ability to drive at any point along a co-axial transmission line appeared necessary for practical hookup. These needs were met by choosing a 60 milliampere output current, producing a 1.5 volt swing on a double-terminated 50 ohm line and a 3 volt swing with a 50 ohm load when interfacing to existing slower logic.

These voltage and current levels required heatsinking of the output transistors. Spring clips were designed to fasten the transistor TO18 cans directly to the connector pins, exploiting the connector as a heatsink and at the same time providing a minimum-inductance connection from the transistor collector (common to the case) out of the module.

# LOGIC DELAY LINES.

Flip-flop feedback delay was provided by løns stripline etched onto the p c board. A meander pattern was selected with a degree of local coupling between loops to achieve around a 7:1 delay-to-risetime ratio. Both the delayed and the undelayed ends of this 50 ohm stripline were made available at the module pins. The undelayed outputs switched simultaneously, allowing a subsequent gate to subtract a delayed flip-flop output signal from its complement undelayed, to produce lons pulses when needed.

Rated performance was 30MHz, limited by the capabilities of the production

sters. Bench testing demonstrated 40MHz capability, with every evidence hat 50MHz performance could have been promised if the testing problem had en solved. Risetimes were better than 1.5ns, despite the need for 100 ohm sistors at transistor bases to damp the self-oscillation of the effectively) common-collector circuit geometry.

dules delivered to customers were used to build satisfactory high rformance systems. However, the need for this level of performance was not despread, being limited to advanced laboratory instrumentation. The io-year product development cycle wore out the initial enthusiasm of most GITAL people, futher attenuating product momentum.

LATION TO OTHER PRODUCTS spite their failure as a product, the VHF modules eventually made a intribution to computer progress. To produce the first commercial mesharing systems, the PDP-6 group needed a way of comparing relocated dresses at high speed. The PDP-6 relocation comparator was designed very lickly using current-mode logic.