Table 1 The computer-space dimensions

| Computer function | it ( von - Neumann, | stured | program | ) |

|-------------------|---------------------|--------|---------|---|

|                   |                     |        |         | _ |

Scientific

**Business**

Control

Communications

(switching|store and forward)

File control

Terminal

√Time sharing

| Logic<br>technology              | Generation | Historical<br>date | Pc.speed (sec) | $Cost/operation \ (\$/bit/s)$ |   |

|----------------------------------|------------|--------------------|----------------|-------------------------------|---|

| Mechanical                       |            |                    |                |                               |   |

| Electromechanical                |            | 1930               | $10^{-1}$      | 1000                          |   |

| (Fluidics)                       |            | (1970)             | $10^{-2}$      |                               |   |

| Vacuum tube                      | first      | 1945               | $10^{-3}$      | 10                            |   |

| Transistor X                     | second     | 1958               | $10^{-5}$      | -1                            |   |

| Hybrid                           |            | 1964               | $10^{-6}$      |                               |   |

| Integrated/IC &                  | third      | 1966               | $10^{-7}$      | 0.1                           |   |

| Medium to large-                 | fourth?    | 197? 2             | $10^{-8}$      | 0.01                          | , |

| scale integrated/<br>MSI ~ LSI 2 | SHA        | 1672 NV            |                |                               |   |

| Word size                                   | Base                             | Data-types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Data-type locater                        |

|---------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 8 b<br>12 b — 6<br>16 b — 185<br>24 b — 185 | binary sæ<br>decimalት ≀√         | word integer address (integer) bit bit vector instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | motor ater-<br>methodates<br>tagged with |

| 32 b 48 b 64 b                              |                                  | character character string word vector where the string words where the string words where the string words where the string was the string words where the string was the string words where the string words where the string was the string was the string was the string was the string words where the string was the string words where the string was the string words where the string was the string was the string words where the string was the string was the string words where the string was the string was the string was the string words where the string was the string was the string was the string words where the string was the | descripts.                               |

|                                             | character (6b)<br>character (8b) | word vector vector matrix array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | h \$ .                                   |

|                                             |                                  | lists, stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          |

| Addresses/instruction            | M.processor state (excluding program counter) |  |  |  |

|----------------------------------|-----------------------------------------------|--|--|--|

| 0 address (stack)                | stack                                         |  |  |  |

| 1 address                        | 1 Accumulator                                 |  |  |  |

| 1 + x (index) address +          | accumulator and index registers               |  |  |  |

| 1 + g (general register) address | general registers array                       |  |  |  |

| 2 address                        |                                               |  |  |  |

| 3 address                        | no explicit state                             |  |  |  |

| n + 1 address                    |                                               |  |  |  |

| Language determined              |                                               |  |  |  |

| Compound                         |                                               |  |  |  |

| Microprogrammed                  |                                               |  |  |  |

# it cosers. VM'S, YC'S

+arch/Inpl. distant

| PMS structure                                             | Switching                             |                   | Processor function |

|-----------------------------------------------------------|---------------------------------------|-------------------|--------------------|

| . 1Pc                                                     | 1:n (duplex)                          |                   | → P.microprogram   |

| 1Pc(interrupt)                                            |                                       |                   | Pc                 |

| 1Pc-nPio                                                  | n:m (time-multiple x)                 |                   | Pc (no io)         |

| 1 Pc-nPio-P(display)                                      | *                                     |                   | +Pio               |

| 2C (duplex)                                               | 2:n (dual-duplex)                     |                   | → P.display        |

| ×nPc(multiprocessing)                                     | n:m (cross-point)                     |                   |                    |

| nPc-P(array special algorithm)                            |                                       |                   | 4 P.array + rest   |

| nPc(parallel processing)                                  |                                       |                   | P.vector move      |

| C (network)                                               |                                       |                   | P.algorithm        |

| Network                                                   | n/2:n/2 (non-hierarchy)               |                   | P.language         |

| Accessing algorithm Mp.size                               | Ms.size                               | $Mp.speed\ (b/s)$ | Ms.speed (b/s)     |

| Linear (stack)                                            |                                       |                   |                    |

| Linear (queue)                                            |                                       |                   |                    |

| Bilinear                                                  | tape (large)                          |                   | $> 10^{5}$         |

| Cyclic-random                                             | disk (medium)   magnetic card (large) |                   |                    |

| Cyclic —drum (large) 🗸                                    | drum (small) photostore (large)       | $> 10^{6}$        |                    |

| Random core (medium)                                      | core (smaller)                        | $>10^{7}$         | $> 10^7$           |

| Content film (small)                                      |                                       | $> 10^{8}$        |                    |

| Associative integrated circuit                            |                                       | $>$ 10 $^{9}$     |                    |

| XMp concurrency Interpro                                  | ocess communication                   |                   |                    |

| ¹ 1 program subrout                                       | tines and traps                       |                   |                    |

| 1 program with interrupts Winterrup                       |                                       |                   |                    |

|                                                           | ocessor interrupts                    |                   |                    |

|                                                           | des (programmed operators for         |                   |                    |

| 7,7,1                                                     | itor calls)                           |                   |                    |

| m + n swapped programs  m + n programs (multiprogramming) |                                       |                   |                    |

| No relocation                                             |                                       |                   |                    |

| 1 segment                                                 |                                       |                   |                    |

|                                                           |                                       |                   |                    |

| 2 segments (pure, impure) >2 segments                     |                                       |                   |                    |

| Pages Pages                                               |                                       |                   |                    |

|                                                           | gment communication                   |                   |                    |

| Fixed length, paged segments                              | smeric communication                  |                   |                    |

|                                                           |                                       |                   |                    |

| Multiple-length paged segments                            |                                       |                   |                    |

| Variable-length segments                                  |                                       |                   |                    |

| Named segments Capabilities-based Compa                   |                                       |                   |                    |

| Processor concurrency (Single P.)                         |                                       |                   |                    |

| Serial by bit Servil by character                         | Event of 6th                          |                   |                    |

| Parallel by word                                          | - tip                                 |                   |                    |

| Multiple instruction streams, 1Pc                         | (Tagrania II                          |                   |                    |

| Multiple data streams (arrays)                            |                                       |                   |                    |

| 1 instruction buffer                                      | le arith units +                      |                   |                    |

| n instruction buffer                                      | es and the victoria                   |                   |                    |

| ↓Look-aside memories                                      |                                       |                   |                    |

| MPipeline processing                                      |                                       |                   |                    |

Median of Handman

CH.1: 7 VIEWS

ab/cm/JM Fil. PERFCOMP

| NOTE: Figures 18 & BPMS not included in draft.                   |

|------------------------------------------------------------------|

|                                                                  |

| Computer Production-Consumption Process                          |

| Structural Levels from Bell and Newell                           |

| Onion Skin                                                       |

| The Basic Interpretive Loop                                      |

| A Processing System                                              |

| Hierarchy of Interpreters                                        |

| Pipes Through Interpreters                                       |

| Levels vs Time                                                   |

| Noyce's Levels                                                   |

| Levels of Integration                                            |

| Network, Not Tree                                                |

| Three Design Styles                                              |

| Evolutions from Base Design B                                    |

| Machine Price and Performance of Time (Machine Planes)           |

| Price vs Time for Each machine Class                             |

| Migration of Constant Performance Machine Use Among P-C<br>Pairs |

| Groschlin                                                        |

| Histogram of Data Type by Application                            |

| Philosophy of Design                                             |

| Product Development Schedule I Fig. 4.21.3 (p.207)               |

| Product Development Schedule II Fig. 4.21.4 (p.207)              |

| Engineers Assigned vs Elapsed Time, Fig. 4.21.7 (p.209)          |

| Vonada's Engineering Maxims                                      |

| The Computer Space                                               |

|                                                                  |

## Appendix Figures

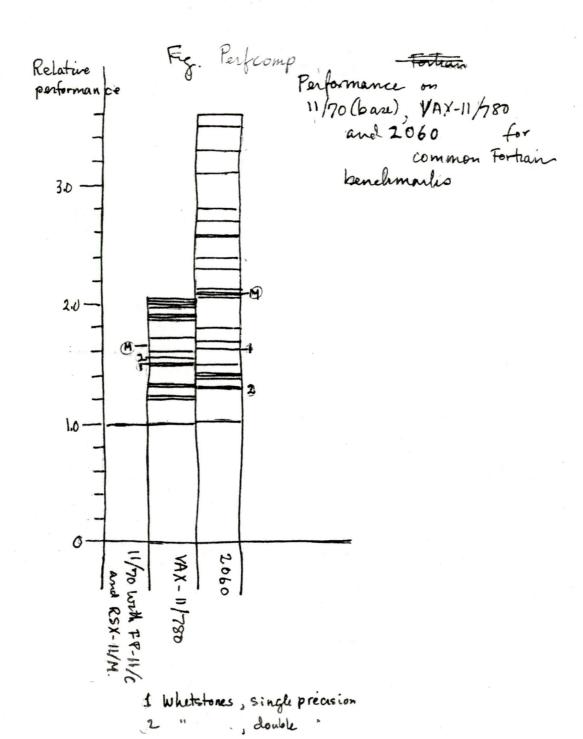

Perfcomp Performance Comparisons

BPMS PMS Diagram of a Basic Computer

Table 3\_

Twelve Test Programs Used in CFA

#### CHAPTER 1: SEVEN VIEWS OF COMPUTER SYSTEMS

A computer is determined by many factors, including such diverse elements as its architecture, its structural properties, the technological environment, and the human aspects of the environment in which it was designed and built. Many of the design factors lie outside the control of the designer, including the availability and price of electronic technology, rules and standards promulgated by government and industry, current and future market conditions, and the cummulative investment in software of the various users.

In this book various authors reflect on a wide range of DEC computers - their goals, their architectures, their various implementations and realizations, and occasionally on the people who designed them. The presentation is limited to the engineering of the basic computer hardware and does not describe, except as interfacial design, the engineering of peripheral equipment or software.

An attempt is made to show the interrelationship of the design to various factors, beginning with the architectural specifications, and to observe how the design was affected by the available technology, by the engineering organization, by the sales and manufacturing aspects, and finally by the application.

Figure 1 shows the organizational entities and implied design activities affecting the design of a computer. The lines indicate the two-way flow of information influencing the product specification. Of the flows shown, the

physical flow of materials is the easiest to trace as it comes from basic technology suppliers, moves through the plants that build basic the computer parts, and then goes to where the final system is assembled.

Computer engineering is the complete set of activities, including the use of taxonomies, theories, models, and heuristics, associated with the design and construction of computers. It is like other engineering, and the definition that Hamming once gave is especially appropriate: engineers first turn to science for aswers and help, then to mathematics for models and intuition, and finally to the seat of their pants.

In the few decades since computers were first conceived and built, computer engineering has come from a set of design activities that were mostly seat-of-the-pants based, to a point where some parts are quite well understood and based on good models and rules of thumb, such as technology models, while other parts are completely understood and employ useful theories such as circuit minimization.

In this chapter, seven views are presented that the authors have found useful in thinking about computers and the process which molds their form and function. The views are intentionally independent; each is a different way of viewing a computer. A computer scientist or mathematician sees a computer as levels of interperters. An engineer sees the computer on a structural basis, with particular emphasis on the logical design portion of the structure. The view most often taken by a buyer is a marketplace view. While these people each favor a particular view of computers, each typically understands certain aspects of the other views also. The goals of Chapter 1 are to increase this

understanding of other views and to increase the number of representations used to describe the object of study and hence improve on its exposition.

Thus, these views should form a useful background for the subsequent chapters on past, present, and future computers.

Since performance is such a major component of the objective function by which a computer is judged, an appendix is provided which looks at the common ways for evaluating performance.

#### VIEW 1: Structural Levels of a Computer System

In <u>Computer Stuctures</u> [ Bell and Newell, 1971 ], a set of conceptual levels for describing, understanding, analyzing, designing, and using computer systems was postulated. The model has survived major changes in technology, such as the fabrication of a complete computer on a single silicon chip, and changes in architecture, such as the addition of vector and array data types.

As shown in Figure 2, there are at least five levels of system description that can be used to describe a computer. Each level is characterized by a distinct language for representing the components associated with that level, their modes of combination, and their laws of behavior. Within each (system) level there exists a whole hierarchy of systems and subsystems; but as long as these are all described in the same language, they do not constitute separate system levels. With this general view, one can work up through the levels of computer systems, starting at the bottom.

The lowest level in Figure 2 is the device level. Here the components are p-type and n-type semiconductor materials, dielectric materials, and metal formed in various fashions. The behavior of the components is described in the languages of semiconductor physics and materials science.

The next level is the circuit level. Here the components are resistors, inductors, capacitors, voltage sources, and nonlinear devices. The behavior of the system is measured in terms of voltage, current, and magnetic flux. These are continuously varying quantities associated with various components, hence there is continuous behavior through time, and equations (including

differential equations) can be written to describe the behavior of the variables. The components have a discrete number of terminals, whereby they can be connected to other components.

Above the circuit level is the logic level. While the circuit level in digital technology is very similar to the rest of electrical engineering, the logic level is the point at which digital technology becomes separate from electrical engineering. The behavior of a system is now described by discrete variables which take on only two values, called 0 and 1 (or + and -, true and false, high and low). The components perform logical functions called AND, OR, NAND, NOR, and NOT. Systems are constructed in the same way as at the circuit level, by connecting the terminals of components, which thereby identify their behavioral values. After a system has been so constructed, the laws of boolean algebra can be used to compute the behavior of the system from the behavior and properties of its components.

In addition to combinatorial logic circuits, whose outputs are directly related to the inputs at any instant of time, there are sequential logic circuits which have the ability to hold values over time and thus store information. The problem that the combinatorial-level analysis solves is the production of a set of outputs at time t as a function of a number of inputs at the same time t. The representation of a sequential switching circuit is basically the same as that of a combinatorial switching circuit, although one needs to add memory components, such as delay elements (which produce as output at time t - ). Thus the equations that specify sequential logic circuit structure must be difference equations involving time, rather than the simple boolean algebra equations which describe purely combinatorial logic

ciruits.

A glance at Figure 2 reveals there is another part to the logic level. This part is called the RT (register-transfer) level. The components of the RT system level are registers (devices that hold a set of bits) and the functional transfers between those registers. The functional transfers occur as the system undergoes discrete operations, whereby the values of various registers are combined according to some rule and then are stored (transferred) into another register. The rule or law of combination may be almost anything, from the simple unmodified transfer (A <-- B) to logical combination (A <-- B ^ C) or arithmetic combination (A <-- B + (plus) C). Thus a specification of the behavior, equivalent to the boolean equations of sequential circuits or to the differential equations of the circuit level, is a set of expressions (often called productions) which give the conditions under which such transfers will be made.

The fourth and last level in Figure 2 is called the PMS (Processor-Memory-Switch) level. At this level one sees only the most aggregate behavior of a computer system. The PMS level consists of central processors, core memories, tapes, disks, input/output processors, communications lines, printers, tape controllers, busses, teleprinters, scopes, etc. The computer system is viewed as processing a medium, information, which can be measured in bits (or digits, characters, words, etc.). Thus the components have capacities and flow rates as their operating characteristics.

The program level has been dropped from the original set of levels shown in Bell and Newell. It was a functional level rather than a structural level,

causing some ambiguities about placement relative to the other levels. The ambiguity is best illustrated by noting that the ISP notation, which was introduced to describe the original program level, has since been used to describe behavior at several of the other levels in Figure 2. For example, ISP has been used at the PMS level to describe the address translation mechanism for inter-computer-module sharing [Fuller, et al, 1973b] and at the RT level within DEC for simulation and microprogramming.

Since the PMS level (processors, memories, and transducers), interconnected by switches (often in a bus structure), was tentatively proposed as a level in 1971, it has become recognized as a formal level. Design at that level has become important as attempts are made to build models of system-level behavior, and will become more important as microcomputers become a standard structural building block and as the cost of interconnect dominates system cost.

Many notations are used at each of the four structural levels. Two of the less common ones are at the PMS and ISP levels. A complete description of the PMS and ISP notations is given in [Bell and Newell, 1971: Chapter 2]. Those aspects of PMS which are used in this book are described in Appendix 2. ISP notation has evolved to ISPS and is described in Appendix 1.

#### VIEW 2: Levels of Interpreters

In contrast to the structural viewpoint given in View 1, this view is functional. According to this view, a computer system consists of layers of interpreters, much like the layers of the onion skin model given in Figure 15.

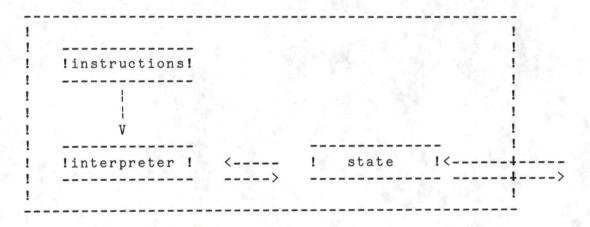

An interpreter is a processing system which is driven by instructions and operates upon state information. The basic interpretive loop is shown in Fig. Iloop. It is most familiar at the machine language level, but it also exists at several other levels.

To formalize the notion of levels of interpretation, one can represent a processing system by the diagram in Fig. formalproc.

Figure Formalproc: A processing system

The state information operated on by an interpreter is either "internal" or "external". This can best be understood by considering the "onion skin" levels of the four processing systems that form a typical airline reservation system. These levels are listed in Table four.

Table Four

Chapter 1

G. Bell, C. Mudge, J. McNamara

Latest Edit 3/8/78

Level 4 Instruction: seat allocation request message

Interpreter: airline reservation system

Internal State: number of requests pending at this moment

location of passenger list on a disk file

number of lines connected to system

rotational position of disk

External State: number of reserved seats on a given flight

airline name for a given flight

Level 3 Instructions: Fortran statement codes

Interpreter: Fortran Execution System

Internal State: memory management parameters

user name

main storage size location of disk files

interrupt enable bits

expression evaluation stack

dimensions of arrays

External State: subroutine names

values of data in arrays

statement number program size

value of an expression DO-loop variable value

printed characters on line printer

Level 2 Instructions: machine language instructions

Interpreter: processor

Internal State: program registers

condition codes program counter

External State: data in main memory

disk-controller registers

Level 1 Instructions: microcode

Interpreter: micro machine

Internal State: instruction register

flip-flops holding error status

stack of microprogram subroutine links

External State: program registers

condition codes

program counter (END, TABLE 4)

The Level 1 system is a microprogrammed processor implemented in real hardware. It is the machine seen by the logic designer. The Level 2 system is the CPU. It is the machine seen by the machine language programmer. The Level 3 system shown here is a FORTRAN-language processing system. The Level 4 system is an airline-reservation system. This interpreter operates on messages received from outside of the system, tests and modifies the state, and generates messages to send back. These four systems form the hierarchy shown in Fig. Hier. Each interpreter sequences through multiple steps in order to perform a single operation for the next-higher-level interpreter.

In practice, few systems are levels of pure interpreters, although layers are present. There are two primary departures from the pure interpreter model: (a) high-level-languages are usually executed by a compiler rather than by an interpreter, and (b) some layers are bypassed when more ideal primitives exist at deeper levels. Figure Pipes illustrates this bypassing process. A pure interpreter implementation of Fortran would use an object time system (OTS) for all Fortran operations designated in the figure as "Type C". The OTS would require an operating system (OPSYS) for the interpretation of some of its operations, and the operating system in turn would be interpreted by the ISP interpreter. However, the Type A operations in the figure would be directly interpreted by the ISP interpreter.

Having presented the pure interpreter model, one can now return to the onion skin layered model and better understand how the different layers relate.

The macromachine hardware can be thought of as a base level interpreter. It is

most often extended upward with an operating system. There may be several operating system levels so that the machine can be built up in an orderly fashion. A kernel machine might manage and diagnose the hardware components (disks, terminals) and provide synchronizing operations so that the multiple processes controlling the physical hardware can operate quasi-concurrently. Next, more complex operations like the file system and basic utilities are added, followed by policy elements such as facilities resource management and accounting. As viewed through the operating system, one sees a much different machine than that provided by the basic instruction-set architecture. In fact, the resultant machine is hardly recognizable as the architecture most usually given by a symbolic assembler. It includes the basic machine, but has much more capable I/O and often the ability to be shared by many programs (or tasks).

Operating systems designers believe all these facilities are necessary in order to implement the next higher level interpreter—the standard language. The language level may include interpreters or compilers to translate back to the machine architecture for ALGOL, BASIC, COBOL, FORTRAN, etc. or any of the other hundred standard languages and their dialects. At the language level, a user again observes a common language machine.

Often an additional special language is used because an application can't be easily expressed using the standard language and it is necessary to have operations that are within the domain of the problem. Using a special language, various application subprograms (a program library) can be created to enable specific application programs to be written. One then may build the application and finally the real user can get a problem solved in a

cost-effective fashion provided there has been the right set of operations (languages) at each of the levels.

Sometimes the stratification is done to help manage complexity or to allow specialization of design activities. Sometimes the underlying layers are completely hidden from the user to aid ease of use [Mudge, 1973].

Finally, note that using fundamentally different outer layers for a common inner set of layers creates quite different machines, hence a set of onions. Therefore it is important to realize that when dealing with common core hardware, multiple operating systems, languages and applications, a network of machines (a crop of onions) is formed, not just a single, layered machine.

In the final analysis, the number of levels is just another tradeoff.

Performance considerations lead to the deletion of levels, complexity leads to the addition of levels.

#### VIEW 3: Packaging Levels of Integration

This is a structural view that <u>packages</u> the various components (hardware and software) into levels. The current levels for DEC computers are as follows.

- 9 applications

- 8 applications components

- 7 special languages

- 6 standard languages

- 5 operating systems

- 4 cabinets

- 3 boxes

- 2 boards

- 1 integrated circuits

This view is the most important in the book, because it shows how computer systems are actually structured, and hence how their costs are structured. Being a structural view of the object being sold, however, it is completely a function of the technology, the organization building the system, and the marketplace, all of which are so rapidly changing with time that the view could better be titled "Dynamic Levels of Integration". There are three major changes taking place:

- 1. Changes in the hardware levels, where the shrinking in physical size of functions has three effects:

- a. Lower levels subsume higher levels

- b. The semiconductor component supplier is forced to assume higher and higher level design responsibilities

- c. Levels disappear

- 2. Changes in the software levels, again with three effects:

- a. Each level grows in size as more functionality is added over time

- b. More levels are added as minicomputers are applied to a broader range of applications

- c. Functions migrate downward from level to level

- 3. Changes in the hardware/software interface, where software functions migrate into hardware for higher performance

For the first of these areas of change, hardware levels, it is interesting to note that interconnection and packaging now constrain and limit design more than any other factor, excluding the basic lowest level component (semiconductor) technology.

The constraining and limiting by the interconnection and packaging take place because most manufacturing costs are associated with the physical structure. As interconnection levels must be introduced to build complex structures, many usually unwanted side-effects occur. The interconnection requires space and interferes with cooling air flow. Long interconnections increase signal transmission delays, and these reduce performance. Signal transmission not only makes the computer susceptable to electromechanical interference, but also may radiate electromagnetic waves will need to be controlled. Finally, there is the domain of industrial design or aesthetics, and everyone is a self-based authority on appearance.

Figure 11 shows the costs of various levels-of-integration versus time for small computers. The cost depends partly on implementation and architecture word-length. As the word-length is made shorter, there is some economy particularly for very small computers, because some levels of integration cease to exist. For example, most hand held calculators are implemented using 4-bit, stored program computers with fixed programs that occupy a single IC. They have no associated modules, backplanes, boxes and cabinets--only a single package that fits one's hand.

Note from Fig. 11 that semiconductors, the lowest level of technology, have had the greatest price decline. This should continue as multiple dice are mounted on one substrate. Modules have a lesser price decline because they are a mix of ICs, printed circuit boards, component insertion labor (and capital equipment to assist insertion), and testing labor (and capital equipment to assist testing). The price decline for the IC portion of the module cost is moderated by the labor intensive nature of module fabrication, thus producing a price decline for modules that is markedly less than that for ICs. At the box level-of-integration, power supplies and metal or plastic boxes are also labor intensive and further moderate the price decline provided by the IC's. Finally, as boxes are integrated (by people), and applied at a system level (by people), the price decline has almost disappeared.

Many of the cost improvements brought about by new technology are derivative.

They are by-products of using less power and less space, thus avoiding the labor intensive levels of packaging integration.

An astute marketing-oriented person might ask, "How, with all the technology

can we do something unique so that we can maximum the benefit from the technology without having to pay so much for labor intensive items such as packaging?" One answer: "Reduce prices by not providing a power supply and mounting hardware. Let the user provide all added-on parts and mount the computer as needed. In this way, the price, though not necessarily the total cost to the user, is reduced. We'll sell at the board level." Computer Automation introduced the "Naked Mini" TM in 1972 at a lower component price so that users could supply more added value - packaging and power technology.

A similar effect can be seen in the PDP-11 series since the PDP-11/20's introduction in 1970. Most models were sold at the box and cabinet level with module level options. In 1976, the LSI11 was sold at the module level, where a module with 4,096 words of memory and processor was provided for \$600. The boxed version costs x, reflecting a negligible improvement over the PDP-11/20 in packaging, since the PDP-11/20 boxed version sold for x1.

The changing levels of integration have also changed the domain of the semiconductor suppliers. In the early 70s, Intel, North American Rockwell, and other semiconductor companies began to use the higher semiconductor densities to reduce the number of levels of integration by packaging a complete processor-on-a-chip. These organizations had assimilated logic design, but were frustrated because their customers could really not identify higher functionality units (beyond memory) requiring on the order of 1,000 gates on a chip. Also, the speed of these high density units was quite low.

They discovered that the best finite state machine to make was just a simple computer, because it provided the finite state machine plus the useful

functions that were not covered by switching circuit theory. It became "simply a small matter of programming" to do something useful. While programs for these simple computers cost \$1-\$100 per instruction to write, the prices for processors-on-a-chip have followed a very steep decline of up to 50% price reduction/year.

Robert Noyce, of Intel, presented Fig. 12 in October 1975. It illustrates what has been happening in the semiconductor industry, and has been modified slightly to show the technology that DEC has assimilated with time. It indicates the breadth semiconductor manufacturers now have in technology, starting from semiconductor device level, through the view Noyce has of the various levels-of-integration, and continuing into end user applications.

Figure 13 assigns ordinal numbers to the levels-of-integration used throughout the book in an attempt to structure this knowledge in a way that will hopefully be viable for quite some time - say 10 years. The numbers associate the physical levels-of-integration with the corresponding levels of the abstract machine (and its language) and with the conceptual levels' design disciplines. Figure 13 also shows how a group of levels are compressed for smaller systems such as hand calculators and more spread out for larger systems.

The levels-of-integration viewpoint can be summarized as components of one level being combined into a system at the next highest level in a hierarchy. A level denotes that there is a single conceptual design discipline or set of interacting disciplines which determine the function, structure, performance and cost of the constituent level. "Level" is a deceptive word, because as

Fig. 14 shows, the structure is actually a lattice or network, and not a tree.

Furthermore, each level can be nested itself.

#### VIEW 4: Computer Classes: A Marketplace View

### SEE p. 1a

Because it is the complete marketplace process (Fig. 1) that produces the computer, this view is the most complex. A computer is characterized (in terms of marketability) as a function of price, performance, and time of introduction in what might appear to be a commodity-like environment.

Because various computers operate at different performance rates and at various costs, computation can be purchased in multiple ways, and price/performance ratios will thus affect marketability. For example: computation can be supplied by a shared large, central batch computer; each organizational entity can own and operate a shared minicomputer; an individual can operate a single desk top system; or each individual can operate a programmable calculator.

Price/performance is not the sole factor determining marketability, however. Program compatibility with previous machines is very important. When users write programs, there is a lifetime associated with the use of those programs, and thus a need to have compatible processors for running those programs today and for a substantial time into the future. Thus, while the supply of rapidly evolving technology permits new designs to be more cost effective, and even radical, continuity with the past must exist.

The Marketplace View begins with a description of how technology provides basic improvements with each new generation (every 6 or so years). An example of alternative new designs is given to show why most new designs usually provide increased performance at constant price. With this background, the

four price/performance classes that have evolved over the last four generations are presented. This simple model is then elaborated and critiqued.

The influence of technology on the computers that are built and taken to the marketplace is so strong that the four generations of computers have been named after the technology of their components: vacuum-tubes, transistors, integrated-circuits (multiple transistors packaged together), and LSI circuits (Large-Scale Integration). Every electronic technology has its own set of characteristics (e.g., cost, speed, heat dissipation, packing density, reliability), all of which the designer must balance. These factors combine to limit the applicability of any one technology; typically, one technology is used until a limit is reached, or another technology supersedes the old.

When an improved basic technology becomes available to a computer designer, there are four paths the designs can take to incorporate the technology:

- use the newer technology to build a cheaper system with the same performance;

- hold the price constant and use the technological improvement to get an increase in performance;

- 3. push the design to the limits of the new technology, thereby increasing both performance and price; or

- 4. find a drastically new structure using the computer as a basic archetype (e.g., calculators) such that the design can be considered off the

evolutionary path.

Figure x shows the trajectory of the first three of the design alternatives. In general, the design alternatives occur in an evolutionary fashion as in Fig. y with a first (base) design, and subsequent designs evolving from the base.

In the first design style, the performance is held constant and the improved technology is used to build lower-cost machines which attract new applications. This design style has as its most important consequence the concept of the "minimal computer". The minimal computer has traditionally been the vehicle for entering new applications, since it is the smallest computer that can be constructed with a given technology. Each year, as the price of the minimal computer price declines, new applications become economically feasible.

The second, constant cost alternative uses the improved technology to get better performance, and will usually yield the best increase in total system-cost-effectiveness. This approach provides a growth in performance and quality at a constant price and is probably the best for the majority of existing users.

If the new technology is used to build the most powerful machine possible (the third alternative design style), then the designs often advance the state of the art. New designs should solve previously unsolved problems. Going too far in price or performance, (i.e., building beyond the technology) is dangerous and can lead to a zero performance, high cost product. There are

usually two motivations for operating at this leading edge: preliminary research motivated by the knowledge that the technology will catch up; and national defense, where an essentially infinite amount of money is available because the benefit--avoiding annihilation--is infinite.

The following table shows the effect of pursuing the two design strategies of

1) constant performance at decreased price, or 2) constant price at increased

performance.

<u>Table:</u> Using New Technology for Constant Cost and Constant Performance Designs Introduction time t t+1 t+1 (generation)

| Design style                                      | base case | constant cost, increased performance | constant<br>performance,<br>decreased<br>price | constant performance, decreased price |  |

|---------------------------------------------------|-----------|--------------------------------------|------------------------------------------------|---------------------------------------|--|

| Application                                       | base      | base                                 | base                                           | new base                              |  |

| Computer price                                    | 1         | 1                                    | 0.5                                            | 0.5                                   |  |

| Operating costs (range)                           | 2-4       | 2-4                                  | 2-4                                            | 1-2                                   |  |

| Total cost                                        | 3-5       | 3-5                                  | 2.5-4.5                                        | 1.5-3                                 |  |

| Performance (and improvement)                     | 1         | 2                                    | 1                                              | 1                                     |  |

| Improvement (in total cost)                       | 1         | 1                                    | .839                                           | .56                                   |  |

| Performance/price (computer only and improvement) | 1         | 2                                    | 2                                              | 2                                     |  |

| Performance/<br>Total-cost                        | .332      | .664                                 | .422                                           | .664                                  |  |

| <pre>Improvement in (Perf./total cost)</pre>      | 1         | 2                                    | 1.21-1.1                                       | 2                                     |  |

The first column gives the base case at a given generation/time, t. The price, performance and performance/price ratio of the computer are all 1. As the computer is applied to a particular environment, operational overhead is added at a cost of 2 to 4 times the original price of the computer; the total cost to operate the computer becomes 3 to 5, and the performance/total-cost ratio is reduced to between .33 and .2 (depending on the total cost).

Now assume the same operating environment, with the same fixed (overhead) costs to operate, at a new generation time, t+1 when technology has "improved"

Latest Edit 3/8/78

by a factor 2. Two alternative designs are carried out, one is at constant price/higher performance and the other is at constant performance/lower price (cols. 2 and 3). The application is constant in three cases (cols. 1-3) and a new base application is discovered for the fourth case (col. 4). Both the constant cost and constant performance designs give the same basic performance/cost improvement -- when only the cost of the computer is considered. However, when one considers the high fixed overhead costs associated with a base application (cols. 1-3), there is a relatively small improvement in cost performance/cost, although there is a cost savings of 17 to 10 per cent with the minimal design. The greatest gains come in applying the computer with greater performance and getting the attendant factor of 2 gain in performance and in performance/price ratio.

To summarize, the constant-price / increased-performance design style gives a better gain because operating costs remain the same. Its gain can only be equalled by the constant-performance design style when operating costs are halved upon its application. This only occurs when a new application is tackled.

Applying the three design styles shown in Fig. x over several generations produces the plot given in Fig. 6. These figures lead to one of the most interesting results of the Marketplace View, which is that computer classes can be distinguished by price and named as follows: sub-micro (to come in the next generation -- say by 1980), micro, mini, midi, maxi, and super. classes midi- and maxi- are sometimes referred to by the single, non-descriptive name, mainframe.

When one distinguishes computer classes by price, a new range of price can be made possible by new technology and create a new class. The new class appears at the low end of the price scale where the minimal computer is introduced at a significantly lower price level than existing computers.

While the measure used to define a new class is price, the measure defining an established class is performance. This is because once a new class has become established in the marketplace, the users become familiar with what computers of that class can do for their applications, and tend to characterize that class on a performance basis. The characterization of existing classes on a performance basis is important to this discussion because at each new technology time, performance increases by one category, and midi performance becomes available on a mini, for example.

The effect of technology upon computer classes can be summarized in the following thesis:

Continual application of technology via the two major design styles results in

- (a) price declines which create new classes of computers,

- (b) new classes becoming established classes, and

- (c) established classes becoming encroached upon.

To refine the thesis, some additional commentary is in order. First, some question may arise as to how much of a price reduction is necessary to create a new class. The continuity implied by the thesis is deceptive in that it

suggests that new classes come about by the continual application of the constant-performance, decreasing cost style of design. Viewing the industry as a whole, this is true. However, a new class is usually not created by the same organization that is designing computers in existing classes. A new company, or new organization within a company, is usually required to provide the requisite fresh viewpoint needed to create a new class. It is the fresh viewpoint and not some arbitrary amount of price reduction that creates a new class.

The minicomputer class came about by DEC founders taking the view that simple machines, unencumbered by the costly general purpose facilities of the mainframes (many data types, sharing mechanisms, etc.), could be built and would be viable.

While the minimal design philosophy pervaded for nearly 10 years as the minicomputer, the semiconductor-based, processor-on-a-chip computer (called microcomputers) name identifies a significantly lower priced computer. This lower cost is fundamentally based on the elimination of a level of integration (interconnection). The microcomputer is dispelling the lethargy growing around the constant-price minicomputer of the mid-1970's and is generally being promoted by companies not in the minicomputer business, or by separate organizations within the minicomputer companies.

The sub-microcomputer is predicted to be a complete computer (with both processor and program memory) on a single chip, although it is not as radical as the microprocessor which eliminated the concept of the box-of-boards computer.

In both the mini and micro cases a fresh organization broke out. Why is a fresh viewpoint needed? Because existing organizations, like most human organizations, act to preserve the status quo, and produce constant-price computers. This can be explained by examining each part of the organization in turn.

- 1. The existing user, who is the potential customer for a new system has a set of fixed costs (overhead). Thus by the same arguments that were just discussed in conjunction with constant cost and constant performance design styles, the existing user generally wants more performance rather than lower price. Productivity improvements are required to stay at equilibrium with his organization and to sustain or increase funding. Operating costs (personnel, paper, power, etc.) are likely increasing due to inflation, and although a lesser priced machine could hold performance/cost constant, there would be no productivity gain. Requiring less or equal funds, would ultimately cause the loss of organizational power since this is based on people, expenses, ability to provide increased service, etc. Thus, the pressure is to get larger, more powerful machines. Furthermore, his software investment requires that the new system be compatible with his earlier system.

- 2. The sales force respond mainly to orders which are lost because of poor performance, because its measure is so tangible. Price (and even lack of functionality) is considered only when the performance of two alternatives is equal. The amount of work a salesperson has to do is measured in sales yields and, indirectly, the number of systems sold.

The reduction of the sales price of a given system by a factor of two, requires selling twice the number of systems to bring in a constant amount of sales dollars. This implies working significantly harder (neglecting the effects of price elasticity). For example, within DEC, because of the wide price range of its products, a salesperson need sell only one large system per year, while at the low end he must sell 1500.

- 3. Marketing reinforces the inputs from the sales force, while interjecting its own bias and noise. Because of the broad range of applications, it presents conflicting product definitions. Thus, a new product must have: the performance of the current most competitive machines; the price of the most marginal competitor (who may be losing money to enter the market); the software of all the competitors (since each differentiates itself by unique software); and all the service of the largest (and possibly highest price competitor).

- 4. Engineering. The new product specification input is to improve performance as seen in paragraph 1 above. Technology pushes engineers to use higher-performance components since technology suppliers behave in an identical fashion to the computer supplier. Although there are various styles of designs (and designers), the most common tendency of the designer is to use new technology to provide higher performance, and to solve the problems inherent in subsequent designs rather than working to reduce costs again. The PDP-8 family provides an example.

- 5. Manufacturing constraints and planning are similar to sales. A plant

is measured in units, quality level, and unit cost. Preserving a given cash flow, when faced with radically different cost products, usually requires substantially different planning, materials handling, manufacturing, testing, etc. The radical changes for a higher volume business (i.e., long term planning) is difficult. Product design change ideas fed back to engineering usually address solving previous problems that add to product cost, rather than addressing radical concepts that could create a new computer class.

The new organization, in addition to providing a fresh viewpoint, must also provide the capability and willingness to deal with progress in multiple areas of technology if the maximum evolution rate for the computer price class thesis is to be maintained. The computer class thesis may seem to suggest that there is one monolithic technology, steadfastly progressing, which provides incremental improvements. In fact, there are several technologies. example, to fully exploit each new circuit technology improvement, a matching advance in packaging technology is needed. Higher circuit densities demand new cooling methods; lower-cost module carriers are needed to match the lower cost microprocessor-based control techniques. However, since engineering projects tend to minimize the number of risk dimensions, a new circuit technology is generally used twice: once with existing packaging and a second time with packaging that matches the technology. There are examples in both the PDP-11 and S/370 families. In addition to packaging technology, mass storage, primary memory, I/O units, logic, and power are areas whose technology must move ahead in step. Unfortunately, in practice this does not occur. Memory prices have consistently halved every two years, whereas electro-mechanical technology is slowly increasing in price.

One of the by-products of the use of new technology is that conflicts occur within the established computer classes. An established computer class, since it is defined on the basis of performance, is entered by constant cost/higher performance successors from the class below it. Moreover, suppliers within a class are, by their dominant constant price/ higher performance evolution, operating to move up out of the class.

While movement by computer designs and computer suppliers between and amongst the various classes may be encouraged by price and performance trends, the speed with which that movement occurs is moderated by software compatibility considerations. The computer class thesis is not meant to imply that each class implements the same instruction set and PMS-level configurations, and that they differ only in speed. Rather, much specialization occurs in each class and many of the attributes of the higher performance machines appear to substantially lesser degrees in the lower performance classes. For example, there are more data types in the larger machines, their address spaces (both physical and virtual) are larger, and the software support is generally broader. Resources devoted to increasing reliability and availability are more common in the higher priced machines. The PDP-11 family, from the VAX-11/780 down to the LSI-11, exemplify these functionality differences.

Another important aspect of the Marketplace View, in addition to the idea of dividing computers into classes based on price for new classes and performance for existing classes, is the concept of economy of scale in the computer industry.

For nearly all man-made objects, such as transportation vehicles, electricity

generators, or buildings, there is usually some economy of scale because there are high fixed costs that do not increase as rapidly as the output of an object increases.

For computers, factors leading to economies of scale often apply over several dimensions. The same software can be used on many models. Sales and field service people can attend to a wide range of equipment. Manufacturing facilities can be adapted to produce different models.

Grosch (1953) suggested that there was an economy of scale for computers according to the performance/price relationship:

2

Performance = constant x Price

Several studies [Bell and Newell, 1971; Knight, 1966; Solomon, 1966; Phister, 1976; Sharpe, 1969; Turn, 1974] have examined whether this is true for a given set of machines. While it is possible to price machines using this relationship, and while it is clearly desirable that the performance increase more rapidly than price for improved operating economy, there is some doubt that the square law holds. Indeed, over the narrow range of prices studied (a factor of four), a linear approximation to the data would appear to fit as well as the square law does. See Fig. Groschlin.

While a square law performance/price relationship is probably too extreme in the case of most computer components, there are some cases where a square law does apply, and other cases where substantially nonlinear performance/price

relationships do exist.

A computer component that could be predicated on a nearly square law relationship is the core memory. The electronic selection is square law; a doubling of the selection circuitry provides access to a four times larger stack. The manufacturing cost for larger stacks follows a less dramatic economy of scale since there is a high set-up cost to threading core memories, and larger memories spread this cost over more bits. All other costs are roughly linear, including such overheard costs as memory packaging, memory power and memory interface.

The definition of performance,

performance = memory size x processing rate

is akin to saying that the performance of an automotive vehicle is the product of its speed and the number of passengers it carries. If one uses this definition, then memory performance does increase as the square of memory price, since both factors (size and rate) are each a function of memory price. To derive this one proceeds as follows.

Let P = price of the memory on the system. Assume the use of a  $2^k$  x 1 memory chip and a memory system n bits wide, and further assume that the processor can use 100% of the memory data rate. To supply concrete cost and performance parameters, use the 4 Kilobit chip; in 1978 it costs about \$25 and had a cycle time (at the processor) of about 500 nanoseconds.

Then,

processing rate = memory data rate

=

$$2.10^6$$

(n + m) where m = number of chips in the processor

=  $2.10^6$  (n + kn) since m is a function of n

=  $2.10^6$  K  $^1$ n

=  $K^{11} - \frac{P}{25}$  since n =  $\frac{P}{25}$  price per chip

and,

substituting, one gets

performance =

$$\frac{4096}{25}$$

=  $K^{11}$   $\frac{P}{---}$  25

Equally important to the hardware considerations of the Marketplace View are the software considerations. Nearly all modern computer designs are part of a compatible computer family which extends over price and time. Compatibility considerations are based on the economic necessity to utilize a common software base. The users' investment in software dwarfs that of the manufacturer, assuming the machine is successful. For example, if there is only one man year of software investment associated with the 50,000 PDP-11s, and each man year costs about \$40,000 and produces something on the order of 5,000 instructions, then there is a cumulative investment of 2 billion dollars

the same scale as the original hardware cost.

and 250 million lines of program for the PDP-11. This investment is roughly

Since technology provides such rapid changes over the generations, it is obvious that there must be backward (in time) compatibility in order to build on and preserve the user's program base. He must be able to operate programs unchanged to take advantage of improvements brought about by technology changes.

In a similar way, compatibility over a range of machines, at a given time is desirable so a user may select a machine that matches his problem set, while having the comfort that the problem can change and there will be a sufficiently large or small machine. As the problem changes with time, it is also desirable to have the appropriate, competitive, compatible machine.

Thus the goals for a complete, compatible computer product line (i.e., set of products) might be:

- 1. the widest range of products in terms of price offering;

- 2. the largest economy of scale factor for performance that separates the models;

- 3. the smallest number of models to minimize costs of design, manufacture, selling and spares inventory;

- 4. the most cost-effective/competitive products (nearest to

with minor additions.

competitive machines) for each price in the space; and

- 5. backward compatibility with past machines.

Goals 3 and 4 are contradictory. How can the number of models be minimized, while at the same time providing competitive machines over a continuous space?

A possible method is described in Bell and Newell (1971) where a multiprocessor alternative to the System/360 is proposed. This approach provides increased reliability and the ability to easily upgrade performance

- Chapter of "The PDP-11 After Three Generations" discusses quantitatively the performance range spanned by the PDP-11, compares it with the span of the S/360, and contrasts the different techniques used.

The discussion of the Marketplace View is a qualitative explanation of the effect of technology on the computer industry. It is an engineering view, rather than one that would be given by technology historians or economists. The twenty years described in this book and the individual cost and performance measures surely invite analysis by professionals. The studies reported in [Sharpe, 1969] are a good departure point.

# VIEW 5: Computer Classes: an Applications/Functional View

Because of the general-purpose nature of computers, all of the functional specialization occurs at the time of programming rather than at the time of their design. As a result, there is remarkably little shaping of computer structure to fit the function to be performed.

The shaping that does take place uses five primary techniques.

#### 1. PMS-level configuration

A configuration is chosen to match the function to be performed. The user (designer) chooses the amount of primary memory, the number and types of secondary memory, the types of switches, and the number and types of transducers to suit his particular application.

#### 2. Physical packaging

Special environmental packaging is used to specialize a computer system for certain environments, e.g., factory floor, submarine, or aerospace applications.

#### 3. Data-type emphasis

Computers are designed with data types (and operations to match) that are appropriate to their tasks. Some emphasize floating-point arithmetic, others string handling. Special-purpose processors, such as Fast Fourier Transform processors, belong in this category also.

#### 4. Operating-system

The generality of the computer is used to program operating systems that emphasize batch, time-sharing, real-time, or transacting processing needs.

### Current Dimensions of Use

In the early days of computers, there were just two classifications of computer use, scientific and commercial. By 1971, when Computer Structures [Bell and Newell] traced the evolution of computer use, computer use had diversified to seven different functional segmentations: scientific, business, control, communication, file control, terminal, and time-sharing. Since that time, very little has changed in terms of functional characterization, but two points are worthy of comment. First, file control computers still have not materialized as mainstream separate functional entities, despite isolated cases such as the IBM 3850 mass-storage system, and second, terminal computers have evolved to a much higher degree than expected.

The high degree of evolution in terminals has been due to the use of microprocessors as control elements, thus providing every terminal with a stored program computer. Given this generality, it is has been an easy matter to provide the terminal user with facilities to write programs. In turn, this phenomenon has affected the evolution of time-sharing (when using the term to denote close man-machine interaction as opposed to shared use of an expensive resource).

Functional segmentation into categories with labels such as "business", "control", communication", and "file control" reflects a naming convention rooted in the old two category "scientific"/"commercial" tradition. An

alternative classification, more useful today, is the segmentation scheme shown in fable Fundiso. It is based on the intellectual disciplines and environment (e.g., home based) using and developing the computer systems. It shows the evolving structures in each of the disciplines, permitting one to see that nearly all the environments evolve to provide some form of direct, interactive use in a multiprogrammed environment. The structures that interconnect to mechanical processes are predominately for manufacturing control. Other environments, such as transportation, are also basically real time control. Another feature of discipline-based functional segmentation is the fact that each of the disciplines operate on different symbols.

Commercial (or financial control) based environments hold records of identifier names for entities (e.g., part number) and numbers which are values for the entity (e.g., cost, number in inventory).

# Table FunDisc: Discipline/Environment Based Functional Segmentation Scheme

Commercial environment [financial control for all industry, retail/wholesale distribution=billing, inventory, payroll, accounts receivable/payable] = records storage and processing traditional batch transaction processing against data base business analysis (includes calculators)\*

Scientific\*, engineering and design based environment

=numbers, algorithms, symbols, text, graphs storage and processing

traditional batch computation\*

data acquisition\*

interactive problem solving\*