CHAPTER 2: TECHNOLOGY, PACKAGING AND MANUFACTURING 2/13/78

### TECHNOLOGY PUSH

Whereas the rest of the book gives examples of the effects of technology push, Mus in this section we define the individual components within the context of use. As users, we must have a model of what the technology has been so that short-term extrapolations are possible.

We should, for completeness, discuss all the technologies shown in the tree of the relevant memory and logic technology in Fig. Memtax. Instead we only this concentrate on semiconductors as they have been the dominant factor. Magnetic recording density, on disks and tapes has evolved rapidly too, and must be understood as a component of cost and a limit of performance. Therefore, we present a cursory model of it. We have ignored communications links (because they have not evolved as rapidly as they might). The packaging (cabinets and boxes), interconnection and power aspects are given in the second section. These do not represent pushes but rather are large, high inertia objects that have to be pushed against and eventually yield.

In the semiconductor section we start by presenting a tree of the possible technologies by the function they carry out and show how these have evolved over the last two or three generations to affect computer engineering. The other relevant cost, semiconductor density, performance and reliability parameters are also briefly discussed.

Page 2

G. Bell

created 1/4/78, latest edit 2/13/78

n mores on to Vie Following the semiconductor evolution model, we discuss how the semiconductors have been applied using various logical design methods and how they have pushed the methods. Of special interest is how and whether users design ICs, as opposed to design with ICs. (The conclusion should be obvious... IC design is expensive and time consuming and should be avoided for all but a few applications.) The advice can also be carried over to those who believe it is necessary to program in assembly language or to have access to microprograms. ceople believe Vuar For some reason, the belief is that there is a need to have access to lower Thes is aken level building blocks when building many large objects. We advise using bricks and mortar, not finding a sand pit, cement and brick factors to fabricate bricks and mix mortar.

There are two sections on memories. The core memory provides a number of y lessons on managing evolving technology; it was the dominant primary memory for about 15 years even though it was challenged several times. It eventually lost because of the larger amount of development being applied to semiconductors. A section describes the notion of memory hierarchies and how they operate to utilize virtually every memory that's either cheaper or faster than any other memory.

In the final section we present some general observations about technology evolution: how technology is measured, why it evolves (or doesn't), cases of it being overthrown and a general model for how it operates and is managed.

Since the chapter is on the evolution and interaction of logic and memory

Chapter 2: Technology, Packaging and Manufacturing Page 3 G. Bell created 1/4/78, latest edit 2/13/78

technology as they effect computer design, the best way to observe the change is via the time line diagram (see Fig. LMtimeline). For logic, small memories, read-only memories and primary memories four lines give the significant events (both in the industry and DEC) that have affected the technology push. The remainder of this section will refer back to the tradeoffs.

#### SEMICONDUCTOR TECHNOLOGY

A single transistor circuit performing a primitive logic function within an integrated circuit (IC) is among the smallest most complex of man-made objects. Alone, such a circuit is intrinsically trivial; but the fabrication process for a set of structures to form a complete integrated circuit is complex. To us, as digital IC users, there are several relevant parameters:

- 1. The function an individual circuit performs within the IC, the aggregate function of the IC, and the functions a complete IC family perform.

- The number of primitive digital switching circuits (or transistors) per IC. This density is a measure of the capability of the IC process.

- 3. Cost.

- 4. The performance of each circuit and the performance of the aggregate IC and/or set of ICs within a family as they affect system performance (as measured by the time it takes to perform its function). The semiconductor

G. Bell

created 1/4/78, latest edit 2/13/78

circuit technology family usually determines this performance.

(TT, Shattling, ECL)

5. The number of interconnections (pins) to communicate outside the IC. This in turn interacts to permit more complex functions to be performed by a complete IC family.

6. The reliability. This parameter is a function of the circuit technology, density, number of pins, the operating temperature and use (or misuse).

7. Power consumption.

#### Function

Figure ICtree shows a family tree (taxonomy) of the most common digital IC's, roughly in order of increasing complexity. The secondary ordering is roughly by the regularity of the function being implemented, and whether there is memory associated with the function. The clustering of circuit types is also by technology generations (from the second to possibly the fifth). Note that we can build large totally regular functions with only memory (e.g., various registers and memories) and with no memory (e.g., adders, multipliers, multiplexors). With large scale integrated circuits it is desirable to implement regular structures to simplify understanding, and aid the testing build in generality.

In the early third generation only completely unconnected components were built. Collections of the basic logic primitives (AND, NAND, Exclusive OR,

Chapter 2: Technology, Packaging and Manufacturing Page 5 G. Bell created 1/4/78, latest edit 2/13/78 Adders) and sequential circuit components (i.e., separated flip flops or collections to simple form registers) permitted what had been logic functions CUT that occupied a single printed circuit board module of the first and second generations to occupy a single IC. This forced modules to take on specialized functions? The drastic reduction in size from the second to the third compan generation transition can be most vividly, by example in the 18-bit implementations for the PDP-15 (page 00).

As the densities began to improve to a hundred gates, complete arithmetic units began to exist; and the earliest and most famous function, the ALU (Fig. ALU), provided up to 32 functions of two variables (each 4-bits). By the fourth generation, purely combinational circuits included a complete 16 x 16-bit multiplication circuit on a chip, requiring about xx gates.

Without well-defined functions such as adders and multipliers, there is no way semiconductor suppliers can provide high density, high volume products because there are not large scale, general purpose universal functions. The alternative for the users is interconnecting simple logic circuits (AND gates, flip flops). This, of course, does not permit efficient use of the technology and the cost per function remains high (about that of the third generation) skown in Fig Icha Hure are because the printed circuit board and IC packaging costs (pins) limit the attendant cost reduction.

The problem of effectively utilizing LSI by customization methods will be For now, the discussed after we have first traversed and discussed

Chapter 2: Technology, Packaging and Manufacturing Page 6 G. Bell created 1/4/78, latest edit 2/13/78 PLA (for Programmable Logic Array) is an array of AND-OR gates for combinational design that can be interconnected to form the sum of products , by blowing fusable links, Specialization can be done either in the factory or in the field terms. (FPLA) to give the general functions of input variables." Shown in the next branch is the gate array structure, an alternative for doing logical design, but is more powerful them the PLA because boths combinatorial and including sequential circuits. Gate arrays are simply a large number of gates placed on the chip in fixed locations which can be interconnected together during using metalization done in the final stages of semiconductor manufacture. I the free shown in fig IC free There is a special branch for the purely memory functions. (Since memories have so many uses, this branch is discussed separately in the memory section. can used as not only Memory is used in the processor as conventional memory, but it is also an alternative for performing combinational logical functions, (i.e., a value can the be looked-up rather than computed as is custom for logical design) and and the autput distanced by reading the contents of that a sequential logic functions (i.e., the memory can hold states in a the Memory can also be used to implement bequested microprogram). functions. Fritample the mesting can ho tes an a manprogram, -The remainder of the interesting logical functions include combinations of such as logic and memory. There are various special functions like encoding algorithms (e.g., LPC, for Linear Predictive Coding) to use in real time and data encryption communications system, Similarly, data encryption can be carried out utilizing a single, special LSI chip. One of the most useful transducers, and the first one to use LSI, was the UART, for Universal Asynchronous Receiver Transmitter), The reader is invited to read our description of our interaction to define the UART.

Page 8

RI

G. Bell

created 1/4/78, latest edit 2/13/78

nausal on a Although we consider the circuit function to be an attribute that's separated from others, it is clearly dependent on the number of circuits which can be placed on a chip. Thus, circuit density in circuits/chip is the single most fun tonality dekenning chip important parameter . From this measure, we can predict the functions likely to be implemented by just following the tree. It should be noted that the whole tree is relatively alive, i.e., increases in density. Both impr node and allows another tree branch to grow. Only the very low density branches at the top (e.g., unconnected gate and register structures) are n the other acces relatively static. Thus as density increases sufficiently, a new branch grows. For example, the processor-on-a-chip started out as a 4-bit processor (or rather as 2 chips for a single processor) and then progressed to have 8-bit and 16-bit processors on a single chip. Similar effects are observed with the arithmetic logic unit, memories, etc. as density improves.

The number of circuits per IC is the measure of density as seen by a user (see Fig. Semiden). This metric is acutally the product of the circuit area times the number of circuits per unit area. Circuits are also photographically reduced in size to yield higher speeds, higher densities and to have better yields. A third factor, circuit and device innovation, also contributes to density increase. Both measures improve with time, reflecting improvements in funcamental process control.

Semiconductor device (individual circuit) performance is also correlated with the implementation technology and density because reduction in size also reflects reduction in power. Chapter 2: Technology, Packaging and Manufacturing Page 9 G. Bell created 1/4/78, latest edit 2/13/78

### An Operational Model for Memory Size versus Time

The model given in Fig. Semidens is exponential and correlates with our prevents observations(Bell) in 1975 that the number of bits per chip doubled every two years according to the relationship:

## t-1962

number of bits per chip = 2 here are sefarate anne each following this relationship for BOH's in This does not give account for the technologies, whether read only or read write, and whether the time value is associated with production quantities or write, and whether the time value is associated with production quantities or a laboratory curiosity. We must scale the state of the art line appropriately on the product and the quantities, one by one or two years according to the following rules:

### [rules]

This gives the following availability of various semiconductor memories:

| Year when firs<br>widely availab |                 |

|----------------------------------|-----------------|

| 1969-70                          | 16              |

| 1971-72                          | 64              |

| 1973                             | 256             |

| 1975                             | 1024            |

| 1977                             | 4096            |

|                                  | Gechnology push |

The significance of these values is that they determine where certain architectures and implementations can occur. The chapter critiquing the PDP-11 uses this model to show how semiconductors accomplish this push.

Page 10

G. Bell

created 1/4/78, latest edit 2/13/78

emplemented

during int del nost ratentant cliquarteratic tes th The cost of ICs is probably the hardest of all the parameters to identify and predict because it is set by a complex marketplace. For circuits that have been in production for some time and for memory arrays, the price is for more circuits that have not yet reached the essentially a commodity commodity status, the prices are higher and depend on the strategy of the supplier -- whether he is willing to encourage competition. As users, we consider ICs as c as commodities, with the attendant benefits (cost) and problems (having a sufficient source of supply). In these cases, the prices are proportional to the die cost (i.e., the die are) and the manufacturing volume.

Two curves are presented to reflect price of various components/IC. Figure Compprice shows the price per component for an IC assuming LSI. There is a price band for the circuit size and circuit technology. Table GateComp gives some idea of how circuit density (in components) relates to actual functions.

The most useful data to understand past and future computer structures is the semiconductor memory cost curves (see Fig. Memprice). Here, the basic cost/bit of various sized memories is given. We note that In 1978, the cost is roughly .08 and .07 cents per bit for the 4 Kbit and 16 Kbit IC per bit chips respectively, giving costs of \$3.30 and \$11.50 for the ICs respectively. Whereas the chip density improves by a factor of two each (Fig. Semiden) year, the cost per bit (at the IC level) is declining at only a factor of 2 every two years. The line drawn in Fig. Memprice has the equation:

> t-197y cost/bit = K x 0.Y

| Chapter 2: | Technology, | Packaging | and | Manufacturing Page                  | 11 |  |

|------------|-------------|-----------|-----|-------------------------------------|----|--|

| G. Bell    |             |           |     | created 1/4/78, latest edit 2/13/78 |    |  |

|            |             |           |     |                                     |    |  |

It is also interesting that the cost compares favorably with the price decline observed in core memory over the period since 1960-1970 for the 18-bit computers, (page 00) and for the cost declines in both PDP-11 and the PDP-8 (pages 00 and 00).

### Performance

The performance for each semiconductor technology evolves at different rates depending on the cumulative learning associated with design and manufacturing process together with the marketplace pressure to have higher performance for the particular technology. We may hypothesize that each technology can be looked at as being relatively appealing or relevant to the particular design(er) styles associated with the computer market levels (view 4, page 00). One would expect the evolution to continue along the lines shown in the following table for the next few years.

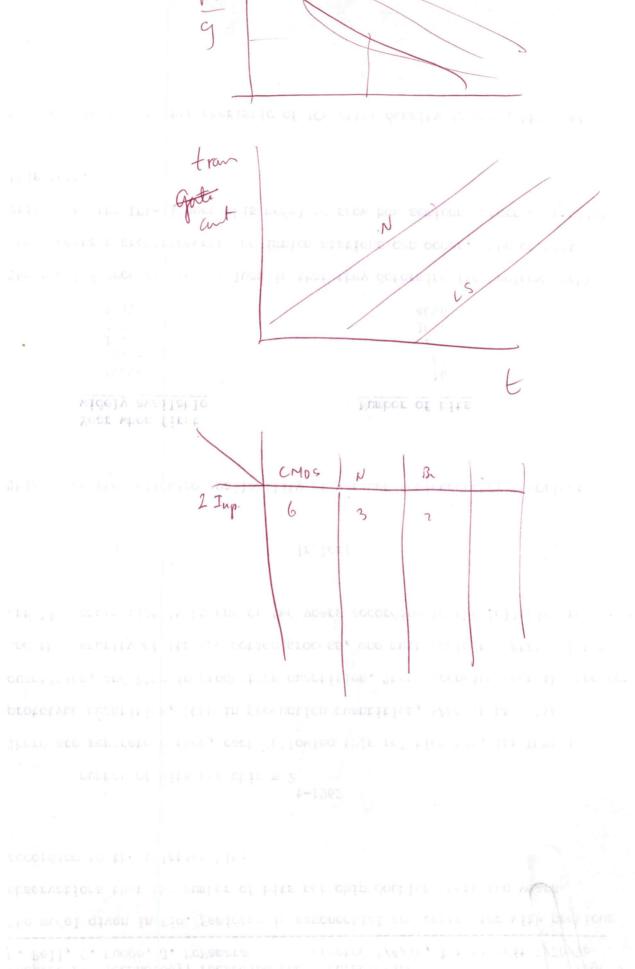

Table SemChar: Characteristics of Dominant (1978) Semiconductor Technologies

- IIC

| Type | Meaning                            | Evolution                      | Use (FIXTHS)                                                                    |

|------|------------------------------------|--------------------------------|---------------------------------------------------------------------------------|

| TTL  | Transistor-<br>Transistor<br>Logic | -<br>TTL/Schottky<br>TTL/LS    | logic, bus interfacing<br>high performance<br>low power, relatively same as TTL |

| ECL  | Emitter<br>Coupled<br>Logic        | MECL II, III<br>MECL 10K, 100K | original, very high performance delays of and ns.                               |

| MOS  | Metal-Oxide-<br>Semiconductor      | p-channel<br>n-channel         | for cost<br>for greater densities, cost<br>evolving to performance<br>(memory)  |

| CMOS | Complementary M                    | es)                            | for low power, speed,                                                           |

Chapter 2: Technology, Packaging and Manufacturing Page 12 created 1/4/78, latest edit 2/13/78 G. Bell have bee MOS noise immunity Note that we have omitted some of the lesser used technologies such I'L-for Integrated-Injection Logic and SOS-for Silicon on Saphire, which both promise yliam TTL higher speed and at lower power than MOS, and hence might displace its use. Both of these reclindlesies have been puted as reflacements Thus, if an entrenched technology has evolved for some time and continues to But evolve, it is difficult for alternative technologies to displace it because of rehnoldar the cummulative investment in process and understanding. This is clearly seen aule in the case of the numerous technologies that attempted to displace the core memory technologies during the 15 years it dominated primary memory use. (It lost because more effort was applied to MOS technology). We have also omitted the early predecessor technologies [RTL--for Resistor-Transistor Logic, TRL--for Transistor-Resistor Logic, and DTL--for acen mitted. and along Diode-Transistor Logic because they were sufficiently deficient in some aspect e corne of cost, performance, or reliability to avoid becoming standards of note. used in anne of Here, we should point out that these were the first ICs, and as such DEC did but many manufactures (including DEC) did not use them because they did not represent an advance (to us) over the 2 addeter discrete transistor circuits we used (e.g., the PDP-8). Similarly, these early circuits were packaged in a flat package, not the dual in-line package used today, hence machine insertion of components was not possible. and The table of parts, above, is weighted heavily to DECs use: TTL for mid- and high-sized minicomputers; ECL for the larger scale DECsystem 10; MOS for memories, microprocessors, and specialized high density circuits; and CMOS for the CMOS-8 (because it exists...not for either lower power or high noise

<sup>1</sup>Semiconductors appear to be characteristic of other technologies in that usually only a single technology is used for a given problem (use)--that is, each technology has a niche and there is only one winner!

G. Bell

created 1/4/78, latest edit 2/13/78

immunity reasons although they are nice).

Figure Speedpwr and Gatedelay give the two most useful measures of performance for the various technologies as they have evolved with time. The performance of circuit is also proportional to the power applied to operate at it. The 0 speed-power product metric for a technology at a given time is a more refined measure and indicates that the user may tradeoff performance against power. There are limits to Hat hadeoff becaunel However this is a bit misleading because unless special cooling is used, only unless special cooling is used, about one watt can be dissipated by an IC package, The first curve presents the speed-power product and was generated by Jerry Luecke of Texas Instruments (TI) at a time when I<sup>2</sup>L technology had just been introduced (Oct. 1975) by TI; some recent data points have been added for recent advances in MOS technology. Table Speedpwr gives some of the operating points for common processes at various times. Figure Gatedelay shows the gate delay through a single gate (logic) circuit and is the best performance measure because the implication of speed and power are interchangeable is erroneous. That is, one can neither operate at very high or very low densities subject to the package power dissipation constraints.

### Interconnections Outside the IC

The number of pins that communicate outside the circuit indicate the packaging technology level. Low and medium scale IC's often need more pins than LSI since the latter is capable of carrying out a complete function independentlyless -and hence can operate longer without interaction with the rest of the world. Memories are especially easily adapted to live with pin limitations since only

experientes have been

undtipliance }

Page 14

G. Bell

created 1/4/78, latest edit 2/13/78

1 pin is required for every factor of 2 increase in size (roughly every year). By time multiplexing the address signals, the requirements for address bits is can be

cheat he

further decreased.

# Reliability

Over the past 15 years, the failure rate for standard ICs has been reduced by two orders of magnitude to the neighborhood of .01% per 1000 hours. This corresponds to  $10^7$  hours mean time to failure (MTTF) per component. Figure Reliab, from a recent survey article by Hodges [1977] shows the trend. The lower curves show the higher reliability obtained when more extensive testing and screening as employed. The improved MTTF of between  $10^8$  and  $10^9$  is obtained at a cost increase of 4 to 100 times per component.

### Power Consumption

The tradeoff of performance and power for a given technology is implied by the speed power product described above. The package constrains power dissipation as previously described.

### EVOLUTION OF SEMICONDUCTOR USE

#### The LSI Dilemma

The economics of the LSI circuit industry make it essential that circuits with a high degree of universality be produced. Because of the learning curve of a manufacturing process (said to be X% per m circuits), cost is inversely proportional to volume. For a design to be sold in high volume, it must be Chapter 2: Technology, Packaging and Manufacturing Page 15 G. Bell created 1/4/78, latest edit 2/13/78

usable in a large number of applications. However, the trend in circuit complexity, which allows semiconductor manufacturers to put more transistors on a constant die area each year, lends to increasing specialization of function. The more specialized the function, the lower the potential volume and the higher the price. Figure generality shows the dilemma. The LSI product designer is therefore continually in search of universal primitives or building blocks. For a certain class of applications, e.g., controller applications the microprocessor is a fine primitive and has been so exploited [Noyce, 1977]. For some applications, circuit complexity can embrace even higher functionality at the PMS level. The Intel 8XXX is an interesting example here: two processors, a 2.5(?) microsecond byte-processor and a 200 nanosecond bit-processor are combined in one LSI circuit.

Moore [1976] discusses this dilemma in a paper on the role of the microprocessor in the evolution of microelectronic technology. He points out that a similar situation existed when i.c.'s were first introduced. Users were reluctant to relinquish the design prerogative they had when they built circuits from discrete components. It was not until substantial price reductions were made that the impasse was broken. Then the cost advantages were sufficient to force users to adopt circuits that fit the technology.

The difference, however, between the i.c. switching circuit level of RT-level building blocks on the one hand and the PMS-level block on the other is that the latter uses the powerful concept of a shared-program computer. Its function is varied by programming. For many applications, including most computer systems, the mircoprocessor on a chip is not a cost-effective building block, and other solutions to the dilemma are found. For example, microprogramming is a highly general way of generating control signals for data path elements, table lookup is a highly general technique. Both methods are attractive because they use memory, an inherently low cost LSI circuit.

Other techniques involve changing the pattern of interconnections via the top level(s) of metallization of an integrated circuit. This can be done by a factory made change or by the user, a much more flexible solution. Some of this customization is required in nearly all digital system design of the fourth and fifth generation. At the very minimum, the values for a read only memory have to be set. Table funvar contrasts the building blocks available in the fourth generation.

As a result of the increased basic circuit functionality available at each new generation, design methods have changed with the generations. This book provides an example of each, as summarized in the following table.

#### Table: Design Method versus Generation

| Design Method:\Generation:                                        | First | Second | Third | Fourth | Fifth | Examples<br>in this book |

|-------------------------------------------------------------------|-------|--------|-------|--------|-------|--------------------------|

| Combinational and sequential;<br>use of "standard" modules, IC's. | s     | S      | S     |        |       | 18-bit; PDP-8            |

| Read only memory and PLA;                                         |       |        | S     | m      |       | PDP-9; PDP-11            |

Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing rate to be 700 microwords per man year for horizontal micro machines. This tends to limit the maximum control store size to about 16 Kwords.

| Chapter 2: Technology, Packaging and                                                  | d Manufac | turing  |        |        | Page    | 17          |

|---------------------------------------------------------------------------------------|-----------|---------|--------|--------|---------|-------------|

| G. Bell                                                                               | created   | 1/4/78, | latest | t edit | 2/13/78 |             |

| Microprogramming with standard<br>RT elements (high perf.)<br>minor logical design    |           |         |        | S      | m       | CMU – 11    |

| Programming using micros<br>and logic for interfaces                                  |           | р       | p      | S      | x       | LSI-11      |

| PMS design using completely<br>specified and pre-designed<br>microcomputer components |           |         |        |        | S       | Cm* (almost |

| Customized chip design<br>and standard logical design<br>(high performance)           |           |         | m      | m      | m       | LSI-11      |

| s - the standard method for most dig:<br>m - done by manufacturers of basic eq        |           | ems     |        |        |         |             |

m - done by manufacturers of basic equipment

x - also used

p - prelude to micros, also done using minis

### Table funvar

| Building block       | Technique<br>for varying<br>function                   | Degree of<br>generality      | Permanence of<br>change             | - |

|----------------------|--------------------------------------------------------|------------------------------|-------------------------------------|---|

| Computer module      | program                                                | v. high                      | none                                |   |

| microprocessor       | program                                                | high                         | low to medium                       |   |

| bit slice            | microprogram                                           | medium                       | medium                              |   |

| ROM                  | factory mask<br>change                                 | v. high                      | irreversible                        |   |

| PROM<br>EAROM<br>PLA | field change<br>field change<br>factory mask<br>change | v. high<br>v. high<br>medium | irreversible<br>low<br>irreversible |   |

| FPLA                 | field change                                           | medium                       | irreversible                        |   |

| gate array           | factory mask<br>change                                 | medium                       | irreversible                        |   |

| RAM                  | write                                                  | v. high                      | none                                |   |

|                      |                                                        |                              |                                     |   |

The design of most relatively high speed digital systems (including low- to

\*Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing Chapter 2: Technology, Packaging and Manufacturing Page 18 G. Bell created 1/4/78, latest edit 2/13/78

mid-range minicomputers is carried out using standard register transfer ICs complete with data path and memory. Part IV discusses the current standard RT register transfer modules set; we would expect these bit-slice components to evolve and take on specialized functions in order to achieve both higher performance (e.g., a multiplier) and to be specialized to particular tasks (e.g., the interpretation of a particular computer's ISP). As an example, the series may be modified for the coding and encoding required in signal processing.

For higher performance computers, there is no alternative to using either tightly packed standard ICs or to build a particular set of ICs using some form of customization. Although Cray continues to build the high speed computers (in the CDC 6600, 7600 and Cray 1) with no custom logic, he does so by using impressively dense modules with high density interconnection and freon cooling. The high performance IBM and Amdahl machines are custom ECL circuits to improve packaging.

The current spectrum of IC's in use is summarized in Table cost speed spectrum.

With the advent of the processor on a chip, digital system design has or will be soon converted completely to computer design. The process of disolving a particular problem (e.g., control of a CRT, a lathe, or building a billing machine or word processing system) is just computer design system design as it has been practiced over the first three generations. The hardware part of the design is straightforward; i.e. the interface to the particular equipment (e.g., keyboard, lathe, printer), whereas the major part of the design is

"Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing

G. Bell

created 1/4/78, latest edit 2/13/78

programming in the same way that it has evolved since the late 40's. In fact, we have seen three comlete generations learn about this form of computer design, especially programming. The first generation discovered and wrote about it. We rediscovered and applied it to minicomputer systems. Now this time, it is being learned by everyone who must use and program the microcomputer. Each time (for each individual or organization) the story is about the same: people start off by programming (using binary, octal or hexadecimal codes) small tasks using no structure or method of synchronizing the various multiple processes; the interrupt mechanism is learned and the symbolic assembler is employed; and finally some more structured system--possibly an operating system is employed. Occasionally users move to higher level languages or macro assemblers but usually not because we (as engineers) are taught to minimize product cost (as opposed to development, life cycle, maintenance, etc. costs).

We believe the design of systems as ourrently practiced will be relatively short lived. The design method here will be at the PMS-level component. It is still too difficult to be done reliably and cheaply by large numbers of engineers. Even though by comparison with logical design and microprogramming, current digital systems design is straightforward and consists of building simple hardware interfaces to relatively poorly defined busses together with programming the application. Therefore, we believe that the components from which the microcomputer systems will be formed will be significantly more advanced using much better packaging, clearly defined busses, standard more general interface, and base level operating systems that are embedded in

<sup>\*</sup>Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing Chapter 2: Technology, Packaging and Manufacturing Page 20 G. Bell created 1/4/78, latest edit 2/13/78

hardware (i.e., placed in read only memory to give the feeling of permanency so that users are less likely to embark on the expensive, unreliable rediscovery path). Standard components will be built which can be interfaced to a wide range of external systems using parameters that are specified by a field programming method instead of using logical design and building with interconnection on modules. In this way, the complexity of individual ICs can be increased and thereby having a standard method for interconnection, higher volume and lower costs will result.

Before we discuss the alternatives associated with IC design, it is important to characterize the various costs. Figure Design.cost shows, at a crude level, what we might expect the relative design costs to be for various inter- and intra-IC design methods. Even the design cost is highly variable depending on the project size, its goals, manufacturing volumes expected and more importantly on the computer aided design programs.

The lowest cost designs stay completely away from modifying the ICs, except to bind programs to read only memories. If these use masked ROMs, the design costs are proportionally higher in order to both make the masks and to make corrections in the event that the ROMs are incorrect. (The manufacturing costs are lower for permanent ROMs.) At the RT level, the standard microprogramming design method is (conservatively) only twice as expensive per instruction as conventional programming, but likely on the order of 5 to 10 times as expensive to solve the same problem that a program written for a microprocessor solves (the speeds are at least a factor of 10 more too). Given that one must design

<sup>\*</sup>Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing Chapter 2: Technology, Packaging and Manufacturing Page 21 G. Bell created 1/4/78, latest edit 2/13/78

controllers with ROMs and PLAs, the cost can be still higher, but lower than with the standard sequential circuits we used in the first few generations--particularly if the module etch is used for the interconnection structure (see also comments about interface design for the 18-bit computers, page 00).

We make no attempt to quantify the manufacturing cost per function using the various design methods because the costs are too dependent on the quantities produced, the manufacturing technology (particular testing) and even how the functions are measured. We intuitively feel that the costs are relatively in the same order as the design costs, however, the cost per function is higher with SSI and declines with density. Doing intra-IC design should yield lower cost for all except standard programming and microprogramming because this method of design is identical to conventional logical design (of the first three generations) and we have come full circle! Therefore, if we postulate that design costs are higher and it is possible that the manufacturing costs are higher with custom design, then why would anyone design their own ICs?

# Design of ICs (Intra-IC Design)

There are numerous reasons why a designer is forced to design ICs. In some engineering environments where there are extremely small space, low power, or extremely high reliability requirements, the engineer is forced into building ICs, without attendant cost savings. Within DEC, however, unless there is a significant manufacturing cost advantage, we do not build an IC. Although the cost differential might be marginal, the performance gain for specially

\*Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing Chapter 2: Technology, Packaging and Manufacturing Page 22 G. Bell created 1/4/78, latest edit 2/13/78

designed ICs is often high. As we pointed out in Cray's computers, not designing ICs (permitting greater design flexibility, lower design costs and faster design turnaround) is simply a tradeoff with special high density packaging and freon cooling. Neither IBM nor Amdahl make this tradeoff, nor do their computers run as fast (but they do build many more computers, more cheaply). Therefore, the added complexity of ICs may be the only way that a high volume product at a given performance may be possible. The maintenance costs are important with higher volume complex designs since the reliability of a system is mostly a function of the man-made explicit connections (including the bond to the semiconductor die) and we can ignore the reliability of the IC die interconnection. Thus reliability is simply measured by counting discrete circuit pins, IC pins module and connector pins to determine the reliability.

To summarize, IC design is used along the same lines as we observe design styles: we build them for performance (for reliability too, because it may be the only way that a complex design can be maintained); we build them to get some decreased cost and higher performance (this permits mid-range designs to be more cost effective); and finally we build very high volume, lower performance computer components--i.e., microprocessors and microcomputers because it is the cheapest way to do a task. The secondary reasons to get size (and cost) reduction for some design occasionally enter in too. With greater semiconductor densities for the non-microcomputer components used to build more general digital systems, the increase in density is double edged--and may force specialization. That is, with these more complex components, there is a greater risk that as they become too large they will become less useful for

<sup>\*</sup>Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microcode. We have measured the writing

The various design methods we might use for various objects and densities are given in the following table.

Table: IC design method versus semiconductor density.

\ Density

IC Design\ VLSI MSI LSI SSI Method Minor variations | busses RT components Special interfaces -(e.g., UART) in standards ckts.(high perf.computers) Set useful for integrating a large possible alt, Gate arrays . .... to custom system (e.g., a computer) design = Small system relatively high Standard cells volume system Custom design | bus interface, high perf. memories, microcomputers (for high including peripherals signal convers. volume parts) |

Therefore, the most straightforward intra-IC design may well be the modification of an existing design. This has been used extensively by use to get the components for implementing computers. Failing, slight design

<sup>\*</sup>Microprogramming, however, does have limitations. The extra level of interpretation extracts a performance penalty and some potential datapath parallelation is often given up to reduce cost. A more subtle, but practical, limitation is the development cost of microsode. We have measured the writing

| Chapter 2: | Technology, | Packaging | and | Manufacturing   |        |      | Page    | 24 |

|------------|-------------|-----------|-----|-----------------|--------|------|---------|----|

| G. Bell    |             |           |     | created 1/4/78, | latest | edit | 2/13/78 |    |

modifications, we are left to the next most straightforward task, designing using arrays of gates and then interconnecting them to form the desired function. This is still desirable because there is only one circuit from which the gate is formed and the gate can be completely parameterized and defined so that interconnection is logic design that we understand. Also design occurs in a completely defined environment. Gates are interconnected to form more complex macro structures (e.g., various flip flop types, adders) and the design is carried out using the arrays of arrays.

It should be noted that this style of design, though never practiced at DEC was one of the extreme design philosophies advocated in the first few generations. Namely, there was a single module<sup>1</sup>, containing a set of gates, and all subsequent logical design was done in its terms (e.g., flip flops are constructed by interconnecting the gates). Note that a design predicated on a single module type simplifies the spare stocking and servicing aspects immensely, and it is possible to troubleshoot a problem by simply replacing circuits according to a pattern. At the other extreme of this design style is to make all modules different from one another and specialized to each task.

Gate array design uses a single well-understoood, well-defined component and the fabrication of all but the last few semiconductor processing steps is identical for all designs (the interconnection of the gates by metal is carried out last). However, there is lower density than more custom methods such as the standard cell (or more precisely, standard logical design element). Standard cell design is identical to the logical design of the first few

In the most recent Cray design there are only three IC types used: two are memory configurations and the third is a set of gates that are interconnected using the printed circuitry of the module and backplane. Thus, while only 3 IC types have to be stocked there is still a large number of module types, and servicing would hardly be done in the field by changing (unsoldering) ICs in the module. large number of circuit types and the set may not be defined well enough to be

reliable.

A representative gate array is a Raytheon RA-116. It has 300 Schottky TTL gates, of three configurations:

| 120 | internal | driver gates    | (3-input | NAND) |

|-----|----------|-----------------|----------|-------|

| 60  | external | driver gates    | (4-input | NAND) |

| 120 | internal | expansion gates | (7-input | NAND  |

|     |          |                 |          |       |

or

2-input OR expanders)

The gates have a typical propagation delay of 5-6 nanoseconds and dissipate 5.5-6 milliwatts per driver and 1 milliwatt per OR expander. Two metal layers are used for tailoring; there are 64 external pins.

Since the designer can arbitrarily interconnect, he constructs flip flops, adders, decoders, etc. Because the primitive is recent, data on package count reduction is scarce. One informal study we know of (for the Raytheon RP-16 aerospace computer) had a measured factor-of-three improvement.

| Chapter | 2: | Technology, | Packaging | and | Manufact | curing  |        |      | Pag     | e 26 |

|---------|----|-------------|-----------|-----|----------|---------|--------|------|---------|------|

| G. Bell |    |             |           |     | created  | 1/4/78, | latest | edit | 2/13/78 |      |

|         |    |             |           |     |          |         |        |      |         | 7    |

For higher speed applications an ECL gate array has been proposed. The ULG exploits the inherent properties of current mode logic to obtain a particularly flexible element (Gaskill et al., 1976].

The most common form of intra-IC design is custom design, although considering the designer, it is a variant of the standard cell since a particular designer has a set, even though he may not have enumerated all the design components a priori. With custom design the designer (theoretically) can specify a circuit for each use within a particular logical design. In this way, by observing that a particular gate or flip flop only drives a certain load, the circuit can be modified to carry out just the desired function in the context of its use. Therefore, with custom design, the whole circuit can theoretically be of optimum since each part is no larger than need by. The advantages are clearly size, cost and speed. The design costs are high because each part can, in principle, be customized. The goodness of the circuit is totally dependent on the single designer who must analyze each circuit geometry in terms of his expectation of performance, operating margins, etc. To the extent that this analysis is carried out, the circuit is clearly good. Design of this type rarely occured in the first few generations; i.e., both circuit and logical design are varied for the context.

Also on the graph is a hypothetical line for universal logic arrays. For at least 15 years, academicians have studied the possibility of designing a single array or arrays of arrays of logical design elements that can be interconnected on a custom basis to carry out a given function. The gate array can be looked

Chapter 2: Technology, Packaging and Manufacturing Page 27 G. Bell created 1/4/78, latest edit 2/13/78

at as the simplest example of this type design. While we are skeptical that such a line exists, we put it here as a target for those who search for the one truly universal logic array to aim at.

Both Read Only Memory (ROM) and Programmable Read Only Memory (PROM) are trivial forms of the truly universal arrays because they can be used in a table look up fashion to several functions of a number of input variables. For example, a 1,024 word ROM arranged in a 256 x 4-bit fashion can generate 4 independent functions of 8 variables. This is a distinct alternative for using a conventional gate structure to carry out combinational functions. Therefore we consider the ROM to be a common form of customization that nearly all users engage in.

However, a disadvantage of table look up implemented by ROM is that the required ROM size doubles for each additional input variable. The PLA is a combinational circuit which remedies this by allowing the use of product terms rather than completely decoding the input variables. Fig. PLA shows a typical circuit. It consists of separate AND and OR arrays; inputs are connected to the AND array, and outputs are drawn from the OR array. Each row in the PLA can implement an AND function of selected inputs or their complements, thus forming a boolean product term, and the OR array can combine the product terms to implement any boolean function.

A simple application is operation-code decoding. For the PDP-11, the 16-bit Instruction Register could be directly connected to a PLA, and the output

interpretation are usually needed: source mode decoding, destination mode decoding, and instruction decoding. Three PLAs could be used. A ROM version would require 64Kx8 for instruction decoding and 128x8 for address mode decoding.

With 2Kx8 ROM's this would require 33 packages as opposed to the 3 PLA packages. The 11/34 CPU uses a PLA in this fashion.

Microcomputers, e.g., the LSI-11 (Chapter ) commonly use the PLA technique for conserving the die area used by their control units.

The PLA becomes an even more fleasible building block when it is made field programmable -- the FPLA. The programmable connectors shown in Figure PLA are fusible nichrome links.

When a register is added to the outputs of the PLA, as with the Signetics 82SXXX, and incorporated in the same integrated circuit, a simple sequential machine is obtained in one package. This greatly increased the package count reduction potential of PLAS. Since register circuits are pin intensive, a factor-of-two package reduction occurs as soon as i.e. complexity allows the registers to be incorporated. The same reduction factor occurs when a ROM chip is augmented by a register.

The first PLAs had propagation times of the order of 150 nanosec [check with

Chapter 2: Technology, Packaging and Manufacturing Page 29 G. Bell created 1/4/78, latest edit 2/13/78

Spencer] and were thus suitable building blocks for slow, low-cost computers. Propagation times of 45 nanoseconds are quite common today, and the PLA is more widely used. A candidate application with these higher speed components is the replacement of the SSI and MSI packages used to implement the control logic for Unibus arbitration.

A more complex application than IR decoding has been documented in (Logue et al., 1975]. An IBM 7441 Buffered Terminal Control Unit was implemented using PLAs and compared with an SSI/MSI version. The PLA design included two sets of registers fed by the OR array: one set fed back to the AND array, and the other set held the PLA outputs. A factor-of-two reduction in printed circuit board count was obtained with the PLA version. The seven PLA's used in the design replaced 85% of the circuits in the SSI/MSI version. Of these circuits 48% were combinational logic, and 52% were sequential logic.

### MEMORY TECHNOLOGY (AND SEMICONDUCTORS USED AS MEMORIES)

In the preceding section we observed how core memory evolved and was challenged several times by alternative technologies and then finally overthrown in its use as the computer's primary memory. We also observed slightly unconventional semiconductor memory use for microprogramming and table look up in logical design. This section will not discuss these uses, but will present the various parameters and discuss the use of memory within a hierarchy to store information both on a short term basis while a program runs and on a longer term basis as permanent files. The slower speed electromechanical memories

| Chapter 2: | Technology, | Packaging | and | Manufact | turing  |        |      | Page    | 30 |

|------------|-------------|-----------|-----|----------|---------|--------|------|---------|----|

| G. Bell    |             |           |     | created  | 1/4/78, | latest | edit | 2/13/78 |    |

|            |             |           |     |          |         |        |      |         |    |

including drums, disks and tapes will be considered superficially, as their performance and price improvements have pushed the computer evolution.

### The Parameters Determining Use

We try to have a small number of parameters for memory because it is the simplest of components. Since memory prices have declined at a combined rate of 30% per year compound, (which amounts to over 50% in two years), all parameters are time variants. While the sole single metric is price/bit, it is mandatory to know the price (or size) of the total memory system because there is an economy of scale. In order to get the lowest price per bit, a user may be forced to a large system. (Is there econcomy of scale? What is the smallest or largest memory that can be built with the technology?)

Performance for electromechanical memories is expressed in two parameters: the number of bits that can be accessed per second after a transfer begins; and time to access the start of a block of memory. Since most all memories we're interested in here can be both read and written, the concern will not be on using write once or read only memory such as video disks.

The operational environmental parameters of power consumption, temperature, space and weight effect the utility. Finally, reliability measures are needed in order to see how much redundancy must be placed in the memory to operate at a given level of availability and likelihood of losing information.

In summary, the relevant parameters for a given memory are:

| Chapter 2 | 2: | Technology, | Packaging | and | Manufacturing            | Page 31     |

|-----------|----|-------------|-----------|-----|--------------------------|-------------|

| G. Bell   |    |             |           |     | created 1/4/78, latest e | dit 2/13/78 |

|           |    |             |           |     |                          |             |

the time the observation is made together with a time history in order to deduce the location of the technology in its lifetime;

2. price per bit; and

3. total memory size or total memory price;

4. performance has two components:

a. the access time to the first word of the block

b. the time to transfer each word (data-rate) in the block

5. operational power, temperature, space, weight

reliability and repairability in order to compute availability and the maximum

For this discussion we will consider only the first four parameters (and often omit no. 3.). In the solely core and semiconductor memories 4b is omited, whereas for electromechanical memory (e.g., disk, tape) the performance is usually determined by 4b (and 4a can be omitted).

Before we observe how the use of memories has affected the evolution, it is important to posit the various technology models as a basis of the past and navigational aids to the future. Figure Memprice gives the expected price of semiconductor memory. Namely, these memories decline in price every two years Chapter 2: Technology, Packaging and Manufacturing Page 32 G. Bell created 1/4/78, latest edit 2/13/78

by a factor of two and the decline is expected to continue well into the 80's based on continued increases of semiconductor densities. Figure Memsizeperf, a graph by Dean Toome, vice president of engineering for Texas Instruments, shows memory size and performance improvements with time and includes the slower perform cyclically accessed Charged Coupled Devices (CCDs) and magnetic bubbles.

While these two graphs allow the processor, primary memory, cache and small paging memories to be understood, we need a model for disk and tape memory in order to complete the memory hierarchy. (I'd like graphs here of:

. Price/byte for 1 platter, 4 platters, 10 platters

. Price per disk for 1 platter, 4 platters, 10 platters

. Tape units at each speed 12/45/75/125/200

. Tape density and transfer rate vs time for each speed

. Price/byte of small systems: DECtape, floppy, cassettes

# Computational Locality and Memory Hierarchies

All information processing systems (computations) appear to be associated with relatively local memory use; as time passes, the location of the computation changes, but still the amount and the location of memory involved in a Chapter 2: Technology, Packaging and Manufacturing Page 33 G. Bell created 1/4/78, latest edit 2/13/78

computation over a relatively long time, is comparatively small.

This phenomenon has been observed to apply to a number of activities within a computer system, and in each case the principle of operation appears to be the same. Thus, armed with the observation, a new memory--providing proportionally more memory for less, should be useful if it is:

cheaper and slower than an existing memory; or it is faster and more expensive (implying that it is smaller).

Of course, any memory that is better in all dimensions of speed, size and cost automatically replaces an existing memory.

Transparency is another consideration about the utility of a given physical memory within a hierarchy that effects use. Namely, does the program(mer) know or have to consider the memory in his use. If we observe the machine at the languge level, then nearly all memory technologies are transparent. For example, the original FORTRAN had explicit statements to read and write tapes where the modern counterpart has operations to access files in different access arrangements; hence, these operational improvements are not quite transparent. However, whether a processor has no, 1 or 16 accumulators is irrelevant to the FORTRAN programmer.

The following table gives the memory hierarchy as currently known. There is a continuum based on need together with memory technology size, cost and

Page 34

G. Bell

created 1/4/78, latest edit 2/13/78

performance parameters.

Table: Computer System Memory Component and Technology

| Part                                    | Transparency<br>(to machine language<br>programs) | Based-on                                                                                                     |

|-----------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Microprogram memory                     | yes <sup>1</sup>                                  | very fast                                                                                                    |

| Processor-state                         | no                                                | very small, very fast<br>register set (e.g.,<br>16 words)                                                    |

| Alternative processor-<br>state context | yes                                               | same (so speed up<br>processor context<br>swaps)                                                             |

| Cache memory                            | yes                                               | fast. used in larger<br>machines for speed                                                                   |

| Program mapping and segmentation        | yes                                               | small number of<br>association, or<br>large map                                                              |

| Primary (program) memory                | no                                                | relatively fast, and<br>large depending on<br>Pc speed                                                       |

| Paging memory                           | yes                                               | can be electromechanical<br>e.g.,drum, fixed head<br>disk, or moving head<br>disk. Can be CCD or<br>bubbles. |

| Local file memory                       | no                                                | usually moving head<br>disk, relatively slow,<br>low cost                                                    |

| Archival files memory                   | yes<br>(preferably)                               | very slow, very cheap<br>to permit information<br>to be kept forever                                         |

book. To begin, microprogrammed memories are normally transparent to the

Chapter 2: Technology, Packaging and Manufacturing Page 36 G. Bell created 1/4/78, latest edit 2/13/78

general registers in an explicit (transparent) fashion, or whether the stack architecture should be used (also requiring a number of registers), but the use is transparent to the programmer. We adopted the general register structure to give better program control of a small number of local variables (i.e., locality) and permit the performance advantages. The change in register use can be observed between the 12-bit and 18-bit designs and the later DECsystem 10 and PDP-11 designs.

As the number of registers increased, and technology improved the processor state was increased to have multiple sets of registers to improve process context switching time. In this way several multiple programs could be active at a time and selected on the basis of interrupt urgency to provide better real time and multiprogramming response.

In the late 60s the cache memory was introduced for large scale computers. This concept was applied to the KL10 and 11/70 in 1975 when the relatively large, (1 Kbit) relatively fast (factor of 5) memory chip IC was introduced. The cache is discussed extensively in chapters 00, 00 and 00. It derives much power by the fact that it is an automatic mechanism and hence transparent to the user. It is the best example of the use of the principle of memory locality.

A similar memory circuit is required to manage (map) multiprogrammed systems by providing relocation and protection among various user programs. The requirements are similar to the cache and may be incorporated in the caching Chapter 2: Technology, Packaging and Manufacturing Page 37 G. Bell created 1/4/78, latest edit 2/13/78

structure. The KI 10 used an associative memory for this mapping function.

The use of semiconductors for the primary memory, replacing core memory is legendary. Section 00 discusses this evolution and tradeoff.

The Atlas computer (Kilburn et al 1962) was designed to have a single, one level large memory and paging drum. This structure ultimately evolved so that multiple users could each have a large virtual address and virtual machine. However, the concept of paging mechanism works because there is not equally random access to each page, but rather only local access to various parts of a program by the processor at a given time. Denning pointed out the clustering of pages for a given program at a given time and called this phenomenon the working set [19]. For most programs the number of pages accessed locally is small compared with the total program size. Initially a magnetic drum was used to implement the paging memory, but as disk technology began to dominate the drum both fixed head and moving head disks (backed up with larger primary memories) were used as the paging memories. In the next few years, the relatively faster and cheaper CCD semiconductor memories and bubble memories are clearly the candidates for paging memories.

For medium sized to large scale systems there is no alternative to disks, with archival files on magnetic tape. Thus files can be stored cheaply on an indefinite basis. For smaller systems there must be less numbers of technologies due to high overhead of a level. At most, two levels would probably exist as separate entities. Chapter 2: Technology, Packaging and Manufacturing Page 38 G. Bell created 1/4/78, latest edit 2/13/78

Alternatively we would expect a combination of floppy disk, low cost tape and magnetic bubbles to be used to reduce the primary memory size and at the same time provide file and archival memory. Currently the floppy disk operates as a single level memory. Here we can see two alternatives for technology tradeoff using the hierarchy: a tape or floppy disk can be used to provide removability, and archivability, whereas bubbles provide the performance.

### MEASURING (AND CREATING) TECHNOLOGY PROGRESS

The previous sections have presented technology in terms of exponentially decreasing prices and/or exponentially increasing performance. Here we present a basis for this constant change. The metric of technology, T(t) at some time, t, has been classically observed to be just:

$$T(t) = K x e^{ct}$$

This can be converted to a yearly improvement rate, r, by changing the base of the exponential to:

$$T(t) = T x r^{t-to}$$

where T = the base technology at to

r = yearly increase (or decrease) in the technology metric

This is the same form we have used for declining (or increasing) cost from base

Chapter 2: Technology, Packaging and ManufacturingPage 39G. Bellcreated 1/4/78, latest edit 2/13/78

С

$C = c \times r^{t-to}$

The questions that may arise as we observe the previous graphs (i.e., semiconductor prices) are:

1. Under what conditions does cost decrease exponentially?

2. Under what conditions does technology improve (i.e., in performance) exponentially?

3. When does a technology reach a limit of improvement?

Clearly there are manufactured goods that neither improve nor decrease in price exponentially, although many presumably could with the proper design and manufacturing tooling investments. The notion of price decline is completely tied to cumulative learning curves both by people building a product for a long time, to process improvement based on learning to build it better and learning by engineers based on history of design. Production learning per se is inadequate to drive cost and prices down because after an extremely long time in production, a few more units contribute little to learning. With inflation in labor costs, then costs actually when the learning is flat. In order to provide us with a base for predicting the inflationary effect, the consumer price index has been plotted Figs. CPI and CPI.log.

| Chapter 2 | 2: Tecl | hnology, | Packag  | ging  | and | Manufact | turing  |          |      |      | Page | 40 |

|-----------|---------|----------|---------|-------|-----|----------|---------|----------|------|------|------|----|

| G. Bell   |         |          |         |       |     | created  | 1/4/78, | latest   | edit | 2/13 | 8/78 |    |

|           |         |          |         |       |     |          |         |          |      |      |      |    |

| Learning  | curves  | don't a  | ppear t | to be | und | derstood | beyond  | intuitio | on.  | They | are  |    |

(empirical) observations that the amount of human energy, En, required to produce the n<sup>th</sup> item is:

$En = K \times n^d$

where K and d are "learning constants". Thus, by producing more items, the repetitive nature of a task causes learning and hence the time and perhaps cost to produce an item decreases with the number produced and not with the calendar time an object is produced. Fusfeld [ ] furthermore conjectures that the technology of the i<sup>th</sup> unit produced also improves exponentially with the number produced just as in the case of the learning curves. Thus, using the technology measure:

Ti = a x i<sup>b</sup>

he found the following technology progress constants:

| Item                                               | Measure, Ti                                              | Quantity<br>produced(i)                                                     | Technology<br>progress(b)                  | Change<br>observed in<br>study | Total<br>change                             |

|----------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------|--------------------------------|---------------------------------------------|

| light bulbs<br>automobiles<br>titanium<br>aircraft | lumens/bulb<br>vehicle h.p.<br>p.s.i./\$/16<br>max.speed | $10^{10}$<br>$3 \times 10^7$ ; $10^8$<br>$3 \times 10^5$<br>$2 \times 10^5$ | .04;.19<br>.11;.74<br>.3;1;1.04<br>.33-1.2 | 33<br>10<br>10<br>6            | 80<br>6;13<br>350<br>56                     |

| turbojet<br>engines<br>computers                   | fuel consumed<br>weight<br>mem.size x<br>rate            | $1.6 \times 10^4$<br>10 <sup>5</sup>                                        | 1.06<br>2.51                               | 2<br>10 <sup>9</sup>           | $2.9 \times 10^{4}$<br>$3.5 \times 10^{12}$ |

Here we note that computer technology (till 197?) evolved substantially more

information nearly all of which are electronic based. In the above technologies, most are mechanically oriented with the associated physical limits. In essence we are comparing systems constrained by Newton's Laws with those determined by Maxwell's Equations.

Fusfeld also showed that provided the number of items produced increases exponentially (with time):

$i = e^{c/b \times t}$ .

then calendar time and units produced can be used interchangeably.

Since there has been exponential growth of computer systems, calendar time can be used instead of units. Time is an easier and more accurate method to measure than learning curves based on units.

The question of why the cost declines exponentially can be conjectured by using Fusfeld's observation that it is because of learning curves and the exponential increase in quantity produced. Furthermore, this exponential increase raises a fourth question;

4. Why is the demand exponential?

Chapter 2: Technology, Packaging and Manufacturing Page 42 G. Bell created 1/4/78, latest edit 2/13/78 ------The demand or quantity, q, sold per unit time is completely elastic,

(exponential), according to the expression:

#### q = k/price

This creates a positive feedback market system whereby decreasing prices increase demand exponentially causing decreased costs (through learning) which support the decreasing prices as shown in Fig. Mkt.cycle (a variant of Fig. 1.).

There has been no attempt to answer question 2 of why technology improves exponentially nor is the answer for why cost declines exponentially at all satisfactory. Simple production learning does not account for the rapid technology changes in integrated circuit for example where totally different production processes have been evolved to support the greater technology. It appears best to simply observe that the three situations <u>have been</u> true, and can be extrapolated to hold over the next few years because we can see ways by which each limit can be overcome.

Technology historians (von Hippel, 197?, and Fusfeld 197?) and futurists have made a number of studies and observations about technology progress:

Quantity produced is simply a good dummy variable to measure improvement.

(With exponential increasing sales, we can use time as the dummy variable.)

| Chapter | 2: | Technology, | Packaging and | Manufacturing          | Page 43      |

|---------|----|-------------|---------------|------------------------|--------------|

| G. Bell |    |             |               | created 1/4/78, latest | edit 2/13/78 |

|         |    |             |               |                        |              |

- 2. Technical problem solving is correlated with business activity. Inventors tend to be stimulated by sales and slacken efforts when sales are low. (This is a counter-initiative observation.)

- 3. Production alone does not stimulate innovation. A lesser number of inventions are stimulated by production needs. Of these, the same user-supplier relationship is the best framework. The users of equipment (the producer for the end product) stimulate the production equipment suppliers.

- 4. Major innovations come from use (sales). This is opposed to innovation arising from a technical possibility for which use is subsequently discovered. In the case of semiconductor technology, the computer designer (user) is responsible for many of the design innovation. Computers also evolve rapidly under this and the levels of integration model because the suppliers are also significant users. The problem of market coupling is diminished significantly. Alternatively with computers, the users write (develop) the applications programs; hence again the user and developer are one in the same--this stimulates use!

The gains in packaging (i.e., printed circuit boards, backplanes, and cables) have been driven by production, versus product functional needs. Testing technology of all types has been motivated solely for production needs. These change least.

Page 44

G. Bell

created 1/4/78, latest edit 2/13/78

The cost of computing is the sum of costs which correspond to the various levels of integration we described in view 4, page 00 plus the operational costs. In actual practice, each layer, or additional level-of-integration is often looked at as overhead. Using standard accounting practice, the basic hardware cost, at the inner layer, is then multiplied by an overhead factor at each subsequent outer level. While this may in principle work operationally, for a stable set of technologies it is hard to condone and we will describe the constituent technologies and resulting structures at the next level together with operational cost models. An overhead-based model will not adequately allow for rapidly evolving technologies or the elimination of levels, for example. By examining each part, as we have tried to do in this section on technology and in the packaging section, we can then make observations about the use and substitution of technology. More importantly, we can draw conclusions about how structures are likely to evolve.

Semiconductor technology is singled out as the main determinant of a computer's cost, performance, reliability and memory size. Magnetic storage technology is of equal importance because disks and tapes memory densities evolve rapidly, even though the cost of a given physical unit does not. These components become an increasing major component of the system price.

# Cost, Performance and Size (Economy of Scale) Relationships Design

We often simplify the understanding of technology to just cost as the only dependent performance parameter. This simplification omits the most Chapter 2: Technology, Packaging and Manufacturing Page 45 G. Bell created 1/4/78, latest edit 2/13/78

significant parameter, calendar time. In a similar way, we often fail to understand whether there is any associated economy of scale when considering the performance (utility) of a given set of devices. That is, do larger units perform significantly better than a set of small units when taken either independently or as a collection? Therefore, a more correct assessment, taking into account economy of scale, and performance, would be:

performance =  $k \times costs \times r^t$

where

k = base case performance

s = economy of scale coefficient

r = rate of improvement of technology

t = calendar time

For many of the technologies in which we're interested, a second dependent parameter, size, is important because it is a measure of utility. It can, with a tradeoff, be a measure of performance but often the two must be taken as independent resources. For example, a certain memory size would permit a certain number of accesses. For some applications, we would ask whether the size were adequate and for other applications we ask whether there is adequate time to access the data. Thus the systems performance in such an example is bottlenecked by either size or access and is the minimum of one of the resources. That is:

system performance = k x min(memory-size, memory performance)

1. Economy of scale holds. A particular object can be implemented at any price, and the performance varies exponentially with price. performance = k x price<sup>S</sup>; s>1

2. Linear price performance relationship.

performance = k x price

3. Constant performance, no matter how much is spent. performance = k

4. & 5. Only a particular device has been implemented. The performance (or size) is a linear sum of such devices. performance = n x (k x price)

Economy of scale holds where it might not otherwise operate because of several effects in the design and product introducion strategy. Because a product is already high priced, adding slightly more cost may have a proportionally higher effect on performance than for lower cost products where the same constant cost addition may be needed. This is akin to the design styles, page 00. This condition is especially true in disks and computer systems. A technique (e.g., a particular recording method employing costly logic for encoding/decoding, the cache memory) is employed at the high priced system first. For example, the cache memory is nearly constant cost, independent of the size machine it is Chapter 2: Technology, Packaging and Manufacturing Page 47 G. Bell created 1/4/78, latest edit 2/13/78

used on. With time, and learning, the technique can then be applied to lower cost (e.g., the 360/85 in 1968 and the 11/70 in 1975) systems.

In Fig. Costvstime, we see what typically happens as the cost of the lowest price unit is kept to a minimum and decreasing whereas the mid range product continues to increase, and the highest performance product increases the most, because it can afford the overhead costs. If we look at the basic technology metric, then there are really three curves too as shown in Fig. Techvstime. The first curve is applied to get the greatest improvement and be applied to the large price unit. With time the technology evolves and is reapplied to the first level copy in the middle range products (to most likely provide the best cost performance) and finally, several years later the technique becomes commonplace and is applied on low cost products. The resultant cost/performance ratios are shown in Fig. Cost/tech.