## Oral History of Robert Garner, part 1 of 2

Interviewed by: Roy Ogus

Recorded December 6, 2018 Mountain View, CA

Edited by Roy Ogus, March 2021 Edited by Robert Garner, January 2024

CHM Reference number: X8869.2019

© 2018 Computer History Museum

**Ogus:** Hello. I'm Roy Ogus, and today is December 6<sup>th</sup>, 2018. I'm here at the Computer History Museum in Mountain View, California, with Robert Garner, who has graciously agreed to be interviewed for an oral history.

I've known Robert for many years. We first met around 1977, when Robert participated in a Digital Design class that I was teaching at Stanford, University, while I was involved with my post-doc research. Following that period, Robert and I have worked together on several product development activities at both Xerox and at Sun Microsystems.

We worked together as designers in the Xerox team in Palo Alto that developed the Dandelion workstation, which, of course, later became the platform for the seminal Xerox Star workstation product. Then a few years later, and actually by coincidence, we worked together again as part of the joint Xerox-Sun Microsystems SunDragon team that developed the Sun SPARCstation products. We'll hear a lot more about these activities in detail during this interview.

So Robert, we've had a long history together, and I'm delighted to be talking to you today about your story. Thanks so much for joining us. We really appreciate it.

**Garner:** Well, Roy, before you start your first question, I want to say I did work for you for a short-time, as you were my manager, and you were actually the best manager I've had --

**Ogus:** That's right. You were actually my manager as well, yes.

Garner: Well, could've flipped, but you were actually the best manager I've had, so...

Ogus: Okay, thank you.

Garner: And so that was--

**Ogus:** That's right. The first part of the Xerox thing.

**Garner:** Yes, and thank you for agreeing to do my oral history.

**Ogus:** Okay. My pleasure. All right. So why don't we start at the beginning? Can you tell me where you were born and when, and where you grew up? At the same time, why don't you also tell us what your parents did and how they influenced your various career decisions?

Garner: Yes. Well, those are all the easy questions.

Ogus: Yes, we start with--

**Garner:** So yes. So I was – I'm a native Californian, actually. I was born on the vernal equinox, 1954. That's when the day is half light and half dark. My parents lived in the Manhattan Beach area in L.A. When I was about one year old, I ran away to Arizona. What really happened is that the companies on the west coast were being encouraged to

expand inland because of the threat during World War II of invasion from Japan. So the company that my father worked for decided to move inland to Arizona.

My father, he grew up with a lot of responsibility early on. I think he taught that to me. When he was a young kid in high school he used to drive all the kids in the high school bus to the high school in Hollister. He would drive down Highway 25, drop them all off, stay at someone's house by candlelight, do homework. Next morning pick them all up one by one as a freshman in high school before he could even have a driver's license and drive all the kids into school.

He wanted to become an aeronautical engineer. His goal in school was to find a crashed airplane, because you couldn't afford to buy one, and to restore it, and to get it to fly again. He ended up joining AiResearch -- next to the Sky Harbor Airport in Phoenix, and worked on gas turbines his career. He kept all his college textbooks and so I ended up devouring his physics textbook. I just loved all the stuff I saw there.

Where I grew up, first in downtown Phoenix, and it was orange groves and being converted into housing divisions, we used to build, make things: Build tree forts. I would make all kinds of contraptions. I was known for building things. As a young kid, I would find strange things, like algebra papers thrown out of cars, and I was totally fascinated by those. Camera lenses in the field, all kinds of crazy things. I even later learned that Spielberg lived in my neighborhood, so it's even possible that I played with him as a young boy, and we certainly went to the same restaurant that he made his first movies in.

Starting somewhere in grade school, we formed-- two, of my best friends and I formed a science club and we met every weekend. We did crazy things: We built 3D chess sets. We built tube-based amplifiers. We did mathematics and calculus. We found adults who had access to computers. So we started writing small programs in seventh grade, sixth and seventh grade. I wrote a Tic-Tac-Toe program. You would kind of hand the program over to some adult and they would go find a computer somewhere to run it for you.

So the two close friends of mine were Jerry Jenkins and Chris Beall. Chris was a brilliant person who, I'll never forget, he wanted to check out a college physics book but they wouldn't let him because they thought he was too young and he was trying to design a particle accelerator. My friend Jerry Jenkins was a brilliant mathematician.

We had access to a terminal system at the high school first that did timesharing to a Scientific Data System, SDS Sigma, Sigma 9 computer or Sigma 7, located at a service bureau in downtown Phoenix called Transdata. That's where I learned that if you actually go to the computer center at night you can get full access to the computer. And it runs faster at night. They let us run the whole Sigma machine ourselves, like at 1:00 A.M. or 2:00 A.M. Quite a fun thing to do. Also, we found that if you searched the wastepaper baskets you found user IDs and passwords, <laughs> so we could get extra free time on the computer and get privileged accounts, because then people didn't realize they shouldn't be typing out user passwords.

Back to my father, I guess, a little bit. He loved the outdoors and we did some hunting and he was very observational. He could see animals before I could, and so he really taught me the skill of being the careful observer and watching things. I was really into botany and natural history. I would devour magazines like Science News but I couldn't figure out how people got their ideas. So I figured, well, maybe you had to study things, so I would take pictures of

landscapes to see how they might change over time. My dad would take me deer hunting. I later realized that wasn't a great thing to be doing. He had a playful, wry sense of humor. We'd go on car camping trips. We visited Lowell Observatory. Arizona has all these observatories -- islands in the sky observatories -- and I'll never forget being impressed by seeing Percival Lowell's hand drawings of the canals on Mars. Lowell so projected into what he was seeing through his refractor telescope that he thought he saw canals. But seeing those original documents really moved me into exploring science and the history of science.

Also, in seventh grade, I got a little carried away. My social studies project ended up being 700 pages of a history of the Conquistadors and the Spanish of the Southwest. I was the school class president in eighth grade and gave the graduation class speech. Oh, I almost forgot. In third and fourth grade with my friend Chris, we were school crossing guards, which is a very responsible position. In seventh and eighth grade I had the responsibility of lowering and raising the American flag on campus. So I had these very kind of responsible things to do.

But that was the time of the Vietnam War and a lot of protests against what was going on. I tended to kind of hang out with the more, with the people saying, "Let's end this war and stop this craziness." So I had kind of an anti-large-establishment mindset, more of the hippie mindset, you could say. So I wasn't really interested in business, but I was more interested in science and technology.

Oh, last thing on my father is that we, well, at that time, I guess, I also joined the Boy Scouts. We went on a lot of backpacking trips in the desert and the mountains in Arizona. I eventually became an Eagle Scout. On the way you do things like Order of the Arrow where they do unusual things like you don't speak for entire day, learning first hand what's it like to go through an entire day without talking. One of the things that came from joining the Boy Scouts was that I attended the International World Jamboree in 1972, which was held in Japan, at the base of Mount Fuji. You could just walk a hundred yards and be with another group of people from somewhere else around the world, which also strengthened my interests.

I had, I guess, something else I hadn't mentioned, is that at the time, Heathkits were very popular -- the electronic kits where you would build things. So I hand-assembled my family's color TV from a Heathkit. Through following the instructions, I hand-assembled a shortwave radio, and you could listen to broadcasts from around the world, late into the night. You could listen to programs from Russia, Cuba, South Africa, and elsewhere. My father and I actually continued our backpacking tradition as I became an adult, and we used to go backpacking into the canyon country of Utah and Arizona and New Mexico. So I was very close to my father.

My mother was raised on a small farm in West Virginia, and she was very caring and inquisitive and believed in science. She really believed in science, and she used to, when she would go shopping, to show you how geeky I was, she would drop me off at the library, which I just loved, and I would spend all day at the library reading books on relativity by Einstein, and math and all these physics things and I was just in heaven.

I just loved the libraries in the Phoenix area. I, as a student in high school, I used to go to the Arizona State Library and hang out in the stacks late at night, and that's where I got acquainted with books on computer design. I guess I did the usual science fair projects. I explored the electrical activity of fish using an oscilloscope. You saw kids doing little, simple computers as science fair projects, but I found them to be too simplistic: If you have access to a real computer, why bother building something which isn't very powerful?

Later we moved to the north Scottsdale desert. This would've been about when I was in sixth grade, and there we lived in the desert but within a golf course, and so that's where I got into running. It was a very meditative thing. I would run the fairways at night through the sprinklers when it's over a hundred degrees outside and jump into the pool. I was a lifeguard at that pool, participated in swim meets, and it was a great -- a great balance between exploring the creatures of the desert -- I had snakes. I used to collect snakes. We had snakes in the house. Terrified my parents when they escaped from their cages and my father would see a snake slithering down the hallway in the middle of the night. <laughs> So I had a very strong interest in the outdoors and natural history.

**Ogus:** Maybe I could just ask a question here. It seems like many of your activities were technically oriented. I mean, your father was in the technical field.

Garner: Yes.

**Ogus:** But you also did a number of other activities that were not technical related. But somehow you kind of moved towards a technical career, and, in fact, you told me that your father actually made/moved you, from doing a natural history type of university education to an engineering one.

Garner: Yes, yes.

**Ogus:** So do you really understand how your interest in getting into the computer field evolved? Was it just innate or was it [as a result of] your influences while you were growing up?

**Garner:** Well, I think it was the -- I was interested in electronics, and I think it was the access to the computers, early access to computers via adults. I think at a very early age I realized that computers could be used to control almost anything mechanical in the world and I, so I -- it was a hobby, designing electronic things. I consumed every issue of Popular Electronics. Never forgot the Altair cover, but my allowance didn't allow me to purchase the kit.

So it was-- and I took Russian as well. Russia was dominating the news, Sputnik and all the spacecraft. It was thought to be important to learn Russian, so I took Russian in high school, and I visited Russia in a foreign language exchange program during the height of the Cold War. In fact, I was in the US consulate, in then Leningrad, the day of the American Bicentennial. It was quite an experience. One thing I remember about Russia is that they really promoted science and technology, so as a geek it was kind of fun. I remember going to a science exhibit featuring rockets, Soyuz and the cosmonauts. There was also a computer that looked a lot like an IBM-360. I later learned that Russia cloned 360s almost exactly. One thing that really helped with computing was that I took a typing class as in grade school, and so therefore a teletype terminal was not intimidating. Many people in the computer business never learned to type, but by taking a typing class first, that made that less intimidating. So that so...

**Ogus:** Was it really true that you were thinking of doing a natural history track?

Garner: Yes.

Ogus: We will get into college next, but--

**Garner:** Well, even before I get to college, one of the other projects I did is I built a -- the Scientific American magazine had an Amateur Scientist section that I consumed every month. One month I decided to build one of the projects, which was a mass spectrometer. I linked up with a physics professor at Arizona State who helped me build it. He called it the best plumbing system in the world, because you have to have a vacuum in them and was a very simple mass spectrometer, but that was lot of fun.

In high school I used to borrow the physics teacher's Geiger counter and I would inject radionuclides in plants. You could actually get samples of radionuclides over the mail by subscribing to free U.S. government publications, since I couldn't afford them. I would inject them into plants to see how they might travel.

Oh, the other thing that happened in high school that really led me to computers was that GE had a recycling center in South Phoenix near the airport [now Apache Electronics], where they would send all their defunct computers, maybe just one or two years old, and tear them apart. These giant mainframe computers, GE 225s or whatever. They would chop off the ends of the printed circuit cards for the gold and sell the disk platters as coffee tabletops. And then they would take all the discrete components and offer them to hobbyists. So we would go visit the GE recycling -- so that probably was my earliest interest in old computers as well, because, "How could they be chopping up old giants into pieces and selling them as coffee tabletops, the disk drives, four-feet diameter disk platters?" I never had enough money to buy one. There were also other old collectible places in town that had that kind of stuff.

I was also very much interested in math, and I remember in high school I was really fascinated by Gödel's Incompleteness Theorem and math philosophy. But I really did, like you say, I really wasn't sure whether to go into natural history or engineering, and my father said: "Well, you'll get paid a lot more doing engineering," and that led me to pursue that. So I went to Arizona State University (ASU). My friend Jerry Jenkins had already started there. At Arizona State you had to -- I wanted to get a B.S. in Electrical Engineering, but they had a B.S. in Engineering degree, so you had, EE would be a specialty, so they made you take a well-rounded engineering curriculum, which --

Ogus: This was 1972.

**Garner:** 1972. Yes, when I started at ASU. I didn't like the fact I had to take mechanical engineering classes necessarily, but it really helped me later in systems design understanding things like fluid and heat transfer. I had two jobs as an undergrad. I found that taking undergraduate classes, especially from perhaps not all inspiring teachers, was a grind. What really helped me get through college as an undergraduate was those two jobs, one for a math professor, Dr. Gregory Nielson, and the other for an experimental psychologist, Dr. Barry Leshowitz.

**Ogus:** So these were during the term time, they weren't like a summer job?

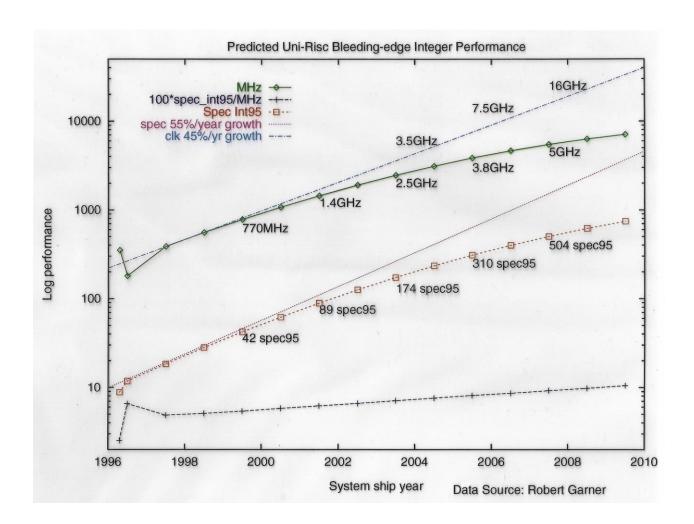

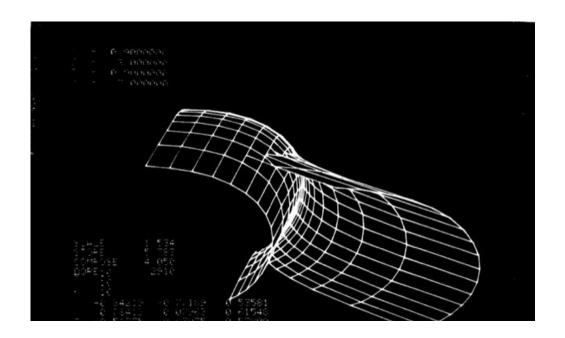

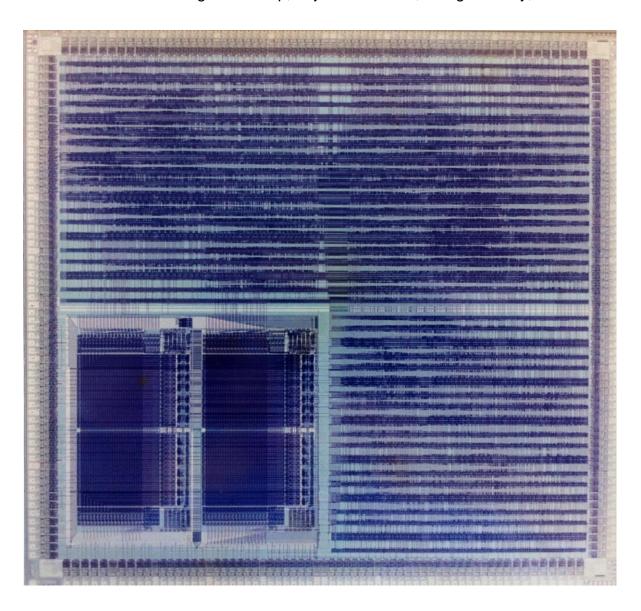

**Garner:** They were during the normal academic year. Dr. Nielson had an office in the Math Department with a Tektronix 4010 storage terminal. As part of his research into splines, he spearheaded one of the early 3D surface drawing programs based on parameterized equations as a function of two parameters, *u* and *v*. We ran the software on a PDP-10, located at a timesharing service over a 300-baud modem line. In would come the coordinates for the 3D surface which would show up on the storage tube. I hand-tuned some of the algorithms in assembly language [and wrote a simple hidden line removal algorithm. [Appendix Image 1-A shows two SURV surfaces on the Tektronix 4010 display]. I learned PDP-10 assembly language at that time. Most of our software was written in FORTRAN.

I also did a special project for Greg. He realized that we could take the 300-baud modem data stream coming in over the phone line, record it on a reel-to-reel tape recorder at the slow speed and then play it back at a higher speed and get a 4x faster rendering speed. I built a little box that converted the modem levels to levels appropriate for a magnetic tape recorder. It was a lot of fun. I also had the honor of access to his office lab at all hours of the day, so that's where I hung out, where I did my homework and reading. I could avoid the campus dorm life and retreat to the math office on Friday nights.

Dr. Barry Leshowitz in ASU's Department of Psychology had a real-time system, a DEC PDP-15, an 18-bit computer, and eventually had two of them. They were used to send auditory signals into a soundproof room. You'd walk into one of those rooms and you can't hear anything due to all the sound-absorbing cones. It was a thing to do those days in experimental psychology -- to determine how the human ears and brain detected distance or location for objects. You would send sounds to the students's ears in the room and they would be the guinea pigs.

One experience that really impacted me a lot working around the PDP-15 and other computers was that they were human-sized. They're in racks and they're mute, but they're smart. You can tell by the blinking lights -- so as a kid you're walking around these big computers with blinking lights. It's a pretty impressive experience and I think that really fashioned my feelings about computers at that time.

Ogus: And so your degree at--

**Garner:** Well, before-- let me finish with the PDP-15. So the technician, Woody [Sisson], he kept-- I noticed several things about that. He was kind of a crazy guy, but he kept a Bible on top of the system. When it booted up, it played a pre-recorded "Good morning, Woody!" greeting. Just imagine that this system in mid-1970s, cost around \$150,000, or in today's dollars, 700 to \$800,000. There were also many costing millions of dollars. It took that kind of system just to play a five-second audio. <laughs> So it was kind of hard to extrapolate into the future from there.

The ASU administration also had a UNIVAC 1110, a large business computer, although an astronomer in the Math Department would complain to me that it never got the same answer on floating point calculations. So I was really learning how computers could be fallible and not necessarily yield reliable results. A friend of mine on the UNIVAC 1110 was able to become superuser and take over command of the admin console right during the middle of a demo that a staffer was giving to visiting dignitaries. The operator freaked out because my friend had rendered a big eye that blinked on the console screen, took over the screen and blinked. <laughs>

Ogus: So talking about UNIVAC, you told me you did a summer job at Sperry on Univac?

**Garner:** Oh, yes. One of the jobs that I had was in the summer, just a summer job. This was Sperry Flight Systems. In the room next door they were encoding and testing the words, "Pull up, pull up," in different voices for the pilot to pull up. In our area, a person had written a compiler for an HP 2100. This was the era when programmers debated whether compilers could generate good code and, in this case, the compiled code didn't fit in memory. So I had a summer job to be a human compiler. I would take the assembler output and rewrite it into a smaller form. I could see how dumb the compilers had been, so that was a great learning experience on compiler technology. <laughs>

Ogus: Were there any other summer jobs you had that were kind of similar type experience?

**Garner:** No. But I do remember a physics student in there, was coinhabiting in the Math Department, who wanted to build a TV terminal to display characters. He couldn't get it to work and I was astonished that somebody with a physics background didn't understand the practicalities of building circuits. So I helped him get his master's degree. So yes, that was my-- so I basically got through-- one thing that was really nice though is the Engineering Department allowed me to take Math Department courses instead of engineering math courses, which was really nice.

So I'd applied to universities. I applied to several. I was so delighted that Stanford admitted me. I didn't realize that by going to Stanford I'd be kind of homecoming to where my father's family had settled in California. [And that my two great aunts Ettie and Lettie Garner had attended Stanford in 1898 - 1902, to teach history and physics in at Hollister High]. I did one other project there at ASU. For the PDP-15, I designed a D-to-A converter, teaching me about that transition out to the analog world.

Ogus: So did you consider other universities as well?

**Garner:** Yes. Yes, I did. I had, I was accepted to some others. Case Western and a few others I can't remember now. For Stanford, I got admitted into the CS Information Theory curriculum.

Ogus: So you chose Stanford, and that was --

Garner: Yes. One thing I liked about Stanford is they had a short master's program, just one year.

Ogus: One year. Okay.

**Garner:** Yes, and that really appealed to me, because I really wanted to get out into the real world. Andy Bechtolsheim, was a student there and he also really wanted to get out in the real world. Of course, Bill Joy over at Berkeley did also, neither staying on for a doctorate.

So I was admitted into Information Theory, which I just loved. But I soon realized that it was an intense subject for just a year, so I asked permission to switch to Computer Science, which they granted. Stanford's EE curriculum had a lot of labs, a lot of work and time. I also took Russian again, which was probably not a good idea, because it didn't help my GPA, as I didn't get A's in that class. But it did imbue me with the beauty of Russian poetry. Political Russian sounds very hack-eyed, but since in the Russian language you can put the words in any order, it makes for lovely poetry.

Some professors that I recall were Bernard Widrow, who really understood analog computing and had his own neural net models. Ed McCluskey, who you remember, Roy, I'm sure, who --

Ogus: He was my advisor.

**Garner:** Your advisor, okay, who taught Karnaugh maps. This is where your brain actually did what's all done by software today, minimizing logic circuits. I had Jim Clark for discrete math, who later started SGI. I had Niklaus Wirth's compiler class, but felt that it was a step backwards because we used an IBM system with punch cards. I actually had to produce my compiler on punch cards. I thought, "for a well-known university this seems really backwards."

**Ogus:** You probably came into contact with Don Knuth as well?

**Garner:** Yes, I had Don Knuth for a class. I signed up for his Algorithms class and attended the first few sessions. Stanford allows you to drop a class after a week. I realized that his class, along with the labs I was taking, was going to be so much work that I couldn't pull it off, so I dropped his class. A few years ago here at the museum over dinner with Don and I said, "Don, I signed up for your Algorithms class and dropped it. I felt like it was two classes in one." He cheerfully responded, "That's right. I did run it as two classes in one." I felt off the hook a little bit.

Then I had electronics labs. Roy, you were my instructor in the electronics lab. I think I built a 3D clock based on a cube, as there are 12 edges on a cube and 12 hours in a day.

Ogus: Right. And you said you still have that device?

Garner: I still have it, yes. I have it somewhere.

Ogus: So you inherited the gene from your father to keep everything, right?

Garner: To keep everything. Yes, I guess so. Yes.

Ogus: Yes.

**Garner:** Yes, that's a good point. My apartment mates were in the OR program, Operations Research at Stanford, Rick Biedenweg, Lynne Weber and Linda Duyanovich. Lynne was brilliant person, National Bridge Championship. Rick was brilliant. He helped me with my math and physics. I met my wife-to-be, girlfriend, Robin, at a Keystone concert in Palo Alto, where the Jerry Garcia used to play on Sunday evenings. One evening, she was there to see the Any Old Time String Band and I was there to see Peter Rowan.

I was itching to get out of Stanford. I attended an on-campus interview hosted by Bob Metcalfe. Late at night he called me and said, "Well, why don't you get out of that easy school stuff!" I'm thinking, "Easy school stuff?" <laughs> "--and get to work?" I suspect he was impressed by my work I'd done for Greg Nielson on the analog tape recording device. [Later I learned that Greg had consulted at Xerox PARC.] So what I like to say is that all that happened was

that my biking route shifted, starting from Latham Square Apartments, two miles eastward from Stanford to the Xerox PARC campus on Coyote Hill Road.

Ogus: So what was it that attracted you about the SDD, System Development Department?

**Garner:** In 1977, that's when I finished my MSEE degree and Bob Metcalfe hired me to work on Ethernet in SDD. His charter was to commercialize the Ethernet as part of the huge Alto commercialization project, called Janus. The hardware plan was with Chuck Thacker... well, the Alto -- I won't go in much of the history, that's been covered so much, but -- Chuck was the chief designer of the Alto. This second system after the Alto that he was designing was called the Dolphin or D0, and it needed an Ethernet controller. So my first role in Xerox SDD, System Development Division, was to design the Ethernet controller for the Dolphin. That was an eye-opening experience!

The Alto was a microcoded machine. You needed to get your hands dirty at that low level so you could actually implement things like BITBLT microcode to move arbitrary rectangles on the screen quickly. Also, the Alto was architected such that device controllers could be mostly implemented in microcode. All the hardware interface needed was a small amount of hardware just to get a few words in and out, but everything else was done with microcode. The Dolphin expanded upon that paradigm, but it ended up falling into the "second system syndrome" trap. We'll do everything the Alto wanted to do, but better. So Chuck wanted to spruce the Alto up and polish it a little too much, and...

**Ogus:** So all this work was being done while you were reporting to Bob Metcalfe and his group, or were you actually in a different group at the beginning?

**Garner:** I don't recall who I reported to right from the very beginning. Could've been Bob. Yes, it was Bob Metcalfe.

Ogus: Okay.

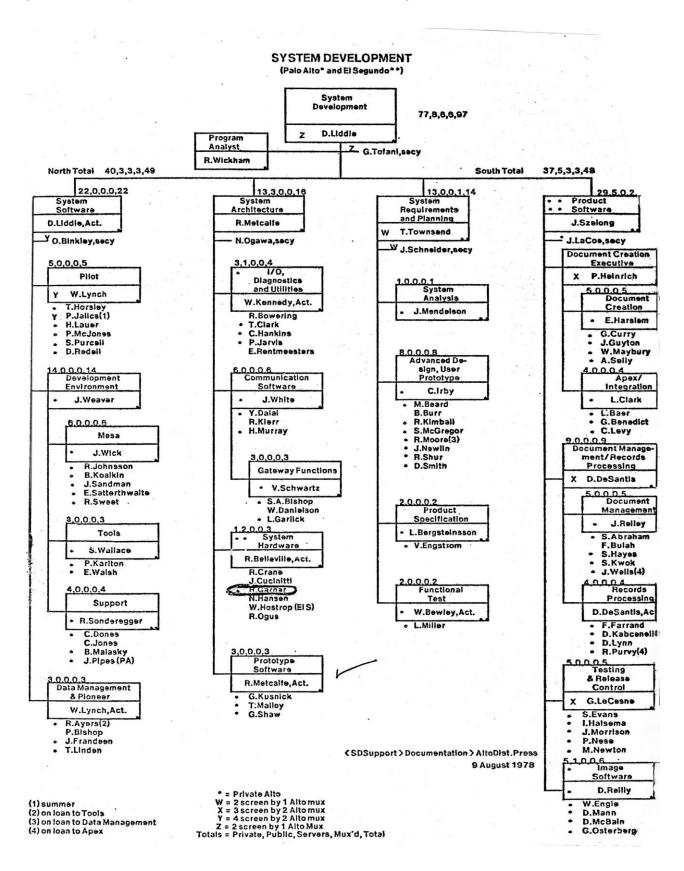

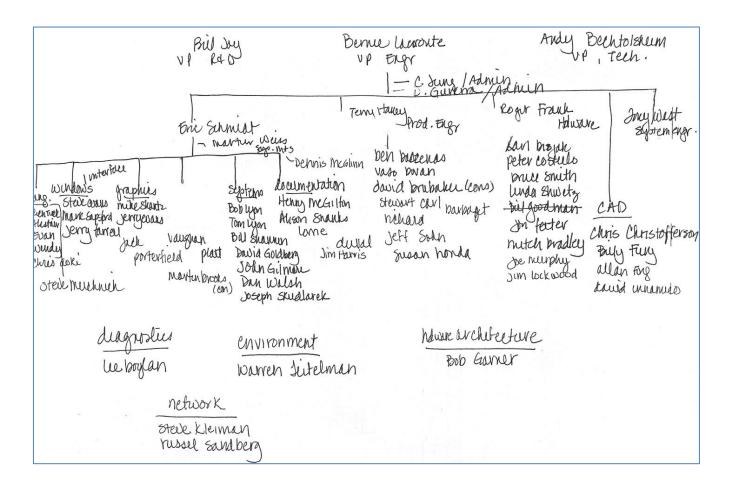

Garner: Yes. I'll have to get the org charts to see [Appendix Illustration 1-B shows Xerox SDD organizational chart].

Ogus: Yes. You told me you were so amazed when you came to Xerox that everyone had an Alto on their desk.

Garner: Yes, yes, yes.

**Ogus:** Of course, it was very different back then.

**Garner:** Yes. Xerox gave each engineer an Alto. If you think about it, an Alto back then cost around \$16,000 to build. In today's dollars that would be something like \$50,000. So to give each engineer, including a kid out of college like me, a \$50,000 tool was pretty remarkable. That was almost half the price of a home in Sunnyvale! I wasn't so impressed by the bitmap screen, but I was flabergasted that the bitmap screen consumed half of all memory. Alan Kay had wanted premium graphics, a 600-by-800 bitmap display. Half of all memory was consumed just to make a document or drawings look good. What was that all about?

But I was completely smitten with the Ethernet. Bob had been inspired by the ALOHAnet in Hawaii, and his idea was just do ALOHAnet on a coaxial cable [augmented with carrier sensing, collision detection and backoff]. The first Ethernet had been done at 3 megabits per second by Dave Boggs and Bob Metcalfe. I'll never forget doing my first FTP between two Altos and, like, the files transmitted instantly. If you're used to 300-baud modems (300 characters per second), 3 million characters per second, through a simple command line interface was shocking. It just really blew me away.

Of course, when I first came on board I couldn't believe they actually paid you for doing your hobby! <laughs> That's what struck me the most. "Oh, Yes, this is pretty cool. This is all fun and they're paying me." It was like \$22,000 per year salary, equivalent to four times that today.

The Xerox System Development Division or SDD, was co-located with PARC at the time. So we kind of felt we were part of the PARC pantheon even though I didn't technically work for PARC at the time. We shared office space, we got to know all the people there. It was like you were in some altered state of reality. Everyone there was an expert. Roy, you might remember that.

There were the set of wizards, who were very generous, kind, unassuming people. The people who fell into that camp were folks like Bob McCreight, Ed Taft, Bob Sproull, Severo Ornstein, who also founded the Computer Professionals for Social Responsibility organization; Will Crowther, also a climber and caver, author of Adventure, the caving game that everybody played; Ken Pier, John Warnock, Hal Murray, Steve Purcell, Don Charnley, Larry Tesler, Carver Mead, Chuck Geshke. They were all very kind and unpretenous folk and just great to be around.

Alan Kay was this wild, inspirational, contrarian and practical man. His famous aphorism: "The best way to predict the future is to invent it!" -- is now embodied on the floor at the new Stanford Huang Engineering Center. He's related that he was angry with the Xerox planners that came to his office asking him: "Well, what's the future going to be like?" He just became upset: "Well, don't-- stop asking me that. Just give us the funds and we'll invent it!"

**Ogus:** That's one of his famous statements, right?

**Garner:** Yes. Well, it came out of being frustrated. I recall him being really frustrated with these planners from Xerox East Coast, and they had no idea what was going on at PARC really. So then there were the kind of the high priests, I call them, these people with very massive and significant egos. Very brazen, unreserved and frank and scrupulous designers. There was Butler Lampson, who was loud, had a booming laugh and an encyclopedic knowledge. You could walk into the PARC cafeteria and you knew he was there because there was a crowd of disciples around him. I don't know if you remember that. He--

**Ogus:** I remember. I also remember that we used to measure the speed of talking by how many "microLampsons" there were!

Garner: Oh, yes. <a href="mailto:slaughter">claughter</a>>

**Garner:** Yes, he was way too smart. He was the lord of Dealer, which was the weekly forum where you sat on bean bag chairs and people gave presentations. You'd think it would be relaxing but people just shot you with bullets from the bean bag chairs.

Chuck Thacker was an intense, brilliant man. Always happy to challenge you with a new physics puzzle. He had kind of a crooked smile and a laugh. He smoked -- that was something we didn't think about back then.

And then Bob Metcalfe, one of the most remarkable people I've known and worked for: a very vibrant imagination, very strong-willed, wry sense of humor, rebellious, politically agilent, inspiring. He was willing to be part of a big company like Xerox [for a while anyway]. Everyone felt they had created their own kingdom. PARC was a castle on the hill. Bob Taylor was very strong willed, paternalistic manager, [focused on keeping everyone working together while doing their best], but with a mischievous laugh as well.

One additional note about PARC is that there were two personality types: the free-thinking radicals and hippie-likes on one side versus the conservative, more traditional working people on the other. I think the tension between the two world views at PARC helped to engender success. Later over the years I noticed that the most successful companies or groups supported a natural tension between these two ways of thinking. It was certainly present at PARC.

**Ogus:** And one thing you told me was you felt that both SDD and PARC, even thought they were part of a very old, traditional company, really gave you the feeling of being in a startup culture there.

Garner: Yes, yes. Everyone felt like we were about to change the world. I mean, this is 1977. There were only character terminals and punch cards. And here they had created, the people at PARC, starting in 1973, an environment with WYSIWYG graphics, email, laser printers, you know, everything in place, and it was just amazing... I would take printouts of, let's say, Russian poetry, and show it to someone and they would react, "How did you generate that?" We all knew we were going to change the world, but we also didn't realize that we were ahead of ourselves and we were ahead of the market...

**Ogus:** Well, they were right. It just took a little longer than they planned.

**Garner:** Yea, unfortunately. So my first asignment, as I was saying, was to co-design the first commercial Ethernet controller [with you, where you focused on the D0 interface and authored the microcode]. It was then called the Xerox Wire internally. The experimental one at PARC had been called Ethernet, but the project code name, Xerox wanted to keep it to itself, and so renamed it the Xerox Wire. It was this "Information Outlet" with like a commodity wall plug outlet as the vision.

The initial speed goal that Bob had for the Ethernet was 20 megabits per second. Dave Boggs, who'd co-designed the first Experimental Ethernet at PARC, related that "The best way to implement it is to have separate transmit and receive sections on the board where you can do full loopback. A transmit packet can be sitting there ready to go or a packet can come in at any time. So I did that. I did a VME-sized board for the Dolphin about this big [one at 3-Mbps and another at 10-Mbps. This allowed the D0 to later be a gateway between the experimental and product Ethernets.] Thus, it was full-duplex: one-half was transmit, one-half was receive. [Appendix Photo 1-C shows the D0/Dolphin 3-mbps Ethernet controller]

But a challenge was that you have to eventually place and route all the TTL components on a printed-circuit board. According to the productization group in El Segundo, the chips weren't going to fit. On my desk was a Fairchild Data Book. One day I opened it up and there was a 10-megahertz CRC chip. So I went to Bob and I said: "This doesn't fit on the board at 20 megahertz." I even went to the Stanford library and investigated ways to do CRCs differently: parallel vs. serial and all this kind of stuff. (Today, you would just google it on the Web.) And I said: "Bob there's no way I can get this to fit. However, if we use this 10-megahertz Fairchild part, it was an F9401, it will all fit at 10 Mbps." So that's why the first commercial Ethernet ran at 10 megabits per second. [Unbeknowst to me at the time, Boggs had used the same F9401 in his 2<sup>nd</sup> spin of the Alto 3-mb Ethernet adapter.] Also, Ron Crane, who was working out the analog signaling on the cable at 20 MHz -- DC collision detect -- there was a bit too much reflection from the taps.

Ogus: I remember there were electrical issues as well.

**Garner:** Yes. So that helped push the speed back down to 10 Mbps. But 10 was still so much faster than anything in the world that it seemed ludicrous that we were trying for 20.

**Ogus:** Yes, we might note that the Alto Ethernet speed was two-point-something which was the clock on the Alto. There was nothing magic about that number.

**Garner:** Yes, the Alto Ethernet ran at 2.94 Mbps.

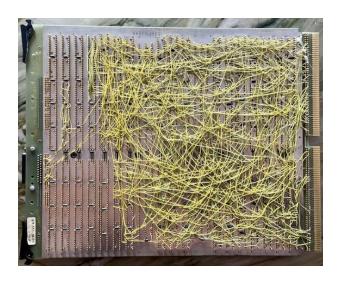

So the D0/Dolphin was an eye-opening experience. Chuck had a self-assured ego and I don't think he was always careful on some things. He wouldn't always do a comprehensive static timing analysis. The technology of the prototype boards was called stitch welding, adopted apparently from a satellite or spacecraft program. I recall the large stich-welding machine -- you could place a board into it and it would directly place a wire between two pins and then weld it to pins on each end. So you could spin a board in just in a few hours. [Appendix Photo 1-C shows the stichweld wiring on the back of the D0 3-mbps Ethernet controller.] If you needed a change to the netlist you could submit the new netlist to, I can't remember her name, the woman...

Ogus: Rosemary.

**Garner:** ... Rosemary who ran the stitch welding machine and you'd get this new board back. So I'm not sure it encouraged -- it didn't encourage simulation or thinking about the design as well up front, but you could very rapidly turn around the board. We went through many iterations before committing them to an etched printed circuit board. But one of the problems with stitch welding is that the welds weren't always reliable. I'll never forget having a Dolphin board out on the card extender and twisting the board to get it to work. That was not a good sign.

**Ogus:** Yes, it was very good to rapidly prototype but it was not reliable.

**Garner:** Yes. I think there were timing issues in it as well. But, anyways, also, the Dolphin was very expensive. And it was kind of designed for a multiprocessor perhaps with a very capable memory system. One problem that it inherited from the Alto was that the microcode would dictate when to explicitly give up control. So a microcode task could take control of the CPU as long as it wanted. Chuck and I had a constant on going battle where I'd come in in the morning and find that the cursor had stopped working, as I was doing the cursor microcode for him. And I would say "Chuck,

I'm losing cycles to your disk microcode." So he would grumble and go fix his disk microcode and my cursor would work again. But the next day the cursor would stop working because he-- so we had this constant battle of who would get control of enough CPU cycles to get work done. And there was no way to allocate it, the bandwidth, among all the users. It was just a free-for-all and it was based on priority ranking, like a traditional I/O bus. So, it just didn't work that well, a painful lesson. Chuck was the interface to the productization group in El Segundo. He had to fly down to El Segundo all the time. The old Scientific Data Systems (SDS) people had been converted over to help bring our products to market and productize them.

Ogus: So one question is, was there any serious consideration to productize Dolphin?

**Garner:** Yes, there was.

**Ogus:** Is that why he was working with the El Segundo people?

**Garner:** Yes. He was going down there. The D0 was on track to be productized but the decision was eventually made that it was too expensive. And it seemed to have timing problems. It was an occurance of the second system syndrome. It was a tough decision that someone made to cancel it as the go-to-market workstation. [It was however incorporated into the flagship Xerox 5700 Laser Printing System announced in 1980, with a list price of \$91,000.] And then at the same time Butler Lampson and Roy Levin at PARC came up with a paper design which addressed the fundamental issue with the two previous designs with a new fixed tasking schedule to access memory and run device microcode.

The new microcode scheduling framework was called a "round" and there were five "clicks" in a round. [Three microinstructions and one memory access could be executed in one click.] I/O devices were assigned to one or more clicks depending on their memory bandwidth requirements. So an I/O controller always knew when its click's microcode was going to run next and get access to main memory within certain number of microseconds. So as long as the system met its cycle time, I/O was guaranteed to work [i.e., there could be no device buffer underruns or overruns]. It was just a remarkable aspect of the Dandelion. It was called Dandelion -- that was the name of the machine eventually.

**Ogus:** I remember it. It was actually called Wildflower in the paper design.

Garner: Wildflower was the name of the PARC design, right.

Ogus: But that really was the impetus to start Dandelion. So, what you next worked on was the Dandelion system?

Garner: Yes. Yes.

**Ogus:** And that, of course, was – I use the word – seminal system. It changed the world. So, perhaps you could tell us a little bit about what was Dandelion all about? You started talking about the architecture that was really ahead of its time. And then you started working on it.

**Garner:** Yes, yes. I went back and looked at my notes. It was interesting. Actually, myself and Bob Belleville, who was my manager at the time, we were both initially skeptical of actually using the Alto Dolphin and Wildflower architecture for a product because we had experienced the Dolphin's bad track record. I actually wrote a memo, "Is this like the dinosaur era?" But eventually I came around to the realization that the Wildflower was both low cost and had this unique feature that if we met the cycle time goal it'd be guaranteed to work.

And so the Dandelion was a very synchronous machine. It could be viewed as an appliance built for the set of I/O devices it supported. It was so synchronous that 7 display bit periods -- each one were like 19.6 nanoseconds -- equaled one CPU clock cycle, 137 nanoseconds. (By the way, 137 is my favorite number – it's the fine-structure constant from physics. So I always thought that was cool -- 137.14, very close to the fine structure constant.) And there were 12 display/pixel periods per disk bit. And 3 clock cycles per memory access. So the entire core of the machine was synchronous. Now, the Ethernet ran asychronously at 10-megahertz so it needed a FIFO and a synchronizer. Otherwise the entire machine was synchronous. So we just had to meet the cycle time goal or the machine wouldn't work. But if we did, it was just going to work.

**Ogus:** It was guaranteed to work.

Garner: Now, the I/O processor, which you worked on, was also asynchronous and handeled the low-speed I/O.

**Ogus:** But that was a whole separate processor. And then, of course, you had the interface between the two machines.

Garner: Well, and you used an 8085?

Ogus: Yes.

**Garner:** It's kind of ironic that the germ of the demise of Xerox's D machines lay in the Intel 8085 in the bowels of the Dandelion.

**Ogus:** The I/O processor is kind of like a PC, right, that Xerox had a little after that.

Garner: Yes, it was. It ended up eating the whole rest of the market alive a few years later.

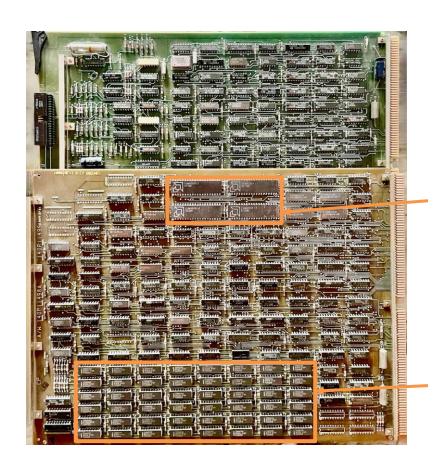

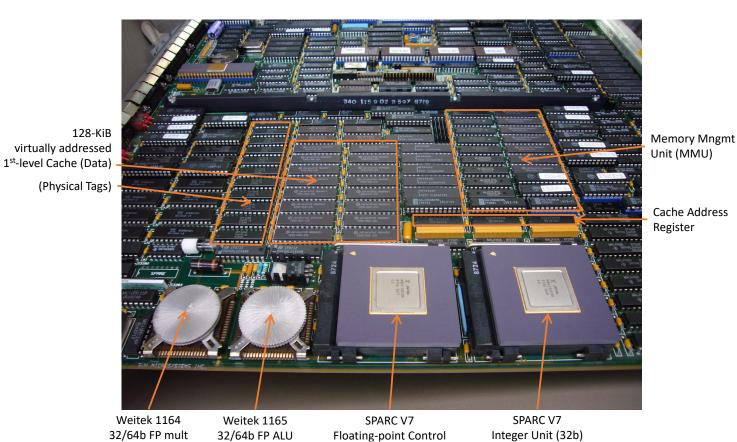

So there was this round robin scheme and two slots were dedicated to the Ethernet: one click for the disk, one click for the display, one click for slow speed I/O, your stuff. And then when any I/O microcode wasn't running the Mesa language emulator ran. So I was responsible for the CPU card design which was based on the four-bit AMD 2901-bit slice. We had 48-bit microinstructions.

I was also responsible for the Dandelion 10-Mbps Ethernet design. And at this time because we were short on real estate I decided to balk at Boggs' advice and go half-duplex. Since the cable was half-duplex -- it was only sending or receiving at any one time -- why not make the controller half-duplex? And receiving would have priority over sending. Boggs wasn't too keen about that, but it ended up working just fine. Ron Crane designed the analog phase-locked

loop part of the Ethernet controller and its interface to the transceiver [designed by Tat Lam]. <Appendix Photo 1-D shows the Dandelion Ethernet controller and CPU board.>

And Ron specified the Ethernet cable signaling levels. And, a big event, he located and repaired several Ethernet transceivers after they were blown out by a lightning strike. [During the early morning of Jan 5<sup>th</sup>, 1978, a lightning strike blew out half a dozen transceivers in a 3-Mbps Ethernet strung between two Xerox Palo Alto buildings.] Ron also designed the display controller, where he even invented a clever addressing mechanism to smoothy scroll the screen [not adopted by the Star developers]. Dan Davies designed the disk controller. Roy, you designed the low-speed I/O processor (IOP) based on the Intel 8085.

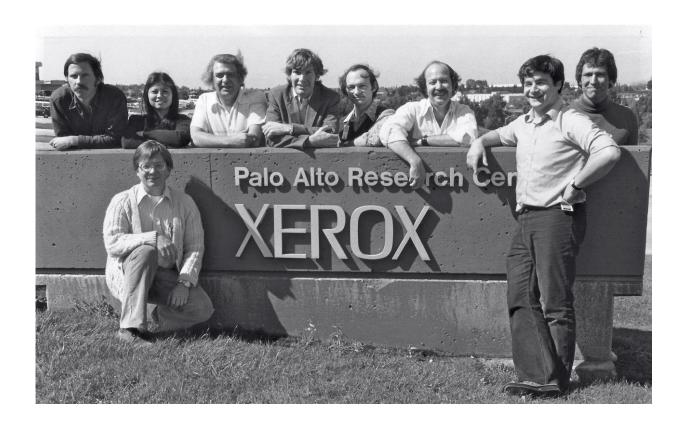

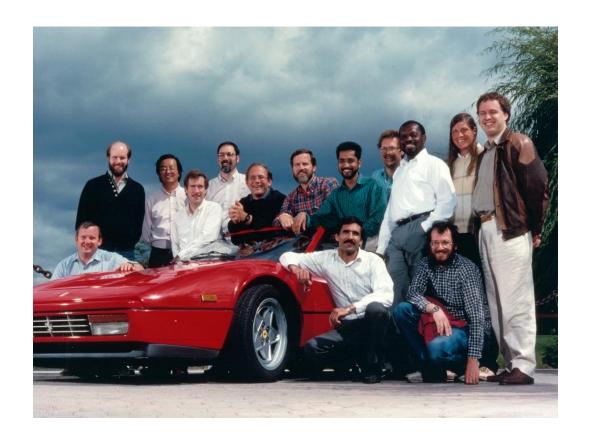

My friend and mathematician Don Charnley wrote the Dandelion BITBLT microcode, the microcode that moves a rectangular area of memory to another rectangular area. He also wrote the Dandelion microcode assembler called MASS. I wanted to implement an arbitrary 16-to-1 rotation in the Dandelion processor because you needed that kind of thing for BITBLT. Don suggested an arbitrary four-bit rotation and followed up by two one-bit rotations to get an arbitrary rotation. So you could do an arbitrary 16-bit rotation in 3 microinstructions. That was a neat suggestion on his part. [Appendix 1-E shows the Dandelion hardware design team]

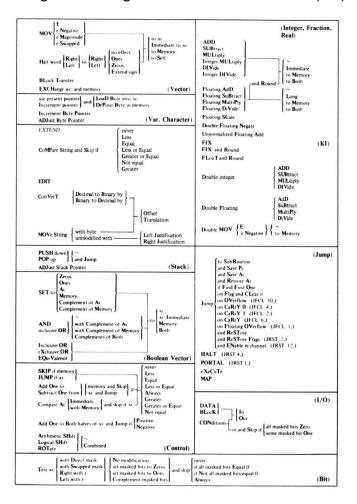

Other people did various microcode: Jim Frandeen, Amy Fasnacht, and Jim Sandman. Also at that time they asked me to become owner of the Mesa instruction set architecture (ISA). Mesa was the proprietary language that had been developed using an instruction set architecture document that had been modeled after the IBM PrincOps document, something I wasn't aware of at the time. But that taught me about the rigor of meticulously defining an instruction set with very precise definitions. I had started defining them using Gordon Bell's ISP notation, but the Mesa developers asked me later to convert it over to Mesa code because then they could then take the Mesa code and just run it on a simulator. That was a better way to make sure the opcodes were defined properly.

**Ogus:** Do you remember how it ended up that you were given ownership of the Mesa language? Because you were someone in the hardware team so it's unusual that they chose you.

Garner: Yes, I don't remember.

Ogus: Very appropriate, I think. But just the fact that they did that was kind of unusual.

**Garner:** Yes, I thought it was pretty cool. I guess I was responsible for parts of the microcode for Mesa emulator. So in that sense it made sense for me to do both.

Ogus: Perhaps that's why.

**Garner:** Now, something that I characterized at the time, what I dubbed the "Mesa high priests." (I can supply names later. [Richard Johnsson, Ed Satterthwaite, Dick Sweet, Jim Sandman]) The Mesa instruction set was a classic what Dave Patterson called a CISC [Complex Instruction Set Computer]. Every week the Mesa developers would rejigger them to make the static code size smaller based on compiling some sample programs in order to fit in a small amount of memory. We only had -- we weren't sure whether we were going to have 384-kB max or 128-kB max main memory. That's not very much main memory (16-bit words). So they were remixing the instruction set every week to shrink

code size. And also to leave some data on the stack; so maybe subsequent instructions could -- further down the stack -- use those values. A very CISCy approach. Everyone was kind of doing that at the time so few thought anything of it.

**Ogus:** We'll later talk about CISC versus RISC. Can you talk a little bit about the bring-up process for Dandelion because you implemented many innovations there as well?

**Garner:** Yes. We had no experience in this, but I thought "Wouldn't it be cool to have all five boards be probeable simultaneously?" So I proposed what was called the Windmill which was a central structure with a flexible vertical circular backplane incorporating all five board connectors. [The technician Jim Cucinitti built it.] You plugged the boards in like petals of a wildflower or windmill. With my background in natural history the name made some sense. This was the same way that the Cray-I was constructed. I learned later that the IBM 801 RISC prototype was done exactly the same way, all its boards were mounted around a vertical column that you could squish together or open up. So that way we could examine signals simultaneously on boards without having to put them on card extenders.

**Ogus:** I remember Cray's production machines are like that too for access later.

**Garner:** Yes. The Cray-1s were. They had trouble with card extenders, too. But the funny part, though, is that our printed-circuit cards were stitch-welded and the characteristic impedance of stitch-welded lines is higher than on a printed circuit board (PCB) so we were taking somewhat of a gamble implementing with stitch-weld first where signals propagate faster than in printed circuit boards. I was sort of aware of that, which also led me to be more conservative in the timing analysis because I knew when we switched over to PCBs with their lower characteristic impedance, like 50 ohms instead of 100 ohms, the propogations delays would be even slower with more crosstalk. It was a risk, but it seemed like it worked.

Ogus: Right. And then we had a debugging system that connected to an Alto to debug it.

**Garner:** Yes, that was so cool. So we used the previous computer the Alto to debug your current one. So Pitts Jarvis developed this thing called Burdock which was a beautiful user interface where you could set breakpoints, you could run microcode, you could look at registers. There was an umbilical cord (we called it that) which went over to the Dandelion. Did that go through the IOP, I think? I don't remember. Did it go through your board?

Ogus: Yes, it did, actually. Yes. So do you remember why it was called Burdock?

Garner: No.

**Ogus:** Well, there's an English drink called "Dandelion and Burdock". And there was an English researcher who was working with us, Dick Snow, and he came up with the name Burdock. So that's a little piece of trivia!

**Garner:** It was a beautiful debugging environment. It's too bad something like that couldn't be commercialized. So with microcoded machines you could have multiple sources going to multiple destinations. And I did a static timing analysis of all of them and some of them just didn't work. So that was kind of ugly. And we had the assembler, MASS, that disallowed those operations. So there was a big chart that showed which sources could be sent to which

destinations and what was illegal. Ugly. But I think that's what helped us to get it to work. So I was kind of proud that it was working, coming up in the lab.

And I remember one day we invited the product engineering people from EI Segundo up into the lab and introduced them to the design. The CPU board was sitting there on an extender card and I was so proud of the thorough diagnostic program that I had written, I said: "Let's pull out a random chip from the board and see what happens." Boy, what a learning experience that was! I amble up to the CPU board and I take the little TTL DIP chip remover and pull out a random chip. And, low and behold, the diagnostic did not detect an error and is still running! I \ looked at the chip in my hand and I'm like "I think I missed something! Or perhaps we don't need this chip!" <laughs> I scratched my head, and examining it later, I had written the diagnostic -- and being new to diagnostics -- I had put the expected answer in a register and then computed the answer and then compared them. Well, the expected answer went through a driver onto a large shared bus called the X-bus. And since I had removed its source driver, the new answer didn't get put on the bus, but instead the expected answer that my diagnostic had supplied earlier was still there. There was so much capacitance on the X-bus that, without a source driving it, the expected value actually hung on for an entire click of 411 nanoseconds. And so even though I pulled out the driver for the new source value, the correct value that had been put there by my diagnostic was still capacitively sitting there on the bus. So I learned that in diagnostic programs you should never -- what you're expecting -- put the right value right before checking for the test value because it might hang around for some unforeseen reason.

**Ogus:** Perhaps we can talk some more about the Mesa development of the PrincOps instruction set. The Mesa work had been done for many, many years independent of Dandelion. There must have been some other tools that had to be developed for Dandelion like Burdock was one. But what about the microcode controller—microcode compiler. Do you remember who did those tools?

**Garner:** Well, the microcode assembler you mean?

Ogus: Sorry, assembler. Yes.

Garner: That was Don Charnley.

**Ogus:** That was Don Charnley.

**Garner:** Yes, Don Charnley did the microcode assembler, called MASS. The Mesa compilers and all of that, I don't remember the names. The museum should do a whole history on the Xerox Star. One thing I remember when I started -- I almost forgot to talk about it – when we made this transition from the paper Wildflower to the actual Dandelion design I queried Butler Lampson: "Butler why don't you want to help implement it?," And ditto for Roy Levin. Their response was: "Well, it's easier to design it on paper than to actually get it to work!" And Butler also famously quipped: "The trouble with paper designs is you don't get bloody enough." And so I thought that's interesting -- time to get bloody!

**Ogus:** Tell me a little bit about how long it took to develop the Dandelion?

**Garner:** So I thought we did it pretty quickly. We started the design, according to my notes here, in mid-1978, so a little less than a year after I joined. So the whole experience with the Dolphin got over pretty quickly. The first Dandelion CPU board was stitch-welded in July a year later, running diagnostics a month later, Ron Crane's display was operational December '79. The first Mesa program ran in March 1980. Then I started to work on the Ethernet. So I did the CPU, then the Ethernet in sequence, and that was the same time the formal Ethernet "Bluebook" spec was being hashed out. We transmitted packets to a Dolphin in August 1980, just 8 months later. We committed the board to etch in September 1980.

This was at the very time Digital Equipment Corp (DEC), Intel, and Xerox announced the "Bluebook" spec for Ethernet, DIX, as the triumvirate was called. The authhors involved included Gordon Bell from DEC [and Rich Seifert, Peter Nesbeda, Tom Ermolovich, Tony Lauck]. I can't remember who was from Intel [Rob Ryan, Bob Beach, George Marshall]. And from Xerox Bob Metcalfe [and John Shoch, Dave Redell, Ron Crane, Yogen Dalal, Will Crowther, Bob Printis, Bill Lynch].

Metcalfe recognized that Xerox would likely keep Ethernet proprietary. That was the thing you did back then, you kept your golden jewels private. Remember that? The STAR [also known as Janus internally] was a very secret project. Everything was proprietary and secret, not open. But Bob [and David Liddle] somehow convinced Xerox to open up [and license the Ethernet patent out for a minimal fee] — I don't know how they did it. [Dave convinced management that there would be little value to Xerox competing in a low-margin Ethernet hardware market.] That's for his oral history and I hope he's done it — convincing management to open up the Ethernet spec.

**Ogus:** Right because it was against the philosophy at the time.

**Garner:** It was totally against the prevailing philosophy. But for us, what was fun about it is that Ron Crane was actually authoring the low-level spec. Remember, he wrote it in Star, actually. It was a Star document. And I recall checking with Ron: the only thing that significantly changed from Ron's spec and our work was the bit ordering [high-order bit out first to low-order bit out first], and also, the CRC was enlarged from 16 to 32 bits [and the packet source and destination addresses were widened from 32 to 48 bits, mainly due to Will Crowther's foresight]. But those were the only changes made at the link level between our work and the official DIX spec. So we kind of felt like -- hey we've got the Ethernet controller going to market at the same time the spec is going public, so, great, we have a time-to-market advantage. We weren't bothered that it was becoming an open standard.

Ogus: Yes, and that happened after the announcement of Star.

Garner: Well, my dates show that it happened in the same month. So in September 1980 the DIX Spec was signed.

Ogus: Oh, so it was actually earlier because the Star was announced in '81.

Garner: It was actually earlier.

**Ogus:** So it was earlier.

**Garner:** One thing I remember working with Hal Murray, he did the device driver for the Ethernet and I did the microcode. He did the device driver. So we had the battle "Whose bug is this?" and endless nights debugging.

Working there at Xerox was like at a startup. We worked past midnight. I used to go home typically at 2:00 or 3:00 A.M., ride my bike by the Alta Mesa Memorial Park graveyard in Los Altos which was kind of spooky. I would wait until 11 o'clock at night to call my girlfriend Robin who had temporarily moved to Bakersfield to save money on the bills that you probably got. Xerox SDD was truly a startup environment.

And I think back about it at-- some of the things I didn't mention earlier, all of my outdoor trips when I was younger. I did solo backpacking trips when I was in high school to the Chiricahua Mountains, Arizona. The cabin my father had built south of Mormon Lake near Flagstaff -- I'd go out wandering around by myself all day or sleeping at night with coyotes around me. So I had a very strong sense of self strength and fortitude and things didn't scare me. So I could stay up all night by myself if I needed to, working on schematics and then biking home by the graveyard at 3:00 A.M. So I think the confidence you get in solo backpacking -- truly in high school, I was doing solo backpacking -- really made hanging around at a workplace late at night not abnormal.

Ogus: So let's see. Sorry, did you have a thought?

**Garner:** Well, I was going to say when it was announced. Yes. So, again, we worked with the ex-SDS crew in El Segundo to productize it. They did really all that work.

The Dandelion hardware was first announced in November 1980 as the Xerox Information Network System or Xerox INS 8000. So Xerox actually first announced Dandelion as a storage server, or what they called a file server, a communication server and a print server at the end of 1980. The hardware was barely working at that time but Xerox announced it anyways which was a bold marketing step. [Also Dave Liddle wanted to announce it before the Xerox 860 group in Dallas announced their verion of a server.]

And then Xerox announced the Xerox Star 8010 Professional Workstation in April 1981 at the World Trade Center. We weren't there. Charles Irby, I think, was there. A professional information system: "A personal information system for business professionals whose main job is to create, interpret and manage information and distribute the results." So email, graphics, printing, all the things that people waste their time on today.

**Ogus:** Yes. I remember that the innovation – this whole idea of servers was a new thing – a client/server paradigm. And that was to their credit – something new that came up.

Garner: Yes. That's a good point. They came there, right there.

**Ogus:** Because in the beginning everything was focused on the workstation. And no one thought about the servers that were needed.

**Garner:** No, that then made the entire system expensive, too, unfortunately.

**Ogus:** Yes, it was expensive.

**Garner:** The Xerox Star 8010 Workstation was announced with a 16, almost \$17,000 purchase price, which would be \$50,000 today for a 1-MIPS workstation (although it did move things quickly on the screen), or \$700 per month rental which is \$2000 per month today. It was also shown at the National Computer Conference (NCC) in May of that year (1981) and that's where Steve Jobs checked it out apparently. He was there to see what Xerox had brought to the market. The DIX Ethernet announcement happened in May, 1980 [and the Ethernet Bluebook 1.0 spec was published in Sept, 1980.]

Ogus: Okay. So, of course, the Star was a phenomenal technological success but not a business success.

**Garner:** No. Well, first of all, it was a huge investment. I mean there were eventually hundreds of people on the Star project, around 350 total [employess plus contractors] on the hardware, software and the operating system...

**Ogus:** Probably three quarters of them were software.

**Garner:** Were software people, yes. So to bring to market all of that—yes, way ahead of its time. So at \$50,000 in today's currency for a single workstation, professionals said, "OK, look, I don't know how to type."

Ogus: Or "I don't want to type."

**Garner:** "I don't want to type." I have secretaries that type for me at that time. "You're telling me you want me to purchase in today's dollars a \$50,000 workstation to make my secretary more efficient?" And then you want me to purchase a file server, a print server and a network box as well. So the total cost is going to run to like \$200K which would be almost \$1 million today. "Just to make my secretaries more efficient?"

Ogus: So you think those are the kind of reasons because if it had been ten times cheaper it might've been different.

**Garner:** Yes, it would've been totally different. And: "What's this thing called a mouse?" And actually, I went back and looked at the original product release. The original press release called the mouse: "an unusual control device" because a mouse had never been announced to the public before.

Ogus: Yes, I think you're right. Ahead of its time is the right description for the problem.

**Garner:** And later I learned maybe only 20,000 were sold and that's what Dave Liddle has said is the number. But the major customers I saw and heard of were NSA (during a visit I had with the NSA later) and the Voice of America since they were multilingual. Star was a success in Japan -- the first Japanese Kanji workstation.

**Ogus:** Yes. So I remember that the Japanese were very interested in it because this was the way to produce their very complicated script in an easy way.

**Garner:** And in a system that cost quite a bit less. And it was very reliable. We never had heard of any field issues with the hardware. The software was very reliable even though it had a very basic virtual memory system. In November 1981 the Xerox Star received the Fortune magazine Product of the Year award which was kind of cool.

[Shown in Appendix Photo 1-U] Every year Fortune selects what are the coolest products that year in the United States and the world.

So, unfortunately for us, right after the Xerox Star was announced, just four months later, IBM announced this thing called the PC with a 4.8-Megahertz Intel 8088. It was announced just four months later. Everyone felt that the rug had just been jerked out from under them. And that Microsoft and Bill Gates were setting the world back three decades with DOS. The Star user interface had been designed to be intuitive, easy to use. The Star GUI design team consulted psychologists and sociologists. It made sense. You started with an existing document and modified it. You also didn't have these horrible DOS-like command interfaces. Unfortunately, Star didn't feature spreadsheets until later.

So it was all kind of downhill from there. The emphasis shifted from Xerox PARC to Apple at that point. I recall the day that Steve Jobs came by and visited PARC in December, 1979. Larry Tesler, who knew my girlfriend [Robin] at the time, gave the demo. He moved to Apple. Bob Belleville moved to Apple and managed the Macintosh hardware team. He had been gunning for... while at SDD -- remember, he built this little small PC... what did he call it?

Ogus: Cub.

**Garner:** A little tiny 6800-based or something, or was it Intel-based?

**Ogus:** Well, I think at that point Intel had come out with a 16-bit processor and he wanted to play with them. And so the Cub was based on that.

**Garner:** Yes. So he kind of knew that the high priests and Xerox doing their own language (Mesa) that needed a microcode machine and operating system was not going to make it. So Bob Belleville went to Apple and actually managed the Macintosh program at Apple. On which my friend Mike Boich worked against whom I had run for freshman class president in high school.

**Ogus:** That's right. So then you actually before you left for Sun you were still at Xerox for a while. You moved to PARC per se.

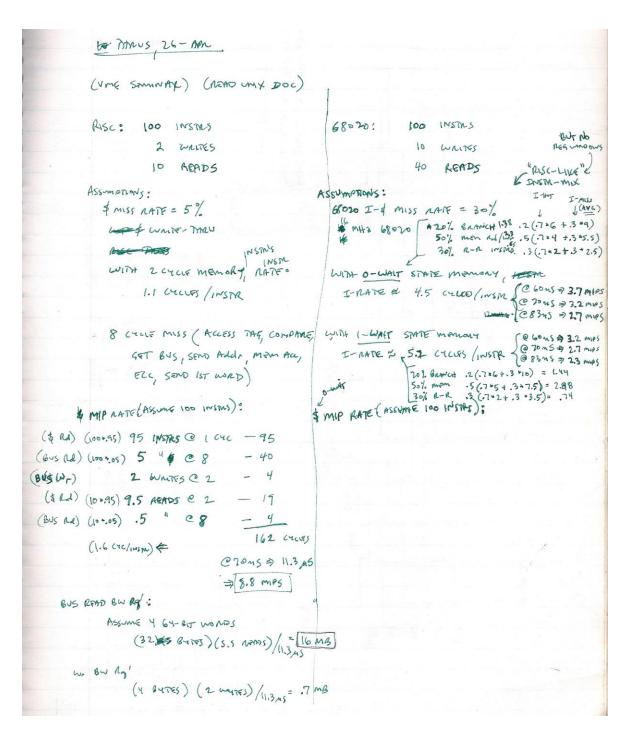

Garner: Yes. Right before I left, I remember there was one interesting thing that happened. This guy named Forest Baskett was coming around and he was into computer benchmarking. He benchmarked Cray's stuff and really understood it. He had this little benchmark called Puzzle which solved a block packing problem that he was running on all the computers he could get access to. He ran it on the Dandelion and the performance was really bad. I've tried to find what the results were, but even though we had a 7.3 megahertz clock, it took three cycles to do a memory access. So we were less than a 1-MIPS machine. So here we are taking what could be a 7-MIPS machine [for non-memory instructions] and making it into a less than a 1-MIPS machine. So that really got my attention. Why had we done this? But I had always wanted to work at PARC proper since we had been over there so much. So, in 1982 I joined PARC itself in Lynn Conway's VLSI group, who was doing...

Ogus: So you joined Lynn Conway's group?

Garner: Yes. So Lynn was doing VLSI design.

**Ogus:** Which is a completely different type of work from what you were doing before.

**Garner:** Entirely. Lynn Conway was a very kind and good-natured person. I never saw her angry. She really cared about people. She really engendered the best in people. She was really an educator with her VSLI design methodology. Her whole history is how she created that whole program to get students tuned into chip design.

I started working with Dick Lyon. He had done an innovative design for an optical mouse based on cross-coupled neural light sensors. It could even worked on blue jeans or any pattern that had equal-distant spots. It would stabilize on a pattern, asynchronously stabilize on another one, and if it detected a change in the dot pattern, it could figure out which way it had moved. A very brilliant design. And I helped productize it for the product group. I also worked on some other things. I actually designed a DARPA MOSIS chip using a Lynn's and Doug Fairbairn's Icarus integrated circuit layout program.

Other people did some more complicated chips but this got my fingers into chip design. I saw that the field, though, needed more advanced software tools. It just wasn't possible to design an interesting chip by hand. Lynn promoted the "stick diagram" method that, in jest, one could say all you needed was blue, red, green, and yellow pencils to design a chip since when red (poly) lines crossed green (diffusion) lines you got a transistor. Blue was metal. But there weren't good design tool methodologies in place yet. John Ousterhout was just formulating his IC layout tool Magic which was really needed. But that's research, that's the nature of research.

**Ogus:** And then you also worked on the PARC Dragon work which was kind of prescient for the future. We'll get to that later.

**Garner:** Right. Yes. So while I was realizing the tools really weren't in a place to do interesting chips there was an attempt to do an interesting chip program at PARC called the Dragon multiprocessor. It was a whole new multiprocessor architecture designed with careful attention to the cache coherency protocols. It was based on a split transaction packet-based bus: You could send a memory request and get the result back later so you wouldn't tie up the bus for a long period of time.

Jean-Marc Frailong and Pradeep Sindhu were the lead architects. Chuck Thacker asked if I would work on the I/O chip for it which I agreed to start spec'ing. But right about that time PARC imploded or, I suppose, exploded would be the better word for whatever reason. PARC's director, George Pake, had come down from his nest on the first floor and poked at Bob Taylor's tight-knit cult leadership. CSL folks loved working for Bob Taylor. So Bob resigned in protest. They were trying to get him to do more practical work. Maybe they thought he had too much power. I don't know. But nearly everyone departed with him from PARC's Computer Science Lab (CSL): Butler Lampson and Chuck Thacker. They formed the new Systems Research Center (SRC) at DEC in downtown Palo Alto.

Ogus: Digital Equipment Corporation.

**Garner:** Yes. So I was standing around all these empty offices in CSL one day with Dave Patterson who had been consulting to the Smalltalk group, Alan Kay's Smalltalk group for some time. He knew me based on my reputation

designing the Xerox Dandelion hardware. And he asked if I might join-- he and his brilliant student from Berkeley, Bill Joy, at a startup doing 68000-based workstations but also planning to do a RISC-based design. And I kind of looked at him like: "A 68000-based workstation company? There are lots of those out there. Why is this one going to be any better than all the other "dirtball" 68K firms?" Dave had been consulting with Bill and the folks at Sun, which was about a year-and-a-half old at that point. And I just ignored him because I was in the PARC citadel. I had spent some time doing a hand design for a Mesa processor. I don't know how practical it was, but it seemed like somebody had to get going on one because there really needed to be a full-custom Mesa chip. Later SSD did that themselves. And then, fortuitously -- this is early '84 my girlfriend Robin Beresford asked me to go pick up an album at Tower Records.

**Ogus:** 1984?

**Garner:** Yes, '84, Tower Records on San Antonio Road. When I went in there to pick up the album there was Bill Joy and Eric Schmidt who had joined Sun a few months earlier from PARC walking up and down the aisles talking about work. You never stopped thinking about work at Sun. They spotted me and had contacted me before. They twisted my arm, insisting: "Why don't you come work here?" And so I gave in. If my wife hadn't sent me to Tower Records that night I don't know what my future would've been.

My interview with Andy Bechtolsheim at Sun was odd because it consisted of him explaining how he had developed a new static timing analysis tool -- a spreadsheet! I didn't realize at the time that he had a reputation for also turning an eye to validating timing. The Sun2 design had manufacturing challenges. In fact, my first day at Sun or maybe during the interview, one couldn't help but notice in one corner of the half-empty building, there was the CEO Scott McNealy, Bill Joy, Andy Bechtolsheim and Vinod Khosla plugging and unplugging 68010s until they could find one that worked because there were timing issues in Andy's board. That was quite an eye-opener. Vinod Khosla presented my employment offer and asked, "Do you ever want to be able to afford a house in Silicon Valley?" That was certainly a motivating factor for joining a startup.

**Ogus:** Let's see, so that's 1984. And so you decided to leave Xerox and move to this new little startup called Sun Microsystems. So what were your impressions when you got there?

Garner: Well, also, before I forget that was the year I married Robin, too. So it was...

Ogus: OK, a very busy year.

**Garner:** 1984. Sun was a very small company. We were just in one building. But the very first day I was kind of jolted by the realization that perhaps I hadn't moved that far because in the mailroom were printouts, Dover laser printer printouts from Stanford. People were driving to Stanford twice a day to pick up. Sun employees were using the Stanford University Network (SUN) Alto network....

**Ogus:** Right, Dover was a Xerox printer.

**Garner:** Yes, it was a Xerox printer. Xerox had installed at Stanford a large number, kind of granted to them a large number of Altos and a Dover laser printer. That's how Andy Bechtolsheim got his motivation to do a better-- a different job, do an open workstation instead of a proprietary workstation like the Alto. [Earlier, in 1978, Andy was a no-fee

consultant at Xerox PARC.] But the folks at Sun were actually using it. I felt like I was still at Xerox because the Dover printouts were in all the inboxes.

There were really amazing people at Sun. Bill Joy was, or is -- was and is -- a remarkable visionary. Just brilliant. He's a visionary of the highest order, a grand weaver of tales, a perception shifter and skilled hyperbolist. He went around doing what I called "cranial acupuncture." He could walk in anyone's office, software, hardware or whatever, and within 30 seconds totally comprehend what they were up to, and immediately giving his advice. He'd walk out of the office and the stunned person would feel like "What just hit me?" He also had this technique of speaking so rapidly that as you tried to process it and keep up with him you'd start falling a sentence or two behind. And eventually, he just flummoxed you. You'd be speechless and tied in knots. It was one of his classic debating techniques. Dave Patterson had remarked that Bill would speak more than he did in class. He was just a very demonstrative person. On the other hand, Bill could also be extremely pragmatic. He had somewhat of a binary personality: Here he'd be crazy and visionary and then a few moments later he'd be practical and proclaim "We'll just do this!"

Dave Patterson was our eminent consultant. He had a fatherly persona, strong, generous, equanimous, pragmatic. He was really good at bringing people together and tying ideas together as he did at Berkeley. He wasn't afraid of conflict or arguments or fights. Later I learned that he was a wrestler in college, which kind of explained why he wasn't afraid of standing up for something. He would break up arguments, the cat fights we would have all the time at Sun. He would say; "That might be the way you think about it, but I think this is the way it's going to be." He was very pragmatic in getting people to adopt the most rational approach.

Andy Bechtolsheim was brilliantly meticulous and extremely detail-oriented. He could sometimes be stubborn. He only designed products that he knew could be built right then and now at low cost and delivered to market quickly. He didn't really look out two to three years, just the next year. Folks used to characterize his design method as "making a Porsche out of Volkswagen parts." He's also the only person I knew of who could actually have two thought trains running concurrently. You could actually talk to him about two threads of thought and he wouldn't trip up. Just an amazing capability. He was a super optimizer who also kept himself grounded in the lab. That drove some people nuts years later when he became known to be extremely wealthy from all his investments, but nevertheless there he'd be in the lab doing technical work. He never backed down from his passion for doing world-class engineering.

Scott McNealy was bitingly and hilariously funny – cutting, jocular humor. He had a lot of fun being the rabble rouser for the computer industry. He didn't fully comprehend computing technology, but he fully trusted Bill and Andy. Totally trusted them, which was a great pairing. Also, I'll never forget, outside my office on the second floor, Scott held a company-wide beer bust every Friday. At the end he would give away all the freebies that executives and salesmen had given to him during the past week. He just gave them away, perhaps so he couldn't be overly influenced.

Bernie Lacroute, who came on later, was the Senior VP of Engineering, a very respected, passionate and caring person. We gave him the nickname "Napoleon" because he was so detailed, driven and forceful.

Ogus: So how big was Sun about at that time?

Garner: Well, I was employee 278. I don't know if--

Ogus: Oh, okay.

**Garner:** You can see that on the badge or not. I was one of the earliest hardware engineers there among, sort of in the top five. Sun had no marketing or sales people, it was all mainly engineering at that time.

**Ogus:** So a few hundred people it sounds like,...