# PROJECT GRIND REPORT

3

ON

# THE HIGH SPEED GATE CIRCUIT

Eugene Breiding Robert Lindsay

## PROJECT GRIND REPORT ON THE HIGH SPEED GATE

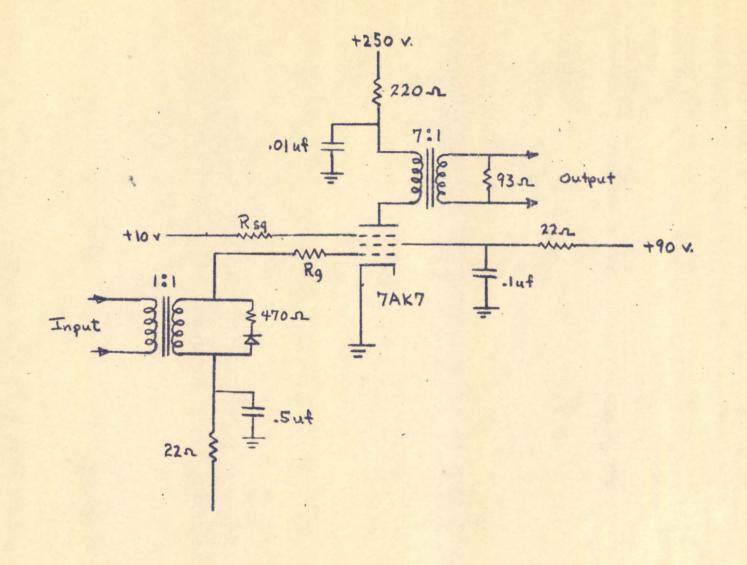

# Circuit Parameters

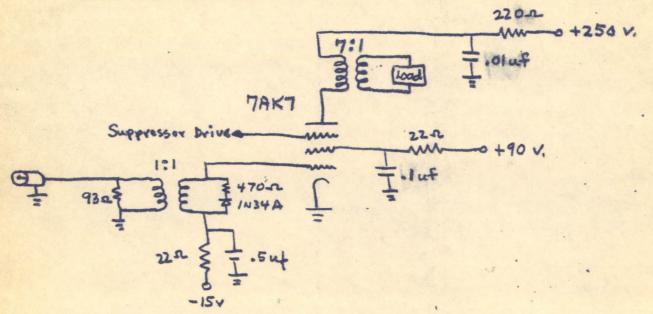

Vacuum Tube: The circuit now under test uses a 7AK7 pentode as the gate tube. Life tests made by MIT on the 7AK7's in WW-1 indicate that the tube has long life characteristics and is therefore a suitable choice. However, characteristic curves and life data in the regions where the tube is to be operated for WW-2 applications is not yet available. Preparations are now being made by Dave Crawford's group at IBM to run 7AK7 characteristic curves in the positive regions, but no data has yet been obtained.

Pulse Transformers: Input and output transformers are being used in the bench test units, although the circuitcan be operated without an input transformer when driven by the secondary of the output transformer of the driving stage.

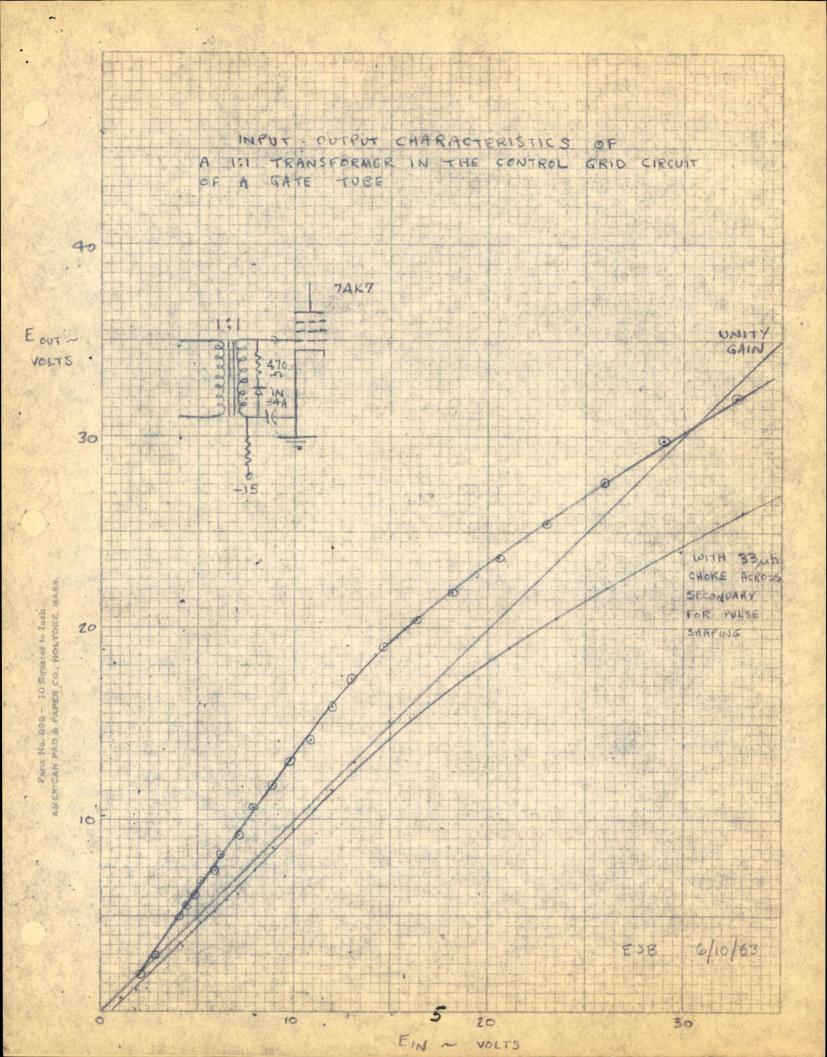

The input transformer is the standard MIT 1:1 transformer. The effect of this transformer upon input pulse amplitude is shown by the curve on page 5. It should be noted that the transformer increases pulse width due to the relatively high leakage inductance. Shunt induct-ive compensation can be used to reduce pulse width, but this also reduces available amplitude. Low leakage transformers are being constructed, and these units will be used for the final tests.

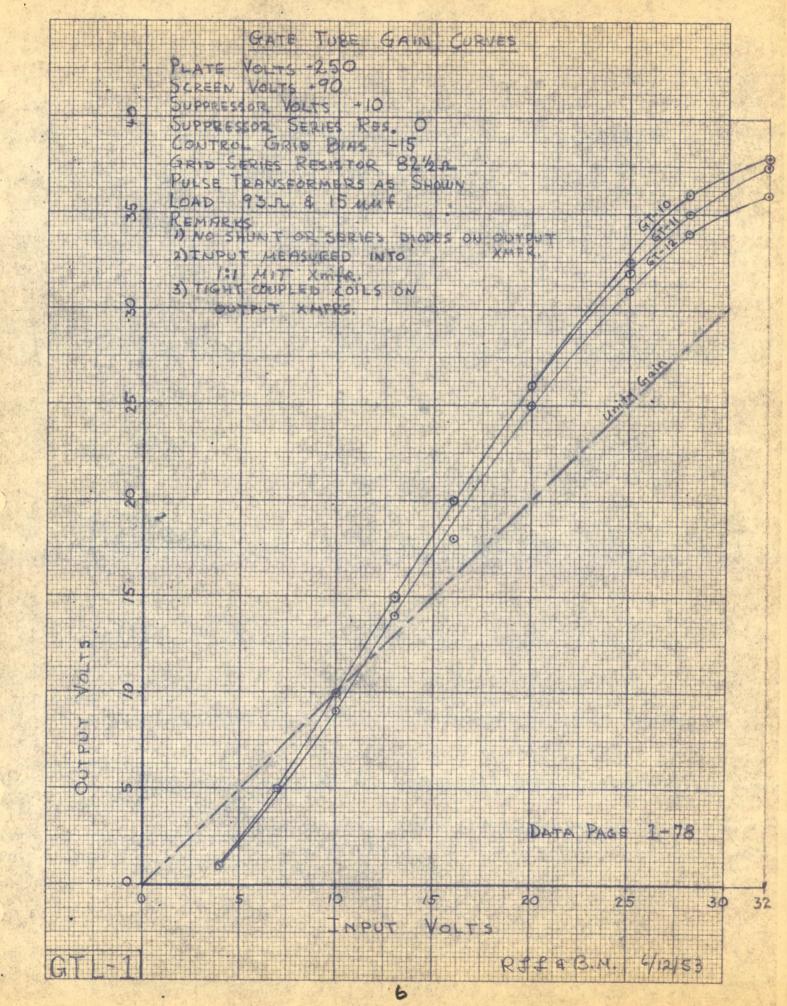

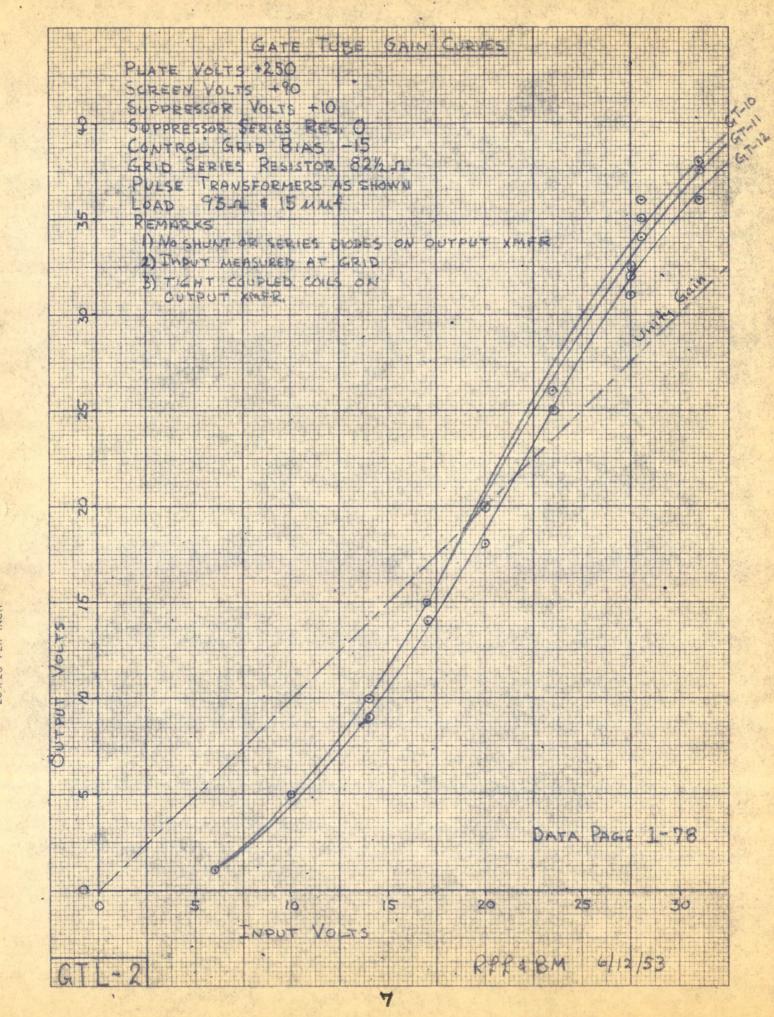

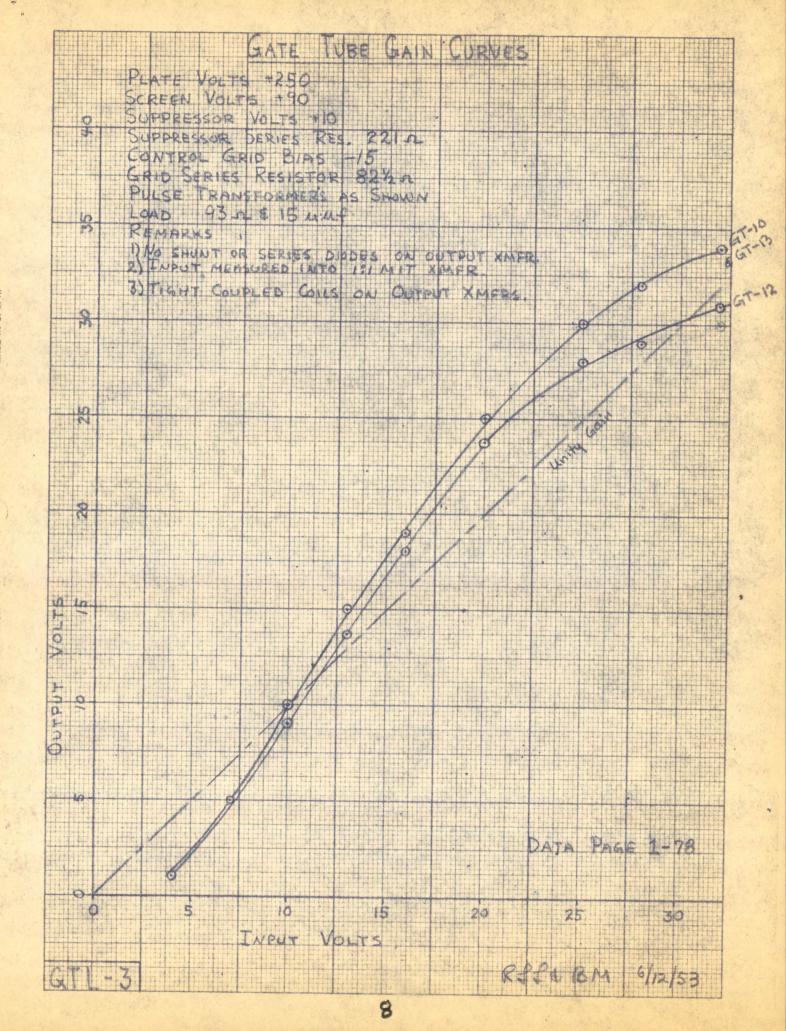

The output transformer is a special 7:1 transformer with tight coupling between windings. Tests have been made on transformers with ratios of 1:1, 3:1, 5:1, 6:1, 7:1, and 8:1, and these tests have indicated that the 7:1 ratio is the most suitable choice. The load line with this ratio for a 93 ohm load is kept below the knee of the Ep-Ip curve to obtain less variation of output voltage with load changes. Gain curves for the 5:1, 6:1, and 7:1 ratios are shown on pages 6,7 and 8.

Transformer Termination: The output transformer termination has been chosen to be 93 ohms because of the following reasons:

- 1. 93 ohm cables will be used in WW-2.

- 2. A 93 ohm termination does not require shunt primary diodes.

- 3. Load capacity may be very large before transformer loading is appreciably changed.

- 4. 93 ohm loading helps to hold line pick-up to a minimum.

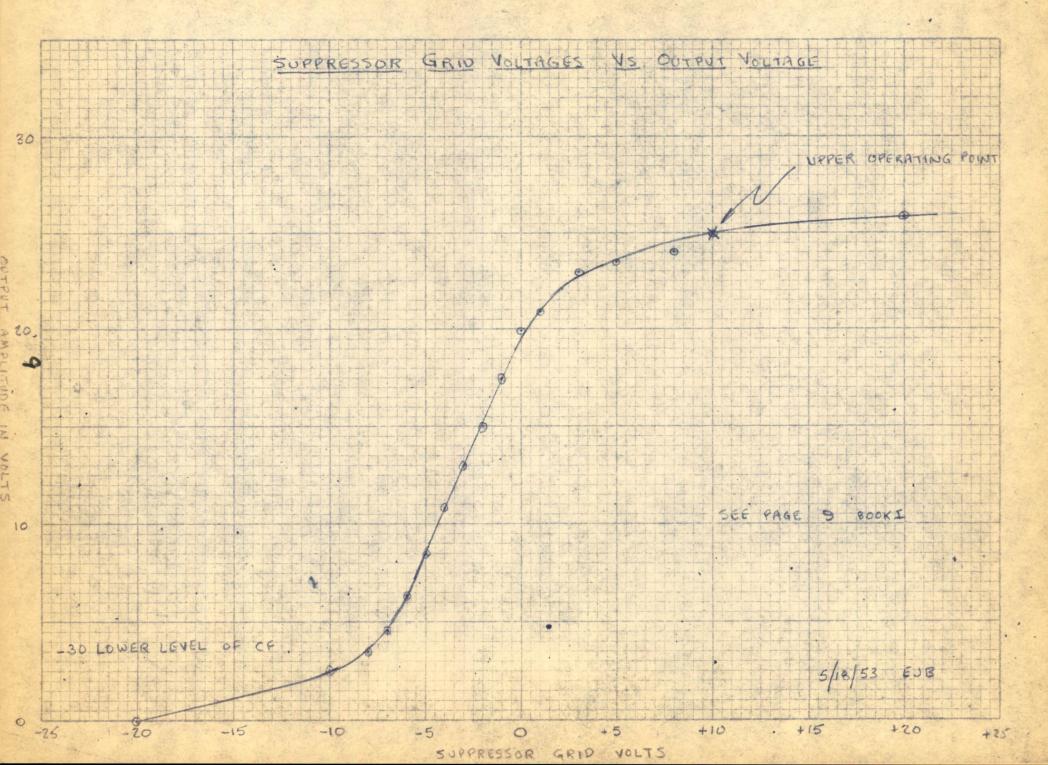

Suppressor Grid Resistance: The effect of simulating a cathode follower resistance by placing a resistor in series with the suppressor grid is

shown in the curve on page  $\vartheta$ . It is seen that this resistance tends to flatten the top section of the gain curve. This is desirable in order to maintain a more constant output over the range of grid input amplitude.

-

Parasitic Suppressor Resistance: Verbal reports from Herb Platt of MIT indicates that the parasitic suppressor is instrumental in holding up output amplitude. No investigation has yet been made by IBM, but tests are being planned to determine the optimum value of this resistance.

Decoupling Networks: Optimum values of decoupling parameters have not been determined, although satisfactory results have been observed with 0.5 uf and 22 ohms in the -15 volt lines, 0.1 uf and 22 ohms in the +90 volt lines, and 0.01 uf and 220 ohms in the +250 volt lines. It is thought that these values are somewhere close to optimum values. Tests to be made will determine the minimum values.

# Driving Voltages and Currents

Suppressor: The DC level is supplied to the suppressor which constitutes one input of the "plus AND" circuit. This level has been established at +10 or -30 volts. The +10 volts has been selected in order to obtain higher amplitude output. It also shows less deviation of output amplitude with respect to a change in the suppressor level as shown on curve  $\# \ q$ . The input capacity of the suppressor grid without stray capacity is approximately 4uuf. The current requirements (during a pulse on the control grid) is approximately 50 ma peak. This grid cuts off at about -10 volts.

Control Grid: 0.1 microsecond pulses are supplied to this grid and these constitute the other input of the "plus AND" circuit. This pulse has been tentatively standardized at 20 to 40 volts in amplitude, 0.08 to 0.12 microseconds in width, a maximum of 0.4 microseconds recovery time, and maximum of 5 volts positive overshoot. This pulse basically is a half sine wave but may be flat on top. The input capacity is 12 uuf. The current required to drive this grid is approximately 50 ma peak with 24 ohms in series and is 20 ma peak with 470 ohms in series with the control grid.

# Supply Voltages

Plate: The plate requires +250 volts with a maximum average current of approximately 15 ma.

Screen: The screen requires +90 volts with a maximum average current of

# approximately 6 ma.

Bias: The bias is set at -15 volts.

# Marginal Checking

No marginal checks have been made to date, Since it was felt that the circuit should be completed and in final form before this type of testing was attempted.

# Work to be Done

A series of final tests have been set up to determine the performance of the final gate circuit under wide conditions of loading and driving applications. These tests will be started as soon as the bench test unit is completed and the required special transformers constructed to required specifications. These transformers are now on order and should be received within a week.

6-30-53

Gate Circuit Diagram

6

RLL 6/30/53 ÷

TRANSFORMERS ON TEST

GT-10

5:1 TRANSFORMER, 40 to 8 TURNE ON FERRAMIC H BODY F262 CORE.

GT-11

6:1 TRANSFORMER, 42 to 7 TURNS ON FERRAMIC H BODY F262 CORE.

GT-12

7:1 TRANSFORMER, 4256 6 TURNE ON FERRAMIC H BODY F262 CORE.

GT-13

REPLACEMENT FOR GT-11, GT-11 DEVELOPED AN OPEN PRIMARY DURING TESTS.

> R.L.L. 6/29/53

EUGENE DIETZGEN CO. MADE IN U. S. A.

NO. 340. 1.20 DIETZGEN GRAPH PAPER 20 X 20 PER INCH

EUGENE DIETZGEN CO. MADE IN U. S. A.

NO. 340. 1-20 DIETZGEN GRAPH PAPER 20 X 20 PER INCH

EUGENE DIETZGEN MADE IN U. S. A.

00

40. 340 1.20 DIETZGEN GRAPH PAPER 20 X 20 PER INCH Porm No. 898 - 10 Squares to Iach American pad & Paper Co., Holyoke, Mass.

### 7AK7 CIRCUIT AND TESTS

Gate Tube Circuit:

Gate Tube Tests:

Data should be taken to plot the following curves:

- 1. Curves of input amplitude versus output amplitude, pulse width versus input amplitude, and recovery time versus input amplitude for the following cases.

- (a) Resistance loads 93, 82, 75, 68, 62, and 51 ohms

- (b) 93 ohms and various capacity loads until output falls off in amplitude.

- (c) Repeat (a) and (b) with 40 feet of RG62/U coax between transformer and loads.

- (d) Load of 3 gate tubes and 1 flip-flop under the following conditions:

- (1) Direct to GT & thru xmfr to FF

- 2) Durect to GT & thru diode logic to FF xmfr

- (3) Thru xmfr to each GT and flip-flop diode logic

(4) Thru common xmfr to GT and diode logic to FF

- (e) Two 7AK7's as an OR circuit with common output transformer. max rep rate of 1 Mc.

- (f) GT driving GT with no xmfr on second GT. Curves should be plotted for second GT by transfer characteristics.

- (g) Repeat steps (d) to (f) with 40 feet RG62/U coax between gate tube and loads.

2. Curves of amplitude output, pulse width and recovery time versus marginal check voltage for plate, screen and control grid voltage marginal checks.

Gene Breiding } 6/22/53 Bub Lindsay

A MAGNETIC-CORE MEMORY WITH EXTERNAL SELECTION

by

Sydney Bradspies

B.E.E. College of the City of New York (1953)

SUBMITTED IN PARTIAL FULFILIMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January, 1955

Signature of Author \_\_\_\_\_\_ Department of Electrical Engineering, January 17, 1955

Certified by \_\_\_\_\_ Thesis Supervisor

Accepted by \_\_\_\_\_ Chairman, Departmental Committee on Graduate Students

#### ACKNOWLEDGMENT

I wish to thank Professor W. K. Linvill, my Thesis Supervisor, and W. N. Papian and J. I. Raffel of the Lincoln Laboratory for their assistance throughout the course of my investigations and during and after the writing of this report. Without their criticism and encouragement, it is doubtful that the job would have been completed.

I must also express my thanks to the large number of secretaries who have had some part in the physical preparation of my thesis, and to the many other people at the Lincoln Laboratory who aided me so freely during the course of the work.

The research reported in this document was supported jointly by the Department of the Army, Department of the Navy and Department of the Air Force under Air Force Contract No. AF 19(122)-458.

1

# A MAGNETIC-CORE MEMORY WITH EXTERNAL SELECTION

#### by

### Sydney Bradspies

Submitted to the Department of Electrical Engineering on January 17, 1955, in partial fulfillment of the requirements for degree of Master of Science.

#### ABSTRACT

A 3-core magnetic-memory cell was built, tested, and analyzed. One of the three cores is exclusively for the retention of information (memory); the other two cores are involved in the selection process, one during "read," the other during "write." The characteristics observed in this memory suggest the satisfactory response that may be expected:

> A complete read and write cycle was completed successfully in 0.5 microsecond.

> Voltage outputs from a single memory core were as large as 2.5 volts.

The ONE-to-ZERO ratios were found to be about 20 to 1. ONE to noise ratios were several hundred to one.

These results compare favorably with those encountered in present coincident-current memories.

Some drawbacks were encountered in this external-selection memory. To obtain the requisite high operating speed, the switch cores must be driven very heavily; also, to obtain maximum efficiency the cores should not switch before the currents have risen to their final values. These conditions require a source of large currents with very fast rise and fall times. In driving a large-scale memory, it is difficult to obtain fast rise and fall times because of the inductance of partially selected cores and because of the long leads required. Furthermore, the voltages induced in the selected switch cores are large; a number of these cores in series might well present an excessive back voltage to the core driver. These and many other problems must be solved before it is possible to realize the fullest capabilities of a magnetic-core memory utilizing external selection.

Thesis Supervisor: William K. Linvill Title: Associate Professor of Electrical Engineering

# TABLE OF CONTENTS

| ACKNOWLEDCMEN | Pa<br>NT                                                                                             | age<br>i |

|---------------|------------------------------------------------------------------------------------------------------|----------|

| ABSTRACT      | i                                                                                                    | 11       |

| TABLE OF CONT | TEN TS                                                                                               | ii       |

| LIST OF ILLUS | STRATIONSi                                                                                           | iv       |

| CHAPTER I     | INTRODUCTION                                                                                         | 1        |

|               |                                                                                                      | 1        |

|               |                                                                                                      | 6        |

| CHAPTER II    | THE NATURE OF THE SWITCH AND MEMORY CORES 1                                                          | 3        |

|               |                                                                                                      | 13       |

|               | B. The Memory Core                                                                                   | 38       |

| CHAPTER III   | THE THREE-CORE-PER-BIT MEMORY                                                                        | ó        |

|               | A. The Operation of the Cycle                                                                        | 50       |

|               |                                                                                                      | 54       |

|               |                                                                                                      | 57       |

| CHAPTER IV    | CONCLUSIONS 10                                                                                       |          |

| APPENDICES    |                                                                                                      | -        |

|               | A. Equivalent Circuit of Partially Selected Switch                                                   |          |

|               | Core 11                                                                                              |          |

|               | B. High-Speed Core Driver 11                                                                         | .4       |

|               | C. The Linearized Coincident Current Memory Cell 12                                                  | 24       |

|               | D. The Algebraic Solution of the Linearized Threep<br>Core-Per-Bit Memory Unit 12                    | 26       |

|               | E. Derivation of the Graphical Solution of the<br>Three Core Memory (Including Loading of Loop B) 15 | 6        |

| BIBLIOGRAPHY. | •••••••••••••••••••••••••••••••••••••••                                                              | 8        |

# LIST OF ILLUSTRATIONS

in the

| Figure No. | Title                                                                                      | Page No.    |

|------------|--------------------------------------------------------------------------------------------|-------------|

| 1.1        | Rectangular Hysteresis Loop of<br>Ferromagnetic Memory Core                                | 3           |

| 1.2        | A Four-by-Four Plane of Ferromagnetic<br>Memory Cores                                      | 4           |

| 1.3        | Nine Bit Memory "Plane," Consisting of<br>9 Memory Cores and 18 Switch Cores               | 8           |

| 1.4        | Read Output of Core A                                                                      | 8           |

| 1.5        | Write Output of Core B                                                                     | 8           |

| 2.1        | Idealized Switch Core Magnetization Curve                                                  | <b>1</b> /4 |

| 2.2        | More Realistic Switch Core Magnetization<br>Curve                                          | 과           |

| 2.3        | Actual Core Magnetization Curves                                                           | 15,16       |

| 2.4        | A Four-by-Four Plane of Ferromagnetic<br>Switch Cores                                      | 18          |

| 2.5        | Single Switch Core, with X and Y Driving<br>Lines Combined                                 | 22          |

| 2.6        | Hysteresis Loop of Core Shown in Fig. 2.5                                                  | 22          |

| 2.7        | Equivalent Circuit of Half-Selected Switch<br>Core                                         | 24          |

| 2.8        | Revised Equivalent Circuit of Half-Selected<br>Switch Core                                 | 24          |

| 2.9        | Open Circuit Output of Half-Selected Switch<br>Core                                        | 25          |

| 2.10       | Idealized Voltage Outputs of Switch Cores As<br>a Function of Time for Various Excitations | 28          |

| 2.11       | Open Circuit Outputs of Fully Selected Switch<br>Core                                      | 29          |

| 2.12       | Equivalent Circuit of Fully Selected Switch<br>Core                                        | 32          |

| 2.13       | Simplified Switch Core Equivalent Circuits                                                 | 33          |

| Figure No. | Title                                                                                                         | Page No. |

|------------|---------------------------------------------------------------------------------------------------------------|----------|

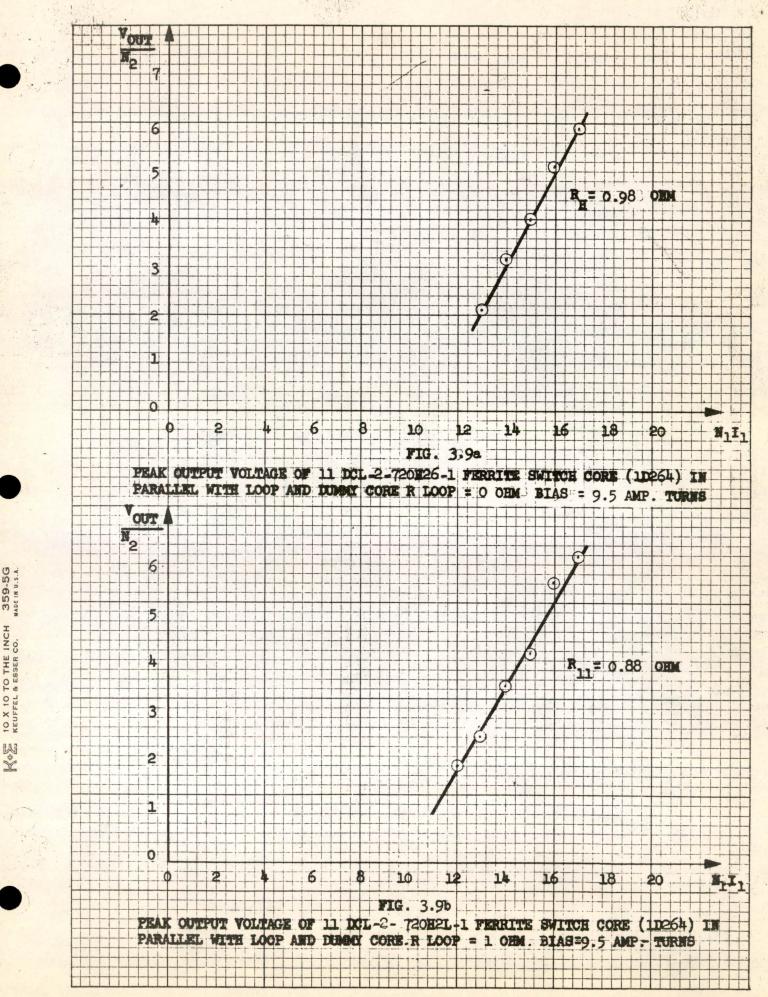

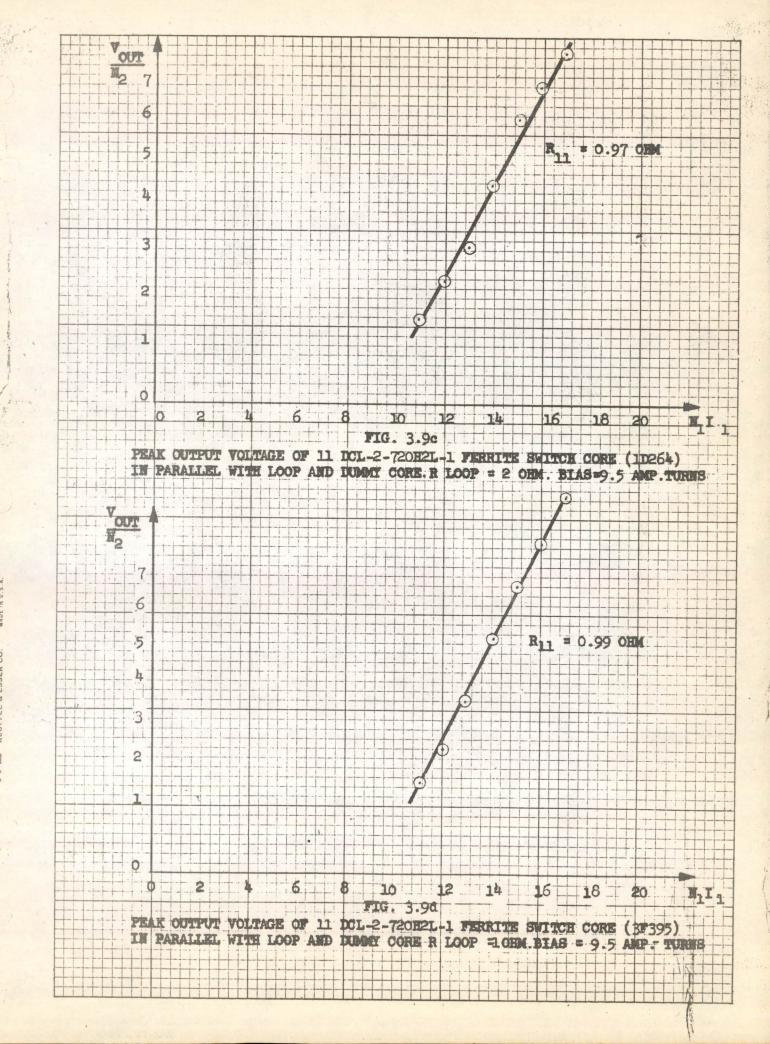

| 2.14       | Peak Open Circuit Voltage Output of<br>11DCL-2-720H2L-1 Ferrite Switch Core<br>(Size 1D264) Versus Excitation | 34       |

| 2.15       | Peak Open Circuit Voltage Output of<br>11DCL-2-720H2L-1 Ferrite Switch Core<br>(Size 3F395) Versus Excitation | 35       |

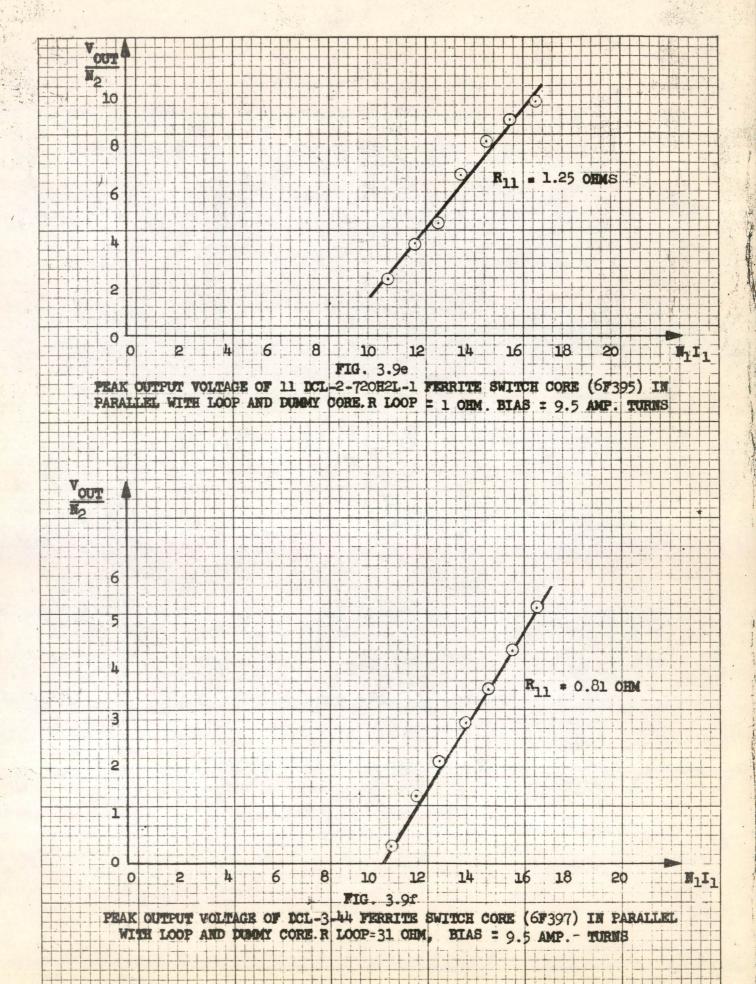

| 2.16       | Peak Open Circuit Voltage Output of<br>11DCL-2-720H2L-1 Ferrite Switch Core<br>(Size 6F395) Versus Excitation | 36       |

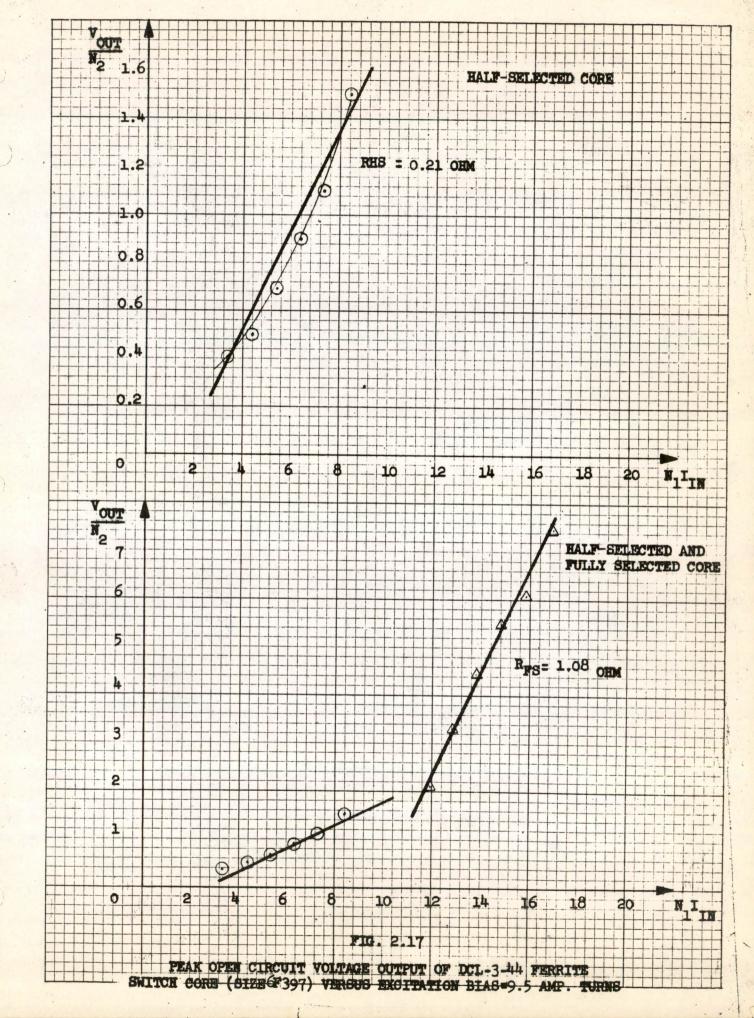

| 2.17       | Peak Open Circuit Voltage Output of<br>DCL-3-44 Ferrite Switch Core (Size 6F397)<br>Versus Excitation         | 37       |

| 2.18       | Open Circuit Output of Fully Selected Switch<br>Core for Various Lengths of On Time                           | 39       |

| 2.19       | Idealized Memory Core Hysteresis Loop                                                                         | 40       |

| 2.20       | Hysteresis Loop of More Realistic Memory<br>Core                                                              | 40       |

| 2.21       | Open Circuit Outputs (Half- and Full-Selects)<br>of Ferrite Memory Core for Various Excitations               | 41,42    |

| 2.22       | Peak Open Circuit Voltage Output of<br>11DCL-2-720H2L-1 Ferrite Memory Core<br>(Size 1F395) Versus Excitation | կկ       |

| 2.23       | Linearized Idealization of Open Circuit<br>Switch Core Characteristics                                        | 45       |

| 2.24       | Linearized Idealization of Memory Core<br>Characteristics                                                     | 45       |

| 2.25       | Voltage Outputs from Coincident Current<br>Type Selection                                                     | 48       |

| 3.1        | One Digit of the Three Core-Per-Bit Memory<br>Unit Simplified                                                 | 51       |

| 3.2        | Hysteresis Loops of the Cores in the Memory Unit                                                              | 51       |

| 3.3a       | Current Pulses Applied to Switch Core A, when<br>Fully Selected                                               | 52       |

| 3.3b       | Current Pulses Applied to Switch Core B, when<br>Fully Selected                                               | 52       |

V

| Figure No. | Title                                                                                                                                  | Page No.       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.4        | Loop Currents, and First Derivative of Loop<br>Currents, for Various Values of Loop Resistance                                         | 56             |

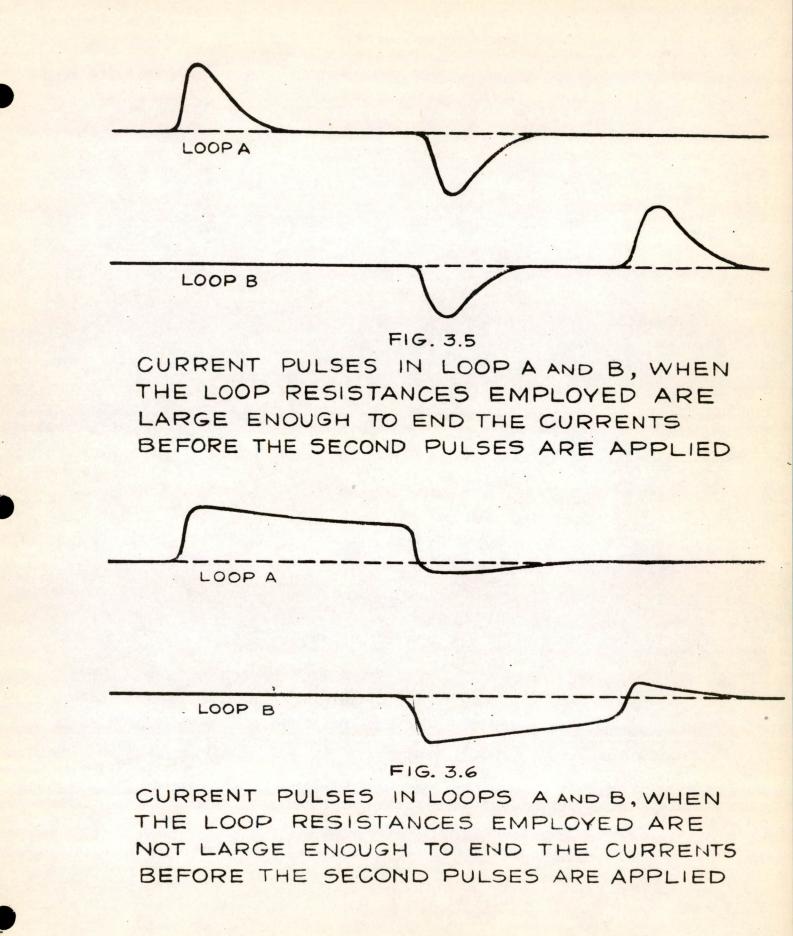

| 3.5        | Current Pulses in Loops, if Loop Resistances<br>are Large Enough                                                                       | 58             |

| 3.6        | Current Pulses in Loops, if Loop Resistances<br>are Too Small                                                                          | 58             |

| 3.7        | Hysteresis Loop Illustrating Possible Operation<br>of Memory Core When Attempting to Write a ONE,<br>if R <sub>Loop</sub> is Too Small | 60             |

| 3.8        | Fully Selected Output Voltages for Various Ex-<br>citing Currents of Switch Core Paralleled by<br>Coupling Loop                        | 62             |

| 3.9        | Peak Output Voltage of Various Switch Cores in<br>Parrallel with Coupling Loop and Dummy Memory<br>Core                                | 63<br>64<br>65 |

| 3.10       | Equivalent Circuit of Memory Unit Shown in Fig. 3.1                                                                                    | 69             |

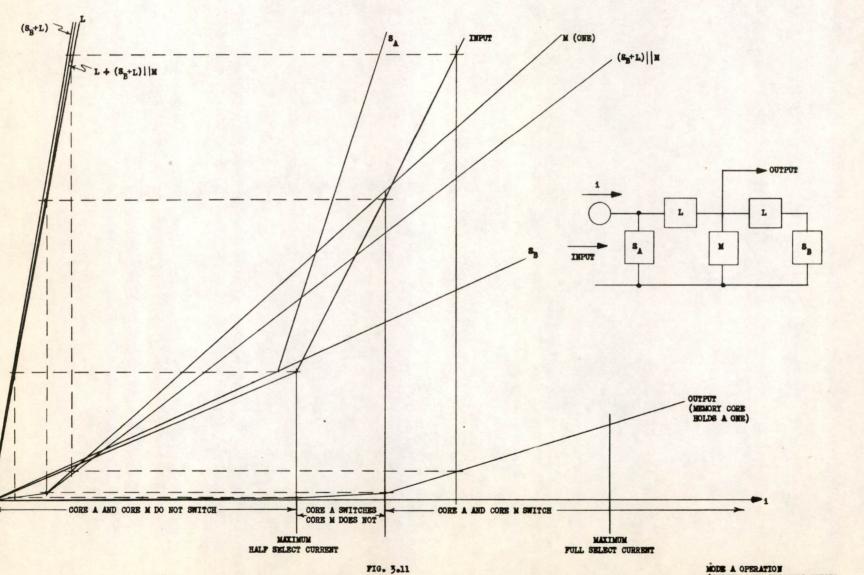

| 3.11       | Graphical Solution of Memory Core Output as a Function of Excitation                                                                   | 71             |

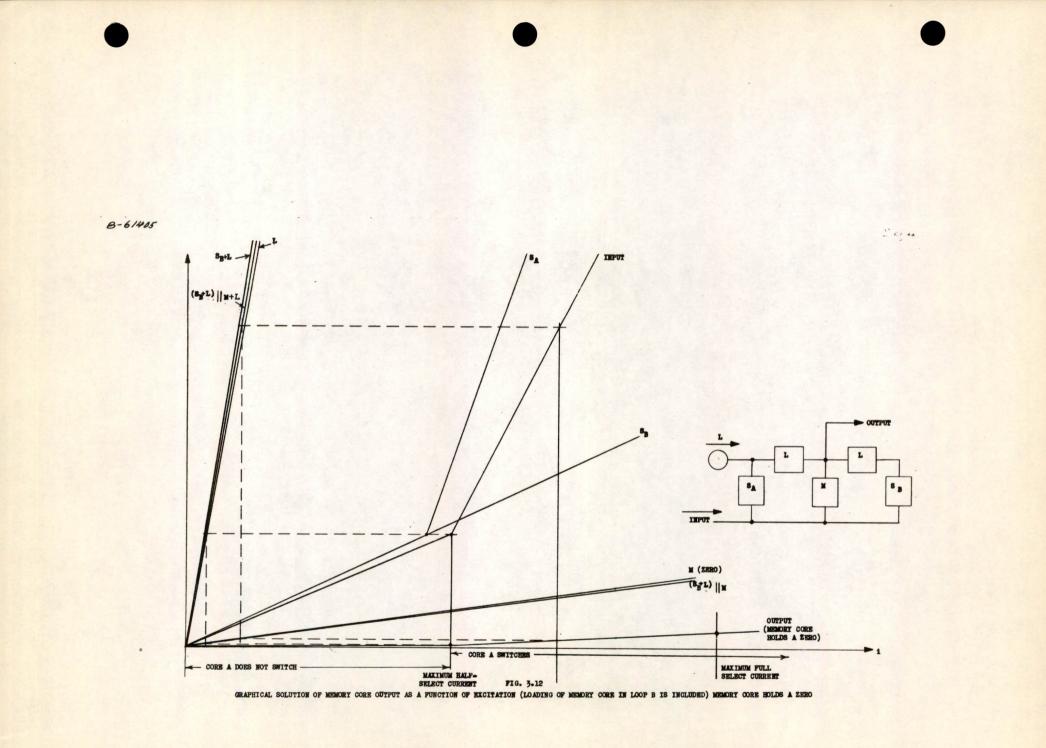

| 3.12       | Graphical Solution of Memory Core Output as a Function of Excitation                                                                   | 72             |

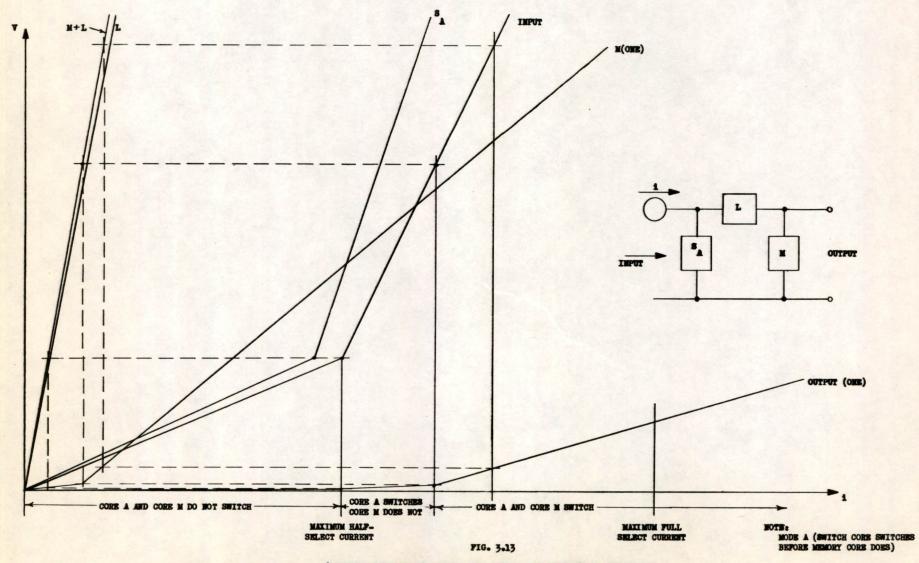

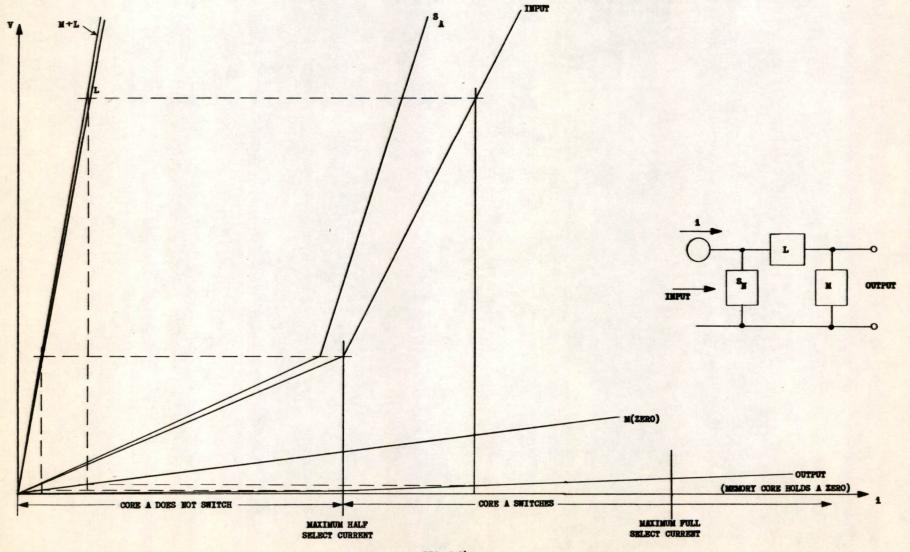

| 3.13       | Graphical Solution of Memory Core Output as a Function of Excitation                                                                   | 74             |

| 3.14       | Graphical Solution of Memory Core Output as a Function of Excitation                                                                   | 75             |

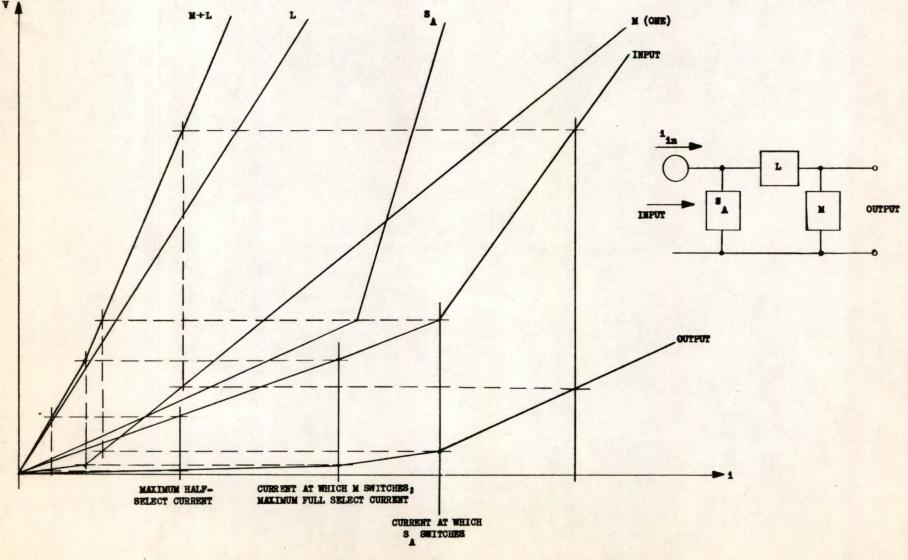

| 3.15       | Graphical Solution of Memory Core Output as a Function of Excitation                                                                   | 78             |

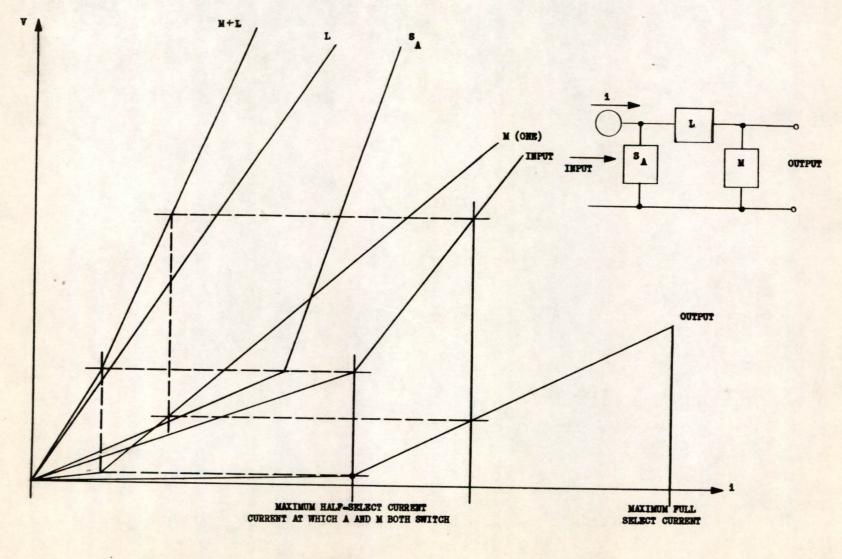

| 3.16       | Graphical Solution of Memory Core Output as a Function of Excitation                                                                   | 80             |

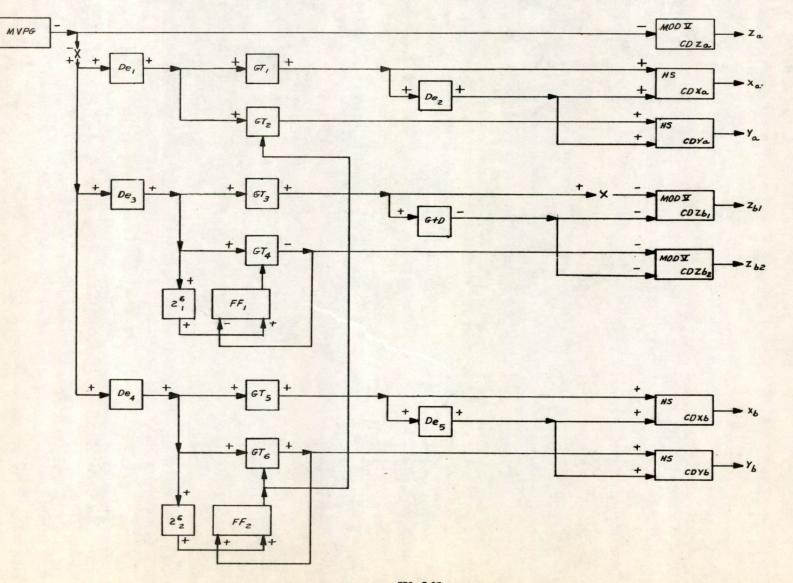

| 3.17       | Schematic Diagram of Equipment Used in Driving the One Bit Memory                                                                      | 82             |

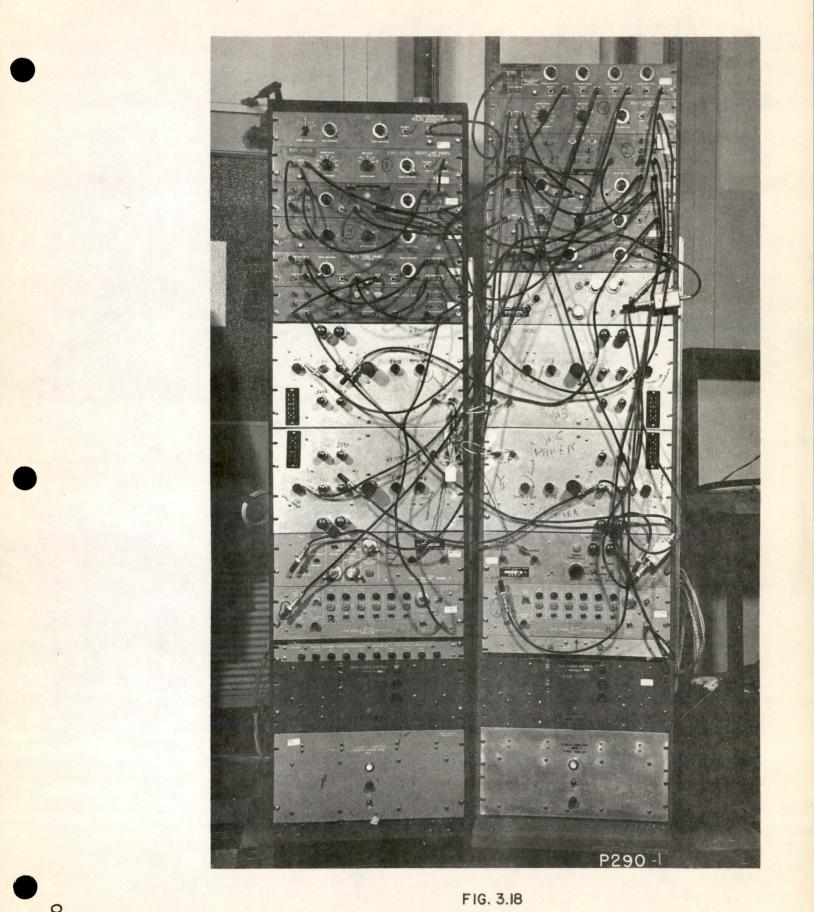

| 3.18       | Photograph of Equipment                                                                                                                | 83             |

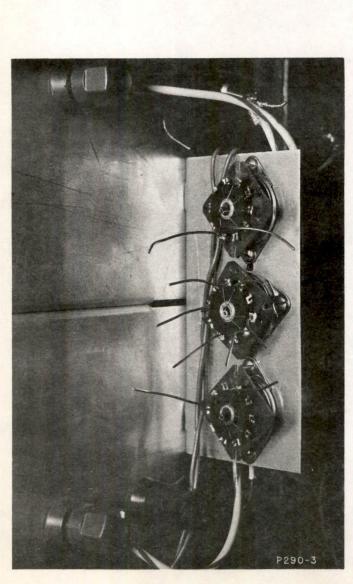

| 3.19       | Photographs of Memory Unit                                                                                                             | 84             |

vi

| Figure No. | Title                                                                                                       | Page No. |

|------------|-------------------------------------------------------------------------------------------------------------|----------|

| 3.20       | Memory Core Outputs                                                                                         | 88       |

| 3.21       | Memory Core Outputs                                                                                         | 89       |

| 3.22       | Memory Core Outputs                                                                                         | 90       |

| 3.23       | Memory Core Outputs                                                                                         | 91       |

| 3.24       | Memory Core Outputs                                                                                         | 92       |

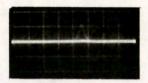

| 3.25       | Memory Core Outputs                                                                                         | 93       |

| 3.26       | Destruction of ZEROs by Half-Select Excitations                                                             | 96       |

| 3.27       | Read and Write ONE and ZERO in Mo-Perm Memory<br>Core                                                       | 99       |

| 3.28       | The Allignment of the Cores in the Basic Memory<br>Unit                                                     | 100      |

| 3.29       | Hysteresis Loops of the Cores Used in the Memory<br>Unit                                                    | 100      |

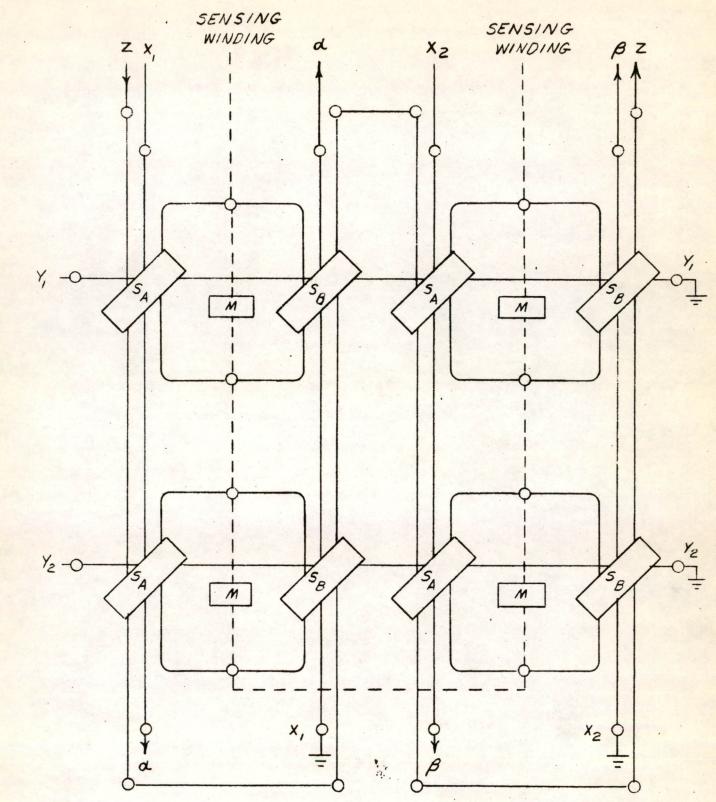

| 4.1        | Two-by-Two Memory "Plane" Demonstrating the<br>Wiring Technique to be Used in Building a 16 by<br>16 Plane. | 105      |

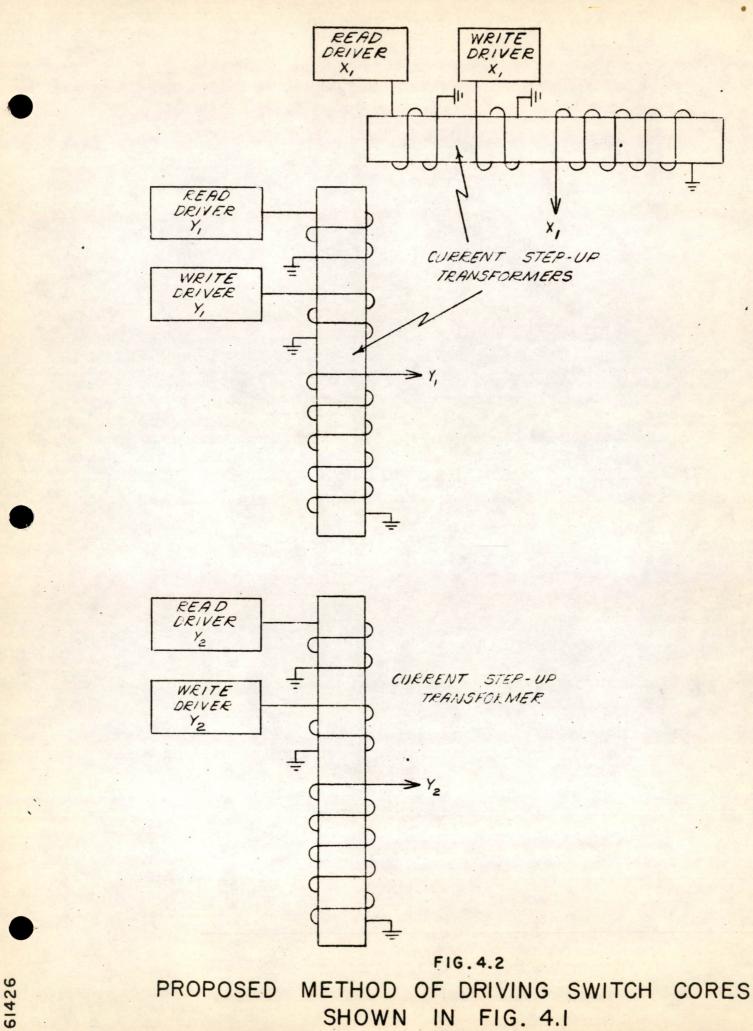

| 4.2        | Proposed Method of Driving Switch Cores Shown<br>in Fig. 4.1                                                | 107      |

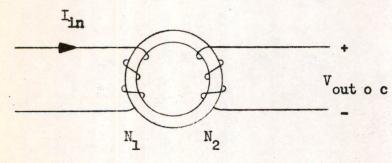

| A.l        | Open Circuit Test of Switch Core                                                                            | 112      |

| A. 2       | Short Circuit Test of Switch Core                                                                           | 112      |

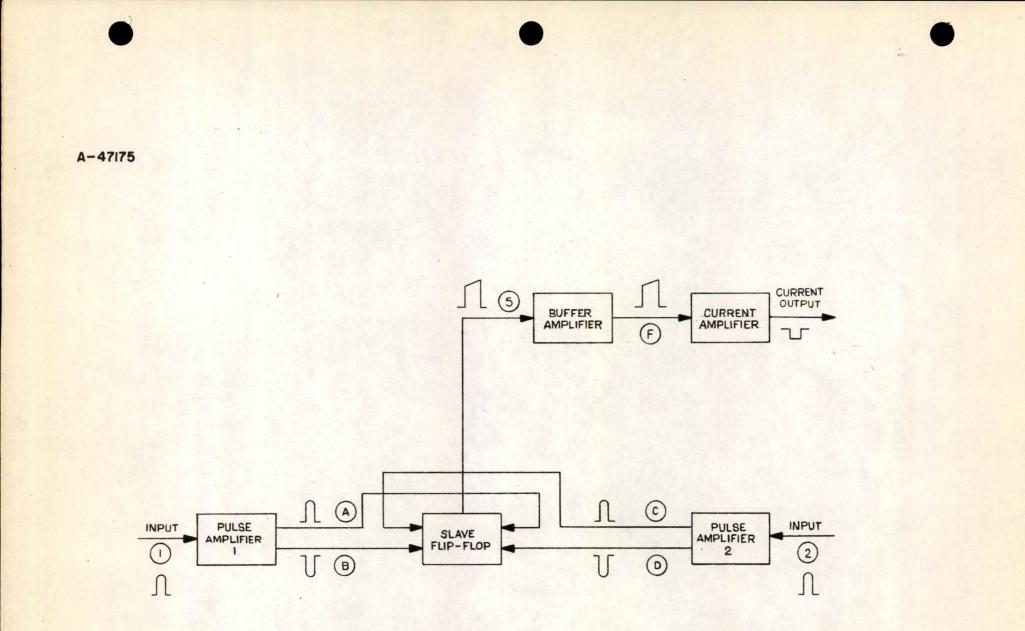

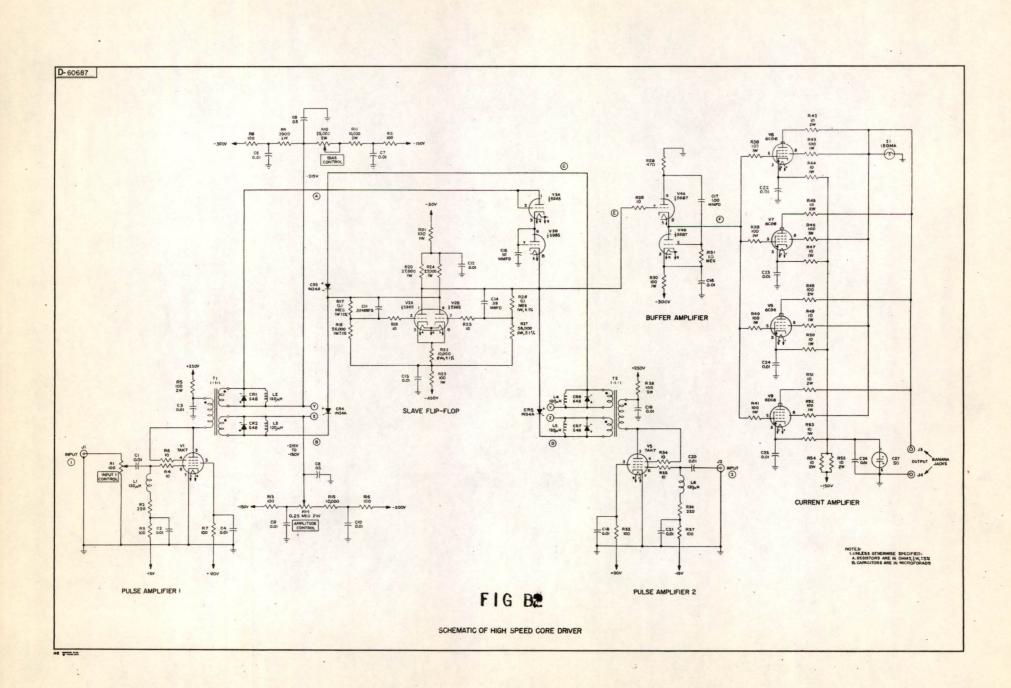

| B.1        | Block Diagram of High Speed Core Driver                                                                     | 119      |

| B.2        | Schematic of High Speed Core Driver                                                                         | 120      |

| B.3        | Input Voltages to Core Driver                                                                               | 121      |

| B.4        | Flip Flop Output                                                                                            | 122      |

| B.5        | Waveform at Plate of CR4                                                                                    | 122      |

| B.6        | Buffer Amplifier Output                                                                                     | 122      |

| B. 7       | Buffer Amplifier Plate Voltage                                                                              | 122      |

| B.8        | Best Core Driver Output Current                                                                             | 123      |

vii

| Figure No. | Title                                    | Page No. |

|------------|------------------------------------------|----------|

| B.9        | Distorted Core Driver Output Current     | 123      |

| B.10       | Distorted Core Driver Output Current     | 123      |

| B.11       | 0.1 Microsecond Output Current           | 123      |

| B.12       | 1.8 Microsecond Output Current           | 123      |

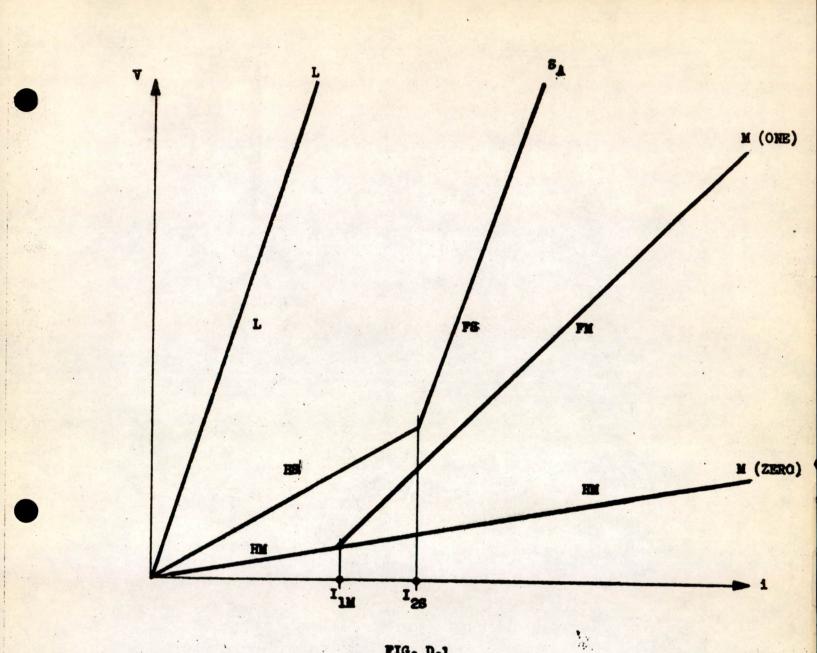

| D.1        | Characteristics of Cores and of Loop A   | 127      |

| D.2        | Connection of Elements Shown in Fig. D.1 | 127      |

#### CHAPTER 1

### INTRODUCTION

The memory function of a digital computer may be provided by a set of cores which can be magnetized in one of two possible directions. There is a correspondence between the identity of the core involved and an address which locates the core. The state of a core is made to correspond to the value (ONE or ZERO) of a digit in a number whose address corresponds to the core. To be useful in a computer, the core must be written into (magnetized) and read from (sensed) and it must hold (remember) a given state until it is changed. Since it is necessary to single out one core for a reading or writing operation, this location of the single core (selection) is an important problem. The present Whirlwind memory system combines the processes of selection and memory into one set of cores (one core per bit). The two processes have conflicting requirements and to divorce the two functions appears to be profitable. The function of this thesis is to analyze a scheme in which one set of cores is used for memory, and another set is used for selection.

In order to fully understand and appreciate the potential advantages offered by a memory with external selection, it is necessary to discuss the properties of the coincident current type memory system which is now in use, and which combines memory and selection in a single core per bit.

A. The Coincident-Current Memory

The operation of the coincident current, two-to-one selection

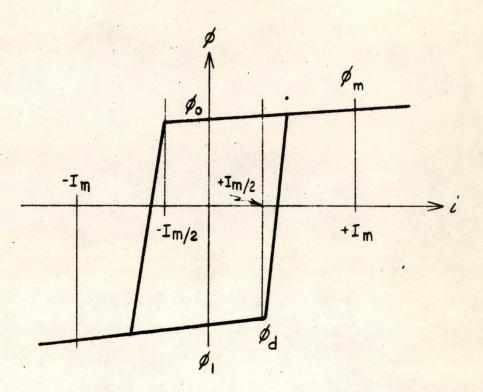

system is explained in Figure 1.1 and 1.21,2

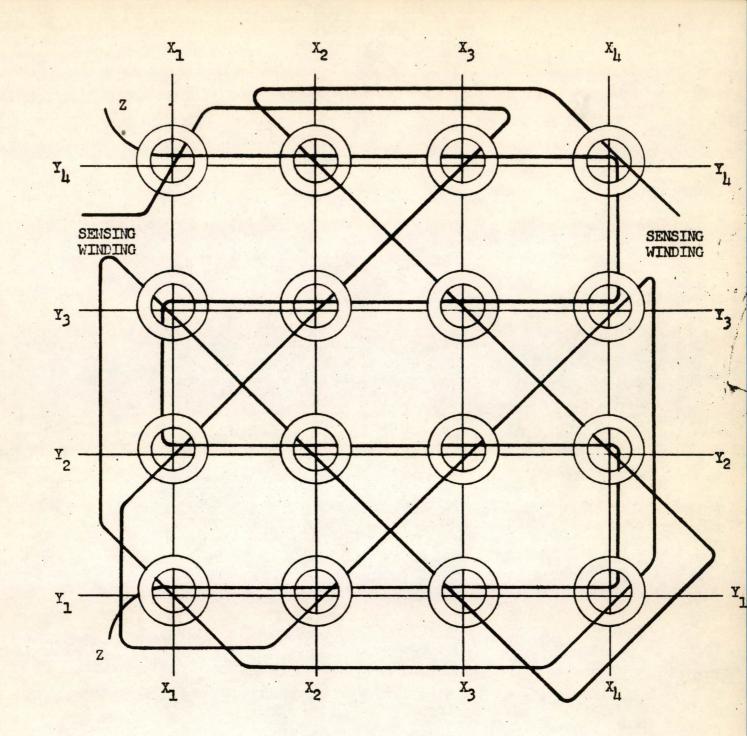

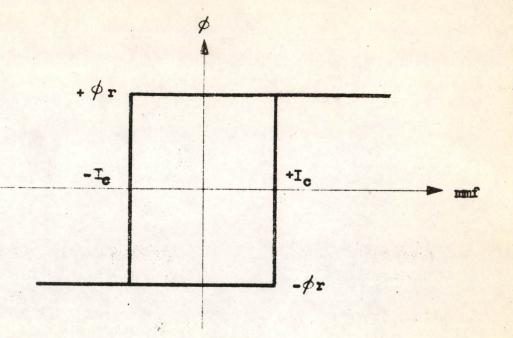

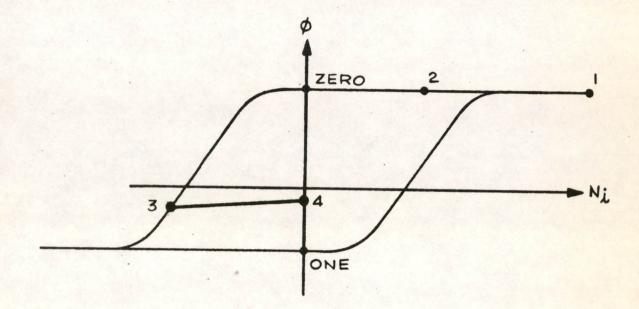

A core will rest in equilibrium either at  $\phi_0$  (arbitrarily called a ZERO) or at  $\phi_1$  (ONE). The point at which a core rests is determined by its recent history. At the intersection of each X and Y line (Figure 1.2), there is a magnetic core. Both a Z (inhibiting winding used for writing ZEROS) winding and a sensing winding (used for reading out of the memory) are threaded through each core.

The "read" operation passes +  $I_m/2$  through the selected X and Y coordinates, exciting the selected core by X +  $I_m$ . If the core holds a ONE, its flux state is reversed, and a large voltage is induced in the sensing winding. If, on the other hand, the core holds a ZERO, there is a relatively small change of flux in the core, and little voltage is induced, provided that the ratio  $\phi_0/\phi_m = 1$  (Figure 1.1). The read operation is destructive; that is, when reading has been finished, the core holds a ZERO, regardless of its original contents.

A number of cores lie on either the selected X coordinate or the selected Y coordinate. These cores are excited by  $+I_m/2$  (that is, they are half selected). At the time of the read operation, the information held by these cores is of no interest; furthermore the information that they hold should not be destroyed. For these reasons, the halfselected cores should not even be partially switched. As a consequence (referring to Figure 1.1), the ratio  $\phi_d/\phi_1$  must be close to unity.

-2-

Numbered references refer to correspondingly numbered references in the Bibliography.

1

FIG. 1.1

RECTANGULAR HYSTERESIS LOOP OF FERROMAGNETIC MEMORY CORE

FIG. 1.2

A FOUR-BY-FOUR PLANE OF FERROMAGNETIC MEMORY CORES

61429

These, then, are the requirements for a core in the coincident current magnetic memory - the ratios  $\phi_0/\phi_m$  and  $\phi_d/\phi_1$  must each be close to one. Because of symmetry,  $\phi_1 = -\phi_0$ . Therefore, these conditions may be combined and restated:  $|\phi_d/\phi_m|$  must be close to unity if the memory is to operate (1) with a minimum of output signals from half-selected cores and from the selected core (if it holds a ZERO); and (2) with a certainty that the information is not being destroyed. The ratio  $|\phi_d/\phi_m|$  is called the squareness ratio,<sup>3,4</sup> and it is generally somewhat less than unity.

Writing is accomplished in one of the following manners: To write a ONE, pass currents of  $-I_m/2$  down the chosen X and Y coordinates.

To write a ZERO, pass currents of  $-I_m/2$  down the chosen X and Y coordinates, and a current of  $+I_m/2$  through the Z (inhibiting) winding.

Block diagrams of operation of a memory may be found in the memorandum "Description of Memory Test Setup Vl."<sup>5</sup>

The core performs two functions in the coincident-current magnetic memory just described: primarily it stores information, but its rectangular hysteresis loop also provides the nonlinearity which is required for selection - that is, discrimination between excitations of  $I_m/2$  and  $I_m$ . Because the core must be used for selection, it must have a rectangular hysteresis loop with  $|\phi_d/\phi_m| \cong 1$ , and the magnitudes of the switching currents are severely limited because  $I_m/2$  must not even partially switch a core.

-5-

For a given switching core, the change of flux is independent of the switching time,  $\Upsilon$ , and the voltage induced in the sensing winding is inversely proportional to  $\Upsilon$ . Thus, shortening  $\Upsilon$  increases the output voltage and also increases the speed of the memory. It has been found <sup>4</sup> that  $\Upsilon$  is inversely proportional to the net exciting current (the net current is  $I_{net} = i - I_m$  and  $H_{net} \Upsilon = S_w$ , a constant of the core material). The total exciting current may not under any circumstances exceed  $I_m$ because of the coincident-current restrictions. This, of course, immediately imposes an upper limit to the switching speed of the cores.

There are two methods that can be used to descrease T. One is to decrease  $S_w$ . This is essentially a problem of trying to improve the magnetic materials of which the cores are made. It has been found that  $S_w$  of metals is generally lower than that of the ferrites. But the coercive force of the metals is considerably lower than that of the ferrites, and so the metals switch more slowly than the ferrites, under the restrictions of the coincident-current memory. A second method is to increase  $H_{net}$ . For coincident current operation this requires a material with very high coercive force.

# B. The Memory With External Selection

A system that does not use the memory cores for selection would avoid the restrictions on exciting current, which could be made very large, thereby significantly reducing the switching time, and it would reduce the rectangularity requirements on the hysteresis loops of the cores to some extent. Such systems have been proposed independently by J. Raffel<sup>6</sup> and Dr. R. Slutz<sup>7</sup>. The system that will be considered in this report is the

-6-

one introduced by the former.

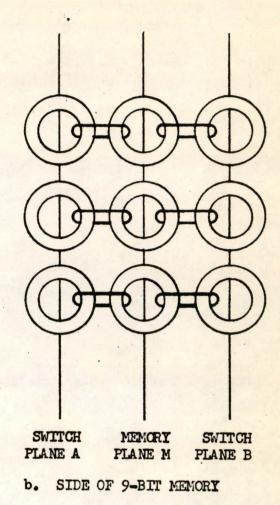

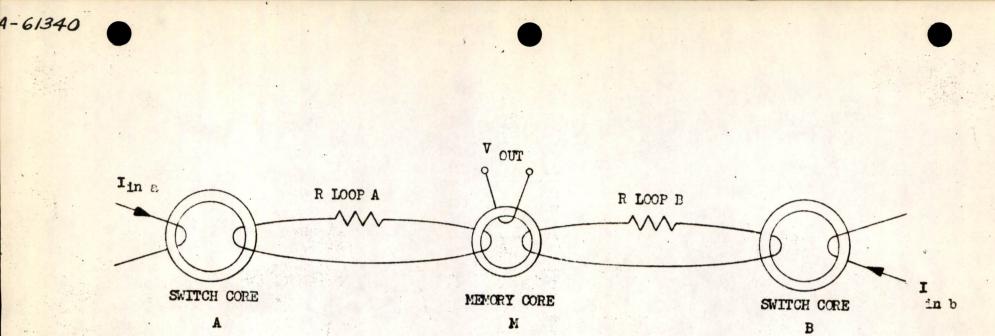

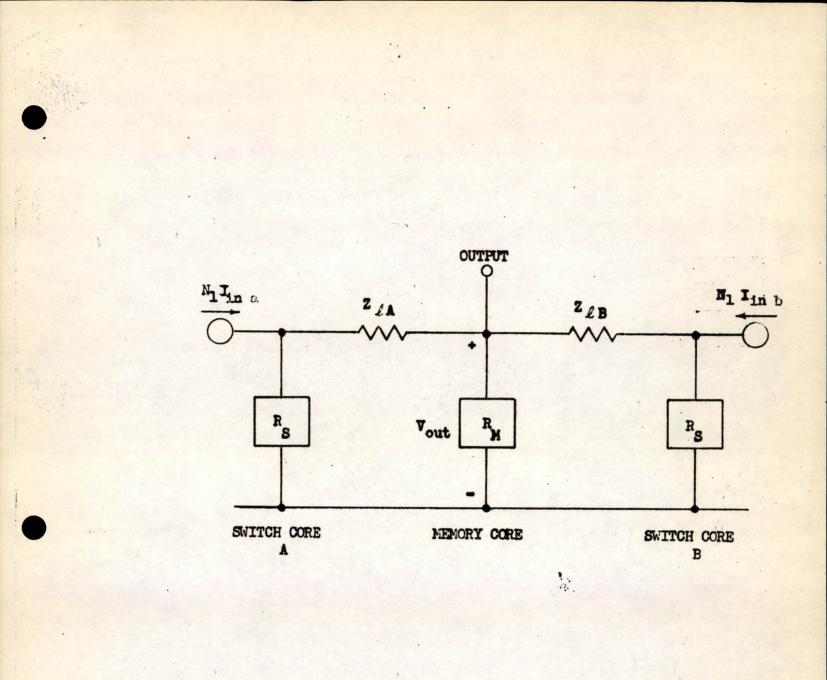

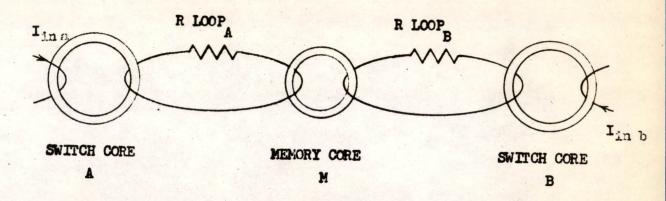

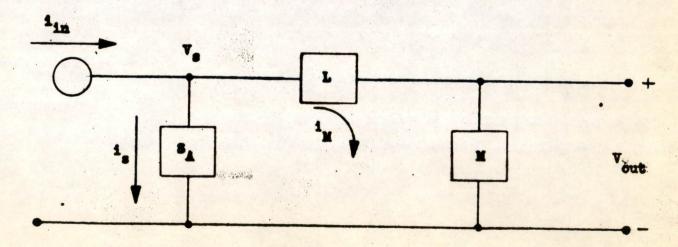

In this memory system, switch cores A and B (Figure 3.1) are used for selection. Memory core M is used solely for the retention of information. This system requires three cores for each bit of information as compared to one core in the present memory.

The principal characteristics that are essential are nonlinearity in the switch cores and remanence in the memory core.

Consider the operation of the 9-core (3x3) memory plane flanked by two 9-core switch planes (Figure 1.3).

The cores of Switch Plane A are for the read operation, and the cores of Switch Plane B are for writing. The Z-winding (Figure 1.3a) carries the bias current  $I_{Za}$  in plane A, and  $I_{Zbl}$  in plane B.

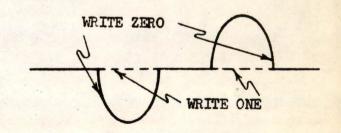

The read operation sends currents  $l_{in} (= I_{xa} = I_{ya})$  along the selected X and Y coordinates. The selected switch core in the A plane is switched from  $Z_a$  to  $Z_a + X_a + Y_a$  (Figure 3.2). When the excitation of lines X and Y is removed, switch core A reverts to  $Z_a$ . The output of core A (Figure 1.4) is coupled to the memory core, M, and the information is read out; at the completion of the read cycle, the selected memory core holds a ONE.

If a ONE is to be written no further excitation is necessary and switch core B is not excited during the write cycle.

If a ZERO is to be written,  $I_{in} (= I_{xb} = I_{yb})$  is passed along the selected X and Y coordinates in switch plane B. The output of core B (Figure 1.5), produces first a negative and then a positive pulse. The negative pulse merely moves core M (which is already in the ONE position)

a. SWITCH CORE PLANE (EITHER A OR B) TOP VIEW

FIG. 1.3

NINE BIT MEMORY "FLAME", CONSISTING OF 9 MELORY CORES AND 18 SWITCH CORES

FIG. 1.4 • READ OUTPUT OF COFE A

FIG. 1.5 WRITE OUTPUT OF CORE B

9-61430

towards saturation. The positive pulse switches the memory core to the ZERO state, and leaves it there.

The advantages that may be derived from the memory unit just described are listed below:

- 1. Speed. The switch cores are not required to retain information. Thus, it is permissible to bias these cores, and drive them very heavily when they are fully selected. They will switch rapidly and their output voltages will be large. The large voltages are used to drive the memory cores, and consequently, the memory cores are also rapidly switched. Complete read and write cycles were finished successfully in less than 0.5 microsecond.

- 2. Large Signals. The high switching speeds discussed above lead directly to the fact that the output voltages are very large. Because of this, the problem of amplifying the signals is greatly simplified. ONES were generally greater than two volts high, when a standard memory core was used as the storage element.

- 3. Low Noise Levels. The memory system using external selection cascades two nonlinear elements. The noise outputs that result from partially selected switch cores are found to be extremely small compared to full select outputs. The ratio of a fully selected ONE to a half selected output is considerably larger in the system using external selection than is the same ratio in the coincident current memory.

-9-

They were several hundred to one. The ONE to ZERO ratios were about the same in the two systems -- about 20 or 30 to 1.

- 4. Relaxation of Requirements on Core Characteristics. The cores are not as critical in a system using external selection as they are in the coincident current scheme. The essential characteristics are a nonlinear switch core, and a memory core with remanence.

- 5. No Destruction of Information. The noise outputs from partially selected switch cores are extremely small, and so there should be no tendency to destroy information stored in the memory cores.

The memory using external selection has several drawbacks, some of which may be extremely serious. All of the disadvantages are listed here:

- Three cores are required per bit of information. The coincident current memory system uses only one core per bit.

Construction Difficulties. The coincident current memory is laid out in a very simple plane (Figure 1.2). It is not possible to construct the memory using three cores in this manner; the difficulty may be appreciated by imagining an attempt to build the memory as shown in Figure 1.3. Other methods of putting the memory together must be conceived.

- 3. The Driving Problem. Large driving currents are required, and these currents must rise very rapidly so that the cores are not switched during the current rise time. The induc-

-10-

tance of partially selected switch cores, plus the inductance of the driving lines, plus the back voltages of fully selected switch cores present a load that will make it very difficult for the source output to rise rapidly to a large value of current. There are several ways in which to reduce the magnitude of this problem. The memory should not be large. A small sized memory will lower the inductance that must be driven. The switch cores should be as small as possible (memory core size) in order to reduce the back voltage induced in a switched core.

- 4. Memory Core Size. If, as indicated above, the switch cores are to be of standard memory core size, then the memory cores must be far smaller than the standard memory core. The reason is that it has been found that the switch core must be five or six times larger than the memory core in order to successfully operate the three core memory. It is not possible to make cores physically smaller than the standard memory core size, and so some other method of reducing the memory core must be introduced. It should be noted that none of the problems just discussed have been successfully solved yet.

- 5. Core Heating. The memory should be driven heavily and a possible result is that the cores will overheat, and their characteristics deteriorate.

-11-

The purpose of this thesis is to analyze, test, and evaluate the memory system just described.

Chapter 2 gives an analysis of the switch and memory cores to be used in the three-core-per-bit memory. The characteristics of these cores are approximated by linearized equivalent circuits which greatly aid the solution of some problems encountered in the memory unit.

Chapter 3 shows a detailed account of the characteristics of the cell comprised of the switch cores and the loop of wire coupling them to the memory core. The results expected from the linearized memory unit are given graphically and algebraically for various operating conditions. Finally, the experimental results obtained using various combinations of parameters in the memory unit are described. Chapter 4 gives the conclusions and the difficulties that may be expected in attempting to put the results of Chapter 3 to use in a practical system.

The appendices contain the derivations of some of the equations encountered in the body of the thesis. One appendix is devoted to a description of the high speed core driver that was developed in order to carry out the tests performed.

-12-

## CHAPTER 2

## THE NATURE OF THE SWITCH AND MEMORY CORES

The characteristics of the cores needed for both of the memory systems described in Chapter 1 will be discussed in this chapter.

The properties of the switch cores to be used in the memory with external selection are presented in Section A. Section B contains a discussion of the memory core, and an algebraic solution of the coincident current memory core outputs. In Chapter 3, these results will be compared to a similar set of equations derived for the memory unit using three cores per bit.

### A. The Switch Core

Much of the material to be presented here concerning the switch core has been known for some time.<sup>6,8</sup> A brief summary of these results and a method of regarding the switch core which leads to an easy analysis of the three-core memory will be given.

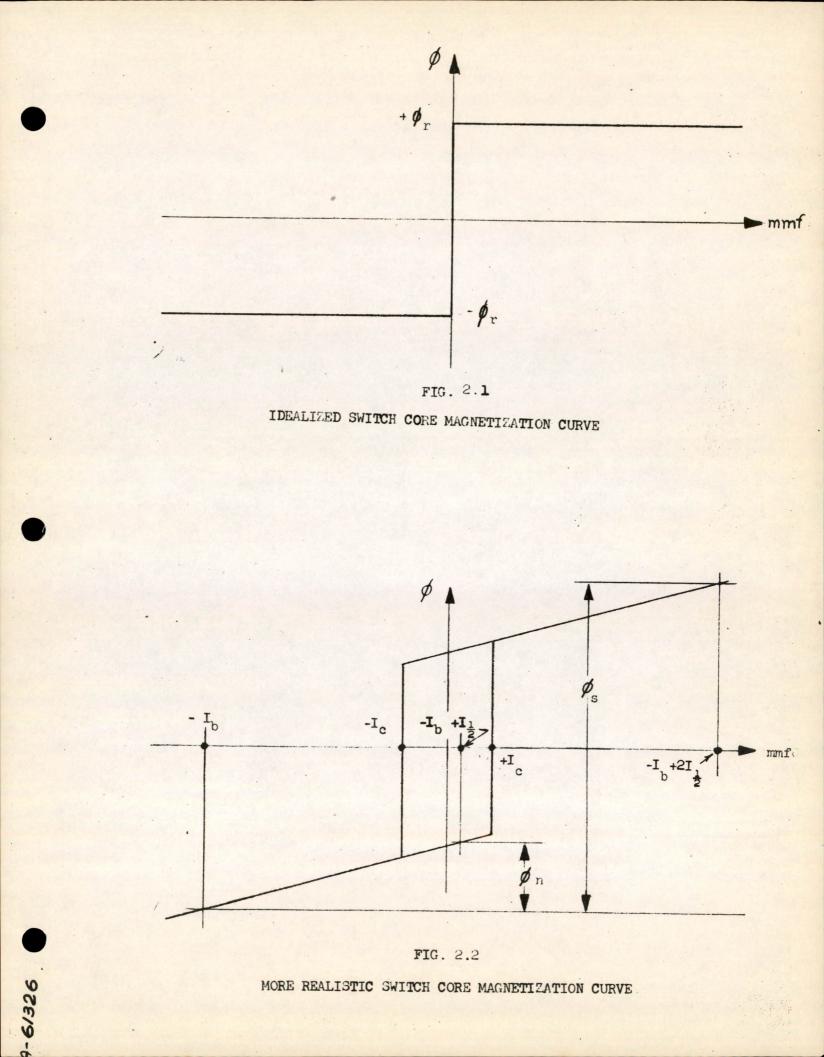

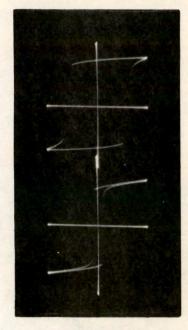

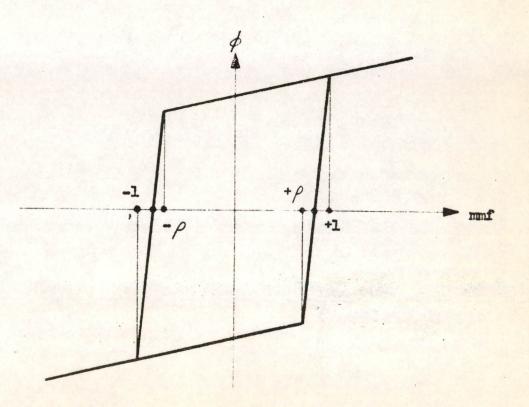

The ideal switch core has the magnetization curve shown in Fig. 2.1. A more realistic approximation is shown in Fig. 2.2. The hysteresis loops of the actual switch cores used for this thesis are shown in Fig. 2.3. It is noted that the pictures shown in Fig. 2.2 and 2.3 are essentially the same. The ideal core differs from the actual cores in two immediately evident manners; (1) the actual core has a hysteresis loop, and (2) the real cores do not saturate as well as the ideal core does.

The first difference is of little or no consequence here. The operation of the switch core is not greatly impaired by the fact that it has a finite coercive force.

-13-

MORE REALISTIC SWITCH CORE MAGNETIZATION CURVE

c- DCL-3-44 SIZE 1F397

B<sub>SATURATION</sub> = 3.2 MAXWELLS H<sub>c</sub> SATURATION = 1.8 AMP-TURNS SQUARENESS RATIO = 0.030

d- MOLYBDENUM PERMALLOY SIZE:  $\frac{1}{6}$  MIL  $x\frac{3}{4}$  DIAMETER  $x\frac{1}{5}$  WIDE x 20 WRAPS B = 1.68 MAXWELLS H<sub>c</sub> SATURATION = 0.36 AMP-TURNS SQUARENESS RATIO = 0.835

NOTE:

A-61332

TOP PICTURE SHOWS MAXIMUM SQUARENESS LOOP. BOTTOM PICTURE SHOWS SATURATION LOOP.

FIG. 2.3

ACTUAL CORE MAGNETIZATION CURVES

a- 11DCL-2-720H2L-1 SIZE 1D264

BSATURATION 27.2 MAXWELLS H 2.35 AMP-TURNS SQUARENESS RATIO 0.815

b- 11DCL-2-720H2L-1 SIZE 1F395

BSATURATION 4.8 MAXWELLS H SATURATION 1.56 AMP-TURNS SQUARENESS RATIO 0.830

NOTE :

A-61333

TOP PICTURE SHOWS MAXIMUM SQUARENESS LOOP BOTTOM PICTURE SHOWS SATURATION LOOP

FIG. 2.3

ACTUAL CORE MAGNETIZATION CURVES

The second difference, however, is of no little importance. The manner in which these cores are operated requires that flux changes in the saturated region be as small as possible.

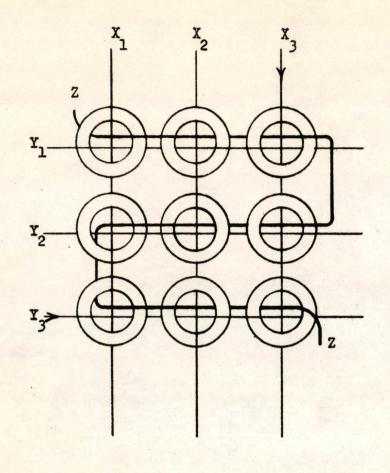

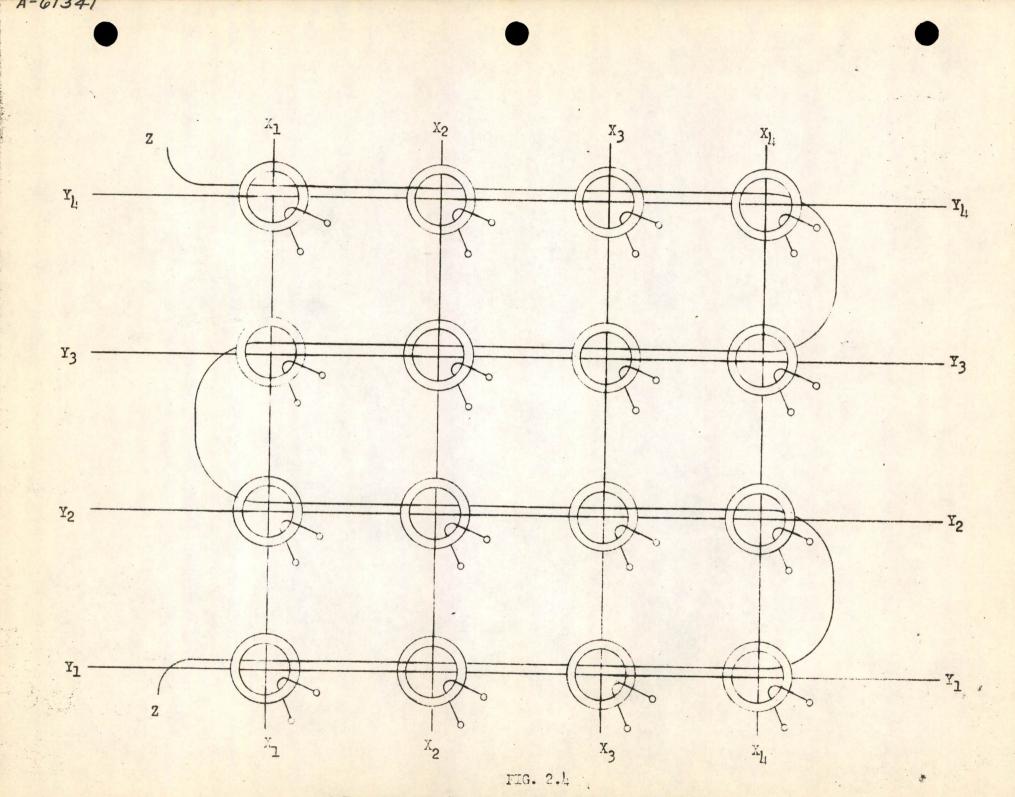

## 1. Operation of the Switch Core

It is possible to build a plane of switch cores. At first glance, it might appear as though the switch plane of Fig. 2.4 and the memory plane of Fig. 1.2 are the same. This is not the case, for there are two differences; (1) the operation of the switch plane is not at all like the operation of the memory plane because of the fact that the switch plane serves a different function, and (2) the sense winding must be removed, for each core has its own load, and each load is driven individually; the switch core is not selected and switched in order to determine its information content, but rather, this operation is carried out in order that the core output may do some work. Thus, a switch core plane is as shown in Fig. 2.4.

In the memory matrix, discussed in Chapter 1, the Z winding was used only when it was desired to write a ZERO into the selected core. The current passed through this "inhibit" winding was utilized in preventing a selected core from switching.

In the switch matrix (Fig. 2.4), however, the Z winding is not necessarily an inhibiting winding, but is always used for the purpose of biasing. (Actually, in switch planes which require inhibition there may be two Z-windings if it is desired to isolate the inhibition (which may or may not be applied) and the bias (which is always applied during the operating cycle).) There are two switch planes required for each digit in the three-core-per-bit memory, which is to be discussed. One plane does not require inhibiting pulses and the other does. Both, of course,

-17-

A FOUR-BY-ROUR PLANE OF FILL DIAGNETIC SWITCH CORES

----

require bias. The bias should consist of a steady direct current. During the course of this work, pulsed d.c. was used for bias because of the equipment available at Lincoln Laboratories. The operation of the memory unit is unaffected by the nature of the bias currents.

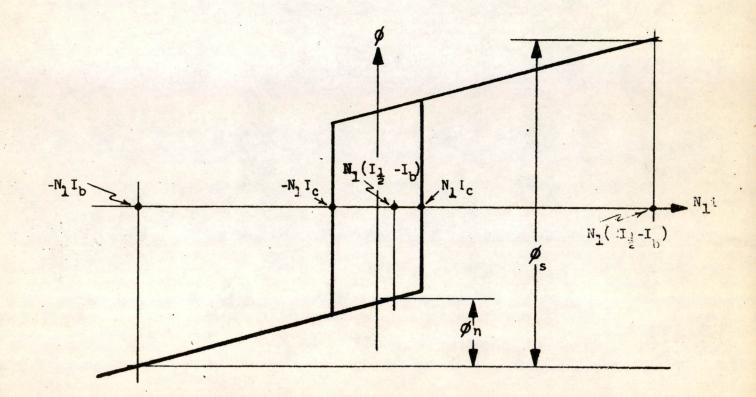

The core whose operation is to be described has the "Realistic Magnetization Curve" of Fig. 2.2. Bias is applied to all cores in the plane by means of the Z winding and it is  $I_Z$  amp-turns. The X and Y coordinate of the selected core are excited with  $\frac{I_{in}}{2} (=I_X = I_Y)$  amp-turns. The net driving mmf applied to the selected core is  $I_{in} - I_Z$ ; a number of cores are partially selected and the excitation that they receive is  $\frac{I_{in}}{2} - I_Z$ ; the remainder of the cores are unexcited and they only receive the bias current,  $I_Z$ .

The excitation experienced by the selected core must exceed the coercive force, and so

$$I_{in} - I_Z > I_C$$

(2.1)

The excitation driving the partially selected cores must not exceed the coercive force, and so

$$\frac{I_{in}}{2} - I_Z \stackrel{<}{=} I_C \tag{2.2}$$

In Chapter I, it was noted that when a core switches,

$$H_{net} \gamma = Sw$$

(2.3)

where  $H_{net}$  is the mmf corresponding (in the case under discussion) to a driving current of  $I_{in} - I_Z - I_C$  (the amount of current by which the coercive force is exceeded),  $\not$  is the switching time and Sw is a constant of the material.

As has been pointed out before, in order to switch a core of a given material as rapidly as possible, it is necessary to raise Hnet.

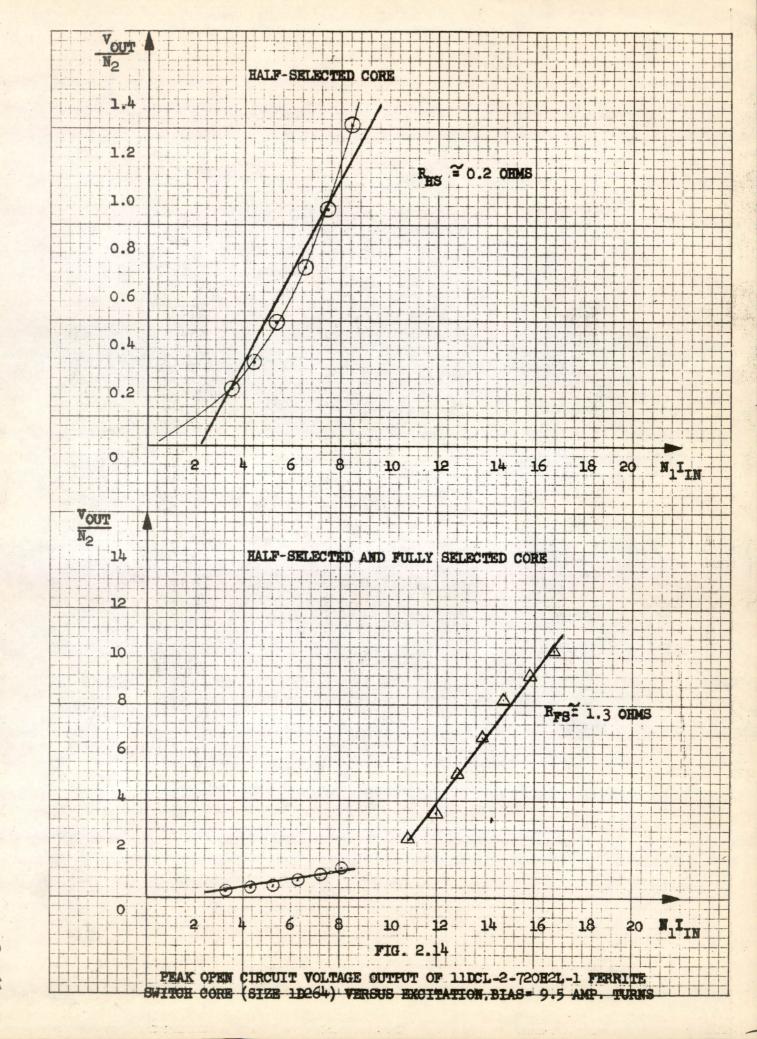

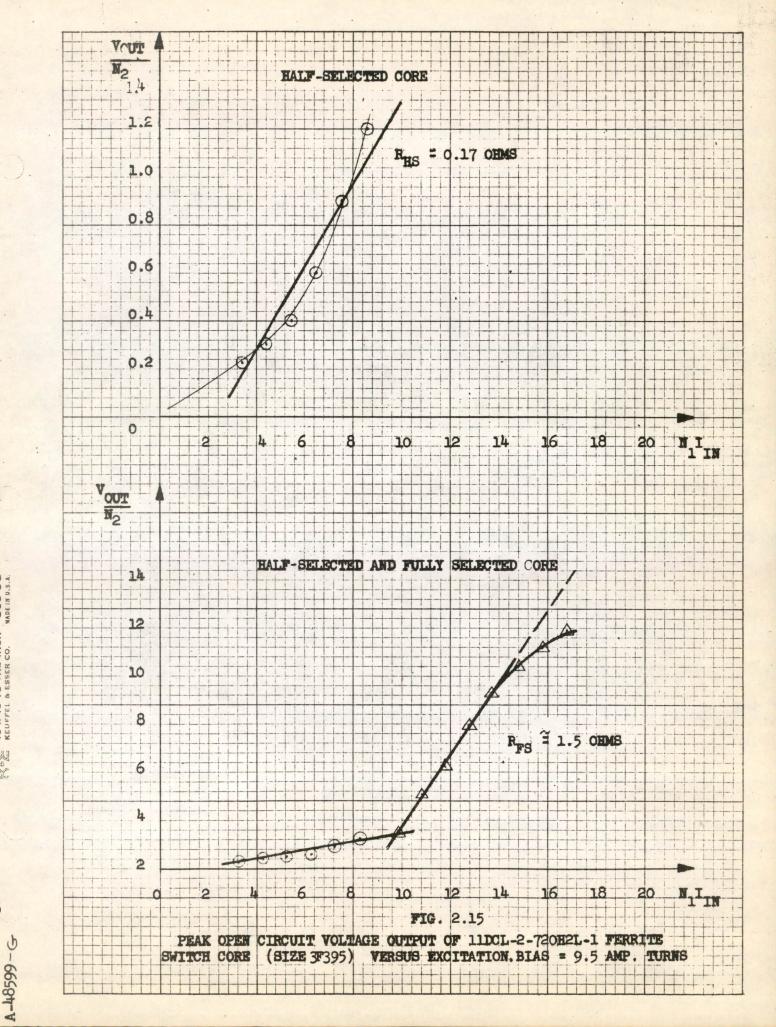

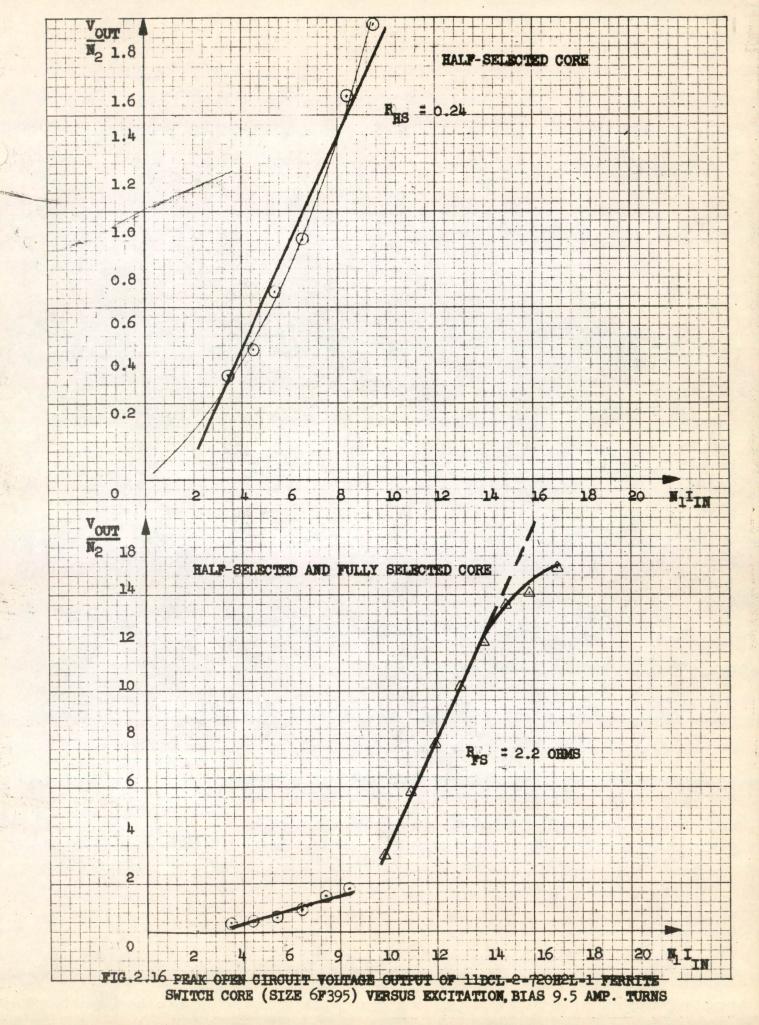

Assume, for convenience, that equation (2.2) is satisfied by the equal sign. Then the net current through a selected core is  $\frac{\Gamma_{in}}{2}$ , and the larger this current is, the faster the core will switch. Although it is true that the most favorable operation, as regards speed, is obtained by employing driving currents as large as possible and adjusting the bias so that equation (2.2) is satisfied, there is a practical difficulty encountered. The core drivers have finite rise times. If the driving current is made excessively large, the result is that the core switches during the rise of the current pulse. The remainder of the current is wasted. This result will be observed in Fig. 2.15 and 2.16, in which the peak open circuit output voltages of several switch cores are plotted as functions of the driving current. This point is discussed in Section A.2c of Chapter 2..

It must also be noted that there is a noise output received from half-selected cores. The greater  $\frac{I_{in}}{2}$  is, the greater the noise flux, one (Fig. 2.2) is. The relative increase in one is slight. The outputs of the partially selected cores could conceivably become large enough to do the job that only a fully selected core should do and this is undesirable. The conclusions that must be drawn, then, are that the allowable amount of excitation of the cores is limited by the rise time of the drivers, and by the desire to keep the noise outputs low.

2. Analysis of Switch Core Operation

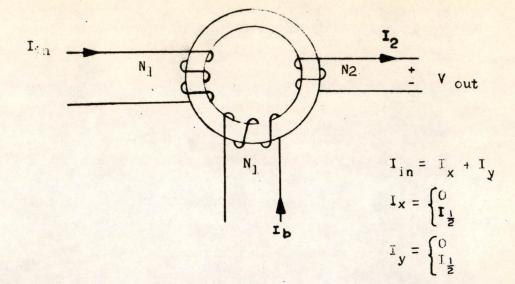

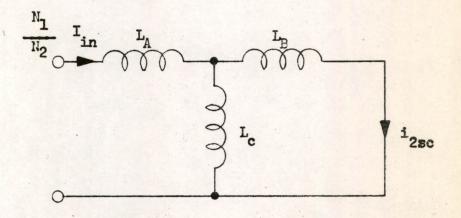

A single switch core is shown in Fig. 2.5. The X, Y and Z windings each have  $N_1$  turns (X and Y are shown as one winding) and the output winding (secondary) has  $N_2$  turns.

-20-

The hysteresis loop of this core is shown in Fig. 2.6. It is essentially the same as that of Fig. 2.2, but the variables have been changed.

### a. The Half Selected Switch Core

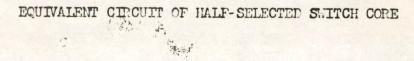

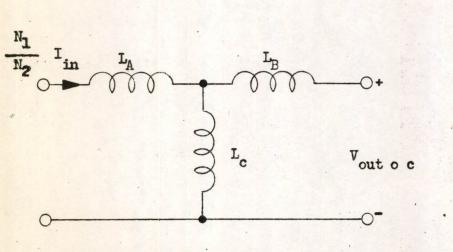

When the switch core is only half selected, it is driven from  $N_1I_2$  to  $N_1\left(\frac{I_{\text{in}}}{2} - I_2\right)$ , and it is not switched. The operating path is along a straight line in the  $\emptyset - N_1$  plane, and this corresponds to a linear inductance. (In an actual case, the departure from linearity is not great; Hughes<sup>8</sup> has shown that for the core used in his work that the relative change in inductance in going from  $N_1$  i = 0 to saturation is less than a ratio of 2:1.) An equivalent circuit is drawn in Fig. 2.7. The parameters are derived in Appendix A.

The rise time of the current output of the core driver that was developed for this thesis (Appendix B) is independent of the current amplitude. It is also found that this current rises from zero in very nearly linear fashion. These two facts are very useful in the analysis of the partially selected core because the voltage induced in an inductor is,

$$V_{\rm L} = L \frac{d1}{dt}$$

(2.4a)

In the light of the aforementioned current characteristics, equation (2.4) becomes,

$$V_{\rm L} = L \frac{\Delta i}{\Delta t} = L \frac{i}{T} = \frac{L}{T} i$$

(2.4b)

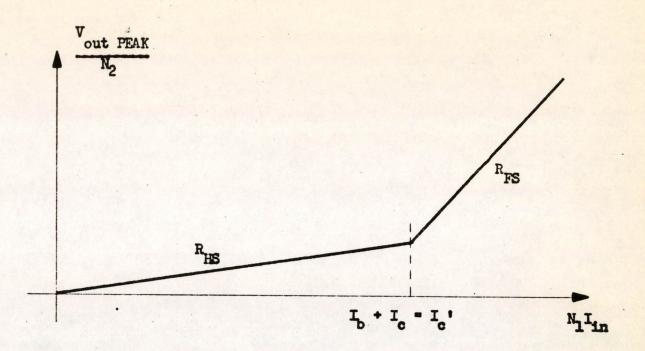

Equation (2.4b) is extremely useful as it stands, for L/T is a constant. This constant may be abbreviated by allowing L/T to equal  $R_{HS}$ . It is to be understood that  $R_{HS}$  is not a resistor. The symbol was chosen because the volt-ampere characteristic of a half-selected switch core is linear.

# SINCLE SWITCH CORE, WITH X AND Y DRIVING LINES COMBINED

FIG. 2.6 HYSTERESIS LOOP OF CORE SHOWN IN FIG 2.5

A-61327

Although it is a fallacy, it is convenient to think of  $R_{HS}$  as a pulsed resistance (that is, a resistor whose value is a function of time, but is not dependent upon the driving current). The usefulness of this assumption will be brought out later in this chapter, and also in Chapter 3.

Thus, the relationship between the real constants, L and T, and the Fictitions constant,  $R_{uc}$ , is

$$R_{\rm HS} = \frac{L}{T}$$

(2.5)

The net result of these maneuvers is that the equivalent circuit of Fig. 2.7 (which is valid for all time, provided that the core is never fully selected), may be replaced by the circuit shown in Fig. 2.8. The new equivalent circuit (Fig. 2.8) is valid only during the rise and fall of the input currents, and is useful only for obtaining the peak output voltages. However, it turns out that the only item of interest is the peak output voltage. Thus, Fig. 2.8 satisfies the present need.

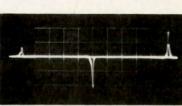

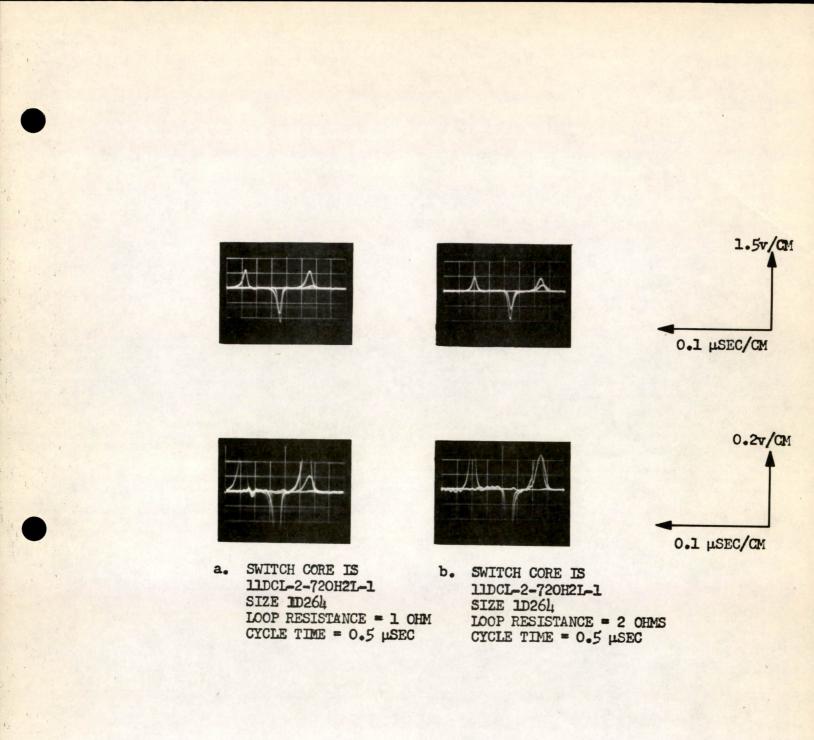

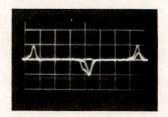

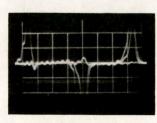

Half-selected switch core output voltages and the corresponding driving currents are shown in Fig. 2.9, for the switch consisting of 1D264, of the material 11DCL - 2 - 720H2L-1. The results are tabulated in Table I, for cores of various materials and sizes, and they are plotted in Fig. 2.14, 2.15, 2.16 and 2.17.

REVISED EQUIVALENT CIRCUIT OF HALF-SELECTED SWITCH CORE

44

4-61350

1/1

When it is

| • | DRIVING EXCITATION<br>(AMPERE-TURNS) | VOLTAGE<br>OUTPUT (VOLTS) |

|---|--------------------------------------|---------------------------|

|   | 8.5                                  | 1.35                      |

|   | 7•5                                  | 0.99                      |

|   | 6.5                                  | 0.76                      |

|   | 5•5                                  | 0.53                      |

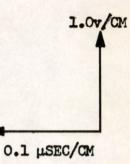

|   | 4.5                                  | 0.37<br>0.5v/cm           |

|   | 3.5                                  | 0.24<br>0.1 JUSEC/CM      |

|   | FIG. 2.                              | 9                         |

(11DCL-2-720H2L-1, SIZE 1D264) FOR VARIOUS EXCITATIONS BIAS = 9.5 AMP-TURNS. SIZES OF SECOND PULSES RECORDED IN VOLTS

### TABLE I

| Driving Current<br>(ampere turns)                                   | Peak Open Circu:<br>11 DCL<br>1D264 |       | ted Switch Cor<br>(bias =<br>720 H2L-1<br>6F395 | e Output Voltage<br>9.5 amp.turns)<br>DCL-3-44<br>6F397 |

|---------------------------------------------------------------------|-------------------------------------|-------|-------------------------------------------------|---------------------------------------------------------|

| (ampere ourns)                                                      | 10204                               | 55575 | 01393                                           | 01391                                                   |

| 3.5                                                                 | 0.24                                | 0.22  | 0.43                                            | 0.4                                                     |

| 4.5                                                                 | 0.37                                | 0.3   | 0.54                                            | 0.5                                                     |

| 5.5                                                                 | 0.53                                | 0.4   | 0.78                                            | 0.7                                                     |

| 6.5                                                                 | 0.76                                | 0.6   | 1.0                                             | 0.9                                                     |

| 7.5                                                                 | 0.99                                | 0.9   | 1.6                                             | 1.1                                                     |

| 8.5                                                                 | 1.35                                | 1.2   | 1.9                                             | 1.5                                                     |

| Peak Resistance<br>of Open Circuit,<br>Half Selected<br>Switch Core | 0.2                                 | 0.17  | 0.24                                            | 0.21                                                    |

#### b. The Fully Selected Switch Core

It has been pointed out that the relationship between the net field strength,  $H_{net}$ , and the switching time of the core,  $\gamma$ , is

$H_{net} \gamma = Sw$ (2.6)

where Sw is a constant of the core material.

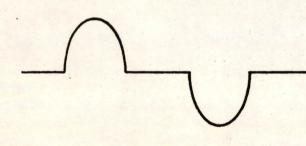

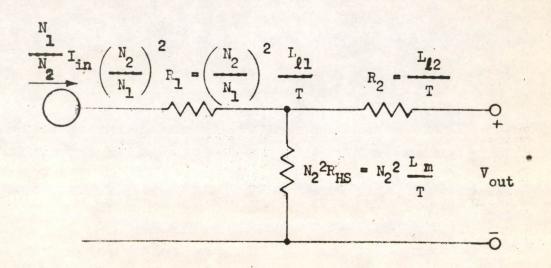

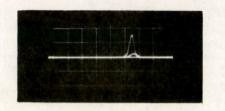

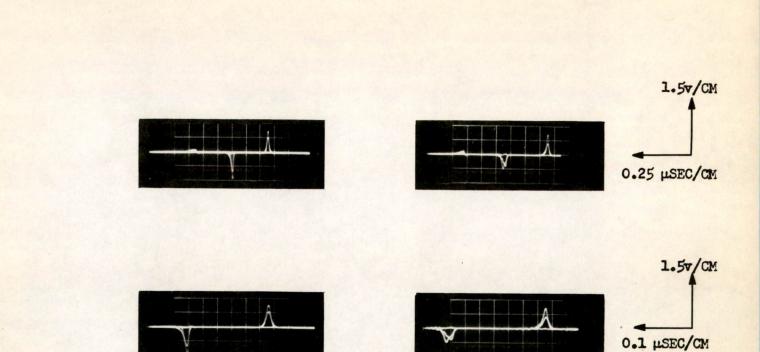

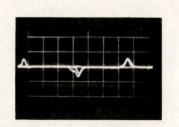

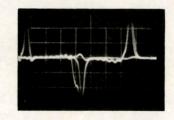

The core that is to be discussed is shown in Fig. 2.5 and its hysteresis loop is drawn in Fig. 2.6. If the core saturates reasonably well, the flux switched  $\emptyset_s$ , when the core is fully selected is virtually independent of the driving current. The shape of the voltage output pulse is generally independent of the driving current (provided that it is driven hard enough); it somewhat resembles a half sine wave. The expected output voltage waves, plotted against time, for various driving currents are shown in Fig. 2.10. Fig. 2.11 shows the actual output pulses of a llDCL-2-720H2L-1, size lD264 switch core. The results are tabulated in Table II, for this and other cores, and are plotted in Figs. 2.14, 2.15, 2.16, and 2.17

| TA | B | LE | I | Ι |

|----|---|----|---|---|

| -  | ~ | -  | - | - |

| Driving Current                                                      | Peak Open Circu<br>11 DCL<br>1D264 |      | elected, Switch (<br>(bias<br>720 H2L-1<br>6F395 | Core Output Voltage<br>= 9.5 amp. turns)<br>DCL-3-44<br>6F397 |

|----------------------------------------------------------------------|------------------------------------|------|--------------------------------------------------|---------------------------------------------------------------|

| (ampere turns)                                                       | 10204                              |      |                                                  | 05397                                                         |

| 10                                                                   |                                    | 1.5  | 3.4                                              |                                                               |

| 11                                                                   | 2.7 .                              | 3.3  | 6.0                                              |                                                               |

| 12                                                                   | 3.6                                | 4.3  | 8.0                                              | 2.2                                                           |

| 13                                                                   | 5.2                                | 6.0  | 10.4                                             | 3-4                                                           |

| 14                                                                   | 6.9                                | 7.6  | 12.2                                             | 4.5                                                           |

| 15                                                                   | 8.4                                | 8.6  | 13.8                                             | 5.6                                                           |

| 16                                                                   | 9.3                                | 9.2  | 14.2                                             | 6.1                                                           |

| 17                                                                   | 10.4                               | 10.0 | 15.2                                             | 7•5                                                           |

| Peak Resistance<br>of Open Circuit,<br>Fully Selected<br>Switch Core | 1•3                                | 1.5  | 2.2                                              | 1.1                                                           |

The area under each voltage time curve must equal the

switches flux,  $\phi_s$ . This requires that the product

$$\frac{V_{\text{out}}}{N_2} \gamma = a \phi_s \qquad (2.7)$$

where a is a constant of proportionately, and  $V_{out}$  is the peak output voltage.

FIG. 2.10

IDEALIZED VOLTAGE OUTPUTS OF SWITCH CORES AS A FUNCTION OF TIME FOR VARIOUS EXCITATIONS

-61335

|   | DRIVING EXCITATION<br>(AMPERE-TURNS) | VOLTAGE<br>OUTPUT<br>(VOLTS) |             |

|---|--------------------------------------|------------------------------|-------------|

|   | 17.0                                 | 10.4                         |             |

|   | 16.0                                 | 9.3                          |             |

|   | 15.0                                 | 8.4                          |             |

|   | 14.0                                 | 6.9                          |             |

|   | 13.0                                 | 5.2                          |             |

|   | 12.0                                 | 3.6                          |             |

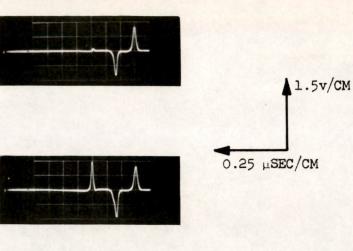

|   | 11.0                                 | 2.7                          | 8v/a        |

| v | 10.0                                 | DOES NOT<br>SWITCH           | O.1 µSEC/CM |

FIG. 2.11

8v/CM

OPEN CIRCUIT OUTPUTS OF FULLY SELECTED SWITCH CORES (11DCL-2-720H2L-1, SIZE 1D264) FOR VARIOUS EXCITATIONS BIAS = 9.5 AMP-TURNS SIZE OF FIRST PULSE RECORDED IN VOLTS

Furthermore, H<sub>net</sub> (= H drive - H coercive) is directly proportional to the net current, I net (= I drive - I coercive), driving the core. The equation used to relate H and i is

$$H = \frac{0.4 N_{1} i}{\bar{d}}$$

(2.8)

in which N<sub>1</sub> is the number of primary turns on the core and  $\bar{d} = \frac{0.D.-I.D.}{I_n(0.D./I.D.)}$ , where 0.D. is the outside diameter of the core, and I.D. is its inside diameter.

If equations (2.7) and (2.8) are substituted into

equation (2.6), the result is

$$V_{out} = \frac{\cdot \mu a}{\overline{d}} \frac{N_1 N_2}{\overline{d}} \frac{\vartheta_s}{sw} \qquad I_{net}$$

$$= \frac{\cdot \mu a}{\overline{d}} \frac{\vartheta_s}{sw} \qquad N_1 N_2 (I_{in} - I_Z - I_C)$$

$$= z N_1 N_2 (I_{in} - I_Z - I_C)$$

(2.9)

The constant z has the dimension ohms per turns squared. It is a property of the core; it is independent of the manner in which the core is used (so long as the core is switched) and of the number of turns wrapped on the core.

Equation (2.9) expresses the linear relationship between the peak open circuit secondary voltage,  $V_{out}$  and the drive current,  $I_{in}$ , when the core is switched.

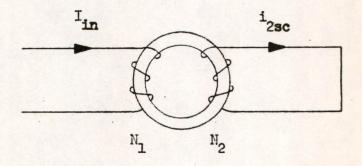

If this output of the core of Fig. 2.5 is short-circuited, then the net ampere turns through it, when switching, must be  $N_1I_C$ . This requires that

$N_1(I_{in} - I_Z) - N_2I_2 = N_1I_C$

$$I_2 = \frac{N_1}{N_2} (I_{in} - I_Z - I_C)$$

(2.10)

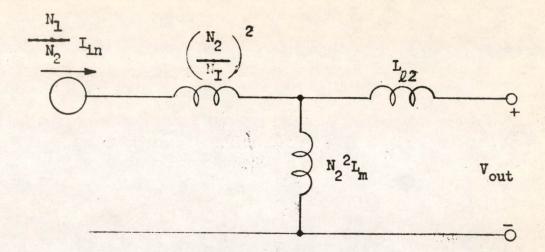

where  $I_2$  is the short circuit current flowing in the secondary. The vinin's Theorem may be applied to equation (2.9) and (2.10) to leading to the output impedance of the core,

-31-

$$Z_{\text{out}} = \frac{V_{\text{out}}}{I_2} = N_2^2 z \qquad (2.11)$$

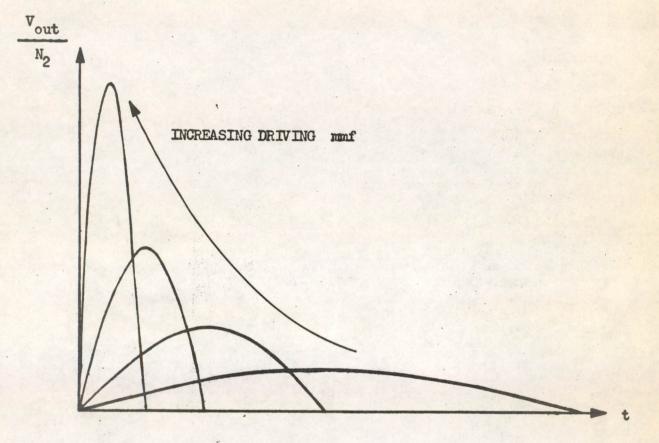

The leakage inductances appear in this equivalent circuit in the same way that they appeared in the equivalent circuit of the halfselected core. (See Appendix A and Fig. 2.7). The equivalent circuit of the fully selected switch core is shown in Fig. 2.12.

## c. The Combined Switch Core Characteristics

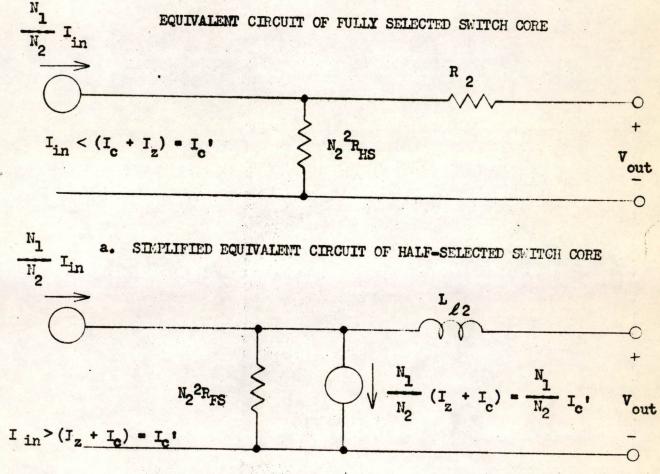

The similarity between the Revised Equivalent Circuit of Half Selected Switch Core (Fig. 2.8) and the Equivalent Circuit of Fully Selected Switch Core (Fig. 2.12) is evident.

If a current source drive is assumed, the leakage inductance  $L_1$ , may be neglected. The equivalent circuits can then be redrawn as in Fig. 2.13.

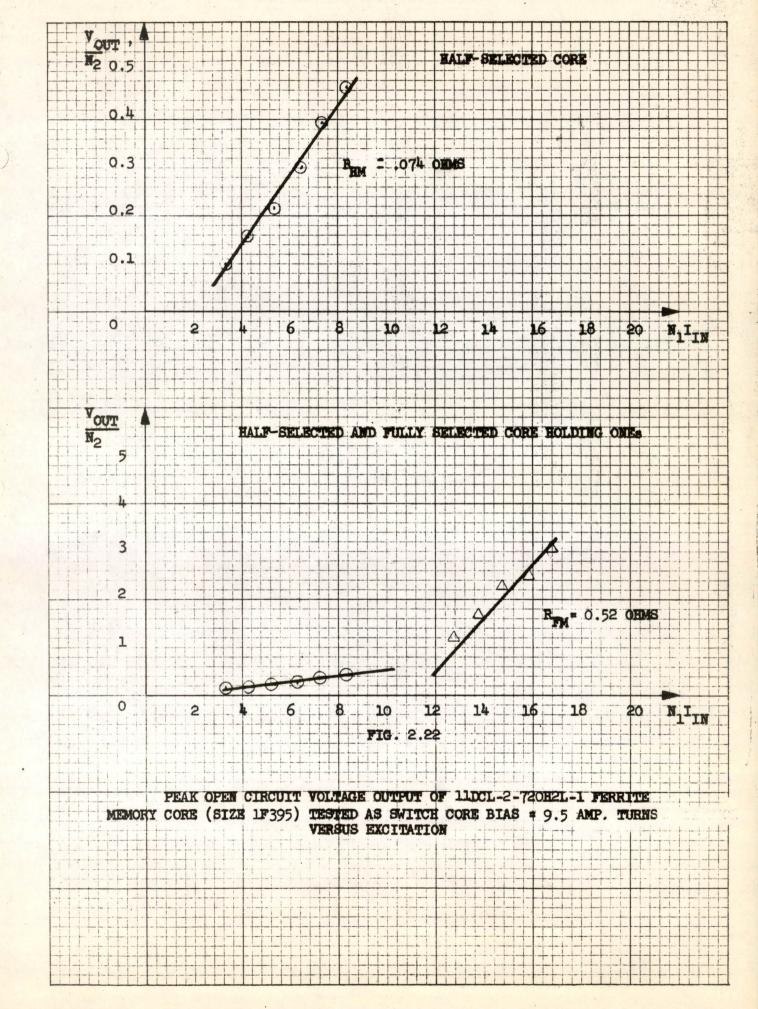

The data of Tables I and II are plotted, and the graphs of Fig. 2.14, 2.15, 2.16, and 2.17 are the results.

The departures from linearity of these curves at large driving currents are not properties of the cores, but are due to the core drivers. When the driving currents are exceedingly large, the cores switch during the current rise times. Because it is quite difficult to determine what the actual current exciting the core is, during switching, the easiest way out was taken - the driving current was assumed to be the

or

b. SIMPLIFIED EQUIVALENT CIRCUIT OF FULLY SELECTED SWITCH CORE

FIG. 2.13

SIMPLIFIED SWITCH CORE EQUIVALENT CIRCUITS (In IS CONSIDERED TO BE EITHER THE X OF Y DRIVE OR BOTH; THE BIAS IS CONSIDERED TO BE A PART OF THE COERCIVE FORCE)

10 X 10 TO THE INCH 359-5G KEUFFEL & ESSER CO. MAREIN U.S.A.

34%

A-48598-G

(7)

HAR TO X TO THE INCH 359-56

RE 10 X 10 TO THE INCH 359-56

A-148600 - G

R4E 10 X 10 TO THE INCH 359-56 Keuffel & esser co. wade in U.S.A.

A-48602-G

final value of the current output. The result is that the actual excitation of the core, during switching, is somewhat less than what is indicated. The broken line indicates what the expected curves should look like.

Figure 2.23 idealizes the above results and gives a piece-wise linear characteristic which can be dealt with analytically for the purpose of performing computations in order to predict the operation of the three core per bit memory unit.

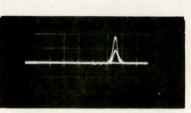

Figure 2.18 illustrates the fact that the open circuit switch core outputs are independent of the length of time that the core sets in one state, provided that the core is allowed to complete its switching in one direction before it is switched back.

B. The Memory Core

The idealized memory core has the hysteresis loop shown in Fig. 2.19. Figure 2.20 shows a more realistic core loop. Figures 2.3b and 2.3c show the loop of the memory core actually used in this thesis investigation.

The operating characteristics of the memory core are essentially the same as those of the switch cores. The equivalent circuits for the memory core are the same as those for the switch core (Fig. 2.7 or Fig. 2.8 for the Half Selected Core, and Fig. 2.12 for the Fully Selected Core). The difference in operation results from the fact that a memory core is not permitted any bias and so,  $I_Z = 0$ . The result is that  $I_C$  of Fig. 2.12 is merely  $I_C$  of the core in question. Figure 2.21 shows output voltages obtained when the memory held ONEs and was driven by various currents. (It is to be noted that a bias was applied to the core in order to determine information concerning the core in the partially selected state. The core was driven as if it were a switch

-38-

ON TIME MICROSECONDS

0.5

0.3

0.2

γA

Ą

0.15

FULL SELECTS = 9.6 VOLTS HALF SELECTS = 0.8 VOLTS

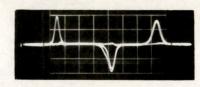

8v/CM 0.1 µSEC/CM

FIG. 2.18

OPEN CIRCUIT OUTPUT OF FULLY SELECTED SWITCH CORE 11DCL-2-720H2L-1, SIZE 1D26L FOR VARIOUS LENGTHS OF ON TIME EXCITATION REMAINS FIXED. BIAS = 9.5 AMP-TURNS. DRIVE = 17.0 AMP-TURNS

A-61330

IDEALIZED MEMORY CORE HYSTERESIS LOOP

HYSTERESIS LOOP OF MORE REALISTIC MEMORY CORE

-61351

| DRIVING EXCITATION<br>(AMPERE-TURNS) | VOLTAGE<br>OUTPUT<br>(VOLTS) |

|--------------------------------------|------------------------------|

| 8.5                                  | 0.17                         |

| 7.5                                  | 0.39                         |

| 6.5                                  | 0.30                         |

| 5.5                                  | 0.23                         |

| 4.5                                  | 0.16                         |

| 3.5                                  | 0.10                         |

A-61329

0.30v/CM

FIG. 2.21a

OPEN CIRCUIT OUTPUT OF HALF-SELECTED MEMORY CORE (11DCL-2-720H2L-1 SIZE 1F395) OPERATED AS A SWITCH CORE FOR VARIOUS EXCITATIONS BIAS = 9.5 AMP-TURNS. SIZE OF SECOND PULSE IS RECORDED

| • | DRIVING EXCITATION<br>(AMPERE-TURNS) | VOLTAGE<br>OUTPUT<br>(VOLTS) |             |

|---|--------------------------------------|------------------------------|-------------|

|   | 17.0                                 | 3.1                          |             |

|   | 16.0                                 | 2.5                          |             |

|   | 15.0                                 | 2.3                          |             |

|   | 14.0                                 | 1.7                          |             |

|   | 13.0                                 | 1.2                          |             |

|   | 12.0                                 | 0.5                          |             |

|   | 11.0                                 | DOES NOT<br>SWITCH           | 27/01       |

|   | FTG                                  | 2.21b                        | 0.1 µSEC/CM |

FIG. 2.21b

2v/CM

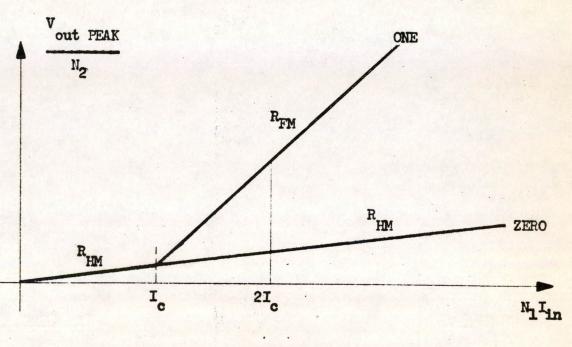

OPEN CIRCUIT OUTPUT OF FULLY SELECTED MEMORY CORE (11DCL-2-720H2L-1, SIZE 1F395) OPERATED AS SWITCH CORE FOR VARIOUS EXCITATIONS. BIAS = 9.5 AMP-TURNS. SIZE OF FIRST PULSE IS RECORDED core). This data is presented in Table III, and plotted in Fig. 2.22. Figure 2.24 shows the linearized characteristic with the bias removed. No data was taken for the operation of the memory core holding a ZERO in these tests. In line with the other linearized assumptions made, it is assumed that the volt-ampere characteristic of a memory core holding a ZERO is merely a continuation of the half-selected characteristic.

## TABLE III

| Driving Current<br>(ampere turns)         | Peak Open Circuit Memory Core Output Voltage<br>(operated as Switch Core) bias = 9.5 amp-turns<br>ll DCL - 2 - 720 H2L-1 |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Half Selects                              | 1 <b>F</b> 395                                                                                                           |

| 3.5                                       | 0.10                                                                                                                     |

| 4.5                                       | 0.16                                                                                                                     |

| 5.5                                       | 0.23                                                                                                                     |

| 6.5                                       | 0.30                                                                                                                     |

| 7.5                                       | 0.39                                                                                                                     |

| 8.5                                       | 0.47                                                                                                                     |

|                                           |                                                                                                                          |

| Full Selects<br>(core holds ONE)          |                                                                                                                          |

| 12                                        | 0.5                                                                                                                      |

| 13                                        | 1.2                                                                                                                      |

| 14                                        | 1.7                                                                                                                      |

| 15                                        | 2.3                                                                                                                      |

| 16                                        | 2.5                                                                                                                      |

| . 17                                      | 3.1                                                                                                                      |

| Peak Resistance of<br>Open Circuit, Fully |                                                                                                                          |

| Selected Memory Cores                     | 0.52                                                                                                                     |

(for ONE)

APE NO X 10 TO THE INCH 359-5G

A-48601-G

FIG. 2.23

LINEARIZED IDEALIZATION OF OPEN CIRCUIT SWITCH CORE CHARACTERISTICS

LINEARIZED IDEALIZATION OF MEMORY CORE CHARACTERISTICS

A- 0352 61352 The selection ratio (R) is defined as the excitation applied to a selected core divided by the maximum excitation applied to any unselected core. R. S. DiNolfo<sup>9</sup> has shown that if an n dimensional selection scheme is employed, that

$$R_{\max} = \frac{1}{P_{\min}} = \frac{n+1}{n-1}$$

(2.12)

The smaller the p of the core is (i.e. - the poorer the core is, Fig. 2.20), the larger the selection ratio must be. But, R is max limited by the number of dimensions used.

The coincident-current memory has a two-dimensional read (X and Y) and a three-dimensional write (X, Y, and Z). In order to obtain symmetrical operation, it is necessary to employ the same excitations during the read and write operations, and so the system is used as if it were three-dimensional. Thus,  $R_{max} = 2$ , and  $P_{min} = 1/2$ . As has been pointed out in Chapter 1, this fact limits the allowable excitation applied to the core.

A large amount of information can be obtained from Fig. 2.24. The maximum half-select current in the coincident-current memory scheme is  $I_c$ . The result is that the maximum full-select current is  $2I_c$ . Utilizing Fig. 2.24 and the computations in Appendix C, the following results are obtained:

$$V_{\text{out} ZERO} = 2 R_{\text{HM}} I_{\text{c}}$$

(2.14)

$$V_{\text{out ONE}} = (R_{\text{HM}} + R_{\text{FM}})I_{c} \quad (2.15)$$

It is necessary that the ONE to ZERO, and ONE to half-select ratios be as large as possible. These ratios are:

$$\frac{V_{\text{out ONE}}}{V_{\text{out ZERO}}} = \frac{R_{\text{HM}} + R_{\text{FM}}}{2 R_{\text{HM}}} = 1/2(1 + \frac{R_{\text{FM}}}{R_{\text{HM}}})$$

$$= 1/2(1 + \mu), \qquad (2.16)$$

and

$$\frac{V_{out ONE}}{V_{out half-select}} = \frac{R_{HM} + R_{FM}}{R_{HM}} = 1 + \frac{R_{FM}}{R_{HM}} = 1 + \mu$$

(2.17)

The factor  $\mu$  is the ratio of the incremental full selected memory core peak resistance to the incremental half selected peak resistance. It is desirable to use cores in which  $\mu$  is as large as possible. In order to obtain maximum discrimination between wanted and unwanted signals.

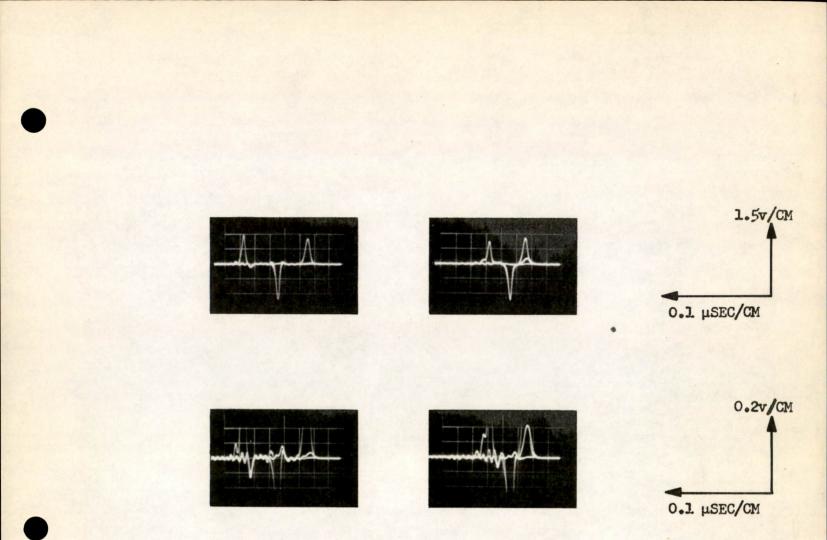

The outputs of 50 MTC memory cores (General Ceramics S-1, Lot E-85) driven with coincident current excitation are shown in Fig. 2.25. This picture shows the size of ONEs compared to ZERO and half selects.

The sizes of the outputs are tabulated below.

| mp.  | AD  | TF | IV |

|------|-----|----|----|

| - 14 | HD. |    | TV |

|                     | Voltage Output From<br>50 Cores | Voltage Output<br>Per Core | Ratio of ONE |

|---------------------|---------------------------------|----------------------------|--------------|

| ONE                 | 7.0                             | 0.140                      |              |

| ZERO                | 0.26                            | 0.0052                     | 27           |

| Half Select<br>ONE  | 0.24                            | 0.0048                     | 29           |

| Half Select<br>ZERO | 0.12                            | 0.0024                     | 58           |

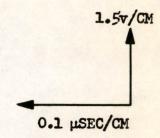

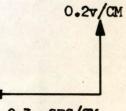

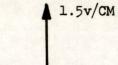

1.5v/CM

0.5 USEC/CM

0.5 USEC/CM

FULL SELECT AND HALF SELECT ONES AND ZEROS SUPERIMPOSED

0.2v/CM

HALF SELECT ONE AND ZERO AND FULL SELECT ZERO SUPERIMPOSED

FULL SELECT ONE = 7.0 VOLTS FULL SELECT ZERO = 0.26 VOLTS HALF SELECT ONE = 0.21 VOLTS HALF SELECT ZERO = 0.12 VOLTS

A-61337

## FIG. 2.25

VOLTAGE OUTPUTS FROM COINCIDENT CURRENT TYPE SELECTION. 50 GENERAL CERAMICS MEMORY CORES NO BIAS HALF SELECT EXCITATION = 0.410 AMP-TURNS The complete cycle is not shown, but it requires about 6 microseconds to completely read and write. About 1 microsecond is require to switch the core completely.

A one-dimensional read and write would remove all restrictions on the allowable drive and would, incidentally, eliminate partial select noises. The necessary core characteristics could be relatively slack p could approach zero. The operating speed could be made extremely rapid, limited merely by how hard the selected cores were driven. The factor # introduced would be of no interest.

In its essence, the three-core-per-bit memory unit described in Chapter 3 is a one-dimensional memory. Actually, it does not quite achieve this mark because of noise outputs from partially selected switch cores.

#### CHAPTER 3

the re

#### THE THREE-CORE-PER-BIT MEMORY

The memory unit utilizing two switch cores and one memory core per bit of information that has been proposed by J. Raffel<sup>6</sup> will be discussed in this chapter.

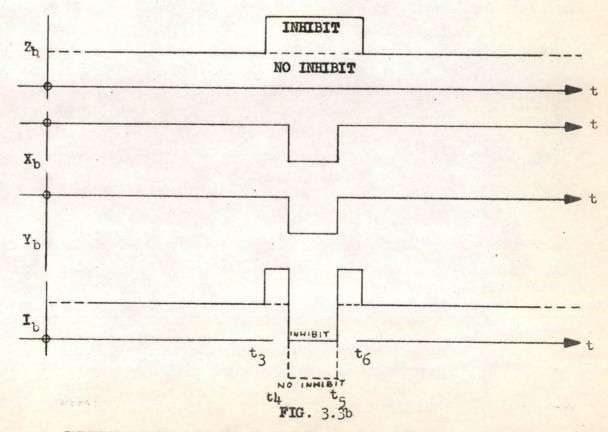

The cores employed are those described in Chapter 2. The basic, simplified, memory unit is shown in Fig. 3.1. The current pictured driving switch core A  $(I_{in a})$  is actually composed of the  $X_a$  and  $Y_a$ drives superimposed on the bias. The current driving core B  $(I_{in b})$ consists of the  $X_b$  and  $Y_b$  and bias excitations; in addition an inhibit pulse may or may not be applied.

## A. The Operation of the Cycle

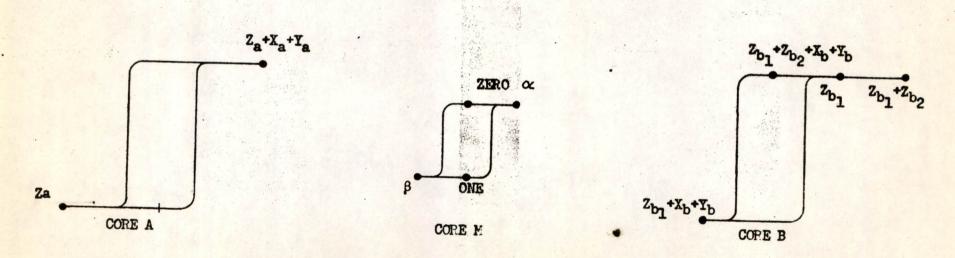

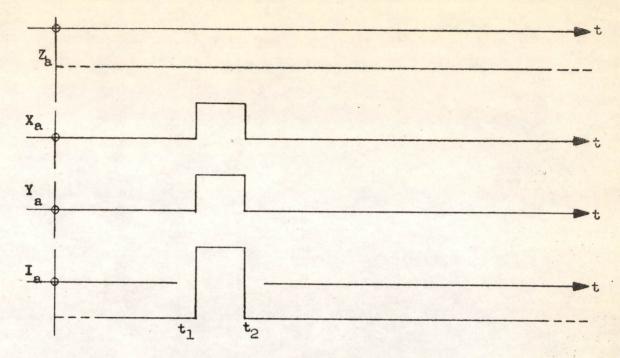

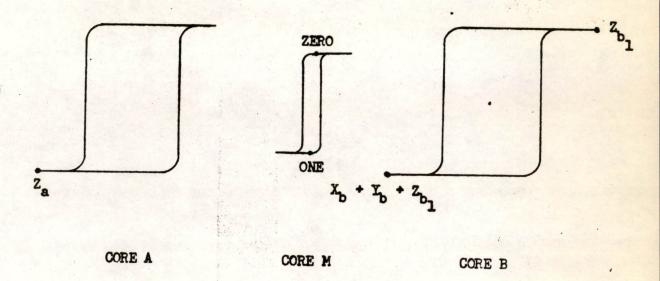

The operation of the system may be explained by referring to the hysteresis loops of the cores (Fig. 3.2) and to the pulse sequences (Fig. 3.3).

At the beginning of the cycle the only current flowing through core A is the bias,  $I_{za}$ , and the core is at the point za on its hysteresis loop (Fig. 3.2). At the time  $t_1$ ,  $I_{Xa}$  and  $I_{Ya}$  are applied, and the result is that core A switches from  $Z_a$  to  $Z_a + X_a + Y_a$ . The output voltage of this core induces a large pulse of current in loop A and core M is driven to point  $\prec$  on its hysteresis loop. When the current pulse dies away, core M rests at the ZERO point. If the memory core had originally held a ZERO, its voltage output would have been relatively small because of the small flux change. However, if the core previously held a ONE, a large output would be induced on its sense winding. This difference in core outputs provides a ready means for determining the original state

-50-

FIG. 3.1

ONE DIGIT OF THE THREE CORE PER BIT MEMORY UNIT, SIMPLIFIED

FIG. 3.2

HYSTERESIS LOOPS OF THE CORES IN THE MEMORY UNIT

CURRENT PULSES APPLIED TO SWITCH CORE A, WHEN FULLY SELECTED

CURRENT PULSES APPLIED TO SWITCH CORE B, WHEN FULLY SELECTED

4-61353

ILLUSTRATING THE RESULT OF THE PRESENCE OR ABSENCE OF THE INHIBITING PULSE. of the core.

At the time t<sub>2</sub>,  $I_{Xa}$  and  $I_{Ya}$  are removed, and core A reverts to point  $Z_a$  on its loop. This induces a current in loop A which drags the memory core to point  $\beta$  on its loop, and the memory core eventually settles at point ONE. At the conclusion of the read operation, the memory core is found to repose in the ONE position, regardless of its original information content.

The purpose of the second switch core, B, is to write the required information into the memory core. If it is desired to write a ZERO, it is apparent that core B must be used to move memory core M from the ONE state. On the other hand, the simplest way of writing a ONE, is to prevent this action of core B.