XFROX

## Internal Memo

То

Ed Da Silva

From

Bo Sramek CPT-77-6604

Subject

Date

Janus Clock Distribution Rules September 29,1977.

This memo is an extension of memo CPT-77-6565, part of which is enclosed as an appendix.

There will be only three critical clocks distributed via low impedance transmission lines at the back panel: EDGE CLOCK (the most critical), RAM CLOCK and CYCLE O CLOCK.

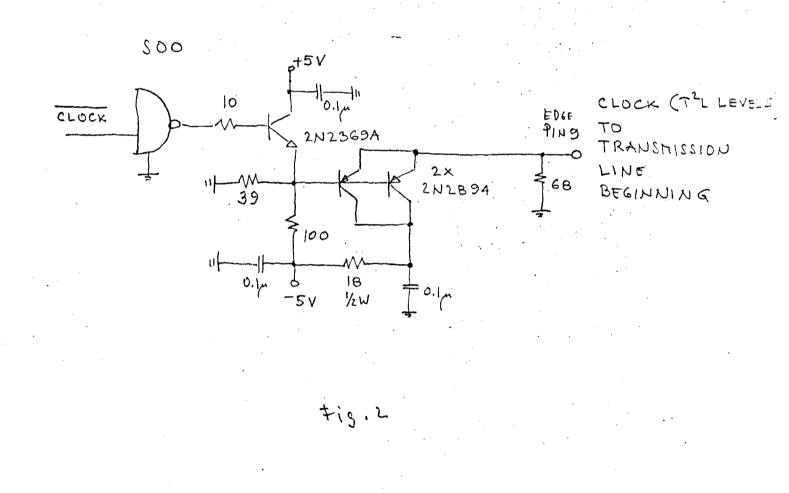

These three clocks have special drivers located on a PC board in location Jl, physically close to corresponding edge connector pins (location PK, NK or NL). The clocks for CPU Control (J1) are tapped from edge connector pins. The special clock drivers will be discrete for first version of layout with probable change into hybrid DIPs, phased in later. (Fig. 2)

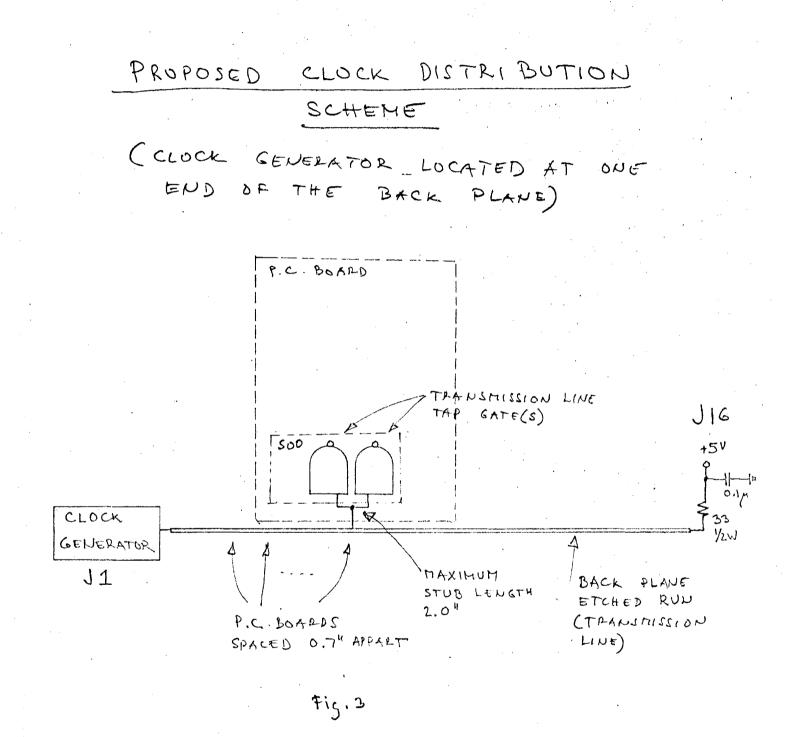

The transmission lines terminating resistors (33 Ohms/0.5W) are located on the back plane close, or at, the connector location J16. The +5V end of each terminating resistor is bypassed to GND by O.luF (maintaining very short leads both of terminating resistors and bypassing capacitors is essential). (Fig. 3)

Other clocks (noncritical ones) are handled and distributed as regular TTL signals, following standard loading and distribution rules.

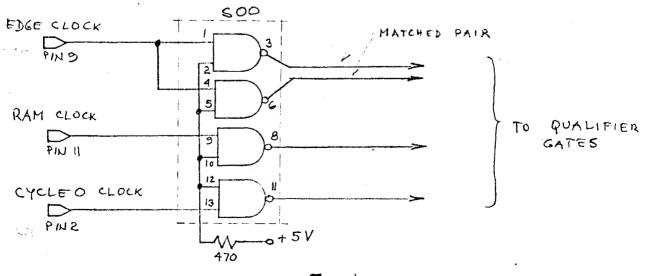

The critical clocks use the same SOO package (transmission line tap package), located nearest the edge connector pins assigned for critical clocks (location PL or PK on the PC board).(fig.1) The pin assignment of transmission line tap package is the same on all boards:

Fig.1

The special clock drivers for low impedance transmission line are described in the enclosed appendix memo.

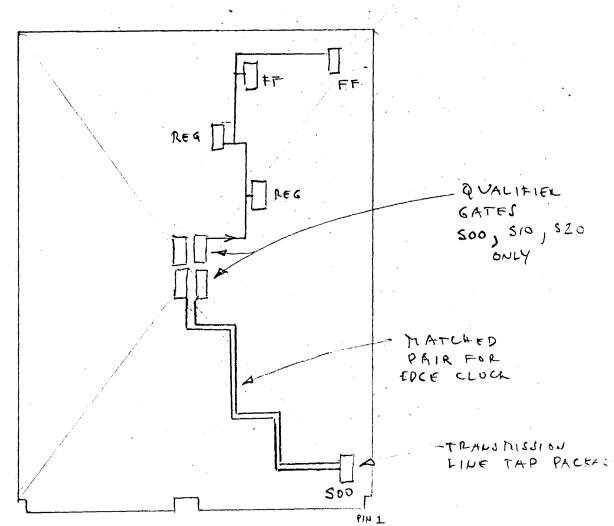

The qualifier gates for all clocks are located as close as possible to the physical center of each PC board. The most critical edge clock qualifier gates are arranged in a square pattern in the center and the remaining qualifier gates immediately surrounding them. (Refer to fig. 4). Clock signal from qualifier gates should be routed serially to various flip-flops and register in each board subdivision.

The edge clock tap package uses two gates (see fig.1) to feed sufficient number of qualifier gates (output pins 3 and 6). It is man-datory, that the connections from outputs 3 and 6 to two groups of edge clock qualifier gates are run as a matched pair.

If there would have been any questions concerning the clock layout or distribution, do not hesitate to call me. (Ext. 2624).

## Distribution:

- C. Thacker.

- H. Kakita

- B. Rosen

- J. Camarata

- R. No

- J. Furst

- F. Itami

- J. Cameron

- R. Matsuda

- W. Klein

- W. Woolever

- T. Chang

- R. Loshak

- R. McNair

- R. Pelby

- L. Sheese

- M. Thomson

- C. Tseng P. Vysin

- P. Venkatachalam

XEROX

## **Internal Memo**

То

Brian Rosen

From

Bo Sramek, X2624

CPT-77-6565

Subject

Janus Clock Distribution

Date

9/16/77

Enclosed you will find some measured data on proposed low impedance transmission line clock distribution scheme.

Assumption was that there will be 16 boards maximum, plugged into the back plane at 0.7" intervals.

The distribution scheme addresses itself mostly to EDGE CLOCK distribution, but is, obviously applicable to remaining clocks, as well.

It was also assumed that maximum load of any board to any low impedance transmission line at one location is two T<sup>2</sup>L gates (one is even better).

Each load was simulated with 2k resistor to +5V and 7.5pF capacitor to ground (hence 16 times 1k/15pF for 16 boards).

The transmission line was simulated with a insulated wire run as close as possible to solid ground plane. The estimated impedance of the etched unloaded run is in the vicinity of 75 Ohms; together with lk/l5pF @ 3ns rise time pulses, the overall impedance of the transmission line is between 30 and 40 Ohms (hence 33 Ohm pullup for far end termination and two 68 Ohm pullups at both ends for the case of driving the transmission line from the middle.)

The clock generator itself consists of three discrete transistors (the transistor types used are the same as in X-WIRE Transceiver) and several resistors and bypassing capacitors.

If any questions, please do not hesitate to call me (note my new extension).

Distribution:

- C. Thacker

- H. Kakita

- J. Camarata

- R. Mo

- J. Furst

- R. Weir

- F. Itami

PROPOSED CLOCK GENERATOR (TO BE LAID OUT ON BOARD JI)

9/15 Bo

9| 15

Bo

P.C. BOARD ASSIGNED LOCATIONS OF TAP AND QUALIFIER GATES

FIG. 4.