INTRODUCTION TO DIGITAL TECHNIQUES

# Individual Learning Program In DIGITAL TECHNIQUES

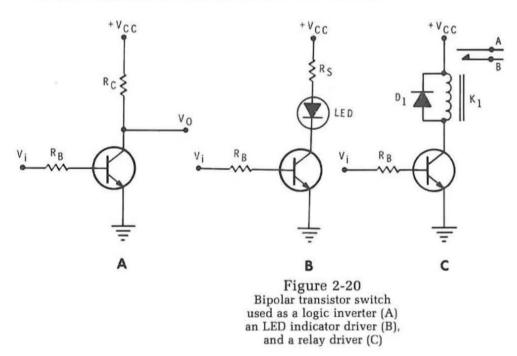

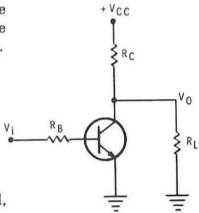

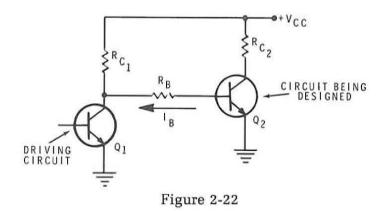

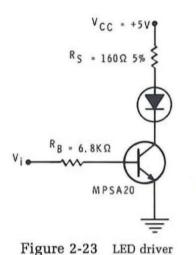

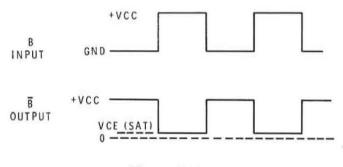

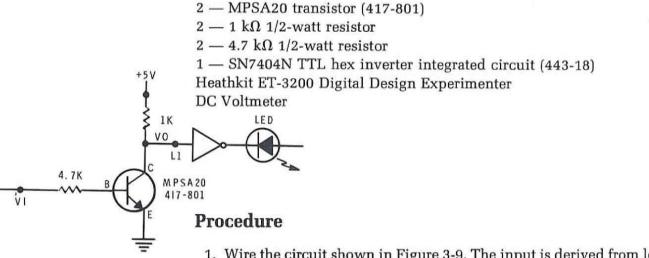

# DIGITAL TECHNIQUES EE-3201

# PARTS LIST

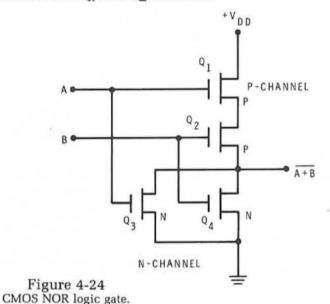

This parts list contains all of the parts used in experiments which you will perform with this course. The key number in the parts list corresponds to the numbers in the parts pictorial. Some parts are packaged in envelopes. Except for this initial parts check, keep these parts in their envelopes until they are called for in the experiment. A container is provided so that you can keep the small parts together in one place.

KEY PART QTY. DESCRIPTION No. No.

#### **RESISTORS (5%)**

| ×A1  | 6-102 | 2 | 1000 Ω 1/2 watt (brown-black-red)     |

|------|-------|---|---------------------------------------|

| XA1  | 6-472 | 4 | 4700 Ω 1/2 watt (yellow-violet-red)   |

| ×A1  | 6-103 | 2 | 10 kΩ 1/2 watt (brown-black-orange)   |

| ×A1  | 6-473 | 2 | 47 kΩ 1/2 watt (yellow-violet-orange) |

| × A1 | 6-224 | 1 | 220 kΩ 1/2 watt (red-red-yellow)      |

| × A1 | 6-151 | 1 | 150 Ω 1/2 watt (brown-green-brown)    |

| × A1 | 6-561 | 1 | 560 Ω 1/2 watt (green-blue-brown)     |

#### CAPACITORS

#### Disc

| × | A2 | 21-47  | 2 | .01 µF  |

|---|----|--------|---|---------|

| × | A2 | 21-140 | 2 | .001 µF |

#### Electrolytic

| × | A3 | 25-111        | 2     | 1000 µF |

|---|----|---------------|-------|---------|

| ~ | 20 | E. O. I I I I | A.c.s | 1000 0  |

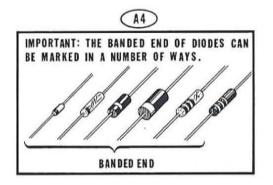

#### DIODES-TRANSISTORS-LIGHT EMITTING DIODE DISPLAY

| > A4  | 56-56   | 4 | 1N4149 silicon diode  |

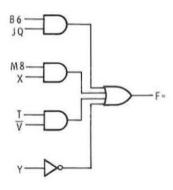

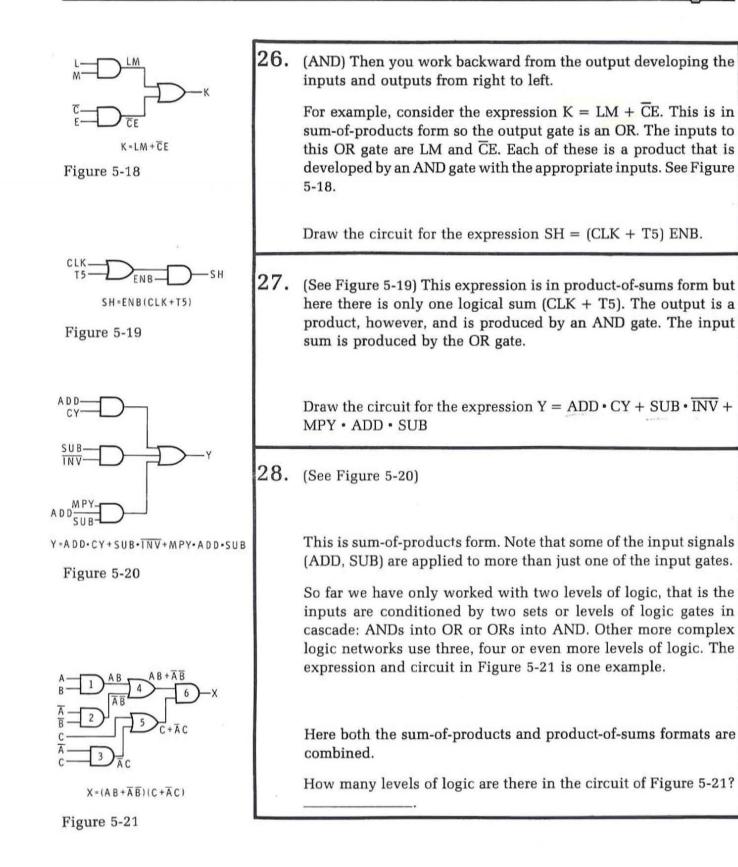

|-------|---------|---|-----------------------|

| )- A5 | 411-819 | 1 | 7 segment LED display |

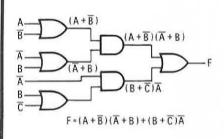

| > A6  | 417-801 | 2 | MPSA20 transistor     |

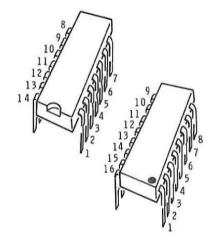

#### INTEGRATED CIRCUITS

NOTE: Transistors and integrated circuits are marked for identification in one of the following ways:

- 1. Part number.

- 2. Type number.

- 3. Part number and type number.

- 4. Part number with a type number other than the one listed.

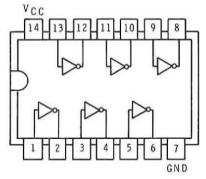

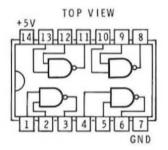

| ¥ A7        | 443-1   | 2 | SN7400N       |

|-------------|---------|---|---------------|

| A7          | 443-2   | 1 | SN420N (7420) |

| ×A7         | 443-629 | 1 | SN7490AN      |

| ×A7         | 443-13  | 1 | SN7475N       |

| ×A7         | 443-16  | 2 | SN7476N       |

| ×A7         | 443-18  | 1 | SN7404N       |

| ×A7         | 443-25  | 1 | SN74151N      |

| >A7         | 443-46  | 1 | SN7402N       |

| ×A7         | 443-53  | 1 | SN7442N       |

| ×A7         | 443-54  | 1 | SN7403N       |

| × A7        | 443-90  | 1 | SN74123N      |

| ×A7         | 443-612 | 1 | SN74193N      |

| $\times A7$ | 443-680 | 1 | SN7495AN      |

| $\times A7$ | 443-694 | 1 | UA9368        |

| $\times A7$ | 443-695 | 1 | CD4001        |

| × A7        | 443-698 | 1 | SN7486N       |

|             |         |   |               |

1

#### MISCELLANEOUS

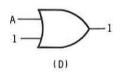

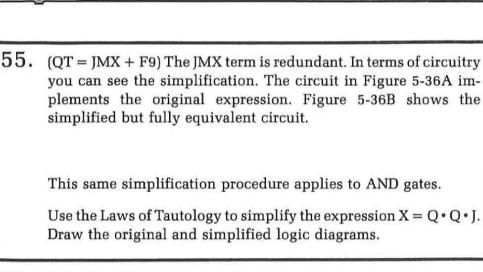

266-962

Small parts container

# INDIVIDUAL LEARNING PROGRAM IN DIGITAL TECHNIQUES

EE-3201

# COURSE OBJECTIVES AND OUTLINE

#### **COURSE OBJECTIVES**

When you complete this program, you will have the following skills and knowledge. You will be able to:

- 1. Discuss the advantages and benefits of using digital techniques in electronic equipment.

- 2. Name the major applications of digital techniques in electronics.

- 3. Convert between the binary and decimal number systems and recognize the most commonly used binary codes.

- 4. Name the major components used in implementing digital circuits and explain how they operate.

- 5. Explain the operation of digital logic gates.

- Identify the more commonly used integrated circuit families used in digital equipment and discuss their operation, characteristics, and features.

- 7. Use Boolean Algebra to express logic operations and minimize logic circuits in design.

- 8. Explain the operation of flip-flops.

- 9. Discuss the operation and application of binary and BCD counters, shift registers and other sequential logic circuits.

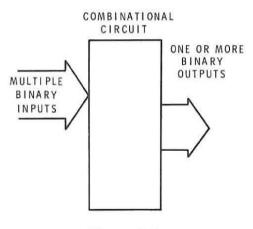

- 10. Name the most frequently used combinational logic circuits and explain their operation.

- 11. Design both combinational and sequential logic circuits for a given application from definition and concept to the selection of the integrated circuits.

- 12. Discuss the operation and application of digital counters in time and frequency measurements.

- 13. Explain how a digital computer is organized and how it operates.

14. Discuss microprocessors, explain their operation and give examples of their applications.

#### **COURSE OUTLINE**

**UNIT 1** Introduction to Digital Techniques Introduction **Unit Objectives** Unit Activity Guide **Digital Techniques** Contrasting Analog and Digital Devices and Techniques Where are Digital Techniques Used? Communications **Telemetry Systems Test Instruments Industrial Controls Consumer Electronic Equipment** Why Use Digital Techniques? **Greater Accuracy** Greater Dynamic Range Greater Stability Convenience Automation **Design Simplicity** New Approaches The Binary Number System Positional Number Systesm Fractional Numbers Converting Between the Binary and Decimal Number Systems Binary to Decimal Decimal to Binary **Binary Number Sizes** Number Identification **Binary** Codes **Binary Coded Decimal** Special Binary Codes Excess 3 Code Grav Code ASCII Code Data Representation **Electromechanical Devices** Transistors **Magnetic Cores** Logic Levels Positive and Negative Logic Parallel vs Serial Data Representation Logic Circuits Unit Summary Examination Answers

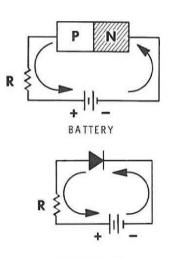

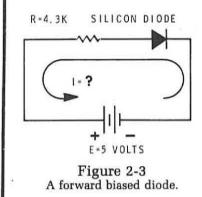

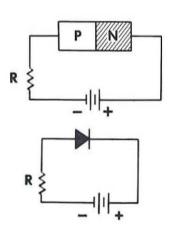

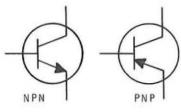

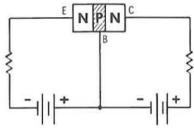

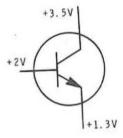

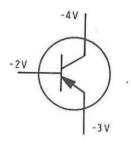

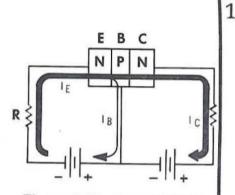

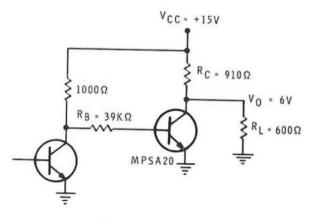

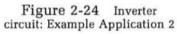

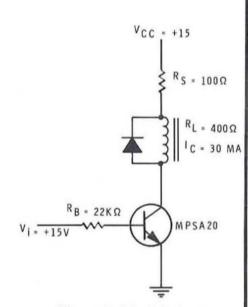

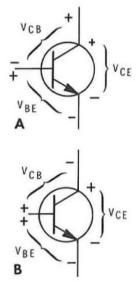

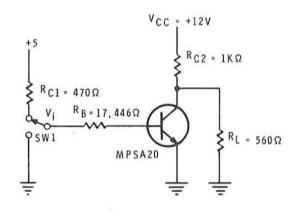

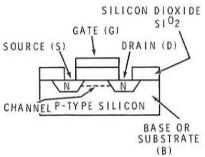

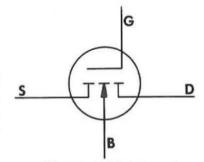

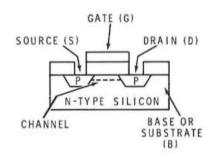

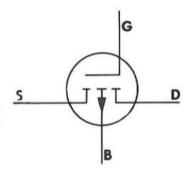

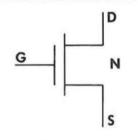

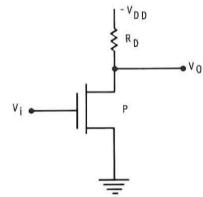

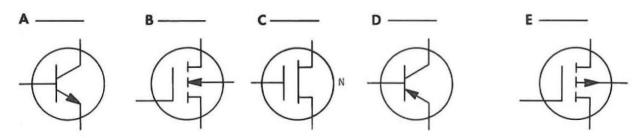

#### **UNIT 2** Semiconductor Devices for Digital Circuits

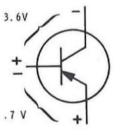

Introduction **Unit Objectives** Unit Activity Guide A Programmed Review of Transistor Operation The Eipolar Transistor Switch Modes of Operation Cut-off Linear Saturation Saturated Switching Circuits Switching Speed Non-Saturating Switching Circuits Designing a Saturated Switch Logic Inverter Procedure **Example Application 1 Example Application 2** Experiment 1 Bipolar Transistor Switch **MOS Field Effect Transistors** The N-Channel MOSFET The P-Channel MOSFET Bipolars vs MOSFET's **MOSFET** Circuits Unit Summary Examination Answers

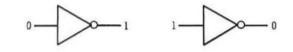

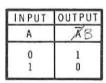

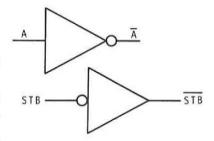

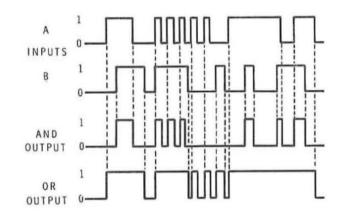

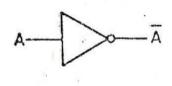

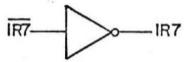

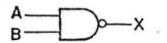

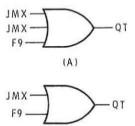

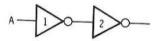

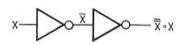

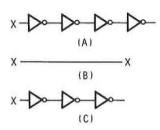

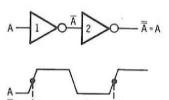

#### **UNIT 3 Digital Logic Circuits**

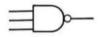

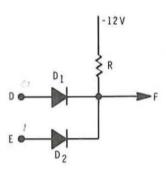

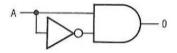

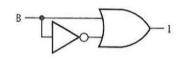

Introduction **Unit Objectives** Unit Activity Guide **Types of Logic Circuits** The Inverter **Experiment 2 Logic Inverter Decision-Making Logic Elements** The AND Gate The OR Gate The Dual Nature of Logic Gates **Experiment 3 Diode Logic Gates** NAND/NOR Gates NAND Gate NOR Gate How NAND/NOR Gates Are Used **Practical Logic Circuits Relays and Switches Discrete Component Logic Circuits Integrated** Circuits **Experiment 4 Transistor Logic Gate** Examination Answers

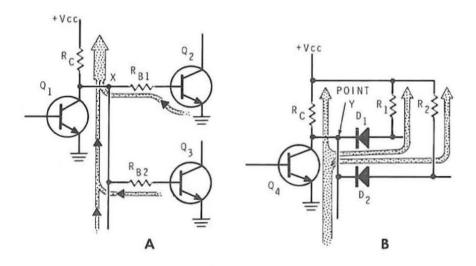

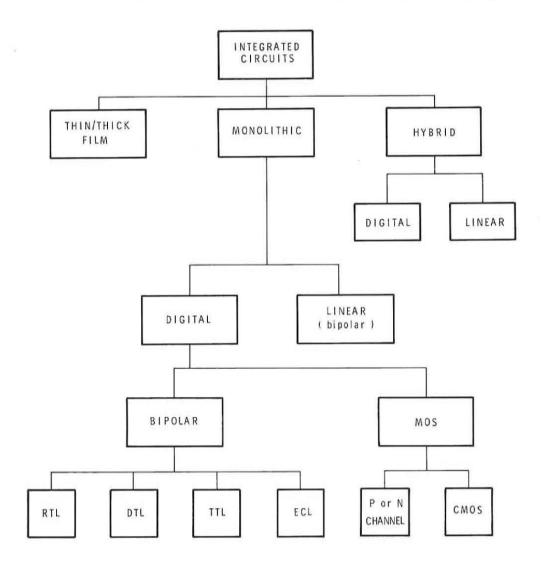

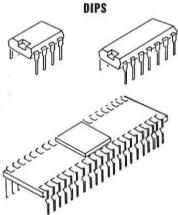

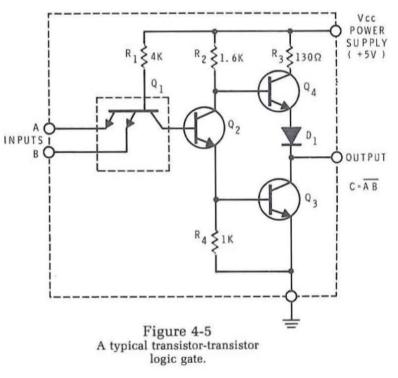

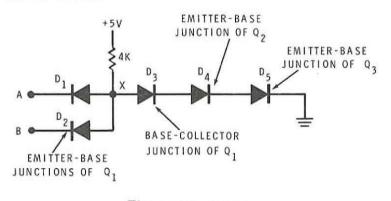

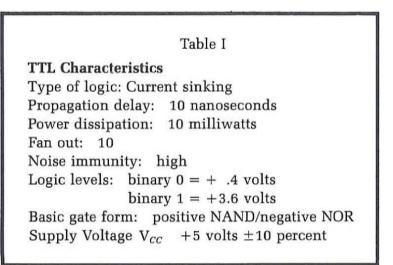

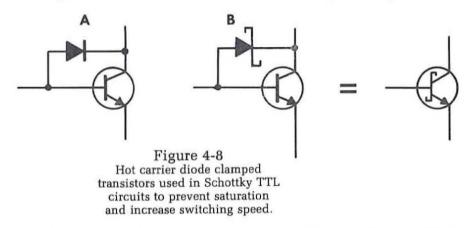

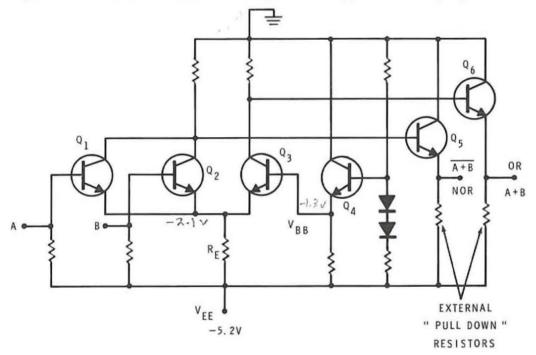

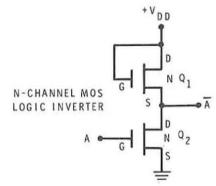

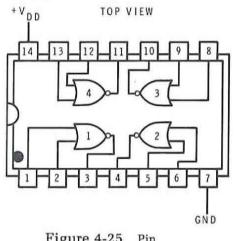

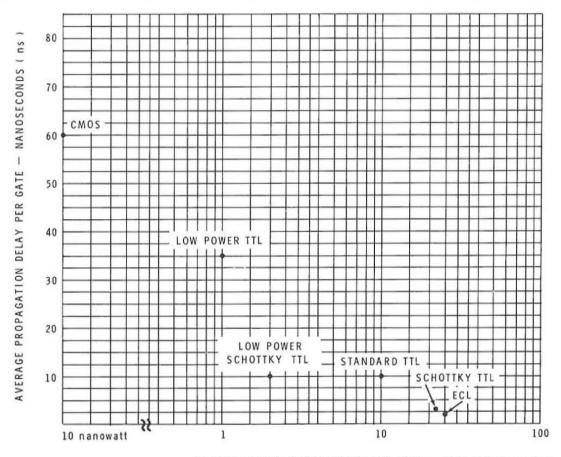

Introduction **Unit Objectives** Unit Activity Guide Logic Circuit Characteristics Logic Levels **Propagation Delay Power Dissipation** The Speed-Power Trade-Off Noise Immunity Fan Out **Current Source Logic** Current Sink Logic Integrated Circuits Manufacturing Methods Monolithic Thin and Thick Film Techniques Hybrid Circuits Application Function Integrated Circuit Packaging TO<sub>5</sub> Flat-Pack DIP **Temperature Ranges Transistor Transistor Logic Circuit Operation TTL Characteristics** Special TTL Variations Low Power TTL High Power TTL Schottky TTL Three State TTL **Experiment 5 TTL Logic Gates Emitter Coupled Logic Circuit** Operation **ECL Characteristics** Metal Oxide Semiconductor Integrated Circuits PMOS and NMOS Circuits **Complementary MOS CMOS** Characteristics **Experiment 6 CMOS Logic Gate** Selecting a Digital Integrated Circuit for a Specific Application Trends **Complex Functions** Trade-Offs Examination Answers

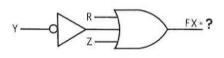

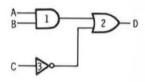

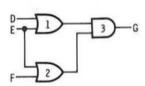

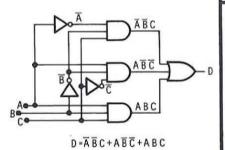

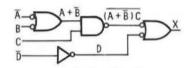

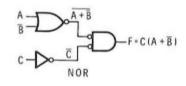

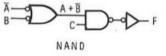

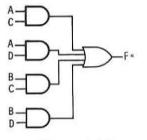

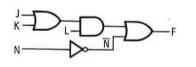

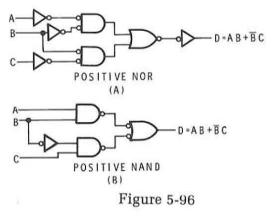

Introduction Unit Objectives Unit Activity Guide Relating Digital Logic Circuits and Boolean Equations Truth Tables Boolean Rules Minimizing Logic Expressions Using NAND/NOR Gates Experiment 7 Applying NAND and NOR Gates Experiment 8 The Wired OR Connection Examination Answers

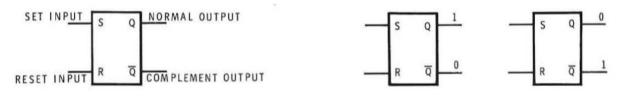

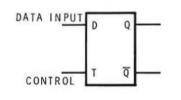

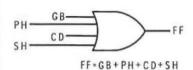

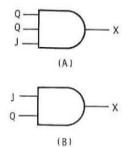

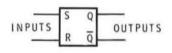

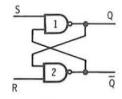

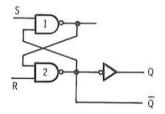

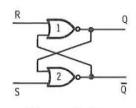

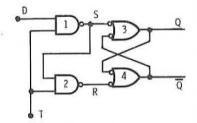

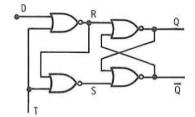

#### **UNIT 6** Flip-Flops and Registers

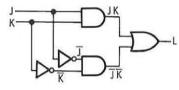

Introduction Unit Objectives Unit Activity Guide Flip-Flops Experiment 9 Set-Reset Flip-Flops D Type Flip-Flops and Registers Experiment 10 D Type Flip-Flops and Registers JK Flip-Flops Experiment 11 JK Flip-Flops Examination Answers

#### UNIT 7 Sequential Logic Circuits: Counters, Shift Registers, and Clocks

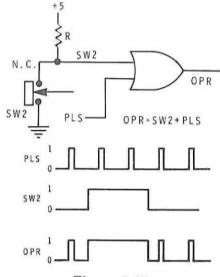

Introduction **Unit Objectives** Unit Activity Guide Counters **Binary Counters Frequency Dividers** Maximum Count **Down Counters Up-Down** Counter Synchronous Counters **Counter Control Functions Typical Integrated Circuit Counters Experiment 12 Binary Counters BCD** Counters **Cascading BCD Counters** The BCD Counter as a Frequency Divider Typical Integrated Circuit BCD Counter Experiment 13 The BCD Counter **Special Counters** Modulo 3 Counter Modulo 5 Counter **Experiment 14 Counter Applications** Shift Registers Shift Register Operation **Bipolar Logic Shift Registers Experiment 15 Shift Registers** Shift Register Applications Scaling Operations Shift Register Memory Sequencer/Ring Counter Counters **Experiment 16 Shift Register Applications MOS Shift Registers Dynamic MOS Shift Registers** Static MOS Shift Registers **Clocks and One Shots Clock Oscillator Circuits Discrete Component Circuits IC Clock Circuits One Shot Multivibrators One Shot Applications** Experiment 17 Clocks and One Shots Examination Answers

Introduction **Unit Objectives** Unit Activity Guide Decoders BCD to Decimal Decoder Octal and Hex Decoders BCD to 7-Segment Decoder **Experiment 18 Decoders** Encoders Experiment 19 7-Segment Decoder-Driver and Display Multiplexers Multiplexer Operation **Multiplexer** Applications Parallel to Serial Conversion Serial Binary Word Generator **Boolean Function Generator Experiment 20 Multiplexers** Demultiplexers **Exclusive OR Exclusive NOR** Applications of the Exclusive OR **Binary Adder** Parity Generator/Checker **Binary Comparators Experiment 21 Exclusive OR Code Converters Experiment 22 Exclusive OR Applications Read Only Memories ROM** Operation **ROM** Construction **Bipolar** ROM MOS ROM's Access Time **ROM Applications** Random Logic **Code Conversion** Arithmetic Operations Microprogramming **Programmable Logic Arrays** Examination Answers

Introduction **Unit Objectives** Unit Activity Guide Design Criteria Maximum Performance Lowest Cost Trade-Offs Combinational Logic Circuit Design **Problem Definition Example** Problem **Truth Table Development Develop the Logic Equations Circuit Minimization** Karnaugh Maps Summary of Karnaugh Map Usage "Don't Care" States Implementing the Logic Equations SSI Implementation **MSI** Implementation **ROM Implementation PLA** Implementation Multiple Output Combinational Circuits **Design Examples** Design Example #1 Solution to Design Example #1 Design Example #2 Solution to Design Example #2 **Experiment 23 Designing Combinational Circuits** Sequential Logic Circuit Design Design Procedure Defining the Problem Developing a State or Flow Table Developing a Karnaugh Map for the Counter Drawing the Logic Diagram **Design Examples Two-Bit Gray Code Counter** XS3 Code BCD Counter **Design Variations Experiment 24 Designing Sequential Logic Circuits** Examination Answers

#### **UNIT 10 Digital Applications**

Introduction **Unit Objectives** Unit Activity Guide Digital Test Equipment: The Frequency Counter Input Circuit Gate and Control Circuits **Time Base** Decimal Counter and Display Modes of Operation **Totalize** Mode **Frequency Measurement** Period Measurement **Time Interval Measurements Frequency Ratio Measurement Counter Specifications Input Sensitivity** Input Impedance **Frequency Range Display Digits Time Base** Modes A Typical Digital Counter **General Circuit Description** Input Circuit and Schmitt Trigger 10 MHz Clock and Scaler Decade Counter and Display **Control Circuitry Over-Range** Detection

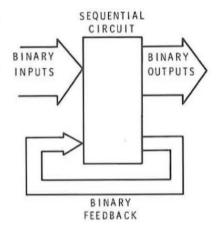

**Digital Computers** What is a Digital Computer? How Computers Are Classified Minicomputers Microcomputers **Programmable Calculators** Microprocessors **Digital Computer Organization** Memory Control Unit Arithmetic-Logic Unit Input-Output Unit **Digital Computer Operation** Programming **Programming Procedure** Writing Programs **Computer Instructions** A Hypothetical Instruction Set **Example Programs** Software Subroutines **Utility Programs** Assembler Compiler Cross Assemblers and Compilers Microprocessors Types of Microprocessors Applications of Microprocessors Where Are Microprocessors Used? **Designing With Microprocessors** Examination Answers

FINAL EXAMINATION (optional)

# **ILLUSTRATIONS FOR AUDIO RECORDS**

UNIT 1, Record 3, Side 1

Figure A

| DECLMAN | BINARY |   |   |   |

|---------|--------|---|---|---|

| DECIMAL | 8      | 4 | 2 | 1 |

| 0       | 0      | 0 | 0 | 0 |

| 1       | 0      | 0 | 0 | 1 |

| 2       | 0      | 0 | 1 | 0 |

| 3       | 0      | 0 | 1 | 1 |

| 4       | 0      | 1 | 0 | 0 |

| 5       | 0      | 1 | 0 | 1 |

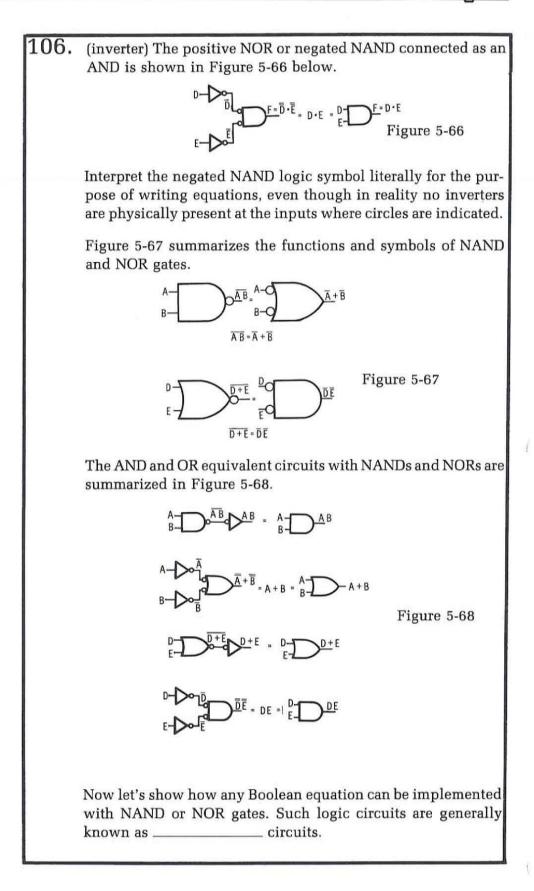

| 6       | 0      | 1 | 1 | 0 |

| 7       | 0      | 1 | 1 | 1 |

| 8       | 1      | 0 | 0 | 0 |

| 9       | 1      | 0 | 0 | 1 |

| 10      | 1      | 0 | 1 |   |

| 11      | 1      | 0 | 1 | 0 |

| 12      | 1      | 1 | 0 | 0 |

| 13      | 1      | 1 | 0 | 1 |

| 14      | 1      | 1 | 1 | 0 |

| 15      | 1      | 1 | 1 | 1 |

Figure C

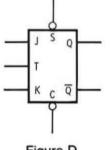

Figure D

Figure E

Figure A

Figure B

Figure C

Figure D

Figure E

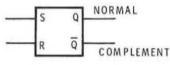

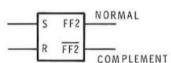

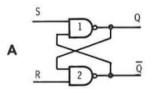

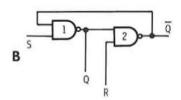

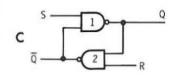

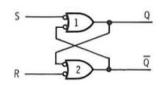

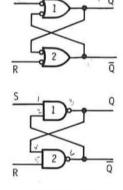

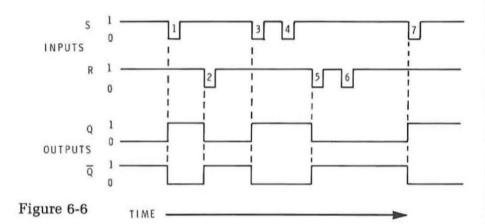

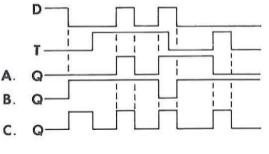

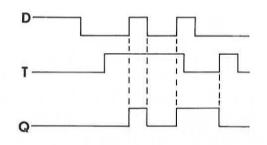

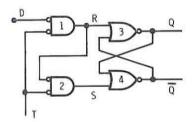

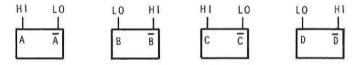

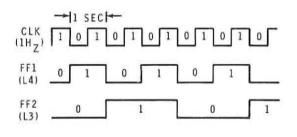

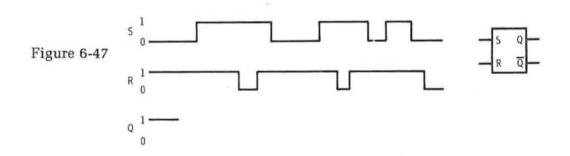

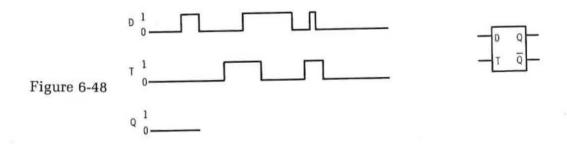

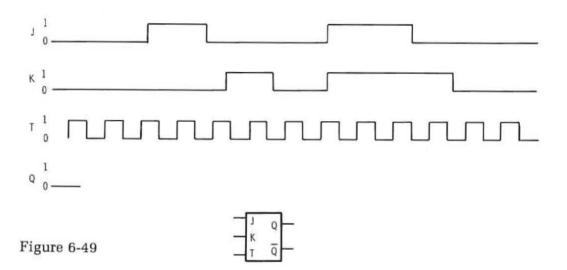

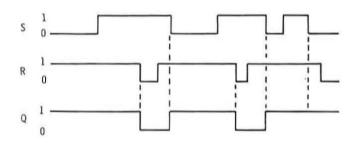

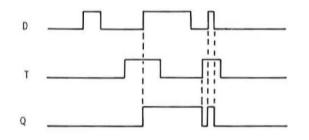

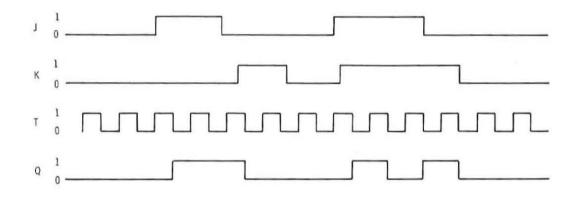

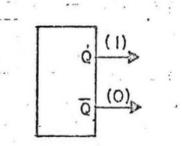

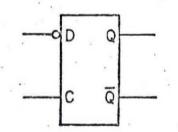

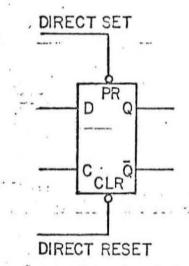

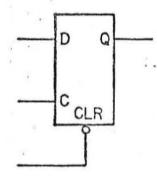

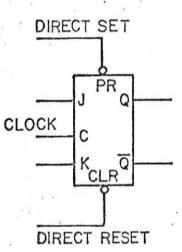

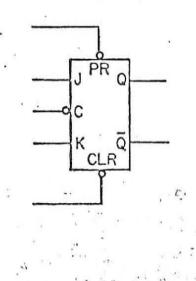

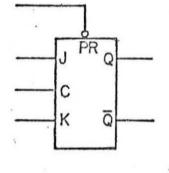

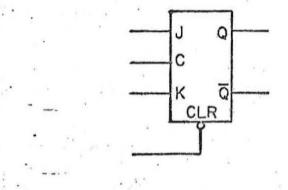

UNIT 6, Record 5, Side 2

Figure A

Figure B

Figure C

Figure D

# UNIT 1

# INTRODUCTION TO DIGITAL TECHNIQUES

EE-3201

HEATH COMPANY BENTON HARBOR, MICHIGAN 49022 Copyright © 1975 Seventeenth Printing — 1981 Heath Company Not Affiliated with D.C. Heath Inc. All Rights Reserved Printed in the United States of America

# CONTENTS

| Introduction                       |

|------------------------------------|

| Unit Objectives Page 1-4           |

| Unit Activity Guide Page 1-5       |

| Digital Techniques Page 1-6        |

| The Binary Number System Page 1-19 |

| Binary Codes                       |

| Data Representation Page 1-38      |

| Unit Summary Page 1-45             |

| Unit Examination Page 1-48         |

#### HEATHKIT CONTINUING EDUCATION

# UNIT 1

# INTRODUCTION TO DIGITAL TECHNIQUES

# INTRODUCTION

The purpose of this first unit on digital techniques is to give you an overview of the subject and to introduce you to the basic concepts. You will learn what digital techniques are, how they are used and why they are used. You will learn about binary numbers and codes which are the basic language of all digital systems. And finally, you will see how digital techniques are implemented with hardware.

This unit provides you with the background and base upon which you will build your knowledge of digital techniques. This foundation will put the concept of digital techniques into perspective so that you can fully relate them to the field of electronics. With the information presented here you will clearly understand the need for and uses of digital techniques.

Digital techniques are so widely used today that it is almost impossible to think of electronic equipment without them. Digital techniques are used in virtually every area of electronics. They have greatly improved electronic methods and have given us practical electronic equipment with amazing capability. And, there is potential for further improvements and advances. As an electronic engineer, technician, or hobbyist you can benefit by knowing digital techniques. This program will provide you with a solid understanding of digital methods and a guide to their application.

Examine the Unit Objectives listed in the next section to see what you will learn in this unit. Then follow the instruction in the Unit Activity Guide to be sure you perform all of the steps necessary to complete this lesson successfully. Check off each step as you complete it, and in the spaces provided, keep track of the time you spend on each activity.

## UNIT OBJECTIVES

When you complete this Unit you will have the following knowledge and capabilities:

- 1. Given a list of physical variables, components, devices, and other items, you will be able to classify them as being either analog or digital in nature.

- 2. You will be able to list at least five advantages of digital techniques over analog methods.

- 3. You will be able to list at least five examples of electronic equipment using digital techniques.

- 4. You will be able to state the factors that have most influenced the growth of digital techniques.

- 5. Given any decimal number, you will be able to convert it into its binary equivalent.

- 6. Given any binary number, you will be able to convert it into its decimal equivalent.

- 7. Given any decimal number, you will be able to convert it into its binary coded decimal (BCD) equivalent.

- 8. Given a BCD number you will be able to convert it into its decimal equivalent.

- 9. Given a list of popular digital codes, you will be able to read and identify them including pure binary, BCD, Gray, excess 3, and ASCII.

- 10. You will be able to list the two key ways binary data is represented with digital hardware.

- 11. You will be able to list the advantages and disadvantages of both serial and parallel methods of binary data transmission.

# UNIT ACTIVITY GUIDE

HEATHKIT

CONTINUING

63

| UN | III ACHVIII GOIDE                                                         | Completion<br>Time |

|----|---------------------------------------------------------------------------|--------------------|

|    | Play audio record: Side 1, Introduction to<br>Digital Techniques, Unit 1. |                    |

|    | Read section Digital Techniques:<br>Pages 1-6 to 1-16.                    |                    |

|    | Answer Self Test Review Questions 1-6.                                    |                    |

|    | Read section The Binary Number System:<br>Pages 1-19 to 1-26.             |                    |

|    | Answer Self Test Review Questions 7-13.                                   |                    |

|    | Read section Binary Codes: Pages 1-29 to 1-35.                            |                    |

|    | Answer Self Test Review Questions 14-21.                                  |                    |

|    | Read section Data Representation:<br>Pages 1-38 to 1-43.                  |                    |

|    | Answer Self Test Review Questions 22-27.                                  |                    |

|    | Complete the Unit Summary.                                                |                    |

|    | Complete the Unit Examination.                                            |                    |

|    | Construct Heathkit ET-3200 Digital<br>Design Experimenter.                |                    |

.

# **DIGITAL TECHNIQUES**

There are two basic types of electronic signals and techniques, analog and digital. Analog signals are the most familiar type. An analog signal is an ac or dc voltage or current that varies smoothly or continuously. It is one that does not change abruptly or in steps. An analog signal can exist in a wide variety of forms. Several types of analog signals are shown in Figure 1-1.

Figure 1-1 Types of Analog signals

Figure 1-1A shows the most common type of analog signal, a sine wave. A significant number of electronic signals are sinusoidal. Radio signals and audio tones are examples. A fixed dc voltage is also an analog signal. Figure 1-1B shows a constant positive dc voltage. Another type of analog signal is varying dc voltage or current. A changing negative dc voltage is illustrated in Figure 1-1C. Any random but continuously varying voltage waveform is considered to be analog. The signal shown in Figure 1-1D is only one of an infinite variety of such signals. Electronic circuits that process these analog signals are called linear circuits.

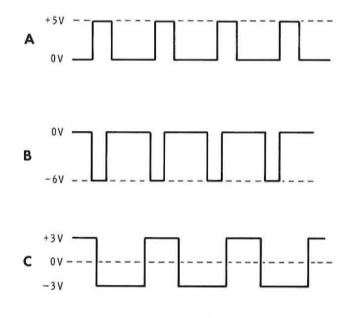

Digital signals are essentially a series of pulses or rapidly changing voltage levels that vary in discrete steps or increments. Digital signals are pulses of voltage that usually switch between two fixed levels. Figure 1-2 shows several types of digital signals. Notice how these signals switch between two distinct voltage levels. In Figure 1-2A, the two levels are 0 (ground) and +5 volts. In Figure 1-2B, the levels are 0 (ground) and -6 volts. In Figure 1-2C the signal alternates between the +3 and -3 volt levels. This two-level, off-on or up-down fast switching characteristic is fundamental of all digital signals. Electronic circuits that process these digital signals are called digital, logic, or pulse circuits.

## **Contrasting Analog and Digital Devices and Techniques**

Now let's further define analog and digital methods in terms of devices and ideas that are already quite familiar to you. For example, a light bulb can be either an analog or digital device depending upon how it is used. The amount of current through a light bulb can be set to any level less than its maximum rated value. We can vary the current through it continuously and its brightness will vary. Used in this way the light bulb is an analog device. The brilliance of the lamp is proportional to the current through it. There are virtually an infinite number of brightness levels.

The lamp can also be used as a digital device where the current through it and its brightness varies in discrete steps. The most common way of using the light bulb as a digital device is to give it two brilliance levels, usually off and on. The important point is that the lamp has two states. Because of this off-on characteristic, we say that the lamp is binary in nature. The term binary designates any two-state device or signal.

Let's take some other examples to illustrate the concept of analog and digital techniques. The VHF channel selector switch on your television set is digital in nature because it can assume only discrete positions. It can be set to any one of thirteen unique states, channels 2 through 13 and UHF. Any type of switch is a digital device because it has two or more discrete positions.

The volume control on your television set is an analog device. You can vary the volume of the sound continuously over a wide range from completely off to extremely loud.

The speedometer on your car is an analog device. It tells you the speed of your car in miles per hour on a smooth and continuously varying basis. You read the speed from a dial that is usually calibrated in no smaller increments than 5 miles per hour. To determine the speeds between the markings you must interpolate, or guess at, the exact speed.

The odometer portion of your speedometer, the part that indicates the number of miles traveled, is a digital device. Since the odometer records mileage in increments of one mile (or in some cases one-tenth mile), it is digital in nature.

Another example of an analog device is a typical clock or watch. It indicates the time continuously by the positions of the hands on a calibrated dial. The second hand sweeps smoothly and continuously around in an analog fashion as do both hour and minute hands. To determine the exact time, you must estimate the positions of the hands. Your ability to read the time accurately is limited by the precision of the dial calibration increments. Digital clocks overcome this problem. On a digital clock, you read the time directly from decimal number display readouts in discrete increments of hours, minutes and seconds. The accuracy is greatly improved and you gain the added convenience of a direct number display.

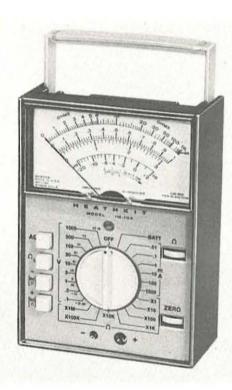

A standard voltmeter is also an analog device. It reads or measures voltage and indicates its value by the position of a pointer on a meter scale. The pointer moves smoothly or continuously as the amplitude of the analog voltage being measured varies. Of course, digital voltmeters are also available. These instruments measure the voltage and display it as discrete digits on a decimal readout.

A typical digital multimeter

Here are a few other analog quantities and devices. temperature — thermometer direction — compass light intensity — light meter

Keep in mind that all of these variables could be monitored and displayed as a digital readout.

Further examples of digital variables are: money heart pulse rate

## Where Are Digital Techniques Used?

Perhaps the greatest use of digital techniques today is in computers. Digital computers are used in virtually all areas of business and industry. They are extremely useful machines that can save man a tremendous amount of effort and greatly extend his capabilities.

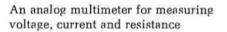

Over the years digital computers have grown in capability, but have become smaller, cheaper and easier to use. As a result, their use has increased tremendously. The small, low-cost but very powerful minicomputer has put digital and computer techniques within the reach

A typical minicomputer. (Photo courtesy Hewlett-Packard)

of nearly everyone. A minicomputer can be quickly and easily designed into a system to replace more conventional equipment and circuitry for control, computation and automation.

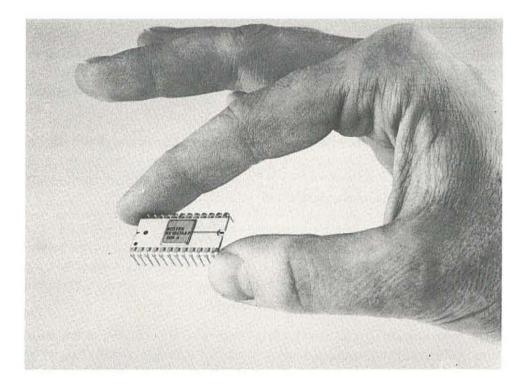

Advanced semiconductor technology has recently given us a computer that is really a component. Known as microprocessors, these devices are complete digital computers in a single miniature integrated circuit package. Microprocessors can replace minicomputers in many applications and can often be used to replace conventional digital circuits. Like all digital computers, the microprocessor must be programmed to carry out its specified function.

But computers aren't the only application for digital techniques. Digital methods are being employed in almost every imaginable area of electronics. Here are just a few examples.

**Communications.** Instead of transmitting information over wire lines or by radio by analog methods, much data is now being transmitted in digital form. It has been found that pulse type signals are easier to work with and are less susceptible to noise and other problems common in communications systems. Digital computers can readily communicate with one another by transmitting information over the telephone lines by using digital techniques.

**Telemetry systems.** Those systems used for transmitting measurement data from a remote location, use digital techniques extensively. In an unmanned satellite, for example, sensors are used to monitor various environmental conditions such as temperature, light, and radiation. The analog voltages produced by these sensors, in response to the quantity being measured, can be transmitted back to the earth via radio by modulating a carrier using conventional analog methods. However, it has been found that by converting the analog variables into digital signals, an improvement in transmission reliability and accuracy can be achieved. Today, telemetry systems in satellites and missiles make extensive use of digital techniques.

**Test Instruments.** The trend in test and measurement equipment is clearly toward the use of digital techniques. Besides the convenience of a direct decimal display and the increased precision of measurement brought about by the use of digital techniques, it is possible to interface many digital instruments with a computer. This permits automatic monitoring, controlling, measuring and recording of data.

The most common electronic test instrument, the analog voltmeter, is gradually being replaced by the more sophisticated digital voltmeter (DVM). The DVM does the same job as its analog counterpart. The DVM measures voltage but instead of presenting the reading to the observer in the form of a pointer on a meter face, the voltage is a direct readout display of decimal numbers. Such an instrument, while generally higher in cost than an analog voltmeter, is extremely convenient to use and read. More important, it gives more accurate measurements of voltages. The digital multimeter (DMM), a DVM with refinements, is capable of measuring voltages as well as resistance and current like an analog VOM.

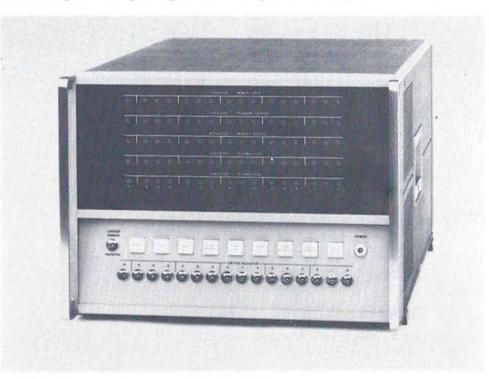

Another widely used digital test instrument is the electronic counter. This unit is widely used for measuring frequency and time intervals. Again the digital techniques provide a convenient decimal read-out of the exact quantity being measured, thereby eliminating man's need to interpolate continuous or analog meter scales to provide a reading. This result is greater accuracy and less error in measurement.

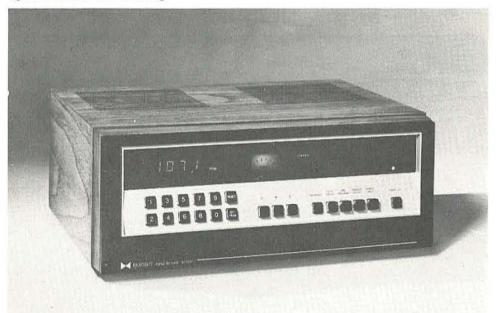

A digital counter used for measuring frequency. (Heath Co.)

**Industrial Controls**. Digital techniques are becoming more widely used in manufacturing plants and refineries where complex operations must be accurately controlled. These systems use sensors to monitor various phases of the operation, and the outputs of these sensors are then used to produce signals that will control the various operations that affect the process.

Industrial feedback control systems have traditionally used analog techniques. Today, many of these control systems are digital in nature. Most involve both analog and digital methods. Analog quantities like temperature, pressure, liquid level and flow rate are monitored by sensors to produce an analog signal. These are converted into digital values by analog-to-digital converters. Other system inputs are already digital in nature such as limit switches or sensors of an off-on or go no-go nature.

All of this digital information is fed into a digital computer which monitors the input variables and according to a predetermined program generates output signals to control the process.

Another popular industrial application for digital techniques is machine tool control. Here a digital computer controls the drilling, cutting, punching and stamping of materials to produce specific metal parts accurately and automatically.

**Consumer Electronic Equipment**. Perhaps the biggest holdout against the use of digital techniques has been common consumer items such as radio, TV, hi-fidelity and other products. The higher cost of some digital methods has been the major reason for the delay in adopting these techniques. However, as prices of digital circuits have dropped, even these products have given way to the use of digital techniques. An example is the circuitry for digital channel selection used in some of the newer color television sets. Some hi-fi receivers use digital frequency synthesizers for tuning.

An FM tuner using digital techniques for frequency selection and display (Heath Co.)

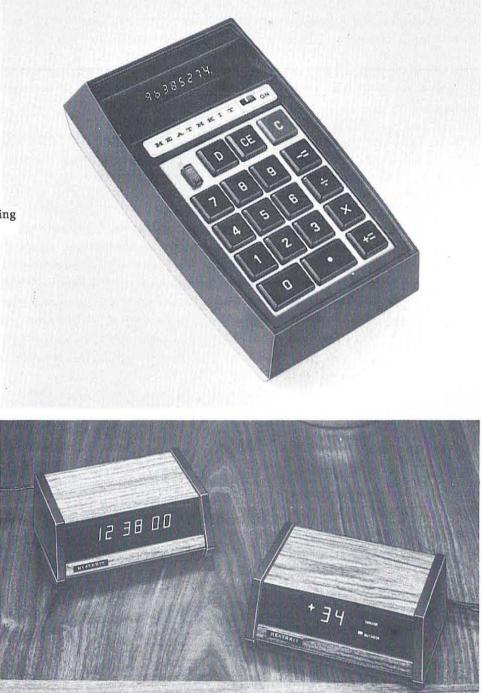

Other popular consumer devices using digital methods are the popular digital clocks and electronic calculators. Even a home digital thermometer is available.

Handheld electronic calculator using digital circuits (Heath Co.)

Digital clock and thermometer. (Heath Co.)

While consumer electronic devices will continue to use analog techniques, more digital controls and circuits will gradually be added to increase versatility and improve performance.

Where are digital techniques used? The answer is almost everywhere in electronics. And their use will increase. Why are digital techniques used? Digital methods are used basically to obtain greater resolution of measurement, control or calculation, and for convenience.

# Why Use Digital Techniques?

The primary impetus for the widespread use of digital techniques has been the availability of low cost, digital integrated circuits (ICs). Advances in integrated circuit technology have produced many excellent low cost digital circuits. Such circuits are small, inexpensive and very reliable. The more recent medium scale and large scale (MSI and LSI) integrated devices can replace entire circuits and instruments. Electronic equipment designers recognize the availability of such devices and have begun to take advantage of them. While digital techniques have been known for years, it took integrated circuits to make them practical.

A large scale integrated circuit. (Photo courtesy MOSTEK).

By using digital IC's many equipment improvements have been made. Reductions in size, weight, cost and power consumption usually result when analog techniques are replaced by digital methods, thanks to digital IC's. Here are a few more reasons why digital techniques have become so popular.

**Greater accuracy**. Digital techniques permit greater precision and resolution in representing quantities or in making measurements than with analog methods.

**Greater Dynamic Range**. Dynamic range is the difference between the upper and lower data values that a system or instrument can handle. Analog systems are limited because of component capabilities and noise to a range of something less than 100,000 to 1. With digital techniques practically any desired dynamic range can be obtained.

**Greater Stability**. Analog or linear circuits are subject to the effects of drift and component tolerance problems. Temperature and other environmental factors affect resistor, capacitor and inductance values. Transistor biases vary causing non-linear operation and distortion to occur. Component imperfections and ageing cause drift and resultant problems. Digital methods greatly minimize or completely eliminate such problems.

**Convenience**. Digital techniques make instruments and equipment more convenient to use. The direct decimal display of data is not only more convenient, but the error of reading or interpolating analog meters or in setting analog dials is eliminated.

Automation. Many electronic processes can be fully automated if digital techniques are used. Special control circuits or a digital computer which are programmed can automatically, set up, control and monitor many operations. Data is readily recorded, stored and displayed.

**Design Simplicity**. Digital equipment is relatively easy to design. The available digital ICs make digital design a pleasure. Little or no breadboarding is required. In analog or linear circuits breadboarding is mandatory to ensure a workable circuit. Digital equipment can go from paper design to finished product in a very short time.

New Approaches. Digital methods permit new approaches to the solution of electronic equipment design. In addition, design solutions impossible with analog techniques are readily implemented with digital circuits. Digital circuits make it possible to do some things that have no analog equivalent.

# **Self Test Review**

1. Analog Signals vary \_\_\_\_\_ while digital signals vary

- 2. Identify the following items as being either analog or digital in nature.

- a. height of a human \_\_\_\_\_

- b. dice \_\_\_\_\_

- c. pages of a book \_\_\_\_\_

- d. typewriter \_\_\_\_\_

- e. barometric pressure \_\_\_\_\_

- f. slide rule \_\_\_\_\_

3. How many discrete voltage levels do most digital signals have?

4. The most widespread use of digital techniques is in \_\_\_\_\_

- 5. List 3 advantages of digital methods over analog techniques.

- a. \_\_\_\_\_

- b. \_\_\_\_\_

- c. \_\_\_\_\_

- 6. The single factor most influential in the increased use of digital techniques was the

- a. recognition of the deficiencies in analog methods.

- b. development of integrated circuits.

- c. discovery of digital methods.

- d. developments resulting from the space program.

| 1. | continuously (or smoothly), in steps (in discrete incre-<br>ments, etc.) |

|----|--------------------------------------------------------------------------|

| 2. | a. analog                                                                |

|    | b. digital                                                               |

|    | c. digital                                                               |

|    | d. digital                                                               |

|    | e. analog                                                                |

|    | f. analog                                                                |

| 3. | Two (2)                                                                  |

| 4. | computers                                                                |

| 5. | greater accuracy                                                         |

|    | greater dynamic range                                                    |

|    | convenience of direct decimal display                                    |

|    | and many others.                                                         |

| 6  | (b) development of integrated circuits                                   |

TINUIN EDUCATION

### THE BINARY NUMBER SYSTEM

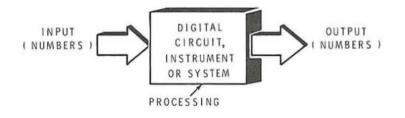

All digital circuits, instruments and systems work with numbers that represent specific quantities. For example, the analog voltage measured by a digital voltmeter is converted into digital form and displayed as a specific decimal number. The number that you enter into an electronic calculator is stored and used in the calculation you specify. The digital computer that prints your payroll check works with numbers, specifically your salary, the number of hours you work and the various deductions. As you can see, numbers or quantities are the basic source for an end product of most digital equipment. Figure 1-3 shows how most digital equipment accepts input numbers, processes them and generates number outputs. The actual form of the input and output numbers depends on the application. They may be in binary or decimal form. In some applications the input and/or output may be in analog form despite the digital processing.

Figure 1-3 A general block diagram of any digital system

The type of numbers we are most familiar with are decimal numbers. In the decimal number system we combine the ten digits 0 through 9 in a certain way so that they indicate a specific quantity. In the binary number system, we use only two digits, 0 and 1. These binary digits, or bits, when appropriately arranged can also represent any decimal number. For example, the binary number 110101 represents the decimal quantity 53. All modern digital techniques are based on the binary number system.

The basic distinguishing feature of a number system is its base or radix. The base indicates the number of characters or digits used to represent quantities in that number system. The decimal number system has a base or radix of 10 because we use the ten digits 0 through 9 to represent quantities. The binary number system has a base of 2 since only the digits or bits 0 and 1 are used in forming numbers. The decimal number system came about basically as a result of man having ten fingers. Man's earliest attempts to represent numbers, count and keep track of quantities involved the use of his fingers. Of course, the decimal number system is universally used and understood because it is our way of communicating information about quantities.

The binary number system, while simple, is inconvenient to use because we are not familiar with it. But once you learn it, you will find it easy to work with. It has special benefits when it comes to constructing the hardware used in digital equipment.

Digital systems can be implemented with either the decimal or binary number systems. However, the advantages of the binary number systems over the decimal number system in terms of hardware implementation are many. If we use the decimal number system, our hardware must have ten discrete steps or states each representing one of the digits 0 through 9. Various types of electrical, electromechanical, or electronic components and circuits are available to do this. A ten position rotary switch or a stepping relay are examples. However, when the binary number system is used, we only need to represent two states. An electronic component or circuit that has only two states is significantly simpler, less expensive, faster and more reliable than one with ten. Each bit can be implemented with components of a simple off/on nature such as switch or relay contacts or a transistor that conducts or does not conduct.

#### **Positional Number Systems**

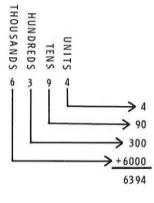

The decimal and binary number systems are positional or weighted number systems. This means that each digit or bit position in a number carries a particular weight in determining the magnitude of that number. For example, you know that a decimal number has positional weights of units, tens, hundreds, thousands, etc. Each position has a weight that is some power of the number system base, in this case ten. The positional weights are  $10^{0} = 1$  (units)<sup>\*</sup>,  $10^{1}$  (tens),  $10^{2}$  (hundreds), etc. We evaluate the total quantity represented by considering the specific digits and the weights of their positions. Consider the decimal number 7438 in which there are 8 ones, 3 tens, 4 hundreds, and 7 thousands. The number can be written as indicated below.

$$(7 \times 10^3) + (4 \times 10^2) + (3 \times 10^1) + (8 \times 10^0) =$$

7000 + 400 + 30 + 8 = 7438

To determine the value of the number, you multiply each digit by the weight of its position and add your results.

HEATHKIT CONTINUING EDUCATION

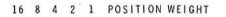

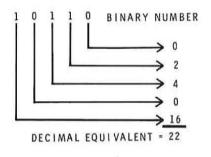

Binary numbers work the same way. Each bit position carries a specific weight. As in the decimal number system, the position weights are some power of the base of the number system. These weights from right to left are  $2^0 = 1^*$ ,  $2^1 = 2$ ,  $2^2 = 4$ ,  $2^3 = 8$ , etc. The weight of each position is twice that of the weight of the number to the right. Consider the binary number 110101. This can be written as indicated below.

$$(1 \times 2^5) + (1 \times 2^4) + (0 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) =$$

$32 + 16 + 0 + 4 + 0 + 1 = 53$

The quantity represented by the number is determined by multiplying each bit by its position weight and obtaining the sum.

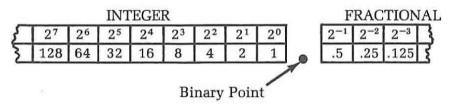

# **Fractional Numbers**

So far we have only discussed whole numbers or integer quantities. But as you know it is often necessary to express quantities in terms of fractional parts of a whole.

Decimal fractions are numbers whose positions have weights that are negative powers of ten such as  $10^{-1} = 1/10 = .1$ ,  $10^{-2} = 1/100 = .01, 10^{-3} = 1/1000 = .001$ , etc. A decimal point separates the whole and fractional parts of a number. The integer or whole number portion is to the left of the decimal point and has weights of units, tens, hundreds, etc. The fractional part of the number is to the right of the decimal point and the positions have weights of tenths, hundredths, thousandths, etc. To illustrate this, the number 278.94 can be written as shown below.

$$(2 \times 10^2) + (7 \times 10^1) + (8 \times 10^0) + (9 \times 10^{-1}) + (4 \times 10^{-2}) =$$

200 + 70 + 8 + .9 + .04 = 278.94

In a fractional binary number, the weights of the fractional positions are negative powers of 2 or  $2^{-1} = \frac{1}{2} = .5$ ,  $2^{-2} = \frac{1}{4} = .25$ ,  $2^{-3} = \frac{1}{8} = .125$ ,  $2^{-4} = \frac{1}{16} = .0625$ , etc. The position weight is one half of the weight of the position directly to the left. A binary point separates the whole and fractional parts of the number.

The binary number 1101.101 is evaluated as shown below.

$(1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) + (1 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3}) =$ 8 + 4 + 0 + 1 + .5 + 0 + .125 = 13.625

<sup>\*</sup>Any number with an exponent of zero is equal to one.

#### Converting Between The Binary and Decimal Number Systems

In working with digital equipment, you will often need to determine the decimal value of binary numbers. In addition, you will also find it necessary to convert a specific decimal number into its binary equivalent. Let's see how such conversions are accomplished.

**Binary to Decimal**. To convert a binary number into its decimal equivalent you simply add together the weights of the positions in the number where binary 1's occur. The weights of the integer and fractional positions are indicated below.

As an example, let's convert the binary number 1010 into its decimal equivalent. Since no binary point is shown, the number is assumed to be a whole number where the binary point is to the right of the number. The right-most bit, called the least significant bit or LSB, has the lowest integer weight of  $2^0 = 1$ . The left-most bit is the most significant bit (MSB) because it carries the greatest weight in determining the value of the number. In this example, it has a weight of  $2^3 = 8$ . To evaluate the number we add together the weights of the positions where binary 1's appear. In this example, 1's occur in the  $2^3$  and  $2^1$  positions. The decimal equivalent is ten.

| <b>Binary Number</b>    | 1   | 0   | 1   | 0   |      |

|-------------------------|-----|-----|-----|-----|------|

| <b>Position Weights</b> | (8) | (4) | (2) | (1) |      |

| Decimal Equivalent      | 8 + | 0 + | 2 + | 0   | = 10 |

As a further illustration of this process, let's convert the binary number 101101.11 into its decimal equivalent.

| Binary Number           | 1    | 0    | 1   | 1   | 0   | 1   | .1   | 1     |   |       |

|-------------------------|------|------|-----|-----|-----|-----|------|-------|---|-------|

| <b>Position Weights</b> | (32) | (16) | (8) | (4) | (2) | (1) | (.5) | (.25) |   |       |

| Decimal Equivalent      | 32+  | 0+   | 8+  | 4+  | 0+  | 1+  | .5+  | .25   | = | 45.75 |

Note that you can disregard the position weights where binary 0s occur since they add nothing to the number value.

After you solve a few practice problems, you will quickly catch on to this procedure.

**Decimal to Binary**. Converting a known decimal number into its binary equivalent can be accomplished by a simple trial and error method once you are familiar with the weighting sequence of binary numbers. Suppose that you wish to convert the decimal number 175 into its binary equivalent. To do this you first determine the highest positional weight that is equal to or less than the number being converted. This is 128. Subtract 128 from 175 and note the remainder.

$$\begin{array}{r}

175 \\

- 128 \\

\overline{47}

\end{array}$$

Again determine the highest positional weight that does not exceed the remainder. This is 32. Next determine their difference and continue to repeat the process until no further subtractions are possible.

The highest positional weight less than 15 is 8.

The highest positional weight less than 7 is 4.

The highest positional weight less than 3 is 2.

$$\frac{3}{-2}{1}$$

And finally, the highest positional weight less than or equal to 1 of course is 1.

Now using this information you construct the equivalent binary number. You write a binary 1 for the weight positions you subtracted from the original number and the remainders. In this exmple, these were 128, 32, 8, 4, 2 and 1. Note that you did not use the 64 and 16 weights, so these positions will be binary 0. The number then is 10101111 = 175. You can check it by converting the binary version back into decimal form using the procedure discussed earlier.

Another method for converting decimal numbers into binary is to repeatedly divide the number by 2 and note the remainder. When dividing by 2, the remainder will always be either 1 or 0. The remainder forms the equivalent binary number.

As an example, convert the number 175 into its binary equivalent.

|                   | REMAINDER            |

|-------------------|----------------------|

| $175 \div 2 = 87$ | 1 <b>→</b> LSB       |

| $87 \div 2 = 43$  | 1                    |

| $43 \div 2 = 21$  | 1                    |

| $21 \div 2 = 10$  | 1                    |

| $10 \div 2 = 5$   | 0                    |

| $5 \div 2 = 2$    | 1                    |

| $2 \div 2 = 1$    | 0                    |

| $1 \div 2 = 0$    | 1 <del>≺−−</del> MSB |

#### **Binary Number Sizes**

Binary numbers are also referred to as binary words. An 8 bit binary number is also an 8 bit word. You will also see the term byte used to refer to binary words. Most digital circuits and equipment use a fixed word size. The size of this word determines the maximum magnitude and resolution with which numbers can be represented. The number of bits in a word determine the number of discrete states that can exist and the maximum decimal number value that can be represented.

The formula below indicates the number of states that can be represented with a given number of bits.

$N=2^n$  N= total number of states.

n = number of bits in the word.

For example, with a 4-bit word, we can represent a maximum of

$N = 2^n = 2^4 = 2 \times 2 \times 2 \times 2 = 16$

This means that by using 4-bit positions, we can create a total of 16 different binary bit patterns or number combinations. These are shown in Table I along with their decimal equivalents.

| DECIMAL | BINARY |

|---------|--------|

| 0       | 0000   |

| 1       | 0001   |

| 2       | 0010   |

| 3       | 0011   |

| 4       | 0100   |

| 5       | 0101   |

| 6       | 0110   |

| 7       | 0111   |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

| 11      | 1011   |

| 12      | 1100   |

| 13      | 1101   |

| 14      | 1110   |

| 15      | 1111   |

TABLE I

Binary and decimal number equivalents for a 4-bit word.

As Table I indicates we represent the numbers 0 through 15 using the binary number weighting system. The maximum decimal number that can be represented is one less than the total number of states. The largest decimal number value (N) that can be represented for a given number of bits (n) is expressed with the formula below.

$$N = 2^n - 1$$

For example, with a 6-bit number we can represent a maximum value of

$$N = 2^6 - 1 = 64 - 1 = 63$$

HEATHKIT CONTINUING EDUCATION

If you know the maximum decimal quantity (N) that you wish to represent with a binary number, you can determine the required number of bits (B) with the expression given below.

$$B = 3.32 \log_{10} N$$

The common logarithm can be obtained from a set of tables, a slide rule or an electronic calculator with log capability. For example, if the maximum decimal number that you need to represent is 500, the number of bits required is:

> $B = 3.32 \log_{10} 500$ B = 3.32 (2.69897) B = 8.96

Of course you cannot implement fractional bits so the total number of bits required is the next highest whole number. Therefore, to represent the number 500, you would need a total of nine bits. Using the previously given expression, you can determine that, with a total of nine bits, the maximum number you can represent is

$N = 2^n - 1 = 2^9 - 1 = 512 - 1 = 511$

The Appendix at the end of this unit contains a table of numbers that are powers of 2. It will help you to quickly determine the relationship between decimal number size and binary word bit length.

#### Number Identification

When working with both binary and decimal numbers, it is often necessary to have some way of identifying whether a number is a decimal or a binary number. This is particularly true of numbers involving only ones and zeros. For example, the number 101 could represent a quantity of one hundred and one if it is a decimal number. However, if this number is in binary form it would represent a quantity of five.

To distinguish binary from decimal numbers a small subscript number is generally written after the number. The identifying subscript number is the base or radix of the number system being used. Several examples of this notation are indicated below.

$$101_2 = 5_{10}$$

$$101_{10} = 1100101_2$$

#### HEATHKIT CONTINUING EDUCATION

# Self Test Review

- 7. The radix of the binary number system is \_\_\_\_\_\_.

- 8. Binary hardware is preferred over decimal hardware in digital equipment because binary components are

- a. \_\_\_\_\_

- b. \_\_\_\_\_

- C. \_\_\_\_\_

- 9. Convert the following binary numbers to decimal.

- a. 100101101

- b. 11100.1001

- c. 111111

- d. 100000.0111

### 10. Convert the following decimal numbers to binary.

- a. 127

- b. 38

- c. 22.5

- d. 764.375

- 11. What is the largest decimal number that can be represented with 8 bits?

- 12. How many discrete states can be represented with 6 bits?

- 13. How many bits does it take to represent the number 3875 in binary?

# Answers 7.2 8. a. faster b. simpler c. more reliable 9. a. $100101101_2 = 301_{10}$ b. $11100.1001_2 = 28.5625_{10}$ c. $111111_2 = 63_{10}$ d. $100000.0111_2 = 32.4375_{10}$ 10. a. $127_{10} = 1.111111_2$ b. $38_{10} = 100110_2$ c. $22.5_{10} = 10110.1$ d. $764.375_{10} = 1011111100.011$ 11. $M = 2^8 - 1 = 256 - 1 = 255$ 12. $N = 2^6 = 64$ 13. $B = 3.32 \log_{10} 3875 = 3.32 (3.58827) = 11.91 12$ bits

# **BINARY CODES**

The general term given to the process of converting a decimal number into its binary equivalent is coding. We express a decimal number as a binary code or binary number. The binary number system, as discussed, is known as the pure binary code. We give it this name to distinguish it from other types of binary codes. In this section you will see some of the other types of binary codes used in digital systems.

# **Binary Coded Decimal**

Because the decimal number system is so familiar, it is easy to use. The binary number system is less convenient to use because we are not as intimately familiar with it. It is difficult to quickly glance at a binary number and recognize its decimal equivalent. For example, the binary number 1010011 represents the decimal number 83. You certainly cannot tell immediately by looking at the number what its decimal value is. However, you know that within a few minutes, using the procedures described earlier, that you could readily calculate its decimal value. The amount of time that it takes you to convert or recognize a binary number quantity is a distinct disadvantage in working with this code despite the numerous hardware advantages. Digital engineers recognized this problem early and developed a special form of binary code that was more compatable with the decimal system. Because so many digital devices, instruments and equipment use decimal input and output, this special code has become very widely used and accepted. This special compromise code is known as binary coded decimal (BCD). The BCD code combines some of the characteristics of both the binary and decimal number systems.

The BCD code is a system that represents the decimal digits 0 through 9 with a four-bit binary code. This BCD code uses the standard 8421 position weighting system of the pure binary code. The standard 8421 BCD code and the decimal equivalents are shown in Table II. As with the pure binary code, you can convert the BCD numbers into their decimal equivalents by simply adding together the weights of the bit positions whereby the binary 1's occur. Note, however, that there are only ten possible valid four bit code arrangements. The 4-bit binary numbers representing the decimal numbers 10 through 15 are invalid in the BCD system.

| 8421 BC |      |

|---------|------|

| DECIMAL | BCD  |

| 0       | 0000 |

| 1       | 0001 |

| 2       | 0010 |

| 3       | 0011 |

| 4       | 0100 |

| 5       | 0101 |

| 6       | 0110 |

| 7       | 0111 |

| 8       | 1000 |

| 9       | 1001 |

TABLE II

| appr | resent a decimal number in BCD notation you simply substitute<br>priate four bit code for each decimal digit. For example, the num<br>BCD would be 1000 0011 0100. Each decimal digit is represen | ber |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | equivalent 8421 four bit code. A space is left between each four<br>in order to avoid confusing the BCD format with the pure bin                                                                  |     |

The beauty of the BCD code is that the ten BCD code combinations are very easily remembered. Once you begin to work with binary numbers on a regular basis you will find that the BCD numbers will come to you as quickly and automatically as decimal numbers. For that reason by simply glancing at the BCD representation of a decimal number you can make the conversion almost as quickly as if it were already in decimal form.

While the BCD code does help to simplify the man-machine interface it is less efficient than the pure binary code. It takes more bits to represent a given decimal number in BCD than it does with pure binary notation. For example, the decimal number 83 in pure binary form is 1010011. In BCD code the decimal number 83 is written as 1000 0011. In the pure binary code it takes only a 7 bit word to represent the number 83. In BCD form it takes 8 bits. The inefficiency arises out of the fact that for each bit in a data word there is usually a certain amount of digital circuitry associated with it. The extra circuitry associated with the BCD code costs more, increases equipment complexity, and consumes more power. Arithmetic operations with BCD numbers are also more time consuming and complex than those with pure binary numbers. As you recall, with four bits of binary information we can represent a total of  $2^4 = 16$  different states or the decimal number equivalents 0 through 15. In the BCD system we waste six of these states (10-15), thus the inefficiency. When we use the BCD number system we trade off some efficiency for the improved communications between the digital equipment and the human operator.

# **Special Binary Codes**

Besides the standard pure binary coded form, the BCD numbering system is by far the most widely used digital code. You will find one or the other in most of the applications that you encounter. However, there are several other codes that are used for special applications. Let's consider some of these.

NA **Excess 3 Code**. The excess 3 code (sometimes abbreviated XS3) is not a weighted code. Here each four bit number is three greater than the standard 8421 code number. To obtain the excess 3 code of a specific decimal number, you simply add 3 to it then use the corresponding 8421 binary code (Table I). For example, the excess 3 code for the number 7 is the binary equivalent of 7 + 3 = 10. The four bit excess 3 code for the number 7 then is 1010. To convert from XS3 to decimal, you simply write the decimal equivalent of each four bit group then subtract three from each digit. The excess 3 code was developed primarily because of its ability to greatly simplify the arithmetic computations with BCD numbers.

M P Gray Code: The Gray Code is a widely used non-weighted code system. Also known as the cyclic, unit distance or reflective code, the Gray code can exist in either the pure binary or BCD formats. The Gray code is shown in Table III. As with the pure binary code, the first ten codes are used in BCD operations. Notice that there is a change in only one bit from one code number to the next in sequence. You can get a better idea about the Gray code sequence by comparing it to the standard four bit 8421 pure binary code also shown in Table III. For example, consider the change from 7 (0111) to 8 (1000) in the pure binary code. When this change takes place all bits change. Bits that were 1's are changed to 0's and 0's are changed to 1's. Now, notice the code change from 7 to 8 in the Gray code. Here 7 (0100) changes to 8 (1100). Only the first bit changes.

| TABLE III | EШ | TABL |

|-----------|----|------|

|-----------|----|------|

THE GRAY CODE

| DECIMAL | GRAY | PURE BINARY |

|---------|------|-------------|

| 0       | 0000 | 0000        |

| 1       | 0001 | 0001        |

| 2       | 0011 | 0010        |

| 3       | 0010 | 0011        |

| 4       | 0110 | 0100        |

| 5       | 0111 | 0101        |

| 6       | 0101 | 0110        |

| 7       | 0100 | 0111        |

| 8       | 1100 | 1000        |

| 9       | 1101 | 1001        |

| 10      | 1111 | 1010        |

| 11      | 1110 | 1011        |

| 12      | 1010 | 1100        |

| 13      | 1011 | 1101        |

| 14      | 1001 | 1110        |

| 15      | 1000 | 1111        |

The Gray code is generally known as an error-minimizing code because it greatly reduces the possibility of ambiguity in the electronic circuitry when changing from one state to the next. When binary codes are implemented with electronic circuitry, it takes a finite period of time for bits to change from 0 to 1 or 1 to 0. These state changes can create timing and speed problems. This is particularly true in the standard 8421 codes where many bits change from one combination to the next. When the Gray code is used, however, the timing and speed errors are greatly minimized because only one bit changes at a time. This permits code circuitry to operate at higher speeds with fewer errors.

The biggest disadvantage of the Gray code is that it is difficult to use in arithmetic computations. Where numbers must be added, subtracted or used in other computations, the Gray code is not applicable. In order to perform arithmetic operations the Gray code number must generally be converted into pure binary form.

**ASCII Code**. The ASCII code is a special form of BCD code that is widely used in digital computers and data communications equipment. This code is known as the American Standard Code for Information Interchange (ASCII). It is a 7 bit binary code that is used in transferring data between computers and their external peripheral devices and in communicating data by radio and telephone lines. With 7 bits we can represent a total of  $2^7 = 128$  different states or characters. The ASCII code is used to represent the decimal numbers 0 through 9, the letters of the alphabet (both upper and lower case) plus other special characters used for controlling various computer peripheral devices and communications circuits. The standard ASCII code is shown in Table IV.

# HEATHKIT CONTINUING EDUCATION HEA

|     | COLUMN   | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|-----|----------|-----|-----|-----|-----|-----|-----|-----|-----|

| ROW | BITS 765 | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| 0   | 0000     | NUL | DLE | SP  | 0   | @   | Р   | x   | р   |

| 1   | 0001     | SOH | DC1 | I   | 1   | А   | Q   | а   | q   |

| 2   | 0010     | STX | DC2 | ••  | 2   | В   | R   | b   | r   |

| 3   | 0011     | ETX | DC3 | #   | 3   | С   | S   | с   | s   |

| 4   | 0100     | EOT | DC4 | \$  | 4   | D   | Т   | d   | t   |

| 5   | 0101     | ENQ | NAK | %   | 5   | Е   | U   | e   | u   |

| 6   | 0110     | ACK | SYN | &:  | 6   | F   | v   | f   | v   |

| 7   | 0111     | BEL | ETB | '   | 7   | G   | W   | g   | w   |

| 8   | 1000     | BS  | CAN | (   | 8   | Н   | X   | h   | х   |

| 9   | 1001     | HT  | EM  | )   | 9   | I   | Y   | i   | У   |

\*

+

,

-

.

1

;

;

<

=

>

?

J

K

L

M

N

0

Z

I

١

1

~

-----

j

k

1

m

n

0

z {

ł

}

~

DEL

|   |          | T    | ABLE | IV          |     |

|---|----------|------|------|-------------|-----|

| N | STANDARD | CODE | FOR  | INFORMATION | INT |

| 0111/011 | 11 | # 7 |

|----------|----|-----|

| 7        |    |     |

10

11

12

13

14

15

1010

1011

1100

1101

1110

1111

LF

VT

$\mathbf{F}\mathbf{F}$

CR

SO

SI

SUB

ESC

FS

GS

RS

US

| Explanation of special     | control function  | is in columns 0, 1, 2 and 7. |

|----------------------------|-------------------|------------------------------|

| mapratication of opoolding | control ranotior. | 13  m columns 0, 1, 2 and 7. |

| NUL | Null                                      | DLE | Data Link Escape        |

|-----|-------------------------------------------|-----|-------------------------|

| SOH | Start of Heading                          | DCI | Device Control 1        |

| STX | Start of Text                             | DC2 | Device Control 2        |

| ETX | End of Text                               | DC3 | Device Control 3        |

| EOT | End of Transmission                       | DC4 | Device Control 4        |

| ENQ | Enquiry                                   | NAK | Negative Acknowledge    |

| ACK | Acknowledge                               | SYN | Synchronous Idle        |

| BEL | Bell (audible signal)                     | ETB | End of                  |

|     |                                           |     | Transmission Block      |

| BS  | Backspace                                 | CAN | Cancel                  |

| HT  | Horizontal Tabulation (punched card skip) | EM  | End of Medium           |

| LF  | Line Feed                                 | SUB | Substitute              |

| VT  | Vertical Tabulation                       | ESC | Escape                  |

| FF  | Form Feed                                 | FS  | File Separator          |

| CR  | Carriage Return                           | GS  | Group Separator         |

| SO  | Shift Out                                 | RS  | <b>Record Separator</b> |

| SI  | Shift In                                  | US  | Unit Separator          |

| SP  | Space (blank)                             | DEL | Delete                  |

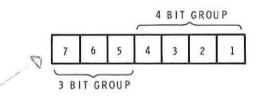

The 7-bit ASCII code for each number, letter or control function is made up of a 4 bit group and a 3 bit group. Figure 1-7 shows the arrangement of these two groups and the numbering sequence. The 4-bit group is on the right and bit 1 is the LSB. Note how these groups are arranged in rows and columns in Table IV.

To determine the ASCII code for a given number letter or control operation, you locate that item in the table. Then you use the three and four bit codes associated with the row and column in which the item is located. For example, the ASCII code for the letter L is 1001100. It is located in column 4, row 12. The most significant 3 bit group is 100 while the least significant four bit group is 1100.

There are both 6 and 8 bit special versions of the ASCII code. In addition, the International Business Machines Corporation (IBM) uses another 8 bit coding system called Extended Binary Coded Decimal Interchange Code (EBCDIC) instead of ASCII, for its peripheral and data communications operations.

Figure 1-7 ASCII Code Word Format

# **Self Test Review**

14. The BCD code is better than the binary code because

- a. it uses less bits.

- b. it is more compatible with the decimal number system.

- c. it is more adaptable to arithmetic computations.

- d. there are more different coding schemes available.

- 15. Convert the following decimal numbers to 8421 BCD code.

- a. 1049

- b. 267

- c. 835

- 16. Convert the following 8421 BCD code number to decimal.

- a. 1001 0110 0010

- b. 0111 0001 0100 0011

- c. 1010 1001 1000

- d. 1000 0000 0101

- 17. Which code is best for minimum hardware errors?

- a. Excess 3

- b. 8421 BCD

- c. pure binary

- d. Gray

- 18. Which BCD code is best for arithmetic operations?

- a. Gray

- b. 8421

- c. Excess 3

- d. ASCII

- 19. Convert the following Excess 3 BCD code to decimal. 1100 0111 0100 0110

- 20. The ASCII code is used primarily in \_\_\_\_\_ and

- 21. What is the ASCII code for the letter "f"? \_\_\_\_\_.

#### HEATHKIT CONTINUING EDUCATION

# Answers

- 14. b. more compatible with the decimal system.

- 15. a. 0001 0000 0100 1001

- b. 0010 0110 0111

- c. 1000 0011 0101

- 16. a. 962

- b. 7143

- c. invalid (1010)

- d. 805

- 17. d. Gray

- 18. c. Excess 3

- 19. 941310

- 20. computers, data communications.

- 21. 1100110

#### **DATA REPRESENTATION**

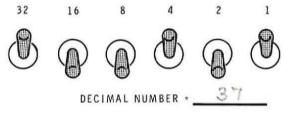

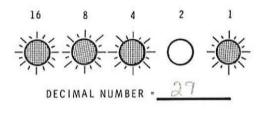

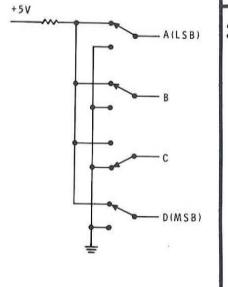

Now that you understand the reason for using the binary number system and are familiar with some of the binary coding schemes used in digital equipment, you are ready to consider the actual hardware means of implementing these binary numbers. By hardware we mean the electronic components and circuits that are used to represent and manipulate the binary numbers used in the digital system. It is relatively easy to represent a binary number with electronic components. The component to represent a specific bit in a binary word must be capable of assuming two distinct states. One of the states will represent a binary 0 and the other a binary 1.

#### **Electromechanical Devices**

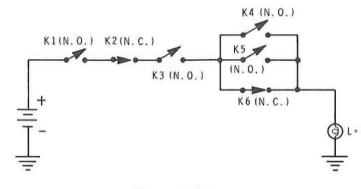

Switches and relays are ideal for representing binary data. A closed switch or relay contact can represent a binary 1 while the open switch or contact can represent a binary 0. Of course these logic representations can also be reversed. Switches and relays are still widely used to implement digital systems or parts of digital equipment. They are used in places where static binary conditions are required or very low speed operation can be tolerated.

Early digital equipment such as computers and test instruments used relays to represent binary numbers. But the relays were soon replaced by vacuum tubes in many applications. Each bit was represented by a vacuum tube that was either conducting or cut-off. When the tube was conducting it represented one binary state and when it was cut-off it represented the other binary state. Vacuum tubes worked well in digital applications. They achieved operating speeds significantly higher than that of relays. However, because of their large size, high power consumption and speed limitations they have been replaced by solid state devices.

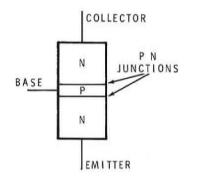

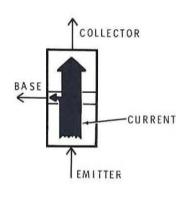

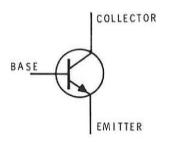

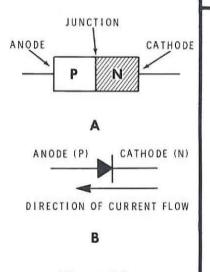

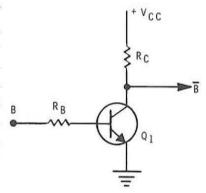

#### Transistors

Today the most common way of representing binary data in digital equipment is with a transistor. A transistor can readily assume two distinct states, conducting and cut-off. When a transistor is cut-off it is essentially an open circuit. When a transistor is conducting heavily, it acts as a very low resistance and accurately simulates a closed switch. Most digital circuitry in use today uses saturated bipolar switching transistors for data representation. Non-saturated bipolar transistor switches are also used in many applications where high speed operation is desirable. Keep in mind that both discrete component and integrated circuit transistors are used in digital applications.

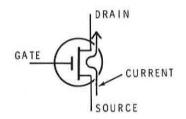

The enhancement mode MOS field effect transistor (MOS FET) is also widely used as a two state switch to represent binary data. This type of transistor is the key element in MOS and CMOS integrated circuits.

# **Magnetic Cores**

Another common means of representing binary data is by the use of a magnetic core. This is a small donut shaped piece of magnetic material approximately one tenth inch in diameter or smaller. A wire passing through the center of the core carries a current that magnetizes the core in either of two directions depending upon the direction of current flow in the wire. One direction of magnetization represents a binary 0 and the other a binary 1. The permeability of the magnetic material is such that the core retains the magnetization once the current through the wire is removed. This means that the core can store one bit of binary data. It remembers in which direction it was magnetized so that the state of the core can be determined later. Such cores are the primary data storage medium for many digital computers.

# Logic Levels

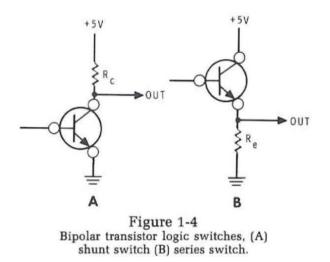

The basic element for representing a single bit of data is a switch: mechanical, electromechanical, electronic or magnetic. The on-off nature of a switch makes it perfect for binary data representation. The exact relationship between the state of the switch and the bit represented by this switch is arbitrary. In actual digital hardware we are not so much concerned with whether the transistor is off or on. Instead the bit assignments are generally represented by voltage levels. The switching element controls these voltage levels. For example, a binary 0 may be represented by 0 volts or ground. A binary 1 may be represented by +5 volts. Depending upon the equipment power supplies available, the exact circuitry used, and the application; almost any voltage level assignments can be used.

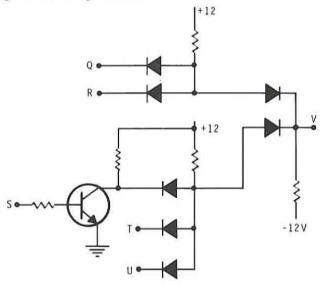

Figure 1-4 shows two ways in which a bipolar transistor can be used to produce two distinct voltage levels. In figure 1-4A, the transistor is connected as a shunt switch. This means that the transistor is in parallel with the output. When the transistor is not conducting, the output voltage is +5 volts as seen through collector resistor Rc. When the transistor is conducting it acts as a very low resistance or near short circuit. At this time the output is some low positive voltage level near ground or zero volts. The switching of the transistor of course is controlled by the application of the appropriate base signal. Switching times in the nanosecond ( $10^{-9}$  seconds) region are possible with modern transistors.

Positive logic lis greater than & ie 1.5v, d- du Negative logic lis les than & ie 1-5v, d- dv

In Figure 1-4B the transistor is connected as a series switch. When the transistor is cut off the output is zero volts or ground as seen through resistor R  $_E$ . When the transistor conducts, it acts as a very low impedance and connects the +5 volts supply line to the output. Again the operation of the transistor is controlled by applying the appropriate signal to the base. You will find both series and shunt transistor switches used in digital circuits.

#### **Positive and Negative Logic**

There are two basic types of logic level representation, positive logic and negative logic. When the most positive of two voltage levels is assigned the binary 1 state, we say that positive logic is being used. When the negative or least positive of two voltage levels is assigned to the binary 1 state, we say that negative logic is being used. Indicated below are several examples of both positive and negative logic level assignments. Keep in mind that the assignments are strictly arbitrary and are selected by the designer when the circuit or equipment is designed.

| Positive Logic       | Negative Logic       |  |  |

|----------------------|----------------------|--|--|

| binary $0 = +.2V$ .  | binary $0 = +3.4$ V. |  |  |

| binary $1 = +3.4V$ . | binary $1 = +.2$ V.  |  |  |

| binary $0 = -6V$ .   | binary $0 = 0$ V.    |  |  |

| binary $1 = 0V$ .    | binary $1 = -6$ V.   |  |  |

| binary $0 = +1V$ .   | binary $0 = +15V$ .  |  |  |

| binary $1 = +15V$ .  | binary $1 = +1V$ .   |  |  |

### **Parallel vs. Serial Data Representation**

There are two basic ways in which digital numbers are transmitted, processed or otherwise manipulated. These methods are designated as serial and parallel. In the serial methods of data handling, each bit of binary word or number is processed serially one at a time. In a parallel system all bits of a word or a number are processed simultaneously.

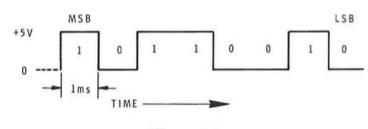

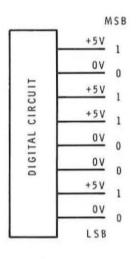

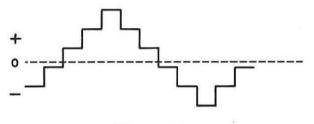

Serial Data. Figure 1-5 shows a binary number represented in a serial data format. The binary number exists as a series of voltage levels representing the binary 1s and 0s. These voltage level changes occur at a single point in a circuit or on a single line. Each bit of the word exists for a specific interval of time. The time interval allotted to each bit is in this example, one millisecond. The most significant bit (MSB) is the one at the far left. It occurs first since time is considered to be increasing from left to right. Because this is an 8 bit binary word, it takes 8 milliseconds for the entire word to occur or be transmitted. Positive logic level assignments are used. By observing the voltage levels at the specific point or on the transmission line, the number can be determined. The number is 10110010. This is the binary equivalent of the decimal number 178.

Figure 1-5 The serial binary word 10110010

The primary advantage of the serial binary data representation is that it requires only a single line or channel for transmitting it from one place to another. In addition, since each bit on the single line occurs separately from the others then only one set of digital circuitry is generally needed to process this data. For these reasons, serial data representation is the simplest and most economical of the two types. Its primary disadvantage is that the transmission and processing time required for a serial word is significant since the bits occur one after the other. Despite this time penalty, serial data representation is widely used because of its economy and simplicity.

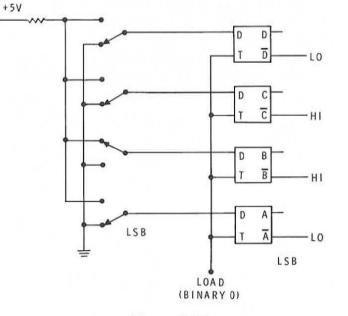

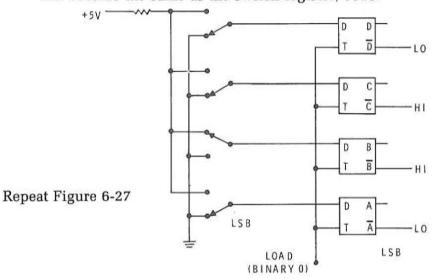

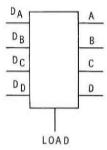

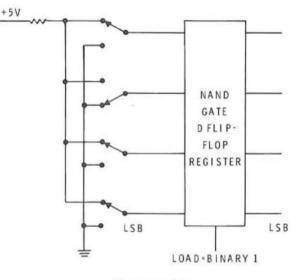

Figure 1-6 The parallel binary word 10110010 **Parallel Data.** The other method of representing, transmitting and processing binary data is designated as parallel. The reason for this is that all bits of a binary word or number are transmitted or processed simultaneously. For this reason a separate line or channel is required for each bit of the word in transmitting that word from one point to another. Refer to Figure 1-6. Here the 8-bit digital word 10110010 is available as voltage levels on eight separate output lines. Since all of the bits of the word are available at the same time, digital circuitry must be provided to process or otherwise manipulate each of the bits in the word simultaneously. The transmission and processing of parallel data, therefore, is more complex and expensive than that required for serial data. However, the clear advantage of parallel data transmission is its speed. All bits are processed at the same time and, therefore, the time required for handling of the data is very short. For high speed applications requiring rapid processing, parallel digital techniques are preferred.