The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# TIB0203 Magnetic-Bubble Memory and Associated Circuits

**NOVEMBER 1978**

TEXAS INSTRUMENTS

JESSE F. CABLE III 3250 ALMANSA CT. SAN JOSE, CALIF. 95127

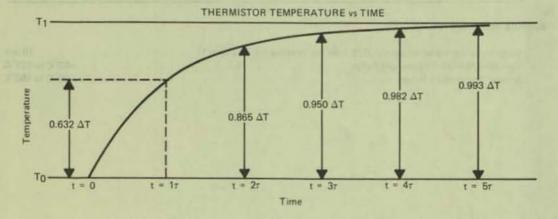

#### IMPORTANT NOTICES

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Information contained herein supersedes previously published data on these devices.

Copyright © 1978

Texas Instruments Incorporated

#### TABLE OF CONTENTS

|                                                              | Page |

|--------------------------------------------------------------|------|

| Introduction                                                 | 3    |

| Magnetic-Bubble-Memory Description                           |      |

| Functional Operation of Bubble Memories                      |      |

| Interfacing with Bubble Memories                             | 7    |

| Advantages of Bubble Memories                                | 9    |

| List of Illustrations                                        | 4    |

| Figure 1 - Magnetic-Bubble Memory (Exploded View)            |      |

| Figure 2 — Magnetic-Bubble Domains                           | 4    |

| Figure 3 - Magnetic-Bubble Propagation                       |      |

| Figure 4 — Architecture Using a Single Loop                  | . 6  |

| Figure 5 - Architecture Using Major and Minor Loops          | . 0  |

| Figure 6 – Bubble-Memory Module                              | . 8  |

| Figure 7 – Timing and Control Functions                      | . 8  |

| Electrical and Mechanical Specifications                     |      |

| TIB0203 — 92,304-Bit Magnetic-Bubble Memory                  | . 11 |

| SN74LS361 — Bubble-Memory Function Timing Generator          | . 23 |

| SN75281 — Bubble-Memory Sense Amplifier                      | . 29 |

| SN75380 - Rubble-Memory Function Driver                      | , 33 |

| SN75382 - Rubble-Memory Coil Driver                          | . 3/ |

| Mechanical Data for SN75281, SN75380, and SN75382            | . 41 |

| TSP102 - Positive-Temperature-Coefficient Silicon Thermistor | . 43 |

| VSB53 – Schottky Diode Bridge (Varo Semiconductor Inc.)      | . 47 |

#### INTRODUCTION

#### magnetic-bubble memory description

Magnetic-bubble-memory technology has advanced considerably since the concept was introduced by Bell Telephone Laboratories in 1967. Research indicated that small cylindrical magnetic domains, which are called magnetic bubbles, can be formed in single-crystal thin films of synthetic ferrites or garnets when an external magnetic field is applied perpendicularly to the surface of the film. These bubbles can be moved laterally through the film by using a varying magnetic field. These characteristics of magnetic bubbles make them ideally suited for serial storage of data bits; the presence or absence of a bubble in a bit pisition is used to define the logic state. Since the diameter of a bubble is so small (as little as a tenth of a micrometer), many thousands of data bits can be stored in a single bubble-memory chip. In the spring of 1977 Texas Instruments was the first to market a 92,304-bit bubble memory. This bubble memory is much like magnetic tape or magnetic disc memory storage in that it is nonvolatile meaning that the data is retained even when power is no longer applied to the chip. Since bubble memories are a product of solid-state technology (there are no moving parts), they have higher reliability than tape or disc storage and do not require any preventive maintenance. In addition, the bubble memory is small and lightweight and is, therefore, an excellent choice for compact designs and portable applications.

#### functional operation of bubble memories

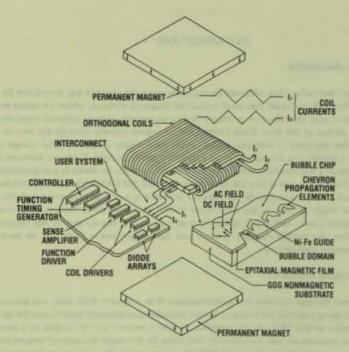

The basic bubble-memory package contains the bubble-memory chip, magnetic field coils, and permanent magnets as shown in Figure 1. A rotating magnetic field created by two mutually perpendicular coils causes the data in the form of magnetic bubbles to move serially through the magnetic film in a manner similar to data in a semiconductor shift register. Two permanent magnets provide nonvolatility and allow for the stable existence of magnetic-bubble domains. Interfacing circuits that are compatible with standard TTL devices complete the memory module to allow a convenient building-block concept for the nonvolatile memory system.

The chip is composed of a nonmagnetic crystaline substrate upon which a thin crystalline magnetic epitaxial film is grown. Only certain materials exhibit the properties necessary to form magnetic bubbles and these include orthoferrites, hexagonal ferrites, synthetic garnets, and amorphous metal films. Among these, the synthetic garnets have the best combination of the desired properties. Synthetic garnets support the formation of small magnetic bubbles that allow high-density data storage. The bubbles are highly mobile and are stable over a fairly wide range of temperatures.

The material chosen for the substrate depends on several factors. The crystalline structure should be compatible with that of the magnetic film, it should have nearly the same coefficient of expansion, and it should be nonmagnetic. The most-used garnet substrate with these properties is gadolinium gallium garnet (GGG). The magnetic film grown on this substrate has a crystalline structure that will allow the formation of magnetic domains (bubbles) in a plane perpendicular to the substrate.

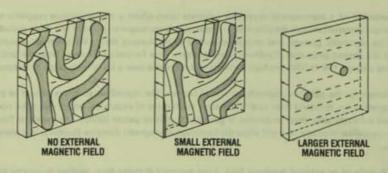

Without the influence of an external magnetic field, these magnetic domains form random serpentine patterns of equal area, minimizing the total magnetic energy of the magnetic film (see Figure 2). The magnetic field of the serpentine domains tends to line up primarily along a single axis (the "easy" axis) that is perpendicular to the plane of the film. If an external magnetic field is applied, its energy tends to expand domains polarized in the direction of the field and to shrink those polarized opposite to the field until they become small cylinders embedded in a background of opposite magnetization. Viewed on end, these cylinders have the appearance of small circles or bubbles with diameters from 2 to 30 micrometers. Increasing the field further causes the bubble to collapse or to be "annihilated". The external field provides a bias that makes the bubbles stable. This bias, being a static field, can be readily provided by permanent magnets with no expenditure of power.

FIGURE 1-MAGNETIC-BUBBLE MEMORY (EXPLODED VIEW)

External magnetic field shrinks random serpentine domains of magnetically neutral crystal to cylindrical form.

Reprinted by permission from Computer Design magazine, Copyright Computer Design Publishing Corp March 1976.

#### FIGURE 2-MAGNETIC-BUBBLE DOMAINS

Before bubbles can be shifted through the magnetic film, they must be generated in accordance with input data. Bubbles are generated by locally altering the bias field with a magnetic field produced by a pulse of current through a microscopic one-turn metallized loop. This loop is located on a secondary layer immediately above the magnetic film on the surface of the chip. Given a current of the correct amplitude and polarity through the one-turn loop, a localized vertical magnetic field opposite to that of the permanent magnets is produced. This localized field establishes a domain wall inversion in the magnetic film resulting in bubble creation.

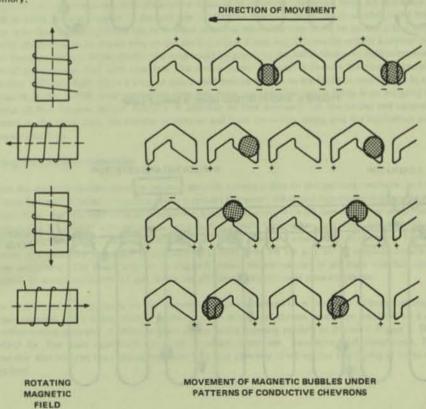

Once a bubble has been created, a method is then required to move the bubble domain along a predetermined path. This is accomplished by the deposition of chevron-shaped patterns of a soft magnetic material on the chip surface above the magnetic epitaxial film. When magnetized sequentially by a magnetic field rotating in the same plane, these chevron propagation patterns set up magnetic polarities that attract the bubble domain and establish motion. Figure 3 shows the various polarities at different positions of the rotating magnetic field. In actual practice the rotating in-plane magnetic field is implemented by applying a two-phase alternating current to the two coils shown in Figure 1.

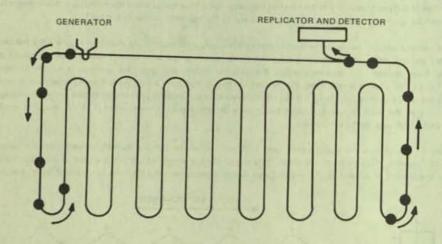

One possible implementation for the magnetic bubble memory is a long shift register. As shown in Figure 4 the bubbles would shift under the influence of the rotating magnetic field following the path determined by the placement of chevron patterns. Even though this approach offers the simplest design and interface control, it suffers a major disadvantage of having the slowest access time. The reason for this is that after a data bit is entered or written it must circulate through the entire shift register before it can be retrieved or read. Another problem with this single loop design is that a single fault in the shift register structure produces a defective bubble memory chip. This results in a low processing yield and a high cost to the consumer.

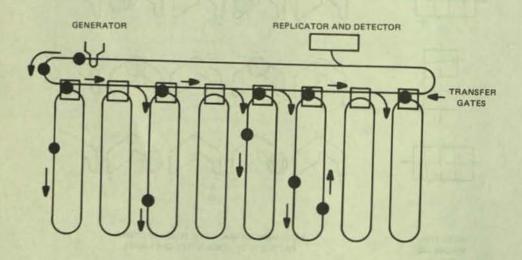

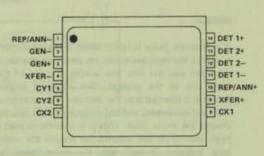

For these reasons TI has chosen the major-minor loop architecture, which offers a dramatic improvement in access time. As shown in Figure 5, during a write operation (data entry), data is generated one bit at a time in the major loop. The data is then transferred in parallel to the minor loops where it circulates until the next time data is to be read out of the memory.

FIGURE 3

FIGURE 4. ARCHITECTURE USING A SINGLE LOOP

FIGURE 5. ARCHITECTURE USING MAJOR AND MINOR LOOPS

During a write operation data are introduced into the major loop by pulses of current through the hairpin loop of the generator. The major loop is essentially a unidirectional circular shift register from which data can be transferred in parallel to the minor loops. Thus a block of data is entered in the major loop and shifted until the first data bit is aligned with the most remote minor loop. At that time, each parallel transfer element receives a current pulse that produces a localized magnetic field causing the transfer of all the bubbles in the major loop to the top bit position of the corresponding minor loop. Once data is written into the magnetic bubble memory, new data may be written only by first removing the old data by doing a destructive read. In this operation bubbles are transferred from the minor loops and annihilated by running them into the Permalloy guard rail that usually surrounds bubble devices.

During a read operation the data block to be accessed in the minor loops is rotated until it is adjacent to the major loop. At this time the data block is transferred in parallel to the major loop. The block of data is then serially shifted to the replicator where the data stream is duplicated. The duplicated data takes the path to the magneto-resistive detector element. The presence of a bubble in the detector lowers the resistance resulting in a corresponding increase in detector current, which can be detected via a sense amplifier. The original data stream remaining in the major loop is rotated and transferred back into the minor loops thus saving the data for further operations.

The magnetic-bubble-memory devices are fabricated using fine geometries that make the manufacture of perfect devices a difficult task. In order to increase production yields and achieve correspondingly lower costs, redundant minor loops on the bubble-memory chip allow some loops to be defective. Defective loops are determined at final test and a map of these loops is supplied to the end user so that the defective loops can be avoided in the final memory system. This redundancy of minor loops can be handled in several ways. The map could be written into a software program that would direct data to be stored only to the perfect minor loops, but this would require a unique software package for each memory system. Alternatively, the map could be stored in the MBM (magnetic-bubble memory) itself with some risk of being written over with new data. The recommended approach is to store the map in a programmable read-only memory (PROM). Each bit in a page of data would then be written to the MBM or read from it in accordance with the contents of the PROM, thus preventing data bits from the defective minor loops from mingling with valid data. Of course all this requires control circuitry in addition to that necessary for the timing and control of the alternating current in the field coils, the transfer of data to and from the minor loops, and the replication and detection of the magnetic bubbles.

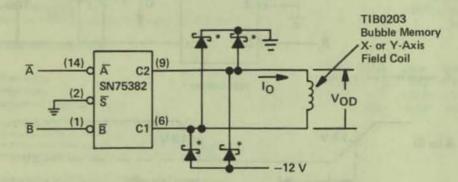

#### interfacing with bubble memories

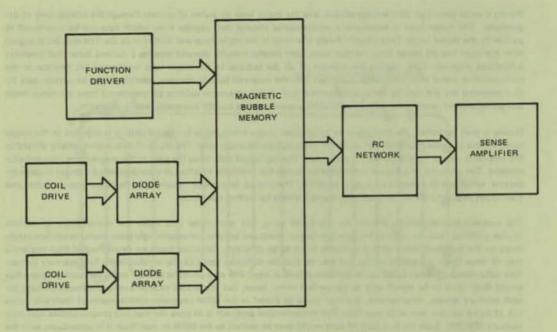

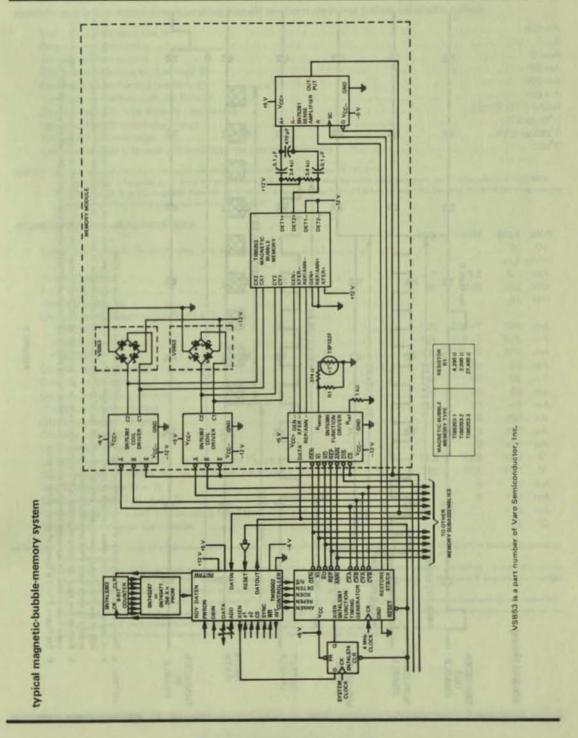

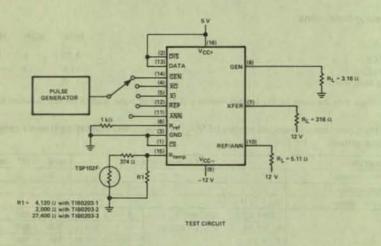

Since the magnetic-bubble memory requires accurate current pulses for the generate, replicate, and transfer operations, an interface circuit called a function driver is needed to convert the digital input control signals to the required current pulses. Also, the two field coils each require a triangular current drive 90 degrees out of phase with each other. This requirement is satisfied with another set of interface circuits (coil drivers and diode array) that is driven with digital input signals. The output signal amplitude of the MBM is relatively small, about 3 millivoits. For this to be useful in a system, the output is converted to standard TTL levels with the use of a set of interface circuits (RC networks and sense amplifiers). The block diagram in Figure 6 shows the connection of all these interface circuits as a memory module. This modular building block promotes efficient construction of mass memories.

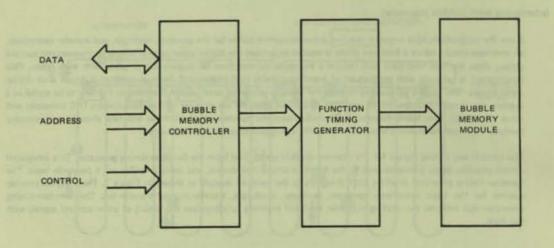

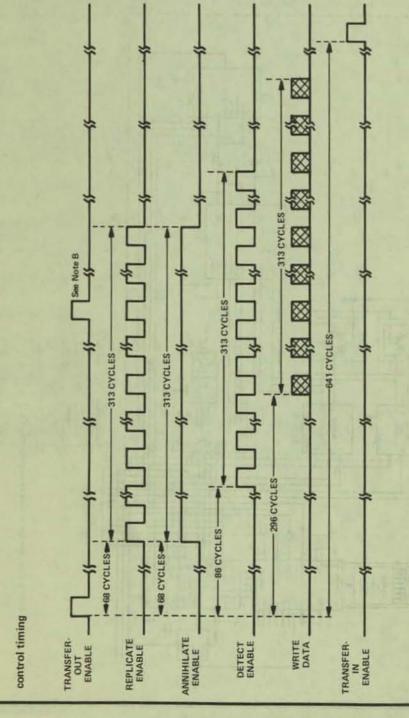

The control and timing signals for the memory module are derived from the function-timing generator. This integrated circuit provides input timing control to the function driver, coil drivers, and sense amplifier on a per-cycle basis. The function-timing generator provides control signals to the memory module as shown in Figure 7. These signals provide control for five basic operations: generate, replicate, annihilate, transfer-in, and transfer-out. The function-timing generator also initiates the rotating magnetic field and precisely synchronizes the timing of other control signals with this field.

FIGURE 6. BUBBLE MEMORY MODULE

FIGURE 7. TIMING AND CONTROL FUNCTIONS

The time at which a particular data bit is detected in the MBM may not exactly match the time at which it is needed in the system. The sense amplifier not only increases the voltage level of the detected data, but also provides temporary storage of the data bits in a circuit called a D-type flip-flop. The sense amplifier receives a control input from the function timing generator to transfer the detected data into the internal flip-flop. In addition, the function-timing generator provides the control signals necessary to put the existing data in a known position during a power shut down. When the system is turned on again, the stored data can then be accurately located and retrieved.

In a typical system the major computing and data processing is done by a microprocessor. To provide a convenient interface from the microprocessor to the MBM system, a custom controller is needed for the read, write, and memory-addressing operations. The TMS5502/TMS9916 MBM controller responds to commands from the microprocessor system and sends control signals to the function timing generator necessary to access a page (or pages) of data. The controller maintains page-position information, handles serial-parallel data conversion between the bubble memory and the microprocessor, and generates the control signals to the function-timing generator to perform read and write operations while handling the redundancy of the minor loops.

#### advantages of bubble memories

The future growth of distributed process systems will be greatly impacted by magnetic-bubble memories. These microprocessor-based systems demand high-density mass storage at low cost. Magnetic-bubble memories satisfy all of these requirements with definite advantages over the existing magnetic storage technologies. MBM's advantages over moving-head disks or floppy disks are low access time (the time necessary to retrieve the desired data), small physical size, low user entry cost, no maintenance, and higher reliability.

The advantages of MBM's over random-access memories (RAM's) are nonvolatility, potentially lower price per bit, and more bits per chip. The RAM has the advantage of much better access time, higher transfer rate, and simpler interfacing.

In summary, the main MBM advantages are the low entry price versus disks for the low-end user, nonvolatility versus semiconductor memories, and high-density storage in a small physical space. Because magnetic-bubble memories are a solid-state, nonvolatile technology, they are ideally suited for portable applications as well as providing memory for traditional processing systems. Industrial applications include memory for numerical control machines and various types of process control. Solid-state bubble memories are more reliable in harsh environments; they are affected much less by shock, vibration, dirt, and dust than electromechanical magnetic memories. Innovative new products include data terminals, calculators, word processing, voice storage, and measurement equipment.

per la principal de management

THE REAL PROPERTY AND ADDRESS OF THE PARTY O

The second contract of the second contract of

## BUBBLE MEMORY

# TYPE TIBO203 MAGNETIC-BUBBLE MEMORY

NOVEMBER 1978

- Major/Minor Loop Architecture

- 100-kHz Field-Rate Operation

- 50-kb/s Input/Output Data Rate

- · Average Access Time (First Bit) . . . 4 ms

- Consumes Less Than 0.7 W for Continuous Operation

- · Weighs Approximately 25 grams

- Rugged Package with Self-Contained Magnetics

- Occupies Less Than 1.25 in<sup>2</sup> (8 cm<sup>2</sup>) of Board Area

TOP VIEW

#### description

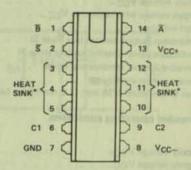

The TIB0203 magnetic-bubble-memory device is a 14-pin dual-in-line module containing a 92,304-bit bubble-memory chip, coils for providing a rotating magnetic field, a permanent-magnet structure for providing the required static magnetic field, and a magnetic-shield assembly. The major/minor-loop architecture consists of 144 circular shift registers (minor loops) of 641 bits each that can transfer data in and out of a control loop (major loop). The major loop contains the generate, replicate, and annihilate control functions as well as the detector.

Control functions (i.e., generate, transfer-in, transfer-out, replicate and annihilate) are accomplished by providing current pulses through the appropriate control elements on the chip. A current pulse through a control element causes a local alteration in the magnetic field. This field alteration, in conjunction with the local permalloy pattern, accomplishes the control function. Pulses must be timed to coincide with the arrival of the bubble domain at the proper location on the chip.

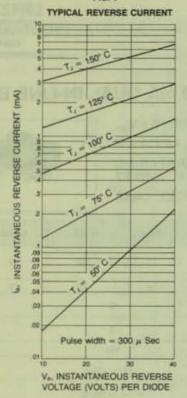

To detect the presence or absence of bubbles, two magneto-resistive elements are provided. These elements may be used as part of a bridge circuit configuration that provides a high degree of noise cancellation when used with an external differential amplifier.

#### operation

#### generation

Bubble domains may be created by applying the specified current pulse through the generate loop. These domains step through the major loop in the predetermined direction. The presence or absence of a bubble in a bit position is used to define the logic state.

#### transfer-in

When a data string equal in length to the number of minor loops (a page) has been generated and shifted such that the first bit is positioned over the first minor loop, the transfer gate may be energized. This operation transfers the page from the major loop into minor loops. The data now circulates in the minor loops. New data may be generated, shifted, and transferred into each of 641 different minor loop page positions.

#### transfer-out

Data is retrieved by doing a transfer-out operation when the desired page rotates to the top of the minor loops. This moves the page out of the minor-loop structure and puts it back into the major loop. The page now moves around the major loop in bit-serial form until the first bit arrives at the replicate/annihilate element. One of two control operations may now be performed: replicate or annihilate.

PRELIMINARY DATA SHEET

Copyright © 1978 by Texas Instruments Incorporated

1178

#### operation (continued)

#### replicate

If a replicate pulse is issued when a bubble domain arrives at the replicate/annihilate gate, that domain is stretched and cut into two bubble domains of the same size as the original. One of these bubble domains is diverted into the detector area where it is read and destroyed, and the other continues moving around the major loop. Thus it is possible to read a page, recirculate the information around the major loop and put it back into the minor loops for nonvolatile storage. This operation provides a non-destructive read capability.

#### annihilate

Annihilation is accomplished by applying to the replicate/annihilate gate a current pulse that transfers the bubble out of the major loop, and into the detector track where it propagates off the chip.

FIGURE 1-BASIC CHIP ARCHITECTURE

#### redundancy

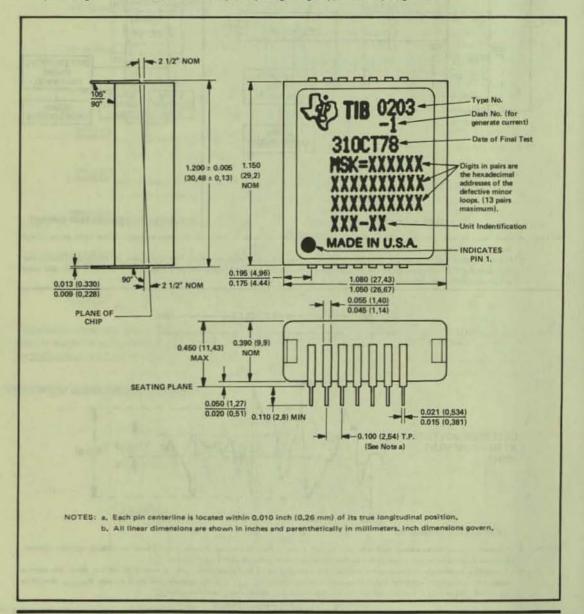

To enhance production yields and thereby reduce device cost, redundancy has been designed in so that as many as 13 of the total 157 minor loops on the chip may be defective. Defective minor loops result from manufacturing processes related to the small geometry of the permalloy patterns. Defective minor loops are identified during factory testing and in no way relate to a field-failure mode. A map of the defective minor-loop locations will be printed on the device at the factory before shipment. This map consists of the hexadecimal address of each defective loop starting from address 00. See Drawing under Ordering Instructions and Mechanical Data.

Writing into defective loops is not an option. Some of these loops will have defects that may reproduce bubbles from normal coil-field drives. The reproduced bubbles may eventually contaminate the entire chip with unwanted bubbles.

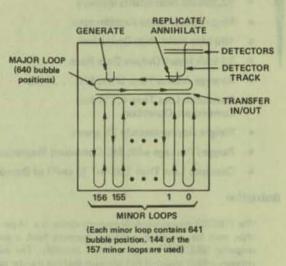

#### coil drive

12

The bubble-memory chip is surrounded by two orthogonal coils that, when driven 90° out of phase, produce a rotating magnetic field in the plane of the chip. It is this rotating field that causes bubble domains to move under the permalloy patterns.

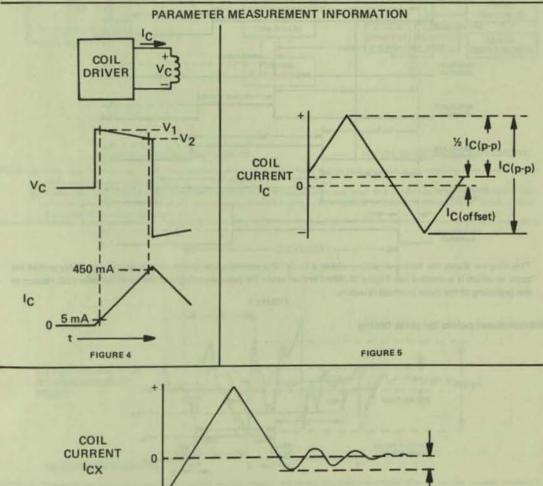

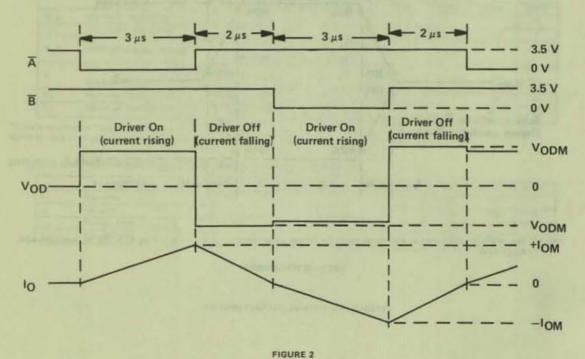

Triangular current waveforms are recommended for driving the two coils. This approach lends itself to precise digital control of the drive field. See Figure 2. It is essential that the starting and stopping sequences shown in Figure 2 be followed exactly to prevent loss of stored data. Starting begins with the buildup of positive current through CX2 and the final event in stopping is the decay of positive current through CX2.

If the two coils are turned on and off in the prescribed manner, bubble-domain motion in the minor loops can be started and stopped without error. Thus, if continuous duty is not required, a power savings can be realized by operating in the start/stop mode. Data in the major loop must be transferred to the minor loops before the field is stopped because data in the major loop is susceptible to loss when the field is stopped.

#### operation (continued)

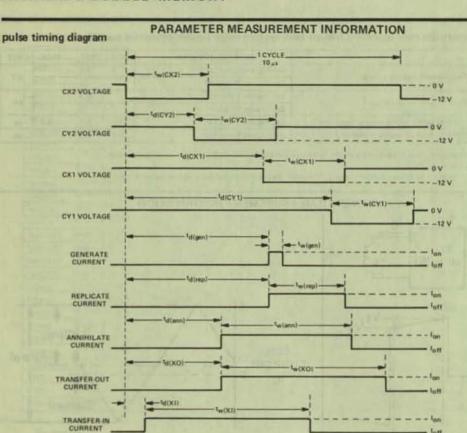

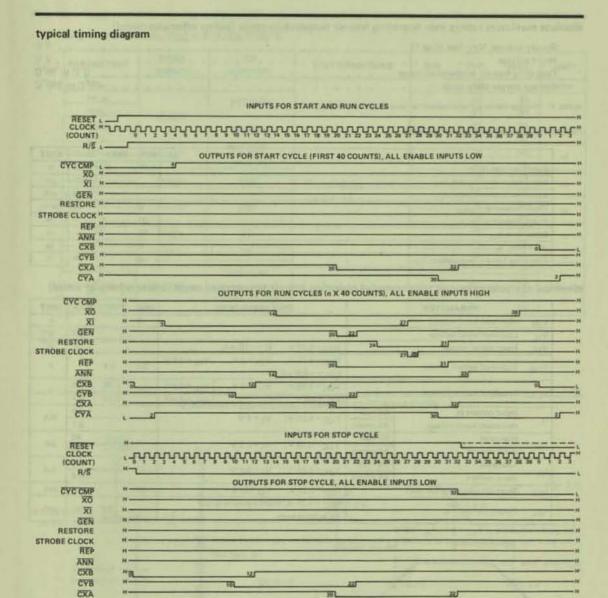

#### control timing

A cycle is the time in which the magnetic field produced by the coil rotates 360°. A bit period is the space within which a data bit (a bubble domain or the absence thereof) occurs, and is also the distance a bubble position moves during one cycle.

The minor loops are spaced two periods apart, so that, when data is transferred from the minor loops to the major loop, one void bit position exists between all data bits in the major loop. Therefore, all major-loop functions (replicate/annihilate, detect, generate) are performed at half the frequency of the drive field. Since the drive-field rate is nominally 100 kHz, the major-loop functions are performed at a nominal rate of 50 kHz.

The overall timing is in cycles (or bit periods). However, the exact timing consists not only of the cycle in which an event takes place, but also of the specific time within the cycle at which the pulse actually begins.

Since all operations in the bubble memory begin with transfer out, cycles are counted from the beginning of the transfer-out cycle. Even the storage of data in the memory begins with the transfer out of old data from the minor loops and the subsequent annihilation of this old data, thereby clearing the page location.

Transfer out is performed when the desired page of data in the minor loops is in position next to the major loop so that it can be transferred to the major loop and operated upon.

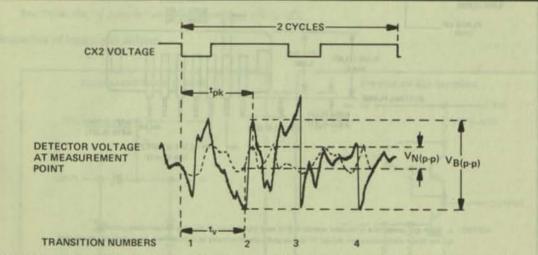

#### detector signal and noise

Noise is produced in the circuit due to circuit layout, control pulses, and the rotating magnetic field. The signal produced by a bubble domain passing the detector is relatively small. Therefore, two detectors, out of phase with each other, are used. Both detectors pick up noise from the circuit, but only one is in position to sense the bubble domains during a given cycle. The noise signals from the two detectors tend to cancel out each other since they are out of phase with one another, thus leaving a more clearly defined bubble signal.

In reality, a bubble domain passing the detector element produces four voltage transitions over a two-cycle period. Since only every other bit position in the major loop is valid, there is no overlapping of signals. However, only the second transition is specified, (see Figure 11) and data should be read only during the time specified for this transition.

NOTES: A. Enable pulses are applied at the function timing generator, data pulses are applied at the function driver.

It in multipase operation where one may of these form but from each of the IET may be form.

B. In multipage operation, when one page of data (one bit from each of the 157 minor loops) has been transferred out of the minor loops and advanced to the other side of the major loop, another page may be transferred out of the minor loops so that it will be in position to be operated upon when the earlier page is in the process of being trans efred back into the minor loops.

G. Each enable pulse (or string of pulses) is 313 cycles long to allow the bits from all 157 minor loops plus the 156 void bit positions between the data bits in the major loop to pass the operating element. Transfer out and transfer.

FIGURE 3

D. See Figure 7 for the timing of pulses within the cycle.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Peak coil current (see Note 1)                                   | 0 mA |

|------------------------------------------------------------------|------|

|                                                                  | 7 mA |

| Transfer element current                                         | 0 mA |

| Replicate element current (see Note 2)                           | 0 mA |

| Generate element current (see Note 2)                            | 0 mA |

| Annihilate element current (see Note 2)                          | 0 mA |

| External magnetic field intensity (see Note 3)                   | A/m) |

| Operating free-air temperature range                             |      |

| Storage temperature range                                        | 00°C |

| Lead temperature 1/16 inch (1.6 mm) from the case for 10 seconds |      |

- NOTES: 1. This value applies for a triangular waveform in each coil at a frequency of 100 kHz.

- 2. These values of current apply only for pulse operation at recommended nominal pulse duration and at a frequency of 100 kHz.

- Exposure to external magnetic fields of an intensity between 20 persteds (1.6 kA/m) and 150 persteds (11.9 kA/m) may require

menual clearing with a calibrated permanent magnet.

#### recommended operating conditions

|                                                                                    | MIN   | NOM   | MAX  | UNIT  |

|------------------------------------------------------------------------------------|-------|-------|------|-------|

| External dc magnetic field intensity, any direction                                |       |       | 20   | Oe    |

|                                                                                    |       |       | (1.6 | kA/m) |

| Detector current                                                                   | . 4.8 | 5.2   | 5.7  | mA    |

| Field frequency                                                                    | . 98  | 100   | 102  | kHz   |

| Generate frequency                                                                 | (A)   |       | 51   | kHz   |

| On-state generate current (see Notes 4, 5, and 6)                                  |       |       |      |       |

| TIB0203-1                                                                          | -10%  | 290-T | 10%  | mA    |

| TIB0203-2                                                                          | -10%  | 360-T | 10%  | mA    |

| TIB0203-3                                                                          | -10%  | 235-T | 10%  | mA    |

| On-state replicate current                                                         |       | 80    | 88   | mA    |

| On-state annihilate current                                                        | 54    | 60    | 66   | mA    |

| On-state transfer-out current                                                      | . 34  | 38    | 42   | mA    |

| On-state transfer-in current                                                       |       | 38    | 42   | mA    |

| Off-state generate current                                                         |       | 0     | ±50  | μА    |

| Off-state replicate/annihilate current                                             |       | 0     | ±50  | μА    |

| Off-state transfer current                                                         |       | 0     | ±50  | μА    |

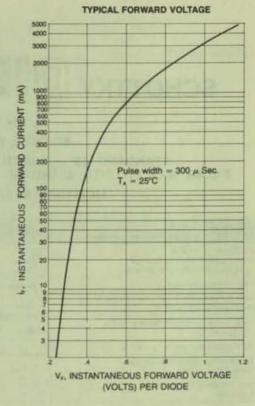

| Coil-drive pulse amplitude, V <sub>1</sub> , I <sub>O</sub> = 5 mA, see Figure 4   |       | 11.9  | 12.5 | V     |

| Coil-drive pulse amplitude, V <sub>2</sub> , I <sub>O</sub> = 450 mA, see Figure 4 |       | 11.1  | 11.7 | V     |

| Dc coil current (see Note 7)                                                       |       | 0     | ±3   | mA    |

| Coil-current offset (see Figure 5)                                                 |       |       | ±10  | mA    |

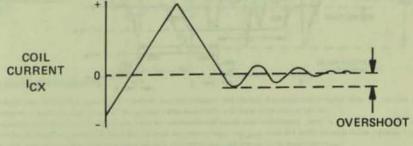

| Current overshoot in coil X on stopping (see Figure 6)                             |       |       | -15  | mA    |

|                                                                                    |       |       |      | °C    |

| Data-retention storage temperature                                                 | -40   |       | 85   | C     |

- NOTES: 4. Care should be taken to ensure that no undershoot is present on the generate pulse as this can adversely affect the performance of the memory.

- 5. Generate pulse amplitude must be temperature compensated from the specified nominal value at the rate of -1 mA/C over the operating temperature range. The quantities shown under NOM give the nominal values at temperature T and the percentages shown for MIN and MAX are tolerances that apply to these nominal values.

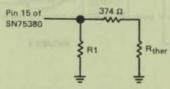

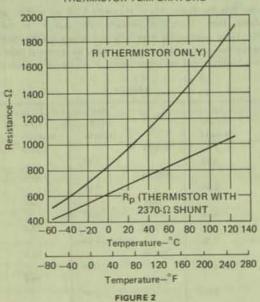

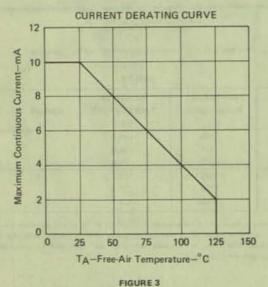

- 6. TI reserves the right to ship any combination of the three dash numbers for this part. All devices packed within the same box shall be of the same dash number. Each dash number requires a different resistor value in the resistor/thermistor network at the R<sub>temp</sub> input of the bubble-memory function driver, SN75380.

- 7. Do call current is the current through the cails in the off condition (cails not driven).

#### timing requirements (see figures 7 and 8)

|                     | PARAMETER                                  | MIN  | NOM  | MAX  | UNIT |

|---------------------|--------------------------------------------|------|------|------|------|

| <sup>t</sup> d(gen) | Generate-pulse delay time <sup>†</sup>     | 5.1  | 5.2  | 5.3  | μs   |

| <sup>t</sup> d(rep) | Replicate-pulse delay time <sup>†</sup>    | 5.1  | 5.2  | 5.3  | μs   |

| td(ann)             | Annihilate-pulse delay time <sup>†</sup>   | 3.4  | 3.5  | 3.6  | μs   |

| td(XO)              | Transfer-out-pulse delay time <sup>†</sup> | 3.4  | 3.5  | 3.6  | μs   |

| td(XI)              | Transfer-in-pulse delay time <sup>†</sup>  | 0.7  | 0.8  | 0.9  | 115  |

| td(CY2)             | CY2-pulse delay time <sup>†</sup>          | 2.47 | 2.50 | 2.53 | μs   |

| td(CX1)             | CX1-pulse delay time <sup>†</sup>          | 4.97 | 5.00 | 5.03 | jas  |

| td(CY1)             | CY1-pulse delay time <sup>†</sup>          | 7.47 | 7.50 | 7.53 | μs   |

| tw(gen)             | Width of generate pulse                    | 0.4  | 0.5  | 0.6  | μs   |

| tw(rep)             | Width of replicate pulse                   | 2.65 | 2.75 | 2.85 | μs   |

| tw(ann)             | Width of annihilate pulse                  | 4.65 | 4.75 | 4.85 | 325  |

| tw(XO)              | Width of transfer-out pulse                | 5.9  | 6.0  | 6.1  | 325  |

| tw(XI)              | Width of transfer-in pulse                 | 5.9  | 6.0  | 6.1  | 316  |

| tw(CX1)             | Width of coil-drive pulse through CX1      | 2.95 | 3.0  | 3.05 | us   |

| tw(CX2)             | Width of coil-drive pulse through CX2      | 2.95 | 3.0  | 3.05 | jes. |

| tw(CY1)             | Width of coil-drive pulse through CY1      | 2.95 | 3.0  | 3.05 | jus  |

| tw(CY2)             | Width of coil-drive pulse through CY2      | 2.95 | 3.0  | 3.05 | jas  |

| tr(gen)             | Generate-pulse rise time                   |      | 0.1  | 0.2  | JAS. |

| tf(gen)             | Generate-pulse fall time (see Note 4)      |      | 0.1  | 0.2  | HS.  |

| tr(rep)             | Replicate-pulse rise time                  | 413  | 0.1  | 0.2  | μs   |

| Tf(rep)             | Replicate-pulse fall time                  | 1    | 0.1  | 0.2  | μѕ   |

| tr(ann)             | Annihilate-pulse rise time                 | 1    | 0.1  | 0.2  | 145  |

| t((ann)             | Annihilate-pulse fall time                 |      | 0.1  | 0.2  | 325  |

| (r(XO)              | Transfer-out-pulse rise time               |      | 0.1  | 0.2  | HS   |

| (OXI)               | Transfer-out-pulse fall time               |      | 0.1  | 0.2  | 145  |

| 4(XI)               | Transfer-in-pulse rise time                | 400  | 0.1  | 0.2  | μs   |

| H(XI)               | Transfer-in-pulse rise time                |      | 0.1  | 0.2  | Jus  |

NOTE 4: Care should be taken to ensure that no undershoot is present on the generate pulse as this can adversely affect the performance of the memory.

#### electrical characteristics over operating free-air temperature range (unless otherwise noted)

|           | PARAMETER                                         | MIN             | TYP: | MAX  | UNIT |

|-----------|---------------------------------------------------|-----------------|------|------|------|

| rg        | Resistance of generate element                    | No. of the last | 4    | 7    | Ω    |

| 'B        | Resistance of replicate element                   | 10.00           | 8    | 12   | Ω    |

| T         | Resistance of transfer element                    | HIST TOTAL      | 300  | 350  | Ω    |

| 'D1       | Resistance of detector element 1                  | 850             | 1100 | 1450 | Ω    |

| D2        | Resistance of detector element 2                  | 850             | 1100 | 1450 | Ω    |

| rD1 - rD2 | Differential resistance between detector elements |                 |      | ±20  | Ω    |

| Lx        | Inductance of coil X (f = 100 kHz)                | 62              | 64   | 66   | μН   |

| Ly        | Inductance of coil Y (f = 100 kHz)                | 57              | 59   | 61   | μH   |

| *x(real)  | Real part of impedance of coil X (f = 100 kHz)    |                 | 4.8  |      | Ω    |

| Zy(real)  | Real part of impedance of coil Y (f = 100 kHz)    |                 | 4.3  |      | Ω    |

<sup>‡</sup>Att typical values are at TA = 25°C.

<sup>&</sup>lt;sup>†</sup>All delay times are measured from the beginning of the cycle (leading edge of the CX2 pulse) in which they occur.

#### operating characteristics over operating free-air temperature range (unless otherwise noted)

|                       |                                                | TEST CONDITIONS       | MIN | TYP‡ | MAX | UNIT |

|-----------------------|------------------------------------------------|-----------------------|-----|------|-----|------|

| Mar .                 | Best as sout but his values                    | See Figures 9 and 11  | 2   | 3.5  |     |      |

| Diff-bi               | Peak-to-peak bubble voltage                    | See Figures 10 and 11 |     | 22   |     | mV   |

| V <sub>N(p-p)</sub> P | Peak-to-peak noise voltage <sup>§</sup>        |                       | 0.5 |      | 200 |      |

|                       | reak-to-peak noise voitage s                   | See Figures 10 and 11 |     | - 5  |     | mV   |

| ty                    | Time to valley before second transition†       | See Figures 9 and 11  | 5.9 | 6.1  | 6.3 | μs   |

| tpk                   | Time to peak of second transition <sup>†</sup> | See Figures 9 and 11  | 6.7 | 7.0  | 7.3 | μs   |

<sup>†</sup>All delay times are measured from the beginning of the cycle (leading edge of the CX2 pulse) in which they occur.

This noise voltage is largely a function of circuit layout. The value specified is typical for a well-designed circuit.

FIGURE 6

<sup>‡</sup>All typical values are at TA = 25°C.

This diagram shows the timing of pulses within a cycle. The control pulse under consideration occurs only within the cycle in which it is enabled (see Figure 3). When it does occur the pulse must begin at the specified time with respect to the beginning of the cycle in which it occurs.

FIGURE 7

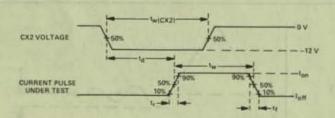

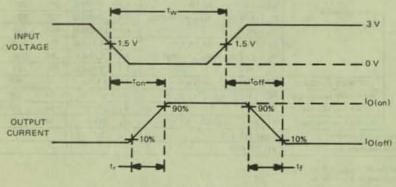

### measurement points for pulse timing

FIGURE 8

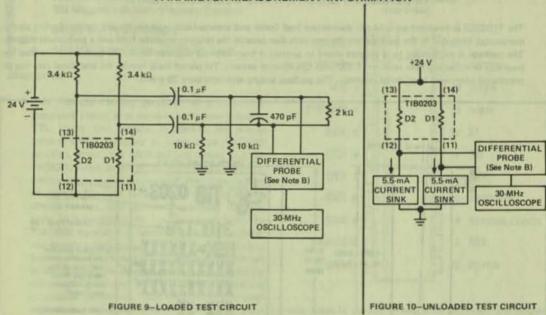

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. Care must be exercised in circuit layout to ensure that detector leads do not pick up noise from coll-drive leads, power-supply leads, and function current pulses.

- 8. Probe impedance must be greater than two megohns and probe capacitance less than five picofarads to avoid attenuating the observed signal. The bandwidth of the oscilloscope and probe should be 20 megahertz or greater. Common-mode rejection ratio should be 60 decibels minimum.

- NOTES: A. The solid line indicates a signal with a bubble domain present; the dashed line indicates a signal with no bubble domain present.

The shape, amplitude, and phase of the actual noise waveform will vary with circuit layout.

- 8. A magnetic-bubble domain passing the detector elements will cause four transitions over a two-cycle period. Only the second transition is specified, and both the peak-to-peak bubble voltage, V<sub>B(p-p)</sub>, and the peak-to-peak noise voltage, V<sub>N(p-p)</sub> should be measured only during the time specified for this transition, i.e., minimum t<sub>p</sub> to maximum t<sub>pk</sub>.

FIGURE 11-VOLTAGE WAVEFORMS

#### ORDERING INFORMATION AND MECHANICAL DATA

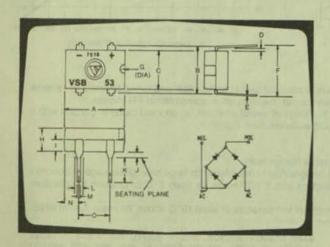

The TIB0203 is mounted on a 14-pin dual-in-line lead frame and encapsulated in an electrically nonconductive plastic compound. Included in the package are the two coils that provide the rotating magnetic field and a permanent magnet. The package is surrounded by a magnet shield to protect it from external magnetic fields. The package is intended for insertion in mounting hole rows on 1.200-inch (30.48-mm) centers. Tin-plated leads require no additional cleaning or processing when used in soldered assembly. The package weighs approximately 25 grams.

NOVEMBER 1978

- Provides Cycle Timing for TIB0203 92,304-Bit Magnetic-Bubble-Memory System

- Single 5-V Power Supply

- 400-Mil-Row-Center 22-Pin Package

#### description

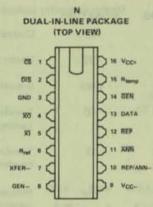

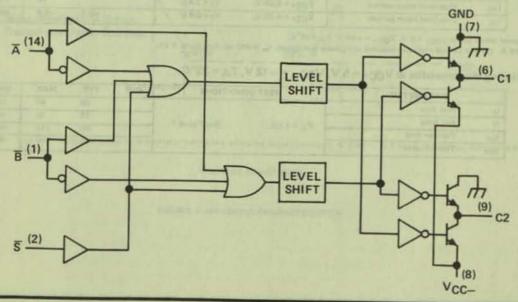

This function timing generator is a monolithic integrated circuit with standard low-power Schottky TTL inputs and outputs. It provides the precise control timing necessary to operate the SN75380 function driver, the SN75382 coil driver, and the SN75281 sense amplifier for the TIB0203 chevronpattern magnetic-bubble-memory. The device consists of control flip-flops, a counter, a decoder matrix, output latches, and gating. The control flip-flops serve to synchronize the run/stop signal from the TMS5502 controller to control the starting, shifting, and stopping sequences of the bubble-field rotation. Each bubble-field rotation is divided into 40 intervals by the counter. The decoder matrix is accessed on the rising edge of the clock pulse during each interval and its outputs are latched. These outputs are then gated

(TOP VIEW) 22 VCC CLOCK 1 RESET 2 21 DETEN R/\$ 3 20 XOEN CYC CMP 4 19 XIEN 18 XI CYA 5 17 XO CXA 6 CYB 7 16 GEN CXB 8 15 RESTORE ANN 9 14 STROBE CLOCK 13 REP **ANNEN 10** 12 REPEN **GND 11**

**DUAL-IN-LINE PACKAGE**

with the control signals from the TMS5502 to provide timing pulses to the coil drivers, sense amplifiers, and function drivers.

The SN74LS361 contains a VCC monitor network that provides data protection during five-volt power up/down transient conditions. This network forces the coil-drive outputs of the function timing generator to the high logic level when the VCC supply drops below approximately 3.5 volts.

The SN74LS361 is characterized for operation from 0°C to 70°C.

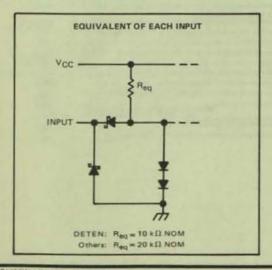

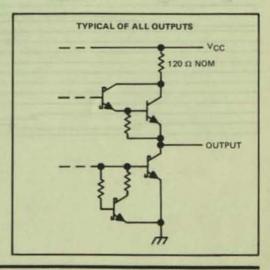

#### schematics of inputs and outputs

PRELIMINARY DATA SHEET

Copyright © 1978 by Texas Instruments Incorporated

| PIN              | SIGNATURE                | FUNCTION                                                                                                               |

|------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1                | CLOCK                    | Receives 4-MHz clock signal, active on low-to-high transition.                                                         |

| 2                | RESET                    | Low level input clears flip-flop and initializes the circuit.                                                          |

| 3                | R/S                      | (Run/stop) High level initiates bubble shift, low level stops it.                                                      |

| 4                | CYC CMP                  | After R/S goes low, CYC COMP goes low when the system is back to page 0 and the drive field will stop 1/4 cycle later. |

| 5<br>6<br>7<br>8 | CYA<br>CXA<br>CYB<br>CXB | Coil Y, phase A Coil Y, phase B Coil X, phase B                                                                        |

| 9                | ANN                      | Provides a signal that, when low, causes the function driver to emit an annihilate pluse.                              |

| 10               | ANNEN                    | High level input enables the ANN output.                                                                               |

| 11               | GND                      | Ground (substrate).                                                                                                    |

| 12               | REPEN                    | High level input enables the REP output.                                                                               |

| 13               | REP                      | Provides a signal that, when low, causes the function driver to emit a replicate pulse.                                |

| 14               | STROBE CLOCK             | Provides a signal that clocks the sense amplifier on the low-to-high transistion.                                      |

| 15               | RESTORE                  | Provides a signal that, when high, initializes the sense amplifier, and when low, allows the signal to be sensed.      |

| 16               | GEN                      | Provides a signal that, when low, causes the function driver to emit a generate current pulse.                         |

| 17               | XO                       | Provides a signal that, when low, causes the function driver to emit a transfer-out current pulse.                     |

| 18               | XI                       | Provides a signal that, when low, causes the function driver to emit a transfer-in current pulse.                      |

| 19.              | XIEN                     | High level input enables the XI output.                                                                                |

| 20               | XOEN                     | High level input enables the XO output.                                                                                |

| 21               | DETEN                    | High level input enables the STROBE CLOCK and RESTORE outputs.                                                         |

| 22               | Vcc                      | +5-V supply.                                                                                                           |

CYA

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)     | <br>     | W.        |   |   |      |    |      |      |    |     |     |    |      |     |   | 1 |   |   | 7V            |

|--------------------------------------|----------|-----------|---|---|------|----|------|------|----|-----|-----|----|------|-----|---|---|---|---|---------------|

| Input voltage                        |          |           |   |   |      |    |      |      |    |     |     |    |      |     |   |   |   |   |               |

| Operating free-air temperature range |          |           |   | * | 4    | *  | 4    | <br> |    | (0) | 100 |    | v. 1 |     |   |   |   |   | 0°C to 70°C   |

| Storage temperature range            | <br>. 14 | <br>11/40 | 1 | - | -2 ( | 81 | (23) |      | 10 | -40 |     | 40 |      | 112 | - |   | - | - | 85°C to 150°C |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                                    | MIN  | NOM | MAX  | UNIT |

|------------------------------------|------|-----|------|------|

| Supply voltage, VCC                | 4.75 | 5   | 5.25 | ٧    |

| High-level output current, IOH     |      |     | -400 | μА   |

| Low-level output current, IQL      |      |     | 8    | mA   |

| Clock frequency, felock            | 0    |     | 12   | MHz  |

| Width of clock pulse, tw           | 20   |     |      | ns   |

| Setup time, t <sub>su</sub>        | 20   |     |      | ns   |

| Hold time, th                      | 0    |     | 200  | ns   |

| Operating free-air temperature, TA | 0    |     | 70   | °C   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      | PARAMETER                     |            | TES                                                    | CONDITION                            | MIN                      | TYPT | MAX  | UNIT |      |

|------|-------------------------------|------------|--------------------------------------------------------|--------------------------------------|--------------------------|------|------|------|------|

| VIH  | High-level input voltage      |            |                                                        |                                      | 2                        |      |      | V    |      |

| VIL  | Low-level input voltage       |            |                                                        |                                      |                          |      | 8.0  | V    |      |

| VIK  | Input clamp voltage           |            | VCC = 4.75 V,                                          | II = -18 mA                          |                          |      | -1.5 | V    |      |

| VOH  | High-level output voltage     |            | V <sub>CC</sub> = 4.75 V,<br>I <sub>OH</sub> = -400 μA | VIH = 2 V,                           | V <sub>1L</sub> = 0.8 V, | 2.7  | 3.1  | 176  | ٧    |

|      | I and book access of the same |            | VCC = 4.75 V.                                          | VIH = 2 V.                           | IOL =8 mA                | -    | 0.35 | 0.5  | V    |

| VOL  | Low-level output voltage      |            | VIL = 0.8 V                                            |                                      | IOL = 4 mA               |      | 0.25 | 0.4  | V    |

|      | Input current at              | DETEN      | VFOEW                                                  | V1=7V                                |                          |      |      | 0.2  |      |

| 11   | maximum input voltage         | All others | VCC = 5.25 V.                                          | Alexa                                |                          |      |      | 0.1  | mA   |

| WOW! | High-level                    | DETEN      | WFOEW                                                  | W - 22W                              |                          |      |      | 40   | 17.6 |

| ин   | input current                 | All others | VCC = 5.25 V,                                          | V1 = 2.7 V                           |                          |      |      | 20   | μА   |

| 14   | Low-level                     | DETEN      | V                                                      | W-04W                                | The state of             |      |      | -0.8 | 1=0  |

| IIL  | input current                 | All others | VCC - 5-25 V.                                          | VCC = 5.25 V, V <sub>1</sub> = 0.4 V |                          |      |      |      | mA   |

| os   | Short-circuit output current‡ |            | VCC = 5.25 V,                                          | Vo=0                                 | -20                      | 9    | -100 | mA   |      |

| cc   | Supply current                |            | V <sub>CC</sub> = 5.25 V,<br>All outputs open          | All inputs at C                      |                          | 70   | 115  | mA   |      |

All typical values are at VCC = 5 V, TA = 25°C

Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER† | FROM<br>(INPUT) | TO (OUTPUT)  | TEST CONDITIONS                                | MIN             | TYP | MAX | UNIT   |

|------------|-----------------|--------------|------------------------------------------------|-----------------|-----|-----|--------|

| †max       |                 |              | the second second second                       | 12              | 16  |     | MHz    |

| TPLH       |                 | CYC CMP      |                                                |                 | 43  | 60  | ns     |

| tPHL       | CLOCK           | CTC CMP      |                                                |                 | 41  | 60  | , this |

| TPLH       | CLOCK           | All others   |                                                |                 | 35  | 55  | -      |

| TPHL       |                 | All Others   | 400-10                                         |                 | 33  | 50  | ns     |

| tPHL.      | RESET           | CYC CMP      |                                                | -               | 26  | 40  | ns     |

| tPLH       | MLOL !          | All others   |                                                |                 | 39  | 55  | 100    |

| tPLH       | ANNEN           | ANN          | D - 21-0 C - 15-5                              |                 | 9   | 15  | ns     |

| TPHL       | MAIAEIA         | ANN          | R <sub>L</sub> = 2 kΩ, C <sub>L</sub> = 15 pF, | Service and the | 13  | 20  | ris    |

| TPLH       | REPEN           | REP          | See Figure 1                                   |                 | 9   | 15  | ns     |

| tPHL       | HEFEN           | ner          |                                                |                 | 13  | 20  | ns     |

| tPLH       | XOEN            | Χō           |                                                |                 | 10  | 15  | -      |

| TPHL       | AGEN            | 70           |                                                |                 | 13  | 20  | ns     |

| tPLH .     | XIEN            | XI           |                                                |                 | 30  | 45  | ns     |

| TPLH       |                 | RESTORE      |                                                |                 | 11  | 15  | ns     |

| tPHL       | DETEN           | HESTONE      |                                                |                 | 13  | 20  | HS     |

| tPLH       | DETEN           | STROBE CLOCK |                                                |                 | 9   | 15  | ns     |

| tPHL.      |                 | STROBE CLOCK |                                                |                 | 14  | 20  | 133    |

†f<sub>max</sub> = maximum clock frequency

tpLH = propagation delay time, low-to-high level output

tpHL = propagation delay time, high-to-low-level output

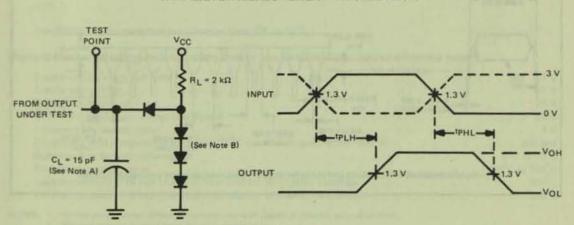

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>L</sub> includes probe and jig capacitance,

B. All diodes are 1N916 or 1N3064,

C. Input pulses are supplied by a generator having the following characteristics:  $t_f \le 15$  ns,  $t_f \le 6$  ns, PRR  $\le 1$  MHz,  $Z_{\rm out} \approx 50~\Omega$ .

FIGURE 1

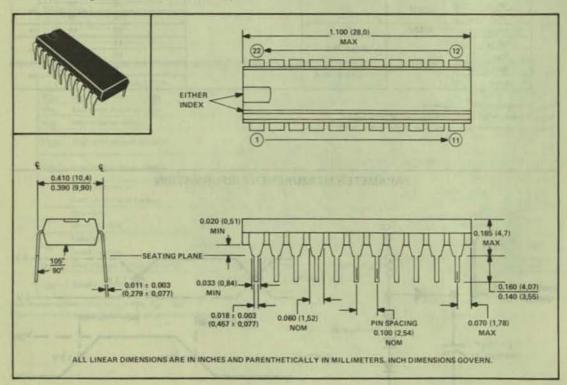

#### ORDERING INSTRUCTIONS AND MECHANICAL DATA

#### general

This circuit is available in the 22-pin plastic dual-in-line package (outline N). Orders for this circuit should include the package outline letter (N) at the end of the circuit type number, i.e., SN74LS361N.

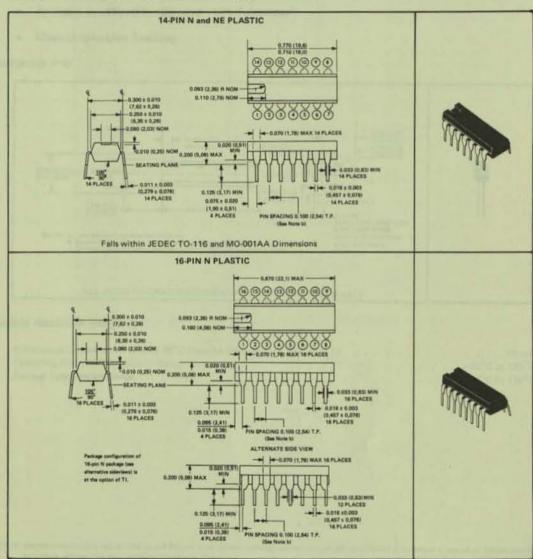

#### N plastic dual-in-line package

This dual-in-line package consists of a circuit mounted on a 22-lead frame and encapsulated within an electrically nonconductive plastic compound. The compound will withstand soldering temperature with no deformation and circuit performance characteristics remain stable when operated in high-humidity conditions. The package is intended for insertion in mounting-hole rows on 0.400-inch (10,16-mm) centers. Once the leads are compressed and inserted, sufficient tension is provided to secure the package in the board during soldering. Leads require no additional cleaning or processing when used in soldered assembly.

# INTERFACE

## TYPE SN75281 BUBBLE-MEMORY SENSE AMPLIFIER

NOVEMBER 1978

- Precision Sensing Threshold Level between 0.8 mV and 1.2 mV

- TTL-Compatible Control Inputs

- · Three-State TTL Output

- Operates from ±5-Volt Supplies

#### description

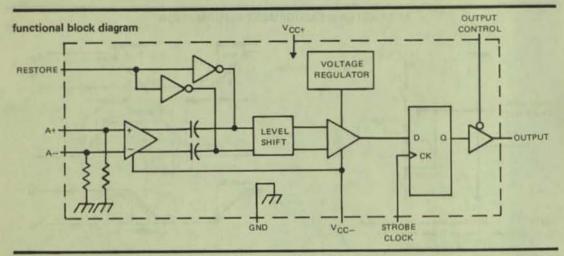

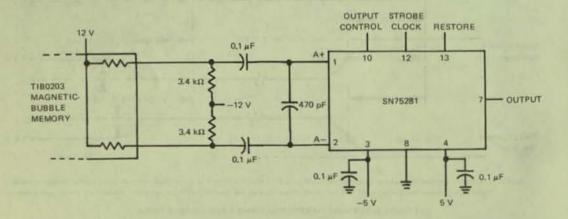

The SN75281 is a monolithic integrated circuit available in either a plastic or ceramic package. It senses the voltage change when a bubble passes the magneto-resistive detector elements in a magnetic-bubble memory. The output of this detector is connected between the differential sense inputs, A+ and A-, through an RC network. The signal produced by the presence of a bubble passing the detector elements is converted to a TTL-compatible output by the sense amplifier.

The SN75281 consists of an internally ac-coupled amplifier, a threshold sense circuit, a D-type flip-flop, and a three-state output.

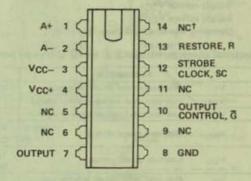

J OR N

DUAL-IN-LINE PACKAGE (TOP VIEW)

NC-No internal connection

<sup>†</sup>Grounding pin 14 improves isolation

between restore and A+ input.

Three TTL-compatible control inputs allow the precise timing necessary to detect the presence or absence of a bubble. The restore input sets the dc reference voltage on the internal coupling capacitors so that data may be sampled a short time later. The strobe clock determines the time at which the input signal is sampled by clocking the output of the differential amplifier into the D-type flip-flop. The output control, when high, sets the output to the high-impedance state.

The SN75281 is characterized for operation from 0°C to 70°C.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage VCC+ (see Note     | 1) .   | 100  | 60   | 0.0 |      | DI.  |      | * :  |      | *   |      |      |     |    |    | 1910 | (6) | * |   |   |     |    | 41 |    | 4  | 10  |    | . 7   | V  |

|-----------------------------------|--------|------|------|-----|------|------|------|------|------|-----|------|------|-----|----|----|------|-----|---|---|---|-----|----|----|----|----|-----|----|-------|----|

| Supply voltage VCC                | 2 2 3  | 4    | 400  |     |      | 4    |      | 6. 6 |      |     |      |      | 165 |    | 6  | *    |     | 6 |   | + | 411 | *  | 2  |    |    | 4   | 4  | -7    | V  |

| Voltage at either sense input     |        |      |      |     | *    |      |      |      |      |     |      |      |     |    |    | 4)   | +   |   |   | * | 187 | 10 |    |    |    | 14  |    | ±5    | V  |

| Differential sense input voltage  | (see N | ote  | 2)   |     |      |      |      |      |      |     |      |      |     |    |    |      |     |   |   |   |     | Į, |    |    |    | 4   |    | ±5    | ٧  |

| Voltage at any control input      |        |      |      |     |      |      |      |      |      |     |      |      |     |    |    |      |     |   |   |   |     |    |    |    |    |     |    |       |    |

| Continuous total dissipation at ( | or be  | low) | 25   | °C  | free | e-ai | r ti | emp  | era  | tui | e (s | ee I | Vot | e3 | 3) | *    |     |   |   |   |     |    | 40 |    | ., | 100 | 80 | 00 ir | W  |

| Operating free-air temperature r  | ange   | 14   | wit: |     |      |      |      |      | 1    |     | -    |      |     |    |    | 141  |     | 2 |   |   | 4   |    | 41 | i. | 1  | o°C | to | 70    | °C |

| Storage temperature range .       |        |      |      |     |      |      |      |      |      |     |      |      |     |    |    |      |     |   |   |   | 10  | *  |    |    | 35 | C   | to | 150   | C  |

| Lead temperature 1/16 inch (1.6   | 6 mm   | fro  | m c  | ase | for  | 60   | ) 56 | cor  | ids: | J   | pac  | kag  | 8   | Ä  | 4  | -    |     |   | 2 | 3 |     | 48 |    |    |    | Ä   | 10 | 300   | °C |

| Lead temperature 1/16 inch (1.6   | 6 mm   | fro  | m c  | ase | for  | 110  | ) 56 | 2001 | nds: | N   | pac  | kag  | e   |    |    |      |     |   |   | 4 | 9   |    |    | *  |    |     |    | 260   | °C |

- NOTES: 1. Voltage values, except differential voltages, are with respect to network ground terminal.

- 2. Differential input voltages are at A+ with respect to A-.

- Above 52°C free-air temperature, derate the J package at the rate of 8.2 mW/°C.

Above 63°C free-air temperature, derate the N package at the rate of 9.2 mW/°C.

PRELIMINARY DATA SHEET

178

Copyright © 1978 by Texas Instruments Incorporated

## TYPE SN75281 BUBBLE-MEMORY SENSE AMPLIFIER

#### recommended operating conditions

|                         |   |  |      |   |   |   |    |   |   |   |    |  |       |  |    | MIN  | NOM | MAX   | UNIT |

|-------------------------|---|--|------|---|---|---|----|---|---|---|----|--|-------|--|----|------|-----|-------|------|

| Supply voltage VCC+     | - |  | 21/2 | i | 4 | - | (A | 4 | 4 | 2 | 14 |  | <br>1 |  | 16 | 4.75 | 5   | 5.25  | V    |

| Supply voltage VCC-     |   |  |      |   |   |   |    |   |   |   |    |  |       |  |    |      |     | -5.25 | V    |

| Operating free-air temp |   |  |      |   |   |   |    |   |   |   |    |  |       |  |    |      |     | 70    | °C   |

#### electrical characteristics at 0°C to 70°C free-air temperature (unless otherwise noted)

| 10.15 | PARAMETER                                 | TEST CONDITIONS                                                                   | MIN | TYPT | MAX  | UNIT |

|-------|-------------------------------------------|-----------------------------------------------------------------------------------|-----|------|------|------|

| VT    | Differential input threshold voltage      | VCC± = ±5 V, TA = 25°C                                                            | 0.8 | 1.0  | 1.2  | mV   |

| VIH   | High-level input voltage (control inputs) |                                                                                   | 2   |      |      | V    |

| VIL   | Low-level input voltage (control inputs)  |                                                                                   |     |      | 0.8  | V    |

| Voн   | High-level output voltage                 | V <sub>CC±</sub> = ±4,75 V, I <sub>OH</sub> = -400 μA,<br>Output control at 0.8 V | 2.4 |      |      | V    |

| VOL   | Low-level output voltage                  | V <sub>CC±</sub> = ±4.75 V, I <sub>OL</sub> = 10 mA,<br>Output control at 0.8 V   |     | 0.5  | 0,8  | V    |

| ин    | High-level input current (control inputs) | V <sub>CC±</sub> = ±5.25 V, V <sub>I</sub> = 4 V                                  |     |      | 20   | μА   |

| TIL   | Low-level input current (control inputs)  | VCC± = ±5.25 V, VIL = 0                                                           |     |      | -0.4 | mA   |

| Zį.   | Input impedance                           | f = 2 MHz                                                                         |     | 2    |      | kΩ   |

<sup>&</sup>lt;sup>†</sup>All typical values are at V<sub>CC±</sub> = ±5 V, T<sub>A</sub> = 25 °C.

#### timing requirements over recommended supply voltage range, TA = 0°C to 70°C

|       | PARAME                                   | MIN                                   | MAX      | UNIT |    |

|-------|------------------------------------------|---------------------------------------|----------|------|----|

|       | Date of the State State of               | sense input high to strobe clock high | 15<br>25 |      | -  |

| tu    | Data setup time (see Figure 2)           | sense input high to restore high      |          |      | ns |

| th    | Data hold time, restore high to sense in | 15                                    |          | ns   |    |

| TRLAH | Delay time, restore low to sense input   | 30                                    |          | ns.  |    |

| t,    | Rise time, restore and strobe clock inp  |                                       | 100      | ns   |    |

| te    | Fall time, restore and strobe clock inpi |                                       | 100      | ns   |    |

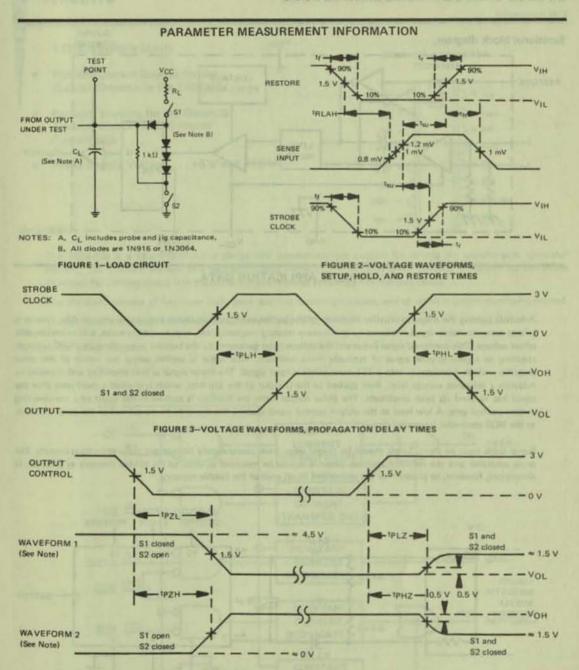

#### switching characteristics at VCC± = ±5 V, TA = 25°C

|       | PARAMETER                                        | TEST CONDITIONS         | TYP | UNIT |  |

|-------|--------------------------------------------------|-------------------------|-----|------|--|

| TPLH  | Propagation delay time, low-to-high-level output |                         | 20  | ns   |  |

| tPHL. | Propagation delay time, high-to-low-level output | R <sub>L</sub> = 4 kΩ   | 20  | ns   |  |

| TPZH  | Output enable time to high level                 | C <sub>L</sub> = 25 pF, | 30  | ns   |  |

| 1PZL  | Output enable time to low level                  | See Figures 1, 3,       | 30  | ns   |  |

| tPHZ  | Output disable time from high level              | and 4                   | 10  | ns   |  |

| TPLZ  | Output disable time from low level               |                         | 10  | ns   |  |

## TYPE SN75281 BUBBLE-MEMORY SENSE AMPLIFIER

NOTE: Waveform 1 shows the output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 shows the output with internal conditions such that the output is high except when disabled by the output control.

#### FIGURE 4-VOLTAGE WAVEFORMS, ENABLE AND DISABLE TIMES

All input pulses are supplied by generators having the following characteristics: t<sub>f</sub> ≤ 7 ns, t<sub>f</sub> ≤ 7 ns, PRR ≤ 1 MHz, Z<sub>out</sub> ≈ 50 Ω.

## TYPE SN75281 BUBBLE-MEMORY SENSE AMPLIFIER

TYPICAL APPLICATION DATA

A bubble passing the magneto-resistive elements on the bubble-memory chip causes a resistance change. Also present is a large common-mode signal produced by the in-plane rotating magnetic field, high-frequency noise, and an undesirable offset voltage. This combined signal (noise and the voltage pulse generated by the bubble) passes through an RC network resulting in a peak-to-peak signal of typically three millivolts. This signal is applied across the inputs of the sense amplifier, which translates it into a TTL-compatible output signal. The input signal is first amplified and clamped to establish a reference voltage level, then applied to the D input of the flip-flop, which is clocked a short time after the signal has reached its peak amplitude. The pulse output from the flip-flop is applied to the input of a noninverting output-control gate. A low level at the output-control input enables the signal to be passed out of the sense amplifier to the MOS controller integrated circuit.

Signal leads must be short. Leads should be placed away from power-supply lines or any noise-generating circuits. The sense amplifier and the resistor/capacitor network should be mounted as close to the bubble memory as possible. It should not, however, be placed near the unshielded (lead) ends of the bubble memory.

## INTERFACE CIRCUITS

## TYPE SN75380 BUBBLE-MEMORY FUNCTION DRIVER

NOVEMBER 1978

- TTL-Compatible Inputs

- Provides Current Sources for the Control Elements in the TIB0203

- Provides Tracking for the Generate Element with Minimal External Components

- Power Supply Voltages . . . +5 V and -12 V

#### description

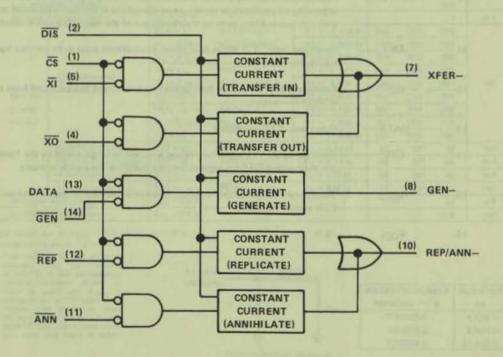

The SN75380 is a 16-pin dual-in-line device with constant-current outputs for driving the transfer gate, generator element, and replicate element of a magnetic-bubble memory. The function driver converts the digital control pulses generated by a timing circuit into the current pulses required to operate the memory device.

The SN75380 consists of five input logic gates and five current generators, one of which is temperature compensated.

The SN75380 is characterized for operation from 0°C to 70°C.

#### functional block diagram

PRELIMINARY DATA SHEET

1178

Copyright © 1978 by Texas Instruments Incorporated

## TYPE SN75380 BUBBLE-MEMORY FUNCTION DRIVER

| PIN NO. | SIGNATURE         | DESCRIPTION                                                                                                                                                                                                                                            |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CS                | Chip-select input: TTL active low.                                                                                                                                                                                                                     |

| 2       | DIS               | Disable input: TTL active low; disables all current sink outputs.                                                                                                                                                                                      |

| 3       | GND               | Ground                                                                                                                                                                                                                                                 |

| 4       | XO                | Transfer-out enable input: TTL active low; enables bubbles in the minor loop to be transferred into the major loop.                                                                                                                                    |

| 5       | XI                | Transfer-in enable input: TTL active low; enables bubbles in the major loop to be transferred into the minor loop.                                                                                                                                     |

| 6       | Rref              | Reference resistor; 1% resistor to-ground sets the XFER— and REP/ANN— output currents.                                                                                                                                                                 |

| 7       | XFER-             | Transfer output; provides a current pulse that generates a transfer (in or out) operation in the bubble memory.                                                                                                                                        |

| 8       | GEN-              | Generate output; provides a current pulse that generates a magnetic domain inversion in the bubble memory.                                                                                                                                             |

| 9       | Vcc-              | -12 V                                                                                                                                                                                                                                                  |

| 10      | REP/ANN-          | Replicate/annihilate output: provides two different types of current pulses that, depending on amplitude or timing, cause the bubble at the replicator either to be split into two bubbles, or to be transferred out of the major loop and eliminated. |

| 11      | ANN               | Annihilate input: TTL active low; causes an annihilate pulse to be emitted from the REP/ANN—output.                                                                                                                                                    |

| 12      | REP               | Replicate input: TTL active low; causes a replicate pulse to be emitted from the REP/ANN— output.                                                                                                                                                      |

| 13      | DATA              | Data input: TTL compatible                                                                                                                                                                                                                             |

| 14      | GEN               | Generate input: TTL active low; causes a current to be generated by the function driver (provided DATA is high) to create a bubble in the bubble memory.                                                                                               |

| 15      | R <sub>temp</sub> | Temperature compensation; a resistor/thermistor network to ground that sets the GEN output current.                                                                                                                                                    |

| 16      | Vcc+              | +5 V                                                                                                                                                                                                                                                   |

### TYPE SN75380 BUBBLE-MEMORY FUNCTION DRIVER

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|            | Itage VCC+ (se    |       |      |     |   |      |    |    |     |    |     |      |    |    |   |    |     |     |    |   |   |     |     |      |    |   |     |    |     |      |     |       |

|------------|-------------------|-------|------|-----|---|------|----|----|-----|----|-----|------|----|----|---|----|-----|-----|----|---|---|-----|-----|------|----|---|-----|----|-----|------|-----|-------|

| Supply vo  | Itage VCC-        |       |      | 110 |   |      | 18 | 1  | Œ   |    | A 3 | . 16 |    |    |   |    | 12. | (8) |    |   | 3 |     |     | W.   |    |   | * 1 |    |     |      | 74  | 13 V  |

| Input volt | tage              |       | 1    | 0/4 |   | . 2  | -  | 14 | 14  | ž. |     |      | 00 | à. |   | 1  |     |     | -  | ě | 4 | i i | 140 | -    | ů. | 1 | 201 | 0  | 4   | 4 1  |     | 5.5 V |

| High-level | output voltage    |       |      | 00  |   | . 10 |    |    |     |    |     |      |    | 97 |   | (9 |     | 91  | 91 |   | , | 4   | 14/ |      |    |   | 56  |    |     | 9. 1 |     | 15 V  |

| Continuo   | us total dissipat | tion  | 4    | 83  |   |      | -  | G  | 300 | 8) |     | 4 7  |    |    |   |    | 4   | (4) | 21 | 8 |   | 4   | 1   | 4    | 11 | 6 |     |    |     | 4    | 600 | mW    |

| Operating  | free-air temper   | ratur | е га | ang | e | -    | *  | 19 |     | -  |     |      | -  | ,  | * | 6  |     |     | 91 |   |   |     |     | )# T | +) |   |     |    | 0   | °C   | to  | 70°C  |

| Storage to | emperature rang   | ge .  |      |     | * |      |    | -  |     |    | 4 1 |      | *  | -  |   | -  |     | 4   | -  |   |   | 4   |     |      |    |   |     | -6 | 5°( | Ct   | 0 1 | 50°C  |

|            | perature 1/16 in  |       |      |     |   |      |    |    |     |    |     |      |    |    |   |    |     |     |    |   |   |     |     |      |    |   |     |    |     |      |     |       |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                         |    |     |     |     |      |    |    |   |     |   |   |   |      |    |    |   |   |   |      |    |   |    | MIN   | NOM | MAX   | UNIT |

|-------------------------|----|-----|-----|-----|------|----|----|---|-----|---|---|---|------|----|----|---|---|---|------|----|---|----|-------|-----|-------|------|

| Supply voltage VCC+     |    |     |     |     | - 10 | l. | 14 |   | 10. |   |   |   | 2182 |    | 9: |   | 1 | 5 | 1.00 |    |   |    | 4.75  | 5   | 5.25  | V    |

| Supply voltage VCC-     | -1 | 12  |     | 180 |      | -  |    | 4 | 14  | 4 |   | 4 | (4)  | 16 |    | - |   |   |      | à. |   | 14 | -11.4 | -12 | -12.6 | V    |

| Operating free-air temp | er | atu | ire | ×   |      |    |    |   |     |   | × | 4 |      | -  | 95 |   |   |   | -    |    | * |    | 0     |     | 70    | °C   |

Caution: Permanent damage may be done to the bubble memory if specified pulse widths for the function timing generator are exceeded.

### electrical characteristics over recommended ranges of V<sub>CC+</sub>, V<sub>CC-</sub>, and operating free-air temperature (unless otherwise noted)

|         | PAR        | AMETER               |                     | TEST CONDITION              | VS .                    | MIN | TYPT   | MAX  | UNIT |

|---------|------------|----------------------|---------------------|-----------------------------|-------------------------|-----|--------|------|------|

| VIH     | High-level | input voltage        | THE PERSON NAMED IN |                             |                         | 2   | -      | p. I | V    |

| VIL     | Low-level  | input voltage        |                     |                             |                         |     |        | 0.8  | V    |

| (O(off) | Off-state  | output current       | Vo = 12 V           |                             | THE PERSON              |     | 11 110 | 1    | mA   |

|         |            |                      | GEN = L,            | DATA = H,                   | R1 = 4,120 Ω            | 264 | 290    | 316  |      |

|         |            |                      | RL = 3.16 ft.       | R <sub>ther</sub> = 826 Ω,  | R1 = 2,000 II           | 328 | 360    | 392  |      |

|         |            | Acres 1              | TA = 0°C            |                             | R1 = 27,400 Ω           | 214 | 235    | 256  | -    |

|         |            | are to the same      | GEN = L,            | DATA = H,                   | R1 = 4,120 Ω            | 241 | 265    | 289  |      |

|         |            | GEN (generate)       | RL = 3.16 Ω.        | R <sub>ther</sub> = 1000 Ω, | R1 = 2,000 Ω            | 305 | 335    | 365  | mA   |

|         | On-state   | See Note 2           | TA = 25°C           |                             | R1 = 27,400 II          | 191 | 210    | 229  |      |

| O(on)   | output     | 7                    | GEN = L,            | DATA = H,                   | R1 = 4,120 Ω            | 200 | 220    | 240  |      |

|         | current    |                      | RL = 3.16 ft.       | R <sub>ther</sub> = 1366 Ω, | R1 = 2,000 Ω            | 264 | 290    | 316  |      |

|         | TANK TANK  |                      | TA = 70°C           |                             | R1 = 27,400 Ω           | 150 | 165    | 180  |      |

|         |            | REP/ANN (replicate)  | REP - L.            | ANN = H,                    | R <sub>L</sub> = 5.11 Ω | 72  | 80#    | 88   | mA   |

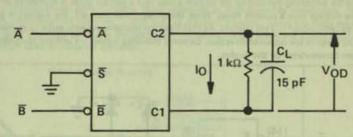

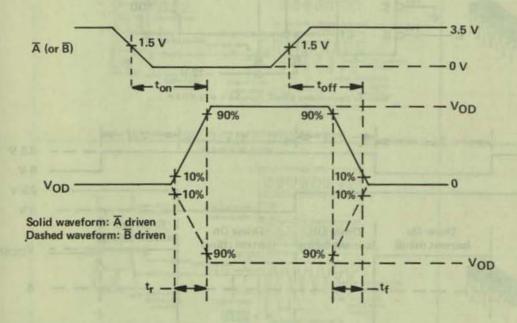

|         |            | REP/ANN (annihilate) | REP - H.            | ANN = L,                    | RL = 5.11 Ω             | 54  | 60*    | 66   | mA   |