# 286 LX SERIES USER'S MANUAL

# 286 LX Series System 286 LX-A and 286 LX-M)

# Table of Contents

| namiledance tamana |

|--------------------|

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

#### STARTING UP THE SYSTEM

Power up the system and wait for the system to show up the system activity on the screen.

#### MEMORY TEST BYPASS

The system performs diagnostics of the system and displays the size of the memory being tested.

Note that you can bypass the memory test by pressing the <ECS> key. This option would be quite useful when the memory on the system is quite large. You should hit the <ESC> key when the message Press <ESC> Key to bypass MEMORY test appears on the screen.

# Figures and Tables

| Figure 1 | Block Diagram of the 286 LX           |    |

|----------|---------------------------------------|----|

|          | Baby Board                            | 7  |

| Figure 2 | Memory Map Options                    | 16 |

| Figure 3 | 36-Pin Card-Edge Connector            | 39 |

| Figure 4 | 62-Pin Card-Edge Connector            | 40 |

| Figure 5 | Pin Description for                   |    |

|          | CLock Modulation PAL                  | 43 |

| Figure 6 | Block Diagram of the 286 LX-A         | 56 |

| Figure 7 | Block Diagram of the 286 LX-M         | 57 |

|          | MEMORY TEST BYPASS                    |    |

| Table 1  | Interrupt Controllers                 | 12 |

| Table 2  | DMA Channels                          | 13 |

| Table 3  | System Cycle Times                    | 15 |

| Table 4  | Description of the Main Board         |    |

|          | Connectors, Jumpers and Switches      | 18 |

| Table 5  | RAM Configuration                     | 26 |

| Table 6  | RAM Configuration                     | 35 |

| Table 7  | I/O Address Map                       | 38 |

| Table 8  | Duration of I/O and Memory Cycles for |    |

|          | Various System Configurations         | 45 |

| Table 9  | CMOS RAM Addresses                    | 53 |

# 286 LX Series System (286 LX-A and 286 LX-M)

# INTRODUCTION

The mother board used for the 286 LX series is a fully IBM PC AT compatible baby board based on the VL82PCAT 5-chip IBM PC AT compatible chip set. The mother board is implemented in an IBM PC/XT compatible form factor, but mounting holes are provided for AT-chassis mounting. This mother board implementation provides jumpers to allow for all of the features of the VL82PCAT set to be evaluated. In this board, only 18 non-memory components (38 total components, including the TTL delay line) are required allowing for a minimum chip count implementation.

Fixed disk drive D rose XXIII neverted

In this document, the following terms are VLSI-specific and require a more detailed explanation.

After that, the setup takes two different paths depending upon the CMOS being initialized or uninitialized.

#### **CMOS** Initialized

Under these conditions you would see the following messages

Fixed disk drive C type:X(if installed else Not Installed.)

Fixed disk drive D type:X(if installed else Not Installed.)

Diskette drive A is 3 1/2"

Diskette drive B is :Double Sided (Other options as above)

Base Memory Size is :XXX KB

Expansion memory size is:XXXX KB

Are these options correct (Y/N)?

Note that the information about Dirive A indicates 3 1/2", as CMOS had been set earlier to reflect this status. If on the contrary, CMOS had been set for a 1.2 MB drive, the message in place of 3-1/2" it would be High Capacity.

If you feel that the information displayed above is right hit < Y > and the <ENTER > key to proceed to system boot with the new information.

#### **CMOS Uninitialized**

### Disk Drive Type Definition

In this case you would have to enter the type of the fixed Drive C in response to the message:

......WARNING......

Entering the wrong disk drive TYPE causes improper operation of the disk.

If disk not installed press < RETURN> For disk TYPE details press < ESC>

Enter disk drive type (1-47)?

Note that the disk type details are only a key stroke away. Hit <ESC> key to find for yourself. You could always come back by hitting <ESC> again. Refer to Appendix B for drive details.

Once you have convinced yourself about the drive type enter the appropriate number and hit <ENTER>.

Note that pressing <ENTER > key alone indicates the absence of the Drive C.

#### **CLOCK MODULATION**

This feature automatically switches the processor clock speed from 12MHz down to 8MHz or 6MHz when an I/O operation is detected. This allows peripherals that have access time problems to function properly with a processor running at 12MHz.

#### 286 LX Series System

## System Board Features of the 286 LX-A and 286 LX-M Systems

- Supports up to 12MHz system operation (optional 10MHz system operation)

- Norton SI Benchmark rating of 15.3

- . 0 wait state READ operation

- 1 wait state WRITE operation

- Clock modulation for 8/6MHz or 12/10MHz system operation with Turbo indicator

- . Fully IBM PC AT compatible

- . 4MB onboard DRAM, 100ns access time

- . IBM PC/XT size form factor (AT mounting holes)

- . 20mA, 200pF slot drive capability

- . 8mA, 150pF DRAM drive capability

- . 4-layer implementation for low-noise operation

- . Minimum component count implementation

## SUMMARY OF SET-UP

The Set-Up screen thus requires you to set

- a). Date.

- b). Time.

- c). Hard Disk Type For Drive C (if present)

- d). Hard Disk Type For Drive D (if present).

The Set-up precedure also automatically detects the following:

- a) Type Of Display Card.

- b) Size Of Real Memory.

- c) Size Of Memory beyond 1 MB.

- d) Presence of 360kb floppy drives.

- e) Presence of a 80287.

Also, if a second Hard Disk drive is physically connected but the CMOS is not set for this Drive D, the SYSTEM informs you about the same and gives you a chance to configure the drive through SETUP

Having setup the CMOS, the SYSTEM runs through the diagnostics again, tests the memory, sets up the devices configured and proceeds to boot.

Note that the Set-up option is available even after a soft reset.

# When does The SYSTEM Prompt You to Run Set-up?

The SYSTEM prompts you to run Set-up under the following conditions

- a) CMOS options not set.

- b) Display Configuration Mismatch

- c) Memory Size mismatch.

- d) Hard Disk Set-up error.

- e) CMOS battery is low.

- f) An additional hard disk presence is detected.

# **Errors Reported By SYSTEM**

SYSTEM performs various diagnostic tests at the time the system is powered up. Whenever an error is encountered during these tests either you hear a few short beeps or see an error display on your monitor. If the error occurs before the display device is initialised the system reports the error by giving a number of short beeps.

If the error is FATAL the system halts after reporting the FATAL error. If the error is NON-FATAL the process continues after reporting the NON-FATAL error.

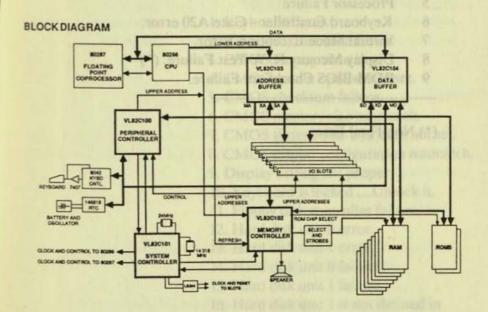

In the diagram, the VL82C100 replaces the bulk of the LSI peripherals used in the PC/AT, while the other components replace MSI and SSI components. In this diagram, the system shown is for 12MHz with zero wait state and 1MB of RAM (1 wait state for reads is an option available with the use of 120ns DRAMs). For various design reasons, certain peripheral functions were left outside of the VL82CPCAT chip set. These include the 146818 Real-Time Clock with its oscillator (14069) and the 8742 keyboard controller. Also left outside are some of the memory control circuitry.

#### Processor

The 286 LX baby board contains an 80286 processor running at 12MHz (slower speeds optional) with a processor clock cycle time of 83.3ns, and an average memory cycle time of 175ns (0 wait state on reads, 1 wait state on writes with a read/write ratio of 9:1). These memory cycle times are more than twice as fast as the memory cycle times of an 8Mhz IBM PC AT running with one wait state.

### Math Coprocessor

A socket is provided for an optional 80287 math coprocessor. The coprocessor runs on a clock that is the same as the processor. For full speed operation, a 10MHz coprocessor is required.

#### **Onboard RAM**

The 286 LX-A contains space for 36 16-pin or 18-pin DRAMs that can contain either 64KB, 256KB or 1MB DRAMs.

The 286 LX-M contains space for 36 16-pin DRAMs that can contain either 64KB or 256KB DRAMs, and 4 30-pin module DRAMs that can contain 256KB or 1MB DRAMs.

When populated with a combination of 256KBs and/or 64KBs, the 286 LX can support memory maps of 512KB, 640KB, 1MB, 2MB or 4MB.

#### **Onboard ROM**

The 286 LX contains sockets for 2 BIOS EPROMs that can either be 27128s or 27256s. The access times for the EPROMs can be either 120ns with 1 wait state or 200ns when using 2 wait state accesses. ROM access cycles are either 3 or 4 processor cycles long.

# USE OF 3 1/2" SUPPORT EFFECTIVELY

DOS 3.20 provides support for 3 1/2" drives. Earlier versions of DOS would require the use of DRIVER. SYS to provide the necessary support.

The 3 1/2" drive can be freely configured as drive A or Drive B with this BIOS. Thus it is possible to boot off directly from a 3 1/2" drive.

A few points would have to be kept in mind when you perform the Setup you define the drives correctly. Incorrect definition could make the drive unusable.

The table below describes the valid combinations on an AT.

| CMOS Sta  | tus Physical | Drive Status Functional |

|-----------|--------------|-------------------------|

| 1.2MB     | 1.2MB        | YES                     |

| 3 1/2"    | 3 1/2"       | YES                     |

| Undefined | 1.2MB        | YES                     |

# DIAGNOSTICS

# Diagnostics Menu

The Diagnostics memu as seen on the screen is shown in Fig. 1 of Appendix B.

Note the following in the Diagnostics Opening Menu:

- a) The Guide Line in Reverse Video specifying the usage of the Cursor Keys, <ENTER> & <ESC> key.

- b) The Configuration of the system in the "Devices Present" box.

- c) The Real Time Clock ticking away at the right hand top corner of the screen.

- d) Diagnostics Options Line Hard Disk, Floppy, Keyboard, Video & Miscellanceous Diagnostics.

- e) Hard Disk Diagnostics Options Window detailing the various hard disk diagnostics that are available.

Table 1 Interrupt Controllers

| NMI | Parity Error            | 80286 NMI         |

|-----|-------------------------|-------------------|

| 0   | Timer Channel 0         | Master PIC, Int   |

| 1   | Keyboard Controller     | Master PIC, Int   |

| 2   | Slave PIC               | Master PIC, Int   |

| 3   | Clock/Calendar          | Slave PIC, Int    |

| 4   | 8-bit Slot, IRQ 9       | Slave PIC, Int    |

| 5   | 16-bit slot, IRQ10      | Slave PIC, Int    |

| 6   | 16-bit slot, IRQ11      | Slave PIC, Int    |

| 7   | 16-bit slot, IRQ12      | Slave PIC, Int    |

| 8   | Math Coprocessor - Busy | Slave PIC, Int    |

| 9   | 16-bit slot, IRQ14      | Slave PIC, Int    |

| 10  | 16-bit slot, IRQ15      | Slave PIC, Int    |

| 11  | 8-bit slot, IRQ 3       |                   |

|     | (Serial Port)           | Master PIC, Int   |

| 12  | 8-bit slot, IRQ 4       |                   |

|     | (Serial Port)           | Master PIC, Int   |

| 13  | 8-bit slot, IRQ 5       |                   |

|     | (Printer Port)          | Master PIC, Int 5 |

| 14  | 8-bit slot, IRQ 6       |                   |

|     | (Flex Disk Drive)       | Master PIC, Int 6 |

| 15  | 8-bit slot, IRQ 7       |                   |

|     | (Printer Port)          | Master PIC, Int 7 |

### 286 LX Series System

#### **DMA Controllers**

The VL2C100 contains 2 82C37A DMA Controllers that handle both 8-bit byte and 16-bit word transfers. These controller operate at 1/2 of the processor clock speed (processor running at 12MHz corresponds to DAM Controller running at 6MHz). Table 2 lists the usage of the DMA channels and the corresponding signals that drive them.

Table 2 DMA Channels

| Slave DMA Master DMA<br>Channel # Channel # | Device               |

|---------------------------------------------|----------------------|

| O the user new the dumping                  | 8-bit Slot, DRQ 0    |

| 1 among the so upandard D                   | 8-bit Slot, DRQ 1    |

| 2 brail sof grimman 4 indi & bo             | 8-bit Slot, DRQ 2    |

| 3 hetmerke the level was now                | 8-bit Slot, DRQ 3    |

| - Wednesday 4 to tank                       | Slave DMA Controller |

|                                             | input to Master DMA  |

| - Maria deposition de la                    | 16-bit Slot, DRQ 5   |

| - 6                                         | 16-bit Slot, DRQ 6   |

| - 7                                         | 16-bit Slot, DRQ 7   |

|                                             |                      |

All the options under Hard Disk Diagnostics require more or less the following inputs:

- a) Disk Drive

- b) Drive Type

- c) Interleave Factor

- d) Bad TRack List

- e) Start Cylinder

- f) End Cylinder

- g) Start Head

- h) End Head

All the above input fields have a default value. Thus a user need not necessarily key-inall the inputs.

We shall discuss the inputs required & their meaning for Hard Disk Format Option. This discussion can however be expended for the rest of the Hard Disk Options.

# Hard Disk Format Option - (Destructive Operation)

Figs 6 & 7 reflect the various screens the user goes through when this option is selected.

Note that in case of a single drive System the disk drive for the operation is assurmed to be drive D.

## a) Drive Type Definition

The default value for the drive type is the SETUP value set during the CMOS setup.

However if the drive was not set during CMOS Setup, the user now has an option of setting the drive to be one among the 46 atandard Disk drive types.

Note that all the information about the drive unfolds when the disk dirve type is being chosen.

Ref. Fig.6 depicting the way the screen looks when this option is chosen.

If the disk drive type does not fall within the 46 standard disk types, use the USER option to define your own parameters for the drive.

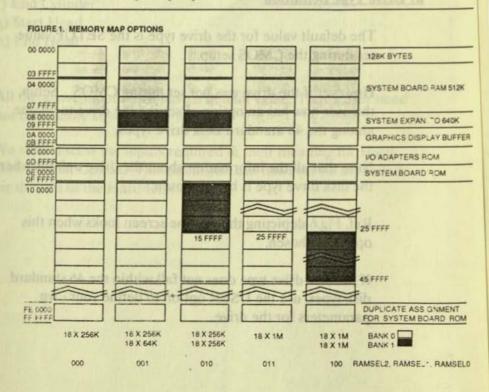

## Memory Maps

The 286 LX supports 5 memory maps ranging from 512K to 4MB.

Any memory reference made to an address outside of the range will be directed toward the system expansion bus. The available maps for this card are shown in Figure 2.

Figure 2 Memory Map Options

# THE MAIN BOARD CONNECTORS, JUMPERS AND SWITCHES

The main board connectors, jumpers and switches are used to configure your system.

The jumpers are used to configure a variety of options that are supported by the VL2CPCAT chip set. These jumpers are described in the following sections.

Connections to the 286 LX must be made through different types of connectors in different places. The description of the connectors are shown in the following sections. Note that the external battery that supplies the RTC should be between the range of 3.6 to 6VDC.

# The Jumpers, Connectors and Switches in 286 LX-A

The location and function of each of these connectors, jumpers or switches are shown in Table 4.

# g) Activity Screen

SYSTEM then proceeds to format the Hard Disk with the specified parameters. While it is formatting SYSTEM displays the Operation in progress, the Cylinder & Head No. that is being formatted.

You could always hit <ESC>key to abort the format operation.

# Auto Interleave Option - (destructive Operation)

This is the most powerful feature which enables you to get the peak performance out of your Hard Disk.

With this feature you need not speculate about the value of the Interleave Factor. SYSTEM is entrusted with the job of finding the optimum Interleave value by a trial & error method & formatting the Hard Disk with this value.

Discover the big advantage with this feature.

# Media Analysis Option - (Destructive Operation)

Media analysis performs the following operations on the Hard Disk:

- Preformats the Hard Disk with specified parameters like Format Option.

- Analysis the surface of the Hard Disk for any errors & makes a note of them.

- Marks the Bad Patches.

This takes quite some time & for best results this test should run uninterrupted.

The parameters required for this are to be inputted in the same way like the Format Option.

# J19 and J20 (Power Connectors)

The pin assignments for the power connectors J19 and J20 are as follows:

J19:

| Pin | Assignment | Color  |

|-----|------------|--------|

| 1   | Power Good | orange |

| 2   | +5v        | red    |

| 3   | +12V       | yellow |

| 4   | -12V       | blue   |

| 5 . | GND        | black  |

| 6   | GND        | black  |

|     |            |        |

J20:

| Pin | Assignment | Color |

|-----|------------|-------|

| 1   | GND        | black |

| 2   | GND        | black |

| 3   | -5V        | white |

| 4   | +5V        | red   |

| 5   | +5V        | red   |

| 6   | +5V        | red   |

|     |            |       |

### J22 (External Battery Connector)

The pin assignments are as follows:

| Pin | Assignment   |

|-----|--------------|

| 1   | v+T and same |

| 2   | NC           |

| 3   | GND          |

| 4   | GND          |

|     |              |

As in the case of hard disk the list below gives the effect of each of the diskette tests:

- a) Diskette Format Destructive.

- b) Speed Test Non-destructive.

- c) Random R/W Test Destructive

- d) Sequential R/W Test Destructive.

- e) Disk Change Line Test- Non-destructive.

## Diskette Format - (Destructive)

This test allows an user to check out the NEC 765 controller's abilities to format a diskette.

The user need not be bothered about the dirve or the diskette in the drive. SYSTEM automatically determines the best way a diskette can be formatted for reliablity, e.g. In case of a 1.2MB drive the user need not specify whether the diskette to be formatted is 1.2 MB or 360 KB capacity. SYSTEM finds the most reliable format automatically.

Note that this test does not write a DOS format on the diskette.

### Drive Speed Test - (Non-Destructive)

The test determines the speed of rotation of the drive. Please note that the following are the allowable speeds for the various drives:

- a) 1.2 MB drive 360 rpm for a 1.2 Mb diskette in it. 300 rpm for a 360Kb diskette in it.

- b) 360 KB drive 300 rpm.

- c) 720 KBB drive 300 rpm.

Allow for a tolerance of 1% on all the speeds. Ensure that the diskette is formatted before performing this test.

### Random Read/Write Test - (Destructive)

This test performs a random read/write operation on the diskette & thus checks out the random seek capability of the drive.

Again ensure that the diskette is formatted before perfor ing this test.

# J1 (Select EPROM Size)

In Specifical

Set the jumper according to the type of chips used for the ROM BIOS:

1-2 Short 27256 chips 2-3 short 27128 chips

# J19 (DRAM Access Timing)

Set this jumper according to the right DRAM access timing.

1-2 short 80/100 ns 2-3 short 120/150 ns

# J28 (Select Backup Battery)

1-2 short Onboard battery 2-3 short Backup battery

#### J30 (Select FASTMODE or NORMAL)

FASTMODE requires zero wait state operation at 12MHz.

1-2 short FASTMODE

2-3 short NORMAL

# J31 (Select One or Zero Wait State)

Do not change the wait stete in cystem running.

ON Zero wait state

OFF One wait state

#### J102 (Select Oscillator)

The default oscillator on the 12MHz system board is a 48MHz oscillator (OSC1). The system provides a spare socket for another frequency oscillator (OSC2). If OSC2 is installed, you can run the system at the OSC2 clock rate.

1-2 short Select OCS1

2-3 short Select OCS2

# Scan/ASCII Code Test

Upon invoking this test a keyboard layout is shown on the screen. This keyboard layout might not necessarily correspond with your keyboard.

The objective of this test is to determine whether the keys depressed match with their scan code.

Thus every time a key is depressed the scan code & the ASCII code of the key is shown.

Use <CNTRL> <BREAK> key to abort this test.

Function keys 11 & 12 in an Enhanced keyboard cannot be checked out by this test.

# Video Diagnostics

Video diagnostics includes the following:

- a) Sync Test

- Checks the Sync capability.

- b) Adapter Test

- Performs test on the Display Memory.

- c) Attribute Test

- Checks the attributes of the Display

memory

d) 80 x 25 Display Test - Checks the 80 x 25 character set of the display adapter.

The video diagnostics requires very little input & the results can be visually observed.

#### Miscellaneous Diagnostics

This includes the following tests:

- a) Serial Communication Port Test.

- b) Printer Port Test.

#### Serial Communication Port Test

This test requires a special RS-232C connector to be plugged on to the port.

The details of this connector are as below:

- RD & TD Shorted.

- DST & DTR Shorted.

- CTS & RTS Shorted.

This test exercises the port for different:

-Baud Rates

# J1 (POWER Connector)

The pin assignments for the power connector J1 are as follows:

J1:

| Pin | Assignment | Color  |

|-----|------------|--------|

| 1   | Power Good | Orange |

| 2   | +5v        | Red    |

| 3   | +12V       | Yellow |

| 4   | -12V       | Blue   |

| 5   | GND        | Black  |

| 6   | GND        | Black  |

|     |            |        |

J1:

| Pin | Assignment | Color |

|-----|------------|-------|

| 1   | GND        | black |

| 2   | GND        | black |

| 3   | -5V        | white |

| 4   | +5V        | red   |

| 5   | +5V        | red   |

| 6   | +5V        | red   |

|     |            |       |

# J2 (Keyboard Connector)

The keyboard connector is a 5-pin, 90-degree PCB mounting, DIN connector. The pin assignments are as follows:

|   | Assignment     |

|---|----------------|

| 1 | Keyboard clock |

| 2 | Keyboard data  |

| 3 | NC             |

| 4 | GND            |

| 5 | +5V            |

|   |                |

# J3 (External Battery Connector)

The pin assignments are as follows:

| Pin     | Assignment             |                          |     |

|---------|------------------------|--------------------------|-----|

| 1 2 3 4 | V+<br>NC<br>GND<br>GND | VE-<br>VE+<br>VE+<br>VE+ | 100 |

# J19 and J20 (Hardware Speed and Hardware Reset Switch)

J19 is the hardware speed switch. This switch is a button switch or post jumper for selecting the system operation at high or low speed. This switch only works if JP9 is short.

J20 is the hardware reset switch. It is used for the hardware reset button.

# J21 (Speaker Connector)

The pin assignments are as follows:

| Pin | Assignment |  |  |

|-----|------------|--|--|

| 1   | SPEAK OUT  |  |  |

| 2   | NC         |  |  |

| 3   | GND        |  |  |

| 4   | +5V        |  |  |

# J22 (Keylock/Power LED)

The keylock and power LED is a 5-pin berg strip. Its pin assignments are as follows:

| Pin | Assignment       |  |  |

|-----|------------------|--|--|

| 1   | GND              |  |  |

| 2   | Keyboard inhibit |  |  |

| 3   | GND              |  |  |

| 4   | not used         |  |  |

| 5   | Power LED        |  |  |

|     |                  |  |  |

# J10 (Turbo Indicator Connector)

The system speed LED indicator indicates the current operating speed of the system. When the LED lights up, the system is operating at high speed.

The pin assignments are

| Pin | Assignment         |  |  |

|-----|--------------------|--|--|

| +   | GND<br>plus driver |  |  |

# J4 (Select Backup Battery)

| 2-3 | short | Onboard  | battery |

|-----|-------|----------|---------|

| 1-2 | short | Backup b | attery  |

# JP1 (Select FASTMODE or NORMAL)

FASTMODE requires zero wait state operation at 12MHz.

short FASTMODE open NORMAL

## J12 (Select Oscillator)

The default oscillator on the 12MHz system board is a 48MHz oscillator (OSC1). The system provides a spare socket for another frequency oscillator (OSC2). If OSC2 is installed, you can run the system at the OSC2 clock rate.

1-2 short Select OCS1

2-3 short Select OCS2

## J3 (Select One or Zero Wait State)

Do not change the wait stete in cystem running.

ON Zero wait state

OFF One wait state

## JP5 (DRAM Access Timing)

Set this jumper according to the right DRAM access timing.

1-2 short 80/100 ns 2-3 short 120/150 ns

## JP6 (Select EPROM Size)

Set the jumper according to the type of chips used for the ROM BIOS:

1-2 Short 27128 chips 2-3 short 27256 chips

## JP7,8,9 (Speed Control Mode)

These three jumpers are used to control the speed mode One of the three jumpers should be short.

| JP7 | short | Keyboard switch, signal   |

|-----|-------|---------------------------|

|     |       | from P13 (pin 30) of 8042 |

| JP8 | short | Keyboard switch, signal   |

|     |       | from P22 (pin 23) of 8042 |

| JP9 | short | for hardware speed switch |

## SW1,2,3 (Select RAM Size)

The system allows 5 onboard memory options for supporting up to a full 4MB system. The memory mapping options are shown in Table 6.

## Table 6 RAM Configuration

| Bank<br>Bank | - | 18X256K | 18X256K<br>18X64K | 18X256k<br>18X256K | 18X1M | 18X1M<br>18X1M |

|--------------|---|---------|-------------------|--------------------|-------|----------------|

| SW-1         |   | ON      | OFF               | ON                 | OFF   | ON             |

| SW-2         |   | ON      | ON                | OFF                | OFF   | ON             |

| SW-3         |   | ON      | ON                | ON                 | ON    | OFF            |

NOTES: Bank 0 comprise of the 18 sockets on top labeled from U1 to U18 or the slots (SIP) labeled slot1 and slot3.

Bank 1 comprise of the 18 sockets on the bottom labeled from U19 to U36 or the slots (SIP) labled slot2 and slot4.

## SW4 (Enable Color)

ON Color OFF Monochrome

#### USING SETUP

Before turning on the power to your system, check that all connectors are connected properly. Also check that all switches and jumpers are set correctly for your system configuration. To check how your system is configured, call out the SETUP routine. Refer to the BIOS menu for details.

## I/O CHANNEL DEFINITIONS

The figures below shows the location and numbering of the I/O channel connectors which consists of eight 62-pin and six 36-pin card-edge.

Cards which IBM declares to be incompatible with the AT architecture and thus the AT baby board includes:

8-bit cards (62-pin connector only) containing system memory.

Cards which will work in the mainboard expansion bus includes:

AT compatible cards.

PC floppy disk controller card.

Some XT type hard disk controllers (including Xebec,

Western Digital, and CDC). Refer to the technical reference manual for the details on installation.

Most 8-bit display adapters.

Most 8-bit cards containing I/O functions only.

DTC 5290 or equivalent Hard 3 Floppy Disk Controller Floppy.

## 286 LX Series System

# Table 7 I/O Address Map

| Address<br>(Hex) | Device                                                |

|------------------|-------------------------------------------------------|

|                  | The figures below shows the location and numbering of |

| 0-1F<br>20-3F    | DMA Controller #1 (82C37) - 8-bit devices             |

| 20-31            | Programmable Interrupt Controller #1 (82C59A)         |

| 40-5F            | Timer/Controller (82C54)                              |

| 60,64            | Keyboard controller (8742)                            |

| 61               | On-board Testing Registers                            |

| 70,71            | Clock/Calendar (146818)                               |

| 70,bit 7         | NMI Mask                                              |

| 78               | On-board Test Stimulus Register                       |

| 80-9F            | DMA Page Register                                     |

| 80               | Diagnostic Port Location                              |

| A0-BF            | Programmable Interrupt Controller #2                  |

|                  | (82C59A)                                              |

| CO-DF            | DMA Controller #2 (82C37A) 16-bit Devices             |

| F8-FF            | Math Coprocessor and Mark and Mark Mark               |

Most 8-bit cards containing I/O frontions only.

Figure 3 36-Pin Card-Edge Connector

| REAR PANI | EI | ì |

|-----------|----|---|

|-----------|----|---|

|           | +   | + DRAM  |       |

|-----------|-----|---------|-------|

| -MEM CS16 | D1  | C1      | SBHE  |

| -I/O CS16 | D2  | C2      | LA23  |

| IRQ10     | D3  | C3      | LA22  |

| IRQ11     | D4  | C4      | LA21  |

| IRQ12     | D5  | C5      | LA20  |

| IRQ15     | D6  | C6      | LA19  |

| IRQ14     | D7  | C7      | LA18  |

| -DACK 0   | D8  | C8      | LA17  |

| DRQ 0     | D9  | C9      | -MEMR |

| -DAC 5    | D10 | C10     | -MEMW |

| DRQ 6     | D11 | C11     | SD08  |

| -DACK 6   | D12 | C12     | SD09  |

| DRQ6      | D13 | C13     | SD10  |

| -DACK 7   | D14 | C14     | SD11  |

| DRQ 7     | D15 | C15     | SD12  |

| +5V       | D16 | C16     | SD13  |

| -MASTER   | D17 | C17     | SD14  |

| GND       | D18 | C18     | SD15  |

|           |     | 1 1 1 1 |       |

Figure 4 62-Pin Card-Edge Connector

|  | PAN |  |

|--|-----|--|

|  |     |  |

|           |     | ++     |             |

|-----------|-----|--------|-------------|

| GND       | B1  | A1     | -I/O CH CK  |

| RESET DRV | B2  | A2     | SD7         |

| +5V       | В3  | A3     | SD6         |

| IRQ9      | B4  | A4     | SD5         |

| -5V       | B5  | 1 1 A5 | SD4         |

| DRQ2      | B6  | A6     | SD3         |

| -12V      | В7  | A7     | SD2         |

| 0 WS      | B8  | A8     | SD1         |

| +12V      | B9  | A9     | SD0         |

| GND       | B10 | A10    | -I/O CH RDY |

| -SMEMW    | B11 | A11    | AEN         |

| -SMEMR    | B12 | A12    | SA19        |

| -IOW      | B13 | A13    | SA18        |

| -IOR      | B14 | A14    | SA17        |

| -DACK3    | B15 | A15    | SA16        |

| ORQ3      | B16 | A16    | SA15        |

| -DACK1    | B17 | A17    | SA14        |

| DRQ1      | B18 | A18    | SA13        |

| -REFRESH  | B19 | A19    | SA12        |

| CLK       | B20 | A20    | SA11        |

| IRQ7      | B21 | A21    | SA10        |

| IRQ6      | B22 | A22    | SA9         |

| IRQ5      | B23 | A23    | SA8         |

| IRQ4      | B24 | A24    | SA7         |

| IRQ3      | B25 | A25    | SA6         |

| -DACK2    | B26 | A26    | SA5         |

| T/C       | B27 | A27    | SA4         |

| BALE      | B28 | A28    | SA3         |

| +5v       | B29 | A29    | SA2         |

| OSC       | B30 | A30    | SA1         |

| GND       | B31 | A31    | SAO         |

|           | +-  | t      |             |

## System Clock Modulation

There are four time-critical operations in IBM PC/AT-compatible machines. These operations are system board, DRAM accesses, system board ROM accesses, expansion memory accesses and expansion bus I/O operations.

In systems running over 8 MHz, the 286 LX supports 10 and 12 MHz speeds. The expansion bus compatible with peripherals are designed to run at a maximum of 8MHz.

A single 20-pin PAL16R6(12ns) has been developed that performs the function of clock modulation with the VL82CPCAT chip set for solving the problems with a high speed slot bus.

## **PAL Description**

Figure 5 shows the pin description for the PAL16R6 that, along with an oscillator, will modulate the system clock during all I/O and off-board memory cycles to either one-half or two-thirds of its normal frequency. In a 12MHz application, the PAL is clocked with a 48MHz oscillator and normally generates a 24-MHz clock which is used to drive the XTAL2(2) input (pin 84) of the VL82C101 (XTAL2(1) is left unconnected). The PAL samples the CPU status lines (S0, S1 and M/IO) and the F16 output of the VL82C102 just prior to the second phase 1 of PROCCLK in the status cycle (when

ALE is due to come out). If an I/O or off-board memory cycle is detected, the PAL outputs either 16MHz or 12Mhz clocks until the end of the cycle.

Table 8 shows the effect of clock modulation down to 6 or 8MHz in a 12MHz system. Because the decision as to the speed of the cycle is made before ALE is generated, it can be seen that many problem areas are covered. It should be noted here that clock modulation only lengthens the ALE pulse width in the case that the operation is detected as an I/O cycle or an off-board memory cycle.

The clock modulation PAL appears to provide an effective way to make a 12 MHz AT-compatible system that is truly compatible on the expansion bus.

Figure 5 Pin Description for Clock Modulation PAL

PAL16R6(Note)

|        | +     | +  |          |          |

|--------|-------|----|----------|----------|

| 48MHz  | -  1  | 20 | - VCC    |          |

| -BY3   | -   2 | 19 | - CPUHLD | A        |

| -S0    | -   3 | 19 | - XTAL   |          |

| -S1    | -   4 | 17 | - SPEED  | HIGH LED |

| MIO    | -  5  | 16 | HLD      |          |

| F16    | -  6  | 15 | Q2       | case of  |

| -READY | -17   | 14 | SLOW     | Sennos   |

| -REF   | -   8 | 13 | - NC     |          |

| -EN    | -   9 | 12 | - SYSCLK |          |

| GND -  | - 10  | 11 | - OE     |          |

|        | +     | +  |          |          |

**NOTE:** Must be a 12ns PAL or equivalent for 12 MHz operation.

## Other Considerations

## Basic I/O System

Several commercially available clones of the IBM BIOS have been successfully tried and all have been found to work properly.

With the exception of the keyboard controller, there is no hardware dependency between the BIOS and the VL82CPCAT chip set. In the case of the keyboard controller (8742), the RAMSEL0 line is connected to it, but regardless of the jumper configuration, the system always boots and configures itself for the actual available memory.

Table 8 Duration of I/O and Memory Cycles for Various System Configurations (Note)

| mora/reibes/tators/n            | 8 MHz AT-Type                  | 286 LX                 |

|---------------------------------|--------------------------------|------------------------|

| On-board I/O<br>( 8 to 8 bit)   | simpatible 6 feb 183           | 606/8MHz               |

| Off-board I/O<br>(8 to 8 bit)   | 6                              | 606/8 MHz              |

| OII-board 1/0                   | Dai-bar                        | 12@6/* Mhz             |

| Off-board I/O<br>(16 to 16 bit) | 6<br>(3 if IOCS16<br>is used)  | 6 or 3<br>@ 6/8 MHz    |

| On-board DRAM                   | Ms. this leaves pro            | 3 (2 if 0 wait states) |

| On-board ROM                    | an R2CS Progra                 | 3 (4 if 2 wait states) |

| Off-board Memory (8 b           | it) 6                          | 606/8 MHz              |

| Off-board Memory<br>(16 bit)    | 6<br>(3 if MEMCS16<br>is used) | 6 or 3<br>@6/8MHz      |

**Note:** All values in System Clocks are at the maximum system frequency, unless otherwise noted.

# TECHNICAL INFORMATION

# Features of the VL82C100/82C101/82C102/82C103/82C104 PC/AT compatible Chip set

- . Fully compatible with IBM PC/AT-type designs

- . High-integration five-chip set

- . Reduces non-memory system device count from 110 to 16

8

- Supports 12 MHz processor clock

- . Devices are available as "cores" for user-specific designs

- . All devices designed in CMOS for low power consumption

# 82C100 PC-AT Peripheral Controller

The VL82C100 PC/AT Peripheral Controller replaces two 82C37A Direct Memory Access Controllers, two 82C59A Interrupt Controllers, an 82C54 Programmable Counter, a 74LS612 AT Memory Mapper, two 74LS573 octal three-state latches, a 74LS138 3-to-8 Decoder, and five other less-complex integrated circuits. Using this internal functionality, the VL82C100 interfaces the keyboard controllers as well as the real-time clock to the PC/AT system.

The device also supplies control signals to the I/O slots, the VL82C101 System Controller as well as the system ROMs.

The device is manufactured with VLSI's advanced high-performance CMOS process and is available in a JEDEC-standard 84-pin plastic leaded chip carrier (PLCC) package. The VL82C100 is individually available, or may be purchased as part of the complete five-device VL82C(PA/AT) kit.

## 82C101 PC/AT System Controller

The VL82C101 PC/AT system Controller replaces an 82C284 clock controller and 82C288 Bus Controller (both are used in 286-based systems), an 82C84A Clock Generator and Driver, two PAL16L8 devices (used for memory decode), and approximately ten other less-complex integrated circuits used as Wait State logic. When used in 12 MHz systems utilizing 80ns DRAMs, the device provides the required one wait state for a "write" operation. a 12MHz system using 120ns DRAMs will be provided.

with one wait state for "write" and one wait state for a "read". The device accepts both the 24MHz crystal to control the system clock as well as the 14.318MHz crystal to control the microprocessor clock. It also supplies reset and clock signals to the I/O slots.

The device is manufactured with VLSI's advanced high-performant CMOS process and is available in a JEDEC-standard 4-pin plastic leaded chip carrier (PLCC) package. The VL82C101 is individually available, or may be purchased as part of the complete five-device IBM-PC/AT kit.

## 82C102 PC/AT Memory Controller

The VL82C102 PC/AT Memory Controller generates the row address strobe (RAS) and column address strobe (CAS) necessary to support the dynamic RAMs used in the PC/AT. In addition, the device allows four motherboard memory options for the user, up to a full 2M-byte system. Three of the four options allow a full 640K-bytes user area to support the disk operating system (DOS). In addition, the VL82C102 provides the upper addresses to the I/O slots, the chip select for the ROM and RAM memory, and drives the system's speaker.

The device is manufactured with VLSI's advanced high-performance CMOS process and is available in a JEDEC-standard 84-pin plastic leaded chip carrier (PLCC) package. The VL82C102 is individually available, or may be purchased as part of the complete five-device VL82C(PC/AT) kit.

## 82C103 PC/AT Address Buffer

tic

The VL82C103 PC/AT Address Buffer provides the system with a 16-bit address bus input and 41 buffered drivers. The buffered drivers consist of 17 bidirectional system bus drivers each capable of sinking 20mA (50 'LS loads) of current and 200 picofarads of capacitance on the backplane; 16 bidirectional local bus drivers, each capable of sinking 8mA (20 'LS loads) of current; and eight memory bus drivers, also capable of sinking 8mA of current on-chip refresh circuitry supports both 256K-bit and 1M bit DRAMs. The VL82C103 provides addressing for the I/O slots as well as the system.

The device is manufactured with VLSI's advanced high-performance CMOS process and is available in a JEDEC-standard 84-pin plastic leaded chip carrier (PLCC) package. The VL82C103 is individually available, or may be purchased as part of the complete five-device VL82(PC/AT) kit.

## 82C104 PC/AT Data Buffer

The VL82C104 PC/AT Data Buffer provides 16-bit data bus input as well as 40 buffered drivers. The buffered drivers consists of 16 bidirectional system data bus drivers, each capable of sinking 20mA (50 'LS loads) of current; eight bidirectional local bus drivers, each capable of sinking 8Ma (20 'LS loads) of current. The VL82C104 also generates the parity error signal for the system.

The device is manufactured with VLSI's advanced high-performance CMOS process and is available in a JEDEC-standard 84-pin plastic leaded chip carrier (PLCC) package. The VL82C104 is individually available, or may be purchased as part of the complete five-device VL82(PC/AT) kit.

#### RECOMMENDED REFERENCES

#### Hardware

Information is available for each of the devices included in the AT baby board from Intel and other semiconductor companies. Sources are shown below:

### Intel:

1985 Component Data Book 80286 Data Sheet iAPX 286 Hardware Reference Manual

#### IBM:

Guide to Operations - Personal Computer AT Installation Setup Personal Computer AT Technical Reference Manual

## Software

Intel:

iAPX 286 Programmer's Reference Manual iAPX 286 Operating System Writer's Guide

IBM:

PC-DOS 3.1 Reference Manual

## CMOS Clock/RAM

The internal clock circuitry uses 14 bytes of the 64-byte CMOS RAM, and the rest are used for configuration information. The CMOS RAM addresses are:

## 286 LX Series System

## Table 9 CMOS RAM Addresses

| Address | Description                     |

|---------|---------------------------------|

| 00-0D   | Real-time clock information     |

| 0E      | Diagnostic status byte          |

| OF      | Shutdown status byte            |

| 10      | Diskette drives A and B type    |

| 11      | Reserved                        |

| 12      | Hard Disk type-drives C and D   |

| 13      | Reserved and what TA sit bas TA |

| 14      | Equipment byte                  |

| 15      | Low base memory byte            |

| 16      | High base memory byte           |

| 17      | Low expansion memory byte       |

| 18      | High expansion memory byte      |

| 19-2D   | Reserved                        |

| 2E-2F   | 2-byte checksum                 |

| 30      | 0 Low expansion memory byte     |

| 31      | 0 High expansion memory byte    |

| 32      | 0 Data century byte             |

| 33      | 0 Information flags             |

|         | (set during power on)           |

| 34-3F   | Reserved by IBM                 |

|         |                                 |

## HARDWARE COMPATIBILITY

This chapter shows the difference between the AT compatible computers, such as the AT baby board, and the rest of the IBM Personal Computer family. It also contains information on what expansion cards will be compatible with the AT baby board or any AT class machine.

The following are hardware features of the IBM Personal Computer AT and the AT baby board that are not supported by the rest of the IBM Personal Computer family:

- The AT baby board uses an Intel 80286 microprocessor.

Programming considerations due to faster processing capability of the 80286 require programs to be written without loops or routines which are dependent on execution speed by the CPU. This is usually no problem, since this is just good programming practice.

- The expansion slots have a 36-pin connector in addition to the 62-pin connector. Adapters designed to make use of the 36-pin connector are not compatible with other machines with only the 62-pin connector.

- 3. The I/O channel is different.

- The system clock signal should only be used for synchronization and not for applications requiring a fixed frequency.

- The 14.31818 MHz oscillator is not synchronous with the system clock.

- c. "ALE" is active during DMA cycles.

- d. The I/O write signal is not active during refresh cycles.

Figure 6 Block Diagram of the 286 LX-A

Figure 7 Block Diagram of the 286 LX-M

## Notes:

# **Table of Contents**

| STARTING UP THE SYSTEM            | 1  |

|-----------------------------------|----|

| MEMORY TEST BYPASS                | 1  |

| SELECT THE SETUP OR DIAGS OPTION  | 2  |

| CMOS SETUP (for AMI)              | 3  |

| Time/Date Setup                   | 3  |

| CMOS Initialized                  | 4  |

| CMOS Uninitialized                | 5  |

| Disk Drive Type Definition        | 5  |

| Floppy Drive Type Definition      | 6  |

| SUMMARY OF SET-UP                 | 8  |

| When does The SYSTEM Prompt You   |    |

| to Run Set-up?                    | 9  |

| Errors Reported By SYSTEM         | 9  |

| Fatal Errors                      | 10 |

| Error Messages                    | 11 |

| USE OF 3 1/2" SUPPORT EFFECTIVELY | 12 |

13 13 14

| DIAGNOSTICS                                              |      |

|----------------------------------------------------------|------|

| Diagnostics                                              | 13   |

| Diagnostics Menu                                         | 13   |

| 1                                                        | 1.4  |

| Diagnostics Options Window                               | 14   |

| nard bisk Diagnostics                                    | 15   |

| osing Hard Disk Options                                  | - 15 |

| naid Disk Format Option -                                |      |

| (Destructive Operation)                                  | - 17 |

| Drive Type Definition                                    | - 17 |

| Interleave Factor                                        | - 18 |

| Mark Bad Tracks                                          | 18   |

| Cylinder Number                                          | 19   |

| Proceed                                                  |      |

| Warning                                                  | 19   |

| Activity Screen                                          |      |

| Auto Interleave Option -                                 | 20   |

| (destructive Operation)                                  |      |

| Media Analysis Option -                                  | 20   |

| (Destructive Operation)                                  |      |

| Performance Test -                                       | 21   |

|                                                          |      |

| (Non-Destructive Operation) Seek Test - (Non-Destructive | 22   |

| Operation)                                               |      |

| Read/Verify Test -                                       | 22   |

| (Non Doots                                               |      |

| (Non-Destructive Operation) Force Bad Tracks -           | 23   |

|                                                          |      |

| (Destructive Operation)                                  | 23   |

| Floppy Diagnostics                                       | 23   |

| Diskette Format - (Destructive)                          | 24   |

| Drive Speed Test - Man Man                 |    |

|--------------------------------------------|----|

| (Non-Destructive)                          | 25 |

| Random Read/Write Test -                   |    |

| (Destructive)                              | 25 |

| Sequential Read/Write Test -               |    |

| (Destructive)                              | 26 |

| Disk Change Line Test -                    |    |

| (Non-Destructive)                          | 26 |

| Keyboard Diagnostics                       | 27 |

| Controller Test                            | 27 |

| Scan/ASCII Code Test                       | 28 |

| Video Diagnostics                          | 28 |

| Miscellaneous Diagnostics                  | 29 |

| Serial Communication Port Test             | 29 |

| Printer Port Test                          | 30 |

| APPENDIX A: INTERLEAVE FACTOR -WHAT IS IT? | 31 |

| APPENDIX B & FIGURES: HARD DISK TYPE       | 34 |

# 286 LX Series System

| THE | MAIN BOARD CONNECTORS, JUMPERS AND SWITCHES | 1   |

|-----|---------------------------------------------|-----|

|     | The Jumpers, Connectors and Switches        |     |

|     | in 286 LX-A                                 | 17  |

|     | J18 (Keylock/Power LED)                     | 15  |

|     | J19 and J20 (Power Connectors)              | 28  |

|     | J22 (External Battery Connector) -          | 21  |

|     | J23 (Speaker Connector)                     | 22  |

|     | J25 (Keyboard Connector)                    | 22  |

|     | J29 (Hardware Reset Switch)                 | 23  |

|     | J103 (Turbo Indicator Connector)            | 23  |

|     | J104 (Hardware Speed Switch)                | 23  |

|     | J1 (Select EPROM Size)                      | 24  |

|     | UIO (DRAM Access Timing)                    | 24  |

|     | J28 (Select Backup Battery)                 | 24  |

|     | J30 (Select FASTMODE or NORMAL)             | 25  |

|     | J31 (Select One or Zero Wait State)         | 25  |

|     | J102 (Select Oscillator)                    | 25  |

|     | SW1,2,3 (Select RAM Size)                   | 26  |

|     | SW4 (Color Enable)                          | 26  |

|     | The Jumpers, Connectors and Switches        |     |

|     | In 286 LX-M                                 | 27  |

|     | J1 (POWER Connector)                        | 28  |

|     | J2 (Keyboard Connector)                     | 29  |

|     | (External Battery Connector)                | 30  |

|     | J19 and J20 (Hardware Speed                 |     |

|     | and Hardware Reset Switch)                  | 5U  |

|     | (Speaker Connector)                         | 2+  |

|     | J22 (Keylock/Power LED)                     | 3.1 |

|     | JP10 (Turbo Indicator Connector)            | 32  |

|     | (Select Backup Battery)                     | 32  |

|     | 1 COLOCT LASTHODE OF MONTAL                 | 33  |

|     | JP2 (Select Oscillator)                     | 22  |

|     | JP3 (Select One or Zero Wait State)         | 13  |

|     | UFD (DRAM Access Timing)                    | 34  |

|     | (Select EPROM Size)                         | 34  |

|     | JP7,8,9 (Speed Control Mode)                | 77  |

## 286 LX Series System

| SW1,2,3 (Select RAM Size)                 | 35 |

|-------------------------------------------|----|

| SW4 (Color Enable)                        | 35 |

| USING SETUP                               | 36 |

| I/O CHANNEL DEFINITIONS                   | 37 |

| System Clock Modulation                   | 41 |

| PAL Description                           | 41 |

| Other Considerations                      | 44 |

| Basic I/O System                          | 44 |

| TECHNICAL INFORMATION                     | 46 |

| Features of the VL82C100/82C101/82C102/   |    |

| 82C103/82C104 PC/AT compatible Chip set - | 46 |

| 82C100 PC-AT Peripheral Controller        | 46 |

| 82C101 PC/AT System Controller            | 47 |

| 82C102 PC/AT Memory Controller            | 48 |

| 82C103 PC/AT Address Buffer               | 49 |

| 82C104 PC/AT Data Buffer                  | 50 |

| RECOMMENDED REFERENCES                    | 51 |

| Hardware                                  | 51 |

| Software                                  | 52 |

| CMOS Clock/RAM                            | 52 |

| HARDWARE COMPATIBILITY                    | 54 |

## SELECT THE SETUP OR DIAGS OPTION

Immediately after the memory and cache test, you will get the following prompt on the screen:

Press < DEL > key to run SETUP or DIAGS

Hit <DEL> key to get into the Setup Mode. Note that <DEL> key will get you into the set-up mode only when the message: Press <DEL> key to run SETUP or DIAGS, is displayed on the screen.

If you hit <DEL> key to the following message appears on the screen:

## WANT TO RUN SETUP OR DIAGS (Y/N)?

If you answer < Y > or <y> followed by <ENTER > then you would be asked to select either Setup or Diagnostics as shown below:

SETUP or DIAG (1/2)?

Hit <1> to use the built-in SETUP option

Hit <2> to use the Advanced Diagnostics option.

## CMOS SETUP (for AMI)

## Time/Date Setup

The Setup screen looks like below:

C M O S S E T U P

Curret date is: XX-XX-XXXX

Enter new date (MM-DD-YYYY)?

To this question you would have to enter the date in the format shown on the screen.

If you feel that the current date should remain unchanged, you would just have to hit the <ENTER > key. In such a case the new date is set to the same value as the current date.

The next question you have on the screen is:

Current time is: XX:XX:XX Enter new time (HH:MM:SS)?

To this question you key in the time in the format defined Press <ENTER> key alone if the current time is right.

As soon as you have done this the systme shows you the type of the display on your system.

#### **PROCCLK**

This is a 2X clock provided to the processor. In a 12Mhz system, this will be a 24MHz clock.

#### SYSCLK

This is the clock that corresponds to the actual 80286 execution. In a 12MHz system, this will be 12MHz.

#### **FASTMODE**

This mode allows for certain timing signals (RAMALE and RAS) to be generated earlier in a memory cycle than would have been by IBM-compatible logic. This option is required to allow no-wait state operation at 12 MHz.

## RAMALE

This signal is an output of the VL82C101 that is used to allow CPU addresses to reach DRAMs earlier when FASTMODE is active. If FASTMODE is inactive, RAMALE behaves exactly like ALE in the IBM design. If FASTMODE is active, RAMALE will stay high, causing the memory address latches to be transparent whenever a memory read or write command is not taking place. If either command becomes active, RAMALE goes low latching the current address that is on the CPU address lines. This function of RAMALE makes memory addresses valid as soon as they propagate from the CPU

#### 286 LX Series System

through the open latches instead of having to wait for ALE to go high.

RAS

When FASTMODE is inactive, this signal behaves as in the IBM design. When FASTMODE is enabled, RAS will go high one PROCCLK cycle before a memory read command.

#### **ENDRAS**

This is an output of the VL82C101 that allows sufficient RAS pre-charge time for the DRAMs between fast memory accesses. ENDRAS will normally go low three PROCCLK cycles after RAS goes high. ENDRAS will not return high until a minimum of 3ns after RAS returns low to avoid a spike on MEMRAS. Using fast memory timing with zero wait state DRAM accesses selected, ENDRAS will go low two PROCCLK cycles after RAS goes high.

## **MEMRAS**

This signal is the logical NAND of RAS and ENDRAS. It is performed in logic that is external to the 82C100 chip set, and directly drives the RAS inputs of the memory array.

Your would then be asked to enter the type of the disk Drive D. The procedure for doing this is the same as that for Drive C. Remember if you do not have disk Drive D on your system. you just have to hit the <ENTER > key.

## Floppy Drive Type Definition

Diskette drive A is 3 1/2" (Y/N)?

The above question is asked if the drive has been found to have 80 tracks. Since a drive with 80 tracks could either be a

- high capacity i.e. 1.2 MB drive

- or 3 1/2" i.e. 720 KB drive,

you would have to answer this question.

By entering <N> or <n> you can select the high capacity drive.

Alternatively enter < Y > or <y > to select a 720 KB drive. This question could come up for the case of drive B as well provided it has been detected as a 80 track drive by the System.

If you hit the <ENTER> key alone, the SYSTEM assumes the drive to be a 1.2 MB drive.

At this point you have entered all the information the SYSTEM requires for starting up the system.

At this point you have entered all the information the SYSTEM requires for starting up the system.

SYSTEM detects a few details by itself, e.g. the diskeete drive type in case of a 360KB drive as shown below:

Diskette drive B is: Double Sided (Other option as above)

Base Memory Size is.: XXX KB

Expansion memory size is :XXXX KB

Are these options correct (Y/N)?

If you are convinced at this stage that all the information you have entered upto this point is right, hit < Y > or <y> key followed by <ENTER> key. When you do this the SYSTEM goes all over again to boot up the system with the information specified.

However, if you would like to modify some information, then you should hit either < N > or < n > key followed by Enter. You would now go through the setup all over again.

### 286 LX Series System

## The Main Board Components for 286 LX-A and 286 LX-M Systems

- AMD 80286 microprocessor

- . 80287 math coprocessor socket

- . Onboard memory socket for up to 4MB in 256K/1M step

- . 128K/256K ROM selection

- . Real-time clock with built-in rechargeable battery

- 8 expansion slots (6 dual 62/36-pin card-edge connectors and 2 62-pin card-edge connectors)

- 4-pin oscillator socket is provided for the optional 20MHz system clock

### General Description

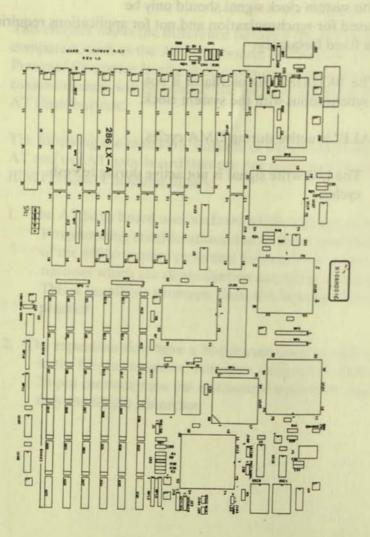

### **Block Diagram**

The block diagram of the 286 LX baby board is shown in Figure 1.

Figure 1 Block Diagram of the 286 LX Baby Board

### **Fatal Errors**

## Beep Count Meaning

- 1 DRAM refresh failure.

- 2 Parity Circuit failure.

- 3 Base 64KB RAM failure.

- 4 System Timer failure.

- 5 Processor Failure

- 6 Keyboard Controller Gate A20 error.

- 7 Virtual Mode Exception Error.

- 8 Display Memory R/W Test Failure. (\*)

- 9 ROM-BIOS CheckSum Failure.

<sup>(\*)</sup> Non-Fatal Error.

### **Error Messages**

## Fatal Errors

- 1. Channel -2 of Timer Not functional.

- 2. Stray Interrupt sensed in controller.

- 3. Interrupt controller #2 not functional.

### Non-Fatal Errors

- 1. Keyboard Error.

- 2. Keyboard/Interface Error.

- 3. CMOS battery state low.

- 4. CMOS system options not set.

- 5. CMOS checksum failure.

- 6. CMOS memory size mismatch.

- 7. CMOS system time and date not set.

- 8. CMOS display configuration mismatch.

- 9. Display setting not proper.

- 10. Keyboard is locked .... Unlock it.

- 11. Floppy disk controller failure.

- 12. Hard disk unit 0 error.

- 13. Hard disk unit 1 error.

- 14. Hard disk unit 0 failure.

- 15. Hard disk unit 1 failure.

- 16. Hard disk unit 1 is not defined in CMOS.

- 17. Cache Memory Bad Do Not Enable Cache.

## System Expansion Bus

The 286 LX provides drive for up to 8 XT compatible cards (6 of which can be AT compatible with the second connector). The busis directly driven by the CMOS chips of the VL82CPCAT family, and can have to 50 LSTTL loads (DC drive capability = 20 mA) and 200pF. The 200pF is the practical limitation to systems since a conservative rule of thumb is that PC compatible cards rarely exceed 25 pF per pin. The 200 pF limitation allows for all 8 slots to be populated and not violate any of the drive specifications. For expansion bus 8-bit accesses, 4 wait states are automatically added in, thus making reads and writes into 6-cycle operations.

int

### Timers

The VL82C100 chips contains an 82C54 timer which provides three programmable timers, each being driven with 1.19MHz. The timers provide for the following:

## Timer Usage

- O Directly drives IRQ to provide a periodic tick to the operating system.

- Provides a refresh request to the DRAM control circuit. Normally set to a value of 12H, this timer generates a refresh request every 15us.

- 2 Provides the speaker output frequency.

### Interrupt Controllers

The VL82C100 includes two 82C59A Programmable Interrupt Controllers that control interrupts to the 80286 CPU. When an interrupt line is driven as a result of the state of a signal on the expansion bus, Table 1 lists the signal and the type of source (8-bit or 16-bit). The 8-bit slots are the 62-pin connectors and the 16-bit slots are the 36-pin expansion slots. Table 1 shows the interrupt line usage.

f) Note that the Block Cursor is on the Hard Disk & the first option under hard disk diagnostics - Hard Disk Format.

### **Key Conventions**

Use the Up & Down arrow keys to move within a Diagnostics Options Window.

Use the <ENTER> key to select the option in the Diagnostics Options Window.

Use <ESC> key to abort & return to previous menu.

## **Diagnostics Options Window**

The individual diagnostics option window is as below:

- a) Fig 1 for Hard Disk Options.

- b) fig 2 for Floppy Disk Drive Options.

- c) Fig 3 for Keyboard Options.

- d) Fig 4 for Video Options.

- e) Fig 5 for Miscellaneous Options.

### Hard Disk Diagnostics

### **Using Hard Disk Options**

The Hard Disk options discussed below fall in -two categories:

- a) Destructive Operation The data on the Hard

Disk is lost

- Non-destructive Operation The data on the Hard Disk is undisturbed.

The list below gives the various Hard Disk Options & the category they fall in:

- a) Hard Disk Format -- Destructive Operation.

- b) Auto Interleave -- Destructive Operation.

- c) Media Analysis -- Destructive Operation.

- d) Performance Test -- Non-destructive

Operation.

e) Seek Test -- Non-destructive

Operation.

f) Read/Verify Test -- Non-destructive

Operation.

g) Check Test Cylinder -- Data on the Test

Cylinder alone is 'ost.

### System Cycle Times

A summary of the system cycle times for various operations is shown in Table 3. The times to perform these operations are stated in both CPU cycles and actual time for a 12Mhz system. For DMA cycles, n equals the number of bytes or words that are being transferred. Thus, a DMA cycle to read one 16-bit word from off board will take 83.3\* (22+8\*(1-1))ns = 1883ns.

(p)

16

Re

R

Table 3 System Cycle Times

| peration                | CPU Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Time (ns)               |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Exter the Shirt A       | (12 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| 16-bit Operations       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Read, 0 wait states(*)  | ) 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 167                     |