2. Pressing toroidal shapes

3. Weight and dimensional quality control of unfired cores using an electro balance accurate to 10 micrograms

4. Cores are fired in kilns at temperatures ranging from 800°F, to 2300°F,

5. Cores are cleaned, sized and tested . . . a continuous quality control program is in effect.

precise, controlled manufacturing techniques

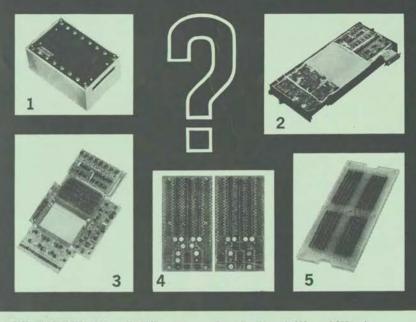

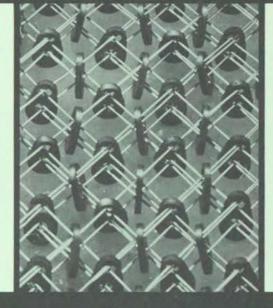

6. Finished, tested ferrite cores are assembled into matrices

7. A continuous program of design and development work utilizes ferrite cores in memory systems

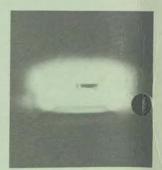

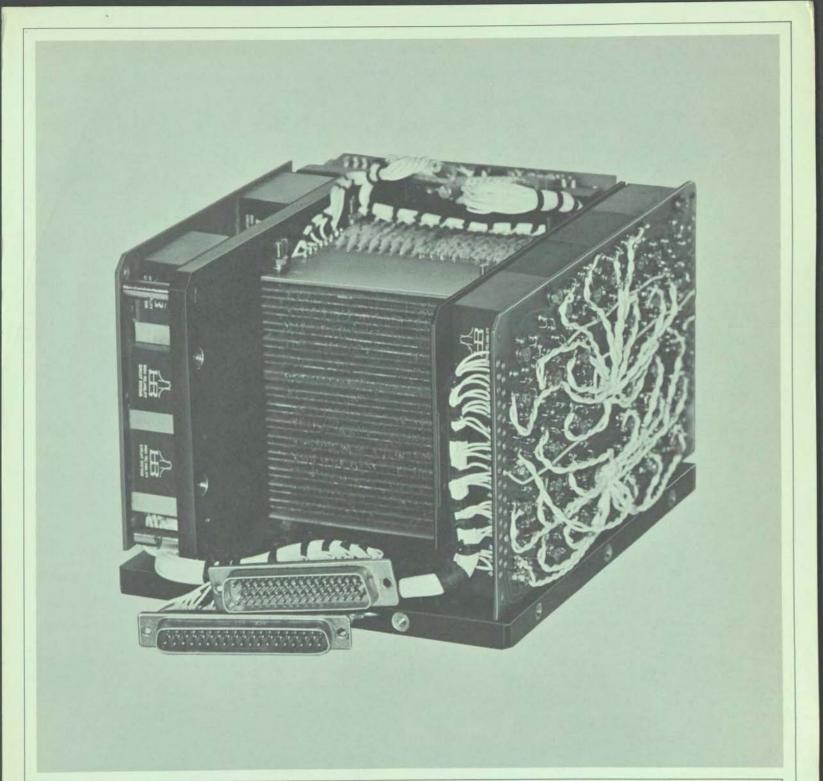

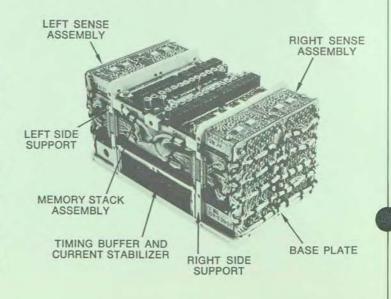

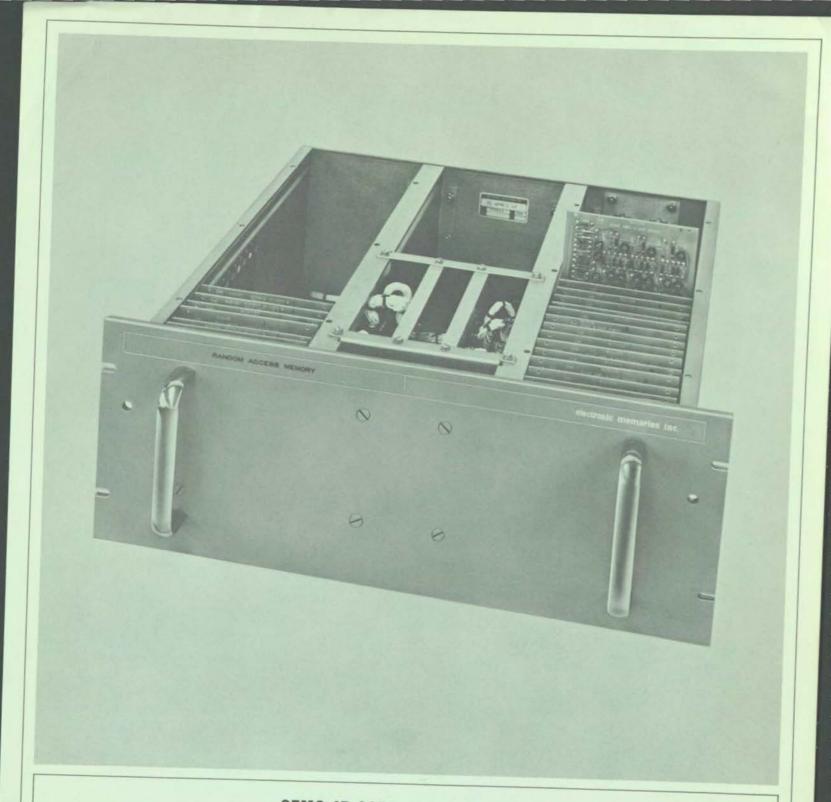

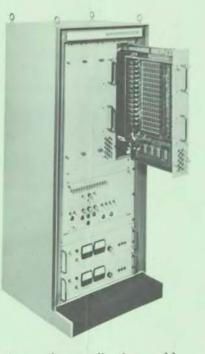

8. A finished product . . . ISODRIVE® Memory Model RE1440Z1

# electronic memories inc.

001 -1 63

### THE COMPANY AND ITS PURPOSE

Electronic Memories, Inc. was formed in June 1961 to develop, manufacture and market electronic and magnetic memory products. The company objective is to fill the increasing need for memory devices in the data processing industry, the communications field, guidance and control systems for the missile industry, communications and control systems for space vehicles and in the broad field of automation.

Electronic Memories, Inc. has designed and produced satellite core memory systems for Applied Physics Laboratories, General Electric Company, Goodyear Aircraft Corporation, Jet Propulsion Laboratory, Space Technology Laboratories, Burroughs Corporation, Aeronutronic, Librascope, and other leading scientific organizations.

Management at Electronic Memories is committed to a program of continuing state-of-the-art developments in cores, arrays, stacks and memory systems. A continuous effort, consistent with the company growth and funds available for research and development purposes, is being carried on in the area of more advanced memory elements and techniques.

### PRODUCTS

*Cores:* The standard ferrite core product line is composed of 30, 50, 80, 140 and 180 mil sizes which have characteristics and specifications in general use throughout the data processing industry.

Electronic Memories has developed and is manufacturing two special types of ferrite cores which represent advances in the state-of-the-art:

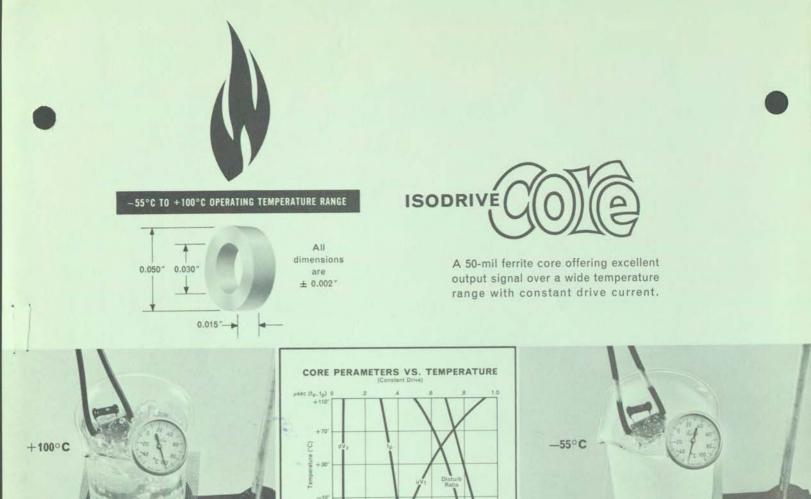

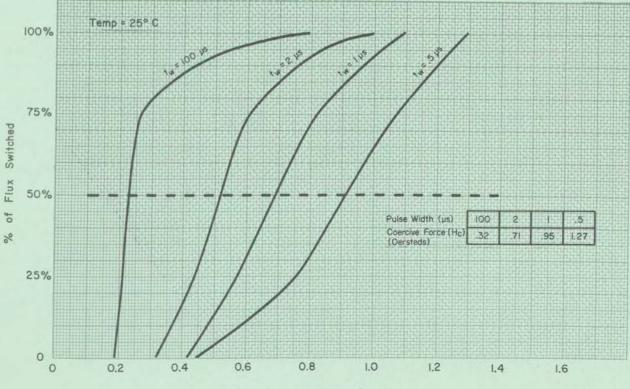

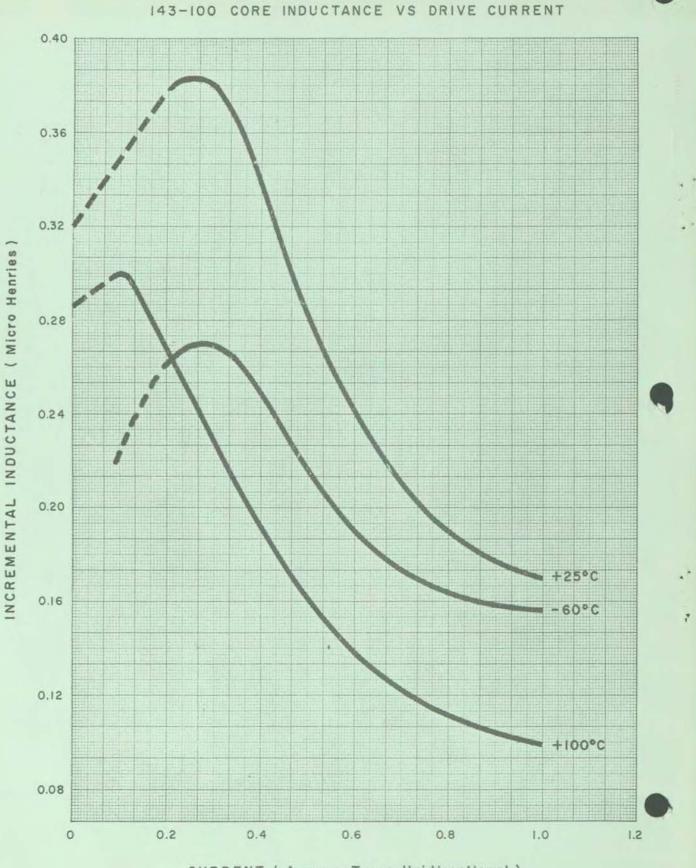

(1) The ISODRIVE core, available in 30, 40 and 50 mil sizes, eliminates the need for either current compensation or oven enclosures when designing memories which must operate over a large temperature excursion; specifically,  $-55^{\circ}$ Centigrade to  $+100^{\circ}$ Centigrade. In addition, the ISODRIVE core yields a high output in millivolts on turnover and has a better disturb ratio, (knee current/full drive current) over the entire temperature range than standard cores have at room temperature. Development of 30 mil ISODRIVE cores for use in memories having cycle times of 1 microsecond and less is being carried on.

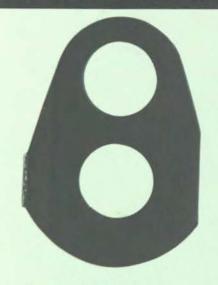

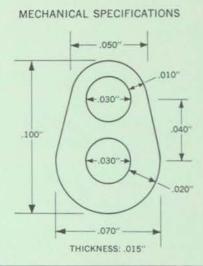

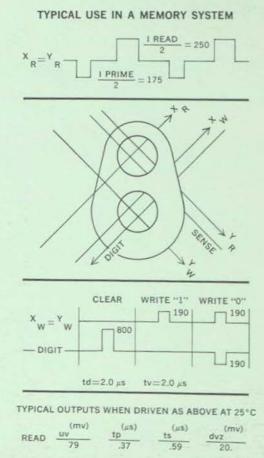

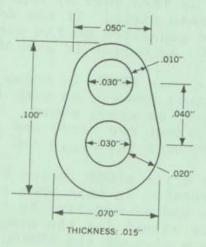

(2) EMI has developed a two-hole "shmoo" shaped transfluxor, which allows the first practical application of a transfluxor in a coincident current nondestructive memory. The "shmoo" shape gives excellent electrical characteristics, such that in the saturated state for Read or Write the unsaturated area of the transfluxor is very small. The physical and electrical characteristics of the Read hole of the transfluxor can be matched with those of a standard 50 mil toroid, allowing a design of a non-destructive coincident current memory and a destructive read "scratch pad" memory using the same drive circuitry design. The transfluxor has been successfully tested in coincident current operation over a temperature range of 0°C to +70°C with compensated drive currents.

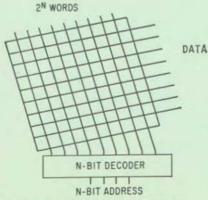

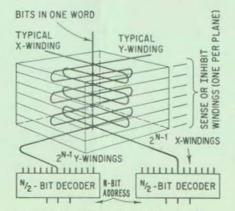

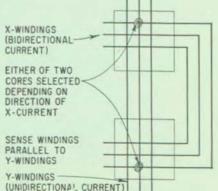

Arrays and Stacks: Electronic Memories provides cores on standard matrices for standard stack configurations, or designed and manufactured for special customer requirements. Standard stacks are completely wired to connectors for the interface and come complete with mounting brackets. Stacks are available in both 50 mil and 30 mil core sizes. With the fast-switching EMI 30 mil cores, cycle times to less than 2 microseconds are achievable in a coincident current system. Among the special designs available are heated stacks for both commercial and adverse environment applications and non-destructive readout stacks incorporating the EMI "shmoo" in a coincident current configuration. For the memory design engineer, EMI has a supply of arrays in stock incorporating our standard cores. The arrays are available on loan so that driving and sensing circuits can be checked out before production quantities are ordered.

*Memories:* The forward steps in ferrite core development described above have given Electronic Memories, Inc. the ability to design and develop unique memory products offering substantially improved operating characteristics to the customer. Two important memory systems have already been developed for the customer who faces severe environmental conditions in his applications:

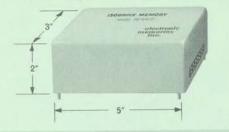

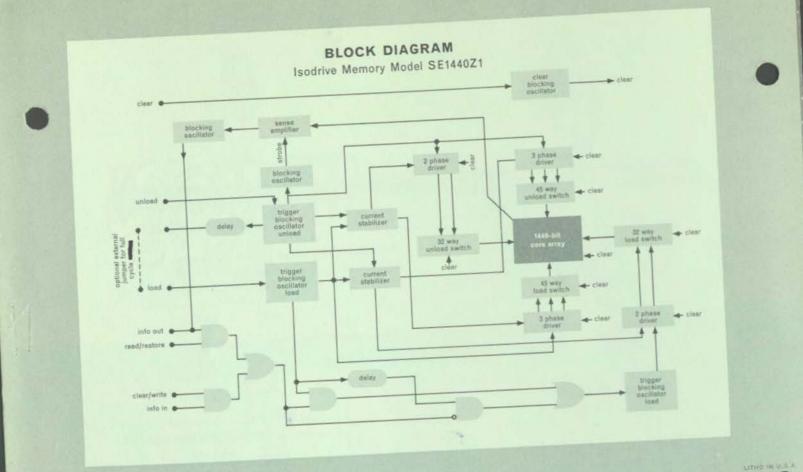

(1) The ISODRIVE MEMORY Model No. SE1440Z1 is a MIL-SPEC bit serial core memory which can perform in space vehicles as a communication buffer, time interval programmer, function control programmer, computer program memory, computer working memory, or as a set of core logic nets. This ISODRIVE MEMORY operates over a temperature range of -30°C to +90°C, weighs less than 16 ounces, occupies a volume of less than 30 cubic inches, has a storage capacity of 1440 bits, and an

operating speed of 100 Kilocycles. The unit is designed to use the minimum number of semiconductors and maximum core logic and core switching. The SE1440Z1 ISODRIVE MEMORY has been designed using MILapproved components, finishes, fabrication standards and quality controls. Memories having capacities of 8000 and 30,000 bits are also available.

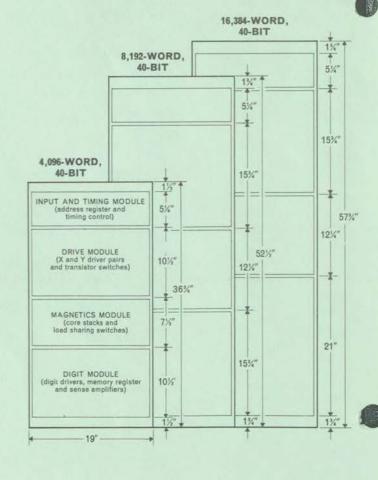

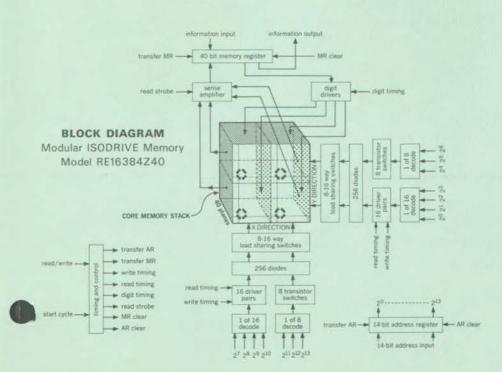

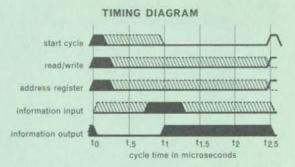

(2) The modular ISODRIVE MEMORY RE4096Z40 designed to meet MIL-SPECS is a medium sized, high speed random access memory. The memory uses coincident current techniques with the ISODRIVE core and has a cycle time of 2.5 microseconds. The memory construction is modular to allow word sizes of 4096, 8192 and 16,384 words with a bit length from 8 bits to 80 bits. The signal levels for both input and output allow for a reasonable range of signal amplitudes. The RE4096Z40 will operate over a temperature range of -30°C to +80°C. The memory has been designed for minimum power consistent with the 2.5 microsecond cycle time. The physical package is designed to give maximum space utilization. Normal use of this ISODRIVE MEMORY will be in ship or ground-based equipment.

Electronic Memories has developed additional memory systems for the requirements of the adverse environment market as well as commercial systems for the data processing and computer field.

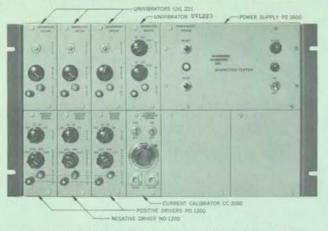

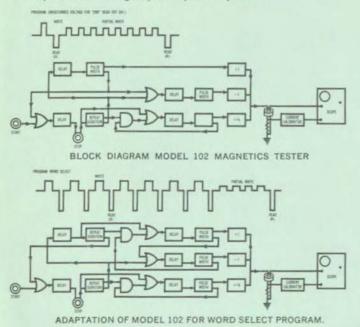

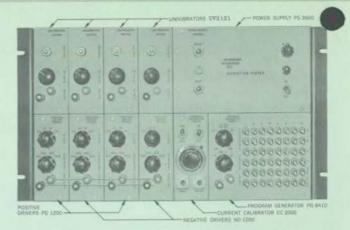

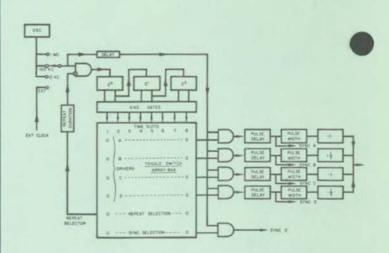

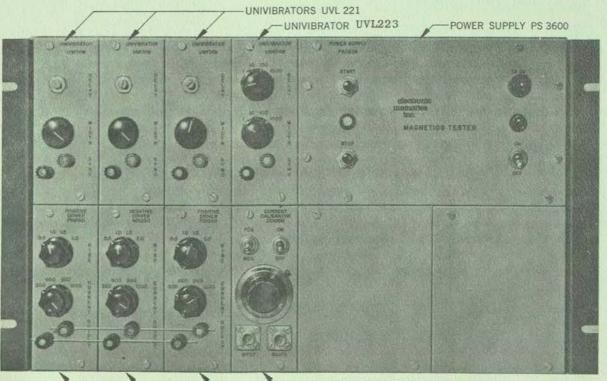

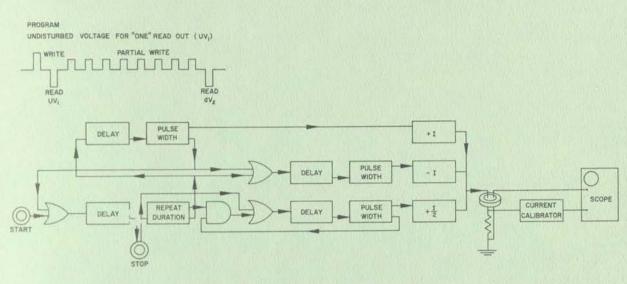

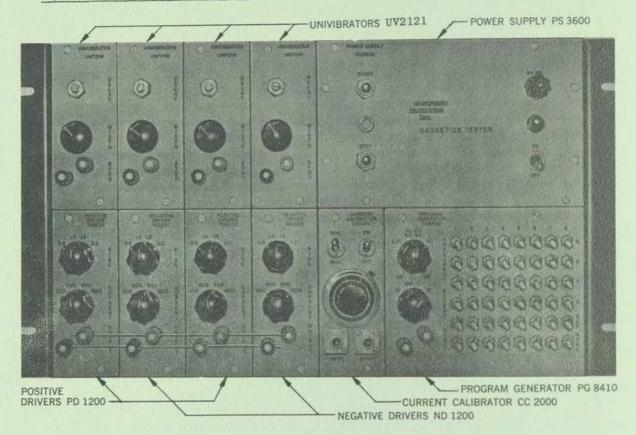

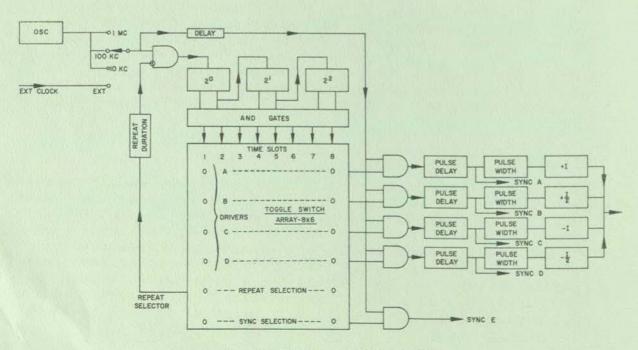

Programmed Magnetics Testers: A series of precise test instruments has been specifically designed for the testing and evaluation of magnetic cores and circuits. The testers are completely modular, allowing cost and test program flexibility.

### PLANT FACILITIES

Electronic Memories, Inc. is housed in a modern building located about 3⁄4 of a mile from the Los Angeles International Airport and 4 blocks from the Manchester Avenue exit of the San Diego freeway. The building has 10,000 square feet of floor space. The plant is well lighted and has an asphalt tile floor; it is efficiently laid out, allowing 2000 square feet for office space, 1000 square feet for Research, and 7000 square feet for Engineering and Production. The entire building is air cooled and the office space and production test equipment areas are air conditioned. An additional 40,000 square feet is being acquired for expansion of the production facilities.

### ENGINEERING

The engineering laboratories at Electronic Memories are well equipped consistent with over-all company size. In addition to the normal complement of oscilloscopes, meters, power supplies and signal generators, the Engineering laboratories contain approximately \$250,000 worth of equipment of special design required in testing and designing magnetic core memories. This equipment includes five magnetics testers used for studying and plotting curves of various core characteristics, three environmental chambers for testing and evaluating core parameters over the various necessary temperature ranges, and a core array tester designed and built by EMI personnel used for studying and evaluating magnetic core properties in arrays, core stacks, and special winding configurations.

### MANUFACTURING

Facilities presently exist in the Manufacturing Department for the production and test of:

ferrite square loop memory cores ferrite square loop switch cores ferrite linear cores core memory systems for space programs core memory systems for military programs core memory systems for commercial computers magnetics testers

Manufacturing facilities include a temperature-controlled and dust-free area for core and array test, three Ramsey high speed core handlers, two DEC core testers, one EMI core stack tester, one random-access memory exercisor and the conventional complement of oscilloscopes, magnetics pulse generators and equipment for the manufacture of cores, arrays and memory systems.

### PERSONNEL

Electronic Memories was founded and is managed by personnel with a unique depth and breadth of experience in the ferrite core, memory and computer industry. Each of these men has held key design, engineering, research, production and marketing management positions in these fields prior to associating with Electronic Memories. *This wealth of talent is our most valuable asset*.

### President: Trude C. Taylor

Mr. Taylor has worked in the computing and data processing industries since 1951, performing engineering, manufacturing, and marketing functions with Northrop, Telecomputing, Telemeter Magnetics, and Ampex Computer Products. Mr. Taylor is a graduate of University of California at Los Angeles (BSME) and the Harvard Graduate School of Business Administration (MBA).

Prior to forming Electronic Memories, Inc., Mr. Taylor was a Vice President and Director of Telemeter Magnetics, Inc. until that company was merged with Ampex Corporation in January 1961. Mr. Taylor joined Telemeter Magnetics as Vice President and Director of Marketing. He was later appointed Vice President and General Manager of the Data Equipment Division, which achieved an annual sales volume in excess of five million dollars.

After TMI's merger with Ampex Corporation, Mr. Taylor held the position

of Director of Marketing for the Ampex Computer Products Company, where he was responsible for the promotion, sales, service and product planning of the previous Telemeter Magnetics business plus other Ampex products being sold to the computer industry.

### Vice President, Engineering: Milton Rosenberg

Mr. Rosenberg, sole or co-inventor of more than twenty-five U.S. patents and author of numerous papers on core memory engineering techniques, brings to Electronic Memories, Inc. a significant reputation in the ferrite core and memory technology. Through effective use of electronics, magnetic and ceramic disciplines, he has made major contributions to the memory art.

As Manager of the Advanced Development Division of Ampex Computer Products Company (and the predecessor, Telemeter Magnetics, Inc.) from June 1959 to June 1961, he was responsible for the development, design and pilot production of new commercial cores, adverse environment cores and satellite memory systems.

As General Manager of the Ferromagnetics Division of Telemeter Magnetics, Inc. from 1955 to 1959, he was responsible for the development, design and production of memory cores. He established a new core facility and developed production to a rate of 2,000,000 cores per week.

During the period 1953 to 1955, he was responsible for the magnetics design of several large core memory systems produced for the Rand Corporation, Argonne Laboratories, Aberdeen Proving Ground, Patrick Air Force Base, and others. At RCA Laboratories in Princeton, Mr. Rosenberg was a Research Engineer from 1946 to 1953. In this capacity he was responsible for development of storage devices utilizing both cathode tube and ferrite core techniques.

### Director of Research: Dr. Robert S. Weisz

The contributions of Dr. Weisz to the metal ceramics field have been numerous and significant. During the past twelve years his efforts nave been devoted exclusively to this field: six years at the RCA Laboratories in Princeton, New Jersey, where he worked continuously in research and development of square loop ferrite core materials and processes. Dr. Weisz's work continued while employed by Telemeter Magnetics, Inc. (now the Ampex Computer Products Company) during the past six years, where he was responsible for the development, design and process formulation of all magnetic cores produced by TMI.

Dr. Weisz has also conducted original research in magnetic thin film techniques, and his work in this field will continue at Electronic Memories, Inc. From 1942 through 1947 Dr. Weisz was employed by the Westinghouse Research Laboratories in Pittsburgh to do advanced research in physical chemistry with emphasis on ceramics techniques including some early research in linear ferrite materials. From early 1947 and until mid-1949 Dr. Weisz continued advanced development and research at the Thomas A. Edison Company as a Research Chemist. His efforts were primarily devoted to development of new and improved thermistors and batteries.

Dr. Weisz has published many professional papers in the fields of inorganic chemistry and electro-chemistry. He was honored in 1951 with an award by the Foote Research Foundation for reporting on his work in lithium ferrite materials. He is sole or co-inventor of over ten U.S. patents in ferrites and electro-chemistry.

Dr. Weisz received his AB from Cornell University in 1939 and his Ph.D. in 1942. The Doctorate was awarded in Physical Chemistry. While earning his advanced degree, Dr. Weisz served as an instructor in analytical chemistry at Cornell University.

### Senior Chemist: Daniel L. Brown

As a Senior Chemist from 1957 to 1961 at Telemeter Magnetics, Inc., Mr. Brown was responsible for new ferrite core development, production engineering, and process formulation of a full product line of memory and switching cores. During the period 1955 to 1957, he was employed by Lincoln Laboratories as Ceramic Laboratory Supervisor responsible for the development of high-speed memory cores for the TXI Computer. He was employed by the U.S. Bureau of Mines from 1952 to 1955 in the synthetic materials group at Norris, Tennessee, responsible for research and development of synthetic asbestos. Mr. Brown received a BS degree from Knoxville College, Knoxville, Tennessee in 1951. He has also completed advanced courses at Northeastern University, Boston, Mass. Mr. Brown is the sole or co-inventor of 3 U.S. patents in ferrite materials and synthetic minerals.

### Senior Staff Engineer: William S. Knowles

Before joining Electronic Memories, Mr. Knowles had been Project Engineer responsible for satellite core memories used as communication buffers, flight programmers and control computers for the VEGA, MARINER, and TRANSIT programs. This work was conducted at Ampex Computer Products Company (formerly Telemeter Magnetics, Inc.) where Mr. Knowles' responsibility included the magnetics, electronics, system and environmental packaging design, and schedule and budget performance.

From 1957 to 1959 at TMI Mr. Knowles was responsible, as Project Engineer, for the design and construction of data translators to convert analog information to computer format magnetic tape; translate magnetic tape to paper tape; and to drive a high-speed Videograph printer from a computer tape input. From 1954 to 1957, Mr. Knowles was a member of an engineering group responsible for the design of a wide line of computer core memories ranging in storage capacity from a few hundred bits to 500,000 bits and operating speeds ranging from 1.5 microsecond to 20 microseconds cycle time. His major concentration was on core driving and sense amplifier circuits.

From 1952 to 1954 he was with ASCOP (Applied Science Corporation of Princeton) where he worked on a digital system for automatic analysis and processing of missile telemetry data. At Johns Hopkins University Applied Physics Laboratory from 1942 to 1952, he participated as an Electronic Design Engineer, later becoming Project Engineer, in the development of proximity fuzes, f.m. receivers, and the basic development of the f.m./f.m. system of missile telemetry instrumentation.

Mr. Knowles is the sole or co-inventor of 12 U.S. patents in the field of electronics.

### Senior Magnetics Engineer: W. Robert Johnston

Mr. Johnston has specialized in core memory development and production design during the past seven years. During the past two years, he has been responsible for the magnetics design of satellite core memories for the VEGA, MARINER, and TRANSIT Programs. In addition, he was the Design Engineer for a satellite decade counter and magnetic logic circuits using ferrite cores.

From 1956 to 1959, Mr. Johnston was responsible for the magnetics and driver circuits for core memories which have been produced in substantial quantities during the past several years. The memories were both serial and random access systems with the former employing magnetic switch cores for access decoding and driving. During the period 1953 to 1956, Johnston was responsible for the design and fabrication of automatic core testing equipment, calibration techniques, quality control procedures, and manufacturing process standards. Mr. Johnston is the sole or co-inventor of 3 U.S. patents.

### Senior Staff Engineer: Ben T. Goda

Twelve years of Mr. Goda's professional career have been concentrated in the design of computer circuits and magnetic core memories. His aggressive design efforts have provided memories of high performance at low manufacturing cost levels. During the period of 1952 to the present, he has concentrated on the design of magnetic core memories for commercial digital computers. As Engineering Section Head at Telemeter Magnetics, from 1956 to 1961, he was responsible for the development and production design of sequential buffer memories, high-speed printer line buffer memories, small random access eight-microsecond memories, and large five-microsecond memories with a storage capacity of 16,384 words of up to 60 bits. These designs provided modular memory packages to meet a wide range of capacity requirements.

From 1952 to 1956, Mr. Goda was a Senior Engineer for Bendix Computer, responsible for the design of a magnetic drum memory and associated circuits (tube) for the G-15 Computer. He also undertook development design of transistor circuits for advanced computers and designed a small random access solid state core memory. Employed by Northrop Aircraft from 1950 to 1952, Mr. Goda was a Circuit Engineer and Peripheral Equipment Designer for the MADDIDA Computer System. Mr. Goda is a graduate of the Engineering School at the University of Southern California (BSEE) and is sole or co-inventor of 6 U.S. patents in the computer field.

### Senior Staff Engineer: Harry L. Knapp

Mr. Knapp is a graduate of Iowa State University with a BSEE degree. At EMI Mr. Knapp is the Project Engineer on a spacecraft memory system. Prior to joining EMI Mr. Knapp was employed at Telemeter Magnetics, Inc. (later Ampex Computer Products Company) as Project Engineer and later Manager of Military Systems. In these capacities he worked on memory design and development for the Bank of America ERMA system, the Air Traffic Control System, and the high speed 1-microsecond Aberdeen Proving Ground memory. In military systems Mr. Knapp was responsible for the design and development of a high speed buffer system for use in radar applications, a buffer system for the BIRDIE missile program, and a spacecraft memory program.

From 1955 to 1958 Mr. Knapp held the position of Design Engineer at Remington Rand UNIVAC and designed the core memories used in their Scientific Computer program. He also worked on the design of the computer proper for the UNIVAC Scientific Computer program.

### Chief Mechanical Engineer: V. E. Hovnanian

Mr. Hovnanian received his BME from New York University. Before joining EMI he held the position of Supervisor, Mechanical Design at Gilfillan Bros. Inc. In this position he was responsible for the transmitter design of a Navy radar system. Prior to this Mr. Hovnanian was a member of the technical staff at Thompson Ramo-Wooldridge responsible for mechanical design of airborne electronic equipment.

From 1957 to 1959 he was the engineer in charge of large engine test stands at Rocketdyne. He was responsible for the design of systems required to test Atlas rocket engines, including electrical, mechanical, pneumatic and propellant systems. From 1950 to 1957 he was Thermodynamicist at Lockheed Aircraft Corporation where he performed design weight analysis of aircraft structures and systems and heat transfer analysis.

Senior Electronics Engineer: Robert W. Chambers

Prior to joining EMI Mr. Chambers was Project Engineer on the Electrada Corporation's Datacom unit. While at Electrada Corporation he worked on design and development of digital data transmitters and mechanical drum test units.

From 1956 to 1960 he held the position of Project Engineer at Advanced Electronics Manufacturing Corporation and worked on control and storage systems for automatic embossing machine equipment, computer input/ output equipment and drum memory storage. Prior to this Mr. Chambers worked on remote metering systems for the oil industry at the Smith Meter Corporation subsidiary of A. O. Smith.

While at the Rand Corporation he worked on the design and development of the prototype Johnniac Computer and the final design.

Mr. Chambers is the co-inventor of one U.S. patent and attended Santa Monica City College and the University of Southern California, where he majored in physics.

### Staff Engineer: Helmet Graf

Mr. Graf engaged in the design of U.H.F. television transmitters from 1951 until 1954. In 1954 Mr. Graf became associated with Motorola as a Design Engineer in a pulse circuitry development group. From 1958 until 1961 he was responsible for design and development of coincident current core memories at Telemeter Magnetics, Inc.

Mr. Graf received a BEE from the Oskar V. Maller College, Munich, Germany. Since his affiliation with EMI he has completed the circuit design for a MIL-SPEC high speed memory.

### Staff Engineer: Loy Spears

Mr. Spears joined EMI in June, 1962. His experience in the design of ferrite memory devices includes a position as Staff Engineer, designing memory systems with Rese Engineering in Philadelphia, Pa. from August, 1961 until June, 1962. Before that, Ampex Computer Products Company (formerly Telemeter Magnetics, Inc.) employed him as a Staff Engineer designing memory systems, from June, 1959 to August, 1961. While with Ampex, Mr. Spears was also the Project Engineer on a 1.5 microsecond memory project. During 1959, he was a Field Engineer with IBM in Kingston, New York.

Mr. Spears attended Santa Monica City College and Reed College (Portland, Oregon) where he majored in mathematics. His present responsibility with EMI is the design of satellite data storage units.

### Manager of Ferrite Production: Donald A. Zumwalt

Mr. Zumwalt received a BS degree from the University of Illinois in Electronic Engineering and has taken advanced courses in metallurgy and electronics at the University of California at Los Angeles.

Before joining EMI Mr. Zumwalt held the position of Production Manager and Chief Engineer for Statnetics Corporation. His work involved producing new types of miniaturized ceramic capacitors. From 1958 to 1961 Mr. Zumwalt was Manager of Ferrite Production at Telemeter Magnetics, Inc. and was responsible for the manufacture of all ferrite memory cores and magnetic head pieces. This included electronic testing, formulation and processing of the ferrite memory cores. From 1956 to 1958 he held the position of Ceramics Engineer with Collins Radio Company where he developed processes for special radio frequency ferrites. Projects included particle size studies and their relation to crystal growth, methods of producing special shapes, formulations, process specification and process methods for extrusion.

Previous to 1956 Mr. Zumwalt worked in research and development for Glascote Products Division of A. O. Smith. The experience gained here covered a wide range of electronic applications, such as special ceramic coatings for high temperature applications used in rockets, aircraft exhaust and automatic reactors. Laboratory work was also done in formulation and testing of electrically resistant glass for chemical pressure tanks.

### Director of Manufacturing: Bernard Hathaway

Mr. Hathaway brings more than ten years of electronic manufacturing production experience to EMI. From 1957 through 1961 he held a series of managerial positions in Engineering and Production at Ampex Computer Products (formerly Telemeter Magnetics, Inc.) Prior to joining TMI, Mr. Hathaway was associated with Lear, Inc. and Canadian Marconi as a Project Engineer.

Mr. Hathaway is responsible for all facets of production at EMI. He supervises the work of more than 100 engineers, technicians and production line workers engaged in the manufacture of ferrite cores, arrays, stacks and complete memory systems.

Mr. Hathaway was educated at Rotherham College of Technology, where he graduated in 1949 with a Bachelors Degree in Electrical Engineering. His professional affiliations include membership in both the Institute of Electrical Engineers and the Institute of Radio Engineers.

### Production Manager: Jack Hill

Mr. Hill brings to Electronic Memories 20 years of experience in electron-

ics manufacturing, maintenance and ferrite core assembly techniques. From 1941 to 1945 Mr. Hill worked with radar and moving target indicator equipment at MIT Radiation Laboratories. During the period 1945 to 1950 he maintained and installed custom-made television projection systems. From 1951 to 1954 he was employed by International Telemeter Corporation in the production and installation of the early pay-as-you-go television systems. During 1954 and 1955 at ITC Mr. Hill was engaged in the development and production of several large scale memory systems for the Rand Corporation, Aberdeen Proving Grounds, and others.

At Telemeter Magnetics (now Ampex Computer Products Company) from 1956 to 1961 Mr. Hill was responsible for the supervision of the Engineering model shop. In this capacity he developed pre-production and production techniques for a complete line of magnetic core buffers and commercial random access memories. He was also responsible for the prototype production and initial production models of a large 1.5 microsecond cycle time memory.

Mr. Hill presently manages a skilled production crew who are producing a number of satellite memories and other memories for MIL-SPEC applications.

### Product Manager: Dean Knutson

During the period 1958 to 1961, Mr. Knutson was employed by Telemeter Magnetics as a Product Application Engineer and later as Sales Manager for the Advanced Development Division. He was responsible for design analysis and application studies of ferrite cores and memories to a wide range of computer, data handling, automatic control systems, and memories for satellite and missile programs.

Mr. Knutson was employed by Waugh Engineering from 1956 to 1958 as Project Engineer for engine fuel flow test facilities. From 1949 to 1956, he was employed by Telecomputing Corporation successively as Customer Service Engineer, Field Service Engineering Manager, Applications Engineer, and Sales Manager for data reduction equipments. During this period, he was actively involved in system and equipment design and application for telemetry, high speed camera and wind tunnel instrumentation, data collection and data processing. Mr. Knutson received a BSEE from the University of California at Berkeley.

### Product Manager: Ronald G. Heath

Mr. Heath received his degree in Electrical Engineering from the Royal Aircraft Establishment College in England in 1952. He has 8 years of experience in sales of core memory and core memory products.

Prior to joining EMI, Mr. Heath was employed by the Military Electronics

Division of Daystrom, Inc. as Sales Manager for high speed memory products and development contracts in the Western USA. From 1958 through 1961, Mr. Heath was associated with Telemeter Magnetics, Inc. as a Project Engineer on high speed memories and buffers, and as a Sales Engineer for their Core Memory Division. Mr. Heath was also associated with Canadair Ltd. in Montreal as a Senior Engineer in the Missile Instrumentation Group. His professional affiliations include membership in the Association for Computing Machinery.

Eastern Regional Sales Manager: Richard J. Dadamo

Mr. Dadamo is responsible for the sales of EMI products in the Eastern seaboard states.

Mr. Dadamo's educational background includes a BSEE at Pennsylvania State University, 1951; MSEE at Drexel Institute of Technology, 1954; Graduate Work, Digital Computers at Moore School, University of Pennsylvania; Graduate Work, Business Administration, Drexel Institute of Technology.

Mr. Dadamo joins EMI from Burroughs Corporation where he was Engineering Manager of the Electronic Instruments Division, responsible for all phases of engineering. He joined Burroughs in 1956 as a Design Engineer responsible for magnetic circuits, memory stacks, memory systems and memory test systems. He participated in the Atlas Guidance system program at Burroughs; and in 1958 he was promoted to Supervisor of the Electronic Design Group, responsible for the development of magnetic devices.

Prior to Burroughs, Mr. Dadamo worked as a Design Engineer at Sperry Rand Univac and for the U. S. Naval Department. In addition, Mr. Dadamo has taught digital computer courses at Temple University, Philadelphia, Pa.

Western Regional Sales Manager: Jack Ogg

Mr. Ogg is responsible for all EMI sales activities in the Western states. He has a wealth of experience in marketing computer related products, having held the position of Marketing Division Manager for Ampex Computer Products Company (formerly Telemeter Magnetics, Inc.) before joining Electronic Memories.

Prior to joining Ampex, Mr. Ogg was employed by Telecomputing Corporation, where he began in 1950 as Data Reduction Supervisor in the Computing Center and rose to Sales Manager, Data Equipment Division in 1957.

Mr. Ogg attended both the University of Southern California and the University of California, Los Angeles, where he majored in Business Administration.

### sales offices

# electronic memories

Thank you for your recent inquiry. The information you requested is enclosed. We look forward to supplying you with ferrite memory cores, arrays and stacks, or complete memory systems.

For your convenience, your nearest EMI representative is listed below.

### CALIFORNIA

Electronic Memories Inc. 12621 Chadron Avenue Hawthorne, California 90250 (213) 772-5201 TWX 910-325-6213

Electronic Memories, Inc. Western Regional Sales Office 13415 Ventura Blvd. Suite 2 Sherman Oaks, California 91403 (213) 872–1062

Tech Marketing Associates 355 West Olive Avenue Sunnyvale, California 94086 (408) 736-3687 TWX 910-339-9227

### ILLINOIS

Electronic Memories, Inc. Central Regional Sales Office 259 E. Rand Road Mt. Prospect, Illinois 60056 (312) 253-7540

Ropek-Cahill, Inc. 5439 West Division Street Chicago, Illinois 60651 (312) 287-7292 TWX 910-221-5219

### MASSACHUSETTS

Electronic Memories, Inc. Eastern Regional Sales Office 11 Chestnut Street Andover, Massachusetts 01810 (617) 475-2101 TWX 710-347-0334

### MICHIGAN

W. R. Hummon & Associates P.O. Box 501 Farmington, Michigan 48024 (313) 474-0661 MINNESOTA

RECEIVED

Lloyd Murphy Associates FRACKIEWICZ 730 Chicago Avenue Minneapolis, Minnesoto 55415 (612) 333-4511 TWX 910-576-3417

OHIO

Jay Engineering Company 1721 East Third Street Dayton, Ohio 45403 (513) 253-2151 TWX 513-944-0256

Jay Engineering Company 4712 West 130th Street Cleveland, Ohio 44135 (216) 252–0486 TWX 216–252–7260

PENNSYLVANIA (AND SOUTHERN NEW JERSEY)

> Electronic Memories, Inc. P.O. Box 470 Bryn Mawr, Pennsylvania 19010 (215) LA 5-6897

### TEXAS

Southwest Electronic Industries, Inc., 621 Meadows Building Dallas, Texas 75206 (214) EM 3-1671 TWX 910-861-4315

Southwest Electronic Industries, Inc. 6001 Gulf Freeway, Room C-102 Houston, Texas 77023 (713) WA 8-5251

# APR 1 1 1967 WASHINGTON

Myron R. Smith & Co., Inc. 6361 First Avenue South Seattle, Washington 98108 (206) PA 5-1665

### EUROPEAN REPRESENTATIVES

Ingenjorsfirman Nordisk Elektronik AB Stureplan 3 Stockholm, Sweden Tel: 08/24 83 40 Telex: 10547 Cable: Nordtron

A/S Nordisk Elektronik Danasvej 2 Copenhagen V, Denmark Tel: EVA 8285 Cable: Lektronord

Munzig International Inc. 6 Av. de Frontenex 1207 Geneva, Switzerland Tel: 35 84 14 Telex: 23 336 Cable: Munzigint, Geneva

Munzig International Inc. McGraw-Hill House Maidenhead, Berkshire England Tel: Maidenhead 20260 Telex: 84330 Cable: Munzigint, London

Munzig International Japan, Inc. #8-2, 4-Chome Akasaka, Minata-Ku Tokyo, Japan Tel: 401-8785, 402-4337 Telex: TK2859 Cable: Munzigint, Tokyo

Technique & Produits 63 Bis, Rue d'Aguesseau Boulogne-Sur-Seine, France Tel: 408-14-00 (9 Lingnes Groupees) Telex: Protec 25997 Coble: PRODUTEC

### electronic memories 12621 chadron avenue, hawthorne, california 90250

telephone (213) 772-5201

1966 ELECTRONIC MEMORIES, INC.

# electronic memories

## application note

RECEIV

APR 1 1 1967

### B. FRACKIEWIL.

# coincident current NDRO memory

to combine nondestructive readout (NDRO) capability with the low cost of coincident current selection.

Electronic Memories is presently producing NDRO stacks type environment.

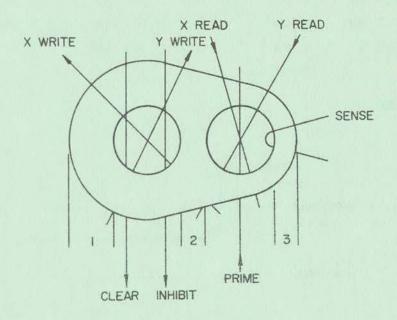

The "Shmoo" core may be operated in a number of different ways. After a discussion of the basic principles of operation of the core, we shall briefly describe two methods of operation in a stack.

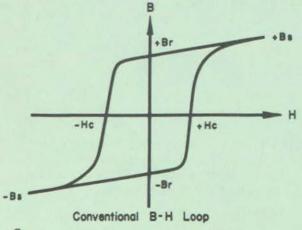

### principles of operation

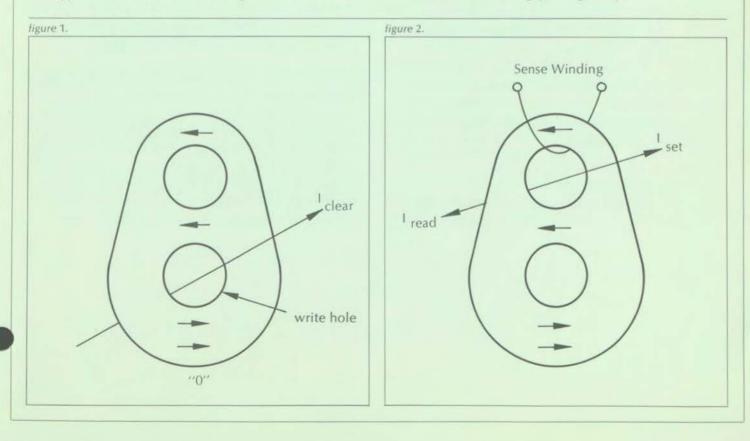

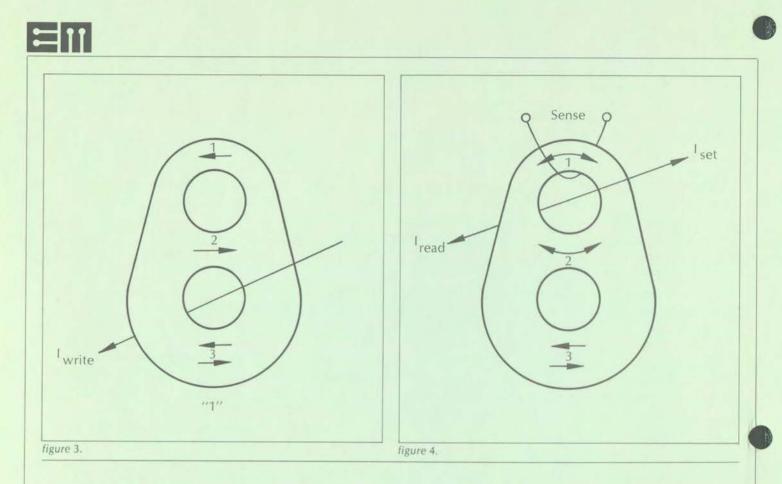

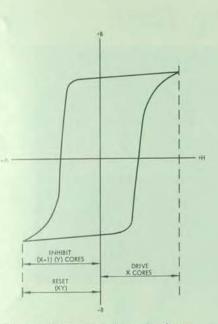

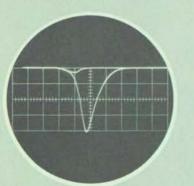

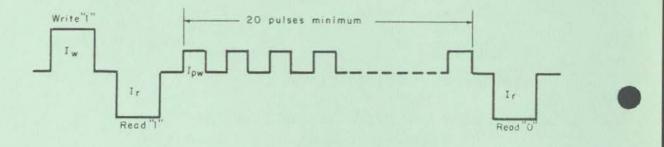

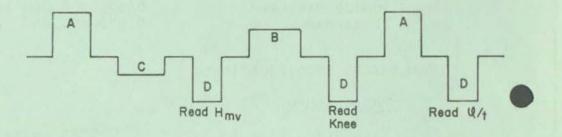

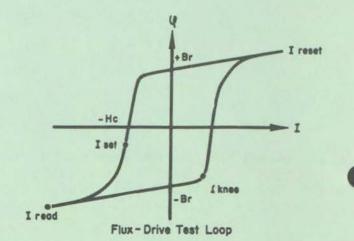

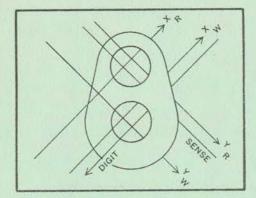

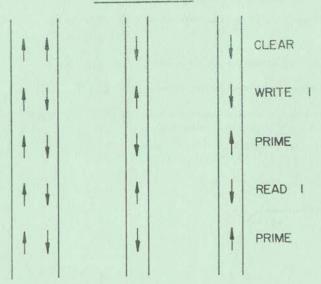

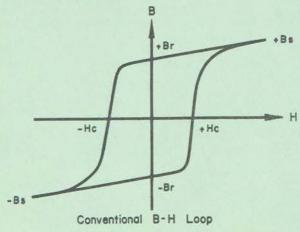

The core in Figure 1 is shown in the "cleared" or "0" state. The core has been fully saturated by a clear current pulse as shown. The orientation of the lines of flux are indicated by the arrows.

If a current pulse is passed through the read hole of a core in the "0" or cleared state, essentially no output voltage will appear across the sense winding. Since the core is in

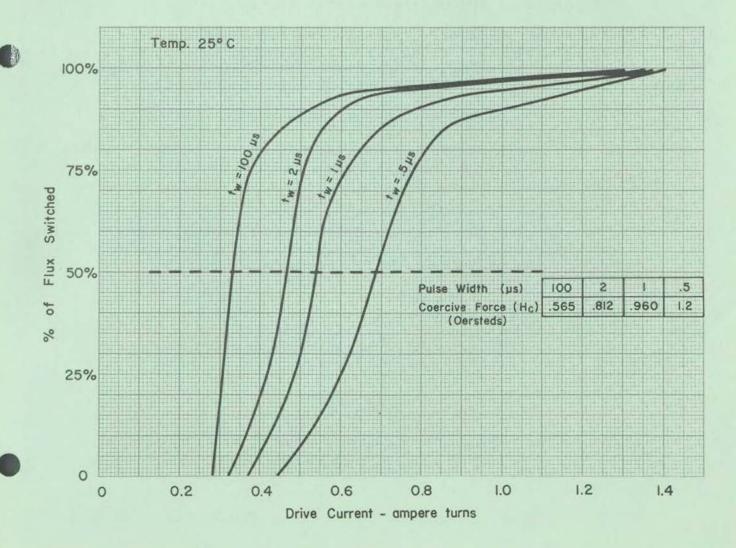

The Electronic Memories "Shmoo" transfluxors are designed hard saturation as shown in Figure 1, any current in the read hole (as shown in Figure 2) will not cause any significant change in flux.

Naturally, there are limitations of current amplitudes for to be operated over a wide temperature range in an aircraft which the above statement is true. These limitations will be discussed later in detail.

> If a current is passed through the write hole in the opposite direction to that of clear current, the flux in leg 2 and part of that in leg 3 will be reversed. The core is now said to be in the "1" state as shown in Figure 3. Write current amplitude must be limited in order not to reverse more than half of the flux in leg 3.

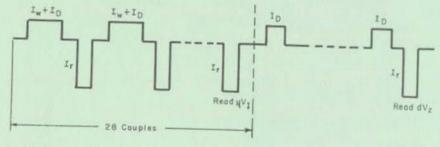

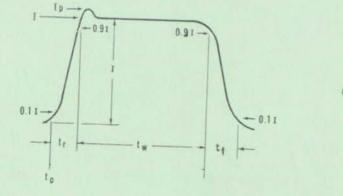

> A current pulse in the read direction in the read hole will now reverse the flux in legs 1 and 2, and will result in an output voltage across the sense winding. A current pulse in the set direction following the read pulse will reset the flux in legs 1 and 2 to the original "1" state condition, and while so doing, will produce an output voltage of opposite polarity across the sense winding (see Figure 4).

### Electronic Memories Application Note

### Coincident Current NDRO Memory

Page 2

The NDRO principle of operation results from the fact that the core can be read and set an infinite number of times without ever having to re-write the information as in a standard toroid memory core.

The information stored is determined by the state of flux in leg 3.

### practical limitations:

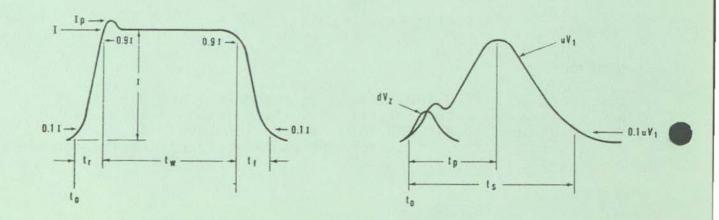

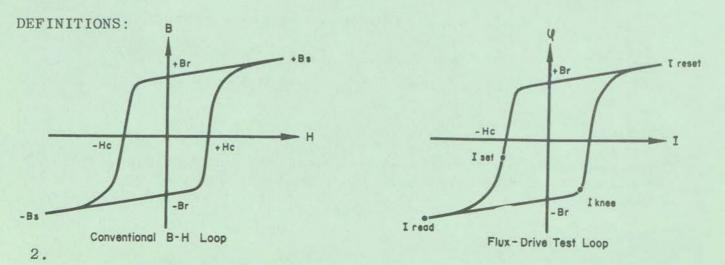

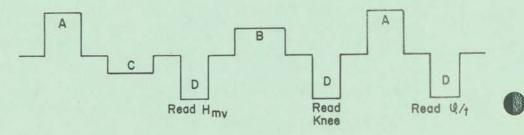

In order to discuss basic limitations of this geometry, some definitions are first in order.

- $I_{KR} = Knee of the read hole.$

- $I_{KW} = Knee of the write hole.$

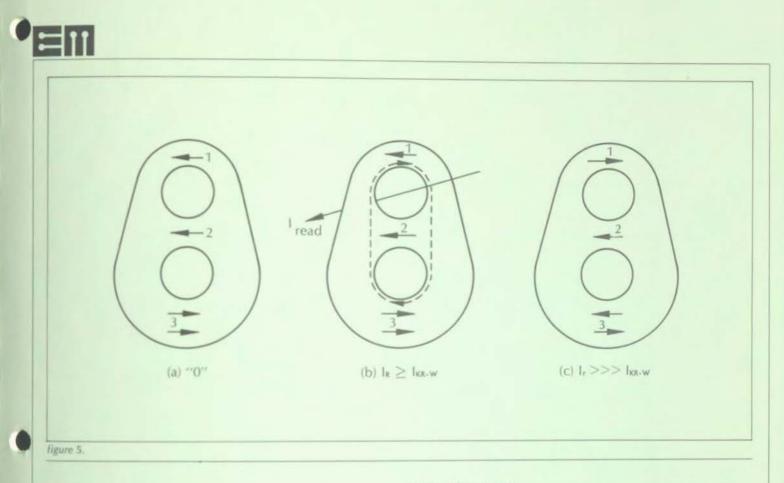

- I<sub>KR-w</sub> = Unblock knee, amplitude of current in the read hole, in the read direction, that will cause a core in the "0"

state to begin to change to the "1" state. Current pulses at this level or higher will cause the information written into the memory to be destroyed.

Hence, the absolute limits for read current are:

$$_{\rm KR}$$

$<$   $I_{\rm R}$   $_{\rm min.}$   $<$   $I_{\rm R}$   $<$   $I_{\rm KR-V}$

where  $I_{R\ min}$  is the minimum value of read current necessary to produce a desired output signal level.

Figure 5 depicts the results of  $I_R > I_{KR-W}$ . Since the flux in leg 2 is already saturated in that same direction, the only possible flux couple is between legs 1 and 3. The current begins to switch the innermost flux in leg 1, along with the innermost flux of leg 3 (shortest path length). When all of the flux of leg 1 has been reversed, half of the flux of leg 3 is also reversed, and the core is now in the "1" state.

Page 5

# HI

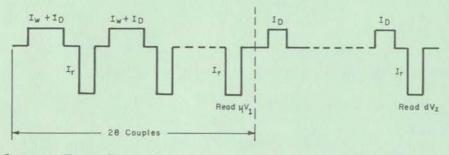

### operation: Write Mode

The write operation is a coincident current operation which may be performed only after the desired word/words to be written into have been cleared by applying clear current in the appropriate clear section.

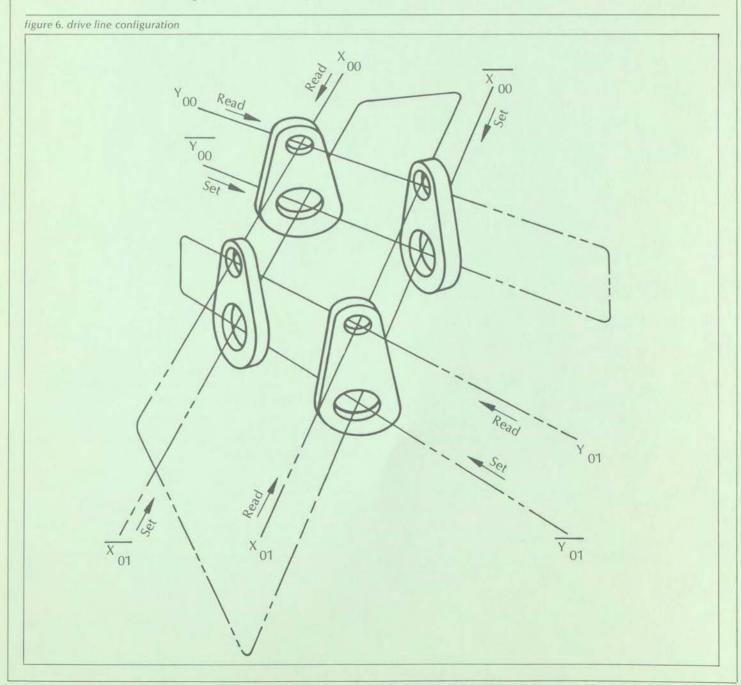

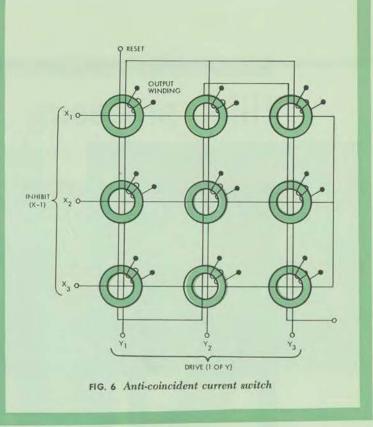

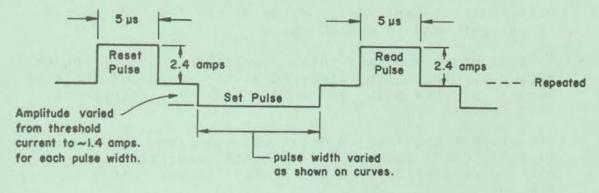

A "ONE" is written by applying a Y set pulse in coincidence with an X read pulse with polarities as shown in Figure 6.

When writing it is imperative that the least significant bit of the X address register be complemented in order to select the proper address. For example, to write a "ONE" in  $X_{00} Y_{00}$ , a  $Y_{00}$  set pulse is applied in coincidence with an  $X_{01}$  read pulse due to the fact that the X drive line through a read hole of a core re-enters the write hole of a core on an adjacent line.

During this operation, the Y read and X set pulses are gated off by a timing generator.

In order to write or maintain a "ZERO," the write operation is performed in coincidence with an inhibit pulse of the proper polarity as is normal for coincident current operation.

### operation: Read Mode

The read mode of operation is identical to the standard coincident current operation of a toroidal core. The core output is sensed during the full read pulse and the core is subsequently set to the original state by a full set pulse of equal but opposite polarity.

### five-wire system

In the five-wire system, each core is threaded in the following manner:

Write Hole

- 1. Clear winding

- 2. Inhibit winding

1

X drive line

Y drive line

Read Hole

3. Sense winding

The clear winding again divides the stack into sections for convenience. The X, Y drive, inhibit and sense windings are conventional.

### operation: Write Mode

In order to write information into the memory, the appropriate clear section/sections must first be cleared by applying a clear current pulse of proper polarity, amplitude and duration to the clear line.

The write operation is performed following a clear operation by selecting in a coincident current manner, the appropriate X and Y lines and driving with current pulses equal to

## $\frac{1}{2}$ (R+W) amplitude.

Hence, writing is accomplished by overdriving the read hole to produce the "ONE" and by adding an inhibit pulse in the clear direction in the write hole to maintain a "ZERO."

### operation: Read Mode

The read operation of the NDRO is performed by coincidence of  $I_{read}$  followed by  $I_{set}$  on the appropriate X, Y lines. In addition, in coincidence with the  $I_{read}$  pulses, a pulse bias in the clear direction may be provided in the write hole on the clear sections common with the selected address to increase the current tolerances.

After writing, the memory must be cycled through completely one time before valid data is available. The reason for this is that while writing with  $\frac{1}{2}$  (R+W) half pulses, cores on the selected lines are left in the readout state and therefore must be reset before being read in the next cycle.

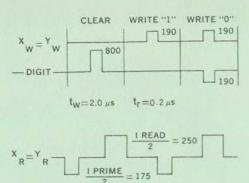

A new "Shmoo" core is currently being developed at Electronic Memories which will not require the pulse bias current in the write hole in the five-wire system. Shmoo's are being made in both the conventional MgMn ferrite and in the low temperature coefficient lithium materials. Cycle times as low as 2 microseconds are obtainable in NDRO memories. Drive currents are as low as 190 ma for half pulses. Signalto-noise ratios of 5:1 with drive current tolerances of  $\pm 10$ percent over a temperature range of 100°C are obtainable. Electronic Memories Application Note

The ratio of  $\frac{I_{KR,W}}{I_{KR}}$  is on the order of 1.7. This ratio results in a loss of tolerance in coincident current operation in comparison with a standard toroid.

Obviously, steps must be taken to prevent this from occurring in a memory system.

The effective path length between the read hole and the write hole may be altered by passing a current through the write hole in the clear direction during the presence of the read pulse. The magnitude of this current must always be less than  $I_{kw}$  in order not to affect the flux surrounding the write hole.

This current may either be in the form of a pulse or a DC bias. The pulse is more desirable as DC current presents another problem during the set pulse if the magnitude of the bias is too large.

The pulsed current may be mechanized by either pulsing the clear line in the presence of the read current pulse, or by re-entering the read hole drive line through the write hole.

### seven-wire system

In the seven-wire system, each core is threaded in the following manner:

- Write Hole

- 1. Clear winding

- 2. Inhibit winding

- 3. X drive line

- 4. Y drive line

Read Hole

- 1. X drive line

- 2. Y drive line

- 3. Sense winding

The X and Y drive line configuration is shown in Figure 6. Notice that the Y drive line through the read hole re-enters the write hole of the same core. The purpose of this is to increase tolerances while guarding against the unblock condition previously discussed.

The X drive line through the read hole re-enters the write hole on an adjacent line.

The clear winding is made common to certain sections of the memory stack. For example, for a 4096 x 12 memory stack, there could be four 1024 x 12 clear sections. This is done in order to compromise between clearing one word at a time (word organized), and having to clear all locations at one time.

The design of EMI's "Shmoo" transfluxor was based upon certain considerations given to an electrically alterable NDRO memory system. Among these considerations was that for an airborne type computer, the information contents would be changed infrequently relative to the number of read cycles performed. From a system standpoint, the writing of information into the memory would generally be accomplished on the ground and would be done in blocks of words. Hence, the advantage of an NDRO system would best be utilized when writing information was performed only on the ground, and the clear operation was more practical when divided into discrete sections of the memory rather than one word at a time.

The inhibit and sense windings, although in separate holes, are threaded in the same manner as in a conventional toroid core memory stack.

The advantage of the seven-wire system is that the same drive lines and drive circuitry may be used for both the read and write modes of operation.

electronic memories

12621 chadron avenue, hawthorne, california 90250 telephone (213) 772-5201

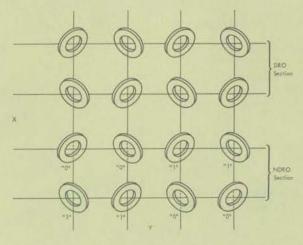

COMBINATION FIXED PROGRAM NDRO AND DRO SCRATCHPAD CORE MEMORY STACK

### FEATURES

For applications where fixed program NDRO and DRO scratchpad memories are desired, this type of stack has the following advantages:

TYPICAL X AND Y DRIVE LINE WIRING FOR DRO AND NDRO SECTIONS

"O" cores in NORO section are not threaded by a Y drive line.

### Coincident Current Selection

No additional circuitry is required for operation of the NDRO section.

Presently, computers having both fixed program NDRO and DRO scratchpad memories typically use two systems, such as a rope memory and a core memory. Each system requires entirely different selection and drive circuitry. When NDRO and DRO storage are combined into a single stack utilizing coincident current selection, overall circuit complexity is drastically reduced.

### High Reliability

The NDRO program is permanently wired; therefore, loss of information resulting from external circuit and/or power failure is not possible.

### Fast Cycle Times

Cycle times are compatible with conventional 4 wire DRO coincident current core memory stacks utilizing the same core type.

### Low Volume

The volume is identical to that of a conventional 4 wire, coincident current core memory stack of the same storage capacity.

### Low Power

Power requirements are less than those of a conventional 4 wire stack of the same storage capacity and the same core type.

### Ruggedized Construction

The stack operates over a wide temperature range of  $-55^{\circ}$ C to  $+100^{\circ}$ C. It is suitable for military and space environments.

### Low Cost

-

The cost is lower than other solutions to this type of application.

### CONSTRUCTION

The ratio of NDRO to DRO storage capacity is virtually unlimited. For the purpose of simplicity, a stack of 4,096 words of N bits, equally divided into 2,048 words of NDRO and 2,048 words of DRO, is used to illustrate the wiring.

### **DRO** Section

- 1. 32 X lines

- 2. 64 Y lines

- 3. Standard diagonal type sense winding for each of the N bits.

- Standard inhibit winding passing through 2,048 cores parallel to the X drive lines. One inhibit winding is required for each of the N bits.

### NDRO Section

- 1. 32 X lines, each of which threads all cores on a given drive line.

- 64 Y lines, each of which threads only those cores containing a "1". The Y drive lines are common to both the DRO and NDRO sections of the memory.

- 3. Standard diagonal type sense winding. The sense winding is also common to both the NDRO and DRO sections of the memory.

- 4. No inhibit line is required, as the NDRO section contains permanent information.

### OPERATION

The operation of the stack is essentially identical to any coincident current core memory stack. The same type and number of drive and sense circuits, as well as address and data registers, are used.

The NDRO section operates on the principle that only cores containing a "1" receive a full current pulse when selected, whereas the "0" cores are limited to a half current pulse because of the nature of the Y drive line wiring.

### PERFORMANCE

The performance of the stack over a wide temperature range of  $-55^{\circ}$ C to  $+100^{\circ}$ C is excellent. High signal-to-noise ratios in conjunction with wide drive current tolerances are obtained even under worst case pattern conditions.

Further details may be obtained upon request.

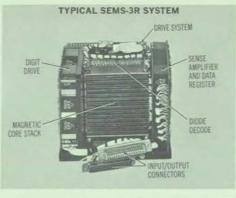

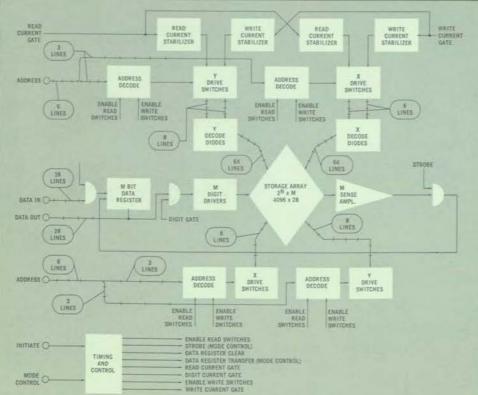

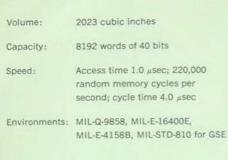

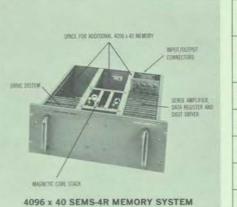

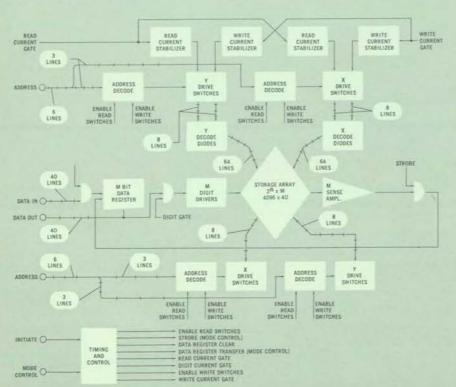

## SEMS-3R AEROSPACE CORE MEMORY SYSTEM

| Capacity:          | 256 to 4096 words / 4 to 28 bits per word                                                 |

|--------------------|-------------------------------------------------------------------------------------------|

| Speed:             | 4.5 µsec cycle time                                                                       |

| Temperature Range: | $-55^\circ\text{C}$ to $+100^\circ\text{C}$ or $-25^\circ\text{C}$ to $+75^\circ\text{C}$ |

| Size:              | 4½" x 5¾" x 6¾"                                                                           |

| Volume:            | 175 cubic inches                                                                          |

Meets MIL shock, vibration and humidity specifications

electronic memories inc. 12621 Chadron Avenue, Hawthorne, California

### THE SEMS-3R 175 cubic inches. 4096 words of 28 bits. Access time less than 1.0 microseconds; 220,000 Random Mem-

ervironments: MIL-E-5400, MIL 16400E,

MIL 4158B.

Volume:

Capacity:

Speed:

The SEMS-3R allows severe environment control and guidance systems designers to put a fast, rugged, large capacity core memory system into tightly restricted space. The memory system is available in a range of word capacities and bit sizes. The SEMS-3R is available in two operating temperature range versions for maximum applications economy.

The SEMS-3R is designed specifically for airborne, satellite, shipboard and ground based applications where high reliability, low weight and volume, minimum power and high speed are required design criteria.

| SPECI                                   | FICATIONS                                                                                                                                                                                                                                            |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Storage Capacity                        | 256, 512, 1024, 2048, or<br>4096 words by 4 to 28 bits<br>(in 2 bit increments)                                                                                                                                                                      |  |

| Operating Temperature                   | -55°C ta +100°C or<br>-25°C to +75°C                                                                                                                                                                                                                 |  |

| Storage Temperature                     | -65°C to +125°C                                                                                                                                                                                                                                      |  |

| Altitude                                | 70,000 ft., or higher at slightly reduced upper temperature limits                                                                                                                                                                                   |  |

| Read/Restore Cycle Time                 | 4.5 μsec.                                                                                                                                                                                                                                            |  |

| Clear/Write Cycle Time                  | 4.5 μsec.                                                                                                                                                                                                                                            |  |

| Access Time                             | Less than 1.0 µsec.                                                                                                                                                                                                                                  |  |

| Operating Rate                          | 0 to 220 Kc                                                                                                                                                                                                                                          |  |

| Input Signal Levels                     | Binary 0 = 0 to 0.5 V<br>Binary 1 = $+4$ V to $+7$ V                                                                                                                                                                                                 |  |

| Output Signal Levels                    | Binary 0 = 0 to 0.25 V<br>Binary 1 = $+5$ V to $+6.5$ V                                                                                                                                                                                              |  |

| Input Currents<br>A. Address            | 3 ma. max. for 1.5 µsec. if<br>line is iff + state; 0 ma. if line<br>in 0 state                                                                                                                                                                      |  |

| B. Mode Control                         | 0.4 ma. in 0 state<br>(CLEAR/WRITE), 0 ma. when<br>in + state (READ/RESTORE)                                                                                                                                                                         |  |

| C. Information                          | 0 level – no current required<br>± level – less than 1.0 ma.                                                                                                                                                                                         |  |

| D. Initiate                             | tevel – less than 1.0 ma.     tevel – no current required     + level – less than 1.0 ma.                                                                                                                                                            |  |

| E. Edge Current                         | In addition to the logic current<br>required, approximately<br>9.0 ma. of edge current must<br>be supplied to charge a<br>capacity of approximately<br>200 µµf to effect a change<br>from one logic level to another<br>level within 100 nanoseconds |  |

| Output Current<br>Information Lines     | 0 level – 0 current<br>+ level – 5.0 ma.                                                                                                                                                                                                             |  |

| Input Signal<br>Characteristics         | Rise Time Width<br>(µsec.) (µsec.)                                                                                                                                                                                                                   |  |

| A. Address                              | .1 1.5 min.                                                                                                                                                                                                                                          |  |

| B. Initiate                             | .1 0.2 to 2.0                                                                                                                                                                                                                                        |  |

| C. Information Lines<br>D. Mode Control | .1 1.0 min.<br>level level                                                                                                                                                                                                                           |  |

| Output Signal                           |                                                                                                                                                                                                                                                      |  |

| Characteristics<br>Information          | .1 2.0 min.                                                                                                                                                                                                                                          |  |

| Power Req'mt (4096 x 28)                | 35 watts for 4.5 µsec. cycle time                                                                                                                                                                                                                    |  |

| Voltages Required                       | +15, +6, -3                                                                                                                                                                                                                                          |  |

| Volume (4096 x 28)                      | 175 cubic inches                                                                                                                                                                                                                                     |  |

| Weight (4096 x 28)                      | 8 lbs.                                                                                                                                                                                                                                               |  |

| Form Factor (4096 x 28)                 | Length = $6.75$ ; Width = $5.79$ ;<br>Height = $4.45$                                                                                                                                                                                                |  |

| Applicable Mil Specs                    | MIL-E-5400, MIL 16400E,<br>MIL 4158B, MIL-Q-9858                                                                                                                                                                                                     |  |

Per applicable mil spec

Word capacities to 8192 and bit length to 56 are available

Welded circuit modules and encapsulated magnetics

Vibration and Shock

Type of Packaging

for special requirements.

# electronic memories

# core memory development 1955-1967

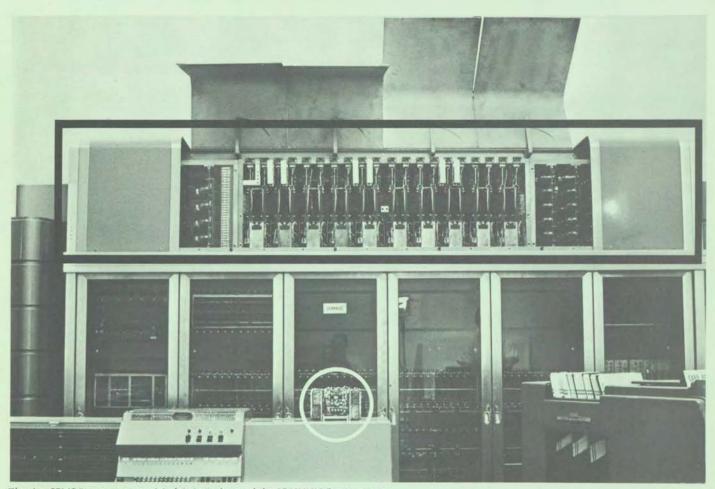

The small white box is SEMS 5 (Severe Environment Memory System), 7 pounds of militarized core memory which stores as much data as the historic 800-pound, 1955 unit behind it, which is the first commercial core memory ever built. Each contains 4,096 words of com-

parable lengths. Electronic Memories personnel instrumental in the design of both offer you a somewhat nostalgic comparison of their characteristics, to underline the strides core memories have made in 12 years.

Page 2

The tiny SEMS 5 core memory (circle) sits in front of the JOHNNIAC computer. Only the height and width of JOHNNIAC'S core memory are shown (outlined portion). The historic memory has a depth of nearly six feet and occupies the entire top portion of the computer.

.

|                                               | A slightly nostalgic comparison of the first commercial core memory ever built-and some of its eccentricities-with a 1967 version, the SEMS 5.                                                                                                                            |                                                                                                                                                                                    |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name                                          | JOHNNIAC MEMORY-1955                                                                                                                                                                                                                                                      | SEMS 5 MEMORY - 1967                                                                                                                                                               |  |  |

| distinction                                   | First commercial core memory ever built. 1955-1967.                                                                                                                                                                                                                       | Smallest commercial core memory ever built wit<br>a storage capacity comparable to Johnniac's                                                                                      |  |  |

|                                               | Preceded only by experimental core memories built at Massachusetts Institute of Technology.                                                                                                                                                                               | Only standard core memory for severe environ ment applications in production.                                                                                                      |  |  |

| age                                           | 12 years old.                                                                                                                                                                                                                                                             | Just over one year old.                                                                                                                                                            |  |  |

| history                                       | Installed 1955 in the JOHNNIAC computer at<br>RAND Corp., Santa Monica, Calif. Retired Feb-<br>ruary 1966 with full honors to the Los Angeles<br>County Museum after 53,000 hours of operation.                                                                           | Introduced for military and aerospace applica<br>tions by Electronic Memories, November 1965.                                                                                      |  |  |

| amount of infor-<br>mation stored             | 4,096 computer words, each 40 bits long.                                                                                                                                                                                                                                  | 4,096 computer words, each 32 bits long.                                                                                                                                           |  |  |

| weight                                        | 800 pounds.                                                                                                                                                                                                                                                               | 6.9 pounds. 1/115th Johnniac's weight.                                                                                                                                             |  |  |

| size                                          | 105 cubic feet.                                                                                                                                                                                                                                                           | 1/13th of a cubic foot. 1/1000th Johnniac's size                                                                                                                                   |  |  |

| power<br>requirement                          | 15,000 watts.                                                                                                                                                                                                                                                             | 60 watts. 1/250th Johnniac's power. No more than<br>used by an ordinary light bulb. 6 watts standby                                                                                |  |  |

| speed                                         |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                    |  |  |

| access time                                   | 15 microseconds.                                                                                                                                                                                                                                                          | 700 nanoseconds. 21 times faster.                                                                                                                                                  |  |  |

| cycle time                                    | 15 microseconds.                                                                                                                                                                                                                                                          | 2 microseconds. Nearly 8 times faster.                                                                                                                                             |  |  |

| split cycle                                   | None.                                                                                                                                                                                                                                                                     | 2.4 microseconds (optional).                                                                                                                                                       |  |  |

| required<br>temperature<br>environment        | Earned the nickname "Pneumoniac" because it<br>worked only when the temperature was a cool<br>44°F (13.5°C). 8 tons capacity of air conditioning<br>was installed to maintain this temperature.                                                                           | Operates unaided in temperatures as brisk as 65°F below zero to a hot 185°F (-55°C to +85°C)                                                                                       |  |  |

| eccentricities<br>about working<br>conditions | The computer was afraid of the dark. Fluorescent<br>nightlights were installed when it refused to<br>operate properly after room lights were turned<br>off. In spite of this temperature failing, Johnniac<br>introduced a new order of reliability and perform-<br>ance. | None. Operates under severe shock, vibratior<br>and humidity conditions as defined by applicable<br>portions of military specifications MIL-E-5400<br>MIL-E-4158, and MIL-E-16400. |  |  |

| voltages<br>required                          | 8 types:<br>-550V, -300V, -200V, -150V<br>+110V, +150V, +300V, +450V                                                                                                                                                                                                      | 3 types:<br>+15V, +5V, -5V                                                                                                                                                         |  |  |

| type                                          | Coincident current; parallel; random access.                                                                                                                                                                                                                              | Coincident current; parallel; random access.                                                                                                                                       |  |  |

# sems 5 severe environment military aerospace memory

electronic memories

## sems 5 military and aerospace memory

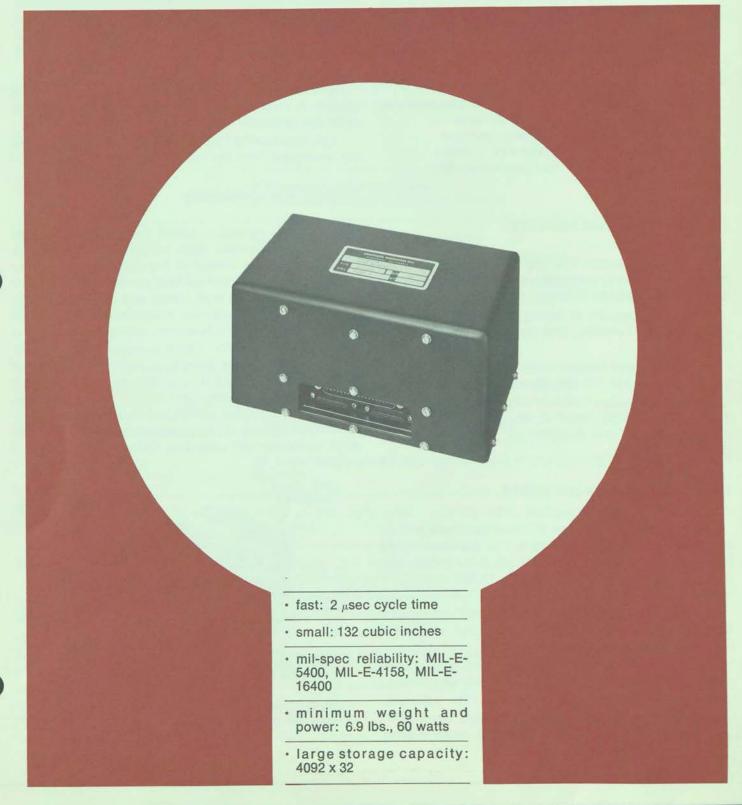

SEMS 5 (Severe Environment Memory System) is a very small, very fast militarized core memory. It is specifically designed for severe environment applications. Reliability, high speed, wide operating margins and minimum power, weight and size are optimally combined in a tightly packaged unit small enough to hold in one hand.

The system is a standard, production-line memory. It is now being delivered for tough airborne, missile, space, ship and ground applications. These include:

| satellites             | electronic countermeasures |

|------------------------|----------------------------|

| avionics               | display systems            |

| military land vehicles | guidance systems           |

| military aircraft      | navigation systems         |

| antisubmarine warfare  | airborne computers         |

| fire control systems   |                            |

### severe environment reliability

The ability of SEMS 5 to withstand severe vibration, shock, humidity and temperature extremes makes it the most rugged memory system available.

SEMS 5 is capable of taking 10 g's as defined by MIL-E-5400 of vibration, and has passed tests up to 30 g's.

It operates over temperatures ranging from 65 degrees below zero to 185 degrees above (-55 to  $+85^{\circ}$ C).

The unit meets applicable portions of military specifications MIL-E-5400, MIL-E-16400, and MIL-E-4158, for vibration, shock and humidity in aircraft, ship and ground applications.

### speed, storage, size and power

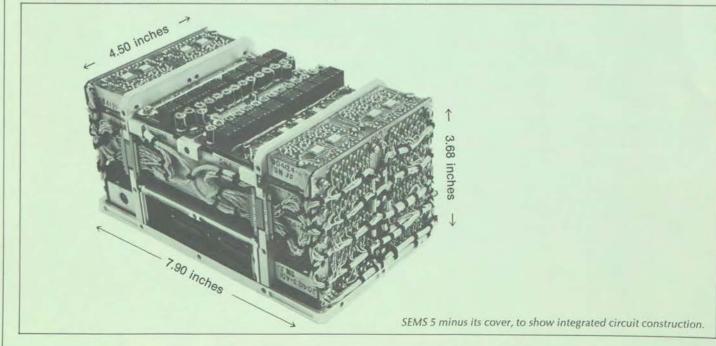

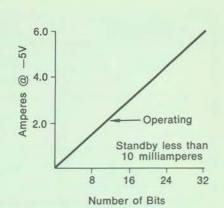

SEMS 5 has a cycle time of 2 microseconds and an access time of 600 nanoseconds. The standard SEMS 5 stores 4,096 words of 32 bits each. Optional storage capacities are available from 256 to 16,384 words of 8 to 32 bits long.

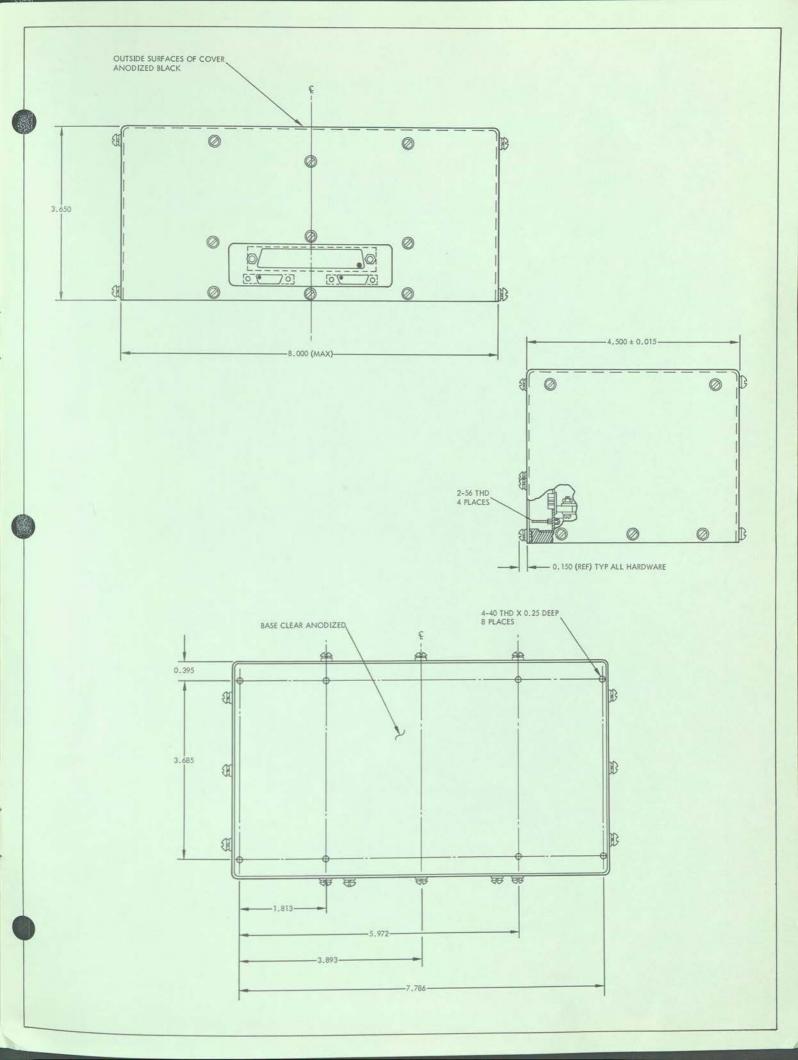

The standard SEMS 5 weighs 6.9 pounds. It measures 4.50 wide by 3.68 high by 8.0 inches long, and has a total volume of 132 cubic inches.

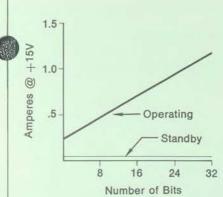

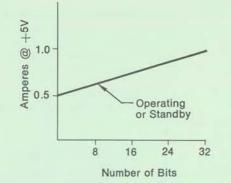

Power consumption is less than 60 watts at maximum worst case dissipation, and only 6 watts on standby.

Voltage requirements are minimal: +15V, +5V, and -5V. Internal tantalum by-pass capacitors store sufficient energy to complete a full memory cycle without fault in the event that supply current is interrupted at initiate time.

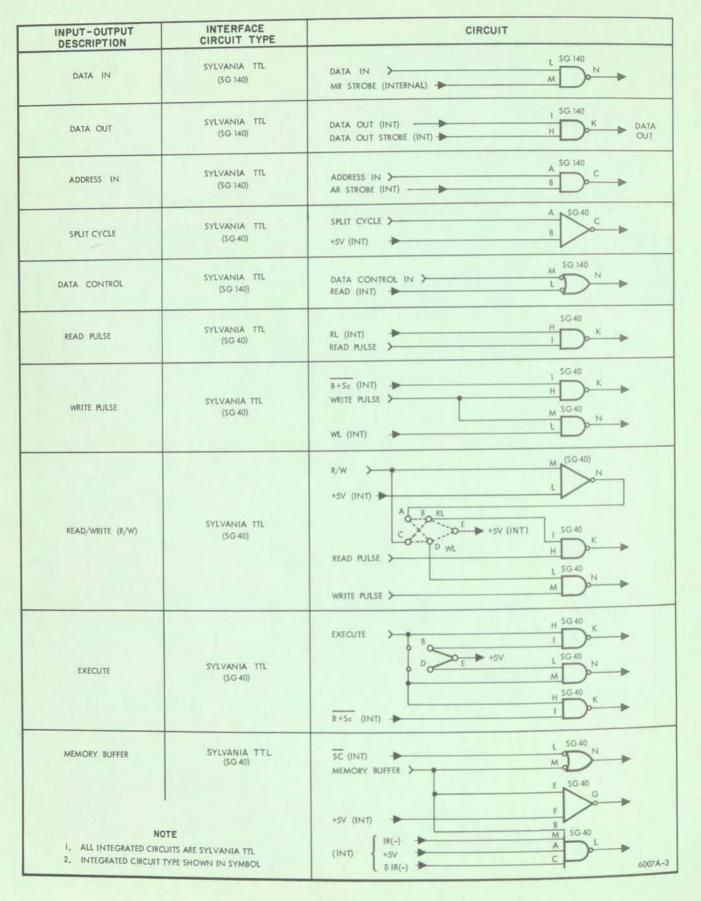

Except in the final drive switch stage and current stabilizers, integrated circuitry is used throughout the system, in logic, sense amplifiers, address decoders, and data and address registers.

### operating modes

Both clear/write and read/restore are standard modes. A read/modify/write split cycle and a buffer cycle are optionally available.

Logic interface is TTL positive true. The input signals are measured from the leading edge of initiate.

### memory stack reliability

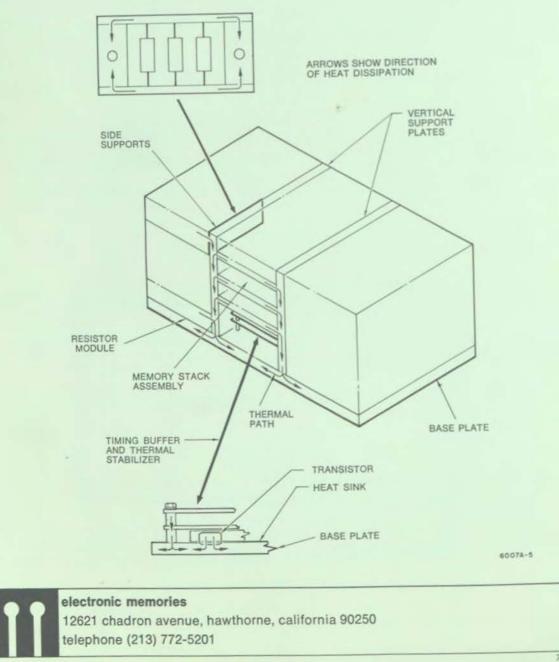

To increase reliability, SEMS 5 employs an unusual magnetic organization. Each coincident current plane contains eight bits instead of the usual one. Only three wires instead of the normal four are used, with a common line performing both sense and inhibit functions. This organization eliminates a significantly large number of electrical interconnections, which are a common source of memory stack failure.

A proprietary stack technique provides exceptional thermal characteristics. It minimizes accessory cooling equipment by dissipating heat through built-in conduction cooling. Because conduction cooling allows components to operate at comparatively cool temperatures, stack reliability and operating life are enhanced.

### options

Power supplies and a memory exerciser are optionally available. Split (read/modify/write) and buffer cycles, and extended or reduced storage capacities are also available.

SEMS 5 can be modified to meet specialized operat- interface circuitry can be provided.

ing environments, unusual storage specifications, or other requirements. In the past systems have been built to operate during 2,000 g's of shock for one millisecond and 27 g's of random vibration. Capacities have been extended to a 40-bit word length, and telemetry link interface circuitry can be provided.

## SPECIFICATIONS

| Speed                                     | 600 nanosecond access time<br>2 microsecond cycle time (2.1 split cycle)                            |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Storage Capacity                          | 4,096 words of 32 bits each, standard.                                                              |

|                                           | 256 to 16,384 words from 8 to 32 bits each, optional.                                               |

| Shock, Vibration &<br>Humidity Resistance | Meets applicable portions of MIL-E-5400, MIL-E-4158, and MIL-E-16400.<br>Also MIL-Q-9858.           |

| Operating Temperature Range               | -55°C to +85°C (Base Plate)                                                                         |

| Volume & Dimensions                       | 132 cubic inches, 4.50 x 3.68 x 8.00 inches.                                                        |

| Weight                                    | 6.9 pounds. (4,096 words x 32 bit capacity)                                                         |

| Power Consumption                         | 60 watts maximum all zero pattern at 2 microseconds cycle time, 6 watts standby.                    |

| Voltage Requirement                       | $\pm$ 5%, $\pm$ 5%, $\pm$ 5%, $-5V$ dc $\pm$ 2%. Voltages may be applied in any sequence.           |

| Operating Modes                           | Clear/write and read/restore, standard. Split cycle (read/modify/write) and buffer cycle, optional. |

| Input/Output Signal Levels                | TTL logic positive true (Sylvania SUHL)                                                             |

| Input Signal<br>Access                    | Memory access is by initiate and read/write mode lines, or by separate read and write pulse inputs. |

| Optional Equipment                        | Power supplies<br>Memory exerciser                                                                  |

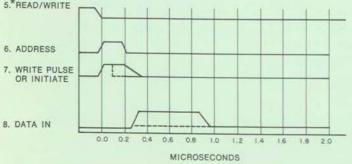

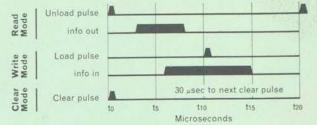

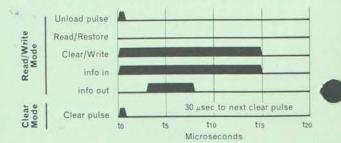

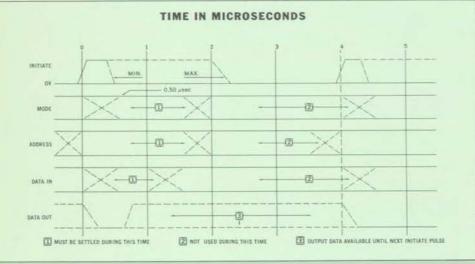

# mode timing

| Read/write control                                                                         | Must be stable at time 0.0 and remain so until initiate returns to 0 volt leve                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                                                                                    | Must be stable from time 0.0 to 0.2 microsecond.                                                                                                                                                                                                                                                                                                    |

| Initiate (read and write)                                                                  | 0.1 minimum microsecond, 0.2 maximum microsecond duration.                                                                                                                                                                                                                                                                                          |

| Data Out                                                                                   | Access time 0.6 microsecond.                                                                                                                                                                                                                                                                                                                        |

| Data In                                                                                    | Must be stable from 0.3 to 0.85 microsecond.                                                                                                                                                                                                                                                                                                        |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |

| Split Cycle-Write                                                                          | Pulse duration time can occur any time after time 0.0 to 0.7 microsecon<br>Next read pulse cannot occur sooner than 1.4 microseconds after leadir<br>edge of write pulse. Minimum full split cycle time is 2.1 microseconds.                                                                                                                        |