-RC

# 2075 Processing Unit -- Volume 1

0000000

000000

Comprehensive Introduction Functional Units Form 223-2872-1 FES \$26-7033

#### PREFACE

This is one of six Field Engineering manuals for the 2075 Processing Unit. These six manuals contain the unit theory of operation, reference diagrams to be used when troubleshooting, and maintenance procedures.

A basic knowledge of the IBM System/360 contained in the IBM System/360 Principles of Operation, Form A22-6821 is considered a prerequisite for studying the unit theory of operation. The theory of operation is contained in a four volume manual identified as a Field Engineering Manual of Instruction (FEMI). Volume 1 is a prerequisite for the detailed information contained in volumes 2, 3, and 4. Volume 1 contains the introduction to the system and the processing unit and a description of the functional units (registers, adders, and decoders) of the processing unit. Volumes 2 and 3 contain detailed information on special features and power supplies and control.

The four volumes of theory of operation contain many references to the diagrams packaged in the associated Field Engineering Diagrams Manual (FEDM). All diagrams in the FEDM are identified by a four digit figure number and unless otherwise specified, all four digit figure references in the FEMI indicate that the figure is contained in the associated FEDM.

The complete titles and form numbers of the six 2075 Field Engineering Manuals are:

- 2075 Processing Unit--Volume 1, Comprehensive Introduction, Functional Units, Field Engineering Manual of Instruction, Form 223-2872

- 2075 Processing Unit--Volume 2, Theory of Operation: Storage Bus Control; Instruction Preparation; FLT, Logout, MCW; Interrupts, Field Engineering Manual of Instruction, Form 223-2873

- 2075 Processing Unit--Volume 3, Theory of Operation: Fixed Point, I Execute, Branch, Floating Point, Variable Field Length, Field Engineering Manual of Instruction, Form 223-2874

- 2075 Processing Unit--Volume 4, Special Features, Power Supply and Control, Appendix, Field Engineering Manual of Instruction, Form 223-2875

- 2075 Processing Unit, Field Engineering Diagrams Manual, Form 223-2876

- 2075 Processing Unit, Field Engineering Maintenance Manual, Form 223-2880

MAJOR REVISION (December 1965)

This edition, Form 223-2872-1, obsoletes Form 223-2872-0. The major change is the addition of Figures 10 and 63.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Systems Development Division, Product Publications, Dept. 520, CPO Box 120, Kingston, N. Y. 12401

# CONTENTS

| COMP   | REHEN    | ISIVE   | INT      | ROL   | DUC  | TIC  | ON    |      |      |      |      |     |      |       |      |    |

|--------|----------|---------|----------|-------|------|------|-------|------|------|------|------|-----|------|-------|------|----|

|        |          |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

| Systen | ns Intro | duct    | ion ,    | • •   | •    | •    | •     | ٠    | •    | •    | •    | •   | •    | •     | •    | •  |

| 207    | 75 Proc  | essor   | Unit     |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | I-Unit   |         |          |       |      |      |       |      |      |      |      |     |      |       |      | 1, |

|        | E-Unit   |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | 5 Proc   |         |          |       |      |      |       |      |      |      | ٠    |     |      |       |      |    |

| 236    | 51 Larg  | e Ca    | pacit    | y St  | ora  | ge   |       |      |      |      |      |     |      |       |      | 1  |

|        | ut/Out   |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | Execut   | ion o   | of Ch    | anne  | ls I | rog  | ran   | ns   | •    |      |      |     |      |       |      | ŝ  |

|        | Comm     | unica   | ation    | s Bet | we   | en ( | CPL   | Jai  | nd   | Cha  | nne  | els |      |       |      | 1, |

| 286    | 50 Sele  | ctor    | Char     | mel   |      |      |       |      |      |      |      |     |      | *     | *    |    |

|        | Channe   | el Op   | perati   | ion   |      |      |       |      |      |      |      |     |      |       |      | ş  |

|        | Channe   | el Int  | terruj   | pts   |      |      |       |      |      |      |      |     |      |       |      |    |

|        | Initial  | Prog    | ram      | Load  | ۱.   |      |       |      |      |      |      |     |      |       |      | ÷, |

|        | Option   |         |          |       |      |      |       |      |      |      |      |     |      |       |      | 1  |

|        | ltisyste |         |          |       |      |      |       |      |      |      |      |     |      |       |      | 1  |

| 2075 1 | Processi | ing U   | Jnit I   | ntro  | duc  | tior | 1     |      |      |      |      | •   |      | •     |      | l, |

|        |          |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | tems C   |         |          |       | •    |      |       |      |      |      |      |     |      |       |      |    |

|        | ntral P  |         |          |       |      |      |       |      |      |      | ٠    | ٠   |      |       |      | ,  |

|        | Instruc  |         |          |       |      |      |       |      | •    | ٠    | ٠    | ٠   |      |       | •    | 1  |

|        | Bus Co   |         |          |       |      | ٠    |       |      | •    |      |      | ٠   | •    |       | ٠    | 1  |

|        | System   |         |          |       |      | ٠    | ٠     | •    |      | ٠    |      |     | ٠    | •     |      | 1  |

|        | Machin   |         |          |       |      |      |       |      | ٠    |      | •    | ٠   | ٠    |       |      |    |

|        | Fault I  |         |          |       |      |      |       |      |      |      |      | •   |      |       |      | 1  |

|        | Interru  | pts     | •        | • •   | ٠    | •    | ٠     |      | •    |      |      | ٠   | ٠    |       |      |    |

|        | Trigge   |         |          |       |      |      |       |      |      |      |      | •   |      |       |      |    |

|        | Specia   | 1 Ret   | tenti    | on D  | evi  | ces  | •     |      |      |      |      | •   |      |       |      |    |

|        | Sequer   |         |          |       |      |      |       |      |      | ٠    | ٠    | ٠   | ٠    |       | ٠    |    |

| Ma     | ijor Un  |         |          |       |      |      |       |      |      |      |      |     |      |       | •    | 1  |

|        | Instruc  |         |          |       |      |      |       |      |      |      | •    |     |      |       |      | ŝ  |

|        | Op Re    |         |          |       |      |      |       |      |      |      |      | ٠   | ٠    | ٠     |      |    |

|        | ICR U    |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | Result   | Stor    | ing      |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | Instruc  | nion    | Exec     | utio  | n E  | can  | iple  | 25   |      |      |      |     |      |       |      |    |

| Pu     | rpose o  | f CPI   | U Fu     | actic | nal  | Un   | its   |      |      |      |      |     |      |       |      |    |

|        | Purpos   | e of    | BCU      | Fund  | ctio | nal  | Un    | its  |      |      |      |     |      |       |      |    |

|        | Purpos   |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | Purpos   |         |          |       |      |      |       |      |      |      |      |     |      |       |      |    |

|        | Purpos   |         |          |       |      |      |       |      |      |      |      |     |      | •     |      |    |

| FUNC   | TIONA    | LUN     | NITS     |       |      |      | •     | •    |      | •    |      |     |      | •     | •    |    |

| Ad     | ders     | 13 1120 | -        |       |      | 2    | 0:27  | 224  |      |      | 12   | 2   | 1.02 | 620   | -    |    |

| Au     | Addres   | seine   | •<br>Add | * *   | •    | •    | •     | •    | .*   |      |      | •   | •    | •     |      |    |

|        | AND-     | OPT     | Nalo     | eisee | OP   | •    | •     | •    | •    | •    | •    | •   | •    | •     | •    |    |

|        |          |         | لللك     | arve  | OR   | ٠    | ٠     | ٠    |      |      | ٠    |     |      | ٠     | ٠    |    |

|        | Decim    | al A    | dder     |       |      | 1.1  | 1.024 | 1000 | 1.00 | 1.12 | 12.5 | 100 | 0.20 | 11210 | 1751 |    |

5

5

11

11

11

19

19

21

22

23

24

25

28

30

30

30

35

35

38

38

40

44

44

45

46

47

48

48

50

50

54

56

60

64

69

69

72

73

75

77

77

77 78 78

82

0000000000

0000

| Gate Select Adder                    |       |    |   |   |    | 85   |

|--------------------------------------|-------|----|---|---|----|------|

| Incrementer Adder                    |       |    |   |   |    | 85   |

| Main Adder-Shifter                   |       |    |   |   |    | 87   |

| Clock                                |       |    |   |   |    | 92   |

| Controlled Clock, Running Clock      |       |    |   |   |    | 92   |

| Counters and Pointers                |       |    |   |   |    | 93   |

| Digit Buffer-Digit Counter           |       |    |   |   |    | 93   |

| S and T Pointers                     |       |    |   |   |    | 95   |

| Y and Z Counters                     |       |    |   |   |    | 99   |

| Decoders                             |       |    | 1 | 1 |    | 104  |

| BOP Decoder                          |       |    |   | - |    | 104  |

| BR1 Field Decoder                    |       |    |   | 1 | -  | 104  |

| Channel Decoder                      |       |    |   |   | •  | 104  |

| Divide Decoder                       |       |    |   | 1 |    | 104  |

| Ran D 1                              |       |    |   |   | •  | 105  |

| EOP Decoder ER1 Field Decoder        | •     | •  |   | • |    | 105  |

| IOP Decoder                          | •     | •  | • |   | •  | 105  |

| 10000                                | •     | ٠  |   |   | •  | 105  |

| Multiply Decoder .                   |       | •  | • |   | •  | 105  |

|                                      | *     | •  |   | * | •  | 105  |

| ATTEN.                               |       |    |   | • | •  | 106  |

|                                      | •     | •  | • | • | •  | 106  |

| V OD                                 | •     | ٠  |   | • | •  | 2012 |

| Key OR<br>Mark OR                    | •     | ٠  |   | ٠ |    | 107  |

|                                      | •     | •  |   |   | •  | 107  |

| VFL Byte Gates-LBG and RBG           | •     | •/ | ٠ |   | ٠  | 107  |

| Registers and Buffers                |       |    | • |   |    | 109  |

| AB Registers.                        |       | •  | • |   | *  | 109  |

| BOP Register                         | 1     | ٠  |   | ٠ | ۰. | 109  |

| Direct Data Register                 |       | ٠  |   |   | ٠  | 110  |

| EOP Register                         |       |    |   | ٠ | ٠  | 110  |

| ER1 Register                         | 9.    | ٠  |   |   | •  | 110  |

| Exponent Register                    | J•    | ٠  | ٠ | ٠ | ٠  | 111  |

| Floating-Point Registers             |       | •  |   |   | ٠  | 111  |

| General Purpose Register             | ł.    |    |   |   | ٠  | 112  |

| H Register                           | 21    | ٠  | ٠ | ٠ | ٠  | 113  |

| IOP Register                         | 14    | ٠  | • | ٠ | *  | 114  |

| J Register                           |       |    |   |   | •  | 116  |

| K Register                           | 100   |    |   | ٠ | *  | 116  |

| Key Buffer Register                  | 3     | ٠  |   |   |    | 117  |

| L Register                           | 3     |    |   | • | •  | 117  |

| LCOP Register                        |       | ٠  |   |   | *  | 117  |

| M Register                           |       | •  |   |   | ٠  | 117  |

| Mark Register                        | and a |    |   |   | ٠  | 117  |

| Program Status Word                  | 1.00  |    |   |   | •  | 118  |

| Register Bus Latch                   |       | •  |   |   |    | 119  |

| Return Address Registers             |       |    |   | ٠ | ٠  | 120  |

| Storage Address Register (SAR)       |       |    |   |   |    | 121  |

| SAR Duplicate                        |       |    |   |   |    | 121  |

| Storage Bus In (SBI) Latch Register  |       |    |   |   |    | 122  |

| Storage Bus Out (SBO) Latch Register |       | •  |   |   | •  | 122  |

| Shift Counter Register • • • • •     |       |    |   |   |    | 122  |

# ILLUSTRATIONS

| unant mannin | REHENSIVE INTRODUCTION                         |    |   |                    | 30 | System/360 Model 75                             | <br>3 |

|--------------|------------------------------------------------|----|---|--------------------|----|-------------------------------------------------|-------|

| SYSTE        | MS INTRODUCTION                                |    |   |                    | 31 | Simultaneous Preparation and Execution          |       |

| 1            | Block Diagram of the Model 75                  |    |   | 5                  | 32 | Execution and Execution Sequencers              | <br>3 |

| 2            | IBM System/360 Model 75 CPU-Storage Systems    |    |   | 5                  | 33 | Simultaneous Instruction Fetching, Preparation, |       |

| 3            | Data Formats                                   |    |   | б                  |    | and Execution                                   | . 4   |

| 4            | Model 75 Information Relationships             |    |   | 6                  | 34 | Functional Sections of the 2075                 |       |

| 5            | Five Basic Instruction Formats                 |    |   | 8                  | 35 | I-Unit Fetch                                    |       |

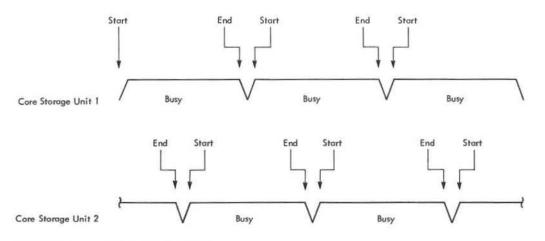

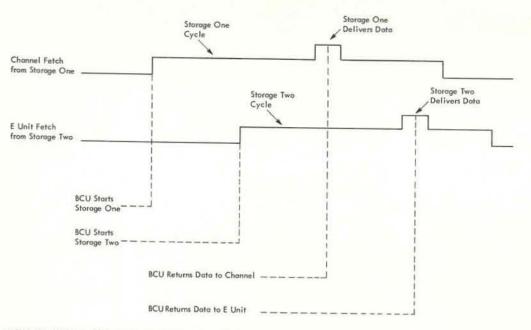

| 6            | Binary, Hexadecimal, Decimal Equivalents .     |    |   | 8                  | 36 | Overlapped Storage Cycles                       |       |

| 7            | Input/Output Channel (Input) Operation         |    |   | 10                 | 37 | Returning Data with Overlapped Storages         |       |

| 8            | Input/Output Channel (Output) Operation        |    |   |                    | 38 | Model 75 Main Storage                           |       |

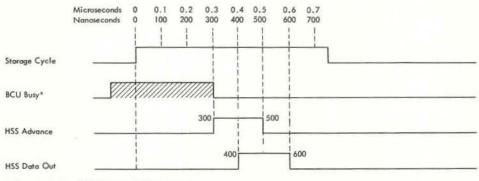

| 9            | Clock Pulse Relationships                      |    |   |                    | 39 | HSS Cycle                                       |       |

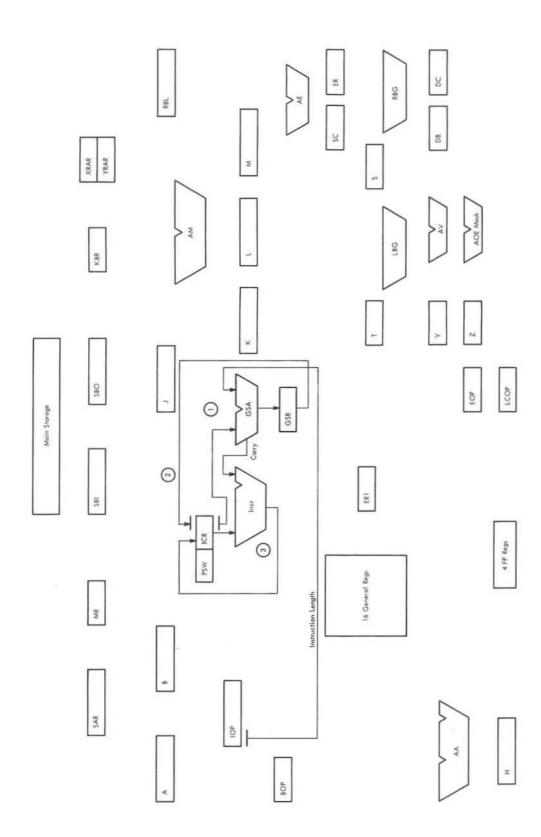

| 10           | Simplified E-Unit Data Flow                    |    |   |                    | 40 | CPU Machine Cycle                               |       |

| 11           | PSW Format                                     |    |   |                    | 41 | AND-OR-Invert                                   |       |

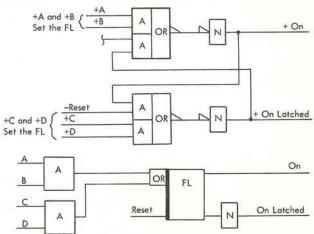

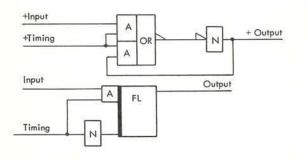

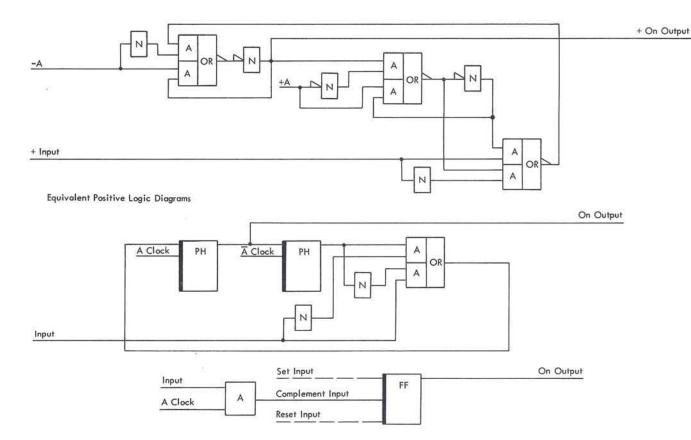

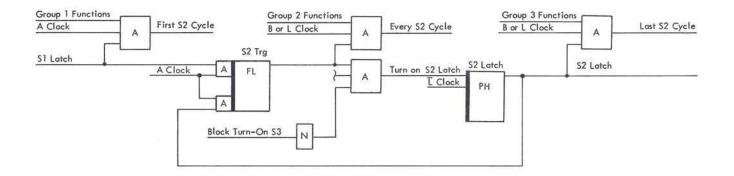

| 12           | Permanent Storage Assignments                  |    |   |                    | 42 | Flip Latch                                      |       |

| 13           | Simplified Core Storage Operation              |    |   |                    | 43 | Polarity Hold                                   |       |

| 14           | Basic Core Storage Operation                   |    |   | 20                 | 44 | Example of PH Use                               |       |

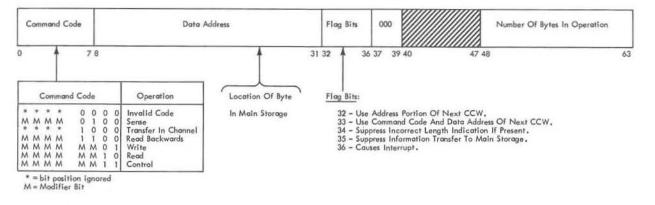

| 15           | Channel Address Word                           |    |   | 26                 | 45 | PH Register Positions                           |       |

| 16           | Channel Command Word                           |    |   | 26                 | 46 | Retention Device Variations                     |       |

| 17           | Channel Status Word                            |    |   |                    | 47 | FL's Used to Alter Signal Timing                |       |

| 18           | I/O Instructions and Condition Codes           |    |   |                    | 48 | 2075 Flip-Flop                                  |       |

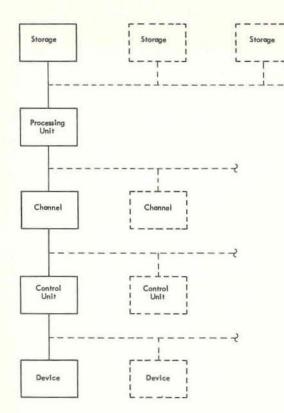

| 19           | Functional Structure of a Basic System         |    |   |                    | 49 | Sequencers and Sequencer Cycles                 |       |

| 20           | Functional Structure of a Channel-to-Channel   | ÷. | 2 |                    | 50 | Major CPU Functional Units                      |       |

|              | Multisystem                                    |    |   | 33                 | 51 | IC Fetch                                        |       |

| 21           | Transmission Control Units as Multisystem      |    |   |                    | 52 | Op Register Loading                             |       |

| 1000         | Connectors                                     |    |   | 33                 | 53 | ICR Updating.                                   |       |

| 22           | Shared Control Units as Multisystem Connectors |    |   |                    | 54 | RX Operand Fetch                                |       |

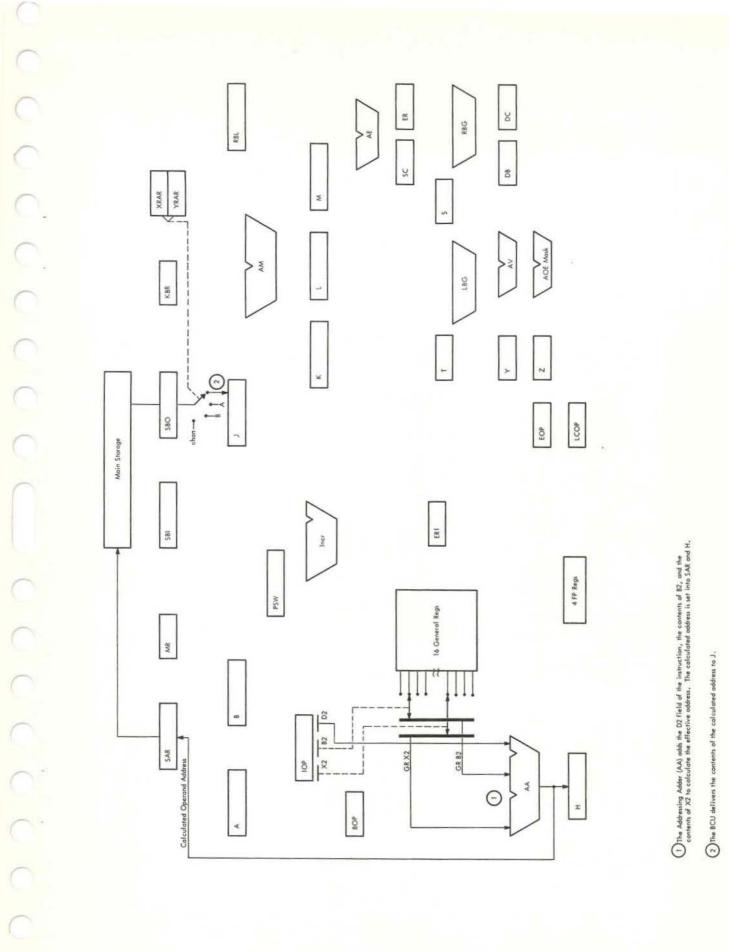

| 23           | Shared Device as Multisystem Connector         |    |   |                    | 55 | Register Operand Delivery                       |       |

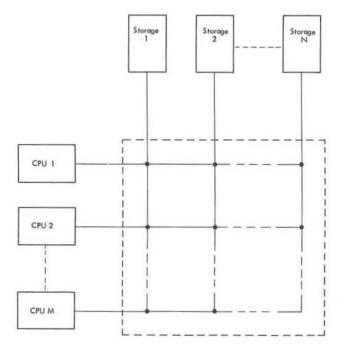

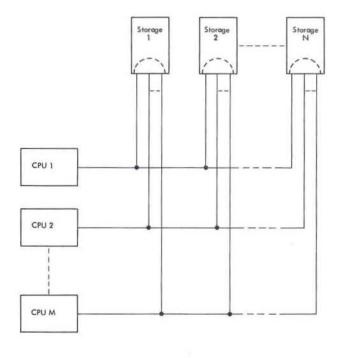

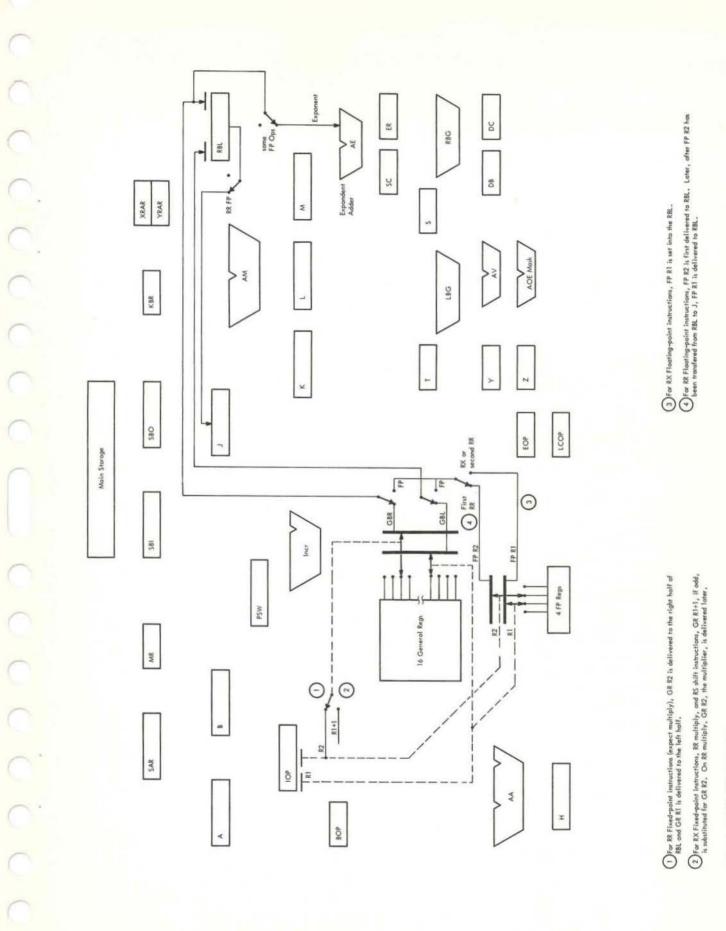

| 24           | Shared Storage as Multisystem Connector        |    |   |                    | 56 | Register Put-Aways                              |       |

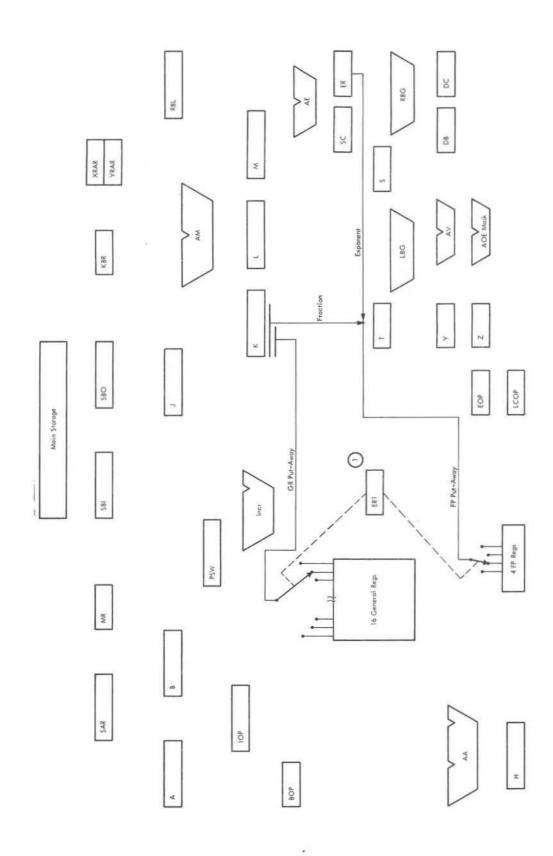

| 25           | Centralized Crossbar Switch Representation .   |    |   |                    | 57 | Operand Store                                   |       |

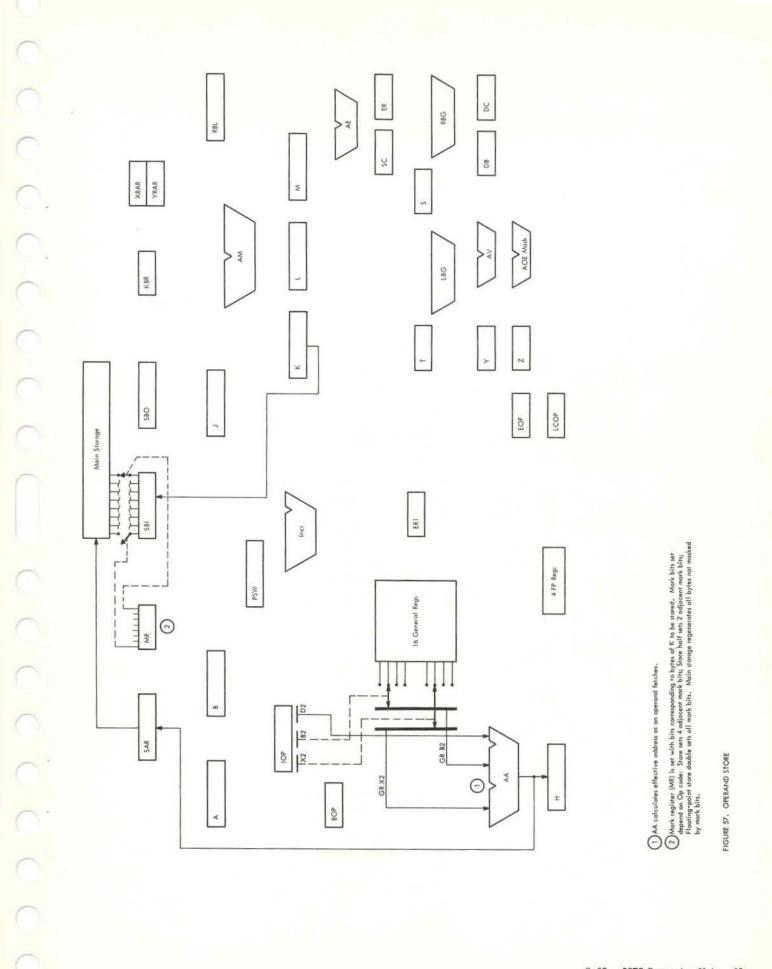

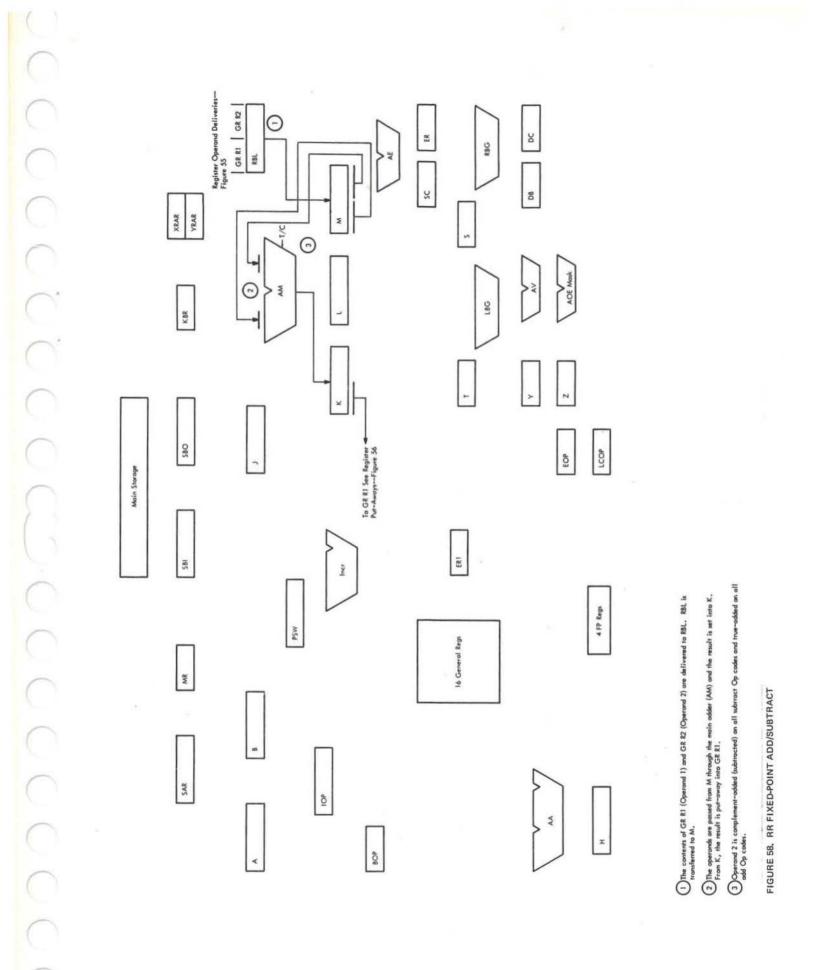

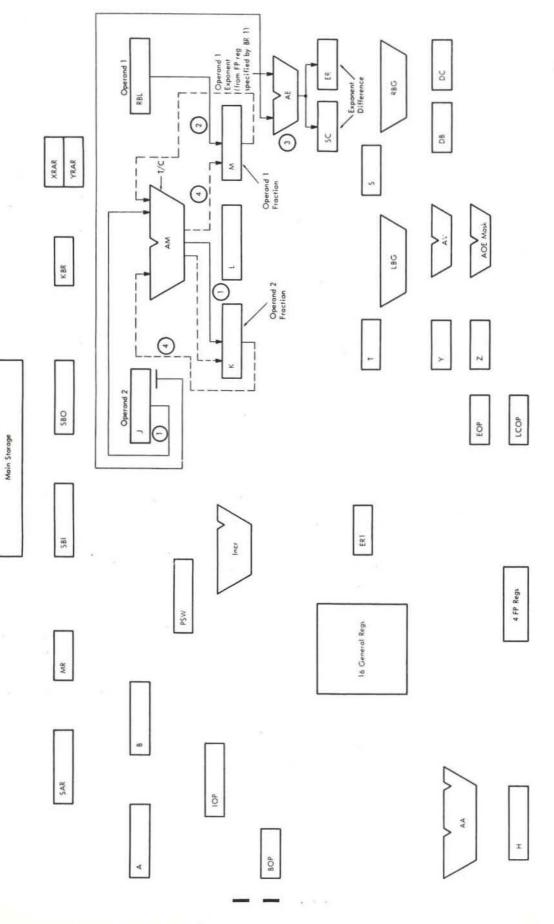

| 26           | Distributed Crossbar Switch Representation .   |    |   |                    | 58 | RR Fixed-Point Add/Subtract                     |       |

| 20           | produced crowell ender representation          |    | 1 | and a state of the | 59 | Basic Floating-Point Exponent Equalization .    |       |

|              |                                                |    |   |                    | 60 | Basic Floating-Point Add/Subtract               |       |

| 2075 5       | ROCESSING UNIT INTRODUCTION                    |    |   |                    | 61 | Basic VFL Add/Subtract Set-Up                   |       |

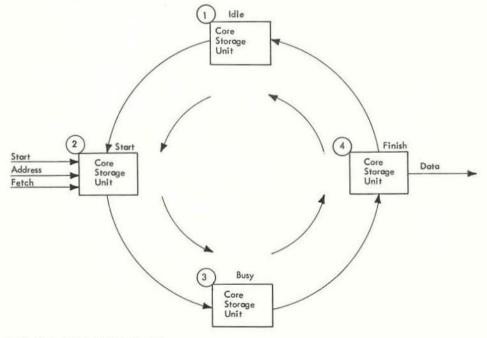

| 2075 P       | Core Storage Cycle                             |    |   | 35                 | 62 | Basic VFL Add/Subtract Iterations               |       |

| 28           | Model 75 Working Areas                         |    |   |                    | 63 | Main Adder-Shifter: Functions, Data Paths, and  |       |

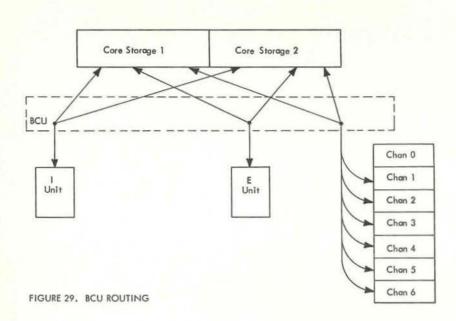

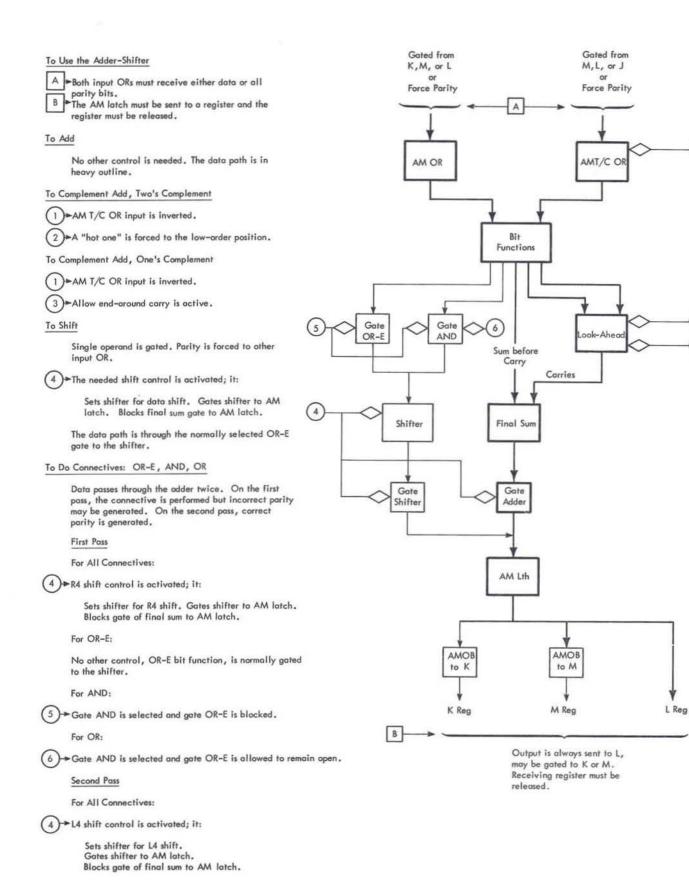

| 28           | BCU Routing                                    |    |   |                    | 00 | Control Scheme                                  | . 8   |

# COMPREHENSIVE INTRODUCTION

# SYSTEMS INTRODUCTION

- The processor is a number of independent units.

- CPU and core storage are integrated units.

- Overlapped cycles between four storage units increase the access speed.

- Each byte in processor storage is addressable.

- Data flow consists of 64 data bits and 8 parity bits in parallel.

- Operands are primarily based on the hexadecimal system.

- Instruction formats use both long and short data formats.

- Instruction cycles, execution cycles, and I/O operations may take place simultaneously.

- Cycle time is dependent upon the speed of the registers and logic.

- A high degree of reliability is obtained through fault location tests, parity checking, and logout.

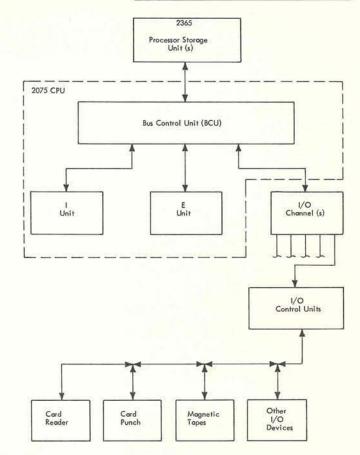

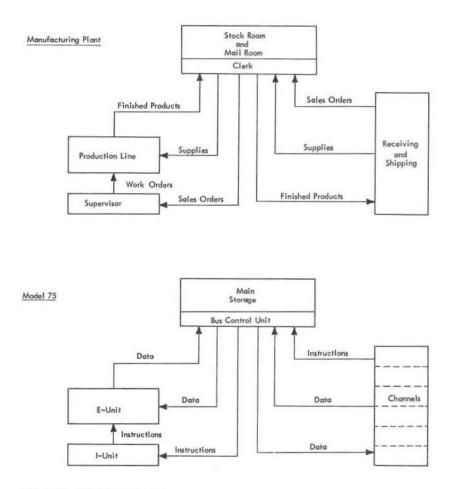

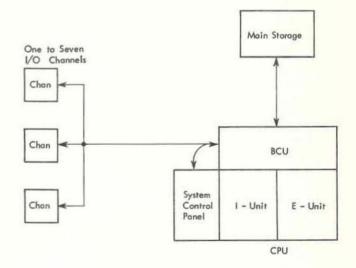

The IBM System/360 Model 75 fills the need for a data processing system with high-speed operation, a versatile instruction set, large core storage capacity, and input/output capabilities for a wide range of applications. The Model 75 basic system (Figure 1) consists of a number of independent sections: the IBM 2365 Processor Storage, IBM 2075 Processing Unit and Bus Control Unit, IBM 2860 Selector Channel, and associated control units and input/output devices.

The functional organization of the central processing unit is equivalent to that of any other IBM System/360; however, its higher performance is attributed to the following:

1. The storage word consists of eight bytes (64 data bits and 8 parity bits).

2. It uses a three input addressing adder capable of handling 24 bits in parallel.

3. Double word floating-point operations as well as single word and fixed-point arithmetic instructions are performed in parallel.

4. Instruction requests from core storage are overlapped with the execution cycle of the current instruction.

FIGURE 1. BLOCK DIAGRAM OF THE MODEL 75

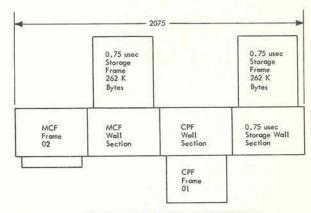

The basic system consists of the Model 75 central processing unit and one 0.75-microsecond processor storage unit installed as a single integrated frame. In another configuration of processor storage, shown in Figure 2, the 2075 central

FIGURE 2. IBM SYSTEM/360, MODEL 75 CPU - STORAGE SYSTEMS

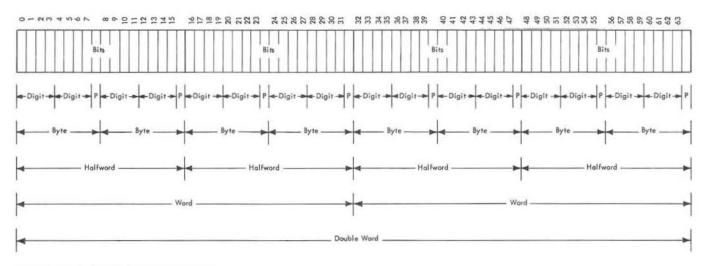

FIGURE 3. DATA FORMATS

FIGURE 4. MODEL 75 INFORMATION RELATIONSHIPS

6 9-65

processing unit consists of a wall used to house the power conversion equipment and cables, the maintenance control frame (in line with the wall), the central processing frame (right angle to the wall), and the 2365 Processor Storage Units (right angle to the wall).

Overlapped cycles between two storage units increase the access speed. Addresses are staggered in the two units, and a series of requests for successive double words activates the two units alternately, thus doubling the maximum rate.

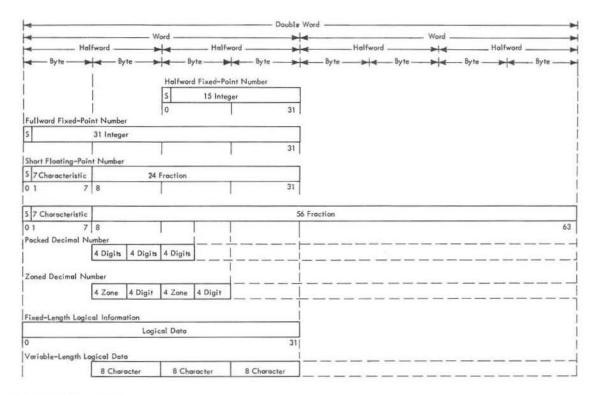

Each byte in the processor storage is individually addressable with a 24-bit binary address; however, instructions concerned with word boundaries must be addressed as such or error conditions result. The location of a stored field is specified by the address of the left-most byte of the field. Variable length fields may start on any byte location, but a fixed length field of two, four, or eight bytes must have an address that is a multiple of two, four, or eight, respectively. Some of the various alignment possibilities are shown in Figure 3.

The Model 75 data flow among the working registers, addressable registers, processor storage, AB registers, and main adder consists of 64 data bits and 8 parity bits in parallel. The working registers (J, K, L, and M) are not addressable but they play an important part in the overall operation of the Model 75 because they function as an intermediate storage for operands, partial products, factors, and multiples during instruction execution. At the completion of an instruction, the intermediate data in the working registers are transferred to storage, a floating-point register or a general register. If the data in the working registers are not stored by the end of the operation, the data are lost when the next instruction is executed.

The addressable registers are the 4 floatingpoint registers and the 16 general registers. Each register is addressable by a 4-bit binary address. In some operations an even-odd address pair of registers are used for addressing purposes. The floating-point registers are always addressed by their even address because they are double words. The general registers contain operands and indexes; the floating-point registers contain operands.

The AB registers hold prefetched instructions from the processor storage. These registers may obtain instructions directly from the storage bus out latch register or via the J register from the storage bus out latch register. From the AB register, the prefetched instructions are gated to the instruction decoders.

Operands are primarily based on the hexadecimal system. Four bits equal one digit; therefore, the value 0000 through 1111 in binary is possible. The binary, hexadecimal, decimal equivalents are shown in Figure 6. Some of the terms used in Model 75 work are as follows(Figure 4):

1. <u>Bit</u>: A bit is a single unit of information; its value is either a 0 or a 1.

2. <u>Digit</u>: A digit consists of four bits, in any combination of bits from binary 0000 through binary 1111.

3. Byte: A byte is two digits plus one parity bit. In most cases, when a byte is mentioned, the main concern is with the eight data bits. The parity bit is assumed to be transferred on the main data paths throughout the system, and it is used for valid byte detection throughout the system. Parity in the 2075 processing unit is odd.

4. <u>Halfword:</u> A halfword is 2 bytes, 4 digits, or 16 data bits plus 2 parity bits.

5. Word: A word, sometimes referred to as a full word, is two halfwords or 32 data bits plus 4 parity bits.

6. <u>Double word</u>: A double word, sometimes referred to as a core storage word, is two words or 64 data bits plus 8 parity bits.

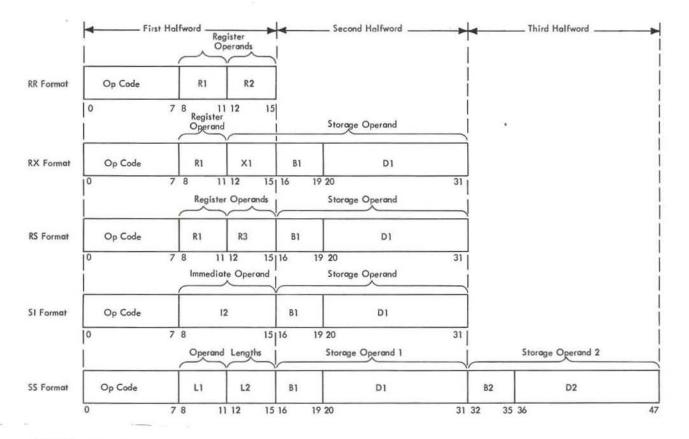

The Model 75 uses several instruction and data formats. Included in the standard instruction formats are the RR (register-to-register), RS (register and storage), RX (register and indexed storage operation), SI (storage and immediate operand), and SS (storage-to-storage) formats shown in Figure 5. In each format, the first instruction halfword consists of two parts: the first byte contains the operation code, and the second byte is either two 4-bit fields or one 8-bit field.

The length and format of an instruction are indicated by the first two digits of the operation code as follows:

- 00 RR format

- 01 RX format

- 10 RS and SI formats

- 11 SS format

The second byte is specified from among the following:

1. Four-bit operand register designators (R1, R2, and R3).

2. Four-bit index register designator (X2).

3. Four-bit mask (M1).

4. Four-bit field length specification (L1 or L2).

5. Eight-bit field length specification (L).

6. Eight-bit byte of intermediate data (I2).

The second and third halfwords each specify a 4-bit base register designator (B), followed by a 12-bit displacement (D). An effective storage address (E) is a 24-bit binary integer given, in the typical case, by

$\mathbf{E} = \mathbf{B} + \mathbf{X} + \mathbf{D}$

where B and X are 24-bit integers from general registers identified by fields B and X, respectively,

FIGURE 5. FIVE BASIC INSTRUCTION FORMATS

and the displacement (D) is a 12-bit integer contained in every instruction that references storage.

The base (B) can be used for static relocation of programs and data. In record processing, the base can identify a record; in array calculations, it can specify the location of an array. The index (X) can provide the relative address of an element

| Binary | Hexadecimal | Decimal |

|--------|-------------|---------|

| 0000   | 0           | 0       |

| 0001   | 1           | 1       |

| 0010   | 2           | 2       |

| 0011   | 2<br>3      | 2 3     |

| 0100   |             |         |

| 0101   | 4           | 4       |

| 0110   |             | 6       |

| 0111   | 6<br>7<br>8 | 6<br>7  |

| 1000   | 8           | 8       |

| 1001   | 9           | 9       |

| 1010   | A           | 10      |

| 1011   | В           | 11      |

| 1100   | C           | 12      |

| 1101   |             | 13      |

| 1110   | D<br>E<br>F | 14      |

| 1111   | F           | 15      |

within an array. Together, B and X permit double indexing in array processing.

The displacement provides for relative addressing of up to 4095 bytes beyond the element or base address. In array calculations, the displacement can identify one of many items associated with an element. Thus, multiple arrays whose indices move together are best stored in an interleaved manner. In the processing of records, the displacement can identify items within a record.

In forming an effective address, the base and index are treated as unsigned 24-bit positive binary integers and the displacement as a 12-bit positive binary integer. The three are added as a 24-bit binary number, ignoring overflow. Since every address is formed with the aid of a base address, programs are readily relocated by changing the contents of base registers.

A zero base or index designator implies that a zero quantity must be used in forming the address, regardless of the contents of general register 0. A displacement of zero has no special significance. Initialization, modification, and testing of bases and indices can be carried out by fixed-point instructions, by branch and link, branch on count, or branch on index instructions. Load effective address provides not only a convenient housekeeping operation, but alos, when the same register is specified for result and operand, an immediate register-incrementing operation.

Several data formats are shown in Figure 3. An 8-bit unit of information (the byte) is fundamental to most of the formats. A consecutive group of N such units constitutes a field of length N. Fixed-length fields of length one, two, four, and eight are termed bytes, halfwords, words, and double words, respectively. In many instructions, the operation code implies one of these four fields as the length of the operands. On the other hand, the length is explicit in an instruction that refers to operands of variable length.

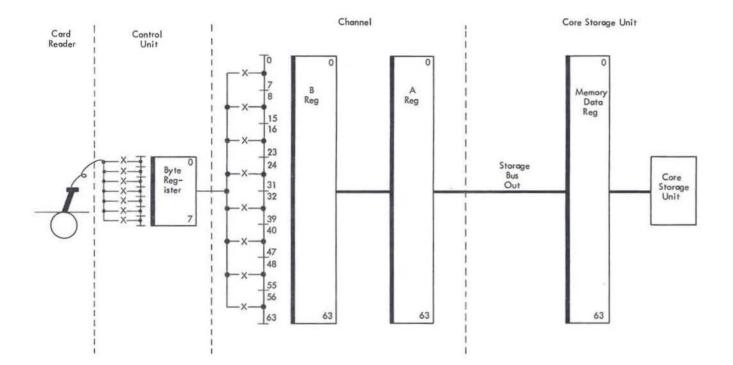

Data are entered into the Model 75 system through input/output devices attached to the input/ output selector channel via control units. Figure 7 shows a block diagram of data input from the card reader. The data sensed at the brushes in the card reader are assembled into bytes in the control unit. Once a byte is assembled, it is transferred to the B register in the selector channel. In the selector channel, the bytes are assembled into double words. When the B register contains an assembled word, it is transferred to the A register. A new double word is assembled in the B register while the double word in the A register is transferred to the memory data register in the core storage unit. Once the data are placed in the memory data register, they are written into the specified address in the core array.

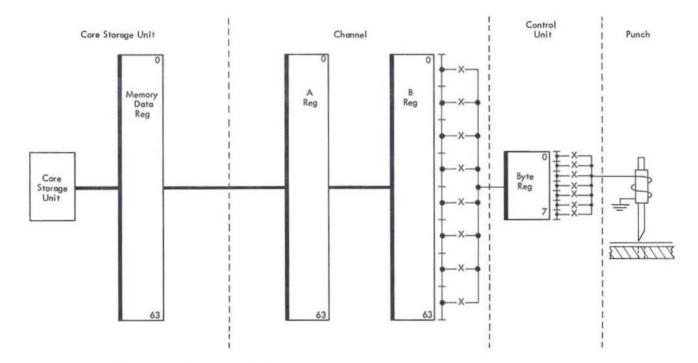

An output operation (Figure 8) is the opposite of an input operation. The data are read from the specified address into the memory data register. From the memory data register, the data are transferred to the A register in the selector channel. When the B register has transferred the last byte of data of the previous core storage word to the byte register in the control unit, the transfer from the A register to the B register occurs. The data, in the B register, are disassembled into bytes for transmission to the byte register in the control unit. From the byte register in the control unit, the byte is disassembled into bits and punched into the card.

Although this is a general description of an input/output operation involving the selector channel, input/output control unit, and a card read/ punch, all input/output operations are basically the same whether they are slow-speed devices such as telecommunication equipment or high-speed devices such as hypertape units; input/output operations, instruction cycles, and execution cycles may take place simultaneously for maximum processing speed.

The fundamental determinant of the central processing unit speed is the time required to take data from the internal registers, process the data through the adder or other logical unit, and return the result to a register. This cycle time is determined by the delay per logical circuit level and the number of levels in the register-to-adder path, the adder, and the adder-to-register return path.

The Model 75 processor has a 64-bit parallel data flow with parity checking on each 8-bit byte. The parity checked main adder operates on a basic cycle time of 200 nanoseconds (0 2 microseconds), and the nominal delay per logic level in the Model 75 is 6 nanoseconds. The basic time cycle of the Model 75 is 200 nanoseconds.

The speed of the central processing unit also depends on the speed of the general registers and the floating-point registers. The general and floatingpoint registers are implemented with 6-nanosecond logic circuits and communicate directly with the adder and other data paths.

The two principal measures of size in the central processing unit are the width of the data paths and the number of bytes of high-speed working registers. The Model 75 has a 64-bit (data) main adder, an 8-bit exponent adder, an 8 bit decimal adder, a 24bit addressing adder, and several other data transfer paths, some of which have incrementing ability. In addition to the 16 general purpose registers, there are 4 floating-point registers, 6 working registers, and a 64-bit program status word register.

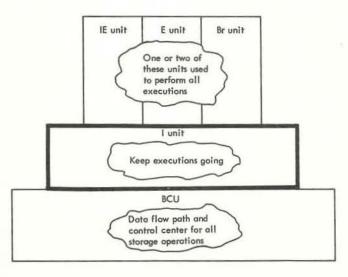

In the Model 75, many operations can take place at the same time. The central processing unit is divided into three units that operate somewhat independently. The instruction preparation unit (I unit) requests instructions from main storage, prepares them by computing their effective address, and initiates the request for the required data. The execution unit (E unit) performs the execution of the instruction prepared by the instruction unit. The third unit, the storage bus control unit (BCU), coordinates the various requests by the other units and by the channels for core storage cycles. All three units normally operate simultaneously, and together they provide a large degree of instruction overlap. Since each of the units contains a number of different data paths, several data transfers may occur during any one single cycle in a single unit.

Standard features of the Model 75 include single and double word floating-point arithmetic, fixedpoint arithmetic, decimal arithmetic, variable field length (VFL) operations, logical and masking operations, storage protection, interval timer, direct control features for external control features for external control signal transmission, and automatic maintenance features such as fault locating tests (FLT), logout, and a comprehensive interrupt recovery system.

FIGURE 7. INPUT/OUTPUT CHANNEL (INPUT) OPERATION

FIGURE 8. INPUT/OUTPUT CHANNEL (OUTPUT) OPERATION

#### 2075 PROCESSOR UNIT

- Simultaneous I and E cycles are possible in CPU.

- I and E units perform interlocked overlapped operations.

- Instruction buffering is provided for greater speed.

The Model 75 has a 64-bit main adder, 8-bit exponent adder, 8-bit decimal adder, 24-bit addressing adder and several other data transfer paths. There are 16 general purpose registers, 4 floatingpoint registers, 6 working registers, and a program status word register.

The Model 75 has simultaneous I and E cycles. The central processing unit is divided into three units which operate somewhat independently. They are the instruction unit (I unit), the execution unit (E unit), and the bus control unit (BCU). As previously discussed, all three units normally operate simultaneously, and together they provide a large degree of instruction overlap. Since the instruction and execution units contain a number of different data paths, several data transfers may occur during any one cycle in a single unit.

The I and E units are interlocked to prevent one unit overrunning the other and to allow proper interrupt recovery. Some instructions, such as input/ output instructions, are executed entirely by the I unit, while multiple load and store and set system mask instructions are executed by both the I and E units.

In addition to the overlapping of the I and E cycles, speed is also obtained by using instruction and operand buffering. Two double word registers (16 bytes) are used for prefetching instructions and one double word register (8 bytes) is used for pre-fetching operands. Prefetching allows most of the core storage access cycle to be overlapped by instruction execution.

# I-Unit Controls and Data Flow

- Main functions are controlled by the clock.

- Instructions are placed temporarily in the AB registers.

- Effective Address (E) = X + B + D.

The I unit and the E unit functions are controlled by the clock. The main function of the clock is to generate, shape, and distribute clock pulses to the I unit, E unit and maintenance console. Two types of pulses are generated by the clock: running pulses and controlled pulses. Running pulses are stopped during system reset; controlled pulses are stopped during system reset, machine check, during all resets, and in single-cycle mode. In single-cycle mode, controlled pulses are emitted one cycle at a time by depressing the single-cycle key.

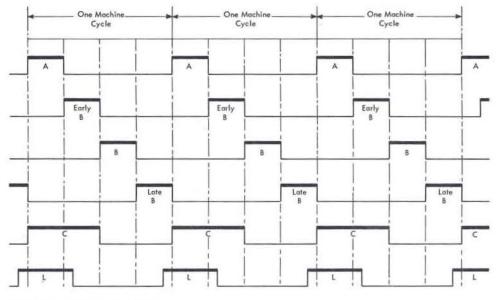

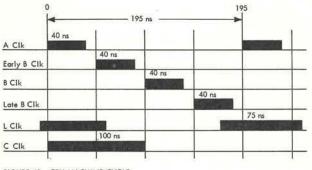

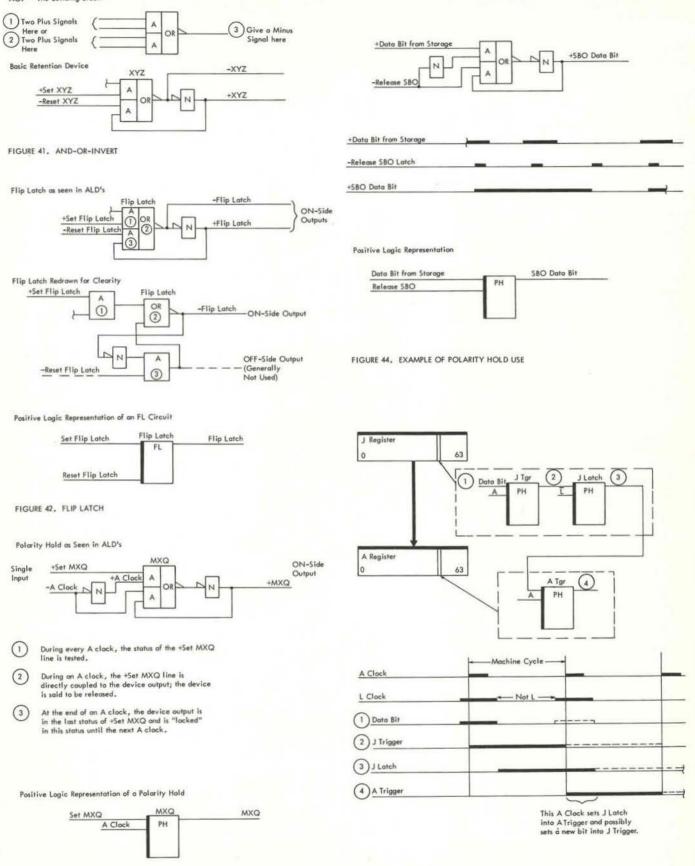

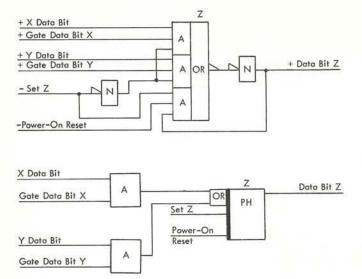

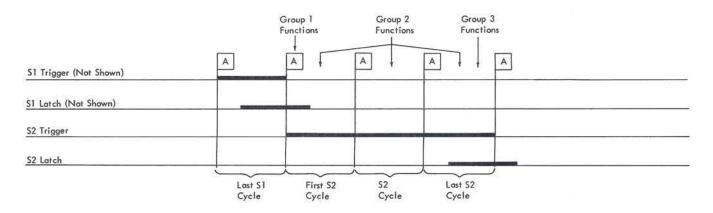

The relationship among the clock pulses is shown in Figure 9. The basic clock pulse (the A pulse, also called A clock) is wide enough to reliably set a control trigger; its leading edge also defines the beginning of a machine cycle.

B cycles are approximately 1/4 cycle long and are generated at three different times within a machine cycle: early B clock is generated for the second quarter of the machine cycle, B clock is generated for the third quarter of the machine cycle, and late B clock is generated for the fourth quarter. Each B clock pulse is timed for its individual use; therefore, these times are not exact.

The L clock pulse is slightly longer than the A clock pulse and brackets the A clock pulse on both sides. The leading edge of an L clock pulse rises in the preceding A clock cycle and its trailing edge falls after the A clock pulse. L clock pulse sets the latch to insure the state of the control is held in the latch for the duration of the L clock even though the A clock is changing the status of the control trigger.

The C clock cycle is one-half cycle long and spans the first half of the machine cycle. It is used for special purposes in the bus control unit and maintenance console. The A, B, C, and L pulses are generated as controlled and running pulses.

The heart of the clock is a crystal controlled oscillator which produces all clock pulses. A provision is also made to gate a fixed or variable frequency oscillator into the pulse shaping and timing circuitry. The switch "enable frequency check" determines the oscillator being used.

Following the oscillator gate is a circuit that allows every other pulse from the oscillator to enter the clock controls and pulse shaping circuits. The shaped oscillator output feeds a delay line and two AND circuits which are gated by the control trigger and running trigger respectively. The delay line insures that the first pulse emitted is a complete pulse. From here the pulses are sent to pulse stretchers and another delay line to form the L and C clock pulses as well as separating the leading edges of the A and L clocks.

The B clock is formed from a L pulse by means of a pulse shrinker and then fed into three different delay lines to form early B, B, and late B clocks. Each clock pulse leaving the large circuit boards has its own delay line, which is adjusted so that all

FIGURE 9. CLOCK PULSE RELATIONSHIPS

pulses of the same kind (A, B, C, or L) arrive at every portion of the machine at the same time.

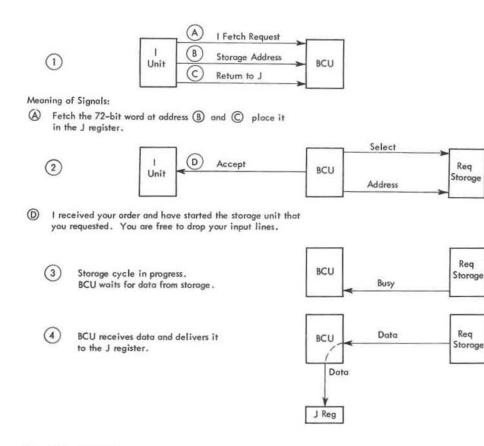

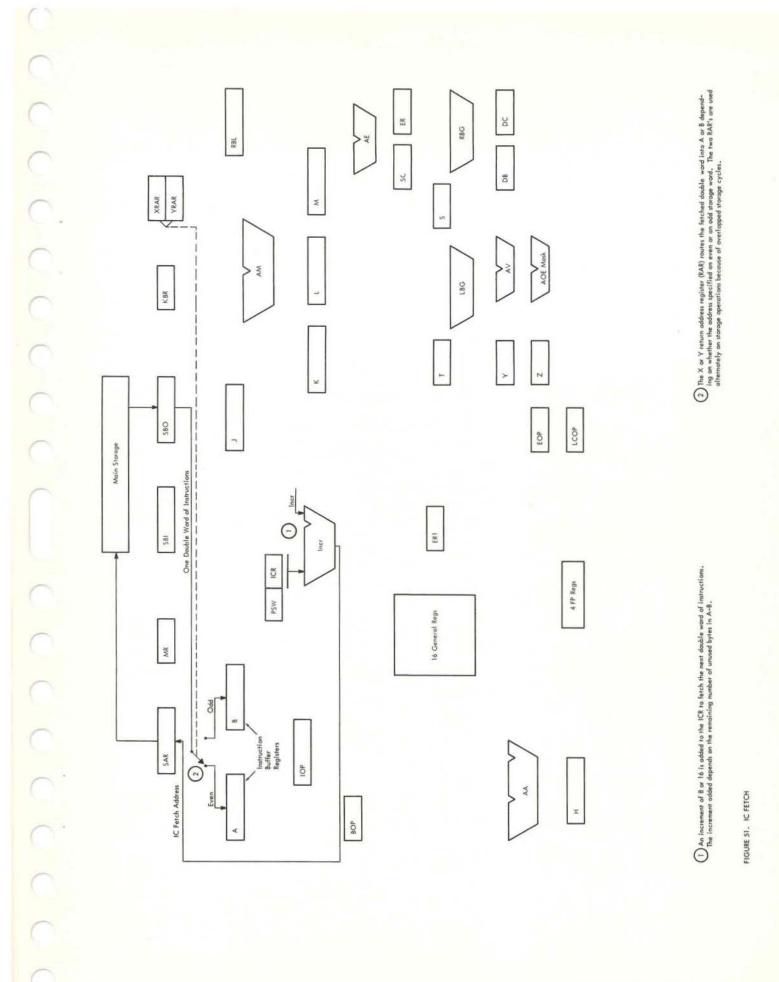

The data flow in the I unit is shown in the IBM 2075 Processing Unit Field Engineering Diagrams Manual, Form 223-2876. See Figure 2000. The instructions are brought from core storage and placed temporarily in the AB registers. Upon the completion of the I time of the previous instruction, the next instruction is transferred into the I operation register. If the next instruction time is not blocked, the next operation is decoded. During I time the instruction placed in the instruction operation register is decoded to determine the operation to be performed. The op code and R1 fields are placed in the B operation (BOP) register. The B operation register is an operation register for those instructions executed by the I unit. The general registers specified by the X and B fields are decoded and the contents of these registers are added to the contents of the displacement (D) field in the addressing adder to calculate the effective address (E). The effective address is gated from the addressing adder to the storage address register (SAR) or the H register. If the effective address specifies a location in core storage, the contents of the storage address register is transferred to the memory address register (MAR) when the storage request is recognized by the bus control unit (BCU). The data from core storage (or the general purpose register or floating-point register specified by R1) is returned to the J register. By the end of instruction time the instruction is decoded, the operands are in the working registers, (if the instruction is an RR format) the instruction counter is updated, and the next instruction is waiting in the AB registers.

# E-Unit Controls and Data Flow

- There are many main data paths in the execution unit.

- Binary arithmetic operations fall into four classes.

- Binary addition-subtraction is accomplished by parallel addition.

- Binary multiplication is performed at the rate of four bits per cycle.

- Binary division uses a non-restoring division algorithm.

- VFL and logical operations process fields of fixed and variable length.

- Instruction sequencing is normally in sequential order.

- Instruction counter controls control the advancing of the instruction counter.

- Branch requests are made in the same way as an operand request.

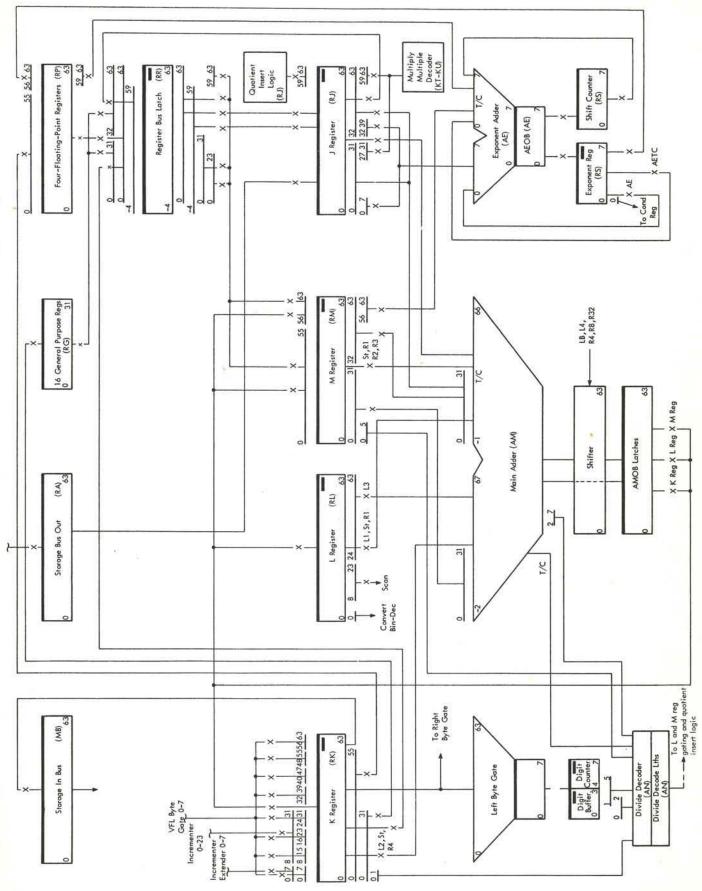

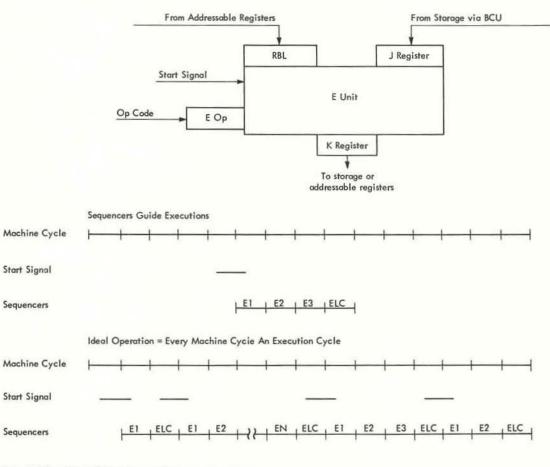

The data flow in the execution (E) unit of the Model 75 is shown in Figure 10. There are many main data paths in the E unit: a typical one is one in which the main adder is used. Data is gated from one or more of the working registers (J, K, L, and M register) to the main adder (AM); the main adder output bus (AMOB) latches are gated back to

Form 223-2872-1 FES S26-7033

one or more of the working registers. A typical floating-point data path is one in which the M register is gated to the true/complement (T/C) input of the main adder, and the K register is gated to the normal input. The sum on the main adder out bus is gated to the K and M registers.

Another data path is the one that is used in expanding a half-word from core storage into a full word. The data flow is from the J register through the main adder, the shifter, the main adder output bus latches, and to the K register. From the K register the data path is to the register bus latch (RBL) and then back to the J register. System/360 Model 75 binary arithmetic operations fall into four classes: fixed-point arithmetic, floating-point arithmetic, logical operations, and decimal arithmetic. The basic arithmetic operand is a 32-bit, fixed-point binary word. Some products and all dividends are 64 bits long, using an even-odd register pair.

Addition, subtraction, multiplication, divisions, and comparisons take one operand from a register and the other operand either from a register or core storage. Floating-point numbers may occur in either of two fixed-length formats -- short or long. These formats differ only in the length of the fractions, as indicated in Figure 3. The fraction of a floating-point number is expressed in 4-bit hexadecimal (base 16) digits. In the short format, the fraction has 6 hexadecimal digits, in the long format, the fraction has 14 hexadecimal digits. The radix point of the fraction is assumed to be immediately to the left of the high-order fraction digit. To provide the proper magnitude for the floating-point number, the fraction is multiplied by a power of 16. The characteristic (exponent), bits 1-7 of both formats, indicates this power. The characteristic is treated as an excess 64 number with a range from -64 through +63, and permits representation of decimal numbers with magnitudes in the range of  $10^{-78}$  to  $10^{75}$ . Bit position 0 in either format is the fraction sign. The fraction of negative numbers is carried in true form.

Floating-point operations are performed with one operand from a register and the other operand from either a register or core storage. The result, located in a floating-point register, is usually of the same length as the operands.

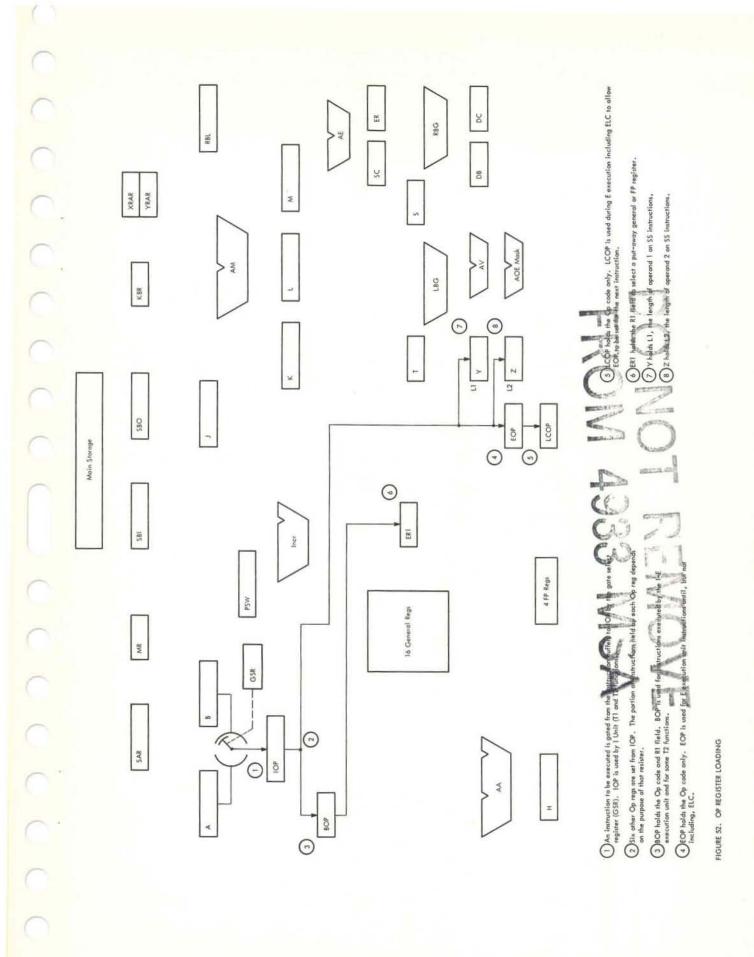

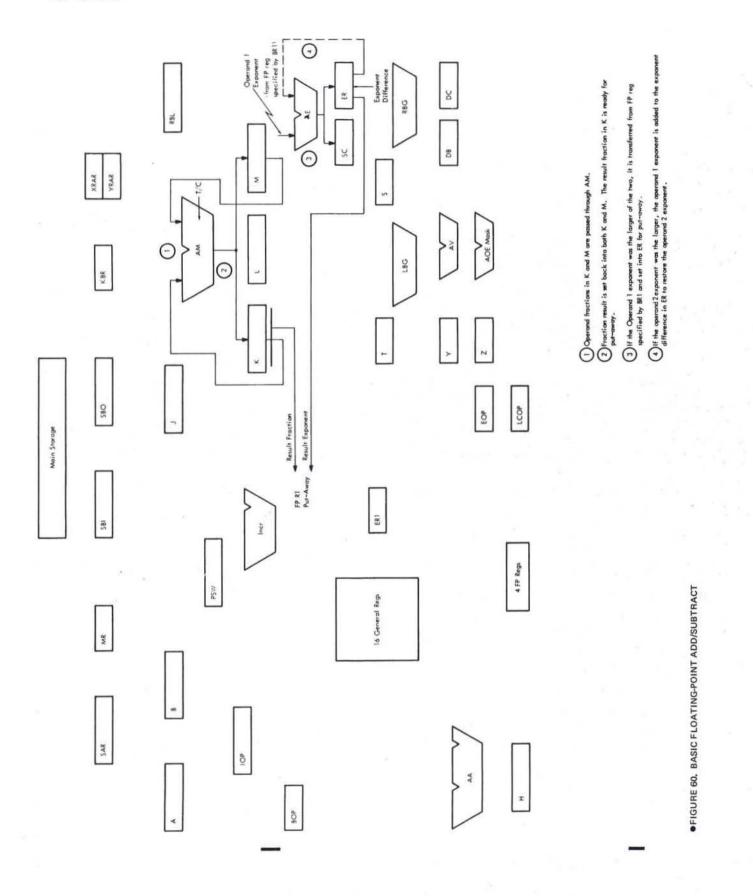

Binary Addition-Subtraction: In the Model 75, binary addition and subtraction is accomplished by parallel addition of the two operands. In RX format instructions, the storage operand is placed in the J register prior to the execution of the first good E cycle, and the R1 operand is brought either from the general register or floating-point register specified by R1 in the instruction and placed in the M register. If the instruction is a fixed-point instruction or a short floating-point instruction, the R1 operand is placed in the high-order half (bits 0-23, for floating-point or bits 0-31 for fixedpoint) of the M register. The result is obtained in one pass through the main adder. The result is returned to the K register; from the K register the result is returned either to the floating-point or general register specified by R1 of the instruction.

Before the add cycle in floating-point add-subtract and compare instructions, the operand with the smaller exponent is shifted right until the exponents are equal. Addition of the fractions follows the shift cycles as in the fixed-point instructions. A guard digit is retained to increase the precision of the result following fraction addition. Subsequent cycles may be necessary to normalize the sum or recomplement the result in case the result is in complement form.

Tests are made during E time to detect exponent overflow, exponent underflow, addressing exceptions, specification, and lost significance for floating-point instructions, and addressing exceptions, specification, and overflow for fixed-point instructions.

Binary Multiplication: The Model 75 incorporates logic which allows binary multiplication at the rate of four-bits per cycle. All even multiples of the multiplicand are provided for addition to or subtraction from the partial product within one cycle, except for the X10 and X14 multiples, which require two cycles. Since only even multiples are used, an even multiplier digit yields a correct partial product; all odd multiplier digits vield a partial product which is the X1 multiple higher than the multiplicand. Correction for this over multiplication is provided for by decoding the unit bit of the next highest multiplier group. When an odd multiplier is anticipated, the X16 multiplicand is subtracted from the partial product. This results in the partial product being the X1 multiple low as the next multiplication cycle by an odd digit begins. The net result of this pair of cycles is a correct product if the units digit of the next multiplier group does not also contain a one bit. The first cycle of multiplication differs from the following cycles in that if the unit bit is odd, the multiplicand, located in the K register, is added to the multiple as though it is a partial product.

Fixed-point multiply is executed by placing the multiplicand in the M register and the multiplier in the J register. During the first cycle, the multiplicand is transferred from the M register to the main adder and back to the K register and the M register. The second cycle develops the X12 multiple by shifting and subtracting the X4 multiple

from the X16 multiple; the result (the X12 multiple) is placed in the L register. The shift counter is set to eight, and the multiply iterations are performed. The multiplier is decoded from the J register to select the proper multiple from the M register or L register. The partial product in the AMOB latches is returned to the K register, the shift counter is decremented, and the J register is shifted right four bits. When the shift counter is decremented to zero, multiplication is complete; the product is stored in the general register specified by R1 of the instruction.

Floating-point multiply is similar to fixed-point multiply; however, the multiplicand is prenormalized before the multiplication cycles and the sum of the exponents is determined. The multiple generation and iteration cycles are the same as for fixedpoint multiply except that the shift counter is set to six for single-precision floating-point instructions or to 14 for double-precision floating-point instructions.

During each iteration cycle, the multiplier is tested for high order zeros; when detected, multiplication is concluded. The partial product is either hex-normalized or a high-order hex-zero digit exists. In the latter case, the hex-zero digit is shifted left four bits and one is subtracted from the exponent.

Floating-point multiplication is terminated by gating the final product from the K register into the floating-point register specified by R1 of the instruction.

<u>Binary Division</u>: In the Model 75, binary division uses a non-restoring division algorithm which incorporates a trial division by a multiple and produces two quotient bits for each iteration cycle. A non-restoring approach is used because by following a trial subtraction which overdraws, with a trial addition, restoration cycles are eliminated.

By execution time, the divisor is placed in the J register for RX format instructions or the M register for RR format instructions. The divisor is hexnormalized by gating it through the main adder and shifter. The result is placed in the K register and the L register. The X 3/2 divisor is generated by adding the contents of the K register to the contents of the L register shifted right one. The result is returned to the L register.

The dividend is placed in the M register, shifted the proper amount, and swapped with the K register. The required divisor multiples are located in the M register and L register. The X1 and X 3/2divisors are obtained by a direct read out from the registers, and the X 1/2 and X 3/4 divisors are obtained by shifting right one. The quotient is assembled in the J register; every second iteration causes the J register to be shifted left four bits by gating it to the RBL and back into the J register; thus space is provided for the next four quotient bits. The shift counter is set to the iteration count and division takes place until the shift counter is decremented to zero or three.

The first step in each iteration cycle is the selection of the divisor. If the dividend is true, the multiple is subtracted from the dividend; if the dividend is complement, the multiple is added to the dividend, and the quotient bits are entered into the J register. Most iteration cycles produce two quotient bits; however, if the X 3/4 divisor is used, three bits are generated. In this case, the third bit is retained and entered in place of the high order quotient bit developed during the next iteration cycle.

When the shift counter is reduced to one or three, the iteration cycles are terminated. If the last divisor used is the X 3/4, the quotient is complete; however, if the X 3/4 divisor is not the last divisor used, one more quotient bit is developed. The last quotient bit is generated by reducing the dividend by the X1 divisor.

In floating-point divide, the exponent is computed, tests are made for exponent overflow, exponent underflow, lost significance, and for division by zero. Also, the quotient is transferred to the floating-point register specified by R1. In fixed-point divide, the remainder is developed and transferred to the general register specified by R1 and the quotient is transferred to R1 + 1.

<u>VFL</u> and Logical Operations: Operands for comparing, translating, editing, bit testing, and bit setting are provided for processing logical fields of fixed and variable lengths. Fixed-length logical operands, which consist of one, four, or eight bytes, are processed from the general registers. Logical operations are also performed on fields up to 256 bytes in length, in which case the fields are processed from left to right, one byte at a time. Two scanning instructions permit byte-by-byte translation and testing via tables. An important special case of variable-length logical operations is the one-byte field, whose individual bits are tested, set, reset, and inverted as specified by an 8-bit mask in the instruction.

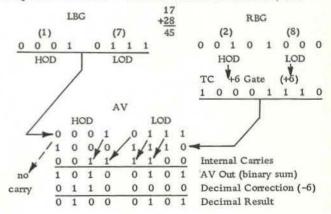

Decimal arithmetic imporoves the performance for processes requiring few computational steps per datum between the source input and the output; decimal arithmetic is provided with the operands and the result located in storage. Decimal arithmetic includes addition, subtraction, multiplication, division, and comparison. Decimal digits are represented in four-bit binary-coded-decimal; they are packed two to a byte, appearing in fields of variable length (from 1 to 16 bytes), and are accompanied by a sign located in the rightmost four bits of the low-order byte. Operand fields are located on any byte boundary and have lengths up to 31 digits plus sign. Instructions are provided for packing and unpacking decimal numbers; packing of digits leads to efficient use of storage, increased arithmetic performance, and improved rates of data transmission.

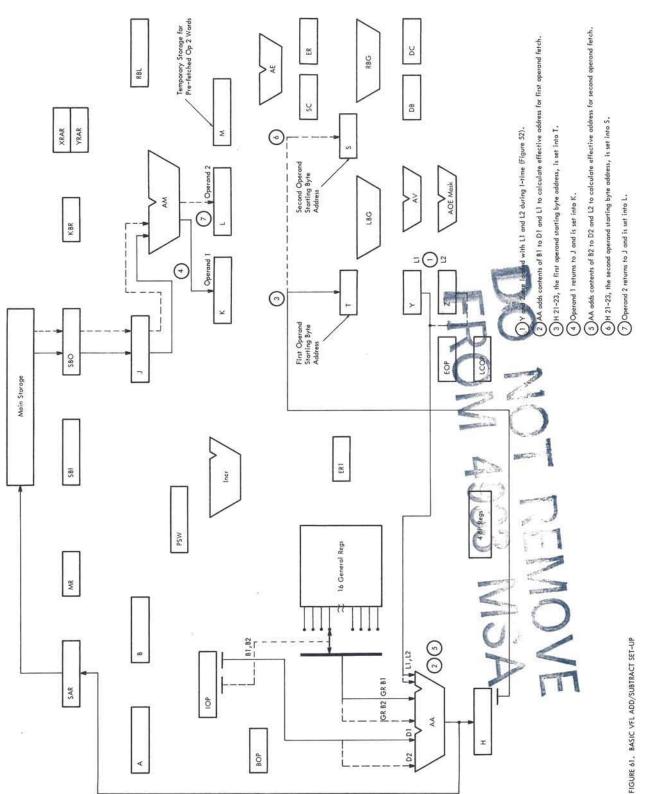

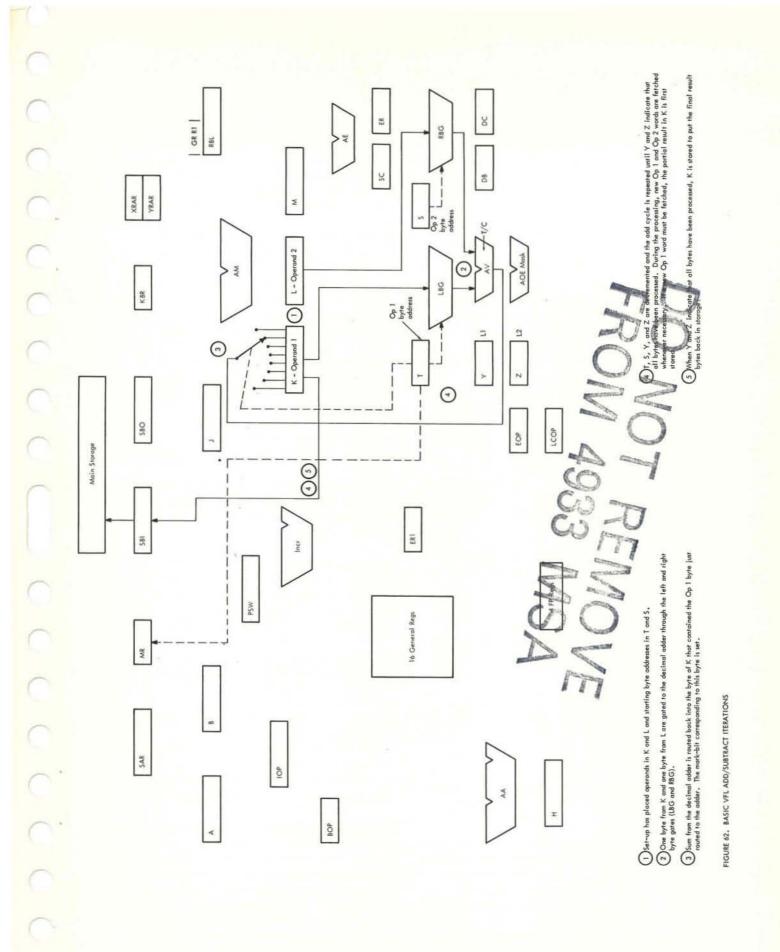

The execution of VFL and decimal instructions is handled by a separate section of the E unit. The K register and the L register are data input sources; the K register doubles as the result register. During VFL and decimal operations, normal I unit operations are suspended and the addressing facilities of the I unit are placed at the disposal of the VFL controls for generation of storage operand addresses.

Generally, a VFL operation requests data from core storage containing operands one and two. These data are placed into the K register and the L registers. The operand bytes are gated to the VFL E unit and the required operation is performed; the result byte replaces the operand byte in the K register. When either the K register or the L register operand is depleted and the operation is not complete, a request is made to obtain the next sequential storage word.

The central processing unit normally takes instructions in sequential order. After an instruction is obtained from a core storage location specified by the instruction counter, the instruction counter is incremented by the number of bytes in the instruction.

Most branching is accomplished by inspecting the condition of two bits of the condition register (bits 34-35 of the PSW). Many of the arithmetic, logical, and input/output operations indicate their outcome by setting the condition register to one of its four possible states (00-11). Subsequently, a conditional branch operation selects one of its four possible states as a criterion for branching. For example, the condition code reflects conditions such as non-zero result, first operand high, operands equal, overflow, channel busy, zero, etc. Once the condition register is set, it remains unchanged until modified by an instruction that reflects a different condition code.

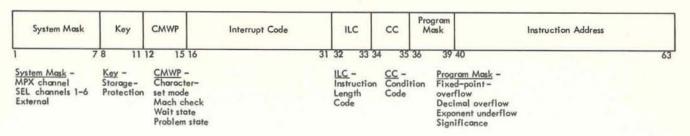

The program status word (PSW), a double word having the format shown in Figure 11, contains information required for proper execution of a given program. The program status word includes the instruction address, condition code, several mask bits, and several mode fields. The active or controlling program status word is called the current PSW; the status of an interrupted program is preserved by storage of the current program status word.

Five classes of interrupt conditions are distinguished:

- 1. Input/output

- 2. Program

- 3. Supervisor call

- 4. External, and

- 5. Machine check.

For each class, two program status words, called old and new, are maintained in the main storage locations shown in Figure 12. An interrupt in a given class stores the current program status word as an old program status word and then takes the corresponding new program status word as the current program status word. If, at the completion of the interrupt routine, the old and current program status words are interchanged, the system is restored to its prior state and the interrupted routine is continued.

The systems mask, program mask, and machinecheck mask bits in the program status word are used to control certain interrupts. When masked off, some interrupts remain pending while others are ignored. The system mask keeps external and input/output interrupts pending; the program mask causes four of the 15 program interrupts to be ignored, and the machine-check mask causes machine-check interrupts to be ignored.

Response of the central processing unit to a special condition in the channel and input/output unit is facilitated by an input/output interruption. The address of the channel and input/output unit are recorded in the old program status word while related information is preserved in a channel status word (CSW) that is stored as a result of the interrupt.

Unusual conditions in a program create program interruptions. Eight of the fifteen possible conditions involve overflow, improper divide operations, exponent underflow, and lost significance. The remaining seven deal with attempted execution of privileged instructions, improper addresses, and similar conditions.

A supervisor-call interrupt results from executing the supervisor call instruction. Eight bits from the instruction format are placed in the interrupt code of the old program status word. Supervisor call permits a problem program to switch central processing unit control back to the supervisor.

The central processing unit responds to signals from the interrupt key on the systems control

FIGURE 11. PSW FORMAT

| 08Initial program loading PSW88Initial program loading CCW 1168Initial program loading CCW 2248External old PSW328Supervisor call old PSW408Program old PSW488Machine check old PSW568Input/output old PSW648Channel status word724Channel address word764Unused844Unused |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 72     4     Channel address word       76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                            |

| 76     4     Unused       80     4     Timer       84     4     Unused                                                                                                                                                                                                    |

| 80 4 Timer<br>84 4 Unused                                                                                                                                                                                                                                                 |

| 84 4 Unused                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                           |

| 88 8 External new PSW                                                                                                                                                                                                                                                     |

| 96 8 Supervisor call new PSW                                                                                                                                                                                                                                              |

| 104 8 Program new PSW                                                                                                                                                                                                                                                     |

| 88 8 External new PSW   96 8 Supervisor call new PSW   104 8 Program new PSW   112 8 Machine check new PSW   120 8 Input/output new PSW                                                                                                                                   |

| 120 8 Input/output new PSW                                                                                                                                                                                                                                                |

| 128 Diagnostic scan-out area*                                                                                                                                                                                                                                             |

\*The size of the diagnostic scan-out area is configuration dependent.

FIGURE 12. PERMANENT STORAGE ASSIGNMENTS

panel, the timer, special devices, or other central processing units through an external interrupt signal. The source of the interrupt is identified by an interrupt code in bits 24-31 of the program status word.

A machine check (if unmasked) is caused by a hardware malfunction; it cannot be caused by invalid data or instructions, and it terminates the current instruction, initiates a diagnostic procedure, and effects a machine-check interrupt. When several interrupt requests occur during execution of an instruction, they are honored in a predefined order.

Overall central processing unit status is determined by four alternatives:

- 1. Stopped versus operating state,

- 2. Running versus waiting state,

- 3. Masked versus interruptible state, and

- 4. Supervisor versus problem state.

In the stopped state (entered and left by manual procedure), instructions are not executed, interrupts are not acknowledged, and the timer is not updated. In the operating state, the central processing unit is capable of instruction execution and of being interrupted.

In the running state, instruction requests and execution take place in a normal manner. The

wait state is entered by the program to wait for an interrupt. In the wait state, no instruction processing takes place, the timer is updated, and input/output and external interrupts are recognized if not masked off. Running versus waiting state is determined by the setting of a bit in the current program status word.

Central processing unit operations are interruptible or they are masked for system, program, and machine interrupts. When the central processing unit is interruptible for a class of instructions, interrupts are accepted. When the central processing unit is masked, system interrupts remain pending and program and machine-check interrupts are ignored. The interrupt states of the central processing unit are changed by altering mask bits in the current program status word.

In the problem state, processing instructions are valid, but all input/output instructions and a group of control instructions are invalid. In the supervisor state, all instructions are valid. The choice of problem or supervisor state is determined by a bit in the program status word.

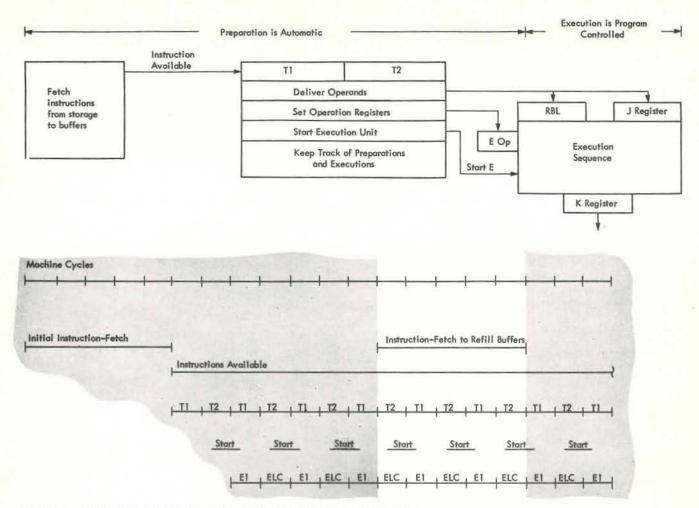

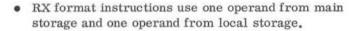

All instructions are initially processed in the instruction unit. The basic I time consists of two sequencers, T1 and T2. Both sequencers may stay on for more than one clock cycle. During T1 and

T2 time, the instruction is decoded, addresses are computed, and most operand requests are made. At the end of the last T2 cycle, the operation code is transferred to the execution unit where the instruction is completed. T1 of the next instruction usually follows T2 of the previous instruction.

At the beginning of every T1 cycle, the two halfwords of the AB register addressed by the gate select latch (gate select addresses the left-most half word) are gated into the IOP register. During T1, instruction decoding is done from the IOP register and any registers required for an effective operand address are gated to the addressing adder. With the turn on of T2 (called TN T2), the addressing adder output is gated into SAR and/or the H register; and any required operand fetch requests are made; operands requested are generally returned to the E unit. During T2, GRP, or FPL register operands required by the E unit are gated to the RBL. At the end of T2, the I to E transfer occurs, providing an interrupt has not occurred. At this time, the instruction is transferred to the execution unit. During T2 time, decoding is done from both IOP and BOP. The turn on of T1, T2, and the I to E transfer are dependent on several conditions being met.

E unit decoding is done from the E-operation register (EOP) in the E unit which is set from IOP. A second E unit op register (LCOP) provides the op code during the last cycle of the E unit instruction execution. During LCOP, EOP is being set for the next instruction, thus assuring the E unit of one cycle of decoding before the I to E transfer. The instruction counter controls control the normal advancing of the instruction counter and the normal requesting of instructions. The instruction counter register (ICR) contains 24 bits. Bits 20-22 are advanced after the I time of each instruction; bits 0-19 are advanced independently of bits 20-22. Bit 23 of the instruction counter register is always zero because instructions start at halfword addresses. The instruction counter register is advanced by two adders: the gate select adder for advancing bits 20-22 and the incrementer for advancing bits 0-19. The gate select adder works in conjunction with the gate select register (GSR) to select gates from the AB registers to the IOP register.

The instruction counter (IC) controls also generate normal instruction counter requests and generate the instruction address. The addresses are generated by adding in the incrementer an amount equal to the length of the instruction plus the amount in the instruction counter register. The controls attempt an instruction counter request as soon as an empty instruction buffer is detected, but any instruction being executed may block an instruction counter request if it would interfere with the instruction being executed. Whenever an instruction counter block condition is generated, the instruction counter request which is not honored by the bus control unit is cancelled.

Special instruction counter request rules are implemented to insure that A and B registers are never both empty by forcing instruction counter requests into the instruction stream and by suppressing instruction requests in anticipation of branch requests.

Instruction counter request addresses are obtained by gating the instruction counter into the incrementer and adding the proper increment amount. The increment amount is determined from the value of the instruction counter register and the empty condition of the A or B register. Bit 20 of the instruction counter request address is zero if the request is for the A register, or a one if the request is for the B register.

Branch requests are made at TN T2 time similar to operand requests. Branch request return addresses are generated for the AB register and the J register. If bit 20 of the address is a zero, the request is returned to the A register, and if bit 20 of the address is a one, the request is returned to the B register.

Branch instructions initiate a request to fill the second buffer. The request is called the branch +1 (BR +1) request, and it is obtained from the storage location following the location of the branch-to instruction. The address for the branch +1 request is computed during T2 of the branch instruction, and it is normally made at the I to E transfer. The return address for the branch +1 request is opposite to that specified for the branch request.

During E time of the branch instruction, the success of the branch is determined. The tests complete (tests cmplt) trigger is turned on, and during this cycle the line branch successful tells the success of the branch instruction.

If the branch operand is returned before tests complete of any branch, the operand is not placed in the AB register; however, it is returned to the J register. If a successful branch is determined during tests complete and the branch operand is already in the J register, the branch operand is gated from the J register into the proper register of the AB register. If the branch operand is returned after tests complete is turned on and the branch is successful, the branch operand is gated into the proper register of the AB registers.

The branch +1 request is made late enough so that the operand is returned after tests complete is

turned on and the success of the branch is determined. If the branch is successful, the BR + 1 operand is gated into the proper register of the AB register; however, if the branch is unsuccessful, the BR + 1 operand is blocked upon its return. If the branch is successful, the branch address (contained in the H register) is gated to the gate select latch through the incrementer and to the instruction counter. If a branch is unsuccessful, normal processing of the next instruction starts at the same time tests complete is turned on.

The execute instruction is processed as a branch instruction, but the instruction counter is not replaced by the contents of the H register. After the instruction constructed by the execute instruction is performed, an instruction counter recovery cycle is taken providing the instruction is not a successful branch instruction. The instruction counter recovery cycle allows the central processing unit program to proceed with the instruction following the execute instruction. The program status word is incremented by the length of the execute instruction rather than the length of the instruction obtained by the execute instruction.

#### 2365 PROCESSOR STORAGE

- 0.75 microsecond access time.

- Eight byte width on an interleaved access is possible.

- Interleaved and overlapping access for greater speed.

- Three main data paths are store data, fetch data, and address.

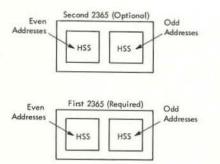

The IBM System/360 Model 75 is supplied with a minimum of 32 K, eight byte words of 0.75 microsecond processor storage (one 2365, Model 3) or a maximum of 128 K, eight byte words of 0.75microsecond processor storage (2365 Model 5). Each 2365 processor storage has a word width of eight bytes (64 data bits and 8 parity bits) on an interleaved access; the Model 3 is a two-way interleaved access, and the Model 5 is a four-way interleave.

Simultaneity in core storage operation is obtained by overlapping the cycles of the two storage units; addresses are staggered in the two units so that a series of requests for successive words activate the two units alternately, thus doubling the maximum rate of the single unit. The 2365 processor storage unit functions the same as any core storage unit; its prime purpose is to provide a quick, high-speed access to data and instructions. Each 2365 Processor Storage houses two ferrite core arrays and their associated logic.

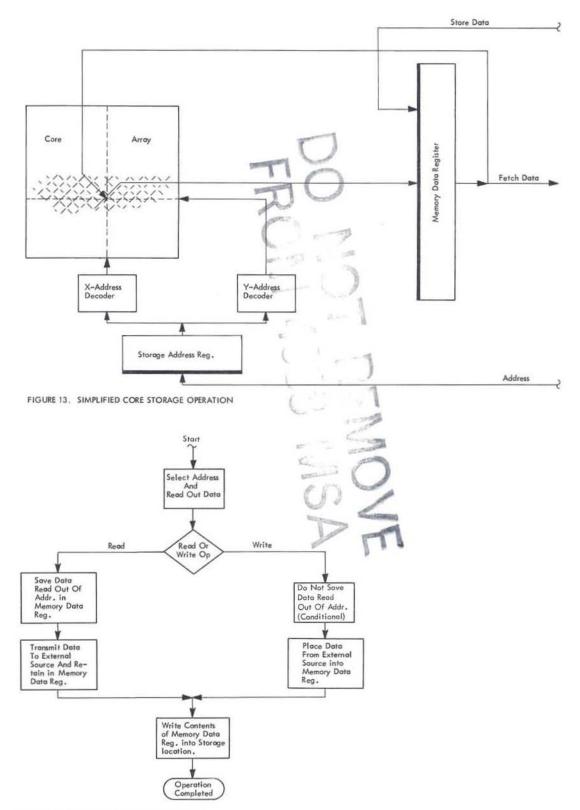

Figure 13 represents the three main data paths necessary to operate the 2365 Processor Storage. The address is an incoming data path carrying data that specifies the location in the processor storage that is affected. Addressing and the transfer from the central processing unit is done in binary. The address transfer from the central processing unit is momentary; therefore, the address must be retained in the processor storage unit. This address is retained in the storage address register (SAR), and is decoded to select the proper X and Y addresses; the output of the decoder selects one 72bit word out of many possible locations.

The store data signal is an incoming data path and brings information from the central processing unit, systems control panel, or input/output channels to the processor storage unit. This data, since it is also momentary, is stored in the memory data register (MDR) instead of the information read out of the specified address. The write cycle places the data into the specified location.

The fetch data is an output data path from the processor storage unit memory data register to the central processing unit registers or to the input/ output channels. The data in the memory data register is also used to rewrite the addressed location because the core read-out cycle is a destructive readout. Figure 14 represents a typical logic flow of any core storage cycle.

#### 2361 LARGE CAPACITY STORAGE

- Prime purpose of LCS is to increase storage capacity.

- One 2361 LCS provides up to 2048 K bytes.

- LCS provides a means of intercommunication between systems.

- Interleaving is an option.

The 2361 large capacity storage (LCS) unit functions the same as any core storage unit; its prime purpose is to increase the amount of storage available, on an immediate access basis, to the system.

The maximum number of 72-bit words available in one large capacity storage (LCS) is 262,144. Figure 13 also represents the three main data flow paths that are necessary for operating the large capacity storage unit. The address is an incoming data path carrying data that specifies the location in storage is affected. The addressing is done in

FIGURE 14. BASIC CORE STORAGE OPERATION

binary, and the address transfer from the central processing unit is momentary; therefore, the address must be retained in the large capacity storage unit. This address is contained in the storage address register, and is decoded in groups of one, three, and four bits each. The outputs of the decoders are combined until the selection is narrowed down to one 72-bit word out of the 262,144 possible word locations.

The store data is an incoming data path and brings information from the central processing unit, systems control panel, or input/output channel to the large capacity storage unit. This data, since it is momentary, is stored in the memory data register in place of the information read out of the specified address. The write cycle places this data into the specified location.

The fetch data is an output data path from the large capacity storage unit's memory data register to the central processing unit registers or to input/output channels. The data in the memory data register is also used to rewrite the addressed location because the read-out portion of the cycle is a destructive read-out.

The 2361 Core Storage shared storage feature provides a means of communication between two IBM System/360, Model 50, 60, 62, or 75. Two systems can have access to the data and instructions contained in the large capacity storage unit. Through this arrangement, one program is available to two systems or data for the programs in two systems is available to both systems for immediate access. Up to four 2361 large capacity storage units in any combination of Model 1 (1024 K bytes) and Model 2 (2048 K bytes), can be attached. Interleaved operation of large capacity storage is an option, with the restriction that two 2361 storages of the same model be paired for interleaving. Pairs of interleaved 2361's can be attached with 2361's not equipped for interleaving, in which case, the interleaved pairs are assigned the lower addresses.

# INPUT/OUTPUT CHANNELS

- I/O operations are performed by selector channels, control units, and I/O devices under control of a supervisory program.