# Mentor Grophics and Gould AMI Derign Manual

### TABLE OF CONTENTS

|           |                                                                                                                                                                                                                                                                          |                                       | . M     |     |                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------|-----|--------------------------|

| Section 1 |                                                                                                                                                                                                                                                                          | terker or to                          |         |     |                          |

| TNTDOD    | NICTTON                                                                                                                                                                                                                                                                  |                                       | 1 1 1   |     |                          |

| INTRUC    | DUCTION                                                                                                                                                                                                                                                                  | N                                     |         |     | 1-                       |

| Section 2 |                                                                                                                                                                                                                                                                          |                                       |         |     |                          |

| GATE A    | RRAY DESIGN STREAM                                                                                                                                                                                                                                                       |                                       | · · · · |     | 2-                       |

| 27.       | 1 How a Gate Array is Designed Schematic Capture Simulation Package Assignment Physical Layout Back Annotation and Simulati Test Vector Generation 2 GATE STATION Support of Gate Design Stream A (Schematic I Design Stream B (Validated N Design Stream C (Date Base I | on                                    |         |     | 2-3<br>2-3<br>2-3        |

|           | GRAPHICS TOOLS FOR GATE ARRAY                                                                                                                                                                                                                                            |                                       | ća 7 ., | Ì., | 3-1                      |

| 3.1       | Design stream descriptions Directory Structure                                                                                                                                                                                                                           | · · · · · · · · · · · · · · · · · · · |         |     | 3-1<br>3-8               |

| Section 4 | *                                                                                                                                                                                                                                                                        |                                       |         |     |                          |

|           |                                                                                                                                                                                                                                                                          |                                       | 2       |     | 1 12                     |

| DESIGN    | METHODOLOGY                                                                                                                                                                                                                                                              |                                       |         |     | 4-1                      |

| 4.1       | Schematic Capture About the symbols Software Macros NETED Features for Gate Array Defining the I/O's on the Chi                                                                                                                                                          | y Design                              |         |     | 4-1<br>4-3<br>4-3        |

| 4.2       | Defining Critical Nets Creating a Root Symbol Simulation How to Design for Useful Simu The Different Conditions for                                                                                                                                                      |                                       |         |     | 4-5<br>4-6<br>4-7<br>4-8 |

## TABLE OF CONTENTS [continued]

| Section     | 4     | DESIG                  | ON ME                                     | THOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OLO                                                             | GY                                 | [                                   | co                 | nt                               | i n                      | ue        | d] |                |          |          |         |     |   |        |    |    |   |   |    |   |   |                                                          |                                 |

|-------------|-------|------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|-------------------------------------|--------------------|----------------------------------|--------------------------|-----------|----|----------------|----------|----------|---------|-----|---|--------|----|----|---|---|----|---|---|----------------------------------------------------------|---------------------------------|

|             | 4.4   | Packa<br>Phys<br>How ( | ical<br>CADIS<br>lacem<br>outin<br>Anno   | t Located ng to the company of the c | badi<br>the<br>the<br>the<br>niti<br>out<br>Work<br>Usi<br>sing | ng<br>Pel<br>Del<br>Del<br>on<br>s | De<br>ay<br>ay<br>ay<br>. CA<br>ADI | De B B B C C DI GR | y<br>las<br>as<br>as<br>GR<br>AP | y<br>ed<br>ed<br>AP<br>H | . 000 H . |    | Te<br>Vo<br>Pr | mp<br>lt | er<br>ag | at less |     | e |        |    |    |   |   |    |   |   | 4-<br>4-<br>4-<br>4-<br>4-<br>4-<br>4-<br>4-<br>4-<br>4- | +-8<br>-10                      |

| Section     | 5     |                        |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                    |                                     |                    |                                  |                          |           |    |                |          |          |         |     |   |        |    |    |   |   |    |   |   |                                                          |                                 |

| DATA        | A TRA | ANSFE                  | R.                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                    |                                     |                    |                                  | ·                        |           |    |                |          |          |         |     |   | ٠      |    |    |   | ٠ |    | × | · | . !                                                      | 5-1                             |

|             | 5.2   | Desi                   | INSTÄ<br>smitt<br>gn St<br>gn St<br>gn St | LL_ding<br>read<br>read<br>read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CSR<br>Dat<br>m A<br>m B<br>m C                                 | Sa                                 |                                     |                    |                                  |                          |           |    |                |          |          |         | *   |   |        |    |    |   |   |    |   | • |                                                          | 5-1<br>5-2<br>5-3<br>5-4<br>5-6 |

| Section MAG |       |                        | , i                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                    | (*)                                 |                    |                                  |                          | *         | •  | •              |          | ,        | į       |     | - | i<br>i |    |    | • |   |    |   | • |                                                          | 6-:                             |

|             | 6.2   | What<br>What<br>How    | Come                                      | s w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ith                                                             | MA                                 | GIC                                 | _                  |                                  |                          |           |    |                |          | ,        | ٠       |     |   | *      |    |    |   | 8 |    | • | * |                                                          | 6-                              |

| Section     | 7     |                        |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                    |                                     |                    |                                  |                          |           |    |                |          |          |         |     |   |        |    |    |   |   |    |   |   |                                                          |                                 |

| APPI        | ENDI  | CES                    |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ٠                                                               |                                    |                                     | ٠                  | ٠                                | ٠                        |           |    |                | ٠        | ٠        | *       | *   | ٠ | ٠      | ٠  | ٠  | ٠ | × | 18 | • | * | ٠                                                        | 7–                              |

|             | 7.1   | Tech                   | nolog                                     | gies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Su                                                              | рро                                | rte                                 | ed                 | by                               | , t                      | ch i      | is | D              | es       | ig       | n I     | Ki: | t | 2-     | 4- | 85 |   | , |    | ٠ | , | ,                                                        | 7-                              |

## TABLE OF CONTENTS [continued]

| Section | 7     | APPENDICES      | [continued] |     |          |      |     |     |        |     |       |     |   |     |   |    |   |   |   |     |    |     |

|---------|-------|-----------------|-------------|-----|----------|------|-----|-----|--------|-----|-------|-----|---|-----|---|----|---|---|---|-----|----|-----|

|         | 7.2   | Packages Supp   | orted 2-4-  | 85  | ,        |      |     |     |        |     |       |     |   |     |   |    |   |   |   |     |    | 7-1 |

|         | 7.3   | AMI ADD DELAT   | Users Man   | ual |          | .0   |     |     |        |     |       |     |   |     |   |    |   |   |   |     | ¥  | 7_9 |

|         |       | TIALLYODOC LTOM |             |     |          |      |     |     | 100    |     |       |     |   |     |   |    |   |   |   |     |    | 7-3 |

|         |       | LOMINTING LUE L | RUGRAM      |     |          |      |     |     |        |     |       |     |   |     |   |    |   |   |   |     |    | 7 0 |

|         |       | THE DELAY EQU   | JATION AND  | TTS | PA       | RA   | ME  | ŤE  | Ro     |     | •     | •   |   | •   | 5 | •  | • | • | Ť | ň   | •  | 7 6 |

|         |       | Parameter       | s From the  | De  | eic      | חי   | E   | 10  | _, , _ | ,   |       | *   | • | ٠   | * | •  | ٠ | • | ٠ |     | •  | 7-0 |

|         |       | Parameter       | s From the  | To  | ohe      | 111  |     | 1 6 | ·_:    | i.  | ٠     |     | ٠ | •   |   | •  | ٠ |   |   | 14  | •  | (-6 |

|         |       | NET NAMES AND   | s From the  | ı e | em       | 101  | OC  | у   | ы      | 16  | 2     |     | • | ٠   | • | 80 | ٠ | • | • | 1.7 | 10 | 7-7 |

|         |       | THE THINKS THE  | CIVITATION  |     |          |      |     |     |        | 1.2 | 1,120 | 12  |   | 123 |   |    |   |   |   |     |    | /_0 |

|         |       | . Excernal      | Synonym Fi  | l e |          |      |     | 100 |        |     |       |     |   |     |   |    |   |   |   |     |    | 7-0 |

|         |       | O' non ying     | III OHE DES | QII | $\Gamma$ | 16   | ;   | 127 | 120    |     | 7/2   |     |   |     |   |    |   |   |   |     | 7  | -10 |

|         |       | LATOUT DELAT    |             |     |          |      |     |     |        | 75  | 15    |     |   |     |   |    |   |   |   |     | 7  | -10 |

|         |       | The Capac       | Toance File | 2   |          |      |     | 40  | 120    | 720 | 727   | 120 |   |     |   |    |   |   |   |     | 7  | -10 |

|         |       | The DDF F       | ile         |     | 520      | 1921 | 127 | 120 | 050    |     | 53    | 200 |   |     | • | •  | • | • | • | •   | 7  | 10  |

|         |       | PTIMT I VITUINO |             |     |          |      |     |     |        |     |       |     |   |     |   |    |   |   |   |     | 7  | -10 |

|         | 7.4   | Designing for   | Testabilit  |     | ٠        | *    | •   | •   | •      | •   | ٠     |     | ٠ | •   | ٠ | •  | • | • |   |     | 1  | -10 |

|         | 2 2 3 |                 | 1030401111  | u y |          |      |     |     |        |     |       |     |   |     |   |    |   |   |   |     | 1  | -12 |

### LIST OF FIGURES

| 2-1. | CATE ARRAY DESIGN FLOW                                | 2-2  |

|------|-------------------------------------------------------|------|

| 2-2  | Mentor Design Stream Support                          | 2-5  |

| 9 1  | Cohamatia Cantura                                     | 3-3  |

| 3-2. | Schematic Capture. Simulation and Package Constraints | 0-0  |

| 3-3. |                                                       | 3-8  |

| 3-4. | Directory Structure                                   | 0-3  |

| 3-5. | GOULD AMI Directory Structure                         | 3-13 |

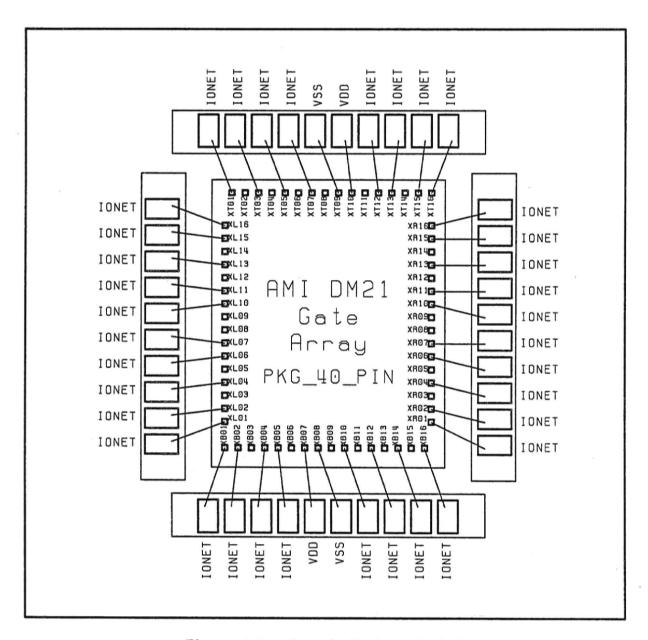

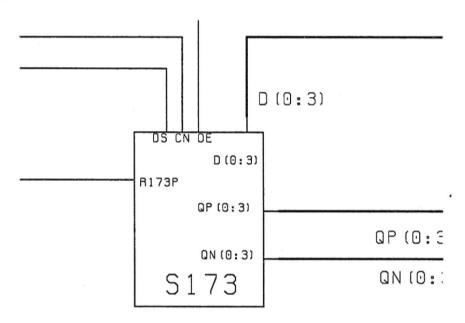

| 4-1. | Example Package Symbol                                | +-14 |

| 6-1. | AGIC                                                  | 6-1  |

| 6-2. | The Shifter                                           | 0-2  |

| 6-3. | Data Select                                           | 0-3  |

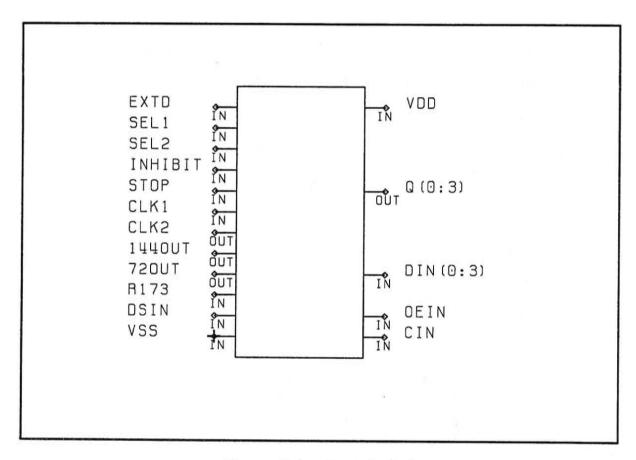

| 6-4. | Root Symbol                                           | 6-4  |

#### INTRODUCTION

This manual provides a tutorial for designing GOULD AMI gate arrays using the Mentor Graphics engineering work station. The work station offers different levels of support in the gate array design cycle, allowing you to choose the amount of control that you have over your design. This manual addresses every level of support from schematic capture through physical layout of the design.

This manual explains the design cycle and the various Mentor Graphics tools which are used to complete a design. This manual also explains how you may alter the design stream and tailor it to your needs. An example circuit serves to demonstrate the design stream.

This manual does not describe all of the capabilities of the Mentor Graphics tools such as NETED, SYMED, etc. Some familiarity with these applications is assumed. Separate reference manuals for each of these tools are available. This manual will refer you to pertinent manuals during the course of the design cycle explanation. The final section of this manual lists the reference manuals that are useful for learning more about the design tools. It is suggested that you take the Mentor Graphics IDEA STATION course before using the GOULD AMI design package.

The first 5 sections describe the design cycle and the tools that are used for the design. Section 6 shows you how to run MAGIC and gives the results from each design step for comparison.

#### 2. GATE ARRAY DESIGN STREAM

### 2.1 How a Gate Array is Designed

The process of designing a gate array can be broken into 6 basic steps -

- 1. Schematic Capture

- 2. Simulation

- 3. Package assignment

- 4. Physical layout

- 5. Back annotation and resimulation

- Test vector generation

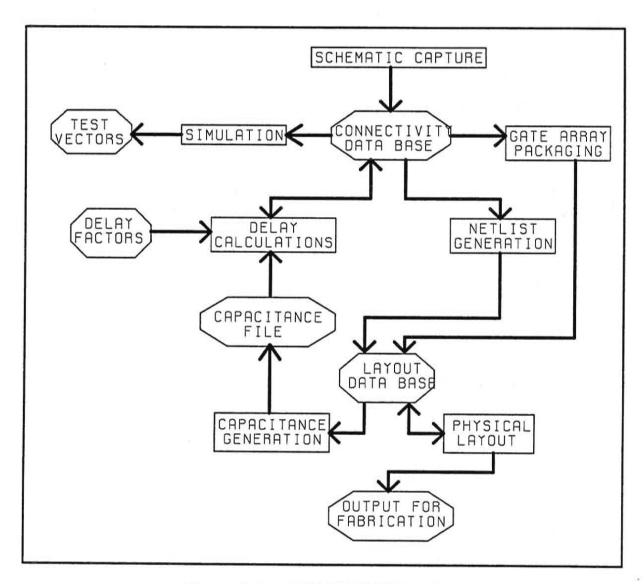

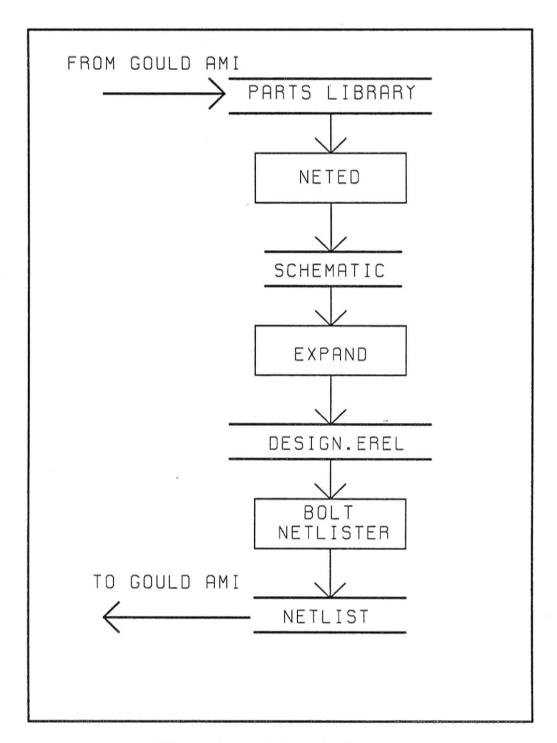

The flowchart in figure 2-1 shows how these steps fit together and the data generated at each step.

### 2.1.1 Schematic Capture

The first step in the design cycle is to define the gate array logic. This is done by selecting the symbols representing the logical functions available in the GOULD AMI gate array family and then connecting the pins together with nets. The symbols contain the information necessary to drive simulation and physical layout. To facilitate the testing and debugging of logic, the design is usually implemented in a hierarchical manner.

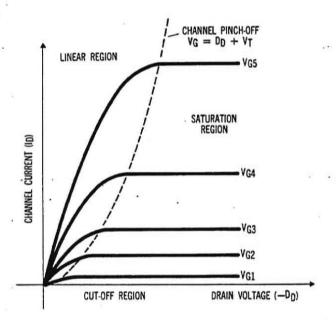

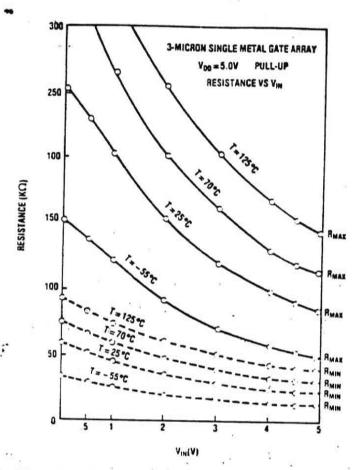

#### 2.1.2 Simulation

Simulation uses the connectivity data generated from the schematics entered in step 1 to model the behavior of the design. Simulation includes timing information as well as the functional logical simulation. Simulation recognizes the delay time required for changing the states of the output pins on each macro, and uses this information to model the behavior of the circuit. Delay time includes the internal gate delay and the delay due to the capacitive loading of gate inputs and predicted wiring. The delay of a signal also varies with voltage, temperature and fabrication process. These factors can be controlled when running the simulation.

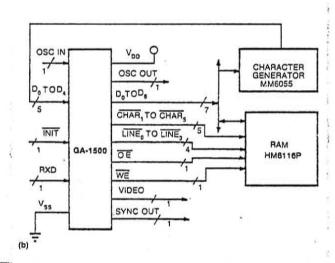

Figure 2-1. GATE ARRAY DESIGN FLOW

### 2.1.3 Package Assignment

There are a large number of package types that can be used for implementing a gate array. The type of package that you choose depends on the number of output pins on the circuit and the conditions under which the gate array must function. The uncommitted gate array (the gate array before any logic has been assigned) has a fixed number of locations for input and output signals to the chip. Not every location is acceptable for any given design. When a subset of the I/O locations are used, there are very specific rules

concerning the use of the locations. The package definition step guides you through the choice of the I/O locations. These assignments must be made before physical layout, because these decisions affect how the signal paths will be routed to the I/O locations.

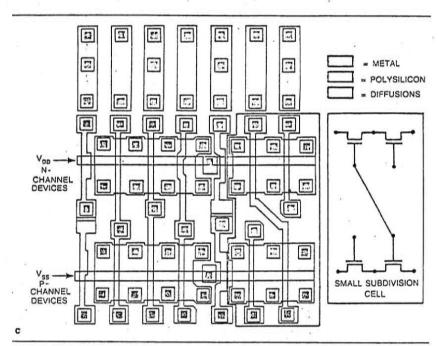

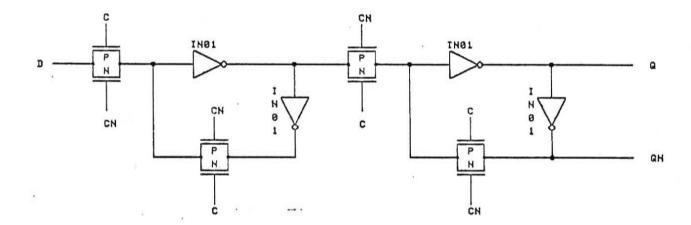

### 2.1.4 Physical Layout

The physical layout step uses the connectivity and package assignment information to implement the design. Starting with an uncommitted chip, the GOULD AMI macros used in the design are optimally placed. Placement defines the functions of transistors on the array by 'placing' predefined patterns of connectivity over the transistors. These patterns of connectivity are called macros and are used to create a variety of logical functions, ranging from inverters to flip-flops and multiplexers. When the transistors have been programmed into a logical function, signal routing is added to connect the logical functions. Both placement and routing can be performed automatically or through interactive graphics.

#### 2.1.5 Back Annotation and Simulation

Once the physical implementation of the design has been determined, a more accurate model of signal delays can be generated. The length of all signal wires is known and the capacitive load of each net can be calculated. Back annotation extracts the capacitance values and updates the simulation data to include these delays. Simulation can now be run with a higher confidence since the true delays are being modeled.

#### 2.1.6 Test Vector Generation

It is necessary to provide a set of input stimuli to test the circuit when it has been produced. These patterns are generated from simulation values, but are formatted to create the commands for the chip test hardware.

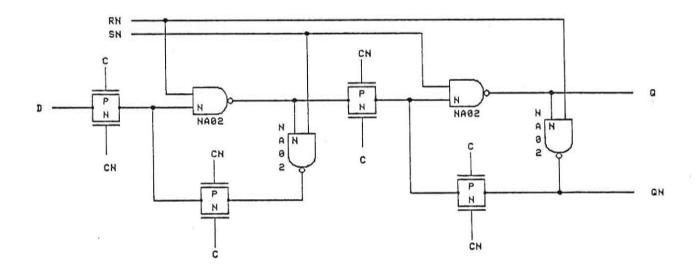

### 2.2 GATE STATION Support of Gate Array Design

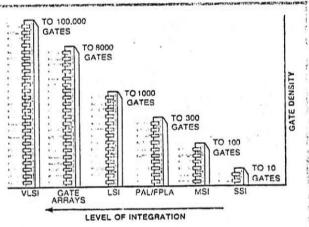

GATE STATION can support the entire gate array design process described above. It is also possible to use a subset of GATE STATION and the GOULD AMI libraries to support different levels of the design process. The following list shows the 3 levels of support that are offered:

- o Schematic Capture Design Stream A (Schematic Interface)

- o Schematic Capture, Simulation and Back Annotation Design Stream B (Validated Netlist Interface)

- o Schematic Capture, Simulation, Physical Layout and Back Annotation Design Stream C (Data Base Interface)

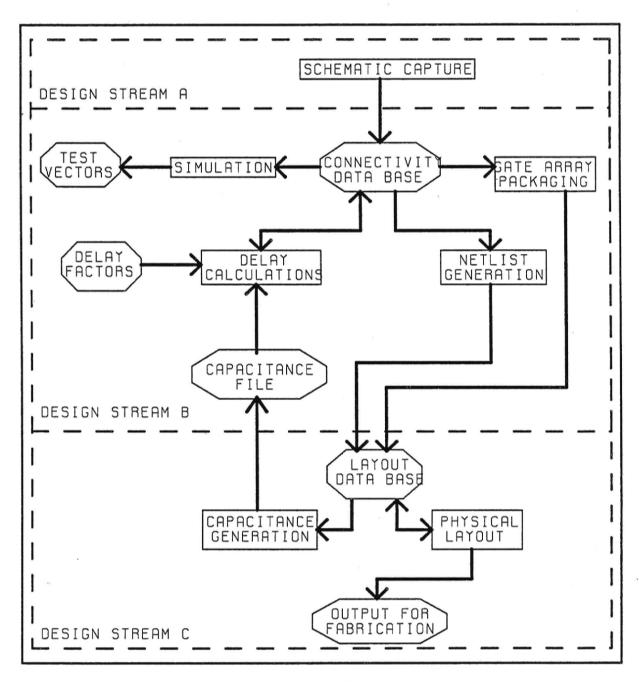

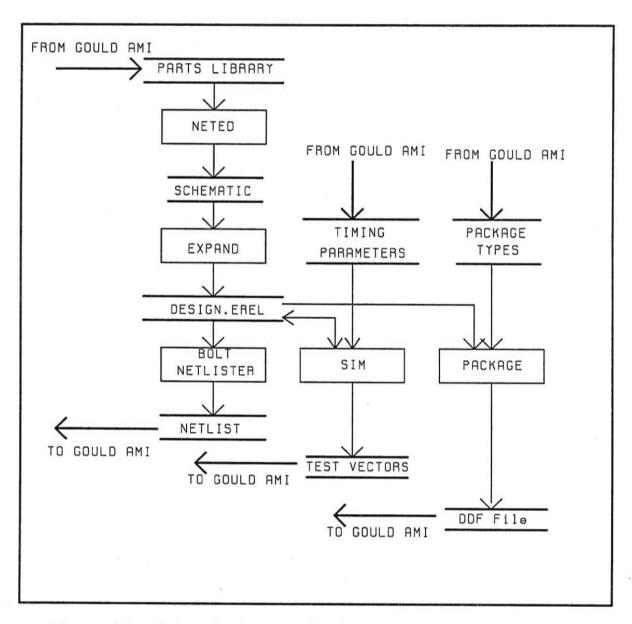

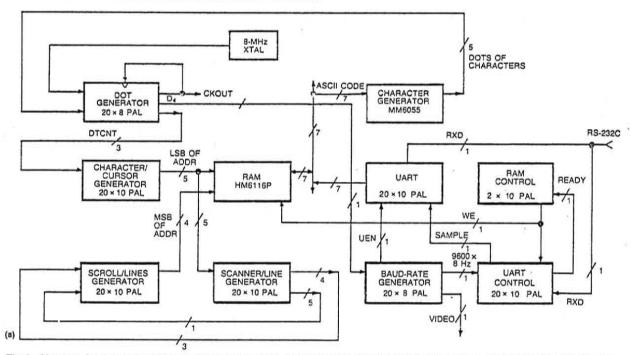

Figure 2.2 shows the the grouping of the design flow into design stream support.

### 2.2.1 Design Stream A (Schematic Interface)

This is the minimum level of support. GOULD AMI provides the symbol library for schematic capture. The library does not support simulation or layout. The Mentor Graphics CAPTURE STATION is the minimum configuration to support this type of design. You would give GOULD AMI a netlist built from the schematic describing the connectivity of the circuit. GOULD AMI would perform the simulation and layout at the factory. Design stream A is highlighted in Figure 2-2.

### 2.2.2 Design Stream B (Validated Netlist Interface)

This stream provides extensive simulation capability in addition to schematic capture. The Mentor Graphics IDEA STATION supports this design stream. GOULD AMI provides a logic library which contains symbols with functional and timing simulation data. You receive data that allows you to test the signal delays based on a variety of different parameters. The signal delays for a design can vary with operating temperature and voltage, fabrication process, and capacitive loading on the signal driver. The capacitive loading is broken into the fanout loading due to input gates and predicted wiring in the net. The GOULD AMI library contains the data necessary to simulate these conditions. The signal delays are automatically calculated when any of these parameters are changed and the simulation files updated.

In addition to simulation, package definition capability is offered. Package definition is a series of programs that help you create a correct bonding diagram based on the package type that you have selected. The bonding diagram is the guide for GOULD AMI that shows the connections between the pads on the chip and the pins on the package. You may, for example, use only a subset of the possible I/O pads on the uncommitted chip. Package definition will ensure that you use the appropriate locations on the chip for this subset to create the correct bonding diagram. This information is used in the layout of the design.

After you are satisfied with the design, it is sent to GOULD AMI for layout. When they complete the layout, a capacitance file is generated and sent back for resimulation. The capacitance values are converted into delay values on your system and the resimulation is performed with these accurate delay values.

Figure 2-2. Mentor Design Stream Support

You would return to GOULD AMI a netlist for the physical layout and a set of test patterns for testing the final chip. Design stream B is highlighted in Figure 2-2.

### 2.2.3 Design Stream C (Date Base Interface)

Design stream C offers all the capability of B plus physical layout. The Mentor Graphics GATE STATION supports this design stream. In addition to the simulation data, you receive the physical data describing the uncommitted chip and the macros. When the layout is complete you can back-annotate the true net delays due to wire length for resimulation.

The test vectors, netlist, and physical layout data are returned to GOULD AMI and the circuit would be ready for fabrication. This design stream gives you complete control over the design process. Stream C is highlighted in Figure 2-2.

#### 3. MENTOR GRAPHICS TOOLS FOR GATE ARRAY DESIGN

Section 2 discussed gate array design and how the design is supported. Section 3.1 provides more detail about the data and programs you will need at each design stream level. Section 3.2 is a description of the directory organization for the GOULD AMI design package.

While this section describes all the data and programs that you will need, it does not describe how to run the programs. Section 4 addresses design methodology and section 7 lists relevant reference manuals.

### 3.1 Design stream descriptions

The GOULD AMI design includes data, programs and documentation. The amount of information you receive will vary depending on the level of design support that you choose. This data will be used as input to the Mentor Graphics tools. You will send back to GOULD AMI the data necessary to complete the design. The steps performed at GOULD AMI to complete the design will vary depending on the design stream option that you use. The following lists describe each design stream in detail.

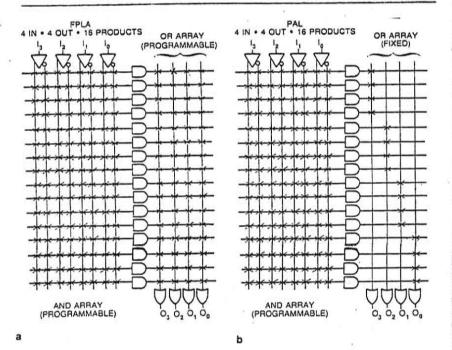

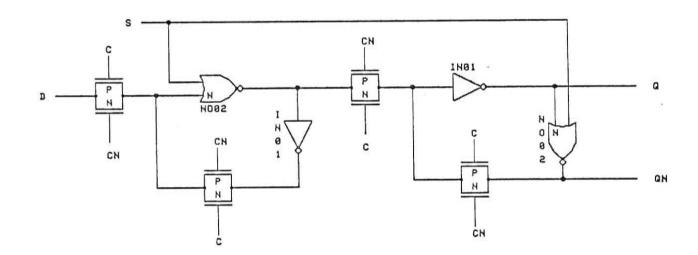

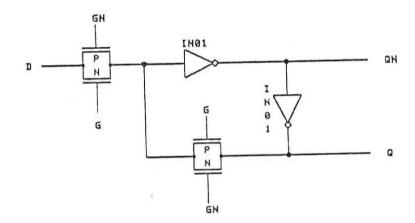

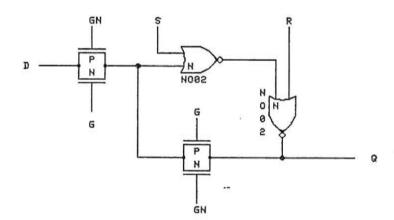

### <u>DESIGN STREAM A - SCHEMATIC CAPTURE</u> (Schematic Interface)

#### WHAT GOULD AMI SENDS TO YOU

- Parts library containing a symbol for each macro. The symbols do not have sheets associated with them for simulation, but the symbols will contain the following properties for netlist generation:

- COMP name corresponding to the macro names in the GOULD AMI library

- b. PIN name corresponding to the pin names in the GOULD AMI library

- 2. The BOLT netlist generator to generate the netlist for simulation and layout at GOULD AMI.

#### MENTOR GRAPHICS TOOLS YOU WILL NEED

1. NETED for schematic capture

- 2. SYMED for hierarchical design

- EXPAND for creating the flattened design to generate the netlist

#### WHAT YOU WILL SEND TO GOULD AMI

- 1. BOLT netlist containing all the connectivity data for the design.

- 2. Logic simulation table of stimuli and reponses

- Package data

- 4. Device Specification

#### WHAT STEPS ARE PERFORMED AT GOULD AMI

- 1. Simulate the design

- Determine and specify layout constraints (I/O preplacement, critical nets)

- Perform physical layout

- 4. Re-simulate using physical layout results for calculating delays

- 5. Determine test vectors

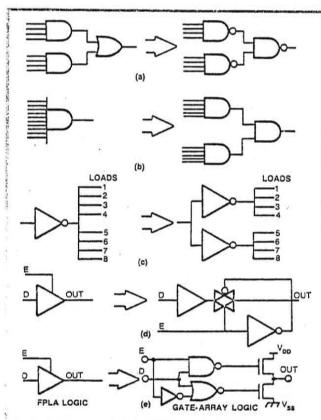

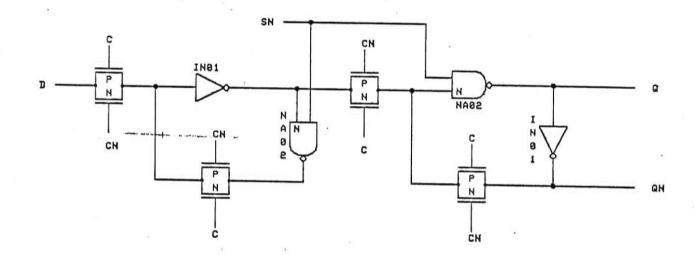

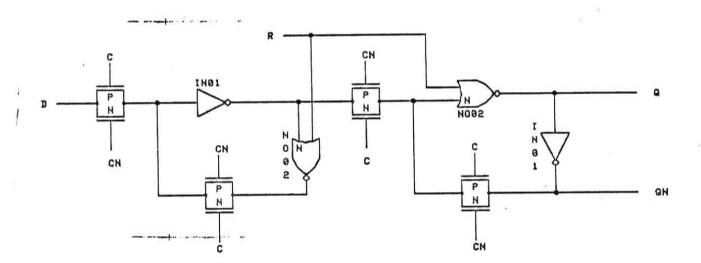

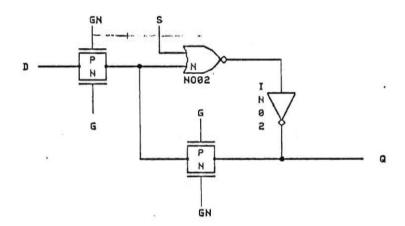

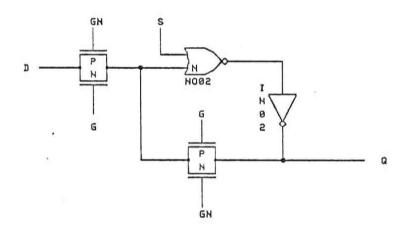

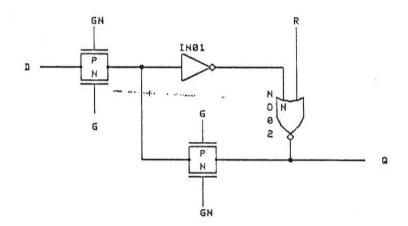

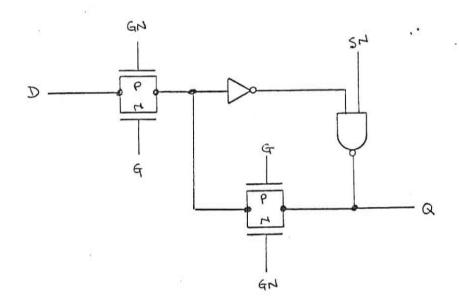

Figure 3-1. Schematic Capture

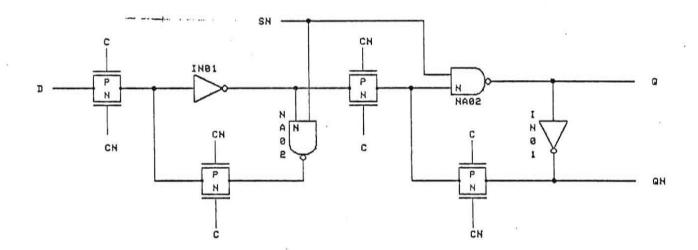

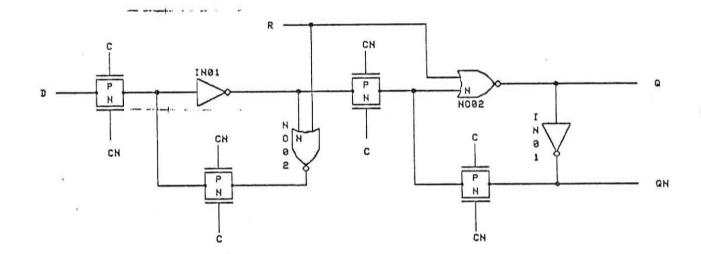

## DESIGN STREAM B - SCHEMATIC CAPTURE AND SIMULATION (Validated Netlist Interface)

#### WHAT GOULD AMI SENDS TO YOU

- 1. All the data needed for Design Stream A

- 2. Sheets describing the functional simulation for each macro

- 3. Timing information for each macro

- 4. Technology file describing the timing information for

- a. different operating temperatures

- b. different operating voltages

- c. process variation

- d. predicted wiring delays based on fanout

- 5. AMI\_ADD\_DELAY program for modifying the simulation timing based on the factors specified in the technology file and GOULD AMI delay equations

- Package Definition program for specifying the gate array packaging arrangement

- Description of each package configuration for use in package definition

#### MENTOR GRAPHICS TOOLS YOU WILL NEED

- 1. NETED for schematic capture

- 2. SYMED for doing hierarchical design

- 3. EXPAND for creating the flattened design to generate the netlist

- 4. SIM for simulation

#### WHAT YOU WILL SEND TO GOULD AMI

- BOLT netlist

- 2. Test vectors

- I/O placement for the selected package type

- 4. Device specifications

### WHAT STEPS ARE PERFORMED AT GOULD AMI

- 1. Perform physical layout

- 2. Generate the capacitance file from the layout

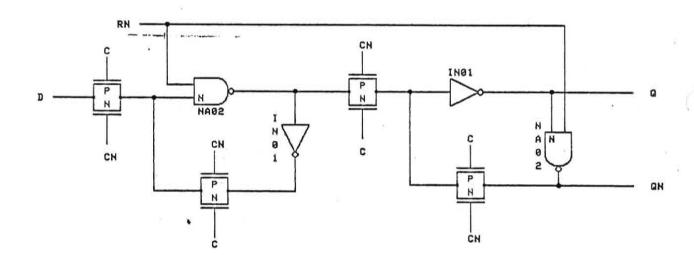

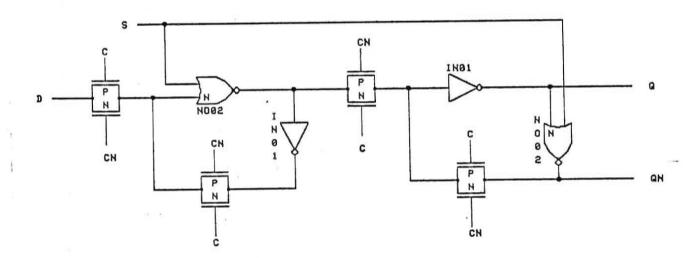

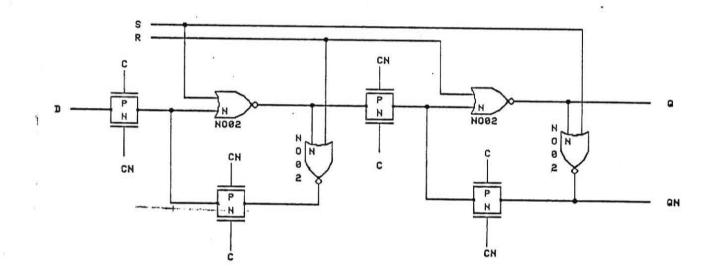

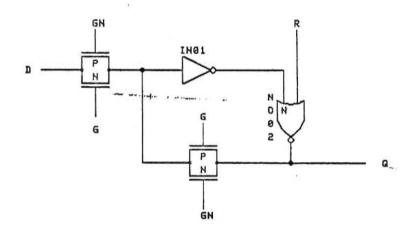

Figure 3-2. Schematic Capture, Simulation and Package Constraints

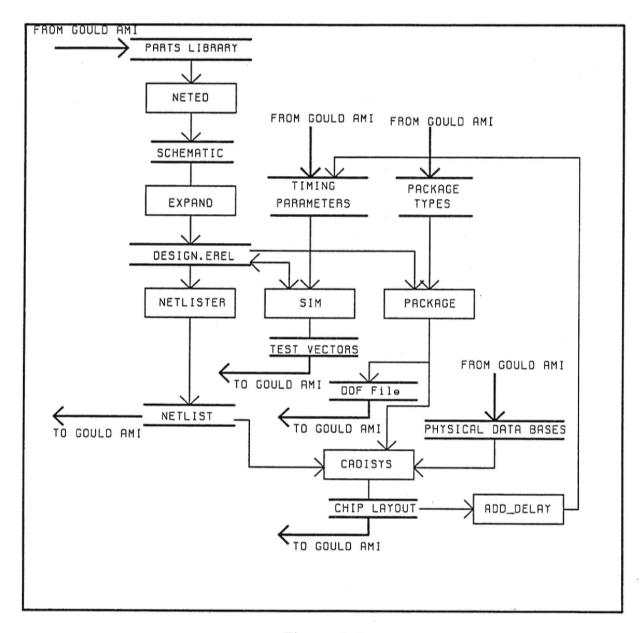

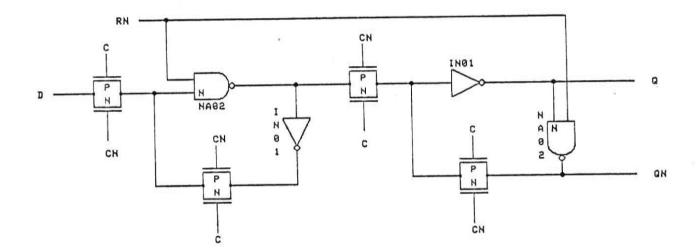

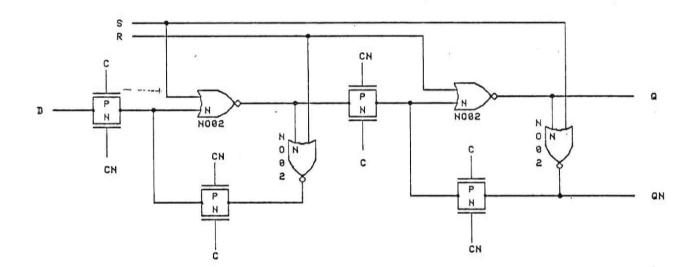

## <u>DESIGN STREAM C - SCHEMATIC CAPTURE, SIMULATION, BACK ANNOTATION AND PHYSICAL LAYOUT</u> (Data Base Interface)

#### WHAT GOULD AMI SENDS TO YOU

- 1. All the data and programs in design streams A and B

- 2. Data bases for physical layout

#### MENTOR GRAPHICS TOOLS YOU WILL NEED

- 1. NETED for schematic capture

- 2. SYMED for hierarchical design

- 3. EXPAND for creating the flattened design to generate the netlist

- 4. SIM for simulation

- 5. CADISYS for doing physical layout

#### WHAT YOU WILL SEND TO GOULD AMI

- BOLT netlist

- Test vectors

- DDF file describing the macro placements and routing data

- 4. Device specification

#### WHAT STEPS ARE PERFORMED AT GOULD AMI

Build the chip

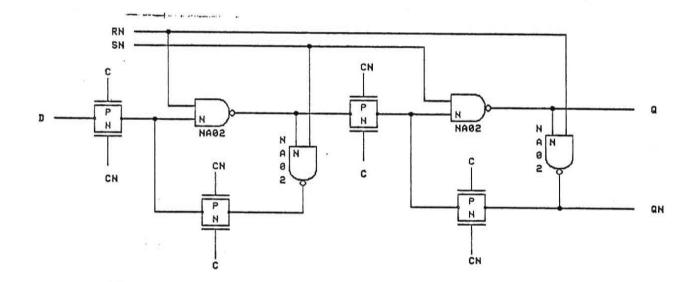

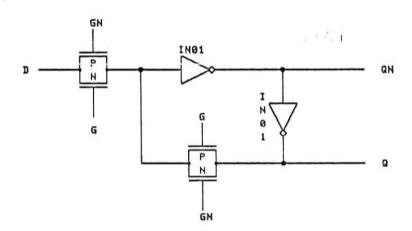

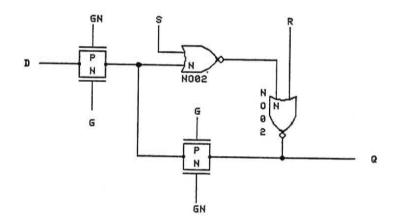

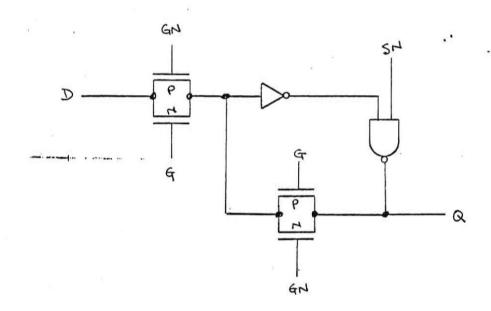

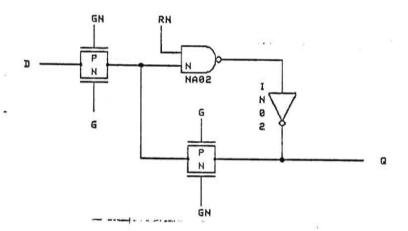

Figure 3-3

### 3.2 Directory Structure

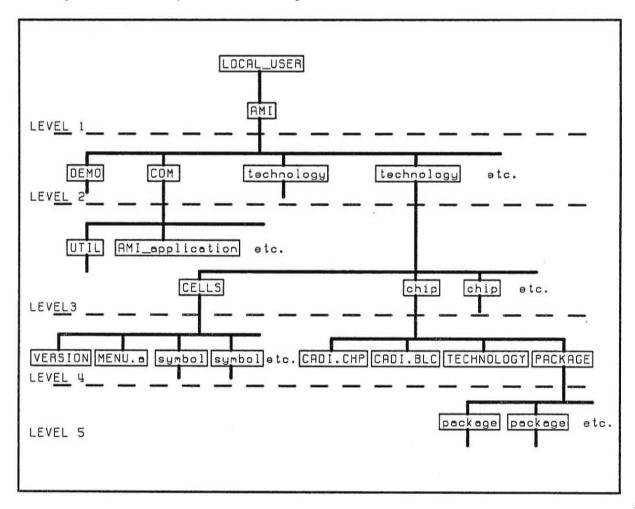

Understanding the directory structure of the GOULD AMI design kit is valuable for doing designs. The naming conventions for the directory structure will be used to describe program execution.

The directory structure is designed to be flexible enough to contain new technologies as they become available and to be expandable as new capabilities are added to the kit. It is also designed to be modular to allow you to delete portions as they become outdated.

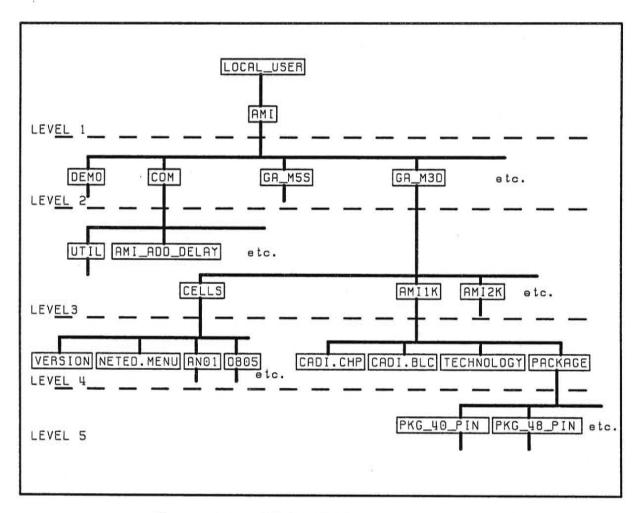

Figure 3-4. Directory Structure

Generic names are used to explain the directory structure. A final diagram will contain the specific GOULD AMI names. In these examples, a simple naming convention is used for directory names: a capitalized name is the name you would see if you looked into the directory. A lower case name in the example will be replaced by a more descriptive name in the actual design kit.

#### Level 1

#### o ~AMI

As figure 3-4 shows, the vendor name appears at the top level. In this case it is AMI. This normally resides in the LOCAL\_USER directory with a pointer to this name in the USER directory. In other words a 'user' should be created for this directory. (For more information on the CREATE\_USER command, type HELP CREATE\_USER or review the <a href="IDEA System Manager's Manual">IDEA System Manager's Manual</a> chapter 7.) This will allow all users on the network to access this directory with the command WD ~AMI. CREATE\_USER is performed automatically with the AMI\_INSTALL command described in section 5 of this manual.

### Level 2

### o ~AMI/DEMO

Under the directory DEMO are the demo circuits for each technology. The actual demo circuit is discussed later in this manual. This directory is for training purposes and can be deleted without affecting designs.

### o ~AMI/COM

The COM directory contains the programs and command files for the GOULD AMI design kit. This includes the command files for AMI\_ADD\_DELAY, AMI\_SIMOUT and so on. This directory should be included in your CSR list (command search rules - type HELP CSR in any AEGIS window for additional information). It is also possible include this CSR in your startup file automatically. Section 5 describes this process.

### o ~AMI/technology

At the second level you will find the directories containing the different types of technologies. For example, you may have a double-level 2 micron gate array library and a two-level 3 micron standard cell library. There may be other technologies at this level as well. Each of these technology directories contains the data specific to that particular technology. This would include the logic symbols, simulation data and so on.

#### Level 3

### o ~AMI/COM/UTIL

This directory contains specific GOULD AMI programs and utility command files.

### o ~AMI/COM/AMI\_application

These are the command files for invoking applications with AMI specific start up sequences. These are automatically activated if ~AMI/COM is included in the CSR list.

### o ~AMI/technology/CELLS

This directory contains all the symbols for schematic capture. These symbols contain the information used to generate netlists. They also contain the information for running a functional and "baseline" timing simulation. A baseline simulation only takes into account the gate delay in the macro. The information for wiring delay and other operating parameters reside in another location. The symbols can be used to build any size chip in the technology family. The timing parameters will vary based on the size of the uncommitted chip.

### o ~AMI/technology/chip

This directory contains all the data specific to a particular uncommitted chip. For example you may have a family of uncommitted chips with gate counts of 1K, 2K, 3K and 4K. Each of these chips would have a separate directory.

#### Level 4

### o ~AMI/technology/CELLS/VERSION

This file contains the version number of this technology and the date the technology was created. This will be used to time stamp your design.

### o ~AMI/technology/cells/MENU.application

There may be several menu files for the different application programs. The menus will be invoked at the beginning of the application. These are ASCII files and can be viewed

### o ~AMI/technology/CELLS/symbol

These are the individual components for schematic capture.

### o ~AMI/technology/chip/CADI.CHP

This is the physical data base describing the uncommitted gate array for this chip size.

o ~AMI/technology/chip/CADI.BLC

This is the physical data base describing the macro library.

o ~AMI/technology/chip/TECHNOLOGY

This is an ASCII file containing the information for running simulations based on chip dependent parameters. Timing, voltage, temperature and fanout parameters are included in this file.

o ~AMI/technology/chip/PACKAGE

This directory contains the sheets for package assignment. Each different package type will be represented by a sheet in this directory

### Level 5

o ~AMI/technology/chip/PACKAGE/package

The sheet for the package type to be used in the package definition program. Each package type is created using NETED.

Figure 3-5 shows an example using the names specific to GOULD AMI. In this example the only technology that is represented is the  $GA\_M3D$  which stands for gate array 3 micron double metal. There are two chip types in the example, the AMI1K and AMI2K.

Figure 3-5. GOULD AMI Directory Structure

#### 4. DESIGN METHODOLOGY

This section provides more detail about the data and programs in your design kit. There are specific features which can simplify gate array design, and these features are highlighted in this section.

### 4.1 Schematic Capture

### 4.1.1 About the symbols

For each macro in a technology there is a corresponding symbol. The symbols reside in the 'technology/CELLS' directory. Symbols can be activated for NETED from this directory. A file containing the NETED commands for creating a menu is located in the file 'technology/CELLS/MENU.NETED'. When this file is executed in NETED, a menu will appear under the COMPONENT LIBRARIES menu allowing you to activate the GOULD AMI components for instantiation in NETED.

The symbol contains information for the programs that access the DESIGN.EREL file. This information is stored in the properties on the symbol. The following list shows each property name and a brief description of its function. When possible, a reference indicates where you can find more information about the property.

You should not use these properties in higher level symbols. This will cause a conflict with some of the design kit programs because they assume that these properties are associated with symbols representing macros.

#### o COMP

This is the name of the macro in the physical data base that corresponds to this symbol. This is the property that links each logical symbol with its physical description in the physical data bases. When the design is expanded for layout it is expanded to the COMP level. For this reason it is important that the COMP property is not used on higher level symbols in the design. The physical layout programs expect to find a macro matching the COMP name.

#### KRISE and KFALL

These are factors used by ADD\_DELAY for converting the loading capacitance into delay times. These properties are attached to the output pins of every symbol. For more information about this property, see the ADD\_DELAY documentation at the end of this manual.

#### o LOAD

This property is used by ADD\_DELAY to compute the new delay due to fanout. LOAD is attached to every input pin and represents the capacitive loading added to the net by the pin. More information about LOAD can be found in the ADD\_DELAY documentation at the end of this manual.

#### o MODEL

The model name indicates to the SIM program which simulator primitive should be used for a given symbol. This property appears only on a primitive symbol or a symbol that uses a behavior language model. The SIM section of the <u>IDEA SYSTEM REFERENCE MANUAL</u> contains more information on this property.

### o PHY PIN

This property is attached to a pin and its value indicates the name of the pin on the physical macro. This property links the pins on the symbol to the pins of the macro in the physical data bases. If this property is not attached to a pin, the PIN property is used to generate the pin name for the physical layout netlist.

#### o PIN

This is the pin name. More information on the PIN property can be found in the SIM section of the <u>IDEA SYSTEM REFERENCE MANUAL</u>.

#### o PINTYPE

This property indicates the direction of the pin to the simulator. More information on the PINTYPE property appears in the SIM section of the <u>IDEA SYSTEM REFERENCE MANUAL</u>.

#### o RISE and FALL

These properties are delay times through the macro. If AMI\_ADD\_DELAY is not run on the design, these are the delay values that will be reflected in the simulation of the circuit. For more information, see the SIM section of the <u>IDEA\_SYSTEM\_REFERENCE\_MANUAL.</u>

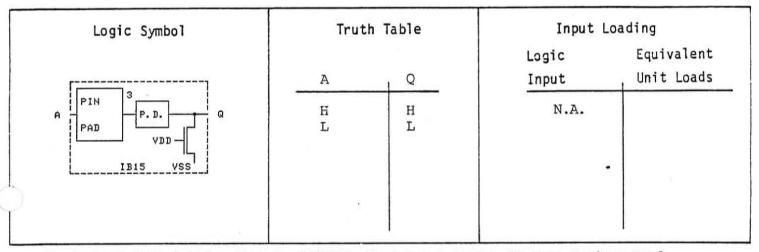

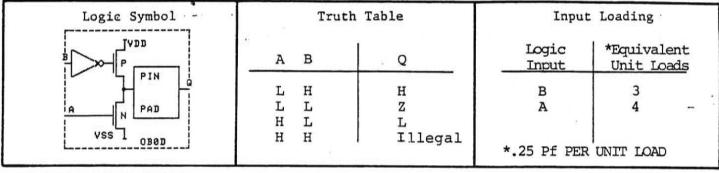

### o SC IO

This property is attached to the I/O macros of the library. The value of the property indicates the type of I/O macro. PKG\_DEF uses

this information to assign I/O macros correctly.

#### 4.1.2 Software Macros

Software macros are created by GOULD AMI to simplify circuit design. These hierarchical macros are represented by a single symbol in the library, but reference the other hardware macros in the library.

Any macro that represents a single physical macro in the GOULD AMI physical data bases is considered a hardware macro. When you use one of these macros you are using a function that is placed on the array as a single entity. This entity ranges from a single inverter to flip flop's and latches. Complete descriptions of all the hardware macros available for design are found in the <u>3µ Single and Double-Metal CMOS Gate Arrays Databook</u>.

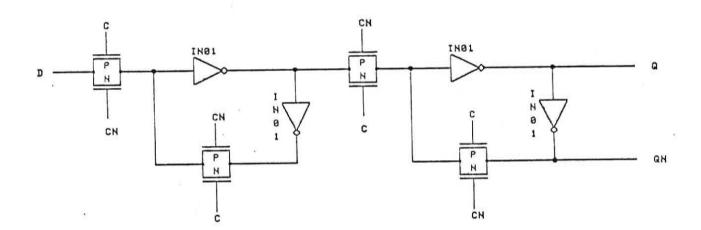

Software macros combine these hardware macros on a NETED sheet to specify a logical function. A symbol representing this function is then created and added to the library. When you instantiate this symbol into your design, you are simply adding another level of hierarchy. The functionality of the software macro has been tested at GOULD AMI. The information for layout that is generated from designs using software macros contains the references to the hardware macros in the physical data base. The layout software will optimize the layout of this macro. When back annotation is performed, the correct delay values will be inserted into the DESIGN.EREL file for each instance of a software macro.

You can create a library of software macros. Once you create a circuit that performs the desired function, you create a symbol to represent it. This symbol can then appear in any other design you have that uses the same GOULD AMI library. Software macros generated from the  $3\mu$  single level library cannot be used in a  $2\mu$  double level design. The simulation and the back annotation program will handle these hierarchical designs correctly so long

you do not use the properties described in section 4.1.1 on your symbol. These properties are reserved for the hardware macros.

### 4.1.3 NETED Features for Gate Array Design

Three features of NETED facilitate gate array design. The following paragraphs explain these features briefly. More detailed information concerning each of these features can be found in the <u>IDEA SYSTEM USERS MANUAL</u> and <u>IDEA SYSTEM REFERENCE MANUAL</u>.

o Hierarchical design

This is a feature of the entire Mentor Graphics system, but it must be considered when entering the schematic.

Symbols represent circuits. A given symbol may be repeated in your design, or it may be used only once. Representing a circuit with a symbol makes the overall design easier to understand. It is possible to create designs that are several levels deep in symbols, with the lowest level of symbols pointing to components from the GOULD AMI library. You may also mix hierarchical symbols and library components on the same sheet.

Each occurrence of a symbol points to the sheet containing the circuit description, so all occurrences of the symbol specify the same function. The circuit in the symbol can be tested independently of the entire design, making the testing of the design easier.

The important concept to note here is that all the tools in the GOULD AMI design kit will work on these hierarchical designs. You can expand each portion of the design and run AMI\_ADD\_DELAY on it independently and predict the behavior of the circuit. When EXPAND is run on the entire design the design is flattened into the DESIGN.EREL file, but the hierarchical information is retained. Back annotation works on this file, so all the true delay values will be represented from the physical implementation.

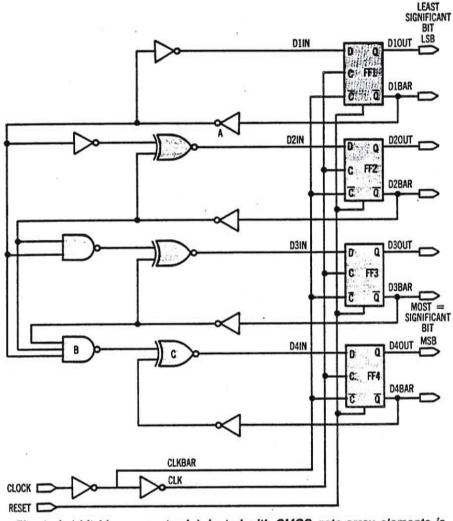

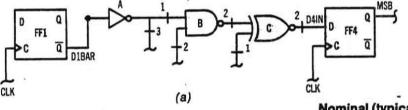

#### o Busses

By using bus naming conventions and bus rippers you can represent multiple signals compactly on your schematic. This makes the schematic easier to understand and easier to draw. Section 4.4 of the <u>IDEA SYSTEM USERS MANUAL</u> gives a tutorial on creating busses and using bus rippers. The sample circuit MAGIC has some simple examples that illustrate the benefits of using busses.

#### o FOR Frames

FOR frames allow you to replicate components using a simple expression. You only instantiate the component or group of components only once and include them in a frame. You then give the frame an expression declaring the number of replications. This has the same benefits as the bus structures. Your schematic is easier to read and more compact. Section 4.5 of the <u>IDEA SYSTEM USERS MANUAL</u> gives a tutorial on using FOR frames. FOR frames used in conjunction with busses are shown in MAGIC.

The command:

### AMI\_NETED circuit

will execute NETED with the GOULD AMI menus included in the component libraries menu.

4.1.4 Defining the I/O's on the Chip

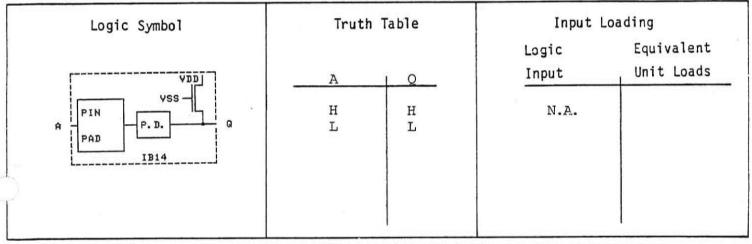

I/O's are the macros that transfer signals between the internal gate array and the outside world. There are special considerations when including these symbols in your schematic.

All the I/O's are prefixed with the letters IB, IO, or OB. The 'I' prefix is for input signals and the 'O' prefix is for output buffers (IOO5 is a bidirectional driver). More information concerning the behavior of all the I/O macros can be found in the Su Single and Double-Metal CMOS Gate Arrays Databook.

It is common practice to assign a net name to the side of the I/O that goes off the chip. This net name is reflected on the root symbol (discussed in section 4.1.6). These net names are normally the pin names for the finished chip. These net names will not appear in the layout because the net names change when they go through the I/O buffer. For ease of use in CADIGRAPH, you should assign an associated net name to the net going to the internal area of the array. As long as this net name is on the top level schematic, the net name will pass into CADISYS unchanged. If the net name is down in the hierarchy of the circuit, a hierarchical name will be assigned to the net. This name is of the form 'instance/instance/assigned net name'.

### 4.1.5 Defining Critical Nets

Nets can be specified as critical to the layout system. When nets are identified as critical, they are given special consideration in both placement and routing. Macros containing the critical net will be placed closer together and the routing of the critical net is done before other nets. There are some ramifications of making nets critical. It can affect the performance of the placement and routing software. Completion rates may be reduced as accomodations are made for the critical nets. For this reason critical nets should be used with discretion.

To assign a critical net you would perform these steps in NETED :

- 1. Define the owner of the PRIO property: 'OWNER PRIO -NET'

- 2. Select the critical net

- 3. Add the PRIO property to the net: 'ADD PROP PRIO value'

space of a reflection real production of the pro

The PRIO property indicates that this is a critical or priority net. The values for PRIO range from 0 to 16. Zero specifies no priority; 16 is the highest priority. A given priority value is not unique for a design. Several nets can have the same value because it is a weighting factor, not a net identifier.

There are three factors to be considered when assigning critical nets.

- Critical nets should be used sparingly because of the reasons listed above.

- 2. Assigning priority to a large net (greater than 20 pins in the net) may not produce good results. In this case, it may be wise to consider preplacement and prerouting (see section 4.4).

- 3. If a priority value is assigned to a net that is repeated in the hierarchy of the design, every occurrence of that net will have a priority value. For example:

- a. Net N\$1 is assigned priority 10 in component A

- b. Component A is instantiated in component B four times

- c. Component B is instantiated in the top sheet 2 times

There are 8 occurrences of the net with a priority of 10

This does not cause an error, but will affect placement and routing as described in the beginning of this section.

### 4.1.6 Creating a Root Symbol

It is necessary to create a root symbol for your chip. This provides information to the layout programs and is used when you generate the data to transfer your design back to GOULD AMI.

The symbol can be as simple as a box with a pin and a name for each pin on the chip. In general these pin names correspond to the output net names on the I/O buffers. Each pin on the symbol must have a PINTYPE property. The value of the PINTYPE property can be :

- IN for input signals

- 2. OUT for output signals

- IO for bidirectional signals

If you do not have a PINTYPE property you will not be able to generate correct test vector files. If the PINTYPE property is not one of the 3 listed values you will get incorrect test vector files.

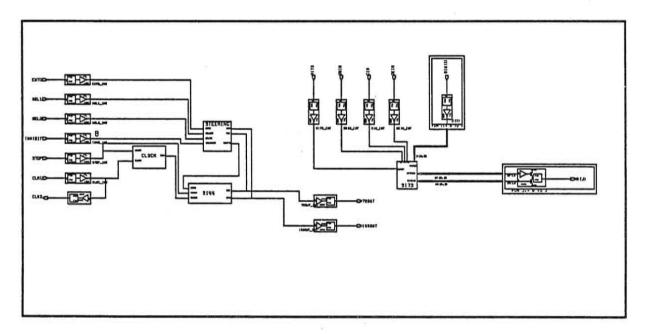

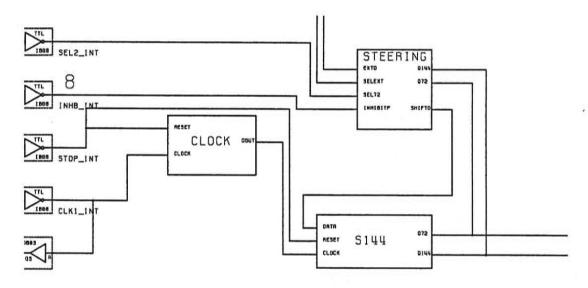

MAGIC demonstrates the correspondence between the root symbol and top level schematic.

#### 4.2 Simulation

When you use the GOULD AMI libraries, SIM and AMI\_ADD\_DELAY you can achieve three results :

a functional and timing analysis of the design before any layout has been performed

The symbols contain the necessary information for functional and base line timing simulation. The AMI\_ADD\_DELAY program in conjunction with the technology data supplied for each array, allows you to vary the operating conditions for the circuit.

2. a timing analysis of the circuit once layout has been performed

The AMI\_ADD\_DELAY program will read the capacitance values from layout and modify the DESIGN.EREL file so that the simulation reflects these accurate models.

3. test vectors generated from your simulation

You will be able to deliver a set of test vectors to GOULD AMI for testing your circuit once it has been fabricated. GOULD AMI will be able to automatically generate the commands for their test equipment from the test vectors.

### 4.2.1 How to Design for Useful Simulation

You can increase the testability of your circuit by considering three factors:

- 1. Initialization The ability to set the circuit to a known state at the beginning of the test cycle.

- 2. Controlability The ability to set the internal nodes of the circuit to a given state with external signals.

- Observability The ability to observe at an output pin, the state of an internal node.

More information concerning these concepts can be found in section 6.3 of the <u>Su Single and Double-Metal CMOS Gate Arrays Databook</u>. This section appears as an appendix to this manual.

### 4.2.2 The Different Conditions for Pre-Layout Simulation

Pre-layout simulation can be performed under 6 conditions and several combinations of these 6 conditions. This is achieved using the AMI\_ADD\_DELAY program. The appendix of this manual contains the AMI\_ADD\_DELAY User Manual. This document explains the input data and equations used by the program in some detail.

In this section, the six simulation conditions are described and the setup for each condition is demonstrated.

### 4.2.2.1 Gate Delay Only

When you run AMI\_EXPAND\_DESIGN on a design, a new DESIGN.EREL file for SIM is created. The only delay values that are associated with each net are the RISE and FALL delays associated with each macro. If you run SIM at this point you will get the gate delays only.

To run a simulation using only gate delays you perform the following steps:

- 1. AMI EXPAND DESIGN circuit technology this will create the new DESIGN.EREL file for the design, circuit.

- 2. SIM circuit you will now be ready to run the simulator.

The command AMI\_EXPAND\_DESIGN runs the Mentor Graphics EXPAND program and creates the design file that is expanded to the primitive level. The design file contains the same information as file generated using EXPAND and the SIM SETUP command. AMI\_EXPAND\_DESIGN will not take over the display when it is executed.

### 4.2.2.2 Fanout Loading Delay

When you run AMI\_ADD\_DELAY it normally calculates the delay due to fanout loading and adds this to the total delay for each net. The only exception occurs when you ask for only layout delay (described in section 4.2.2.3). Also, when you run AMI\_ADD\_DELAY you get the delay from the predicted wiring added to the total delay for the net, unless you specify only fanout delay. The default for AMI\_ADD\_DELAY adds both the fanout and predicted wiring delays to the DESIGN.EREL file.

To run a simulation using both fanout and layout delays perform the following steps:

- AMI\_EXPAND\_DESIGN circuit technology— if you have a current DESIGN.EREL file this is not necessary

- 2. AMI\_EXPAND\_COMP circuit technology- this will create a COMP.EREL file

- AMI\_ADD\_DELAY circuit technology array this will modify the DESIGN. EREL file to contain the new delay values

- 4. SIM circuit ready for simulation

The AMI\_EXPAND\_COMP command again runs the Mentor Graphics program EXPAND, but now expands the design to the component level. The values for fanout calculation reside at the component level. Again, you will not see EXPAND take control of the display. This expansion will run faster than AMI\_EXPAND\_DESIGN because you are not expanding to the primitive level.

The parameters for AMI ADD DELAY are

- 1. circuit the design name

- 2. technology the GOULD AMI technology; GA\_M3D, GA\_M2D etc.

- 3. array the array that is being used; AMI1K, AMI2K etc.

The technology and array names are described in more detail in section 3.2 of this manual and a list of all possible technology and array combinations is included as an appendix of this manual.

To run a simulation using fanout delay only, perform the following steps :

- 1. AMI\_EXPAND\_DESIGN circuit technology if you have a current DESIGN.EREL file this is not necessary

- AMI\_EXPAND\_COMP circuit technology- this is not necessary if you have a current COMP.EREL file

- AMI\_ADD\_DELAY circuit technology array -FO the format of this command is the same as above, but now the switch -FO indicates that this is fanout only

- 4. SIM circuit ready for simulation

### 4.2.2.3 Predicted Wiring Delay

As described in section 4.2.2.2, the default for AMI\_ADD\_DELAY is to calculate and include the predicted wiring delay for simulation. The method for simulating with both fanout and predicted wiring delays appears in section 4.2.2.2.

To run simulation with predicted wiring delay only, perform the following steps:

- AMI EXPAND DESIGN circuit technology if you have a current DESIGN.EREL file this is not necessary

- AMI\_EXPAND\_COMP circuit technology if you have a current COMP.EREL file this is not necessary

- 3. AMI\_ADD\_DELAY circuit technology array -LO the switch -LO will update the delay values in the DESIGN.EREL file with predicted layout only

- SIM circuit ready to simulate

The parameters and programs are the same as those described in section 4.2.2.2.

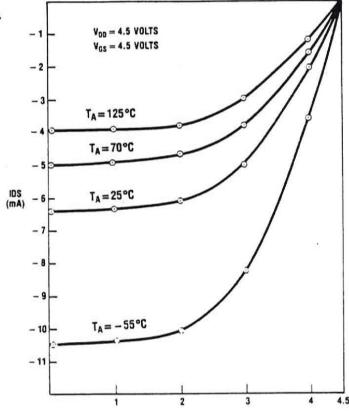

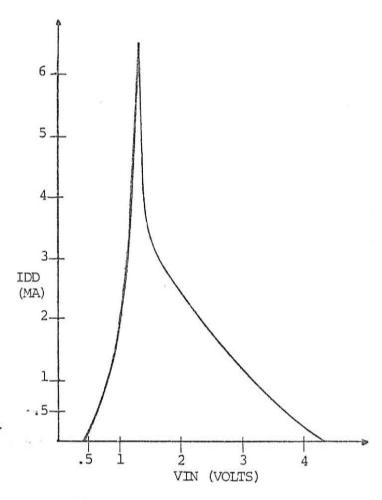

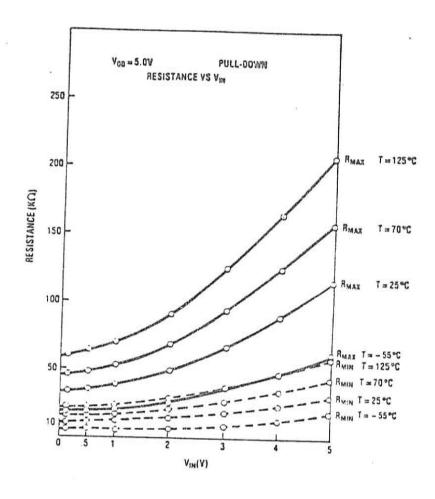

### 4.2.2.4 Varying the Delay Based on Temperature

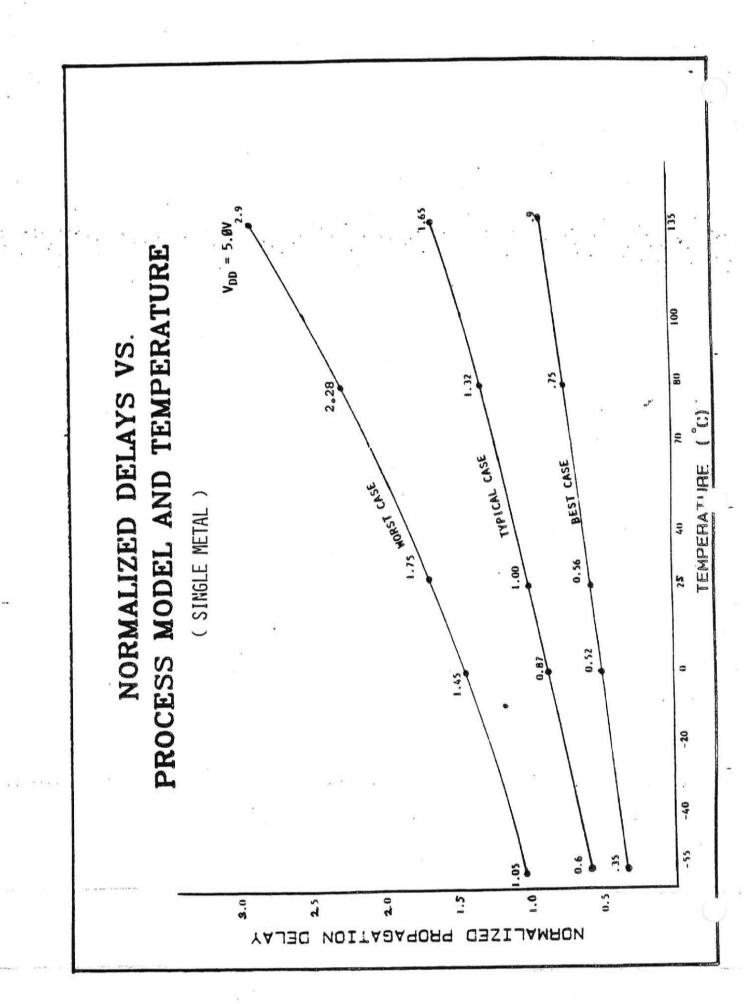

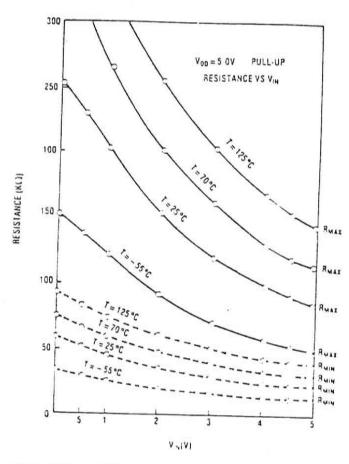

The operating temperature of the chip affects its performance. You can simulate thes operating conditions by specifying an operating temperature to AMI\_ADD\_DELAY. AMI\_ADD\_DELAY reads the equation describing temperature affects from a file. This file is created for each technology/array combination. From this file a multiplicative factor is generated and used to modify the delay values of the entire array. This process is described in more detail in the AMI\_ADD\_DELAY\_USERS\_MANUAL appears as an appendix to this document.

A word of caution - Though the AMI ADD DELAY USERS MANUAL describes the method for building files that contain the coefficients for temperature equations, you should not change these coefficients. The equation they describe was derived from experimental data on test arrays. Changing the equation will decrease the accuracy of the procedure for modeling the behavior of GOULD AMI arrays.

To run a simulation with a specific operating temperature perform the following steps:

- AMI\_EXPAND\_DESIGN circuit technology if you have a current DESIGN.EREL file this is not necessary

- AMI EXPAND COMP circuit technology if you have a current COMP.EREL file this is not necessary

- AMI\_ADD\_DELAY circuit technology array -TEMP number the -TEMP switch followed by a value (in degrees Centigrade) will modify the delays for circuit.

- 4. SIM circuit ready for simulation

In this example, the fanout and predicted wiring delays will also be included in the new delay values. The -TEMP switch can be used with the -LO and -FO switches as well. The -TEMP switch can also be used with the -V and process switches described in sections 4.2.2.5 and 4.2.2.6.

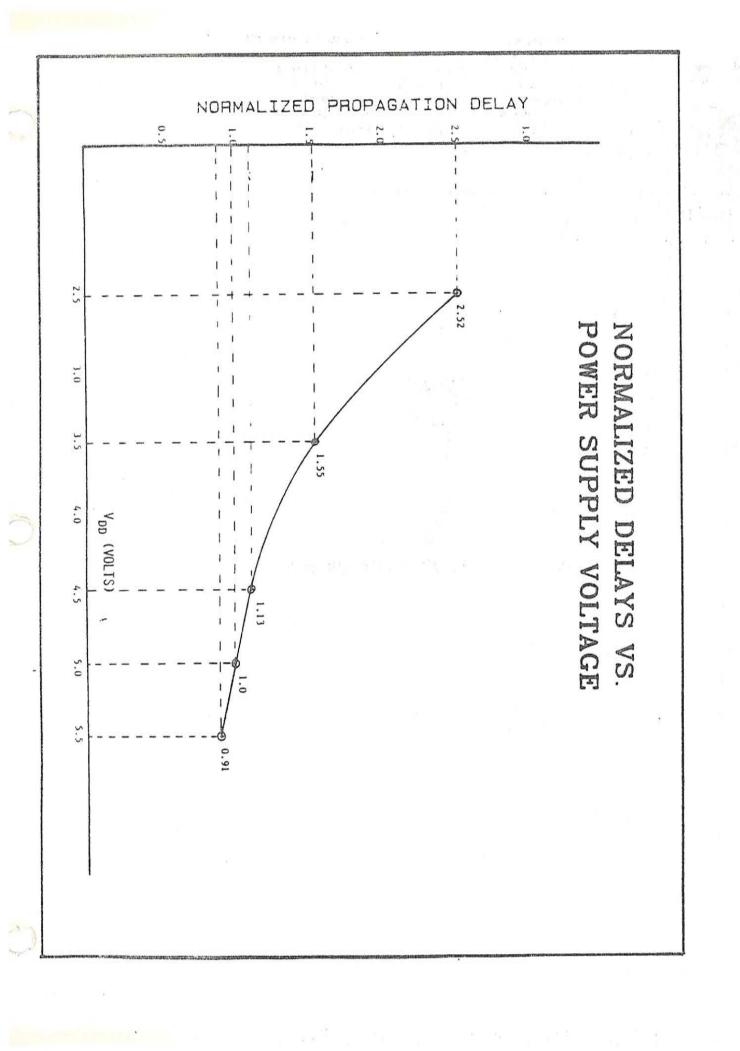

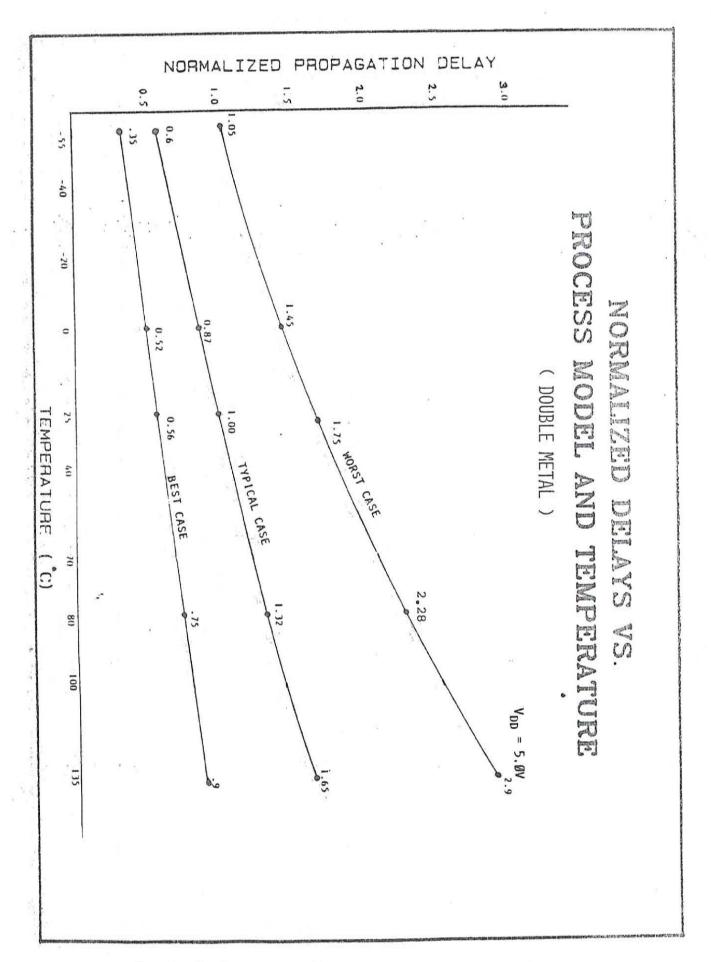

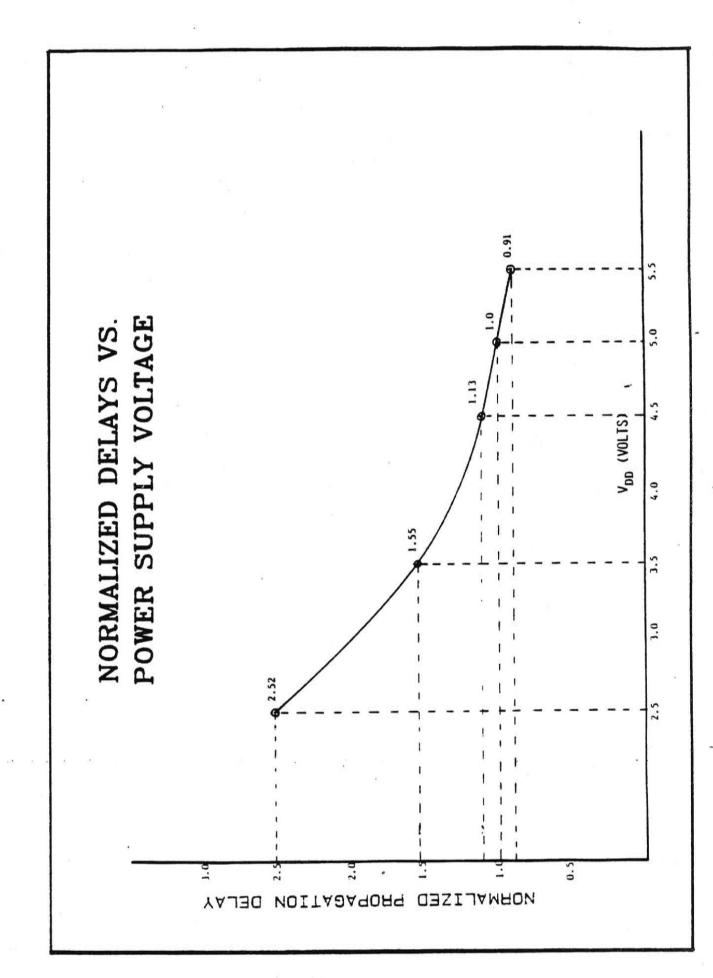

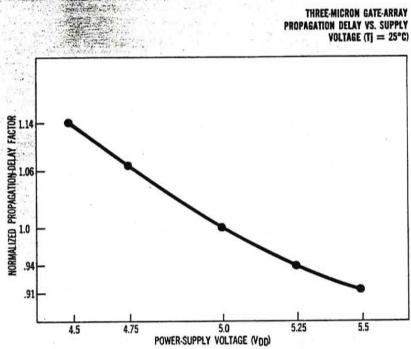

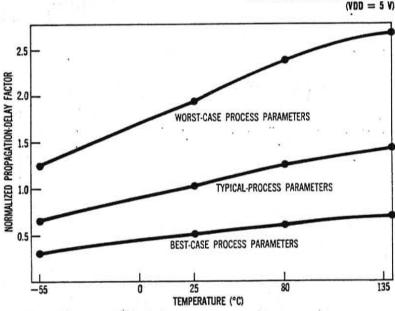

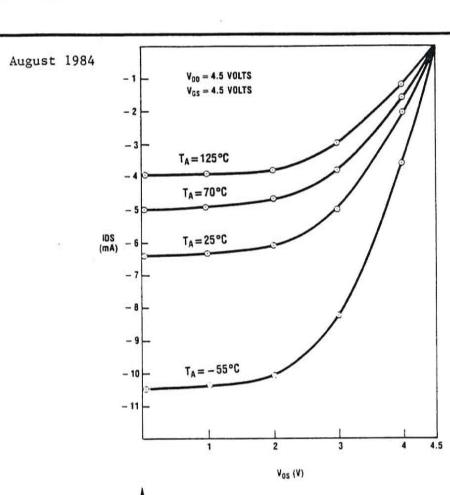

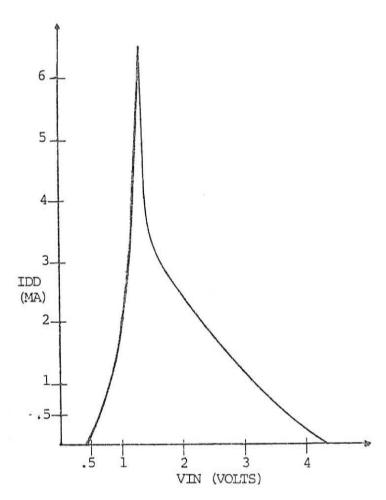

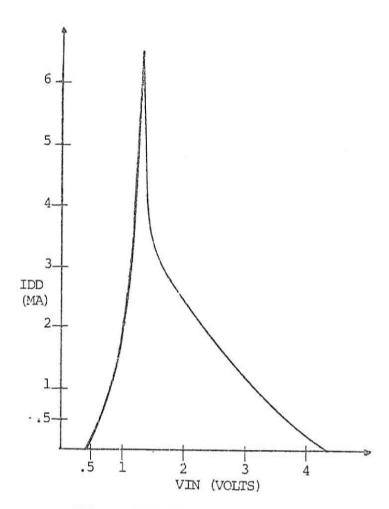

The current range for the temperature value is -55 to 135 degrees Centigrade. If you enter a value outside this range, an error message will appear in the output report file and the delay values will not be modified. The multiplicative factor for the delay values created by the new operating is in the output report. This report 'circuit/ADD DELAY.LOG'. The operating temperature that gives multiplicative factor of 1 (nominal operating temperature) is 25 degrees. A. curve displaying the affect of temperature on the performance of the array is included at the end of the 3μ Single and Double-Metal CMOS Gate Arrays Databook.

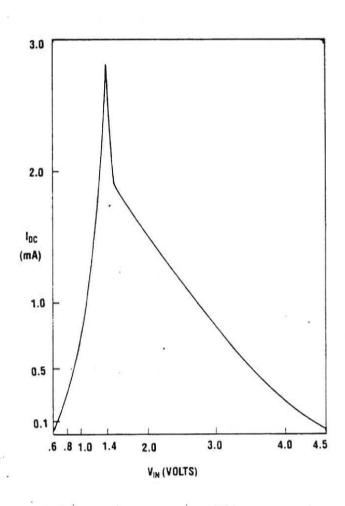

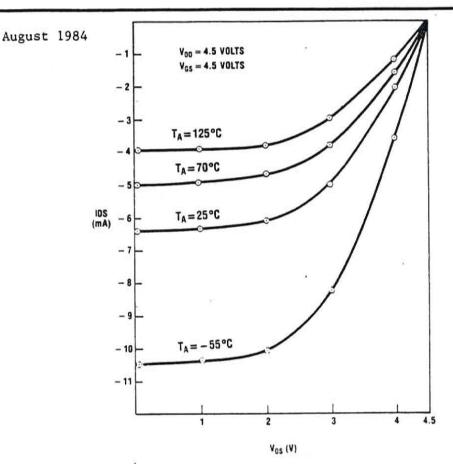

### 4.2.2.5 Varying the Delay Based on Voltage

As described in section 4.2.2.4, the operating voltage will affect the performance of the design. The method for altering the delay values based on operating voltage is the same as described for operating temperature. The word of caution also applies; do not change these files.

To run a simulation with a specific operating voltage perform the following steps :

- AMI\_EXPAND\_DESIGN circuit technology if you have a current DESIGN.EREL file this is not necessary

- 2. AMI\_EXPAND\_COMP\_circuit\_technology if you have a current COMP.EREL\_file this is not necessary

- 3. AMI\_ADD\_DELAY circuit technology array -V number the -V switch followed by a value will modify the delay values

### 4. SIM circuit - ready for simulation

In this example the fanout and predicted wiring delays will be calculated and used as well. The -V switch can be used with the -LO, -FO, -TEMP and process switches.

The current range for the voltage value is 4.5 to 5.5 volts. If you enter a value outside this range, an error message will appear in the output report file ('circuit/ADD DELAY.LOG') and the delay values will not be modified. The multiplicative factor for the delay values created by the new operating voltage ( and temperature if applicable) is in the output report. The operating voltage that gives a multiplicative factor of 1 (nominal operating voltage) is 5 volts. A curve displaying the affect of voltage on the performance of the array is included at the end of the  $3\mu$  Single and Double-Metal CMOS Gate Arrays Databook.

### 4.2.2.6 Varying the Delay Based on Process

There are three process conditions that are defined for modifying the delay values. The default value is the nominal process, and multiplies all the delay values by 1. You can also choose best and worst case process conditions for simulation.

To run a simulation with either best or worst case process, perform the following steps:

- AMI\_EXPAND\_DESIGN circuit technology if you have a current DESIGN.EREL file this is not necessary

- 2. AMI\_EXPAND\_COMP circuit technology if you have a current COMP.EREL file this is not necessary

- 3. AMI ADD DELAY circuit technology array -BEST (-WORST) the -BEST (-WORST) switch indicates that nominal process is not being used, and the multiplicative factor for the delays should be modified accordingly.