# The Computer Museum

300 Congress Street Boston, MA 02210 (617) 426-2800

March 5, 1984

Stephen Swerling Vice President-Engineering Mentor Graphics Corporation 8500 SW Creekside Place Beaverton, OR 97005-7191

Dear Steve,

Delighted to have met you at the AEA meeting in Portland. It was especially nice for me that you were enthusiastic about The Computer Museum. A copy of the most recent issue of our quarterly, The Computer Museum Report, is enclosed.

You are personally invited to become one of our Founders — a unique opportunity that lasts until June — to help an international institution get off the ground.

I hope that you will urge Mentor Graphics Corporation to become a Corporate Founder (\$2500).

Software is one of the most difficult things to exhibit at the Museum — and the issue that everyone talks about. If you have any ideas about how your products might be used to explain CAD, I'd be delighted. We are planning a major gallery on "The Computer and the Image" developed by Dr. Oliver Strimpel. His proposal for this gallery is enclosed and if you see any way for Menotor to be involved, we'd love to have you. We do have an excellent relation with all the folks at Apollo and will have a work station or two, as needed.

To give you some background, the Museum was started by Digital in 1979 based on Ken Olsen's and Gordon's collection. Then, in 1982, it was established as a separate entity with its own Board of Directors. This year a home was found for it on Boston's Museum Wharf, where it will open on October 1. It is a nonprofit, public, charitable foundation dedicated to preserving and exhibiting an industry-wide, broad-based collection of the history of information processing. Computer history is interpreted through exhibits, publications, videotapes, lectures, educational programs and other activities. The Museum archives both artifacts and documentation and makes the materials available for scholarly use.

When you are in Boston let us know and we will give you a behind-the-scenes look at the Museum.

503-626-7000

Cordially, Director

GB/jb encl. cc:

cc: Oliver Strimpel

Original Apollo : 'Green Node': had green node;

Sales off Lesungton

Rt 4 + 225 8635776 Belfind St J Bren Denin Watts ad Nof P

SWERLING, Stepher

of station

# The first fully integrated and computerized design path from concept to prototype test.

Rising gate counts. Tighter real estate requirements. Increased functionality. Compressed product development cycles.

They're all facts of life for today's hardware design engineer. And they won't go away any time soon.

The only real solution is to take full advantage of state-of-the-art VLSI computing power and make it an integral part of your hardware design team. From initial concept all the way to verification of the prototype.

Moreover, this computer power must be applied in such a way that each individual computerized engineering tool is fully integrated into the design system as a whole. And that the system itself gives you maximum flexibility, performance and growth potential.

Only one computer-aided engineering (CAE) system satisfies all these requirements.

The Mentor Graphics IDEA 1000.

Why? Because Mentor Graphics is both a pioneer and leader in the field of computer-aided engineering. We're working from a solid knowledge base to bring you CAE solutions that combine unmatched performance depth with a level of system-wide integration found only in the IDEA 1000.

With Mentor Graphics, you're assured of a single CAE design path from concept to prototype test. A path that gives you more room for increased productivity and innovation than ever before possible.

### Network architecture yields optimum performance.

At the heart of the IDEA 1000 system is a networked computer architecture that brings you all the benefits of a timeshared host computer, but none of the disadvantages.

The IDEA system uses any number of engineering workstations connected together in a high-speed (12 Mbits/ sec) network. Each workstation has its own Apollo DOMAIN 32-bit computer with resident hard disk storage and high-resolution graphics hardware. Every workstation has complete, transparent access to data stored anywhere within the system. You get the centralized file organization of a host system, but without performance degradation of timesharing on a central CPU.

Further, the Mentor network can include gateways to mainframes for access to existing CAD tools through protocols such as Ethernet, X.25, HASP or 3270 emulation. Also, peripheral and computational servers within the network can provide all workstations with common resources such as printers, plotters and array processors.

#### DBMS system forms a solid yet flexible foundation.

The core of any engineering design system is the data used to describe and test the design. Because the database plays such a critical role, Mentor has designed its own Full Relational Database Management System targeted specifically at the needs of electronic engineering organizations.

You get a complete set of data management tools which control and safeguard your data movement as it evolves during the engineering process. Files are automatically monitored for conditions such as version updates, data interdependencies and access rights.

Mentor's DBMS also allows a great deal of flexibility without any risk to the integrity of stored data. Different programs can access the same data file in any format a particular application calls for. New data formats can evolve without modifying applications programs. Equally important, new design engineering tools can be introduced without modifying existing ones or the data they use.

# Uniform interface molds to individual styles.

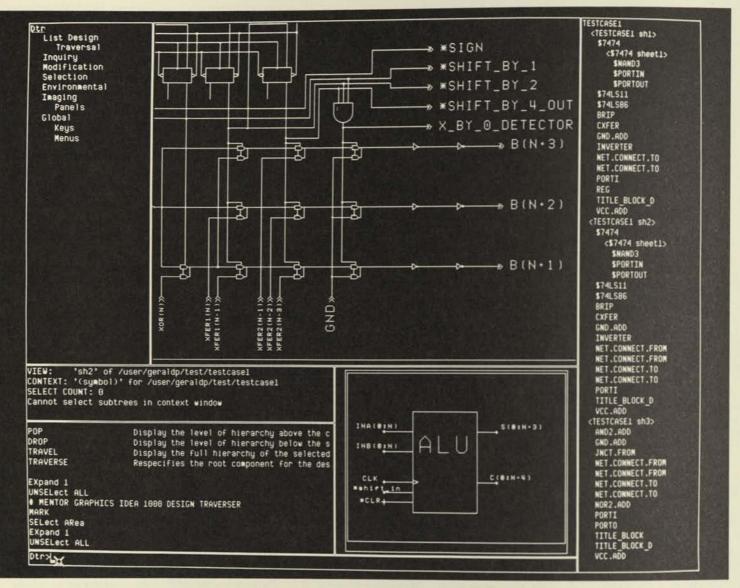

One of the central challenges in computer-aided engineering is to present the user with an interface that remains consistent as different design tools are used. This way, the engineer's learning curve is kept to a minimum and applies across the entire system.

Mentor's IDEA 1000 interface solves the problem through a high resolution, graphics interface that remains the same across the entire Mentor tool set. This interactive interface includes a rich set of features such as on-line help, tutorials, command macros, soft keys and programmable display windows. The result is an interface that is rapidly learned and grows in sophistication along with the user, who can "customize" it to individual working styles.

### Select from a highperformance hardware lineup.

A Mentor engineering workstation can be configured from any Apollo DOMAIN computer, giving you broad latitude in selecting the optimum hardware mix for your particular engineering environment. All workstations feature powerful 32-bit processing, local hard disk storage and high resolution graphics hardware.

The IDEA 1001 and 1002 represent the ultimate workstation processing performance. Each has a CPU with 32-bit external and internal data paths, providing throughput comparable with even the largest of supermini computers. At a single workstation, you can run up to 24 concurrent processes, with 256 Mbytes of virtual memory per process.

The IDEA 1200/1300 puts mainframe processing power at the desktop level and becomes a cost-effective addition to any Mentor network.

The IDEA 1000 Series brings powerful 32-bit processing and high-resolution color graphics to the entire range of Mentor design tools.

# Capture your front-end creativity as well as your schematics.

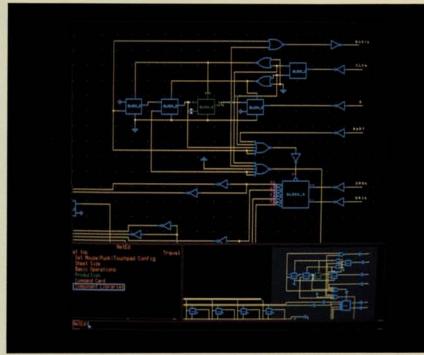

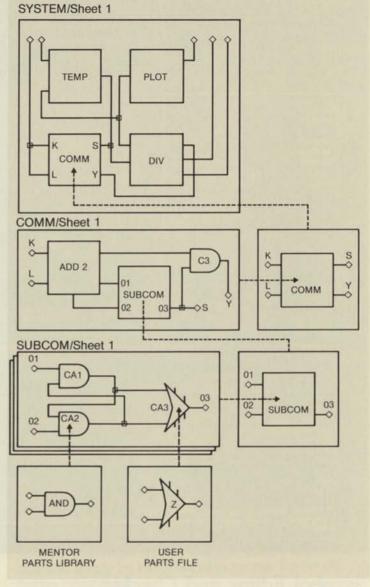

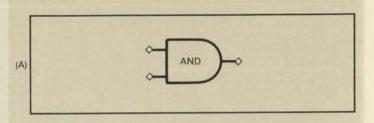

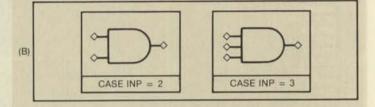

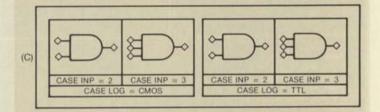

#### Hierarchical design entry promotes innovation.

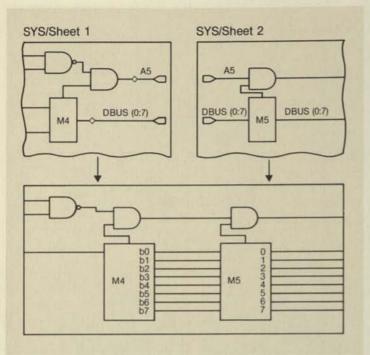

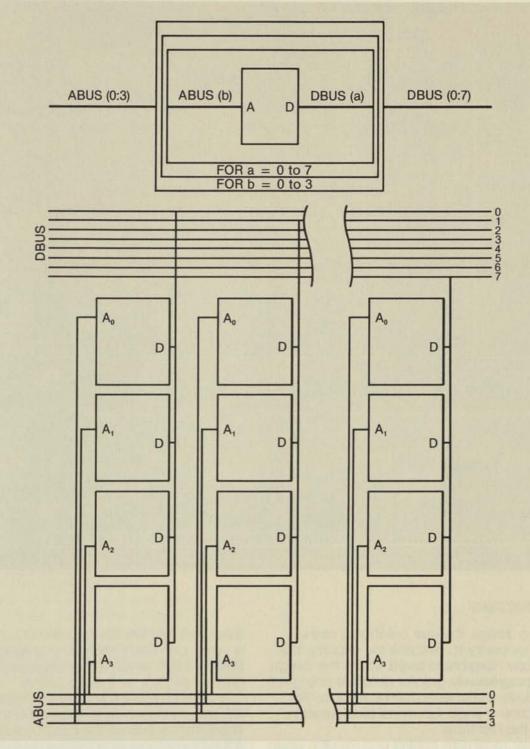

Mentor goes a step beyond graphic entry of "flat" schematic sheets and also lets you approach your design in a hierarchical fashion. You express your design in its broadest functional terms at the "top" of the hierarchy as a series of interconnected function blocks.

As your project progresses, lower layers in the design hierarchy express these functional elements in ever finer detail. At the bottom you have a fully expanded design expressed in its most primitive elements, such as interconnected gates or transistors. When building your hierarchy, you can start at any level you choose and then work either up or down.

The advantage of this approach is that you can view and perceive your design from many different perspectives, depending on your position in the hierarchy. This gives you vastly expanded opportunities to make innovative modifications. And to make them quickly and easily.

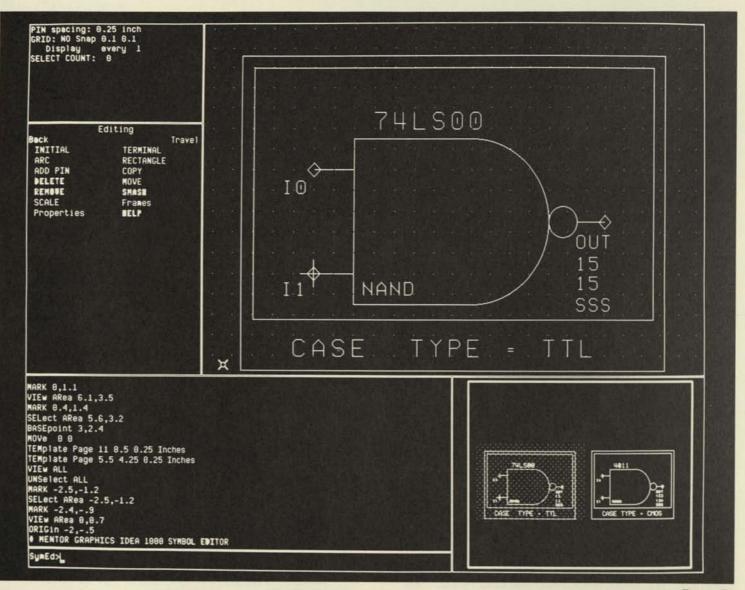

# Use standard symbol parts or create your own.

While some schematics require only "standard" electrical parts symbols, such as TTL, many others will require custom parts. In either case, Mentor gives you a solid solution.

For standard parts, Mentor furnishes a series of parts libraries that meet many different types of applications requirements, including gate array design.

For custom parts, The IDEA 1000 Symbol Editor gives you a powerful graphic tool set to create symbols for even the most complex parts.

#### Graphic tools speed schematic entry.

The graphic placement and interconnection of parts symbols often consumes a very large portion of a designer's time. Accordingly, Mentor gives you a high-performance Network Editor that puts a powerful array of graphics-oriented tools at your disposal. Schematic entry is faster, easier, and more accurate.

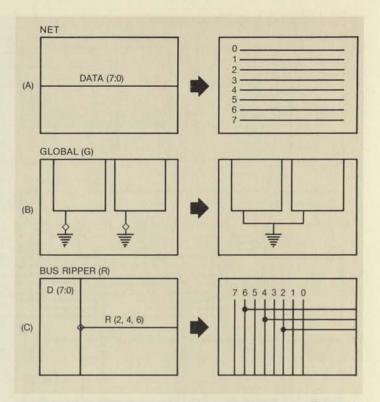

You can invoke powerful graphics commands that simultaneously move, pivot or rotate whole groups of symbols. Or use a single line to define an entire data bus. Or call upon "frames" to express large volumes of repetitive circuitry in just a few symbolic entries.

# Netlisters allow remote simulation/layout.

To protect your current engineering software investment, Mentor provides a broad range of netlisters that transform IDEA 1000 schematic data into formats acceptable by simulator and layout programs resident on a host mainframe.

This includes simulators such as Tegas and Logcap, and layout programs such as SCI-CARDS and Computervision. Further, you can use Mentor's complete programming environment for creating your own netlisters to interface proprietary engineering tools.

The IDEA 1300 is a cost-effective workstation for schematic entry tasks and includes a 17" highresolution CRT.

# Simulate your way around costly prototype revisions.

# Logic analysis in software.

One of the principle advantages of the Mentor IDEA 1000 system is that your entire design is captured and preserved in the system's database. This means that many of the debug operations that once required a hardware prototype can now be performed entirely in software.

As a result, you can save yourself many costly prototype iterations by performing the vast majority of your debug operations before the design ever reaches the physical prototype stage.

#### Start debugging even before your design's complete.

One powerful advantage of simulation using the IDEA 1000 system is that you don't have to wait for the completed design data to begin debugging. You save time, cut costs and considerably reduce the complexity of debug operations.

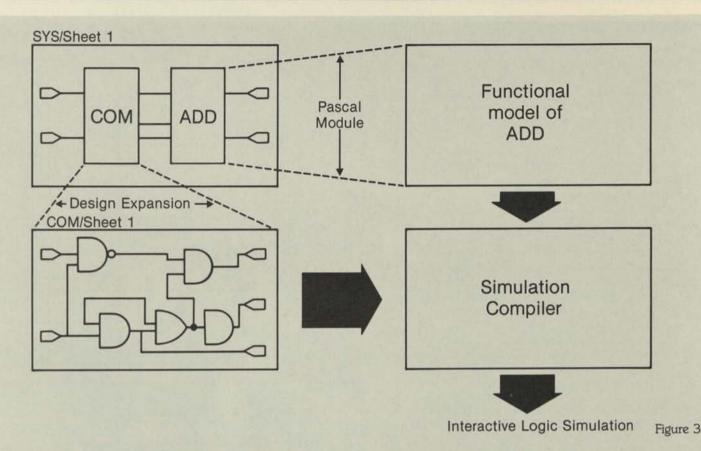

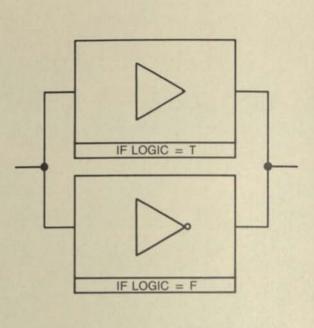

It's done through a technique called Functional Modeling, which emulates the logical behavior of components that have not yet been designed down to the gate level. Each component is described through a Pascal-based behavior language which describes the circuit's logical outputs in response to input stimulus.

During simulation, these functional models can be freely intermixed with fully designed circuitry to give you a highly accurate preview of how your completed design will perform.

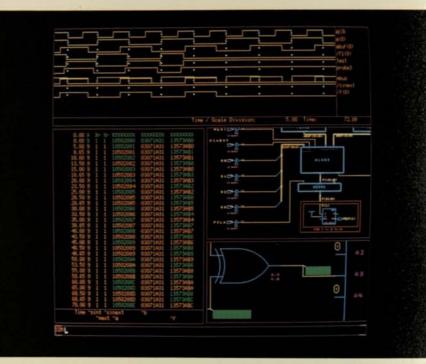

#### Interactive logic and timing simulation reveal potential errors.

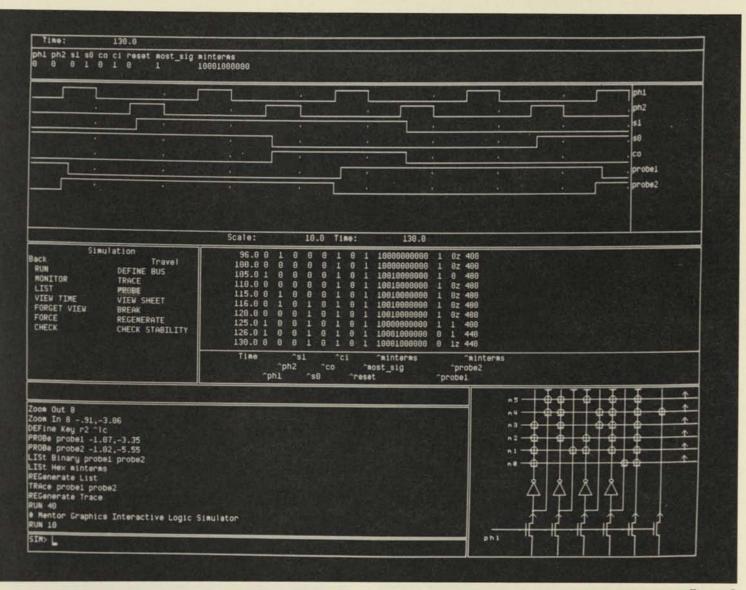

Mentor's interactive interface puts logic flow displays and circuit diagrams on the same screen at the same time when you're performing simulation tasks. You get a direct visual relation-

ship between the circuitry under test and its logical behavior. You can even graphically "probe" individual circuit nodes to monitor or force their states.

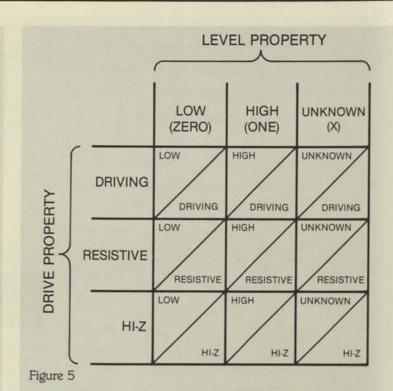

You're not limited by technology, either. Mentor's simulators can accommodate components from gates to PLA's. It also covers MOS as well as TTL and ECL, and supports nine distinct logic states.

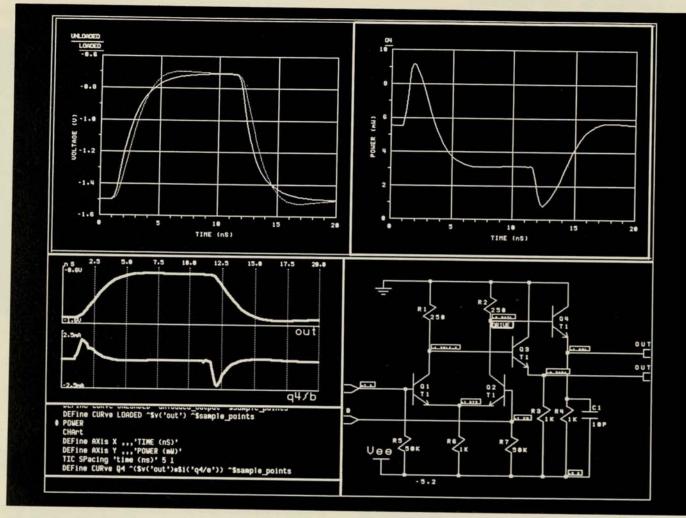

# MSPICE models the analog side of your design.

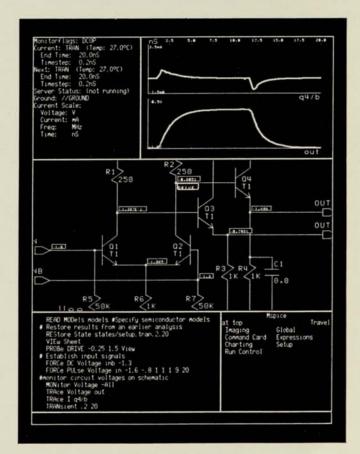

If you are designing down to the analog circuit level, you can model your design's analog behavior through MSPICE, Mentor's version of the popular circuit simulator program.

MSPICE represents a significant ad-

vance in analog simulation because it automates the cumbersome input and output operations associated with conventional SPICE programs.

MSPICE works directly with the Mentor design database to extract the information required to perform DC, AC, DC operating point or transient analysis. During a simulation session, you can call up the schematic to be simulated and graphically modify circuit parameters. You can even specify points of interest in the schematic and watch their parameters change during the actual simulation run.

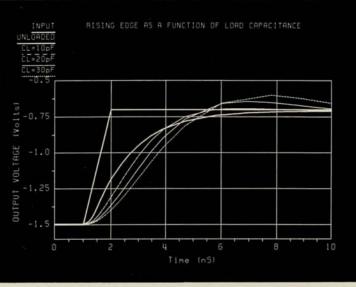

Simulation results are displayed graphically on the high resolution user interface. You can also call in powerful post-simulation processing programs to calculate and graphically display any specific information that your application requires.

The IDEA 1002 provides the 32-bit processing performance that many digital and analog simulations require.

# Automate a wide range of physical layout tasks.

# Fully automatic gate array layout.

Mentor's CADISYS gate array physical design package represents a dramatic leap in the automation of gate array layout. Designs that once took months to move from the schematic stage to the physical layout stage can now be done in a matter of hours.

Besides enormous time savings, you benefit from a state-of-the-art performance level. When converting your schematics from symbols to completed silicon placement, the automated CADISYS typically offers over 90% gate utilization, and connection rates that are typically 98% to 100%.

These outstanding performance levels mean your design will often fit on a smaller, less costly gate array. Also, you can implement more functions in an array of any given size. You save real estate, you save time, you save money.

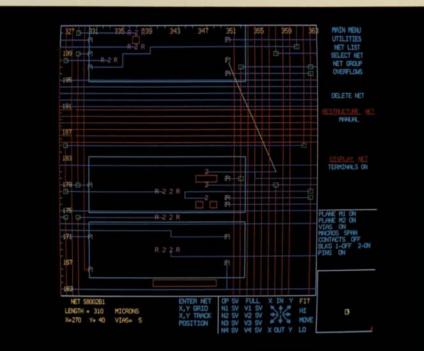

### A streamlined path from block placement to final layout.

Mentor's CADISYS gets you through the gate array physical layout process in three easy steps that not only get your design done faster, but also more efficiently.

First, Mentor CADIPLACE takes your design and puts it onto the gate array image so that performance and routability are optimized.

Second, Mentor CADIROUTE works with the placed functional blocks and automatically performs the interconnections.

Third, Mentor CADIGRAPH provides an interactive tool for use either before or after automatic routing. You can quickly predefine critical routes or rapidly finish up any overflow connections.

#### Design data feedback permits a faster finished product.

When a logic schematic version of a design is transformed into a physical layout for a gate array, delay times can be introduced which may be inconsistent with the original schematic specifications.

At this point, Mentor's system-wide integration of automated design tools becomes invaluable. First, CADISYS automatically produces a file containing net capacitance delay data for every interconnection in the layout. This data is then used by a tool called the Design File Interface to automatically insert this new timing information into the original schematic data. The updated logic schematic design is then rerun through the simulator tools to verify its adherence to specifications. If the simulation indicates performance problems, the design is modified accordingly and then sent back for another physical layout.

This entire data feedback cycle takes place entirely within the Mentor system. With an extremely high degree of automation and a significant reduction in labor cost.

The IDEA 1002 provides powerful color graphics hardware to present a friendly interface for physical layout tasks.

# Verify prototype functions with fully integrated logic analysis.

### MIDAS 7000 brings you high-performance logic analysis.

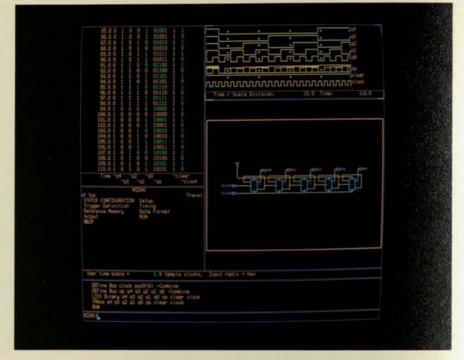

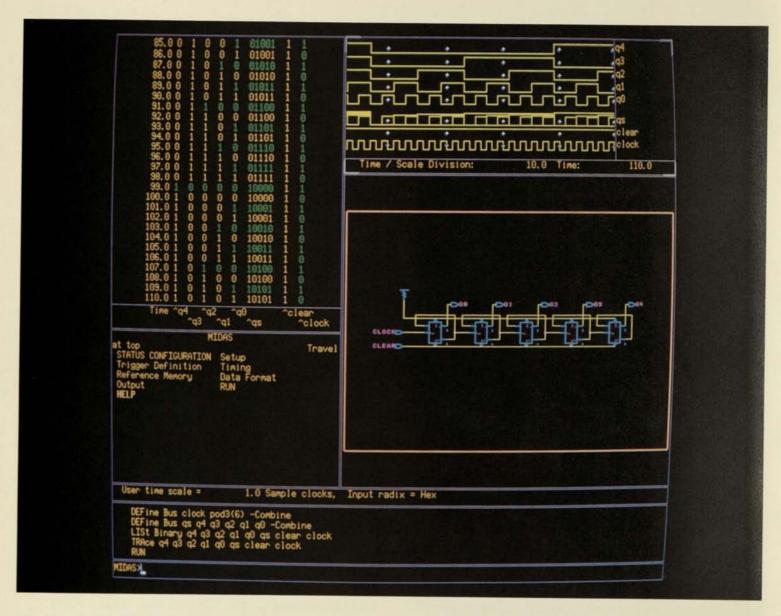

The hardware design cycle doesn't end with physical realization, so neither does Mentor. The MIDAS 7000 is a fully integrated logic analysis system that lets you perform all your prototype test and verification functions from any IDEA 1000 workstation.

MIDAS 7000 gives you a full array of logic state and timing instrumentation and is controlled through the same powerful graphics interface as all other Mentor design tools. You can even use it in conjunction with other design tools to create powerful synergies only possible with Mentor.

MIDAS 7000 has a modular architecture that accepts a wide range of instrumentation cards. You get maximum latitude in selecting the right performance combination plus the capability to easily update your instrumentation lineup.

#### Interactive state analysis with up to 15 trigger states.

MIDAS 7000 lets you tackle even the most convoluted software acquisition problems through sophisticated clocking and triggering, and data widths up to 80 channels.

Sample clocks can be synthesized from up to 7 clock lines, giving you the power to decode the buses of advanced 16-bit and 32-bit microcomputer systems.

Triggering uses a RAM-based state machine and can include up to 15 distinct states that allow for both data acquisition and qualification.

### Timing analysis up to 100 MHz with unprecedented data depth.

MIDAS 7000's timing analyzer not only lets you sample 16 channels up to 100 MHz, it also gives you wider acquisition windows than ever before possible. It's done through a data compression technique called transition triggering that lets you acquire data windows up to 130,000 samples wide.

What's more, you can cross-link the MIDAS 7000 timing and state analyzers for time-synchronized acquisition of both hardware and software data.

### Powerful postacquisition analysis.

Once again, the system-wide integration of IDEA 1000 tools makes the difference. All data acquired by the MIDAS 7000 can be automatically transferred to a workstation's main memory or disc storage for unlimited post-acquisition processing.

This includes automated comparisons with data accumulated by other Mentor tools, such as the Interactive Logic Simulator. Compare physical data from a prototype with the simulator model to measure accuracy. It also includes programs such as performance analysis histograms and mnemonic disassembly packages.

The MIDAS 7000 system gives all the power of a CAE workstation coupled with a high-performance logic analyzer.

# Manage and document the entire design process.

#### DOC: the premier technical documentation tool.

Research shows that over half the typical engineer's day is spent on nondesign tasks, such as documentation and conference time. Accordingly, Mentor has integrated these functions into its system in a way that keeps the time and cost of your design "overhead" to an absolute minimum.

DOC is a professional documentation system several generations beyond conventional word processing. It includes the usual "cut and paste" editing features, but then expands to give you a series of features that completely cover the needs of the professional engineering environment.

For instance, you can reach into the Mentor database and pull diagrams into your text from sources such as schematics, symbol libraries, simulator and logic analysis displays.

Certain numbering tasks, such as figure and section numbers are eliminated altogether through automatic incrementing, even when nested. Footnotes are automatically placed and numbered. "Bookmarks" allow rapid travel to anywhere in the text. You can even annotate a document without affecting its existing format. And use multiple fonts within the same text, such as Bold, Greek, Math and many others.

Also, you can divide a single document into "sub-documents" to allow several writers to work on a single project.

# Electronic mail keeps you in constant touch.

Another obstacle to design productivity is the amount of conference time needed to keep a project moving forward. Here you're faced with countless schedule conflicts and meeting space arrangements.

Mentor solves this problem through electronic mail, which conquers both space and time when it comes to engineering team communications. Each user has an electronic memo writer to send messages and an electronic mailbox to receive them.

With electronic mail, your team communicates better, works faster, and achieves superior end results.

The IDEA 1400 workstation provides a cost-effective vehicle to handle project management and documentation tasks.

#### **Mentor Graphics Corporation**

8500 S.W. Creekside Place Beaverton, Oregon 97005-7191 503-626-7000 Telex 4742102 MENTOR

#### Mentor Graphics Corporation

2620 Augustine Drive Suite 280 Santa Clara, CA 95051 (408) 727-9667

Lexington, MA 617-863-5776

Orlando, FL 305-422-1841 Dallas, TX 214-392-2992 Albuquerque, NM 505-296-3767

San Jose, CA 408-294-9933

714-752-0200

Irvine, CA

Beaverton, OR 503-626-7000

Fort Lee, NJ 201-585-9395

Mentor Graphics Japan Akasaka Twin Tower Bldg. 17-22 Akasaka 7-Chome Minato-K, Tokyo, Japan

Orion Technologies Ltd. 1 Korazin Street Givatayim, 53583 Israel 03-772031 Telex: 32188 CLLSY **U.S. Sales Offices**

Minneapolis, MN 612-835-7007

## **International Sales Offices**

Mentor Graphics (U.K.) Ltd. Reading, Berks., England, RG7 1SS 0734-884888 Telex: 849975 MENTOR G

Mentor Graphics (Deutschland) Gmbh Eching, West Germany 089/319-1003 Telex: 5214474 MENT D

Mentor Graphics (France) SARL Centre Commercial et Industriel Silic 59-61 Rue des Solets 552 Rungis France

© 1984 Mentor Graphics Corporation Printed in USA 1008A 02/84

# MSPICE

# Mentor

# **MSPICE** Overview

Mentor Graphics offers MSPICE (Mentor Spice), a program for interactive analog circuit analysis. MSPICE is offered for use in conjunction with Mentor IDEA 1000 computer-aided engineering (CAE) systems, which are designed with the depth and flexibility to support all aspects of complex electronic circuit design and analysis.

Mentor SPICE consists of an interactive graphics preand post-processor, coupled with the analytical strength of the most up to date version of Berkeley SPICE. When used in conjunction with the IDEA 1000 workstation, you have an integrated, comprehensive computerized circuit design system versus a stand alone design tool, such as SPICE. Rather than entering circuit descriptions in a timeconsuming and error-prone textual manner, MSPICE runs directly off of the design database you create with the IDEA 1000 Design Creation Tools. This same database is also used by the other IDEA 1000 design verification and physical design tools.

During simulation, MSPICE provides you with highlyinteractive analysis control including the ability to monitor and stop analysis, perform user-specifiable custom analysis, and parameter modification on-line. After the simulation is complete, MSPICE's general purpose graphing capability is used to present output in either MSPICE format or any other customized format you specify. Modifications to your existing versions of SPICE are not lost since the MSPICE pre- and post-processor can interface with almost any analog circuit simulator. Regardless of whether that simulator runs on your IDEA 1000 CAE system, another IDEA 1000 in the network, an IDEA high-performance computational system, a mainframe, or special purpose array-processor, MSPICE supports your analysis requirements.

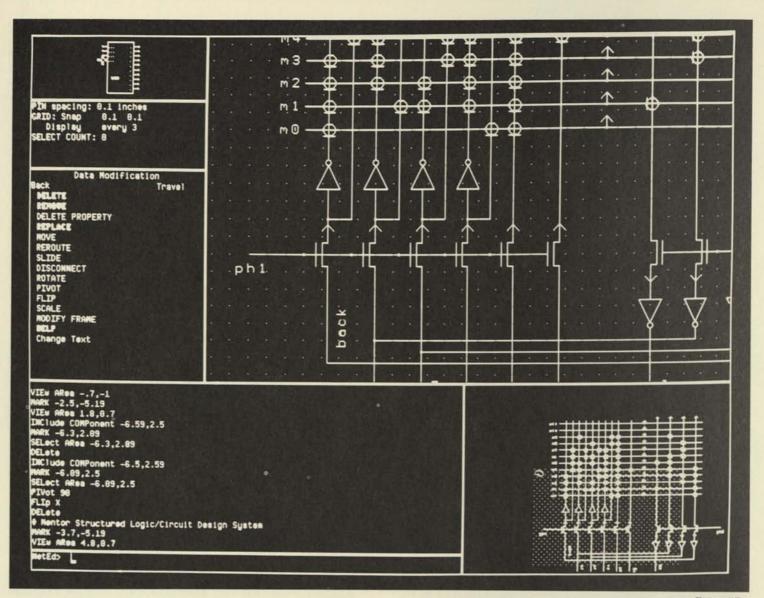

# Creating the design for use with MSPICE

The design to be simulated with MSPICE is created with the Structured Logic/Circuit Design module of the IDEA 1000 system. This integrated set of software tools permits the creation of circuit designs through the user interface in a graphics-oriented format. Circuit components are represented by a set of analog symbols available from the Mentor-supplied parts library, or through symbols that you create with the IDEA 1000

# MSPICE

Symbol Editor. Using the Network Editor, you connect the symbols through nets; lines which represent various electrical paths, to create the circuit schematic. Values for resistors, capacitors, and other passive components are assigned via properties associated with the symbol, and are visible on the schematic. If the symbol represents a diode, transistor, or other active device, its values or "model" are contained in a separate file. A property associated with the symbol identifies the model within this file. If you have more than one active device with the same model, you simply assign them the same property.

You may also design hierarchically with MSPICE. The IDEA 1000 Design Creation Tools allow the schematic to contain higher-level components than the basic passive and active components. For example, a symbol representing an op amp could be created with the Symbol Editor and used in a schematic which contained various passive and active components. The op amp symbol would be fully described by a lower-level schematic containing a set of interconnected transistors. Furthermore, using the hierarchical design capabilities of the IDEA 1000 Design Creation Tools, you may create circuit schematics which represent basic logic functions such as and/or gates, flipflops, etc., and use the symbols which represent these logic functions in higher-level schematics. Having done this, you now have the design verification capabilities of the IDEA 1000 Interactive Logic Simulator, Interactive Timing Verifier, Design File Analyzer, and MSPICE available.

Once you have entered the circuit schematic on the IDEA 1000, the only step required before entering MSPICE is to expand the design down to the interconnection of primitive components acceptable for analog simulation. This is accomplished through the use of the IDEA 1000 Design Expander. While using the Design Expander, you may wish to utilize the Design File Analyzer which provides the capability to guery the entire design at once, perform design rule checks, and perform specialized computations utilizing any IDEA 1000 or userdefined properties associated with symbols. Once a design is expanded, you may perform an unlimited number of MSPICE simulations without re-expanding. Changes made to component values are handled within MSPICE, and therefore, do not require re-expansion. Certain topological changes such as deleting components also do not require re-expansion. For other types of topological changes, only those schematics which have changed need to be re-expanded, rather than the whole design. This greatly increases the efficiency of the expansion process.

## Performing the simulation

To start the circuit simulation, you simply invoke the MSPICE command specifying the appropriate design name. The pre-expanded design file is transparently translated into syntax required by the analysis routines within MSPICE. Also, the "models" for active devices are

| THIS IS A MACRO THAT SWEEPS THE RESISTANCE OF EACH OF THE RESISTORS IN THE                |

|-------------------------------------------------------------------------------------------|

| . CIRCUIT FROM BOX TO 120X OF NOMINAL                                                     |

|                                                                                           |

| DIMENSION LO_DCOPS 5 ARRAY TO CONTAIN THE VOL'S FOR THE CIRCUIT                           |

| DIMENSION HI DCORS 5 & ARRAY TO CONTAIN THE Vol 5 FOR THE CIRCUIT                         |

| DIMENSION SHTRE 5 ARRAY TO CONTAIN THE SHEET RESISTANCES USED                             |

| ASIN SHTP (1+1)                                                                           |

| ASSIGN ENTRS(1-71 SHTR                                                                    |

|                                                                                           |

| FIRST RESET ALL THE SPICEPARS IN THE CIRCUIT TO THEIR ORIGINAL VALUE                      |

|                                                                                           |

| CHANGE SIMULATION PROPERTY SPICEPAR -ALL                                                  |

|                                                                                           |

| NON LOOP THROUGH ALL THE RESISTANCES AND MODIFY THEM BY SHITH                             |

| ASSIGN INST "AFIRST_INSTANCE('R') WET THE 'FIRST' INSTANCE OF A REDISTOR                  |

| LOOP                                                                                      |

| IF "(INST = "") THEN , EXIT LOOP , END IF , END LOOP WHEN NO MORE RESISTORS               |

| CHANGE THE VALUE OF THE RESISTOR TO ITS CURRENT VALUE TIMES THE SHEET & PERCENTAGE        |

| CHANGE SIMULATION PROPERTY SPICEPAR 'INST 'ISHTR + \$INSTANCE_PROPERTY( SPICEPAR', INST ) |

| ASSIGN INST "INSTANCE("R")                                                                |

| END LOOP                                                                                  |

|                                                                                           |

| RUN THE ANALYSIS AND SAVE THE DATA                                                        |

| RUN                                                                                       |

| ASSICN L0_DCOPSII-71 ~#DCOP_V(/OUT/)                                                      |

| ASSIGN HI_DCOPStI-71 -#DCOP_V(*OUTD*)                                                     |

|                                                                                           |

| END LOOP                                                                                  |

|                                                                                           |

| AND THE HIGH OUTPUT VOLTAGE AS A FUNCTION OF SHEET RESISTANCE                             |

| CHART                                                                                     |

| CHART DEFINE ARIS X                                                                       |

| DEFINE AND Y                                                                              |

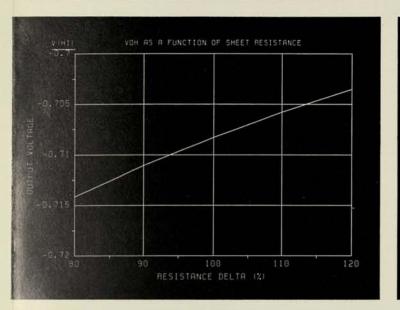

| DEFINE CURVE V(HI) -HI_DCOPS -(SHTRS + 100)                                               |

| AXIS TITLE Y 'OUTPUT VOLTAGE'                                                             |

| AXIS TITLE X "HESISTANCE DELTA (X)"                                                       |

| TIC SMACING X 10 5                                                                        |

| AXis RAnge y - 72 - 7                                                                     |

| TIC Spacing y 000                                                                         |

| CHART LITTE AND AD A FORCE TON OF SHEET HERIDIANCE                                        |

| CHArt Title 'VOH AS A FUNCTION OF SHEET RESISTANCE'                                       |

appended to the input data being prepared for simulation. You then interactively enter any set-up commands required to control the simulation to be performed. Set-up commands include setting the temperature parameter or any other parameter used to define component values. setting any simulation control values, specifying the type of analysis to be performed (DC operating point, AC, DC, transient, etc.), simulation monitor commands, and setting force parameters for circuit power supplies and inputs. Since power supplies are handled as set-up commands and currents are handled directly by MSPICE output, you no longer need to put voltage sources in your circuit. As you interactively enter set-up commands, they are translated into SPICE analysis commands and appended to the previous input data. Only when you type "RUN" is the input data set to the analysis portion of MSPICE. Therefore, changes to set-up commands can be made prior to the actual execution of the simulation.

Unlike batch versions of SPICE, you retain complete control of the simulation with MSPICE. Instead of the graphics display going blank during the execution of the simulation, you are presented with constantly updated status information on your simulation in an easy to understand graphics format. Also during simulation, a copy of the schematic is displayed on the screen complete with status windows next to the nodes specified in the monitor commands. As the simulation is progressing, signal values are displayed in these windows. Another portion of the screen contains waveforms for selected points in the circuit that you have specified. During simulation, these waveforms are incrementally generated and displayed on the screen. Status information is also given in textual form and provides you with information on whether the simulation is still active, plus the current value of dependent variables in the circuit. With all this information available, you can

# Mentor

easily determine whether the simulation is progressing satisfactorily, or whether modifications to the circuit or parameters need to be made. If the latter is the case, you can simply stop the analysis at any time with results computed to that point available for study. No longer will you have to wait with crossed fingers for the results of your simulation. Instead, you will make optimum use of your IDEA 1000's computing resources, and more importantly, your own valuable time.

In many cases, after you have decided upon the changes that your circuit requires, you need only enter new set-up commands and run the simulation again. Changes such as defining new power supply values, changing component values, and updating simulation control commands can be made without leaving MSPICE. In some cases, adding and deleting components can be performed without changes to the circuit schematic. Through the use of the IDEA 1000 macro command language, complete with conditionals and looping, you can quickly develop and execute with one command a sequence of multiple set-up and RUN commands. This provides you with the capability to perform analyses which require multiple simulations; a capability not available with batch circuit simulators.

# Post simulation processing

After you have completed the simulation, the MSPICE post-processing capability is available to view and analyze the results. Unlike batch versions of SPICE, you need not specify which points in the circuit you want to view prior to simulation. Upon inspection of the signal values of waveforms presented while monitoring the simulation run, you may request information on any other points in the circuit without re-running the simulation. Unlike many

versions of SPICE, zero-valued voltage sources are not required to display currents within MSPICE. As a result, both voltage and current are directly available to you as output. Output is presented as waveforms in true graphical format as opposed to printer plots available in other simulators. Graphs are easily obtained via a single

# Menbr

## Mentor Graphics Corporation 8500 S.W. Creekside Place Beaverton, OR 97005-7191 (503) 626-7000

command with the detail of axis labeling and scaling handled by MSPICE. Also, you have the option of specifying your own labeling and scaling dependent upon your application. On color IDEA 1000 systems, each waveform in a graph is represented in its own color, while on monochrome IDEA 1000 systems, each waveform is differentiated by using narrow, bold, dotted, or dashed lines. In either case, waveforms are easily discernable, and there is no limit to the number of waveforms on a single graph.

Through the use of expressions allowed in the MSPICE post-processor, waveforms may be generated utilizing any parameter in the circuit and any voltage or current computed by the simulation. Therefore, you are not limited to waveforms representing voltage and current. This allows you to generate waveforms representing such values as instantaneous power. Through the use of arrays within the macro command language, results computed from each simulation run may be stored away for processing at a later time. Coupling arrays with looping and conditionals in macros along with component value modification gives you the ability to perform specialized analysis which require multiple simulation runs. These waveforms from different simulation runs may be combined on the same graph, and through expressions a waveform can be constructed which contains the output from multiple simulations.

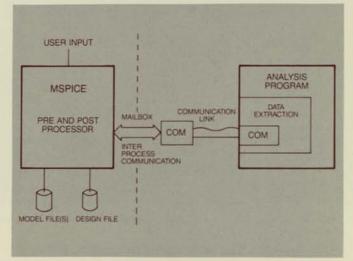

# **MSPICE** Architecture

As delivered with the IDEA 1000 CAE system, MSPICE provides a completely integrated turnkey circuit analysis system. However, the architecture of the MSPICE product has been designed in such a manner that you are not required to choose between MSPICE and your own proprietary version of SPICE which may have been tailored to your specific design and environment.

MSPICE consists of two main software components; a graphics-oriented pre- and post-processor and the simulation server. The pre-processor is used to convert design data created by the IDEA 1000 Design Creation Tools into a format acceptable by the simulation server, while the post-processor creates graphs from results computed by the simulation server. These MSPICE

processors always reside on an IDEA 1000 CAE system. The simulation server consists of three components; the analysis program which computes simulation results, a communications link used to pass data between the preand post-processor and the simulation server, and subroutines used to extract analysis data at each analysis

point. As required, you can use the Berkeley SPICE analysis program provided within the MSPICE server or substitute your own. Circuit analysis programs containing your own modifications may be included in the MSPICE server by incorporating the data extract subroutines into your analysis program. The simulation server may run on any IDEA 1000 CAE system, an IDEA high performance computational system, mainframe, or special purpose array processor. Transporting your simulation server, running on a mainframe or other system, to an IDEA 1000 CAE system is easily done since the IDEA 1000 system supports programs written in ANSI standard FORTRAN 77.

When the simulation server is run on an IDEA 1000 CAE system or IDEA high-performance computational system, the communication link consists of the Apollo DOMAIN interprocess communication facility, and if necessary, the DOMAIN local area network. If your simulation server is not running on an IDEA 1000 CAE system, the communications link also includes one of the many Apollo DOMAIN communication gateways.

# U.S. Sales Offices

Fort Lee, NJ 201-585-9395 San Jose, CA 408-294-9933

Lexington, MA 617-863-5776

Orlando, FL 305-422-1841 Irvine, CA 714-752-0200

Dallas, TX 214-392-2992 Beaverton, OR 503-626-7000

Albuquerque, NM 505-296-3767

Minneapolis, MN 612-835-7007

CALIFORNIA AUTOMATED DESIGN, INC. Santa Clara, CA 408-727-9667

## International Sales Offices

Mentor Graphics Japan Co., Ltd. Toshima-ku, Tokyo 170, Japan (03) 989-7950

Mentor Graphics (U.K.) Ltd. Reading, Berks., England, RG7 1SS 0734-884888 Telex: 849975 MENTOR G

Mentor Graphics (Deutschland) Gmbh Eching, West Germany 089/319-1003 Telex: 5214474 MENT D

# TEST AND MEASUREMENT TOOLS

## An Overview

The IDEA 1000 is a self-contained, computer-aided engineering (CAE) workstation dedicated to the design and analysis of complex electronic circuitry. The system is integrated with Apollo DOMAIN computer systems linked together in a distributed network architecture. This way, each operator receives the benefit of independent 32-bit local processing and high resolution graphics, and still has full access to a common full relational data base shared by the Mentor system as a whole. In this networked environment, the user does not experience the performance degradation typical of a multi-user central host architecture.

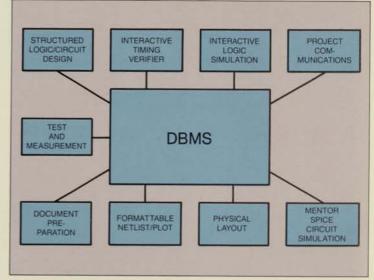

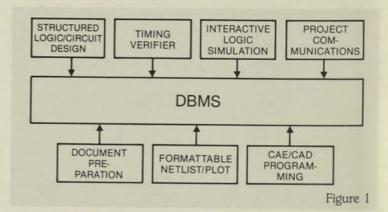

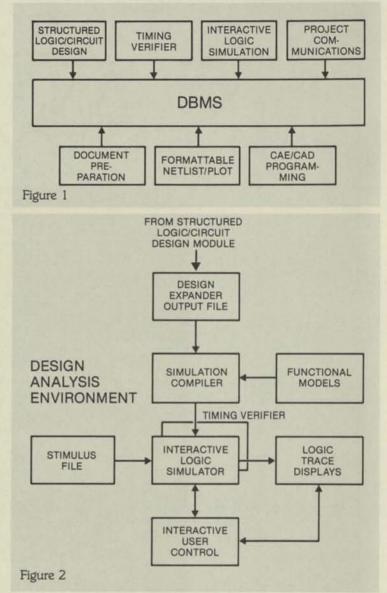

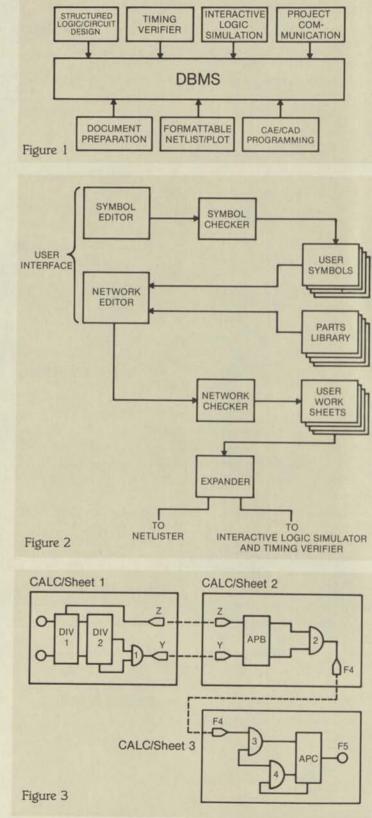

Within the IDEA 1000 system are a number of software modules used to implement the various phases of the logic or circuit design process. These include Structured Logic/Circuit Design, Interactive Logic Simulation, Timing Verification, Physical Layout, Circuit Simulation, Project Management, Document Preparation, Formattable Netlist/Plot and CAE/CAD Programming. Each of these modules is tied into the high-performance full relational data base management system for fast, efficient access to any required information across the network (Figure 1).

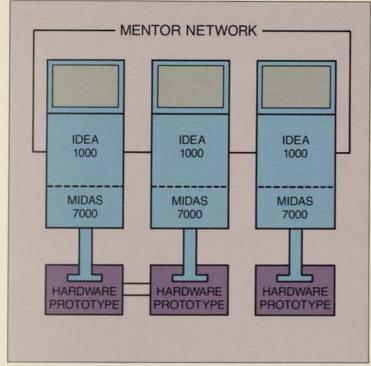

In addition to these software modules, there is a hardware/software Test and Measurement module which is fully integrated with both the IDEA 1000 system software and the Apollo DOMAIN computer system. This module is called the MIDAS 7000, and extends Mentor's CAE tool set to cover the final phase of the hardware design cycle, verification and test. With MIDAS 7000 installed, the IDEA 1000 CAE system covers every phase of circuit design, from product definition to real-time verification of the completed hardware.

# MIDAS 7000. The Mentor Interactive Design Analysis System.

MIDAS 7000 is a powerful logic analysis system that provides full trace capabilities for both state and timing analysis, with state acquisitions up to 80 channels and timing measurements up to 100 MHz. Since it is fully integrated into the IDEA 1000 system, the user benefits from many capabilities not found in a conventional, stand-alone logic analyzer:

Standardized User Interface. All aspects of the MIDAS 7000's operation are controlled from the standard IDEA 1000 user interface, which takes advantage of the workstation's high-resolution color graphics and programmable keyboard. During logic

#### Figure 1

analysis, the user is presented with the same graphic interface format and procedures used with all other IDEA 1000 design tools. This unified interface promotes faster, more accurate work, with no loss of continuity when moving from one tool to another.

Automatic Comparison of Real-Time and Simulated Data. Any real-time data acquired by MIDAS 7000 can be retained for powerful postacquisition processing by the IDEA 1000 workstation's 32-bit CPU. One such application is the comparison of data generated by Mentor's Interactive Logic Simulator and real-time data later acquired by MIDAS 7000 from the actual hardware. This capability gives you a fast, accurate means of checking and verifying hardware performance against the schematic model without ever leaving the IDEA 1000 design environment.

Performance Analysis. During hardware/software integration, it is often important to monitor your code's real-time execution and analyze its performance in terms of design specifications. With MIDAS 7000, you can acquire real-time software data, and run it through post-acquisition processing that presents its performance in a graphic format, such as a frequency histogram.

Mnemonic Disassembly. The design and debug of microprocessor-based systems often calls for the acquisition and display of software flow as executed on the bus of the target hardware. After a MIDAS 7000 has acquired the software data, the IDEA 1000 can call upon stored mnemonic disassembly tables to convert your code into readable form. This includes both standard microprocessor or special user-defined instruction sets.

# Menior IDEA 1000

Figure 2

# An Expandable Test and Measurement Architecture

The MIDAS 7000's data acquisition hardware has an expandable modular architecture which accepts individual test and measurement instrumentation cards. For logic analysis, you can install exactly the configuration of state and timing that your application requires. In addition, you will be able to install other types of instrumentation cards as they become available. This way, you have a test and measurement tool with the same room for growth, depth and flexibility found throughout the IDEA 1000 tool set.

# A fully integrated logic analysis tool.

MIDAS 7000 makes logic analysis an integral part of the IDEA 1000 system through its tightly coupled position in the system architecture (Figure 2). Data acquisition probes from MIDAS attach to the hardware under test, and acquired data is stored first in a local data acquisition memory and then uploaded to the local workstation memory, where it can be either stored on disk, processed, displayed or output to peripheral devices.

Because the IDEA 1000 interface allows fully transparent access to both hardware and software

#### Figure 3

tools anywhere on the network, the MIDAS 7000 analysis functions can be controlled from any workstation on the network. Also, acquired data, reference data, and post-acquisition processing programs can be copied or viewed from any network node.

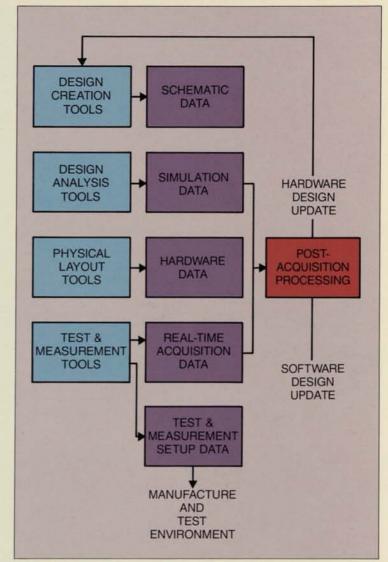

Figure 3 shows how the MIDAS 7000 test and measurement tools are an integral part of Mentor's support for the design cycle through computer-aided engineering. At the beginning of the cycle, Design Creation Tools allow schematic information to be graphically edited for entry into the design's database. Next, Design Analysis Tools allow the software version of the design to be simulated in terms of logic and timing. Physical Layout Tools then allow the design to be expressed as a physical entity, such as a gate array. To complete the cycle, MIDAS 7000's Test and Measurement Tools allow the

# TEST AND MEASUREMENT TOOLS

physical version of the design to be tested and verified in terms of the original functional specifications. At each and every step in the design cycle, you work through the same Mentor graphics user interface.

Hardware test and verification procedures are ideal candidates for the powerful post-acquisition processing capabilities of the IDEA 1000 System. As mentioned, this includes automatic comparison of simulation and data acquisition files. The information obtained from post-acquisition processing can then be used to update the original hardware design files or to modify the product's software.

An additional benefit of MIDAS 7000 is that test and measurement procedures developed during the design stage of product development can be transported to the Production Engineering test department. Selected instrument setups, reference data and post-acquisition processing can all be retained on disk and then transferred to similar instruments and their controllers located in the manufacturing environment.

## Interactive State Analysis

The MIDAS 7000 Logic State Analyzer allows up to 80 parallel channels of synchronous state acquisition at sample rates up to 10 MHz. The acquisition memory for each channel is 4096 bits deep, which provides data acquisition windows wide enough to trace complex software transactions.

State data is sampled into memory through probes

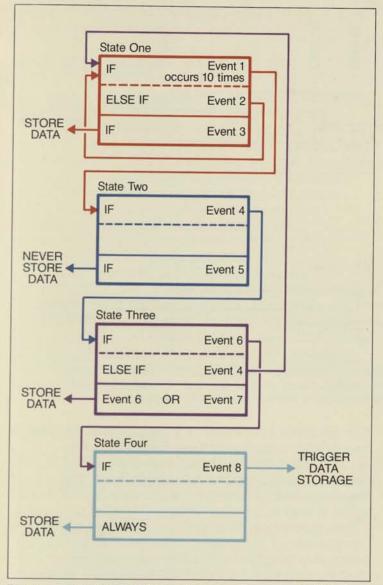

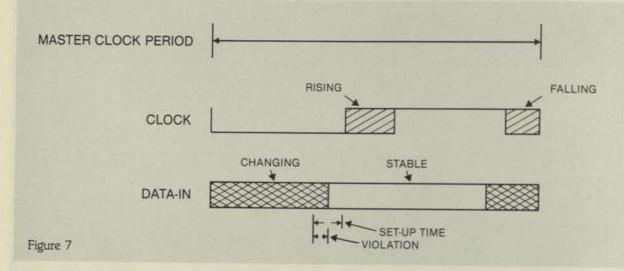

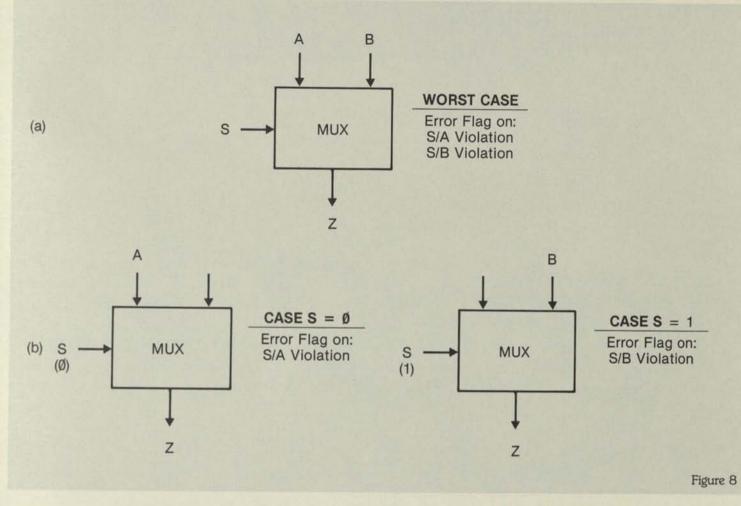

Figure 4 - The Interactive State Analyzer provides up to 15 distinct states for use in trigger definition and data storage qualification. This diagram shows how four such states could use jumps and branches to track complex software flow as it occurred in the system under test.

attached to hardware under test. The sample clock can be synthesized from up to five ORed clock inputs to define the master sample clock. Either the rising or falling edge of each clock signal may be defined as the sampling edge. For acquisition of multiplexed buses, there are also two HOLD clocks which eliminate the need for cumbersome double probing. (A HOLD clock latches the first phase of data sampled off the bus and holds it until the second phase data is present. Both phases are then simultaneously sampled into acquisition memory). Together, these clocking features provide enough flexibility to trace the bus transactions of popular but complex 16-bit and 32-bit microcomputer systems.

MIDAS 7000 data acquisition triggering for state information is implemented through a RAM-based state machine which allows up to 15 distinct states to be defined. During data acquisition, a given state can result in a number of actions, including jumping to another state, triggering and data storage qualification (Figure 4). This arrangement allows you to accurately acquire data even when convoluted software execution paths are followed.

Each state can have its own user-defined mnemonic label to simplify trigger definitions. Within each state, you can call upon up to four word recognizers which define the event or events comprising the state. When an event comes true, its assigned word recognizer initiates a preprogrammed action such as qualifying data for memory storage, halting data acquisition (triggering), starting a counter or transferring data acquisition control to another state.

To simplify the trigger definition process, a symbol definition table lets you specify various trigger events in convenient mnemonic form, which means you can name events using the same labels found in the source code, or any other meaningful terminology.

## **Interactive Timing Analysis**

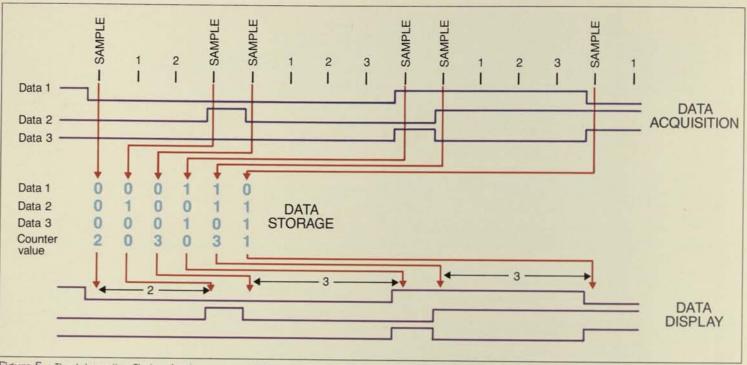

The MIDAS 7000 Logic Timing Analyzer acquires parallel channels of data at sample rates up to 100 MHz. The nominal memory depth per channel is 510 bits, however the timing analyzer's architecture includes several features that significantly extend this memory depth during data acquisition.

One such feature is transitional timing, which only samples data into memory when a logic transition actually occurs on one of the data acquisition channels. When a logic transition is detected and sampled, a counter is activated which counts the number of samples until the next transition occurs. When data acquisition is complete, the timing analyzer uses the stored transitions and the counter delta time information to reconstruct a timing diagram representation of the logic activity as it occurred in real-time (Figure 5). This technique enables a relatively small amount of acquisition memory to capture data over an extremely wide time window. In effect, you can acquire real-time data windows up to 130,000 samples wide.

Another data compression feature is the "multitriggers" mode, which allows you to make 16 "mini-

# TEST AND MEASUREMENT TOOLS

Figure 5 - The Interactive Timing Analyzer uses a data compression technique called transitional timing to expand the data acquisition window. Data sampling only occurs when a transition occurs on one of the channels, thereby minimizing storage requirements. A counter tracks the sample count between transitions, and this information is used to reconstruct a real-time representation of timing activity.

acquisitions" of at least 32 samples each in the course of a single data acquisition. Each of the 16 subgroups has the same trigger event located at its center. During data acquisition, the timing analyzer will acquire at least 32 samples when the trigger event occurs, and then stop storing data until the trigger event occurs again. This cycle is repeated 16 times until the acquisition memory is full. You now have 16 records of events surrounding successive occurrences of the trigger event, with all other data filtered out.

The MIDAS Logic Timing Analyzer can also be programmed into a cross-triggering relationship with the Logic State Analyzer. When a trigger event occurs on the timing analyzer it can be used to either arm or trigger the state analyzer. Conversely, a state trigger can either arm or trigger the timing analyzer. In either case, the data is time-synchronized to let you see the true relationship between software and hardware events as they occurred in the system under test.

# Post-acquisition processing

Any data acquired by either the MIDAS state or timing analyzers is automatically transferred to the main memory of the IDEA 1000 workstation, where it can be either processed or stored on disk for later processing. Since every IDEA 1000 workstation participates fully in a Mentor network and full relational database, the MIDAS 7000 Test and Measurement Tools and the data they produce are tightly linked to all other Mentor CAE tools and data.

One powerful form of post-acquisition processing is comparison of logic data produced by the Mentor Interactive Simulator with data acquired later in the design cycle by the MIDAS 7000 Logic State Analyzer. This comparison is carried out by a Mentor file compare command, and allows all discrepancies between the two data files to input to a third file as well as output to the display or a printer. This comparison technique gives you a powerful means of verifying that the physical hardware's performance conforms to the original design model specifications.

Mentor also will support microcomputer software/ hardware integration by offering a series of disassemblers for popular 8-bit, 16-bit and 32-bit processors with bus cycle rates up to 10 MHz. Realtime software flow acquired by MIDAS 7000 off the bus of the hardware under test is post-processed by the disassembler software to provide data similar to an assembly source code listing.

Another Mentor post-acquisition is performance analysis, which statistically measures various aspects

of your code's execution as acquired off the bus of the system under test.

## I/O Functions

Since it is fully integrated into the IDEA 1000 system, MIDAS 7000 can take full advantage of all the system's input/output capabilities. All instrument setups and acquired data can be filed on disk and then accessed by any workstation located anywhere in the system. At an even higher level, these diskbased files can become part of powerful macro command files that automate entire test and measurement procedures, from setup and processing of acquired data to reporting and formatting the final results.

In addition, any MIDAS display of setups or acquired data can be output to a plotter to obtain hardcopy of test procedures and results. Also, logic state lists can be output to a printer. For fast, efficient communication across the network, any MIDAS data can be sent via Mentor's electronic mail system to selected individuals or groups of individuals for review or comments.

## Specifications

#### MIDAS 7000 Interactive State Analyzer

#### HARDWARE SPECIFICATIONS

#### INPUTS

CLOCK CLOCK CHANNELS: 5 ORed Sample clocks and 2 Hold clocks INPUT LOADING OF CLOCK PROBE: 1 TTL FAST load (lin-low = 0.6 ma.) MAXIMUM INPUT VOLTAGE: 0.5 V to 7.0 V. DYNAMIC RANGE: 0 V to 5.0 V. THRESHOLD: 1.6V. TTL THRESHOLD: 1.6V. TTL MINIMUM CLOCK PULL MAXIMUM SYCHRONOUS SAMPLE RATE: 10 MHz MINIMUM CLOCK PULLS WIDTH: 25 ns. CLOCK MODES: Normal: Demultiplex CLOCK MODES: Notifue, Bennanguer DATA: DATA: DATA CHANNELS: 16 to 80 input channels. 16 channels per P.2902 Data Probe INPUT LOADING OF DATA PROBE: 1 TTL ALS load (lin-low = 0.1 ma.) MAXIMUM INPUT VOLTAGE: 0.5 V to 7.0 V. DYNAMIC RANGE: 0 V to 5.0 V. THRESHOLD: 1.6 V. TTL DATA SETUP TIME: 25 ns. DATA HOLD TIME: 0 ns. EVTERNAL RNC: INPUT: 1 TTL load (lin-low = 1.6 ma.)

OUTPUTS

CLOCK PROBE: REALTIME PROGRAMMABLE OUTPUT (FROM STATE MACHINE): 2 lines; open collector; internally pulled up by 4.7 Kohm RUN/STOP LINE; open collector; internally pulled up by 4.7 Kohm

CROSS-LINK BNC: CROSS-LINK LINE: programmable output: 50 ohm line driver

#### ANALYSIS

ACQUISITION MEMORY: Configurable from 16 to 80 channels with 4096 memory depth per channel. REFERENCE MEMORY:

STATE MACHINE:

STATE MACHINE: NUMBER OF INDEPENDENT STATES: 15 WORD RECOGNIZERS PER STATE: 4 total: 2 used for branching, triggering and output control: 2 used for storage qualification (ANDred or ORed); all words-value, NOT, Don't Care. OUTPUTS PER STATE: 2 real time output lines and 1 cross link line. EVENT COUNTERS PER STATE: 1, programmable from 1 to 40% EVENT COUNTER MODES: after N times, before N times or N times (N = 1 to 40%) EVENT COUNTER INPUTS: sample clocks, store clocks or word recognizer occurrences

#### SOFTWARE SPECIFICATIONS

FORMAT: channel group assignment; display order; group labels; radix and polarity selection; sample and hold clock and muxinon-mux setup; Run/Stop polarity TRIGECR: state machine programming; trigger position (begin, center, end and delay to 4090); storage qualification programming; symbolic state definition. Multiple Preview Acquisition selection; programmable start state; store state transitions SYMBOL: word recognizer symbol name and value definition; find word and mask words

words DISPLAY: HEX, OCTAL, BINARY and ASCII display formats; acquisition or reference: single line, page or block scrolling; reference edit; find word (scroll by value); INPUT/OUTPUT; save and load setup and data to and from disk; or display; print data, symbols or trigger information

GO MODES: Go forever; Go until acquisition = reference; Go until acquisition > < reference; Halt

#### MICROPROCESSOR SUPPORT

Z80 Z8001 Z8002

The MIDAS 7000 can be effectively used with all of the following microprocessors, plus more, using the unique universal clocking scheme: using the unique univ

| and an orocarding a arrante |              |       |

|-----------------------------|--------------|-------|

| 6800/6802<br>6801/6803      | 8080<br>8085 | 16032 |

| 6809                        | 8086         | 1802  |

| 68000                       | 8088         | 1000  |

| 6805                        | 80186/286    |       |

## MIDAS 7000 Interactive Timing Analyzer

#### HARDWARE SPECIFICATIONS

CLOCK

- MAXIMUM SAMPLE RATE: ASYNCHRONOUS: 100 MHz. (10 ns. resolution) - internal clock SYNCHRONOUS: 100 MHz. using external clock

- CLOCK SPECIFICATIONS: RANGES: 10 ns. to 10 ms. in in 1,2,3....9 sequence

RANGES: 10 ns. to 10 ms. in 1.2. ACCURACY: Crystal controlled

#### DATA:

INPUT MODES: 16 CHANNEL MODE: Sample and store input data value with every clock transition; 508 bits

memory per channel 10 CHANNEL TRANSITION MODE: Sample and store only on data level changes: 8-bit counter for delta time between transitions; up to 128K effective memory in special case GLITCH CAPTURE:

mum pulse detection; glitch latch PROBES: INPUT IMPEDANCE: 1 megohm, 5 picoFarads THRESHOLD RANGE (VARIABLE): +/- 5.5 volts MAXIMUM NON-DESTRUCTIVE INPUT VOLTAGE: +/- 25 volts

SPECIAL HARDWARE CHARACTERISTICS: MULTI-TRIGGERS MODE: capture up to 15 regions of 32 samples; all center triggered ANALYSIS:

1) Pattern occurrence with OR'ed edges (AND'ed levels AND'ed with OR'ed edges)

2) Pattern duration greater than a specified time

3) Pattern duration less than a specified time

4) Start of pattern (transition into pattern)

5) End of pattern (transition out of pattern)

6) Set-up time violation

2) Hold-time violation

- B) Hold-time violation

B) All modes can be combined with Interactive State Analyzer cross-triggering and arming

#### SOFTWARE SPECIFICATIONS

#### USER MENUS:

FORMAT: 16 channel or transition mode selection; single or multi-triggers mode selection; sample or glitch mode: channel group assignment; threshold adjustment; trigger setup; trigger position; group labels; channel activity indicator DISPLAY: timing waveform display; channel label assignment; vertical trigger setup; find word; delta time readout; window and cursor scrolling; magnification selection LIST: state display of acquired data; absolute or relative time readout between acquisitions; data scrolling.

INPUT/OUTPUT: save and load setup and data to and from disk; or display; print

## State / Timing Cross Linkage

#### TRIGGERING:

State triggers timing: timing triggers state

#### ARMING

State arms timing to begin looking for an independent trigger event; timing arms state to begin looking for an independent trigger event

Mentor Graphics Corporation 10200 S.W. Nimbus Avenue, G-7 Portland, OR 97223 (503) 620-9817 Telex: 4742102 MENTOR

Mentor Graphics Corporation is dedicated to providing the finest computer-aided engineering tools possible, and to ensuring that these tools follow an optimized long-term growth path that produces continuous gains in both productivity and design innovation.

FortLee, NJ San Jose, CA Lexington, MA Edina, MN 201-585-9395 408-294-9933 617-863-5776 612-835-7007 U.S. Sales Offices Orlando, FL Irvine, CA Dallas, TX Albuquerque, NM 305-422-1841 714-752-0200 214-392-2992 505-821-2775 Portland, OR 503-620-9817 International Mentor Graphics (U.K.) Ltd. Mentor Graphics (Deutschland) GmbH Reading, Berks., England RG7 1SS Sales Offices Eching, West Germany 0734-884888 089/319-1003 Telex: 849975 MENTOR G Telex: 5214474 MENT D Mentor Graphics Japan Co., Ltd. Toshima-ku, Tokyo 170, Japan 989-7950

102655151

Printed in USA 1007A 11/83

# PROJECT MANAGEMENT TOOLS

# An Overview

IDEA 1000 is a self-contained, computer-aided engineering (CAE) system dedicated to the design and analysis of complex electronic circuitry. The system is integrated with Apollo DOMAIN computer workstations, linked together in a distributed network architecture. This way, each operator receives the benefit of independent 32-bit local processing and high resolution graphics, but still has full access to a common data base shared by the system as a whole, without the performance degradation of a central host architecture.

Within the IDEA 1000 system are a number of software modules used to implement the various phases of the logic or circuit design process. These include Structured Logic/ Circuit Design, Interactive Logic Simulation, Timing Verification, Project Communications, Document Preparation, Formattable Netlist/Plot and CAE/CAD Programming. Each of these components is tied into a high-performance full relational data base management system for fast, efficient access to any required information (Figure 1).

Two of these basic modules, Project Communications and Document Preparation, provide a complete tool set to handle the management of electronic engineering projects. Almost any project requires extensive intercommunication between team members and documentation of the design effort. For this reason, Mentor has made communication and documentation tools an integral part of the IDEA 1000 computer-aided engineering system. Both of these tools have complete access to the systems's design files, allowing project management to proceed with a high degree of speed and accuracy.

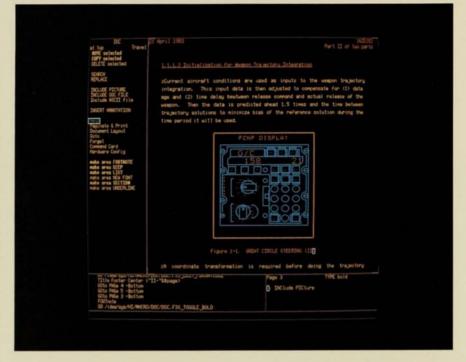

The Document Preparation module takes advantage of the Apollo workstation's high resolution graphic display to provide fast and comprehensive text processing. A user can rapidly enter edit, format and file documentation which includes both text and pictures. The Project Communications module provides a fast, orderly flow of "electronic mail" between team members, allowing intersystem communications that overcome both time and location problems.

# **Document Preparation**

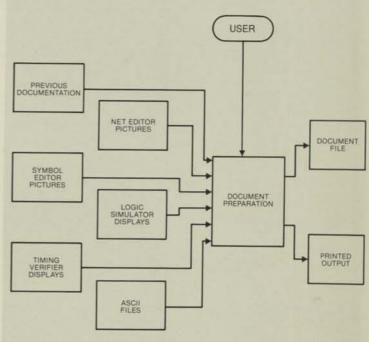

Documentation is an essential part of the logic/circuit design process, and the IDEA 1000 Document Preparation Module lets the user generate high quality documentation which can immediately draw upon design information maintained by the system's data base management system. When generating new text, the user can bring in previous documentation or ASCII files, plus graphics produced by the Symbol Editor, Network Editor, Logic Simulator or Timing Verifier (Figure 2). In this manner, users have all the resources to create timely and accurate documentation at their immediate disposal.

Document Preparation gives the user a powerful set of commands to handle text generation while maintaining the comfort level that a conventional "pencil and paper" approach provides. For instance, a command is provided to "turn" through pages of a filed report. Most important,

Figure 2

Document Preparation displays generated text on a "what you see is what you get" basis, so the user immediately sees the effect of any command upon the substance of the document, rather than having to wait for later processing to see the final results.

The Document Preparation command set is generally divided into two subsets. One is the editing commands associated with the entry and modification of the text itself. The other is formatting commands which form the text into whatever visual arrangement is desired by the user. In addition there are commands which let the user travel quickly to any location within the document for viewing, editing or formatting purposes. These commands are possible because the editor is context-sensitive and understands concepts such as a "section", "page" or "list".

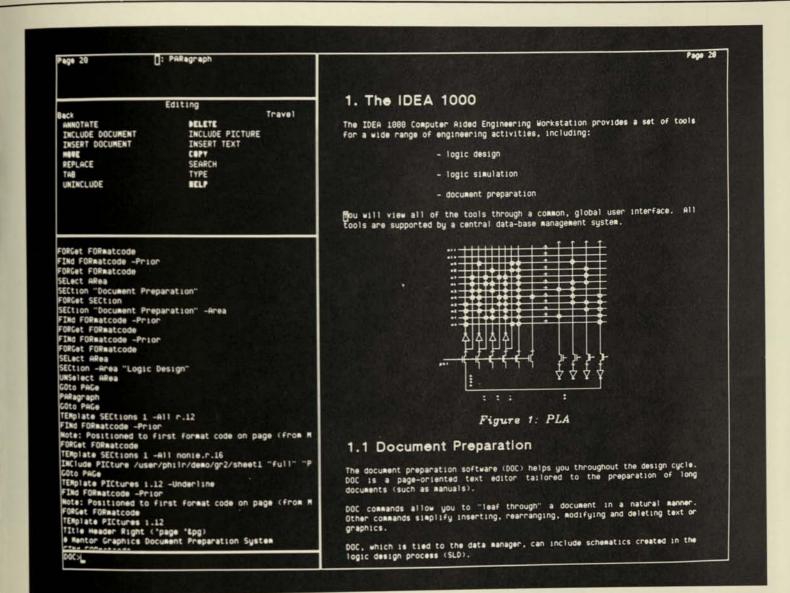

Figure 3 illustrates a previously completed document that has been called up for editing. Notice that a graphic

| <pre>Idealib installed as userilo.private<br/>20000 - 2fFFFF 0 //node_51/local_user/idea.srl.0/idealib<br/>Checking genryl's intransit wall.<br/>Unviewed Messages in "//node_51/local_user/idea.srl.0/idealib<br/>Checking genryl's intransit wall.<br/>Unviewed Messages in "//node_51/local_user/idea.srl.0/idealib<br/>The refrest exet usion on the set usion.<br/>The set usion of the set usion.<br/>The set usion.<br/>The set usion of the set usion.<br/>The set usion of usions on of the usion.<br/>The set usion of usions on of the usion of usions of of the usion.<br/>The set usion of usions on of the usion of usions on of the usion.<br/>The set usion of usions of of the usion of usions of of the usion.<br/>The set usion of usions of of the usion of usi</pre> |                                                                                                                                                                                                                                           |                                                                                                                     |                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>Idealib installed as userilo.private<br/>20000 - 2fFFFF 0 //node_51/local_user/idea.srl.0/idealib<br/>Checking genryl's intransit wall.<br/>Unviewed Messages in "//node_51/local_user/idea.srl.0/idealib<br/>Checking genryl's intransit wall.<br/>Unviewed Messages in "//node_51/local_user/idea.srl.0/idealib<br/>The refrest exet usion on the set usion.<br/>The set usion of the set usion.<br/>The set usion.<br/>The set usion of the set usion.<br/>The set usion of usions on of the usion.<br/>The set usion of usions on of the usion of usions of of the usion.<br/>The set usion of usions on of the usion of usions on of the usion.<br/>The set usion of usions of of the usion of usions of of the usion.<br/>The set usion of usions of of the usion of usi</pre> |                                                                                                                                                                                                                                           |                                                                                                                     |                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                                              | 1982/11/22.23:07:03 utc; 1484E555.A000001F8                                                                                                                                                                                    |

| <pre>sent: 1/19/1982 452 pa (pat)<br/>to: gerpl<br/>cc: dever<br/>uub; CHANGES IN ALU DESIGN</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                           |                                                                                                                     |                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                                              | from: boby                                                                                                                                                                                                                     |

| <pre>to: gerry1<br/>C: gevry<br/>subj: CHARGES IN ALU DESIGN<br/>As per our discussion on Monday, I have corrected the logic errors<br/>no the RUU design Oue for release next Thursday. To see where the changes<br/>impact your portion of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project, refer to version 3 of schematic file<br/>"Course of the project or project components. I believe that<br/>site changed the lack specifications to project see we properties<br/>from the vendor. If he forgot to update the files, we could be simulating<br/>and the lack specifications to project simulator 1 noticed a<br/>potential problem on bus "dat_32". The their on bits if and 15 lows to<br/>close for comfort. Suggest you take another look at it.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                           |                                                                                                                     |                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                                              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                          |