#### ASICs WORLDWIDE 1995

#### TABLE OF CONTENTS

#### PERSPECTIVES

| 9501            | 5/29/95      | Cell-Based ICs to Dominate Gate Arrays in 1998                               |

|-----------------|--------------|------------------------------------------------------------------------------|

| 9502            | 12/1/8/95    | SLI to Dominate ASIC market by 2000                                          |

|                 |              |                                                                              |

| <u>MARKET I</u> | TRENDS       |                                                                              |

| 9501            | 1/22/96      | ASIC Design War: Reports from the Battlefield                                |

| <u>MARKET S</u> | TATISTICS    |                                                                              |

| 9501            | 3//27/95     | Final 1994 Worldwide ASIC Market Share                                       |

| 9502            | 5/22/95      | Worldwide ASIC Forecast                                                      |

| 9503            | 10/23/95     | Worldwide ASIC Forecast                                                      |

| <u>COMPETI1</u> | TVE DYNAMICS |                                                                              |

| 9501            | 10/30/95     | The Fab Four (Competitive Analysis)                                          |

| 9501            | 6/26/95      | HD-PLDs: Where Are We Growing? (Product Analysis)                            |

| 9502            | 7/31/95      | Packaging Update: ASICs Fuel BGA Growth (Product Analysis)                   |

| 9503            | 8/28/95      | System Dissection ASICs Continue to Differentiate Systems (Product Analysis) |

| FOCUS STU       | JDIES        |                                                                              |

| 9501            | 8/14/95      | The ASIC Road Map to the Multimedia Dream                                    |

.

•

.

#### USER WANTS AND NEEDS

| John March System Designers Oncover Asic Opportunities | 9501 | 6/26/95 | System Designers Uncover ASIC Opportunities |

|--------------------------------------------------------|------|---------|---------------------------------------------|

|--------------------------------------------------------|------|---------|---------------------------------------------|

# Dataquest

Perspective

ASICs Worldwide Dataquest Predicts

### SLI to Dominate ASIC Market by 2000

**Abstract:** Dataquest is introducing a new area of research called "system-level integration" (SLI), also known as "system on a chip." Under the SLI umbrella is both hardware and software co-design, as well as SLI application-specific integrated circuits (ASICs) sold to one user and SLI application-specific standard products (ASSPs) sold to more than one user. Today, the SLI ASIC market is about \$1.1 billion and accounts for about 10 percent of the ASIC market (gate arrays and cell-based ICs). Dataquest predicts the SLI ASIC market will reach \$14 billion by the year 2000 and account for about 60 percent of the ASIC market. In this document, Dataquest explores SLI applications, leading suppliers, and technology drivers. We also forecast the future of this dynamic market. By Bryan Lewis

#### System-Level Integration: Profits on a Chip

We are entering a new era of electronic system design that we are calling "system-level integration" (SLI). We now have the technology to incorporate the entire system on a single chip. Design methodology, design reuse, and intellectual property will play vital roles in determining the winners among both suppliers and users. Companies such as LSI Logic and VLSI Technology have proven to Wall Street that ASIC suppliers can be profitable if bets are placed in the right areas. System suppliers are finding many benefits to using SLI technology, including improved design times, improved performance, and improved product differentiation, all of which help increase profit margins. SLI is the well-paved road to profits for both suppliers and users.

#### Dataquest

Program: ASICs Worldwide Product Code: ASIC-WW-PD-9502 Publication Date: December 18, 1995 Filing: Perspective (For Cross-Industry, file in the Semiconductors, Volume 2 of 3 binder behind the ASICs Worldwide name)

#### **SLI Definition**

At its October 1995 Semiconductor Conference, Dataquest introduced a new term and area of research to the industry—system-level integration. Other terms used in the industry today that have a similar meaning include "system on a chip" or "systems on silicon." We have not chosen these terms because they imply that the system is hardware only. We strongly believe that future system design will include hardware/software co-design, so we have chosen a broader term that encompasses both elements. This document focuses on the hardware portion of the market, and we define the hardware market as follows:

System-Level Integration: An integrated circuit that contains a compute engine, memory, and logic on a single chip and has more than 100,000 utilized gates.

There are two types of SLI devices: ASICs (application-specific integrated circuits that are sold to a single user) and ASSPs (application-specific standard products that are sold to more than one user).

#### Market Size and Applications

Dataquest's preliminary 1995 estimate for the SLI ASIC market is \$1.1 billion, and we estimate \$0.9 billion for SLI ASSPs. About half of the 1995 SLI ASSP market is in telecom chips, including LANs, modems, switching, wireless, and Asynchronous Transfer Mode (ATM). The other half of the SLI ASSP market is in graphics, audio, core logic, and consumer.

SLI ASICs are entering the market at a rapid pace, with many high-volume applications slated to use the technology, including the following:

- Personal electronics

- Video games

- Set-top boxes

- Portable computing

- Portable communications

- Multimedia

There are three primary reasons to move to SLI technology: improved functionality, improved performance, and reduced size. The majority of SLI applications today benefit from improved functionality and reduced size, but we believe that speed improvements will soon play a role.

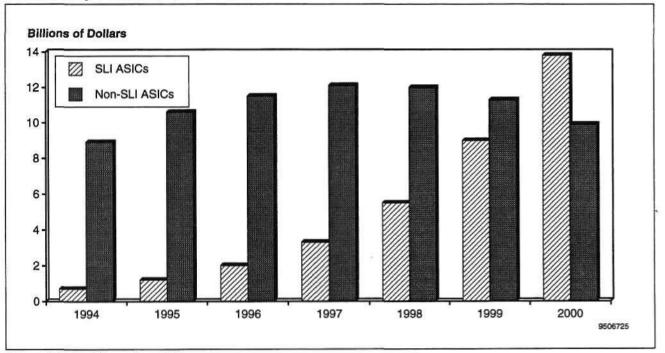

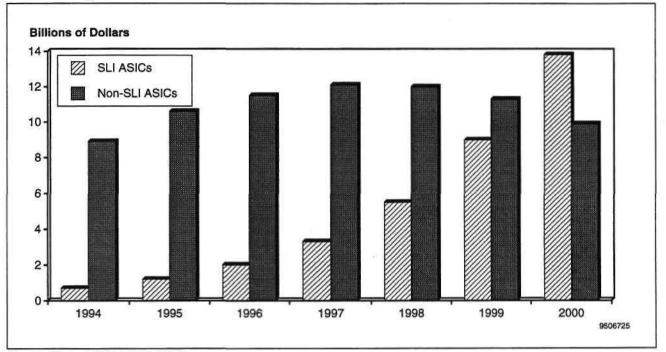

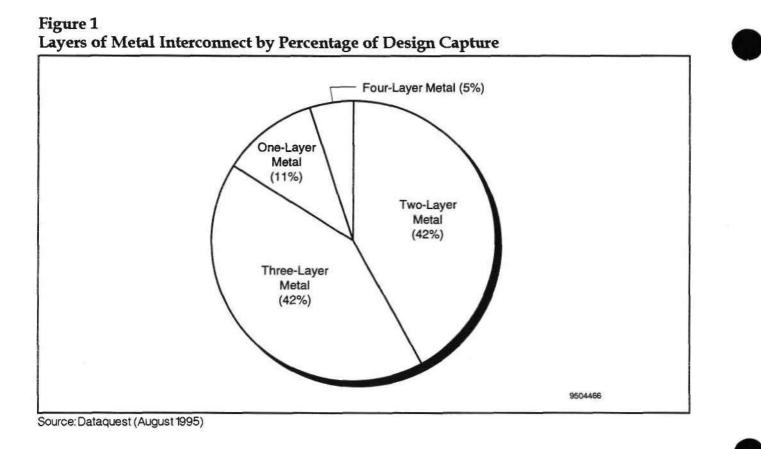

We believe that SLI ASICs account for about 10 percent of the combined total of the 1995 gate array and cell-based IC market and will account for about 60 percent of the market by the year 2000 (see Figure 1).

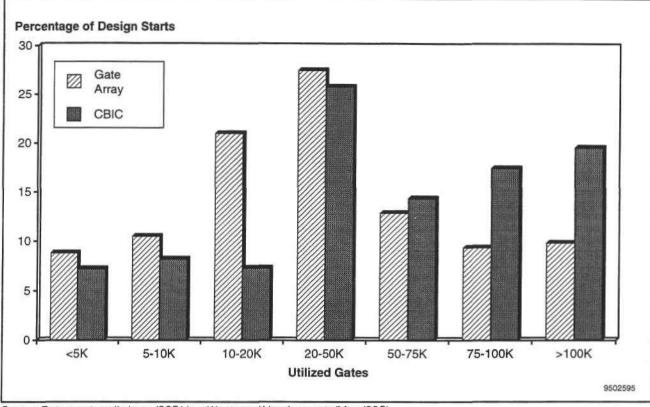

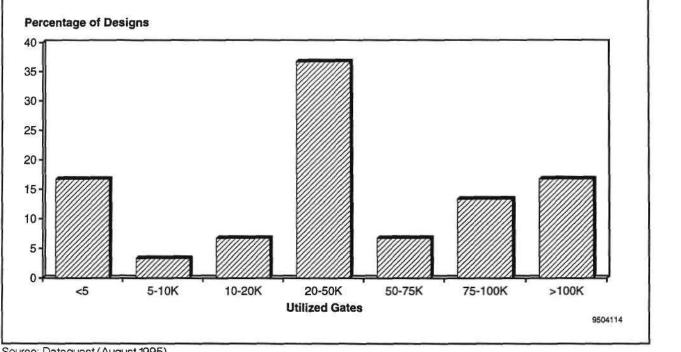

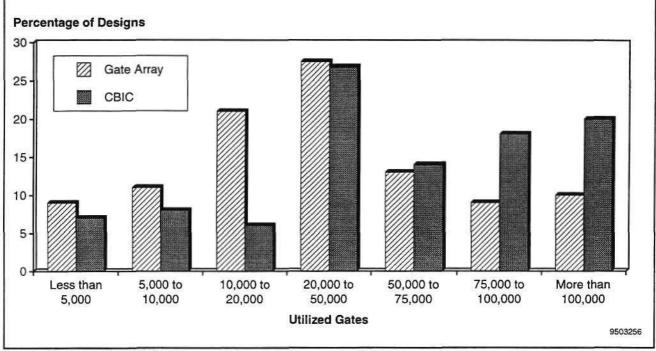

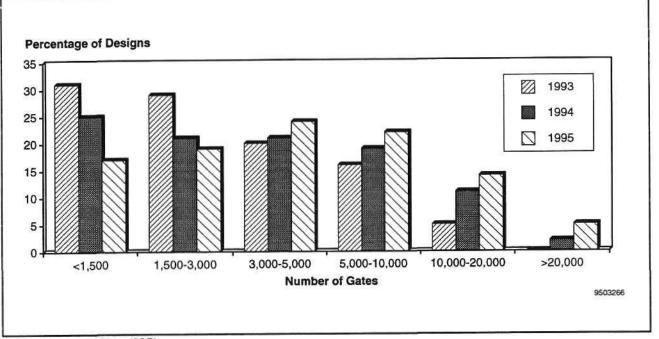

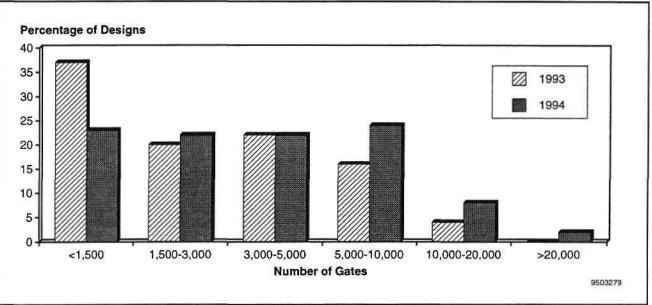

As a cross-check to our forecast, we looked back six years, when 50,000-to-100,000-gate technology was just being introduced and mainstream was 5,000 to 10,000 gates. In 1989, about 15 percent of ASIC designs were greater than 20,000; 85 percent of designs were less than 20,000 gates. In 1995, about 25 percent of ASIC designs are less than 20,000 gates and about 15 percent are greater than 100,000 utilized gates. We believe that average ASIC complexity in 2000 will be about 125,000 gates and that SLI ASICs will account for the majority of all ASICs. Judging from history, our SLI forecast could be conservative.

t.as f r∉∵ enue

#### Figure 1 Preliminary Worldwide SLI ASIC Market

Source: Dataquest (December 1995)

#### **Leading SLI Suppliers**

Nearly all ASIC companies have targeted this market for growth. Leading companies in this market include the following:

- LSI Logic

- IBM

- AT&T

- VLSI Technology

- Toshiba

- NEC *I*, *i* = *i* =

Other companies actively pursuing the SLI market with increasing revenue include Hewlett-Packard, Motorola, Texas Instruments, Mitsubishi, Fujitsu, Hitachi, Oki, Symbios, Samsung, and LG Semicon.

LSI Logic is the largest supplier in this market and has proven that ASIC companies can be profitable with a strong focus on system-level integration and intellectual property. Although LSI Logic struggled to post profits in its first ten years of operation, the company continued to invest in advanced system design methodology and intellectual property that paved the road to profitability. The company has now been highly profitable for over two years and is experiencing record revenue and record profits.

VLSI Technology is another publicly owned ASIC/ASSP company that has pursued the same strategy as LSI Logic and is also posting record revenue and profits. Other companies with a strong focus on the SLI market with profits that are more difficult to track include IBM, AT&T, Toshiba, and NEC. All of the leading SLI companies have or are close to announcing 0.35-micron processes that are capable of over 2 million gates; they are also investing heavily in advanced system design methodology and intellectual property, including dedicated cell libraries tailored to specific applications.

#### New Technologies Enable SLI

System-level integration has been dreamed of for many years, but the technologies required to execute SLI have only recently emerged. Five key areas are critical for the success of the SLI market, as follows:

- 0.35-micron processes with up to 5 million usable gates

- Comprehensive focused cell libraries

- Improved test capabilities

- Improved design tools

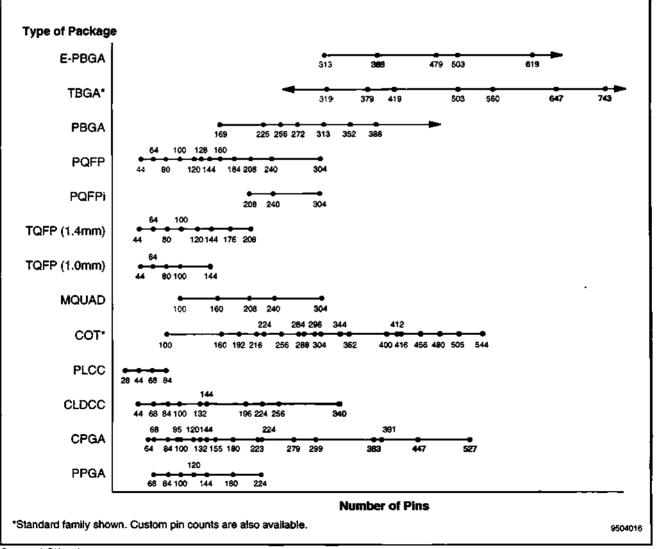

- New packages with high pin counts

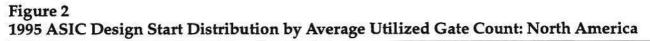

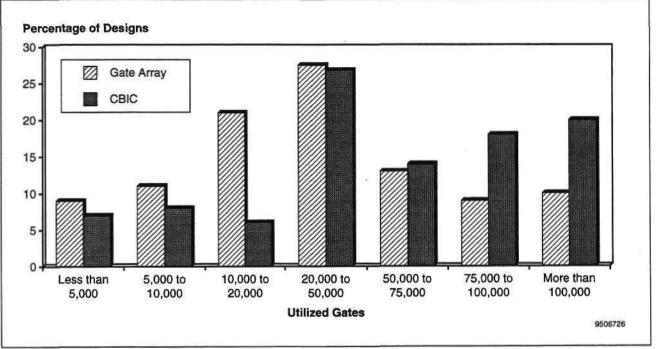

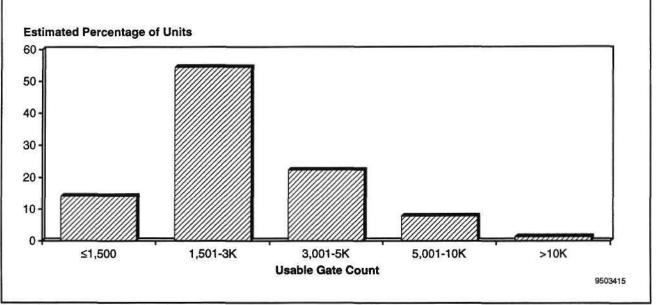

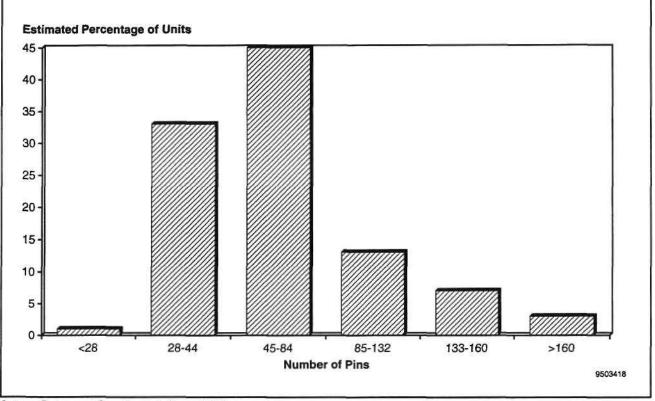

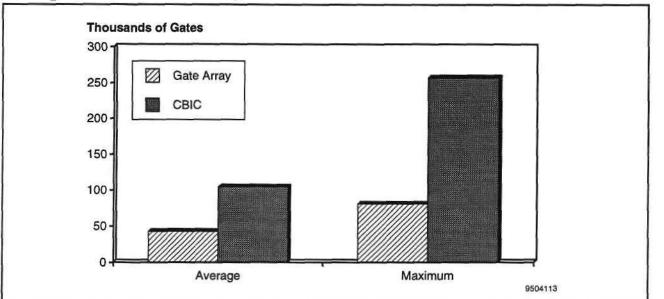

While the mainstream market is still designing in gate counts far below 1 million gates, leading ASIC suppliers are announcing 0.35-micron products with up to 5 million usable gates. The 0.35-micron product families not only give a high maximum gate count but also increase the usable gate count of the cost-effective solution. The cost-effective solution, or sweet spot, of 1995 ASIC designs is in the 50,000-to-100,000-gate range (see Figure 2). We are seeing a much higher percentage of designs with greater than 100,000 usable gates as system designers use 0.6-micron and 0.5-micron ASIC families. As system designers strive for system-level solutions and embrace 0.35-micron ASIC families, the sweet spot of these product families will be close to 1 million gates, which offers considerable silicon real estate for incorporating system functions on a single chip.

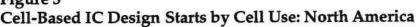

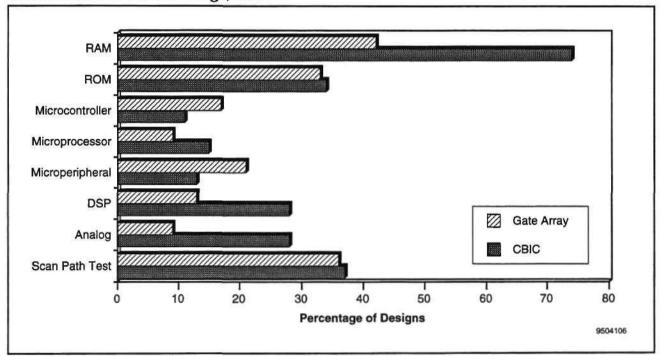

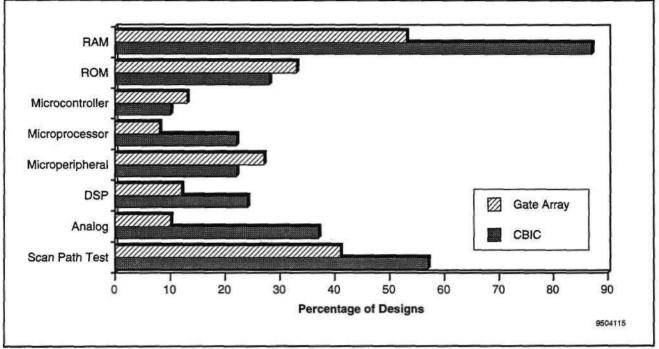

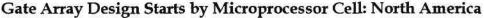

Today, only a small portion of gate arrays and cell-based ICs have on-chip compute engines or microprocessors. The microprocessor cores have simply been too large and therefore not cost-effective for incorporation into the ASIC design. We believe that with the new 0.35-micron and 0.25-micron product families, we will see a much higher percentage of compute engines, such as the MIPS and ARM cores, going on chip. Memory and logic are available today and are practical, as shown in Figure 3.

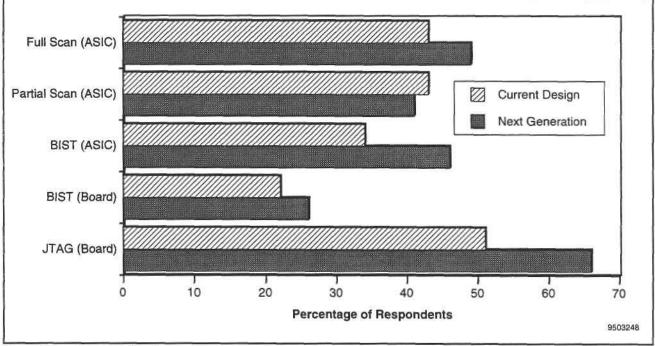

Test is also critical for SLI designs. Over 40 percent of cell-based designs in 1995 had on-chip test (see Figure 3), and most designs over 100,000 gates had on-chip test.

4

Source: Dataquest (December 1995)

Source: Dataquest (December 1995)

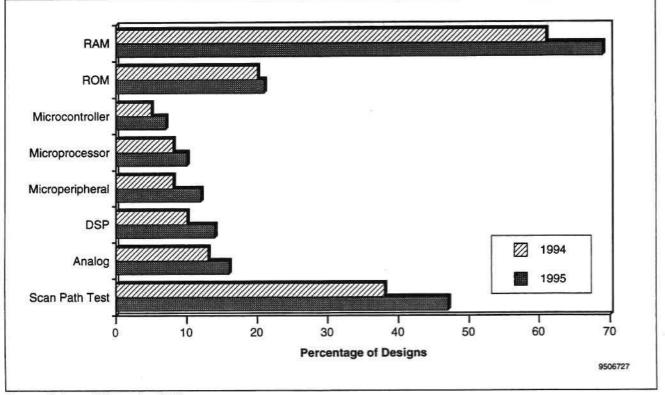

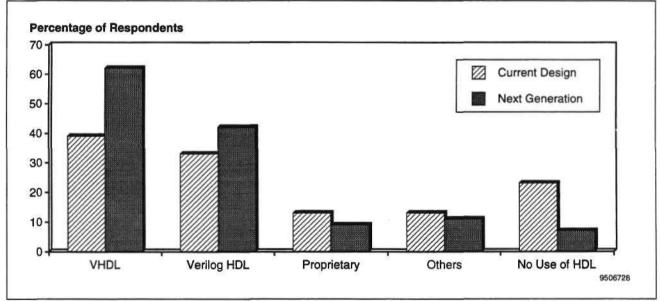

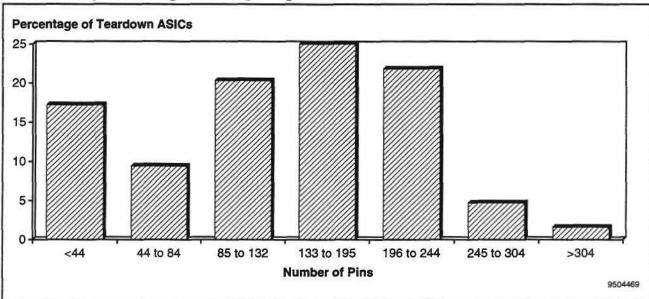

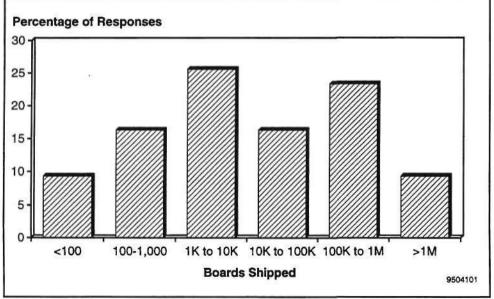

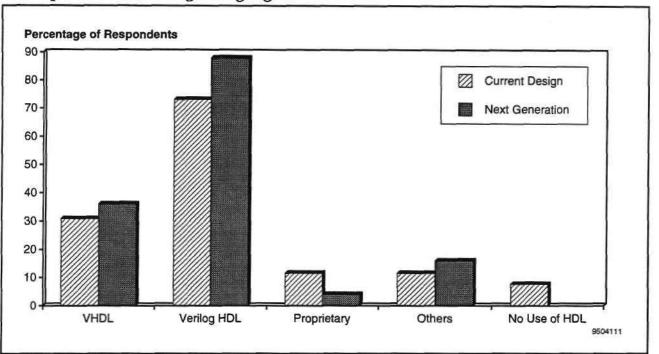

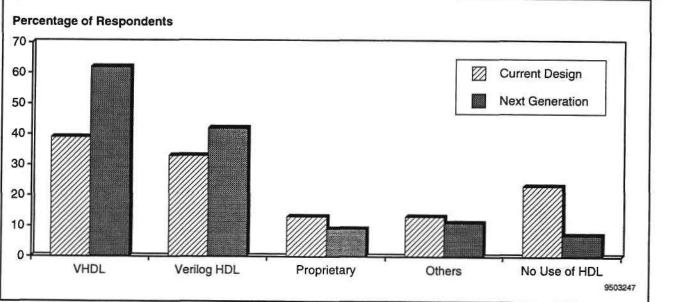

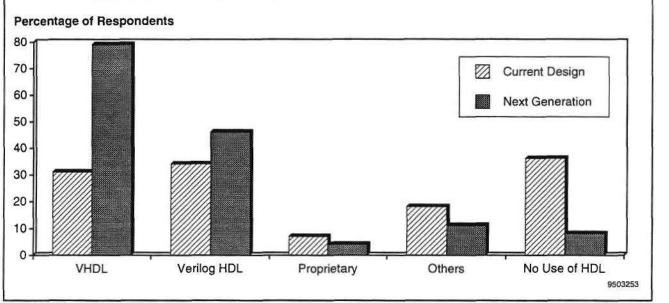

Design reuse is of paramount importance when designing high-complexity ASICs or SLI devices. System designers must design on the block level and be able to reuse and alter the intellectual property (IP) in a number of subsequent designs. Hardware description languages, specifically VHDL and Verilog, are the wave of the future. While Verilog still has a strong following and must be supported by SLI vendors, most system designers plan to use VHDL for their next-generation designs, as shown in Figure 4.

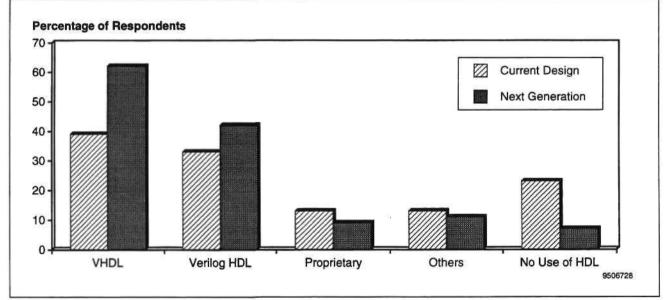

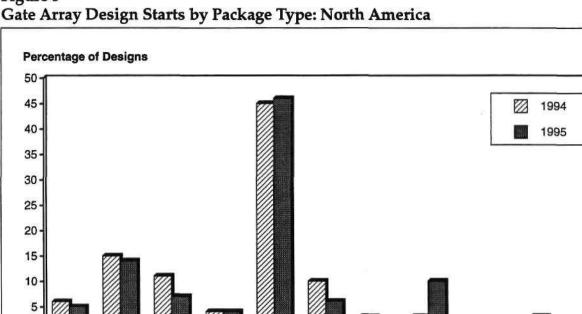

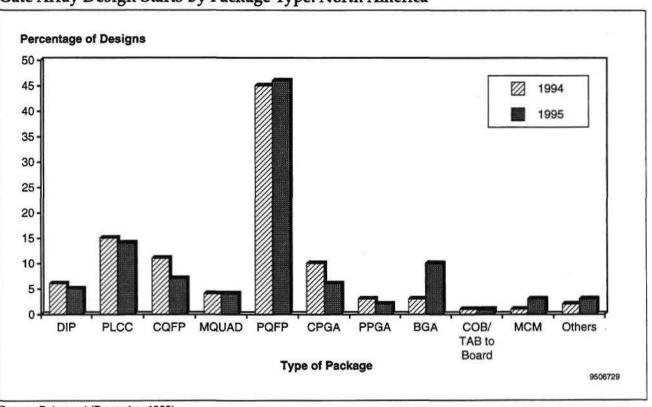

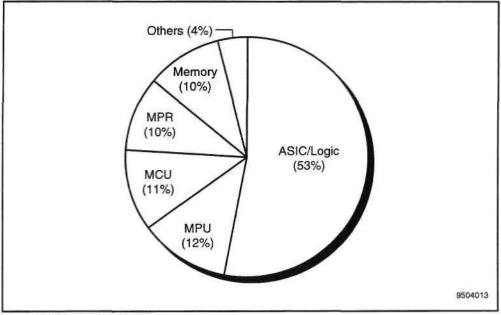

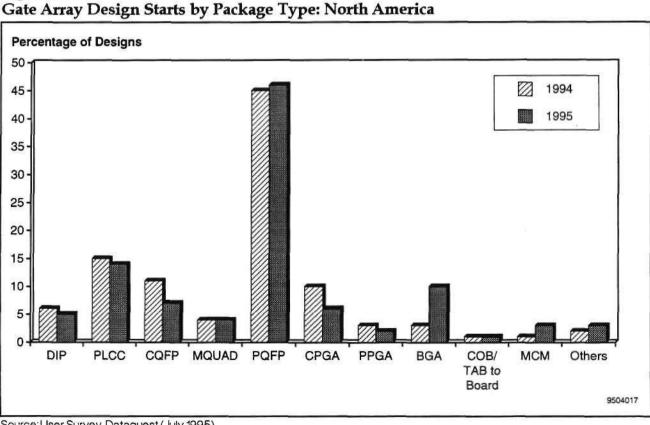

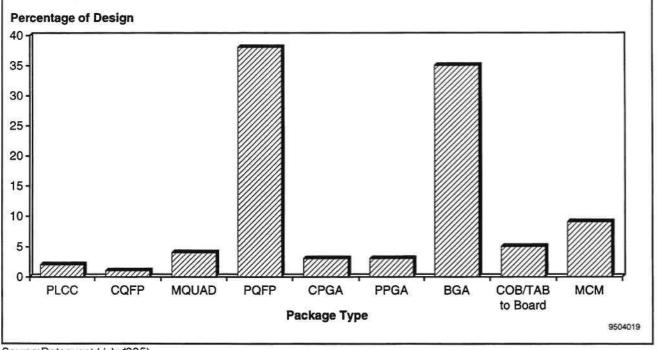

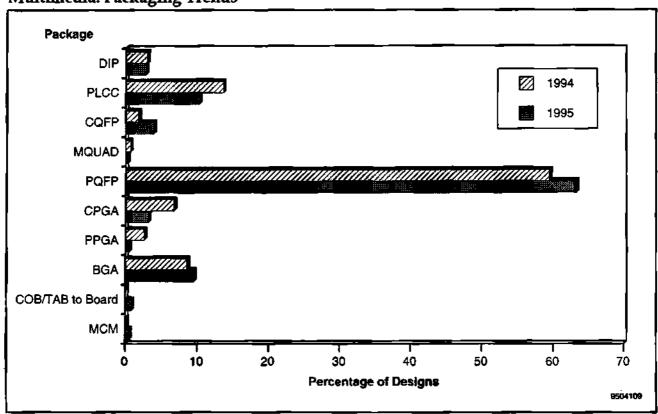

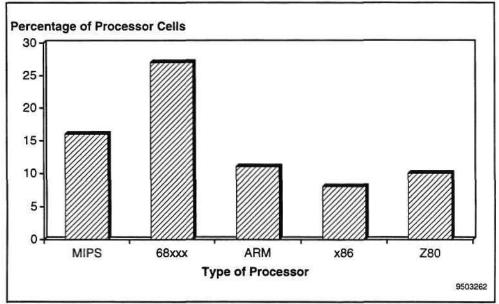

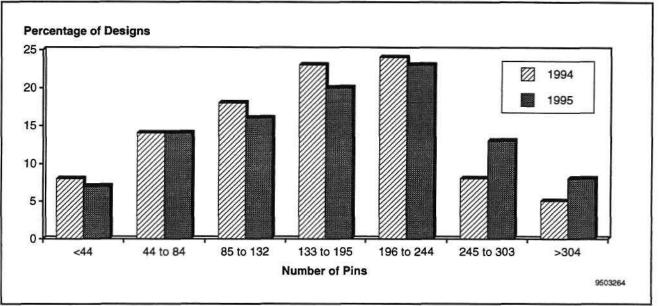

New developments in packaging technology are also spurring the growth of the SLI market. Ball grid array packages (BGA) have made major strides in the high-pin-count area (greater than 250 pins), and we believe that BGAs will be the package of choice for mainstream SLI designs of the future. BGAs now account for about 10 percent of gate array designs today (see Figure 5) and we believe that they will account for over 40 percent of all ASIC designs and over 70 percent of SLI designs in the year 2000.

#### Figure 4 Use of Hardware Description Languages: North America

Source: Dataquest (December 1995)

bove

## Figure 5

Source: Dataquest (December 1995)

PLCC

CQFP

MQUAD

PQFP

CPGA

Type of Package

PPGA

BGA

COB/

TAB to Board

MCM

Others

9506729

DIP

#### **Dataquest Perspective**

The SLI market is poised for rapid growth. Advances in manufacturing processes, cell libraries, design tools, and packaging will fuel this market. At this point, design tools are the weakest link and must improve to bring widespread acceptance of SLI technology.

The benefits to suppliers and users are many. For suppliers, SLI is the well-paved road to profitability. Suppliers must focus on advanced system design methodology, advanced processes, design reuse, and IP, including focused cell libraries dedicated to specific applications. Supplier differentiation will be determined by system knowledge of the specific application, library offering, and track record in the specific application.

The benefits of SLI to users or system designers include the following:

- Improved design cycle times

- Improved design flexibility

- Improved performance

- Improved functionality

- Improved system profit margins

The bottom line is that if system designers receive improved system profit margins by using SLI technology, SLI suppliers will also receive improved profit margins. Invest now or be left behind!

#### For More Information...

| Bryan Lewis, Principal Analyst |                      |

|--------------------------------|----------------------|

| Internet address               | blewis@dataquest.com |

| Via fax                        |                      |

The content of this report represents our interpretation and analysis of information generally available to the public or released by responsible individuals in the subject companies, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients. Reproduction or disclosure in whole or in part to other parties shall be made upon the written and express consent of Dataquest. ©1995 Dataquest Incorporated—Reproduction Prohibited

Dataquest

Dataquest is a registered trademark of A.C. Nielsen Company

Perspective

ASICs Worldwide Dataquest Predicts

### **SLI to Dominate ASIC Market by 2000**

Abstract: Dataquest is introducing a new area of research called "system-level integration" (SLI), also known as "system on a chip." Under the SLI umbrella is both hardware and software co-design, as well as SLI application-specific integrated circuits (ASICs) sold to one user and SLI application-specific standard products (ASSPs) sold to more than one user. Today, the SLI ASIC market is about \$1.1 billion and accounts for about 10 percent of the ASIC market (gate arrays and cell-based ICs). Dataquest predicts the SLI ASIC market will reach \$14 billion by the year 2000 and account for about 60 percent of the ASIC market. In this document, Dataquest explores SLI applications, leading suppliers, and technology drivers. We also forecast the future of this dynamic market. By Bryan Lewis

#### System-Level Integration: Profits on a Chip

We are entering a new era of electronic system design that we are calling "system-level integration" (SLI). We now have the technology to incorporate the entire system on a single chip. Design methodology, design reuse, and intellectual property will play vital roles in determining the winners among both suppliers and users. Companies such as LSI Logic and VLSI Technology have proven to Wall Street that ASIC suppliers can be profitable if bets are placed in the right areas. System suppliers are finding many benefits to using SLI technology, including improved design times, improved performance, and improved product differentiation, all of which help increase profit margins. SLI is the well-paved road to profits for both suppliers and users.

#### Dataquest

Program: ASICs Worldwide Product Code: ASIC-WW-PD-9502 Publication Date: December 18, 1995 Filing: Perspective (For Cross-Industry, file in the Semiconductors, Volume 2 of 3 binder behind the ASICs Worldwide name)

#### **SLI Definition**

At its October 1995 Semiconductor Conference, Dataquest introduced a new term and area of research to the industry—system-level integration. Other terms used in the industry today that have a similar meaning include "system on a chip" or "systems on silicon." We have not chosen these terms because they imply that the system is hardware only. We strongly believe that future system design will include hardware/software co-design, so we have chosen a broader term that encompasses both elements. This document focuses on the hardware portion of the market, and we define the hardware market as follows:

System-Level Integration: An integrated circuit that contains a compute engine, memory, and logic on a single chip and has more than 100,000 utilized gates.

There are two types of SLI devices: ASICs (application-specific integrated circuits that are sold to a single user) and ASSPs (application-specific standard products that are sold to more than one user).

#### **Market Size and Applications**

Dataquest's preliminary 1995 estimate for the SLI ASIC market is \$1.1 billion, and we estimate \$0.9 billion for SLI ASSPs. About half of the 1995 SLI ASSP market is in telecom chips, including LANs, modems, switching, wireless, and Asynchronous Transfer Mode (ATM). The other half of the SLI ASSP market is in graphics, audio, core logic, and consumer.

SLI ASICs are entering the market at a rapid pace, with many high-volume applications slated to use the technology, including the following:

- Personal electronics

- Video games

- Set-top boxes

- Portable computing

- Portable communications

- Multimedia

There are three primary reasons to move to SLI technology: improved functionality, improved performance, and reduced size. The majority of SLI applications today benefit from improved functionality and reduced size, but we believe that speed improvements will soon play a role.

We believe that SLI ASICs account for about 10 percent of the combined total of the 1995 gate array and cell-based IC market and will account for about 60 percent of the market by the year 2000 (see Figure 1).

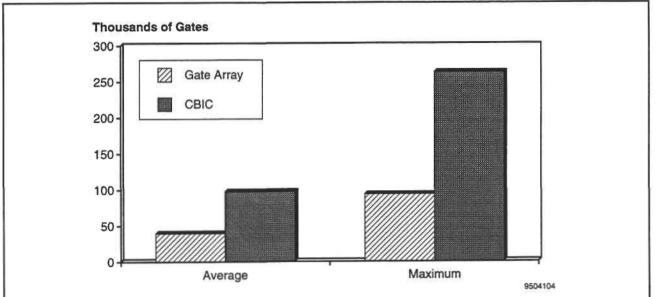

As a cross-check to our forecast, we looked back six years, when 50,000-to-100,000-gate technology was just being introduced and mainstream was 5,000 to 10,000 gates. In 1989, about 15 percent of ASIC designs were greater than 20,000; 85 percent of designs were less than 20,000 gates. In 1995, about 25 percent of ASIC designs are less than 20,000 gates and about 15 percent are greater than 100,000 utilized gates. We believe that average ASIC complexity in 2000 will be about 125,000 gates and that SLI ASICs will account for the majority of all ASICs. Judging from history, our SLI forecast could be conservative.

#### Figure 1 Preliminary Worldwide SLI ASIC Market

Source: Dataquest (December 1995)

#### **Leading SLI Suppliers**

Nearly all ASIC companies have targeted this market for growth. Leading companies in this market include the following:

- LSI Logic

- IBM

- AT&T

- VLSI Technology

- Toshiba

- NEC

Other companies actively pursuing the SLI market with increasing revenue include Hewlett-Packard, Motorola, Texas Instruments, Mitsubishi, Fujitsu, Hitachi, Oki, Symbios, Samsung, and LG Semicon.

LSI Logic is the largest supplier in this market and has proven that ASIC companies can be profitable with a strong focus on system-level integration and intellectual property. Although LSI Logic struggled to post profits in its first ten years of operation, the company continued to invest in advanced system design methodology and intellectual property that paved the road to profitability. The company has now been highly profitable for over two years and is experiencing record revenue and record profits.

VLSI Technology is another publicly owned ASIC/ASSP company that has pursued the same strategy as LSI Logic and is also posting record revenue

ASIC-WW-PD-9502

and profits. Other companies with a strong focus on the SLI market with profits that are more difficult to track include IBM, AT&T, Toshiba, and NEC. All of the leading SLI companies have or are close to announcing 0.35-micron processes that are capable of over 2 million gates; they are also investing heavily in advanced system design methodology and intellectual property, including dedicated cell libraries tailored to specific applications.

#### New Technologies Enable SLI

System-level integration has been dreamed of for many years, but the technologies required to execute SLI have only recently emerged. Five key areas are critical for the success of the SLI market, as follows:

- 0.35-micron processes with up to 5 million usable gates

- Comprehensive focused cell libraries

- Improved test capabilities

- Improved design tools

- New packages with high pin counts

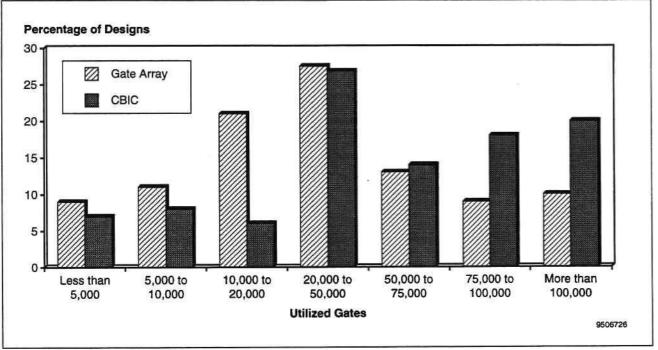

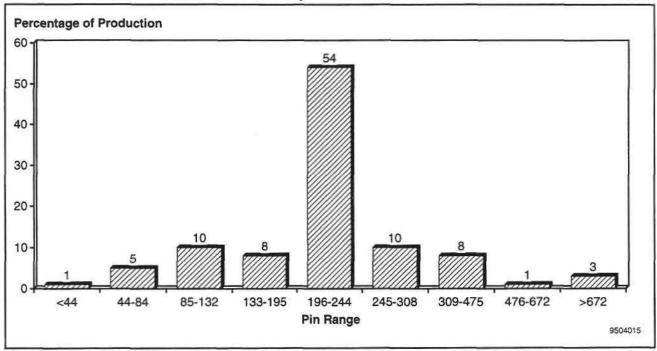

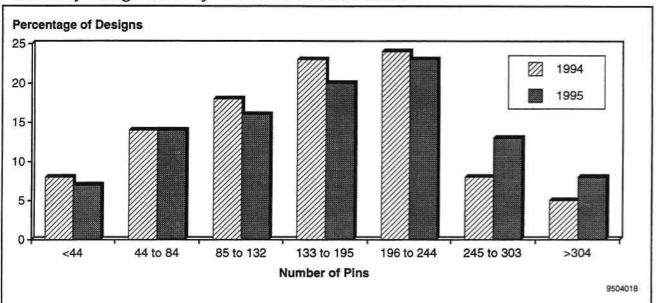

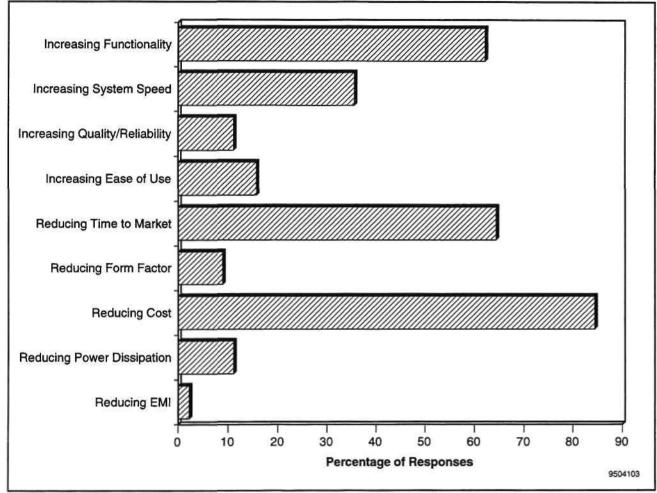

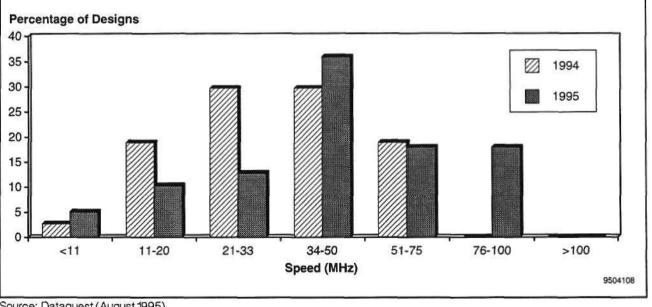

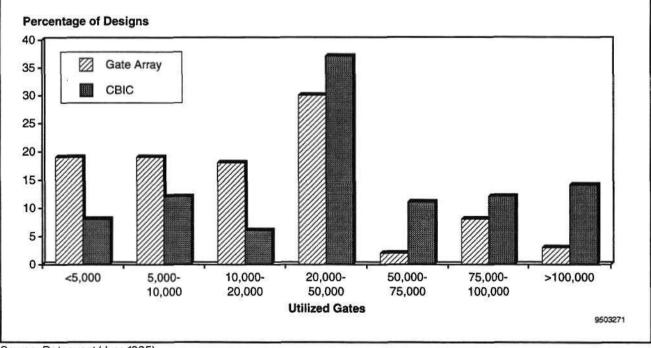

While the mainstream market is still designing in gate counts far below 1 million gates, leading ASIC suppliers are announcing 0.35-micron products with up to 5 million usable gates. The 0.35-micron product families not only give a high maximum gate count but also increase the usable gate count of the cost-effective solution. The cost-effective solution, or sweet spot, of 1995 ASIC designs is in the 50,000-to-100,000-gate range (see Figure 2). We are seeing a much higher percentage of designs with greater than 100,000 usable gates as system designers use 0.6-micron and 0.5-micron ASIC families. As system designers strive for system-level solutions and embrace 0.35-micron ASIC families, the sweet spot of these product families will be close to 1 million gates, which offers considerable silicon real estate for incorporating system functions on a single chip.

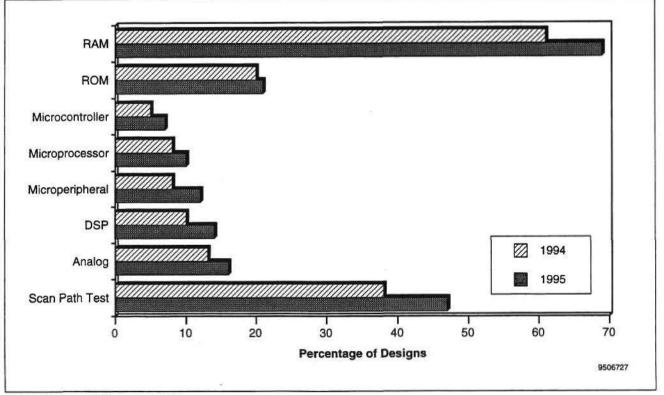

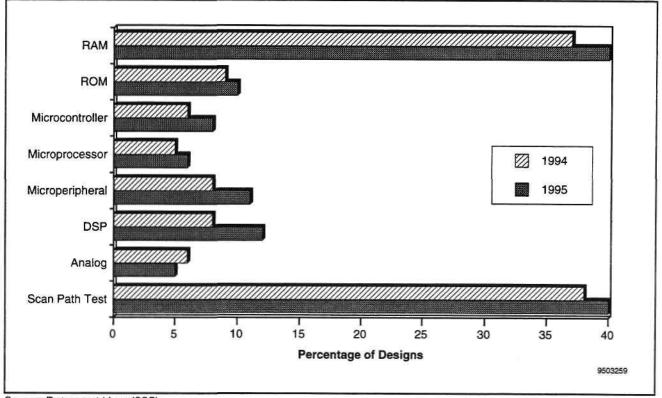

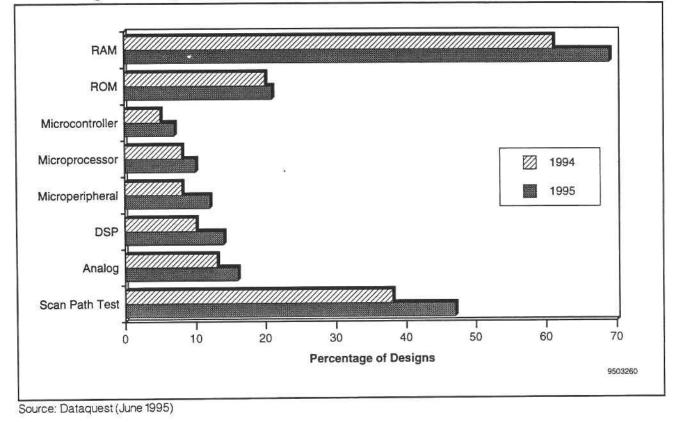

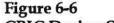

Today, only a small portion of gate arrays and cell-based ICs have on-chip compute engines or microprocessors. The microprocessor cores have simply been too large and therefore not cost-effective for incorporation into the ASIC design. We believe that with the new 0.35-micron and 0.25-micron product families, we will see a much higher percentage of compute engines, such as the MIPS and ARM cores, going on chip. Memory and logic are available today and are practical, as shown in Figure 3.

Test is also critical for SLI designs. Over 40 percent of cell-based designs in 1995 had on-chip test (see Figure 3), and most designs over 100,000 gates had on-chip test.

1

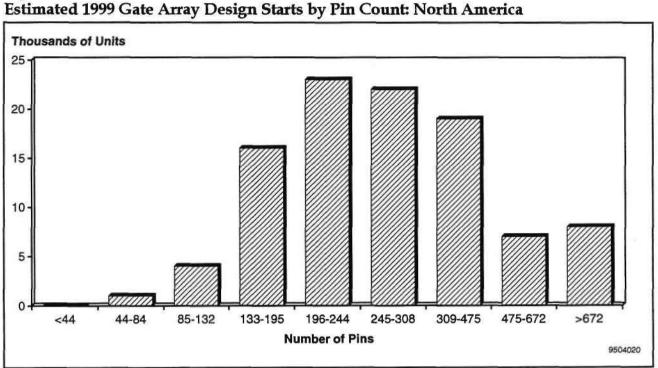

#### Figure 2 1995 ASIC Design Start Distribution by Average Utilized Gate Count: North America

Source: Dataquest (December 1995)

#### Figure 3

### Cell-Based IC Design Starts by Cell Use: North America

Source: Dataquest (December 1995)

Design reuse is of paramount importance when designing high-complexity ASICs or SLI devices. System designers must design on the block level and be able to reuse and alter the intellectual property (IP) in a number of subsequent designs. Hardware description languages, specifically VHDL and Verilog, are the wave of the future. While Verilog still has a strong following and must be supported by SLI vendors, most system designers plan to use VHDL for their next-generation designs, as shown in Figure 4.

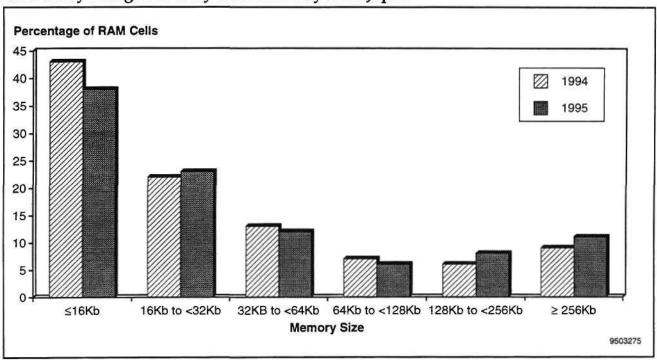

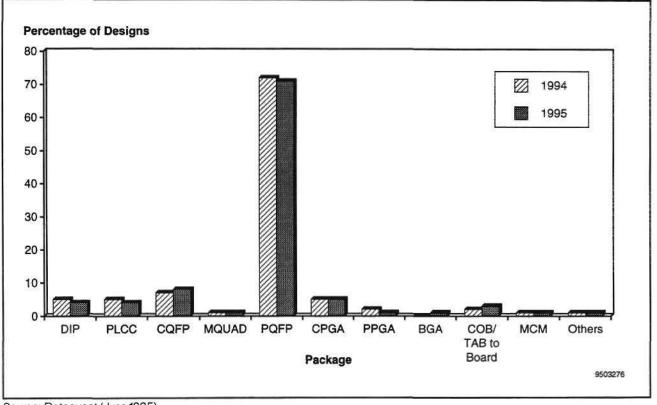

New developments in packaging technology are also spurring the growth of the SLI market. Ball grid array packages (BGA) have made major strides in the high-pin-count area (greater than 250 pins), and we believe that BGAs will be the package of choice for mainstream SLI designs of the future. BGAs now account for about 10 percent of gate array designs today (see Figure 5) and we believe that they will account for over 40 percent of all ASIC designs and over 70 percent of SLI designs in the year 2000.

#### Figure 4 Use of Hardware Description Languages: North America

Source: Dataquest (December 1995)

#### Figure 5 Gate Array Design Starts by Package Type: North America

Source: Dataquest (December 1995)

#### **Dataquest Perspective**

The SLI market is poised for rapid growth. Advances in manufacturing processes, cell libraries, design tools, and packaging will fuel this market. At this point, design tools are the weakest link and must improve to bring widespread acceptance of SLI technology.

The benefits to suppliers and users are many. For suppliers, SLI is the well-paved road to profitability. Suppliers must focus on advanced system design methodology, advanced processes, design reuse, and IP, including focused cell libraries dedicated to specific applications. Supplier differentiation will be determined by system knowledge of the specific application, library offering, and track record in the specific application.

The benefits of SLI to users or system designers include the following:

- Improved design cycle times

- Improved design flexibility

- Improved performance

- Improved functionality

- Improved system profit margins

The bottom line is that if system designers receive improved system profit margins by using SLI technology, SLI suppliers will also receive improved profit margins. Invest now or be left behind!

Qty:

1

```

ASIC-WW-PD-9502

Ms. Maria Valenzuela

Dataquest Incorporated

1-1100

.,

--INTERNAL DIST.--

```

2

5

#### For More Information...

| Bryan Lewis, Principal Analyst |                      |

|--------------------------------|----------------------|

| Internet address               | blewis@dataquest.com |

| Via fax                        |                      |

The content of this report represents our interpretation and analysis of information generally available to the public or released by responsible individuals in the subject companies, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients. Reproduction or disclosure in whole or in part to other parties shall be made upon the written and express consent of Dataquest. ©1995 Dataquest Incorporated—Reproduction Prohibited

Dataquest B a company of The Dan & Bradstreet Corporation

Dataquest is a registered trademark of A.C. Nielsen Company

#### Market Analysis

ASICs Worldwide Market Analysis

## **Cell-Based ICs Soar in 1994 ASIC Market Share**

**Abstract:** Cell-based IC revenue growth outpaced that of MOS PLDs and gate arrays, according to Dataquest's 1994 market share survey. In this article, Dataquest examines the 1994 ASIC market share rankings by company and product and explores the key areas where suppliers can invest to maximize profits. By Bryan Lewis

#### **Traditional ASIC Suppliers Move to Higher Ground**

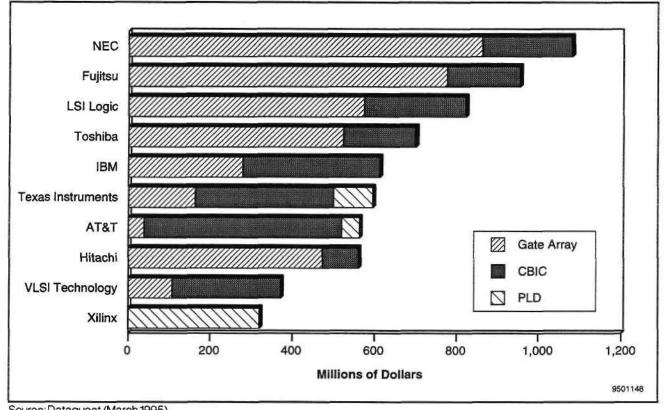

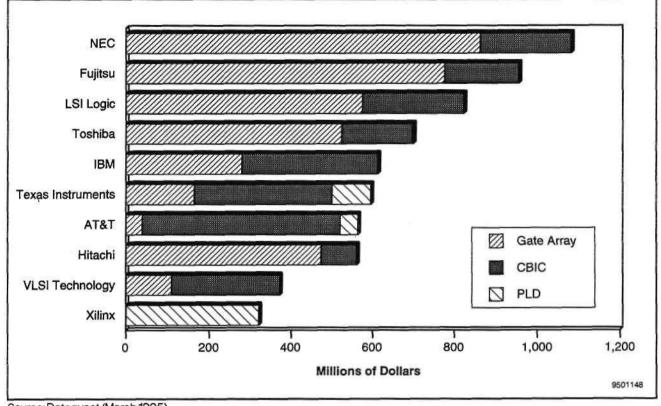

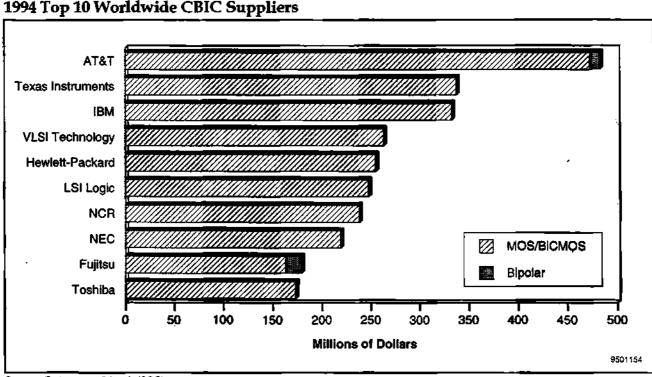

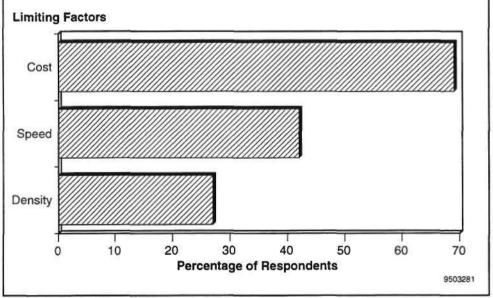

Leading ASIC suppliers are shifting their focus from low-value commodity gate arrays to higher-margin, value-added cell-based ICs (CBICs). According to Dataquest's 1994 market share estimates, the top five ASIC suppliers experienced a combined 50 percent increase in CBIC sales over 1993, compared to a 15 percent increase in MOS gate array sales. LSI Logic, the largest merchant ASIC supplier and second-largest MOS gate array supplier, posted an outstanding 176 percent increase in CBIC sales, compared to a meager 4 percent increase in gate array sales. The entire worldwide MOS CBIC market had the highest growth rate of all the ASIC products, posting a 29 percent increase, followed by MOS PLDs with a 23 percent increase and MOS gate arrays with a 19 percent increase. Traditional ASIC suppliers are moving to higher-density devices (more than 100,000 gates) using large functional blocks where margins are higher, while FPGA and CPLD suppliers are moving in on the lower-density market to fill the void.

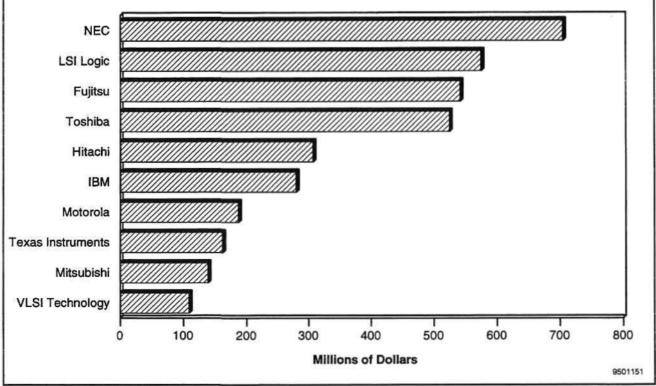

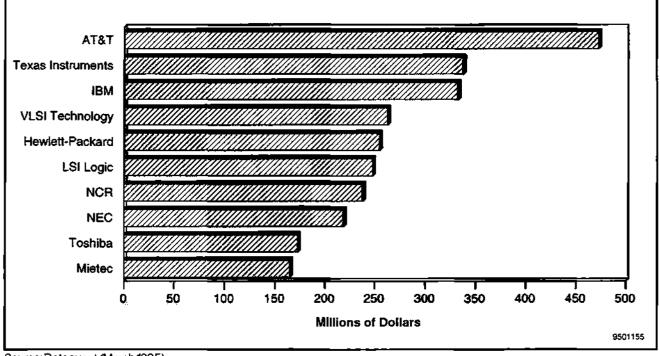

During 1994, NEC extended its lead over Fujitsu in total ASIC sales (see Figure 1) by increasing its CBIC sales 87 percent. LSI Logic strengthened its position in total ASIC sales by jumping from the No. 12 position in 1993 total CBIC sales to No. 6 in 1994 sales. Xilinx was one of the big winners in 1994 and set the record for the first exclusively MOS PLD company to make the top 10 in total ASIC sales. Xilinx's success in making the top 10 supplier

#### Dataquest

Program: ASICs Worldwide Product Code: ASIC-WW-MA-9501 Publication Date: March 20, 1995 Filing: Market Analysis

#### Figure 1 1994 Top 10 Worldwide ASIC Suppliers

Source: Dataguest (March 1995)

list is proof that MOS PLDs are filling the gap as traditional ASIC suppliers are abandoning the lower-density market.

Two important points should be kept in mind when examining the following market share rankings. First, yen appreciation against the dollar helped most Japanese companies post better-than-average growth rates (the yen appreciated about 8 percent against the dollar). Second, Dataquest estimates include sales to internal division (intracompany sales). Although NEC is the largest total ASIC supplier, LSI Logic is the largest merchant market ASIC supplier.

#### **1994 ASIC Market Share**

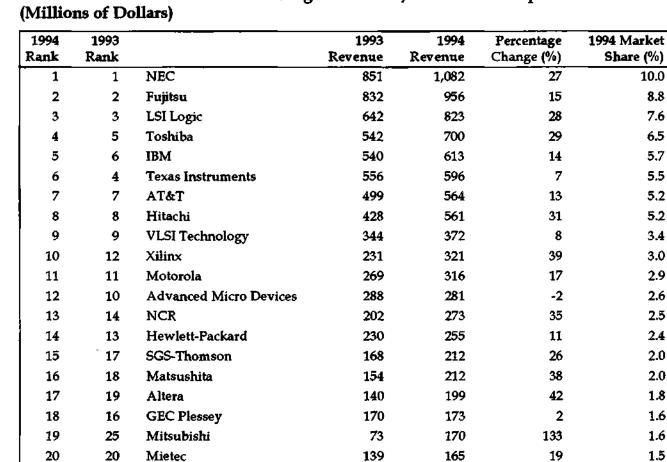

Table 1 shows the 1994 top 20 ASIC suppliers.

The following are footnotes to the ASIC market estimates:

- Total ASIC rankings include gate arrays plus CBICs plus PLDs.

- Rankings are based on dollar shipments, which include the following five sources of revenue:

- Intracompany revenue (sales to internal divisions)

- Nonrecurring engineering (NRE) revenue

- ASIC software revenue

| 1994<br>Rank | 1993<br>Rank |                        | 1993<br>Revenue | 1994<br>Revenue | Percentage<br>Change (%) | 1994 Market<br>Share (%) |

|--------------|--------------|------------------------|-----------------|-----------------|--------------------------|--------------------------|

| 1            | 1            | NEC                    | 851             | 1,082           | 27                       | 10.0                     |

| 2            | 2            | Fujitsu                | 832             | <b>95</b> 6     | 15                       | 8.8                      |

| 3            | 3            | LSI Logic              | 642             | 823             | 28                       | 7.6                      |

| 4            | 5            | Toshiba                | 542             | 700             | 29                       | 6.5                      |

| 5            | 6            | IBM                    | 540             | 613             | 14                       | 5.7                      |

| 6            | 4            | Texas Instruments      | 55 <del>6</del> | 596             | 7                        | 5.5                      |

| 7            | 7            | AT&T                   | 499             | 564             | 13                       | 5.2                      |

| 8            | 8            | Hitachi                | 428             | 561             | 31                       | 5.2                      |

| 9            | 9            | VLSI Technology        | 344             | 372             | 8                        | 3.4                      |

| 10           | 12           | Xilinx                 | 231             | 321             | 39                       | 3.0                      |

| 11           | 11           | Motorola               | 26 <del>9</del> | 316             | 17                       | 2.9                      |

| 12           | 10           | Advanced Micro Devices | 288             | 281             | -2                       | 2.6                      |

| 13           | 14           | NCR                    | 202             | 273             | 35                       | 2.5                      |

| 14           | 13           | Hewlett-Packard        | 230             | 255             | 11                       | 2.4                      |

| 15           | 17           | SGS-Thomson            | 168             | 212             | 26                       | 2.0                      |

| 16           | 18           | Matsushita             | 154             | 212             | 38                       | 2.0                      |

| 17           | 19           | Altera                 | 140             | 1 <del>99</del> | 42                       | 1.8                      |

| 18           | 16           | GEC Plessey            | 170             | 173             | 2                        | 1.6                      |

| 19           | 25           | Mitsubishi             | 73              | 170             | 133                      | 1.0                      |

| 20           | 20           | Mietec                 | 139             | 165             | 19                       | 1.5                      |

# Table 11994 Worldwide Market Share Ranking: Total MOS/BiCMOS and Bipolar ASIC(Millions of Dollars)

Source: Dataquest (March 1995)

- PLD development kit revenue

- Device production revenue

- Full-custom IC revenue is excluded from ASIC market share.

- ASIC product revenue is based on the combined revenue from digital, mixed analog/digital, and analog product.

- The U.S. dollar depreciated 8.4 percent against the yen during 1993. Dataquest's exchange rates are: U.S.\$1 = ¥111.20 (1993), U.S.\$1 = ¥101.81 (1994).

#### **Product Overview**

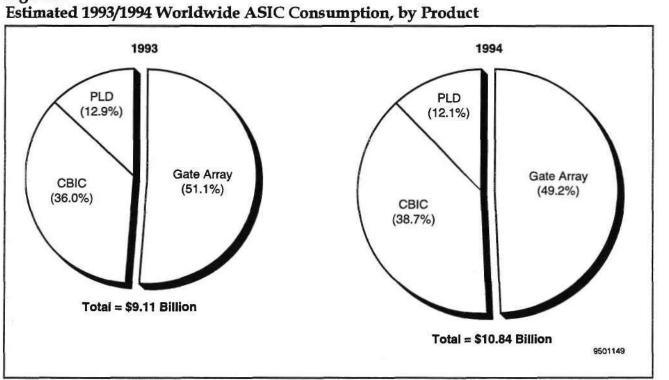

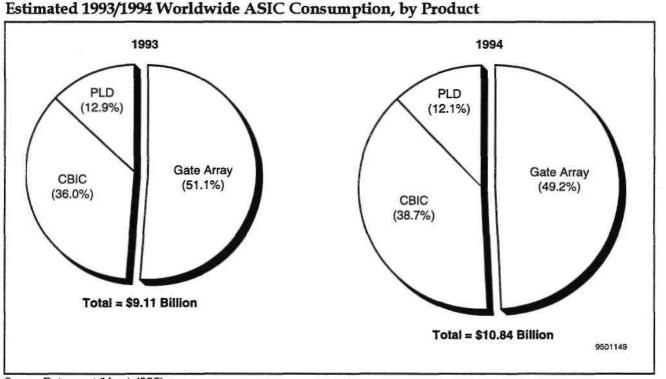

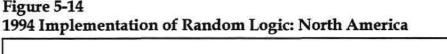

Figure 2 presents the composition of the ASIC market by product. Although gate arrays continue to dominate the market, CBICs are gaining market share. Total PLDs lost market share because bipolar PLDs had a dismal year, declining 29.4 percent (see Table 2). Bipolar PLDs are being replaced by MOS PLDs, which had a solid 22.6 percent growth rate, exceeding the growth rate of the total ASIC market.

# Figure 2

Source: Dataquest (March 1995)

#### Table 2

Estimated 1993/1994 Worldwide ASIC Consumption, by Product (Millions of Dollars)

|                          | 1993  | 1994   | Percentage Change |

|--------------------------|-------|--------|-------------------|

| MOS/BiCMOS Gate Array    | 3,785 | 4,520  | 19.4              |

| Bipolar Gate Array       | 873   | 818    | -6.3              |

| MOS/BiCMOS Cell-Based IC | 3,201 | 4,116  | 28.6              |

| Bipolar Cell-Based IC    | 82    | 77     | -6.1              |

| MOS/BICMOS PLD           | 925   | 1,134  | 22.6              |

| Bipolar PLD              | 248   | 175    | -29.4             |

| Total Market             | 9,114 | 10,840 | 18.9              |

Source: Dataquest (March 1995)

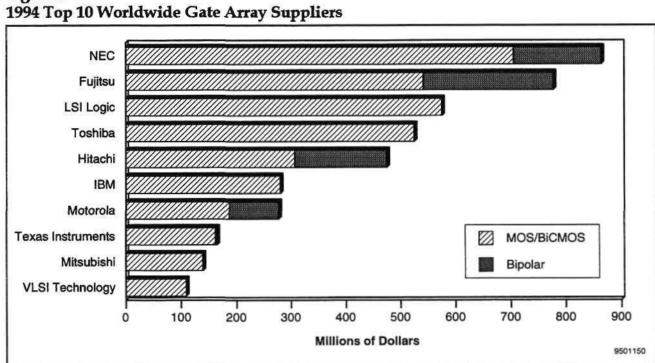

#### **Gate Arrays**

The year 1994 was good for the MOS/BiCMOS gate array market, which had 19.4 percent growth, and an above-average year for bipolar gate arrays, with a 6.3 percent decline. MOS/BiCMOS gate array growth was fueled by strong market performance in personal computers/workstations and telecommunications. The bipolar gate array market was expected to decline faster than the 6 percent reported because of declining mainframe sales. Companies such as Fujitsu had a temporary increase in mainframe computer sales, which reduced the percentage decline in bipolar gate arrays.

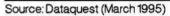

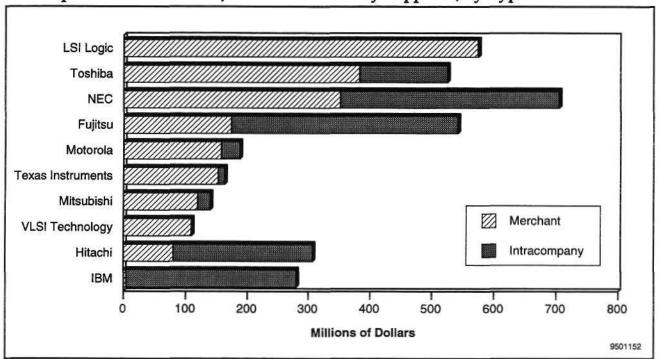

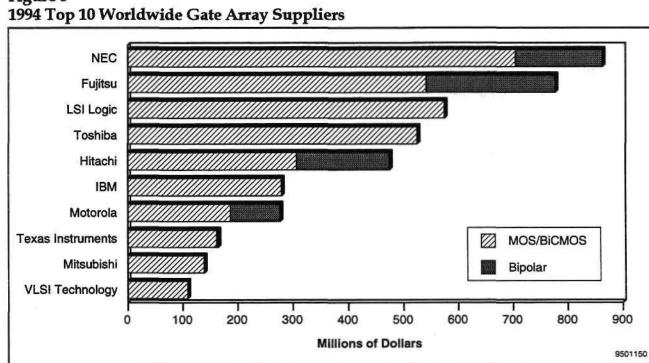

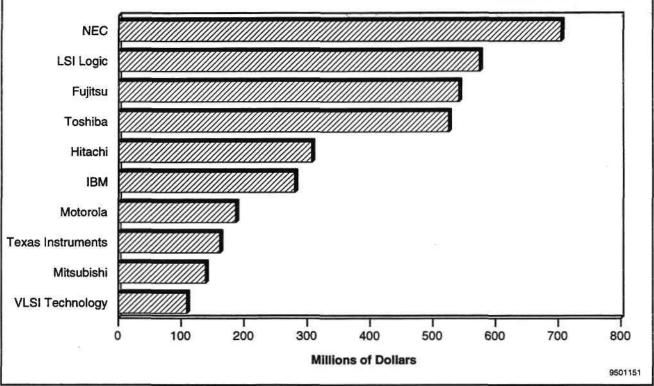

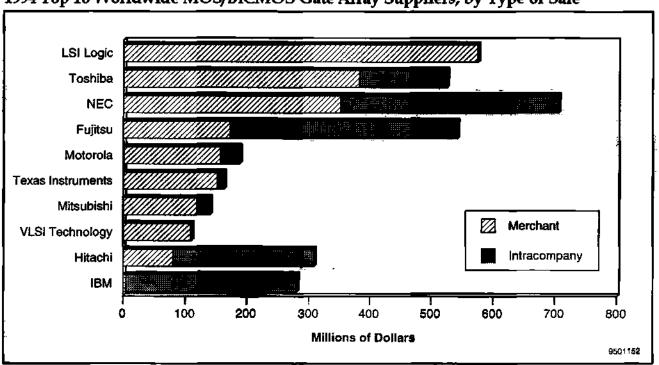

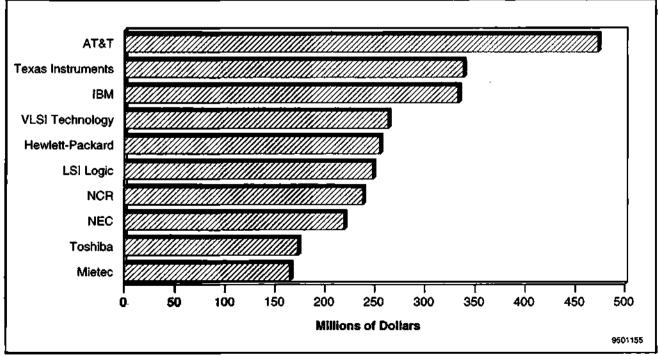

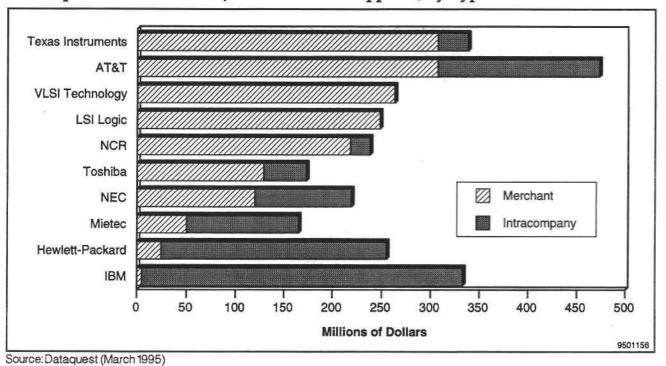

Figure 3 shows the 1994 worldwide gate array suppliers' revenue by technology of the top 10 companies. Figure 4 shows the top 10 1994 MOS/ BiCMOS gate array suppliers, while Figure 5 ranks the same suppliers by

©1995 Dataguest Incorporated

## Figure 3

Source: Dataquest (March 1995)

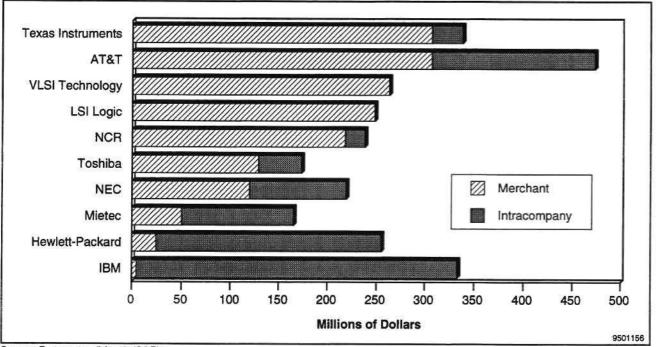

#### Figure 5 1994 Top 10 Worldwide MOS/BiCMOS Gate Array Suppliers, by Type of Sale

Source: Dataquest (March 1995)

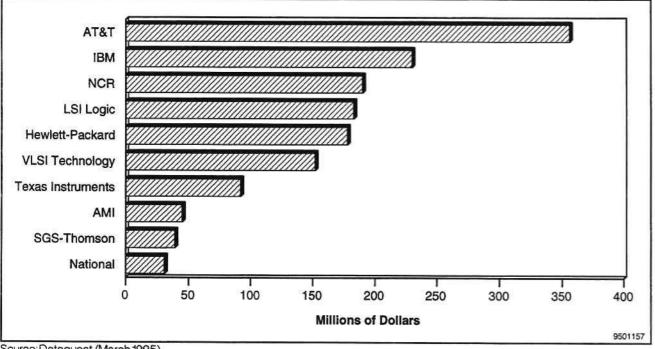

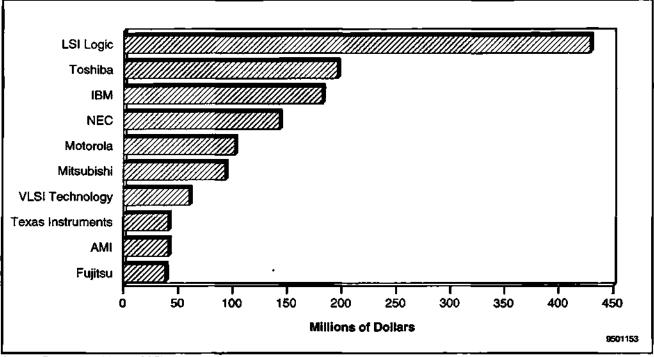

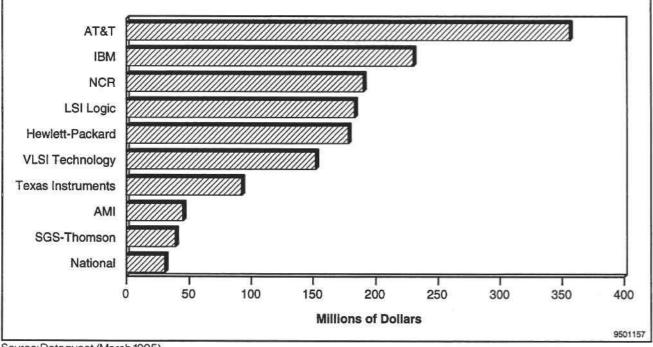

size of estimated merchant sales. Table 3 lists the hotly contested top 20 1994 worldwide MOS gate array suppliers and their respective revenue, growth rates, and market shares. Figure 6 takes a snapshot of leading MOS/BiCMOS gate array suppliers in North America.

North America-based companies grew 9 percent in 1994 worldwide MOS/ BiCMOS gate array sales, compared with 28 percent growth (including 8.4 percent yen appreciation) for Japan-based companies, 4 percent growth for Europe-based companies, and 27 percent growth for Asia/Pacific companies.

Noteworthy points regarding the 1994 gate array rankings include the following:

- NEC passed LSI Logic to become the No. 1 MOS/BiCMOS gate array supplier. However, a significant portion of NEC's sales are to internal divisions. LSI Logic remains the largest merchant gate array supplier, as shown in Figure 5.

- VLSI Technology had a weak year in MOS/BiCMOS gate arrays because the company focused on the CBIC market, where it had a solid year.

- Mitsubishi had an outstanding year, leaping from the No. 16 position in 1993 to No. 9 in 1994 MOS/BiCMOS gate arrays. Mitsubishi's 140 percent growth was driven by a few high-volume designs in the PC/workstation market.

| 1994<br>Rank | 1993<br>Rank |                        | 1993<br>Revenue | 1994<br>Revenue | Percentage<br>Change (%) | 1994 Marke<br>Share (%) |

|--------------|--------------|------------------------|-----------------|-----------------|--------------------------|-------------------------|

|              |              |                        |                 |                 |                          |                         |

| 1            | 2            | NEC                    | 550             | 705             | 28                       | 15.6                    |

| 2            | 1            | LSI Logic              | 552             | 575             | 4                        | 12.3                    |

| 3            | 3            | Fujitsu                | 466             | 542             | 1 <del>6</del>           | 12.0                    |

| 4            | 4            | Toshiba                | 427             | 525             | 23                       | 11.0                    |

| 5            | 6            | Hitachi                | 235             | 307             | 31                       | 6.                      |

| 6            | 5            | IBM                    | 243             | 280             | 15                       | 6.                      |

| 7            | 7            | Motorola               | 147             | 187             | 27                       | 4.                      |

| 8            | 9            | Texas Instruments      | <del>99</del>   | 162             | 64                       | 3.                      |

| 9            | 16           | Mitsubishi             | 58              | 139             | 140                      | 3.                      |

| 10           | 8            | VLSI Technology        | 145             | 109             | -25                      | 2.                      |

| 11           | 13           | Matsushita             | 73              | 95              | 30                       | 2                       |

| 12           | 11           | Seiko Epson            | 80              | 91              | 14                       | 2                       |

| 13           | 10           | GEC Plessey            | 83              | 88              | 6                        | 1.                      |

| 14           | 12           | SGS-Thomson            | 73              | 80              | 10                       | 1.                      |

| 15           | 15           | окі                    | 61              | 78              | 28                       | 1                       |

| 16           | 17           | Samsung                | 57              | . 68            | 19                       | 1                       |

| 17           | 18           | Sharp                  | 48              | 62              | 29                       | 1                       |

| 18           | 23           | AMI                    | 21              | 43              | 105                      | 1                       |

| 19           | 19           | National Semiconductor | 42              | 40              |                          | ō                       |

| 20           | 20           | Sony                   | 25              | 36              | 44                       | 0                       |

# Table 31994 Worldwide Market Share Ranking: MOS/BiCMOS Gate Array(Millions of Dollars)

Source: Dataquest (March 1995)

#### Figure 6 1994 Top 10 North American MOS/BiCMOS Gate Array Suppliers

Source: Dataquest (March 1995)

#### **Cell-Based ICs**

The CBIC market was the place to be for ASIC suppliers in 1994. MOS/ BiCMOS CBICs had a record year with 28.6 percent growth. One key reason for this record growth was the increased use of CBICs in Japan, primarily by large vertically integrated Japanese companies.

Although many North American companies had a good year in CBICs, total North America-based companies grew 23 percent in 1994 worldwide MOS/BiCMOS CBIC sales, compared with 54 percent growth for Japanbased companies, and 23 percent growth for Europe-based companies. Japan-based companies continue to target this market for future growth.

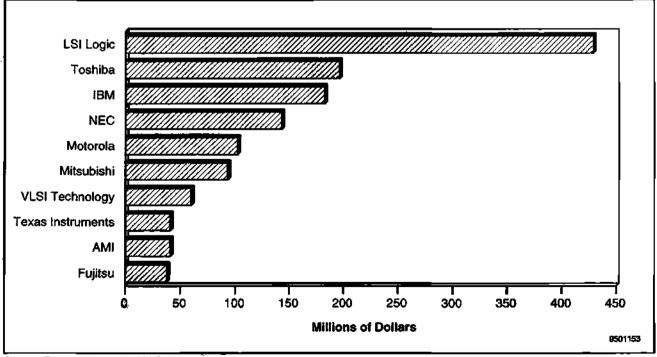

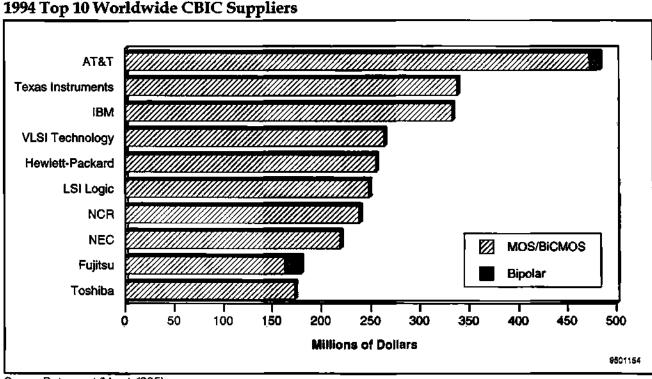

Figure 7 shows the top 10 1994 worldwide CBIC suppliers' revenue by technology. Table 4 shows the top 20 1994 worldwide MOS CBIC suppliers by their respective revenue, growth rates, and market shares. Figure 8 illustrates the top 10 worldwide MOS/BiCMOS CBIC suppliers, while Figure 9 shows the same suppliers ranked by estimated merchant sales. Figure 10 examines the top 10 1994 North American MOS/BiCMOS CBIC suppliers.

Noteworthy points regarding the 1994 CBIC rankings include the following:

LSI Logic had a stellar year in CBICs, jumping from No. 11 in 1993 MOS/BiCMOS CBIC sales to No. 6 in 1994. LSI Logic's Core-ware products are primarily CBICs, and many previously captured computer and telecom designs moved into high-volume production in 1994.

Source: Dataquest (March 1995)

Figure 7

| 1994<br>Rank | 1993<br>Rank |                        | 1993<br>Remonue | 1994<br>Barrana | Percentage | 1994 Market |

|--------------|--------------|------------------------|-----------------|-----------------|------------|-------------|

|              |              |                        | Revenue         | Revenue         | Change (%) | Share (%)   |

| 1            | 1            | A <b>T</b> &T          | 419             | 473             | 13         | 11.5        |

| 2            | 2            | Texas Instruments      | 344             | 338             | -2         | 8.2         |

| 3            | 3            | IBM                    | 297             | 333             | 12         | 8.1         |

| 4            | 5            | VLSI Technology        | 199             | 263             | 32         | 6.4         |

| 5            | 4            | Hewlett-Packard        | 230             | 255             | 11         | 6.2         |

| 6            | 11           | LSI Logic              | 90              | 248             | 176        | 6.0         |

| 7            | 7            | NCR                    | 137             | 238             | 74         | 5.8         |

| 8            | 9            | NEC                    | 117             | 219             | 87         | 5.3         |

| 9            | 10           | Toshiba                | 114             | 173             | 52         | 4.3         |

| 10           | 6            | Mietec                 | 139             | 165             | 19         | 4.0         |

| 11           | 8            | Fujitsu                | 134             | 163             | 22         | 4.0         |

| 12           | 12           | Matsushita             | 81              | 117             | 44         | 2.3         |

| 13           | 13           | SGS-Thomson            | 80              | 113             | 41         | 2.3         |

| 14           | 14           | Austria Mikro Systeme  | 67              | 86              | 28         | 2.3         |

| 15           | 18           | Hitachi                | 39              | 86              | 121        | 2.3         |

| 16           | 15           | GEC Plessey            | 63              | 67              | 6          | 1.0         |

| 17           | 21           | OKI                    | 35              | 62              | 77         | 1.          |

| 18           | 17           | National Semiconductor | 58              | 58              | 0          | 1.4         |

| 19           | 16           | Harris                 | 62              | 47              | -24        | 1.          |

| 20           | 19           | AMI                    | 39              | 45              | 15         | 1.          |

# Table 41994 Worldwide Market Share Ranking: MOS/BiCMOS Cell-Based IC(Millions of Dollars)

Source: Dataquest (March 1995)

#### Figure 8 1994 Top 10 Worldwide MOS/BiCMOS CBIC Suppliers

Source: Dataquest (March 1995)

#### **Figure 9** 1994 Top 10 Worldwide MOS/BiCMOS CBIC Suppliers, by Type of Sale

Source: Dataquest (March 1995)

#### Figure 10 1994 Top 10 North American MOS/BiCMOS CBIC Suppliers

Source: Dataquest (March 1995)

- AT&T had a good year in the merchant market and is tied with TI in 1994 merchant CBIC sales, as shown in Figure 9.

- Companies on the move in the CBIC market with high 1994 growth rates include: VLSI Technology, NCR (now called Symbios), NEC, and Toshiba.

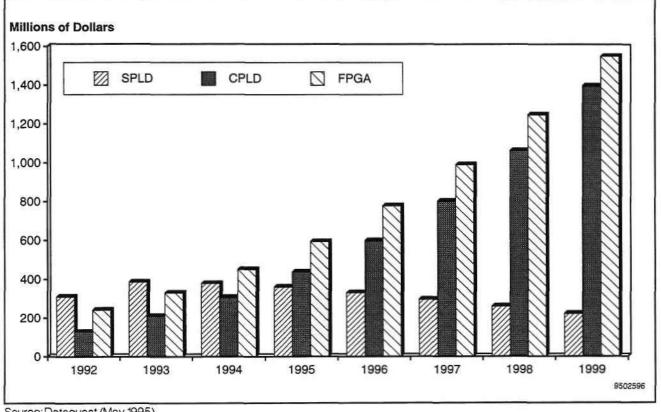

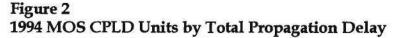

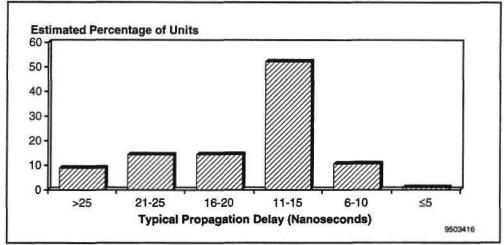

#### PLDs

MOS/BiCMOS PLD growth continued at a solid pace in 1994 (22.6 percent), while bipolar PLDs had the worst year in history (down 29.4 percent). Of the MOS/BiCMOS products, CPLDs lead the pack with an annual growth rate of 45.7 percent, followed by FPGAs with 36.8 percent and SPLDs with a decline of 2.1 percent. Growth rates can be deceiving because of the differences in the dollar bases. FPGAs continued to dominate the market by growing about \$121 million in 1994 for a total market of \$450 million, compared to a \$96 million dollar increase for CPLDs for a total market of \$306 million in 1994. SPLDs declined about \$8 million in 1994 for a total market of \$378 million. MOS/BiCMOS PLD growth came at the expense of bipolar PLDs, which dropped \$73 million for a total 1994 market of \$175 million.

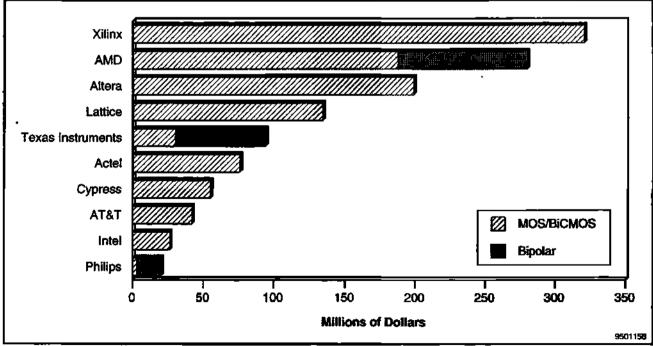

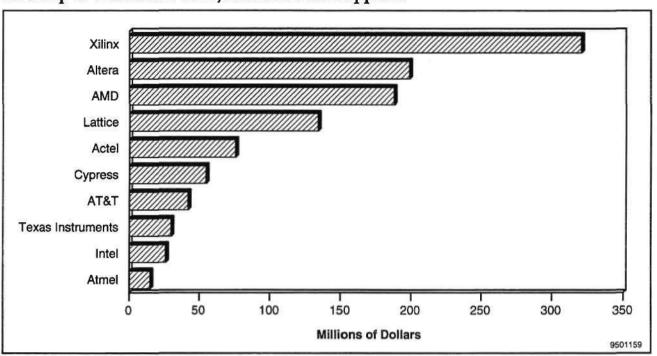

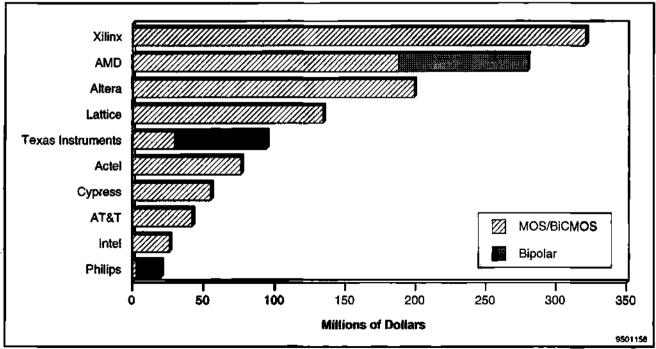

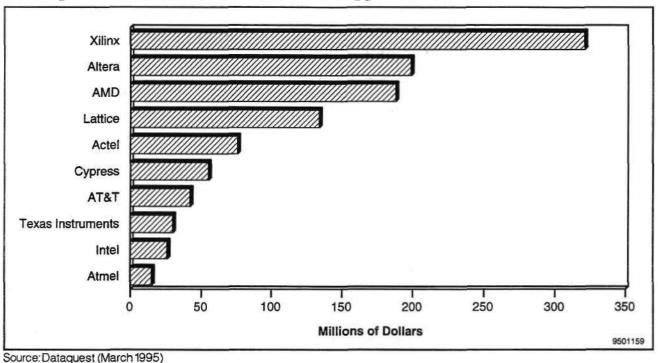

Figure 11 shows the top 10 1994 worldwide PLD suppliers' revenue by technology, while Figure 12 and Table 5 show the leaders in the hotly contested MOS/BiCMOS PLD market.

#### Figure 11 1994 Top 10 Worldwide PLD Suppliers

Source: Dataquest (March 1995)

#### Figure 12 1994 Top 10 Worldwide MOS/BiCMOS PLD Suppliers

Source: Dataquest (March 1995)

# Table 5 1994 Worldwide Market Share Ranking: MOS/BiCMOS PLD (Millions of Dollars)

| 1994<br>Rank | 1993<br>Rank |                              | 1993<br>Revenue | 1994<br>Revenue | Percentage<br>Change (%) | 1994 Market<br>Share (%) |

|--------------|--------------|------------------------------|-----------------|-----------------|--------------------------|--------------------------|

| 1            | 1            | Xilinx                       | 231             | 321             | 39                       | 28.3                     |

| 2            | 3            | Altera                       | 140             | 199             | 42                       | 17.5                     |

| 3            | 2            | Advanced Micro Devices       | 160             | 188             | 18                       | 16.6                     |

| 4            | 4            | Lattice                      | 127             | 134             | 6                        | 11.8                     |

| 5            | 5            | Actel                        | 60              | 76              | 27                       | 6.7                      |

| 6            | 6            | <b>Cypress Semiconductor</b> | 47              | 55              | 17                       | 4.9                      |

| 7            | 8            | AT&T                         | 32              | 42              | 31                       | 3.7                      |

| 8            | 9            | <b>Texas Instruments</b>     | 29              | 30              | 3                        | 2.6                      |

| 9            | 7            | Intel                        | 45              | 26              | -42                      | 2.3                      |

| 10           | 11           | Atmel                        | 12              | 15              | 25                       | 1.3                      |

Source: Dataquest (March 1995)

Noteworthy points regarding the 1994 PLD rankings include the following:

- Xilinx passed AMD for the No. 1 supplier in total PLDs with an exclusive MOS PLD product line.

- Altera passed AMD to capture the No. 2 position in MOS PLDs by growing 42 percent, compared to AMD's 18 percent.

- To accurately reflect the sale of Intel's PLD Division to Altera, the first three quarters of Intel's 1994 PLD revenue is included under Intel, and the last quarter's revenue is included in Altera's revenue.

- Actel outpaced the MOS PLD market in 1994 with 27 percent growth and is well-positioned with the recent acquisition of TI's FPGA business for a battle with Lattice for the No. 4 position.

- Although Lattice's MOS PLD sales only grew 6 percent in 1994, the company doubled its CPLDs sales, which helps position it for stronger growth in 1995.

#### **Dataquest Perspective**

The ASIC wave continues to grow in size and power as the 1994 market exceeded \$10 billion with nearly 20 percent growth. LSI Logic, the largest merchant ASIC supplier, posted record sales and profits during 1994. LSI Logic's net income after tax (profits) increased from 7.5 percent of its 1993 sales to 12.1 percent of 1994 sales. The ASIC market is growing and is profitable for those companies that have invested in three key areas: intellectual property, value-added cell libraries, and system knowledge.

The low-density market (fewer than 20,000 gates) is now being ruled by a half dozen FPGA and CPLD suppliers that have a major patent position in device architectures. These companies enjoy rising revenue streams as well as healthy profit margins because of their intellectual property position.

On the other end of the spectrum, the high-density market (more than 100,000 gates), ASIC suppliers that have established value-added cell libraries targeted at specific applications are the most profitable. System knowledge is critical in developing complete, focused cell libraries where system designers can differentiate their systems. The market is quickly moving to system-level integration (SLI) where the entire system or subsystems can be implemented on a single chip. Such high integration requires a solid understanding of system design, design tools, library support, and test methodologies.

Cell-based ICs are gaining momentum as the preferred ASIC product for high-density designs and SLI because of their small die size. Embedded gate arrays (megacells such as SRAM diffused into the gate array base wafer) have also become a viable option for the high-end market because of their improved time to market over CBICs. As sub-0.35-micron, four- and five-layer-metal, 2-million-gate ASICs become common, we believe that CBICs will offer only minor advantages over the high utilization and quick time-to-market benefits of embedded gate arrays.

The need for system designers to differentiate their systems to achieve higher profit margins is driving the growth of the ASIC market. Although revenue will continue to grow for most ASIC suppliers, profits will only increase for those suppliers that continue to invest in intellectual property, focused cell libraries, and system knowledge.

#### For More Information...

| Bryan Lewis, Director/Principal Analyst |                      |

|-----------------------------------------|----------------------|

| Internet address                        | blewis@dataquest.com |

| Via fax                                 | (408) 437-0292       |

The content of this report represents our interpretation and analysis of information generally available to the public or released by responsible individuals in the subject companies, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients. Reproduction or disclosure in whole or in part to other parties shall be made upon the written and express consent of Dataquest. ©1995 Dataquest Incorporated – Reproduction Prohibited

Dataquest is a registered trademark of A.C. Nielsen Company

Perspective

## ASICs Worldwide Dataquest Predicts

## **Cell-Based ICs to Dominate Gate Arrays in 1998**

**Abstract**: Dataquest predicts that cell-based ICs will be the largest ASIC market by 1998. Dataquest also predicts that embedded arrays will account for half the gate array consumption by the year 2000. In this newsletter, Dataquest forecasts all ASIC products by technology through 1999. For more details on ASIC forecasts and assumptions, please see the ASIC Market Statistics report entitled "Worldwide ASIC Forecast," dated May 22, 1995 (ASIC-WW-MS-9502). By Bryan Lewis

#### **Cell-Based ICs Strike It Rich**

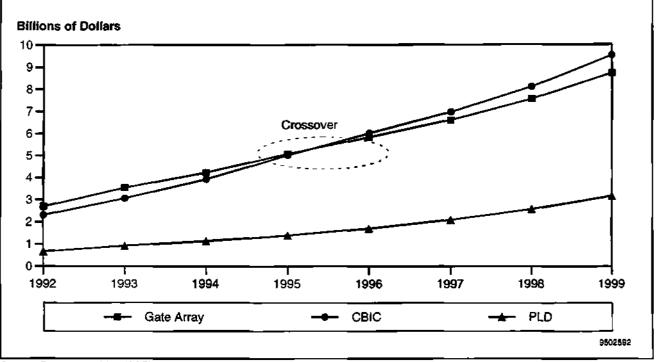

According to Dataquest's new ASIC forecast, total cell-based IC (CBIC) revenue is expected to surpass total gate array revenue in 1998. Furthermore, MOS CBIC revenue should exceed MOS gate array revenue in 1996.

To some, the crossover between CBIC revenue and gate array revenue may come as a great surprise. CBICs are winning in high-volume applications where cost is critical and in high-density applications where increased functionality is important. In North America and Europe, CBIC revenue has been larger than gate array revenue for some time. Japan, once the die-hard gate array nation, is now moving to CBICs to reduce cost and improve functionality. Japan's move toward CBIC technology is causing the shift in worldwide ASIC consumption from gate array to CBIC.

One important point that should be considered, when examining the ASIC product trends, is that embedded arrays (megacells such as SRAM blocks defused in the gate array base wafer) historically have been counted under the gate array category. In this newsletter, we have estimated the portion of the MOS gate array market we believe will be embedded array versus traditional gate arrays. Some ASIC suppliers have been counting embedded

#### Dataquest

Program: ASICs Worldwide Product Code: ASIC-WW-PD-9501 Publication Date: May 29, 1995 Filing: Perspective arrays under the CBIC category in their reporting to Dataquest, and we have attempted to pull this revenue out of CBICs and report it under the gate array category. It is possible that some embedded array revenue slipped into the CBIC category during market collection. To avoid this confusion, Dataquest will start breaking out embedded arrays as a separate category versus traditional arrays and CBICs in 1995 market share collection. Embedded arrays are a very competitive product to CBICs in high-volume and high-density applications.

#### ASIC Consumption by Product

The worldwide 1995 ASIC market is expected to experience the highest growth rate in recent history (20.7 percent, excluding full-custom ICs). Although yen appreciation against the dollar will increase 1995 dollar growth rates (we factored in 10 percent yen appreciation at the time of the forecast), we believe the ASIC market will post outstanding growth rates because of a fundamental change in the products being shipped. Leading ASIC suppliers are shifting their focus from low-value commodity gate arrays to higher-margin, value-added CBICs. CBICs had the highest growth rate of all ASIC products in 1994 (28 percent), and we believe this trend will hold true for 1995 in all regions.

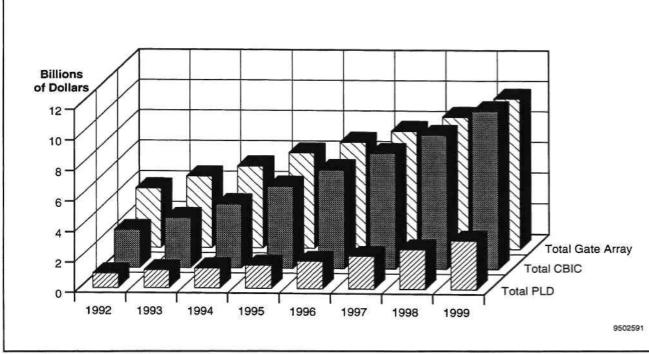

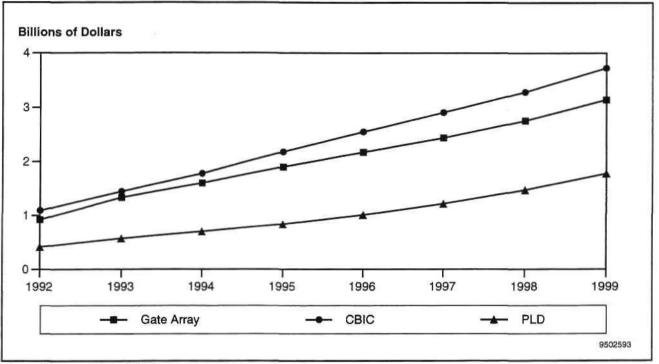

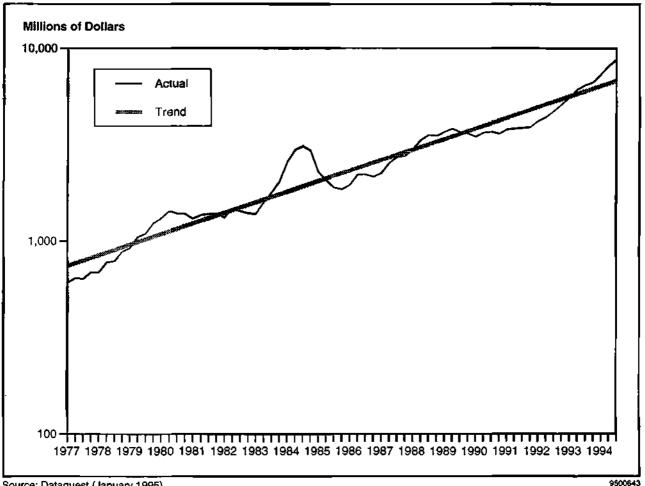

Figure 1 shows ASIC consumption from 1992 through 1999 for total gate array, total CBIC, and total PLD. Table 1 shows a detailed product forecast for all the ASIC products by technology. Figure 2 illustrates the 1995 to 1996 crossover between MOS gate array and MOS CBIC on a worldwide basis, while Figure 3 illustrates the point that MOS CBIC revenue has been larger than MOS gate array revenue in North America for more than three years.

#### Figure 1 Estimated Worldwide ASIC Consumption by Product

Source: Dataquest (May 1995)

Total PLD

MOS PLD

**Bipolar PLD**

Total Cell-Based IC

Total Full-Custom IC

MOS Cell-Based IC

Bipolar Cell-Based IC

MOS Full-Custom IC

**Bipolar Full-Custom IC**

BICMOS Cell-Based IC

|                          |                 |        |              |        |        |        |              |        | CAGR (%)           |

|--------------------------|-----------------|--------|--------------|--------|--------|--------|--------------|--------|--------------------|

|                          | 1992            | 1993   | 1 <b>994</b> | 1995   | 1996   | 1997   | 1 <b>998</b> | 1999   | 1 <b>994-199</b> 9 |

| Total ASIC               | 9,648           | 11,657 | 13,309       | 15,430 | 17,397 | 19,419 | 21,866       | 25,088 | 13.5               |

| MOS ASIC                 | 7,632           | 9,739  | 11,448       | 13,540 | 15,500 | 17,475 | 19,883       | 22,960 | 14.9               |

| Bipolar ASIC             | 1,746           | 1,543  | 1,388        | 1,267  | 1,078  | 906    | 747          | 613    | -15.1              |

| BICMOS ASIC              | 270             | 375    | 473          | 623    | 819    | 1,038  | 1,236        | 1,515  | 26.2               |

| Total Gate Array         | 3 <b>,8</b> 61  | 4,658  | 5,338        | 6,214  | 6,929  | 7,668  | 8,604        | 9,820  | 13.0               |

| MOS Gate Array           | 2,701           | 3,544  | 4,232        | 5,087  | 5,844  | 6,612  | 7,555        | 8,733  | 15.6               |

| Bipolar Gate Array       | <del>9</del> 69 | 873    | 818          | 768    | 642    | 524    | 412          | 317    | -17.3              |

| <b>BICMOS Gate Array</b> | 191             | 241    | 288          | 359    | 443    | 532    | 637          | 770    | 21.7               |

1,309

1,134

4,193

3,931

77

185

2,469

2,151

318

175

1,515

1,388

5,359

5,022

73

264

2,342

2,043

299

127

1,795

1,705

6,466

6,022

68

376

2,207

1,929

278

90

2,150

2,087

7,545

6,978

61

506

2,056

1,798

258

63

2,614

2,569

8,757

8,105

45

53

599

1,891

1,654

237

3,202

3,170

10,327

9,535

47

745

1,739

1,522

217

32

Note: Columns may not add to totals shown because of rounding. Source: Dataquest (May 1995)

#### Figure 2 Estimated Worldwide MOS ASIC Consumption by Product

957

677

280

2,486

2,313

2,344

1,941

403

94

79

1,173

925

248

3,283

3,067

82

134

2,543

2,203

340

Source: Dataquest (May 1995)

19.6

22.8

-28.8

19.8

19.4

-9.4

32.1

-6.8

-6.7

-7.3

#### Figure 3 Estimated North American MOS ASIC Consumption by Product

Source: Dataquest (May 1995)

#### Gate Array

Although CBIC growth rates are higher than those of gate array, we still expect strong gate array growth in 1995. The worldwide MOS gate array market is expected to grow 20.2 percent in 1995, compared with the 19.4 percent experienced in 1994. Part of the increase is because of the strong yen appreciation against the dollar. MOS gate array revenue growth by region in 1995 is forecast as follows: almost 19 percent increase for North America, 24 percent increase for Japan, 7 percent increase for Europe, and 27 percent increase for Rest of World (ROW). Europe is expected to experience a very high growth rate in CBICs at the expense of gate arrays.

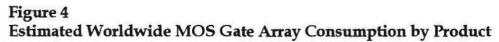

As mentioned, embedded arrays are counted under the gate array category. Our belief is that embedded arrays will experience rapid growth over the next five years (see Figure 4). Embedded arrays offer the reduced turnaround times of gate arrays, along with the increased functionality of CBICs. Traditional sea-of-gates gate array growth will flatten out over the next three years, then decline because they are being squeezed by PLDs on the low end (fewer than 20,000 gates) and embedded arrays and CBICs on the high end (more than 100,000 gates). Furthermore, Dataquest predicts that about half the gate arrays consumed in the year 2000 will be embedded arrays.

Cell-Based ICs

Worldwide 1995 MOS CBIC growth is expected to be the highest of all the ASIC products (27.7 percent). MOS CBIC revenue growth by region in 1995 is forecast as follows: 22.5 percent increase for North America, 34 percent increase for Japan, 32.9 percent increase for Europe, and 26 percent increase for ROW. The shift in focus from gate array to CBIC in Japan is increasing the worldwide MOS CBIC growth rate and causing the 1996 crossover in revenue from gate array to CBIC.

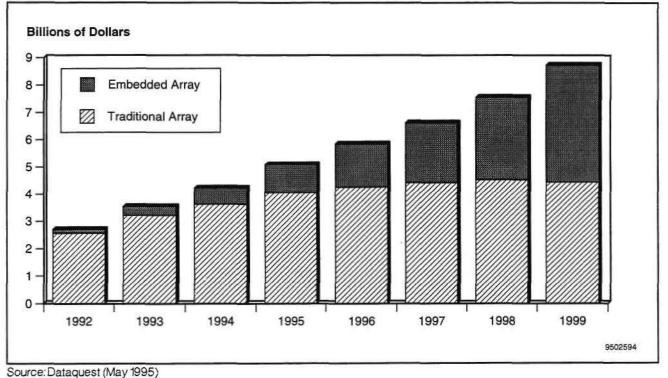

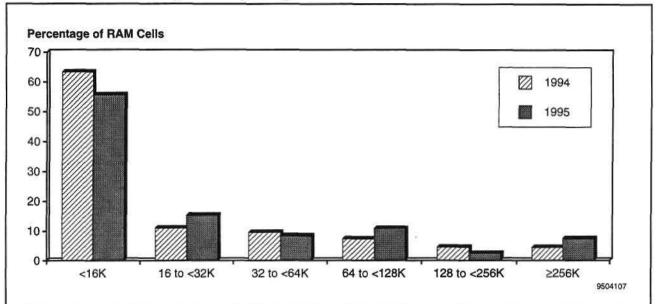

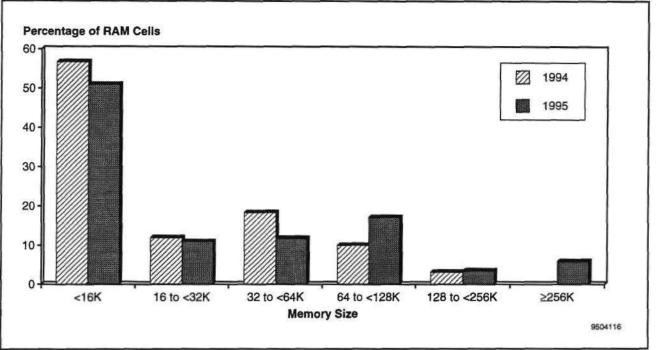

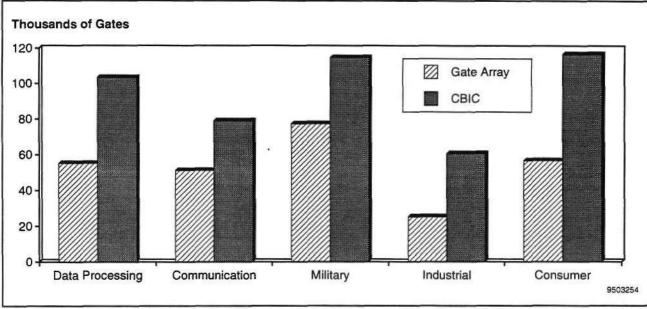

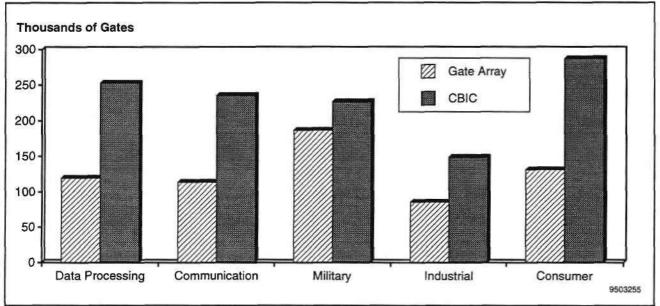

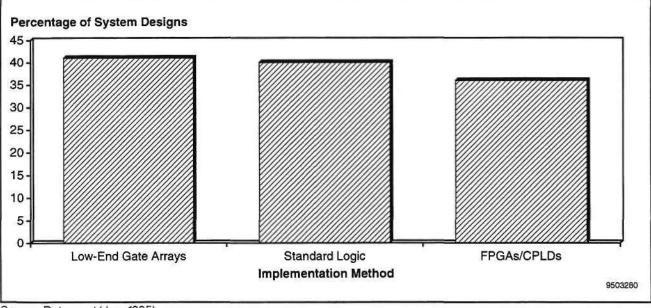

Strong CBIC growth is a result of CBICs winning the battle with gate arrays in high-volume and high-density applications. According to preliminary results from our 1995 User Wants and Needs survey of more than 650 system designers in North America, Japan, and Europe, CBICs have a higher percentage of designs with greater than 100,000 usable gates. Figure 5 shows preliminary 1995 North American ASIC design starts by gate count by product. CBICs clearly are winning the battle above 100,000 usable gates.

Source: Dataquest preliminary 1995 User Wants and Needs survey (May 1995)

#### PLDs

Worldwide MOS PLD growth in 1995 is expected to be very similar to that of 1994 (22.4 percent in 1995 versus 22.6 percent in 1994). On a regional basis, we are expecting about 20 percent growth in North America, 32.5 percent in Japan, 21.5 percent in Europe, and 32.2 percent in ROW. The MOS PLD dollar base in North America and Europe is quite large in comparison to Japan and ROW, and therefore it is much more difficult for these regions to experience growth rates in the 30 percent range.

Key products contributing to the growth of the PLD market are fieldprogrammable gate arrays (FPGAs) and complex PLDs (CPLDs). We expect 31.8 percent growth in 1995 for FPGAs and 42.4 percent growth for CPLDs. Contrasting with these two rapidly growing segments is a 5.1 percent decline in simple PLDs (SPLDs), which are being swept into high-density programmable logic. FPGA and CPLD growth stems from the replacement of standard logic, SPLDs, and low-end gate arrays (fewer than 20,000 gates). Figure 6 illustrates the size of the worldwide MOS PLD market by logic complexity.

#### Figure 6 Estimated Worldwide MOS PLD Consumption by Logic Complexity

Source: Dataquest (May 1995)

#### **Dataguest Perspective**

The year 1995 will be outstanding for the ASIC market. Many ASIC suppliers posted record sales, bookings, and profits during the first quarter of 1995. We believe that 1995 ASIC growth rates will be the highest in recent history. High ASIC growth rates are being fueled by booming electronic equipment markets coupled with the need for systems integration and system differentiation.

Dataquest predicts that traditional gate arrays will start to decline in revenue within three years as they wrestle with PLDs for the low-density/ low-volume business and with CBICs for the cost-sensitive business such as video games, printers, and disk drives. Furthermore, we predict that embedded array will account for half the gate array revenue by the year 2000. Embedded arrays and CBICs will battle for the largest pot of gold, namely the high-volume and high-density market. Each market can be profitable for suppliers with the appropriate intellectual property and system knowledge.

٠

#### For More Information...

| Bryan Lewis, Director/Principal Analyst |                      |

|-----------------------------------------|----------------------|

| Internet address                        | blewis@dataquest.com |

| Via fax                                 | <b>A</b>             |

The content of this report represents our interpretation and analysis of information generally available to the public or released by responsible individuals in the subject companies, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients. Reproduction or disclosure in whole or in part to other parties shall be made upon the written and express consent of Dataquest. ©1995 Dataquest Incorporated -- Reproduction Prohibited

©1995 Date The Dun & Bradstreet Corporation Dataquest

Dataquest

Dataquest is a registered trademark of A.C. Nielsen Company

## Dataquest

## Dataquest

## **Worldwide ASIC Forecast**

Program: ASICs Worldwide Product Code: ASIC-WW-MS-9503 Publication Date: October 23, 1995 Filing: Market Analysis

## **Worldwide ASIC Forecast**

Program: ASICs Worldwide Product Code: ASIC-WW-MS-9503 Publication Date: October 23, 1995 Filing: Market Analysis

#### Table of Contents \_\_\_\_\_

| w., a.,                              | Page |

|--------------------------------------|------|

| Introduction                         | 1    |

| Segmentation                         | 1    |

| Definitions                          | 1    |

| Product Definitions                  | 1    |

| Revenue Classification               | 3    |

| Merchant versus Captive Consumption  | 3    |

| Regional Definitions                 | 3    |

| Forecast Methodology and Assumptions | 3    |

| ASIC Forecast Methodology            | 4    |

| ASIC Forecast Assumptions            | 4    |

| ASIC                                 | 4    |

| Gate Arrays                          | 4    |

| Cell-Based ICs                       | 5    |

| PLDs                                 | 6    |

| Exchange Rates                       | 7    |

••

i

## List of Figures \_\_\_\_\_

\_\_\_\_\_

| Figure |                  | Page |

|--------|------------------|------|

| 1      | ASIC Family Tree | 2    |

ŧ

#### List of Tables \_\_\_\_\_

| Table |                                                                                                                | Page |

|-------|----------------------------------------------------------------------------------------------------------------|------|

| 1     | Exchange Rates                                                                                                 | 7    |

| 2     | Estimated Worldwide ASIC Consumption by Product<br>(Millions of Dollars)                                       | 8    |

| 3     | Estimated Worldwide ASIC Consumption by Product<br>(Percentage Growth)                                         | 9    |

| 4     | Estimated Worldwide ASIC Consumption by Technology<br>(Millions of Dollars and Percentage of Revenue)          | 10   |

| 5     | Estimated Worldwide ASIC Consumption by Region (Millions of Dollars)                                           | 11   |

| 6     | Estimated Worldwide ASIC Consumption by Region<br>(Percentage Growth)                                          | 12   |

| 7     | Estimated Worldwide ASIC Consumption by Region<br>(Percentage of Revenue                                       | 13   |

| 8     | Estimated Worldwide Gate Array Consumption by Technology<br>(Millions of Dollars and Percentage of Revenue)    | 14   |

| 9     | Estimated Worldwide Gate Array Consumption by Region<br>(Millions of Dollars)                                  | 15   |

| 10    | Estimated Worldwide Gate Array Consumption by Region<br>(Percentage Growth)                                    | 16   |

| 11    | Estimated Worldwide Gate Array Consumption by Region<br>(Percentage of Revenue)                                | 17   |

| 12    | Estimated Worldwide Cell-Based IC Consumption by<br>Technology (Millions of Dollars and Percentage of Revenue) | 18   |

| 13    | Estimated Worldwide Cell-Based IC Consumption by Region<br>(Millions of Dollars)                               | 19   |

| 14    | Estimated Worldwide Cell-Based IC Consumption by Region<br>(Percentage Growth)                                 | 20   |

| 15    | Estimated Worldwide Cell-Based IC Consumption by Region<br>(Percentage of Revenue)                             | 21   |

| 16    | Estimated Worldwide PLD Consumption by Technology<br>(Millions of Dollars and Percentage of Revenue)           | 22   |

| 17    | Estimated Worldwide PLD Consumption by Region (Millions of Dollars)                                            | 23   |

| 18    | Estimated Worldwide PLD Consumption by Region<br>(Percentage Growth)                                           | 24   |

| 19    | Estimated Worldwide PLD Consumption by Region<br>(Percentage of Revenue)                                       | . 25 |

| 20    | Estimated Worldwide PLD Consumption by Logic Complexity<br>(Millions of Dollars)                               | . 26 |

| 21    | Estimated Worldwide PLD Consumption by Logic Complexity<br>(Percentage Growth)                                 | . 27 |

Note: All tables show estimated data.

.

•

#### Worldwide ASIC Forecast

#### Introduction

This document contains detailed information on Dataquest's view of the application-specific integrated circuit (ASIC) market. Included in this document are the following:

- 1995-1999 ASIC consumption forecast

- 1995-1999 gate array consumption forecast

- 1995-1999 cell-based IC (CBIC) consumption forecast

- 1995-1999 programmable logic device (PLD) consumption forecast

More detailed data on this market may be requested through Dataquest's client inquiry service. Qualitative analysis of this data is provided in the Dataquest Market Trends and other documents located in the binder of the same name.

#### Segmentation

This section outlines the market segments that are specific to this document. Dataquest's objective is to provide data along lines of segmentation that are logical, appropriate to the industry in question, and immediately useful to clients.

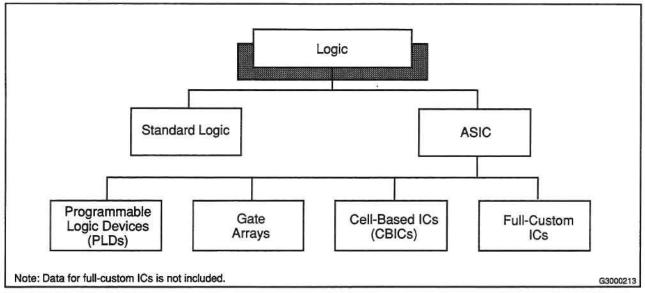

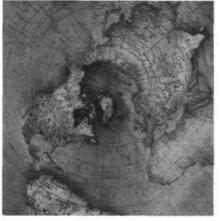

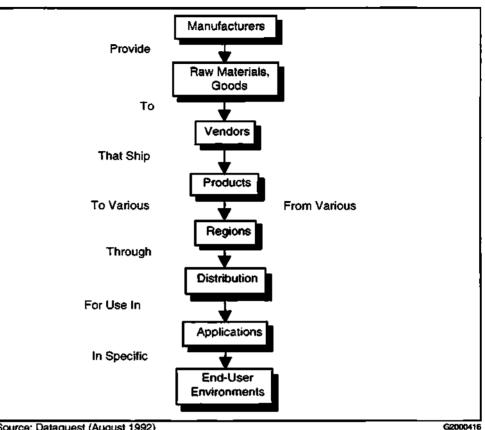

Dataquest defines the ASIC market according to the segmentation scheme in Figure 1.

Figure 1 shows Dataquest's segmentation into the two main categories of standard logic and ASIC. The ASIC family tree breaks out ASICs as follows: PLDs, gate arrays, CBICs, and full-custom ICs. CBICs and full-custom ICs are personalized by altering the full set of masks, whereas PLDs and gate arrays are personalized by electrically programming the devices or by altering only the final layers of interconnect. ASICs are further classified according to process technology: MOS, bipolar, and BiCMOS.

#### Definitions

This section lists the definitions used by Dataquest to present the data in this document.

#### **Product Definitions**

#### Application-Specific Integrated Circuits (ASICs)

This term is used to describe all IC products customized for a single user. ASIC products are a combination of digital, mixed-signal, and analog products. Customized ICs purchased by more than one user become standard products and are no longer counted as ASICs.

#### Figure 1 ASIC Family Tree

Source: Dataquest (April 1995)

#### Programmable Logic Devices (PLDs)

PLDs are defined as ICs programmed after assembly. Memory devices such as PROMs and ROMs are not included in this market segment. PLDs are subdivided into three main categories:

- Simple programmable logic devices (SPLDs): SPLDs have fixed or preconnected architectures capable of providing up to two levels of logic without using additional input, output, or I/O cells or pins.

- Complex programmable logic devices (CPLDs): CPLDs are productterm or segmented PAL-based devices that may or may not implement multiple levels of logic without using additional input, output, or I/O cells or pins.

- Field-programmable gate arrays (FPGAs): FPGAs are based on segmented programmable interconnect and typically consist of an X-Y matrix of logic modules typically fed by a limited number of preconnected signals.

#### **Gate Arrays**

Gate arrays are ASICs that contain a configuration of uncommitted elements in a prefabricated base wafer. They are customized by interconnecting these elements with one or more routing layers. Included in this category are traditional gate arrays (channeled and sea-of-gates architecture) and embedded gate arrays (channeled or sea-of-gates architecture that also include megacells such as SRAM diffused into the gate array base wafer).

#### CBICs

CBICs are ASICs that are customized using a full set of masks and use automatic place-and-route tools. Included in this category are traditional standard cells (fixed-height/fixed-width cells) as well as megacells (variable-height/variable-width cells) and compiled cells.

#### Full-custom ICs

Full-custom ICs are defined as ASIC devices that are produced for a single user using a full set of masks. This process involves manual routing and placement of cells.

#### **Revenue Classification**

Because systems may be fabricated, assembled, and sold in several different locations, Dataquest's regional device consumption is defined according to the shipping destination.

Consumption estimates include the following five sources of revenue:

- Intracompany revenue (sales to internal divisions)

- Nonrecurring engineering (NRE) revenue

- ASIC software revenue

- PLD development kit revenue

- Device production revenue

Despite the care taken in gathering, analyzing, and categorizing the data in a meaningful way, careful attention must be paid to the definitions and assumptions used herein when interpreting the estimates presented in this document. Various companies, government agencies, and trade associations may use slightly different definitions of product categories and regional groupings, or they may include different companies in their summaries. These differences should be kept in mind when making comparisons between data and numbers provided by Dataquest and those provided by other suppliers.

#### Merchant versus Captive Consumption

Dataquest includes all revenue, both merchant and captive, for semiconductor suppliers selling to the merchant market. Dataquest's consumption estimates do not include captive-only manufacturing companies represented by companies such as Digital Equipment Corporation, Northern Telecom, or Unisys that do not sell semiconductor products in the merchant market.

#### **Regional Definitions**

North America: Includes Canada, Mexico, and the United States

Europe: Western Europe and eastern Europe

Japan: Japan

Asia/Pacific-Rest of World: All other countries

#### Forecast Methodology and Assumptions

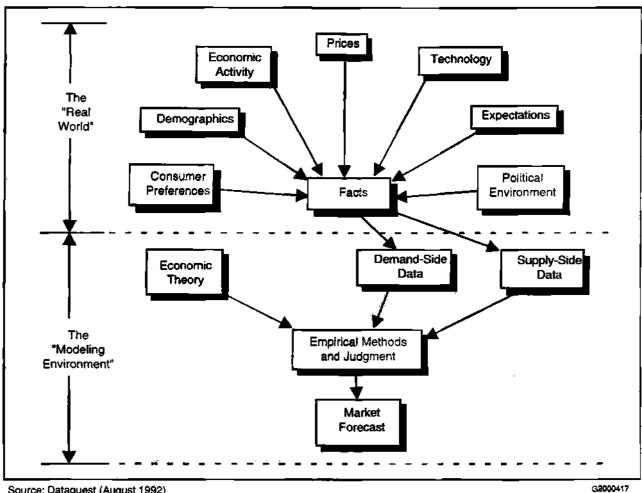

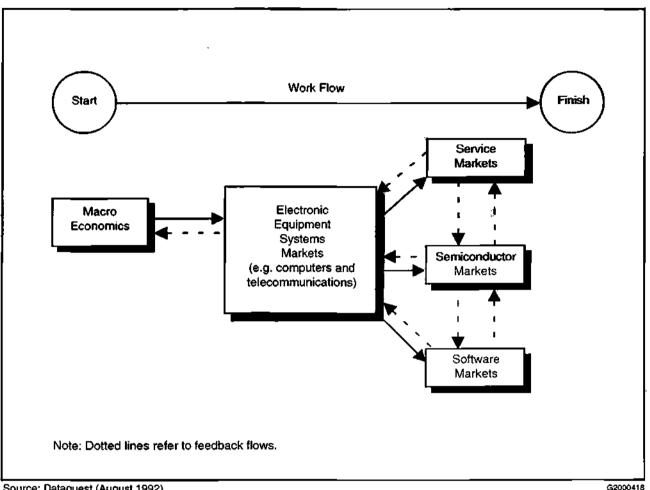

Dataquest publishes five-year factory revenue forecasts for the ASIC market during the first and third quarter of each year. In doing so, Dataquest utilizes a variety of forecasting techniques (both qualitative and quantitative) that vary by technology area. An overview of Dataquest forecasting techniques can be found in the Dataquest Research Methodology guides.

#### **ASIC Forecast Methodology**

Dataquest's forecast methodology includes the following steps:

- Formally and informally survey the leading ASIC vendors (in gate arrays, CBICs, and PLDs) throughout the year for their expectations, as well as for their views of the application markets in which they participate

- Formally survey ASIC users for their expected buying patterns, in addition to their views on the growth of the application markets in which they participate

- Examine statistics provided by a number of industry and government organizations (such as the World Semiconductor Trade Statistics, the Japanese Ministry of International Trade and Industry, and the U.S. Department of Commerce) for up-to-date monthly trends

- Perform time-series analysis as well as apply judgmental industry knowledge to product and application trends

#### **ASIC Forecast Assumptions**

#### ASIC

The worldwide 1995 ASIC market is expected to experience the highest growth rate in recent history (23.7 percent, excluding full-custom ICs). Although yen appreciation against the dollar will increase the 1995 dollar growth rate of the ASIC market (we factored in about 10 percent yen appreciation at the time of the forecast), we believe the market will post outstanding growth rates because of a fundamental change in the products being shipped. Leading ASIC suppliers are shifting their focus from low-value commodity gate arrays to higher margin, value-added cell-based ICs. Cell-based ICs had the highest growth rate of all ASIC products in 1994 (30.4 percent), and we believe this trend will hold true for 1995 in all regions. Furthermore, Dataquest predicts the size of the worldwide cell-based IC market to surpass that of the gate array market by 1998, and for it to become the largest ASIC market.

#### **Gate Arrays**

#### **MOS Gate Arrays**

CMOS continues to be the dominant gate array technology for the foreseeable future because of its low cost, low power consumption, and high integration.

The North American CMOS gate array market will closely track the computer market because more than 60 percent of all gate arrays are consumed in data processing applications.