# **Multichip Modules**

# Published by Dataquest Incorporated The content of this report represents our interpretation and analysis of information generally available to the public or released by knowledgeable individuals in the subject industry, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients. Printed in the United States of America. All rights reserved. No part of this publication may be reproduced, stored in retrieval systems, or transmitted, in any form or by any means-mechanical, electronic, photocopying, duplicating, microfilming, videotape, or otherwise-without the prior permission of the publisher. © 1992 Dataquest Incorporated June 1992

# **Table of Contents**

| Chapter 1 | Exe | cutive Summary                         |             |

|-----------|-----|----------------------------------------|-------------|

| -         |     | Methodology                            |             |

|           |     | General Assumptions                    |             |

|           |     | Multichip Module Drivers               |             |

| Chapter 2 | Mul | ltichip Module Forecast                | 2-1         |

| -         |     | Introduction                           |             |

|           |     | Package Forecast                       |             |

|           |     | Semiconductor Component Forecasts      |             |

|           |     | ASIC                                   |             |

|           |     | Microprocessors                        |             |

|           |     | Memory                                 |             |

|           |     | Analog                                 |             |

| Chapter 3 | МС  | M Applications                         | 3-1         |

| •         |     | Introduction                           |             |

|           |     | Regional Overview                      |             |

|           |     | Dataprocessing                         |             |

|           |     | Communications                         |             |

|           |     | Military/Aerospace                     |             |

|           |     | Transportaion                          |             |

|           |     | Technology Design Tradeoffs            | 3-15        |

| Chapter 4 | МС  |                                        |             |

| •         | 4.1 | Design Software                        | <b>4-</b> 1 |

|           | 4.2 | Chip Procurement                       |             |

|           | 4.3 | Profile of the Vendor Community        |             |

|           | 4.4 | Consortium Activities                  |             |

|           |     | Worldwide R&D Spending                 |             |

|           |     | United States                          |             |

|           |     | State Funded R&D                       |             |

|           |     | Japan                                  |             |

|           |     | Europe                                 |             |

|           | 4.5 | Standardization                        |             |

|           | 4.6 | Superchip vs MCM                       | 4-20        |

|           |     | Economic Issues                        | 4-21        |

|           |     | Other Advantages of MCM                |             |

|           |     | Cost Timing Scenario                   | 4-22        |

|           |     | Strategic Considerations               | 4-24        |

| Chapter 5 |     | rconnect Trends                        |             |

|           | 5.1 | Driving Forces in Single Chip Packages |             |

|           |     | Memory Packaging                       |             |

|           |     | Logic Packaging                        | 5-5         |

|           | 5.2        | Chip Interconnect Density Trends          | 5-7  |

|-----------|------------|-------------------------------------------|------|

|           |            | Gate Array Pin Count                      |      |

|           |            | Microprocessor Pin Count                  |      |

|           |            | Pin Count Forecast                        |      |

|           |            | Pins Needed and Available                 |      |

|           |            | Pin Density                               |      |

|           | 5.3        |                                           |      |

|           |            | Chip Requirements                         | 5-16 |

| Chapter 6 | Sub        | ostrates for Multichip Modules            |      |

| Chapter   | 6.1        | Introduction                              | 6.1  |

|           | 6.2        | Substrate Pros & Cons                     |      |

|           | 0.2        | Maximum Clock Rate                        |      |

|           |            | Simultaneous Switching Noise              |      |

|           |            | Thermal Fatigue                           |      |

|           |            | Substrate Interconnect Density            |      |

|           |            | Cost                                      |      |

|           |            | Chip Power Requirements                   |      |

|           |            | MCM Power Handling Capacity               |      |

|           | 6.3        | Interconnect Density Capability           |      |

|           | 6.4        | Summary of Finished Substrate Cost Models |      |

|           | 6.5        | Silicon Substrate Cost Model              |      |

|           |            | Facilities Improvements                   |      |

|           |            | Equipment Expenditures                    |      |

|           |            | Labor Requirement                         |      |

|           |            | Impact of Production Volume On Cost       |      |

|           |            | Round vs. Square Substrates               |      |

|           |            | Substrate Yield                           |      |

|           |            | Price and Factory Revenue                 |      |

|           |            | Substrate Selling Prices                  |      |

|           | 6.6        | Power Handling in MCM's                   |      |

|           |            | Power Scaling Theory                      |      |

|           |            | Microprocessor Power Trends               |      |

|           |            | Memory Power Trends                       |      |

|           |            | ECL Power Trends                          |      |

|           |            | Microprocessor Power Trends With Time     |      |

|           |            | Saving Power in CMOS Chips                |      |

|           |            | Three Volt Power Trends                   |      |

|           |            | Example of Thermal Management Systems     |      |

|           |            | Substrate Power Handling                  |      |

|           |            | The System of the Future                  |      |

| Chapter 7 | MCI        | M Test and Assembly                       |      |

| F         |            | •                                         |      |

|           | 7.1<br>7.2 | Component Test                            | 7-2  |

|           | 1.7.       | sum resi                                  | 1=7  |

|            | 7.2.1 Theory of VLSI Test                | 7-3  |

|------------|------------------------------------------|------|

|            | Testing a Complex Logic Function         | 7-3  |

|            | Test Vectors                             | 7-4  |

|            | Stuck Faults                             | 7-5  |

|            | Fault Coverage                           | 7-7  |

|            | Storage Elements Complicate VLSI Test    | 7-7  |

|            | Scan Logic                               |      |

|            | Built In Self Test                       |      |

|            | Test Software                            | 7-9  |

|            | Summary                                  | 7-9  |

|            | 7.2.2 Chip Test Problems                 |      |

|            | Impact of Chip Quality on Module Quality | 7-11 |

|            | The IEEE 1149 Test Standard              | 7-13 |

|            | Requirements for Chip Test               | 7-14 |

|            | 7.2.3 Burn-in Test                       | 7-14 |

|            | 7.2.4 Chip Power Handling                | 7-14 |

|            | 7.2.5 Chip Contact Techniques            |      |

|            | High Frequency Probes                    |      |

|            | TAB                                      |      |

|            | Ceramic Carriers                         | 7-16 |

|            | Socket Approaches                        |      |

|            | 7.2.6 Other Chip Handling Issues         |      |

|            | 7.3 Substrate Test                       | 7-19 |

|            | Bed of Nails                             | 7-20 |

|            | Two Point Probe                          | 7-20 |

|            | Glow Discharge                           | 7-21 |

|            | E-Beam                                   | 7-22 |

|            | Automatic Optical Inspection             | 7-23 |

|            | Summary                                  | 7-23 |

|            | 7.4 Module Test                          | 7-24 |

|            | 7.4.1 Test Requirements                  | 7-25 |

|            | 7.4.2 IEEE 1149                          |      |

|            | 7.5 MCM Intraconnect                     |      |

|            | 7.6 MCM Packaging                        |      |

|            | 7.7 MCM Reliability                      |      |

|            | 7.8 Costs                                |      |

| Appendix A | Vendor Profiles                          | A-1  |

|            |                                          |      |

| Appendix B | Application Market Definitions           |      |

|            | Data Processing                          |      |

|            | Communications                           |      |

|            | Industrial                               |      |

|            | Consumer                                 |      |

|            | Military/Civilian                        | B-2  |

|            | Transportation                           |      |

# List of Tables and Figures

| Table  |                                                                          | Page   |

|--------|--------------------------------------------------------------------------|--------|

| 2.2.1  | Estimated Worldwide Package Production                                   | 2-2    |

| 2.2.2  | North America - Estimated Package Production                             |        |

| 2.2.3  | Japan - Estimated Package Production                                     |        |

| 2.2.4  | Europe - Estimated Package Production                                    |        |

| 2.2.5  | Asia Pacific - Estimated Package Production                              |        |

| 2.3.1  | Estimated Worldwide Standard Logic Package Production                    |        |

| 2.3.2  | North America - Estimated Standard Logic Package Production              |        |

| 2.3.3  | Japan - Estimated Standard Logic Package Production                      |        |

| 2.3.4  | Europe - Estimated Standard Logic Package Production                     |        |

| 2.3.5  | Asia-Pacific - Estimated Standard Logic Package Production               |        |

| 2.4.1  | Estimated Worldwide Gate Array Pin Count Production                      |        |

| 2,4.2  | North America-Estimated Gate Array Package Production                    |        |

| 2.4.3  | Japan-Estimated Gate Array Package Production                            |        |

| 2.4.4  | Europe-Estimated Gate Array Package Production                           |        |

| 2.4.5  | Asia/Pacific-Estimated Gate Array Package Production                     |        |

| 2.5.1  | Estimated Worldwide Microprocessor Package Production                    |        |

| 2.5.2  | North America - Estimated Microprocessor Package Production              |        |

| 2.5.3  | Japan - Estimated Microprocessor Package Production                      |        |

| 2.5.4  | Europe - Estimated Microprocessor Package Production                     |        |

| 2.5.5  | Asia/Pacific - Estimated Microprocessor Package Production               |        |

| 2.6.1  | Estimated Worldwide MOS DRAM Package Production                          |        |

| 2.6.2  | Estimated Regional MOS DRAM Package Production                           |        |

| 2.6.3  | Estimated MOS DRAM Module Organization                                   |        |

| 2.6.4  | MOS DRAM Emerging Package Technologies                                   |        |

| 2.6.5  | Estimated Slow SRAM Packaging Forecast                                   |        |

| 2.6.6  | Estimated Fast SRAM Packaging Forecast                                   |        |

| 2.6.7  | Estimated Worldwide MOS SRAM Package Production                          |        |

| 2.6.8  | Estimated Worldwide MOS EPROM Package Production                         | 2-35   |

| 2.6.9  | Estimated Worldwide MOS ROM Package Production                           | 2-36   |

| 2.6.10 | Estimated Worldwide MOS EEPROM Package Production                        | , 2-37 |

| 2.7.1  | Estimated Regional Analog Market Package Production                      | 2-38   |

| 3.1.1  | Electronic Equipment Production Forecast                                 | 3-2    |

| 3.2.1  | Computers and Data Storage North America Electronics Equipment Using MCM | 3-5    |

| 3.2.2  | Communications North America Electronics Equipment Using MCM             | 3-5    |

| 3.2.3  | Industrial North America Electronics Equipment Using MCM                 | 3-6    |

| 3.2.4  | Consumer North America Electronics Equipment Using MCM                   | 3-6    |

| 3.2.5  | Military/Aerospace North America Electronics Equipment Using MCM         | 3-6    |

| 3.2.6  | Transportation North America Electronics Equipment Using MCM             |        |

| 3.2.7  | North America - Electronics Equipment Using MCM                          | 3-7    |

| 3.2.8  | North America Value of Semiconductors Used in MCMs                       |        |

| 3.2.9  | Estimated MCM Revenue in North America                                   | 3-8    |

| 3.2.10 | Japan Electronics Equipment Production                                   | 3-9    |

| 3.2.11 | Japan Electronics Equipment Using MCM                                    |        |

| 3.2.12 | Japan Semiconductors Used in MCMs                                        |        |

|        |                                                                          |        |

| 3.2.13 | MCM Revenue in Japan                                                      | 3-10 |

|--------|---------------------------------------------------------------------------|------|

| 3.2.14 | Europe Electronics Equipment Production                                   |      |

| 3.2.15 | Europe Electronics Equipment Using MCM                                    |      |

| 3.2.16 | Europe - Semiconductors Used in MCMs                                      |      |

| 3.2,17 | MCM Revenue in Europe                                                     |      |

| 3.2.18 | Asia-Pacific Electronics Equipment Production                             | 3-13 |

| 3.2.19 | Asia/Pacific Electronics Equipment Using MCM                              | 3-13 |

| 3.2.20 | Asia/Pacific Semiconductors Used in MCMs                                  | 3-14 |

| 3.2.21 | MCM Revenue in Asia/Pacific                                               | 3-14 |

| 3.3.1  | MCM Design Technology                                                     | 3-15 |

| 4.2.1  | North America Bare Die Consumption                                        | 4-5  |

| 4.2.2  | Japan Bare Die Consumption                                                |      |

| 4.2.3  | Europe Bare Die Consumption                                               |      |

| 4.2.4  | Asia/Pacific Bare Die Consumption                                         |      |

| 4.3.1  | Bare Die Contractors                                                      | 4-8  |

| 4.4.1  | United States Research Consortia                                          | 4-11 |

| 4.4.2  | University Packaging Interconnect Research                                | 4-12 |

| 4.4.3  | Package Related R&D Program Structures in Japan                           | 4-14 |

| 4.4.4  | European Packaging R&D Projects                                           |      |

| 4.4.5  | European Collaborative Packaging R&D Projects                             |      |

| 4.6.1  | Chip-Level Comparison of Single and Multi Chip Implementations of the     |      |

|        | Same System Function                                                      | 4-20 |

| 4.6.2  | Computed Delays for a 4 Chip System as a Single Chip, MCM, and PCB        | 4-23 |

| 4.6.3  | Assembly-Level Comparison of Single and Multi-Chip Implementations of the |      |

|        | Same System Function                                                      | 4-25 |

| 5.3.1  | Minimum Interconnect Density for Component Limited Substrates             | 5-19 |

| 6.2.1  | Maximum Clock Rates At Which Transmission Line Effects Can Be Ignored     | 6-4  |

| 6.2.2  | Lithography Tool Resolution Requirements for Printed Circuit Boards,      |      |

|        | Cofired Ceramic, and High Density Substrates                              | 6-6  |

| 6.2.3  | Comparison of Substrate Costs for Four Different Alternatives             |      |

| 6.3.1  | Typical Minimum Line Pitches of Printed Circuit Boards, Cofired Ceramic,  |      |

|        | and High Density Substrates                                               | 6-10 |

| 6.3.2  | Typical Minimum Via Pitches of Printed Circuit Boards, Cofired Ceramic.   |      |

|        | and High Density Substrates                                               | 6-11 |

| 6.3.3  | Typical Patterning Tool Capabilities                                      |      |

| 6.4.1  | Comparison of Important MCM Substrate Manufacturing Technologies          | 6-14 |

| 6.5.1  | Facilities Improvements for Substrate Fabrication Facility                |      |

| 6.5.2  | Manufacturing Equipment for Substrate Manufacturing Area                  |      |

| 6.5.3  | Labor Requirement for Substrate Manufacturing Facility                    |      |

|        | Head Function Count                                                       | 6-17 |

| 6.5.4  | Wafer Cost Analysis for Two Different Substrate Manufacturing Facilities  |      |

| 6.5.5  | Gross Available Substrates on Round and Square Material                   |      |

| 6.5.6  | Yield of Membrane/Substrates                                              |      |

| 6.5.7  | Factory Revenue at 10,000 Wafers per Period                               |      |

| 6.5.8   | High-Volume Membrane/Substrate Yielded Selling Prices             | 6-25 |

|---------|-------------------------------------------------------------------|------|

| 6.6.1   | Power Dissemination of Microprocessor Chips                       | 6-26 |

| 6.6.2   | Power Dissipation of Memory Chips                                 | 6-29 |

| 6.6.3   | Some Examples of Thermal Management Systems                       | 6-34 |

| 6.6.4   | Thermal Performance of Various Substrate and Dielectric Materials | 6-35 |

|         |                                                                   |      |

| 7.2.1   | Comparison of Substrate Test Equipment Test Timed                 | 7-22 |

| 7.2.2   | Estimated Test Costs for Substrate Test Equipment                 |      |

| 7.5.1   | Intraconnect Issues                                               |      |

| 7.8.1   | CPU Module Cost Comparison for Three Substrate Types              |      |

| 7.8.2   | CPU Module Cost Comparison for Packaged Units on a PCB            |      |

| 7.8.3   | CPU Module Comparisons                                            |      |

|         | •                                                                 |      |

| Figures |                                                                   | Page |

| 1.4.1   | MCM Application Drivers                                           | 1-2  |

| 1.4.2   | Worldwide MCM Revenue Share by Applications                       |      |

| 1.4.3   | Emerging Package Trends                                           |      |

|         |                                                                   |      |

| 2.2.1   | Worldwide Package Share                                           | 2-3  |

| 2.5.1   | 1991 Worldwide Microcomponent Shipments                           |      |

|         | · ·                                                               |      |

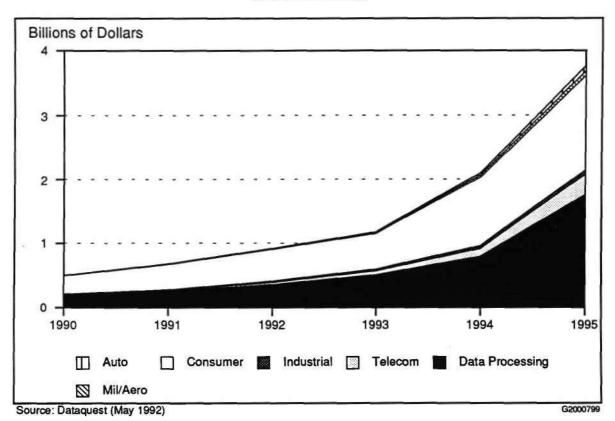

| 3.2.1   | Worldwide MCM Revenue by Application                              | 3-3  |

|         | , , , , , , , , , , , , , , , , , , , ,                           |      |

| 4.2.1   | Worldwide Bare Die Market                                         | 4-4  |

| 4.3.1   | MCM Domain                                                        | 4-7  |

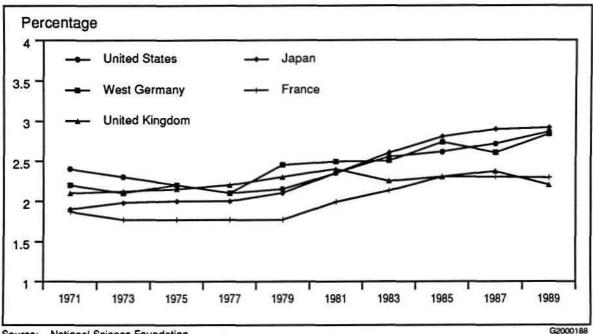

| 4.4.1   | R&D/GNP Ratios by Country 1971-1988                               | 4-9  |

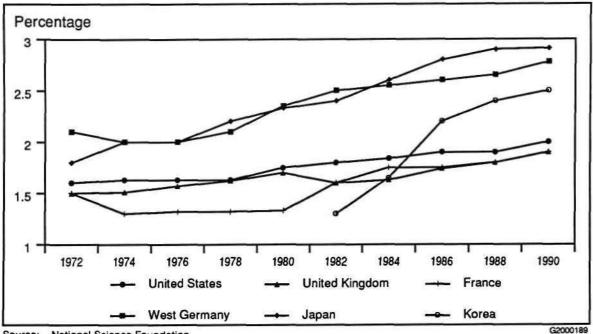

| 4.4.2   | Nondefense R&D/GNP Ratios by Country 1971-1988                    | 4-10 |

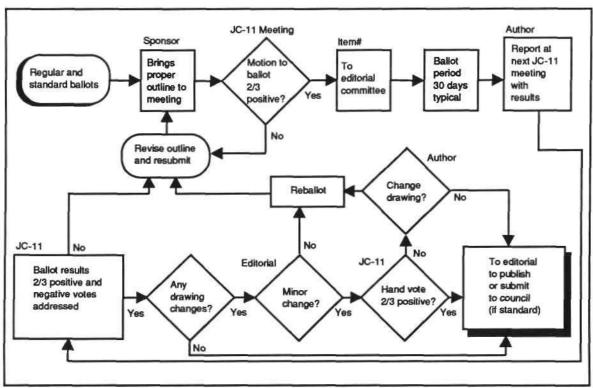

| 4.5.1   | JEDEC JC-11 Registration and Standards Ballot Flowchart           | 4-18 |

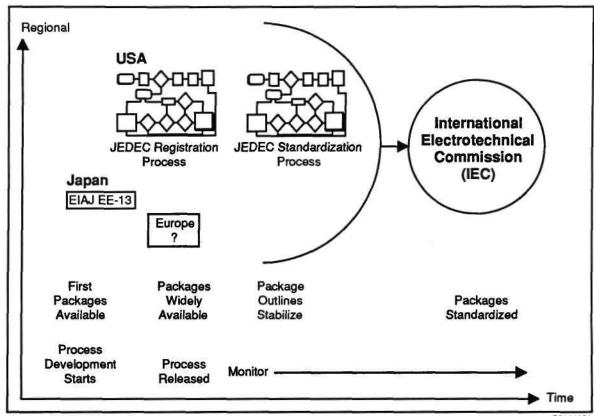

| 4.5.2   | Impact of Package Standardization on System House Assembly        |      |

|         | Process Development                                               | 4-19 |

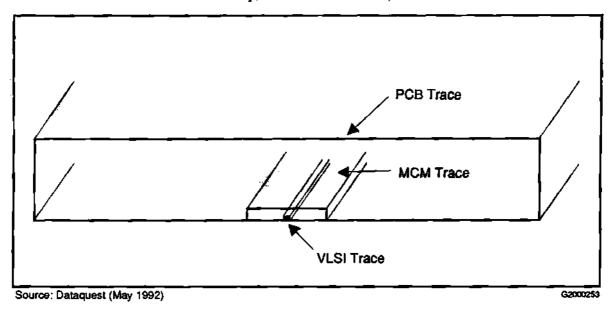

| 4.6.1   | Cross Sectional View of Typical Metal Traces on a VLSI Chip,      |      |

|         | an MCM-D Substrate, and a PCB                                     | 4-22 |

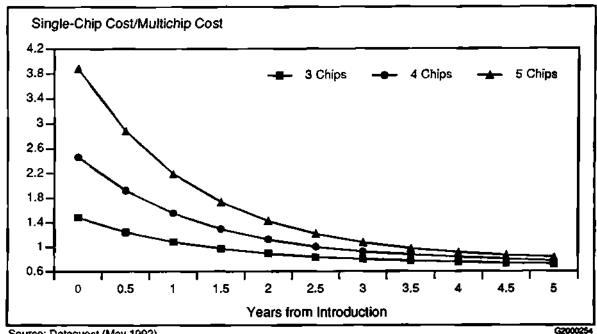

| 4.6.2   | Relative Module Cost                                              | 4-24 |

|         |                                                                   |      |

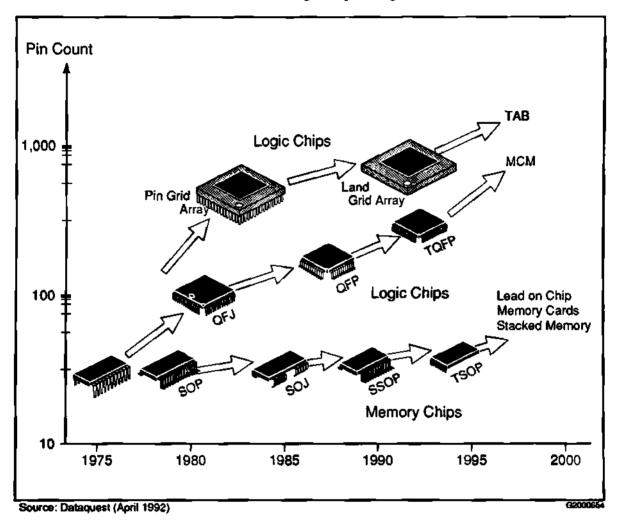

| 5.1.1   | Evolution of Single Chip Packages                                 |      |

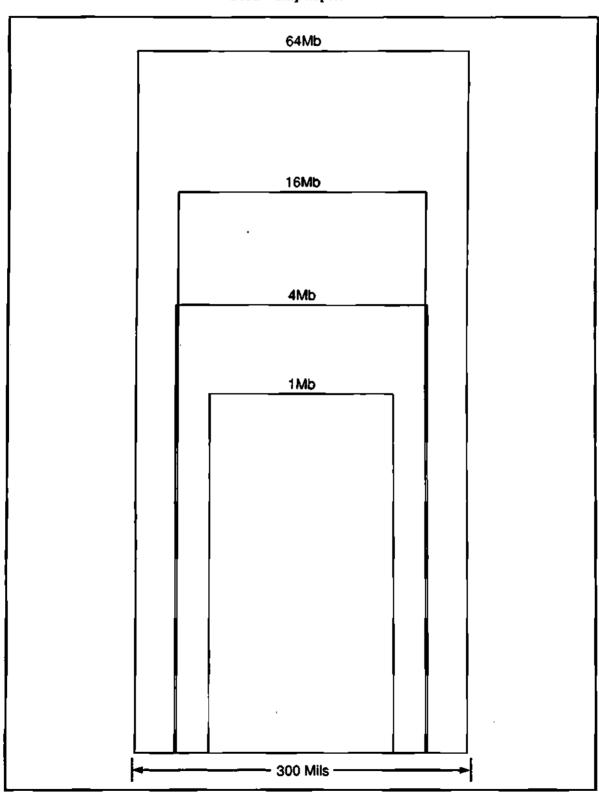

| 5.1.2   | DRAM Chip Aspect Ratios                                           |      |

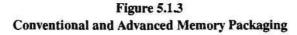

| 5.1.3   | Conventional and Advanced Memory Packaging                        |      |

| 5.1.4   | Pad Limited Gate Array                                            |      |

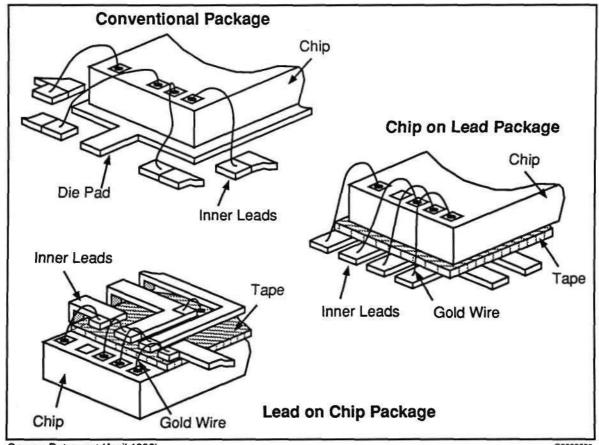

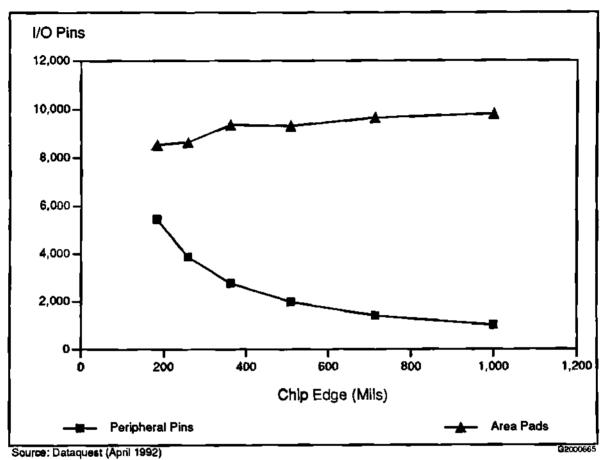

| 5.1.5   | Chip Size Impact on Available I/O                                 |      |

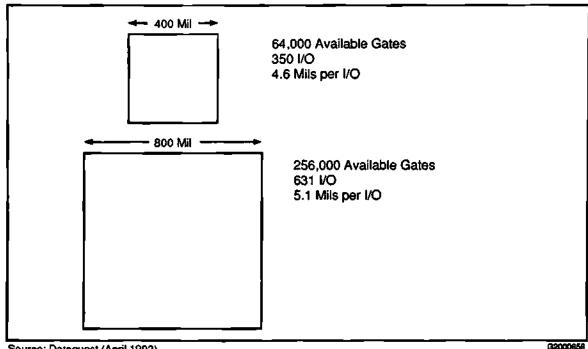

| 5.2.1   | Available Gate Array Pinout                                       |      |

| 5.2.2   | Microprocessor Pin Count                                          |      |

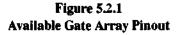

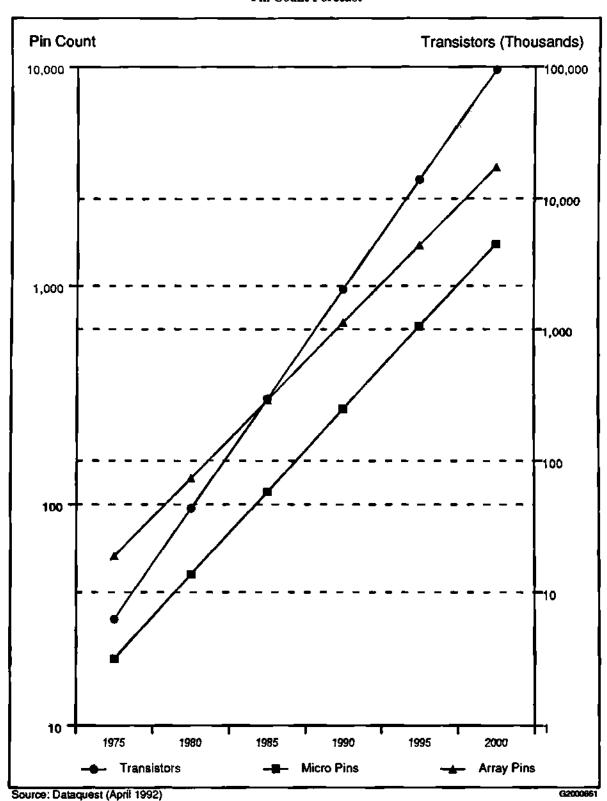

| 5.2.3   | Pin Count Forecast                                                |      |

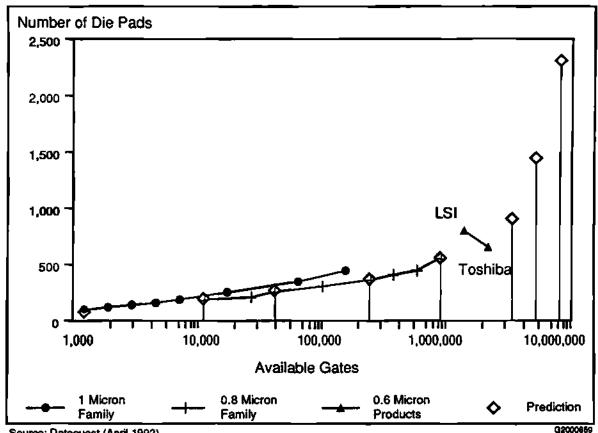

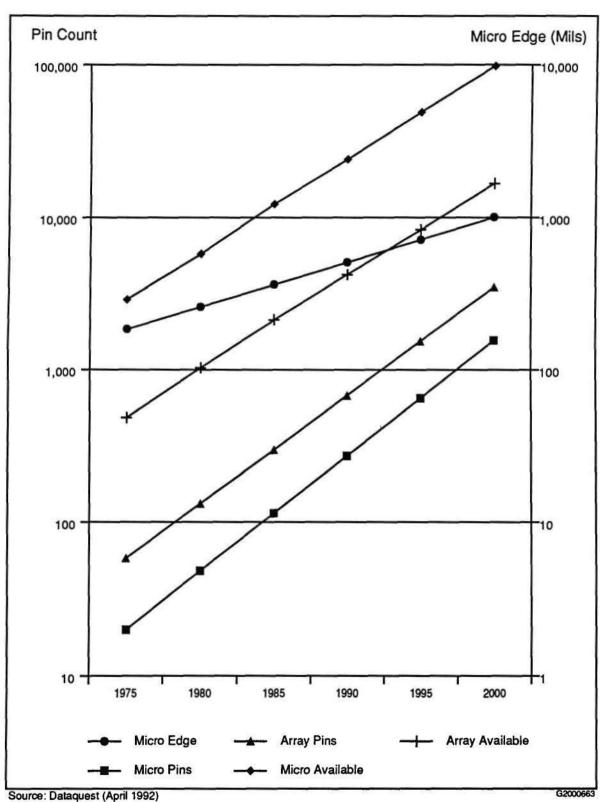

| 5.2.4   | Pins Needed and Available                                         |      |

| 5.2.5   | Pins Needed and Available                                         |      |

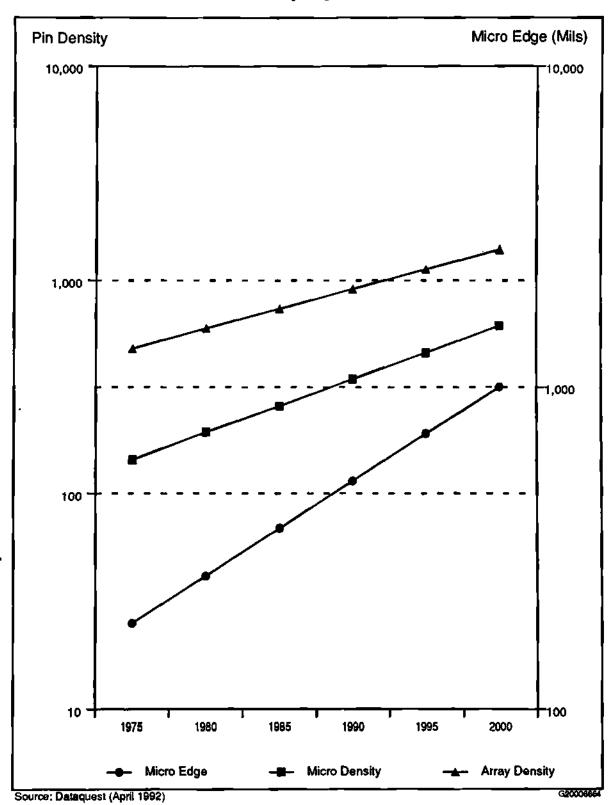

| 5.2.6   | Pin Densities Needed                                              |      |

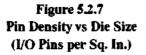

| 5.2.7   | Pin Density vs Die Size                                           |      |

| 5.3.1   | Interconnect "Tangledness"                                        |      |

| 5.3.2   | Wiring and Component Limited Substrates                           | 5-18 |

| vi      |                                                                   |      |

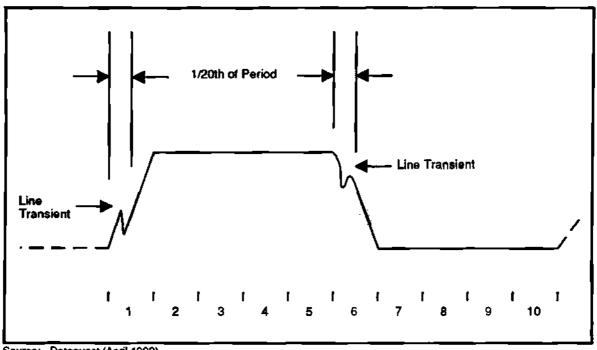

| 6.2.1  | Waveform Illustrating Maximum Clock Rate for Which Transmission   |      |

|--------|-------------------------------------------------------------------|------|

|        | Line Effects Can Be Ignored                                       | 6-2  |

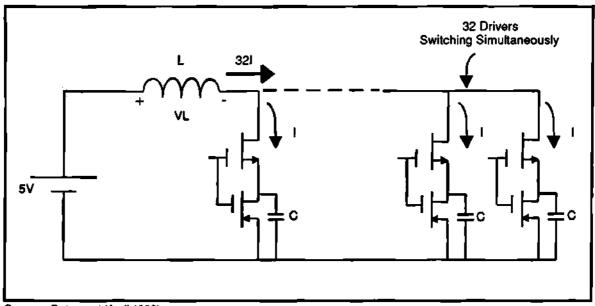

| 6.2.2  | Simultaneous Switching Noise                                      | 6-3  |

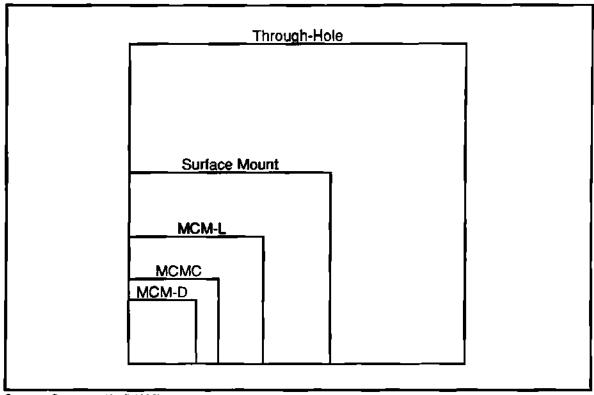

| 6.2.3  | Size Comparison of Five Different Substrate Alternatives          |      |

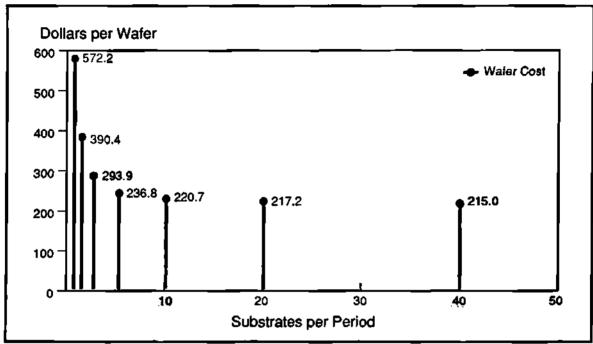

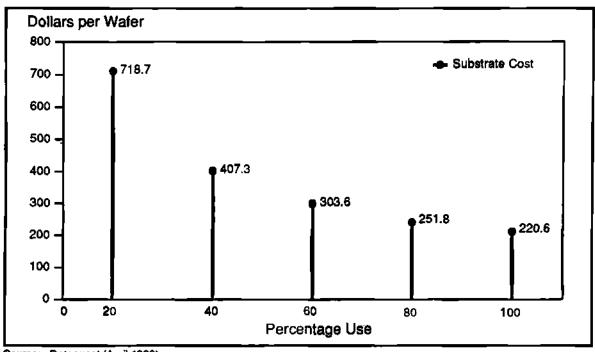

| 6.5.1  | Substrate Cost versus Factory Size                                |      |

| 6.5.2  | Substrate Cost versus Factory Utilization                         |      |

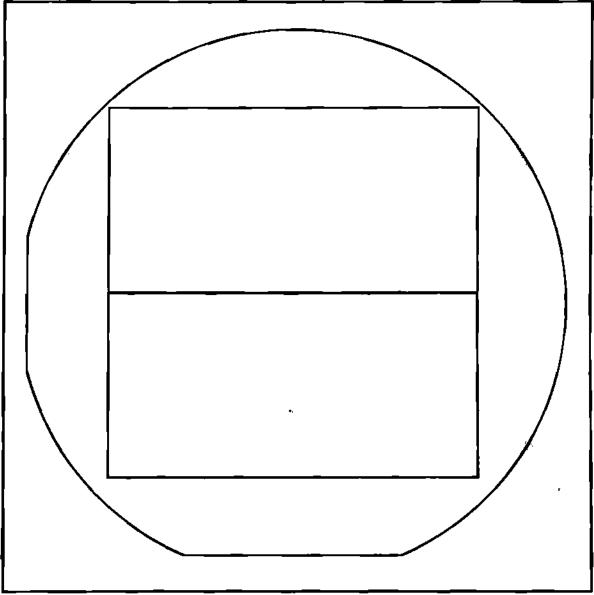

| 6.5.3  | Layout of 8-Square-Inch Substrates 2 x 4 Inches on a 6-Inch Wafer | 6-21 |

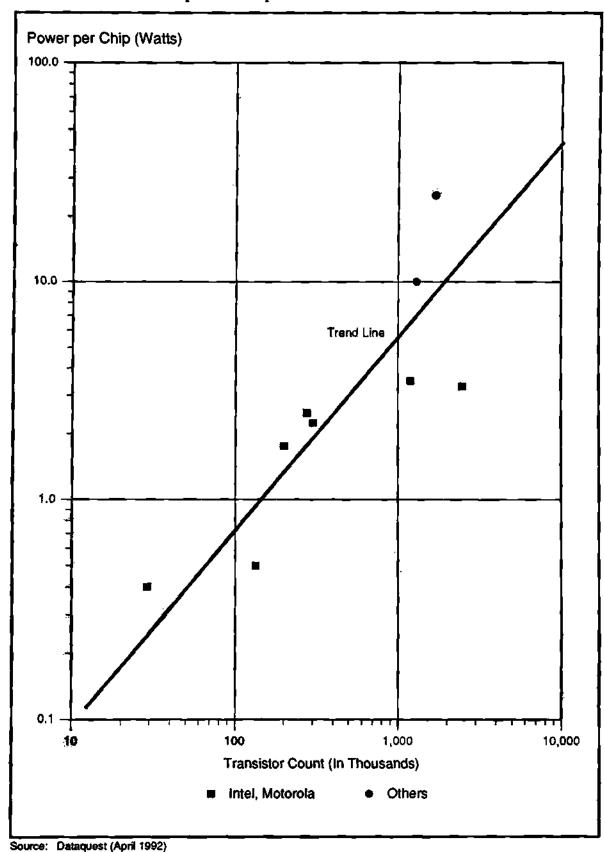

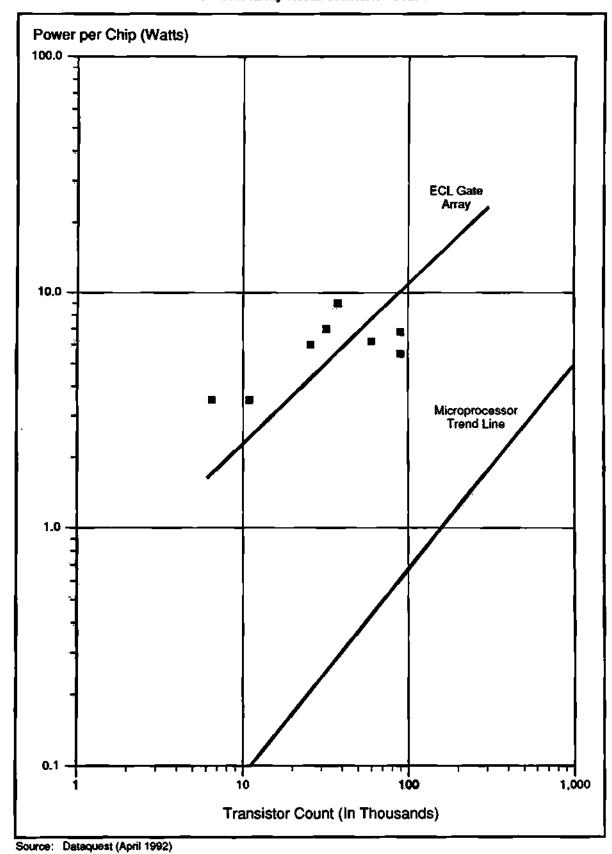

| 6.6.1  | Microprocessor Chip Power versus Transistor Count                 |      |

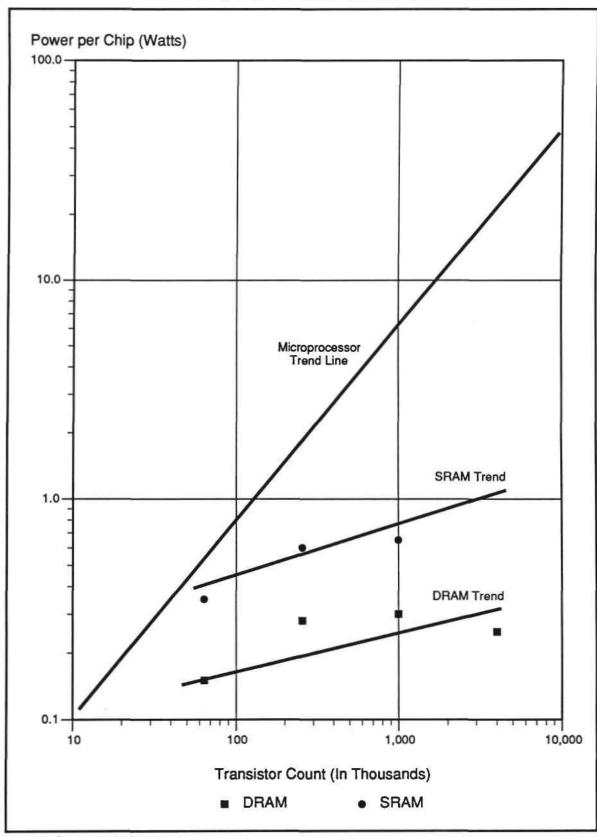

| 6.6.2  | Memory Chip Power versus Transistor Count                         |      |

| 6.6.3  | ECL Gate Array Power versus Transistor Count                      |      |

| 6.6.4  | Microprocessor Chip Power versus Time                             |      |

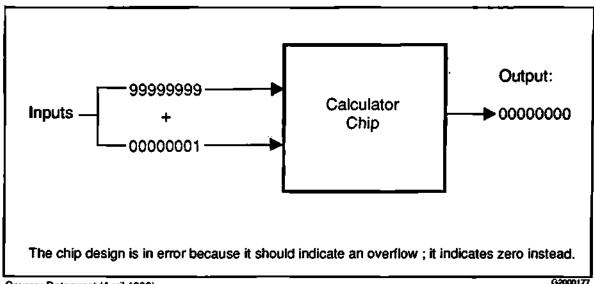

| 7,2,1  | Incorrect Function of 8-Digit Calculation                         | 7-2  |

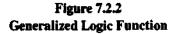

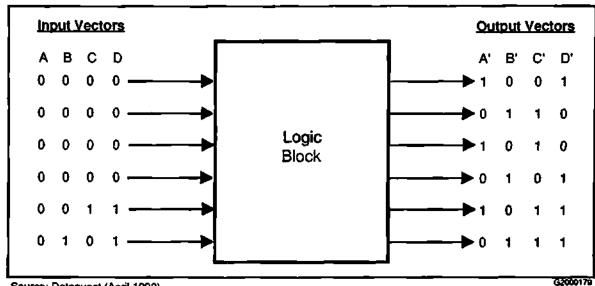

| 7.2.2  | Generalized Logic Function                                        |      |

| 7.2.3  | Illustration of Test Vectors                                      |      |

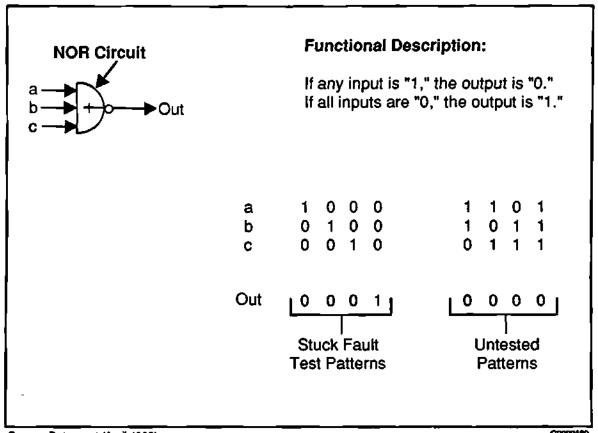

| 7,2,4  | Testing for Stuck Faults                                          |      |

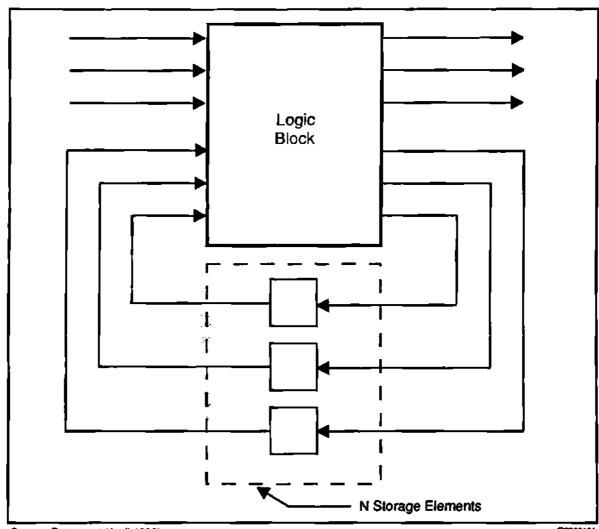

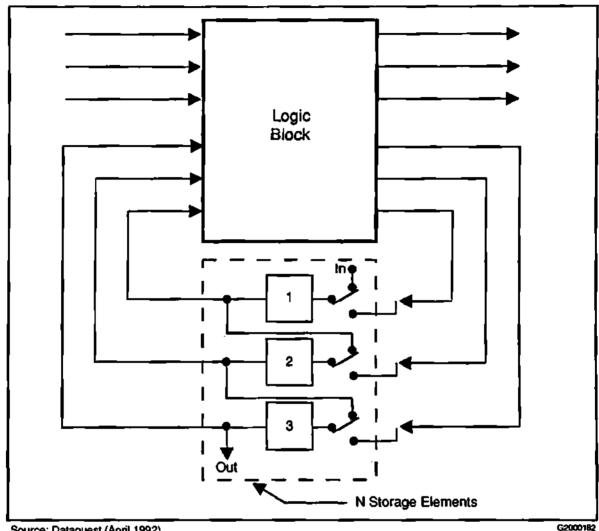

| 7.2.5  | Generalized Logic Function With Storage                           |      |

| 7.2.6  | Generalized Logic Function With Scan Logic                        |      |

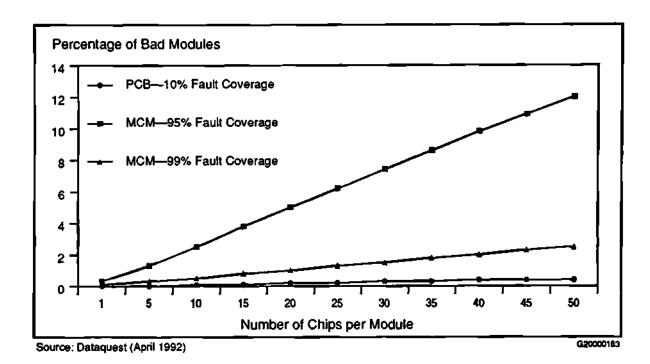

| 7.2.7  | Module Defects vs Chip Count for PCB & MCM                        |      |

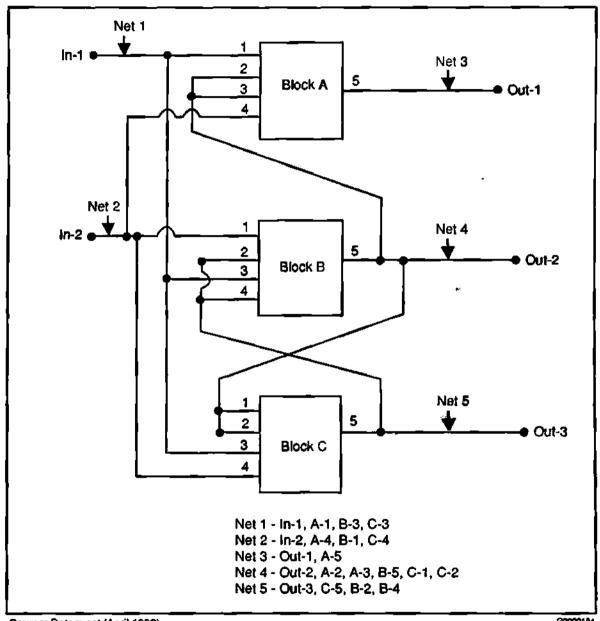

| 7.2.8  | Logic Network with 5 Nets                                         |      |

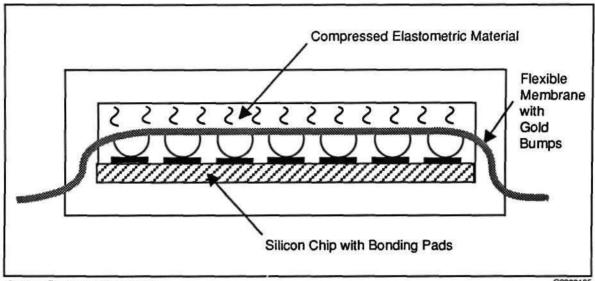

| 7.2.9  | Membrane Socket for Chip Test                                     |      |

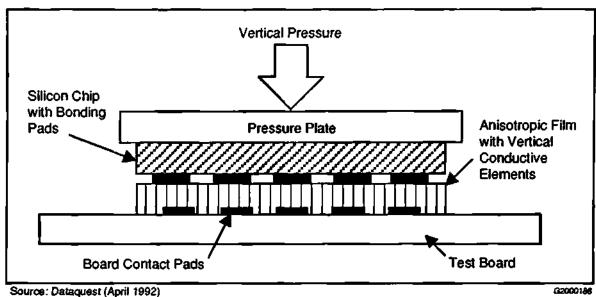

| 7.2.10 | Anisotropic Conductive Film for Chip Connection                   |      |

| 7.2.11 | Glow Discharge of MCM Substrate                                   |      |

# **Foreword**

Multichip modules are a major new trend in component packaging technology. MCM user's can take advantage of this technology to build more competitive products—products that use less power or are faster or smaller. MCM user's can optimize their product design and procurement of various MCM technologies based on the information available in this study.

The objective of the Multichip Modules: Issues and Trends study is to provide participants with comprehensive information that is qualitative as well as quantitative on the critical trends and major opportunities for multichip module products in the global electronics market.

The written analysis and data assembled in the study were accomplished by Howard Z. Bogert and Mary A. Olsson. The semiconductor component and application forecasts were provided by Jerry Banks, Gary Grandbois, Jim Handy, Brian Lewis, Ken Lowe, Lane Mason and Greg Sheppard of Dataquest.

## Chapter 1 — Executive Summary

Multichip module (MCM) technology in production today offers reduced interconnect line width over traditional board technologies in density efficiencies and less area of silicon per package. The advantages of using MCM technology are that high lead count die, on a high interconnect density substrate, require less than 1 mil pitch, and offer 50% to 60% package efficiencies over single chip packages on a PCB which require 4 mil to 8 mil geometries. The disadvantages of MCM technology are that it is a new technology, it is in the prototyping stage for most suppliers to the merchant market, and there is a lack of general consensus on how to handle MCM test issues.

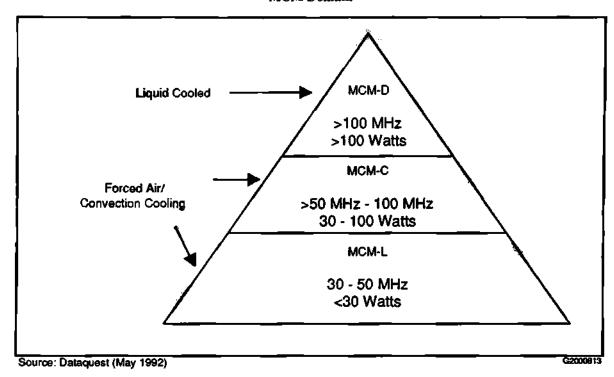

The types of MCM technology that will be covered in this study will be referenced by the acronyms MCM-L(L = laminated), MCM-C(C = cofired), and MCM-D(D = deposited), as defined by IPC-MC-790 classifications. Dataquest's market definition for a multichip module is as follows:

- A module interconnects two or more chips on a single substrate.

- A module achieves higher computation clock rates by reducing propagation delays between chips.

- A module has the potential to be less expensive than conventional technology for highly interconnected digital circuits.

- It doesn't matter how the module is constructed so long as it fills the market need.

The goal of this study is to answer the following questions:

- What performance improvements can be achieved now and in the future through MCM technology?

- What are the current and future MCM costs likely to be?

- What problems stand in the way of more complete MCM implementation?

- What are the capabilities and costs of the different MCM technologies?

- Who are the major MCM vendors and what services do they supply?

#### Methodology

To set the full business context of the MCM market from 1990 through 2000, Dataquest provides the following:

- Estimated share of available bare die that could be configured in a MCM design.

- Estimated share of electronic equipment that has one or more MCMs.

- Estimated percentage of the semiconductors in that equipment that are designed in a MCM configuration.

- Estimated MCM value in electronic equipment.

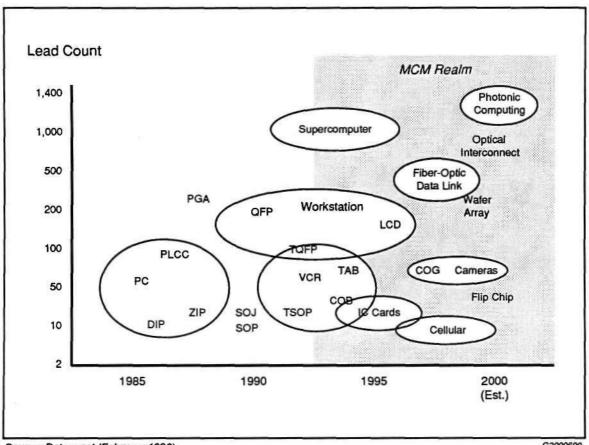

Figure 1.4.1 **MCM Application Drivers**

Source: Dataquest (February 1992)

G2000690

#### **General Assumptions**

After surveying suppliers and users of MCM technology, Dataquest has concluded the following:

- MCMs will only be designed into new products.

- The majority of MCM designs will be consumed in the dataprocessing, consumer, and communication application markets by 1995.

- The propensity for designers to switch to MCMs for various types of applications will be driven basically by the performance application segments, all other segments are cost driven.

- Captive share of the MCM market is approximately 80 percent of total MCM revenue in 1992.

#### **Multichip Module Drivers**

As shown on Figure 1.4.1, the application drivers for MCM technology will continue to flow from the computer sector. The premier metric of computer economics is price/performance, essentially, the dollar cost of one performance unit. As one of the fundamentals of buyer decision making, a low price/performance ratio has one compelling benefit: volume sales.

In terms of price/compute performance, the average 1991 workstation will remain over six times superior to the average supercomputer and over thirty-one times that of the average mainframe. This gap will widen substantially over the next five years. By 1997, the average workstation price/performance should be thirteen times lower than that of a supercomputer and seventy-three times lower than for a mainframe. The primary drivers widening this gap for the workstation are shortened design cycles allowing rapidly accelerating performance improvements, coupled with rapidly accelerating shipment volumes, and hence, price declines. Significantly, Dataquest anticipates that workstation price/performance will even that of personal computers by 1993.

However, in terms of absolute compute power, the highest performance product segment in the computer industry remains the supercomputer. Dataquest anticipates that the average mainframe will reach today's average supercomputer performance level in the 1994-1995 timeframe and the average workstation this same performance in the 1999-2000 timeframe.

The workstation segment is progressing at a relatively fast rate compared to other segments because of the design time for systems development and hence new technology incorporation. Mainframes and supercomputers typically take 3-7 years for design compared to 9 months to two years for a workstation. While both supercomputers and workstations today often incorporate similar CPUs (eg. RISC), several key differences remain which add to the system design time for the larger systems. The most significant ones contributing to the complexity of the supercomputer and mainframe hardware and software design include the following:

- Prevalence of multiprocessor technology.

- Specialized vector processors.

- More advanced and complex I/O subsystem and communications requirements.

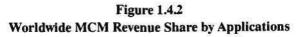

In the 1995 timeframe, the dataprocessing segments are expected to represent 62 percent of MCM revenue worldwide. MCM-C and MCM-D will be the prevalent MCM technologies of this share of market.

Overall, workstation performance and MCM market development are keyed to the continued market dominance of five chip technologies: HP PA, MIPs, Motorola 68000, IBM POWERchip, and SPARC. Within the workstation technology arena, the HP PA architecture provides the industry's leading RISC performance. This combined superscalar/superpipelined architecture is capable of up to 66 MHz in CMOS. In 1991, HP PA represented approximately 3.6 percent of the total workstations shipped. However, by 1995, PA RISC is expected to represent 11 percent of the total workstation shipments.

Dataquest assumes that the MIPs RISC architecture will allow more agressive performance enhancements since the superpipeline design will allow comparable performance to a superscalar implementation with less silicon. Moreover, we assume caches will initially be larger with such pipelined architectures.

Our workstation forecast assumes an agressive increase in the IBM's RISC shipments, rising from 8.1 percent of the 1990 workstation total units to 20 percent of the 1997 workstation shipment total. In the final analysis, we believe that it is more likely that architectures dependent on clock speed will achieve leading performance (eg. superpipelined) than those dependent on complex logic (eg. superscalar).

Source: Dataquest (May 1992)

G2000691

Overall, due to intense marketshare competition among workstation participants, Dataquest forecasts that over 60 percent of the total systems shipped in the 1992 timeframe will be entry level systems, consisting of 1 to 2 generation-mature RISC technology. In the 1993-1995 timeframe, the average desktop workstation performance will be fueled by the following key factors:

- Emergence of BICMOS technology.

- Superscalar floating point.

- Branch prediction.

- Full 64-bit RISC implementations.

- MCM packaging efficiences.

- Enhanced memory performance due to volume availability of 4Mb SIMMs.

- Larger on-chip caches for superpipelined architectures.

As shown on Figure 1.4.2, the consumer market will represent the second largest share of MCM revenue by 1995, while communications is expected to represent a 9 percent share. MCM-L will be the prevalent technology of these two markets.

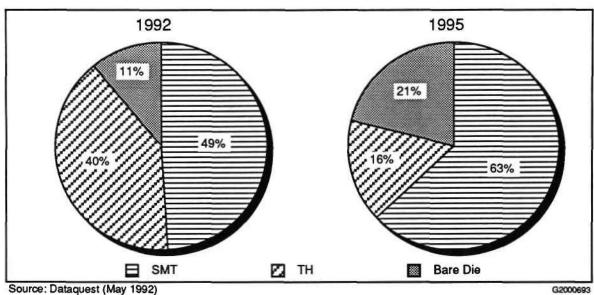

Figure 1.4.3 Emerging Package Trends

| r                       | 1991<br>——–                                              | 1993<br>—— | 1995<br>                                           | 1997              | 2000                                                            |

|-------------------------|----------------------------------------------------------|------------|----------------------------------------------------|-------------------|-----------------------------------------------------------------|

| Market<br>Drivers       | Performance                                              |            | Miniaturization<br>Weight Reduction                |                   | Cost<br>Reliability<br>Ease of Use                              |

| Electronic<br>Equipment | Industrial<br>Equipment Expansion                        |            |                                                    | rsonal<br>tronics | Advanced A/V<br>Advanced Information<br>Automotive              |

| Technology              | High-Density SMT<br>High Speed                           |            | Ultrahigh-Density SMT<br>Custom Packaging/Bondin   | פר                | Ultracompact<br>Packageless TABs                                |

| Components              | CMOS<br>Multiple Pins<br>Small Pitch<br>1.5 µm<br>25 MHz |            | BICMOS<br>SSOP/TSOP<br>LOC/VOFP<br>1.0µm<br>50 MHz |                   | Advanced BiCMOS<br>Module SMDs<br>Stackable<br>0.5µm<br>100 MHz |

Source: Dataquest (May 1992)

32000582

As part of the continuing review of emerging package trends as illustrated on Figure 1.4.3, other markets and technology drivers that will promote the MCM market will be analyzed extensively in Chapters 2 and 3 of this study.

## Chapter 2 — Multichip Module Forecast

#### Introduction

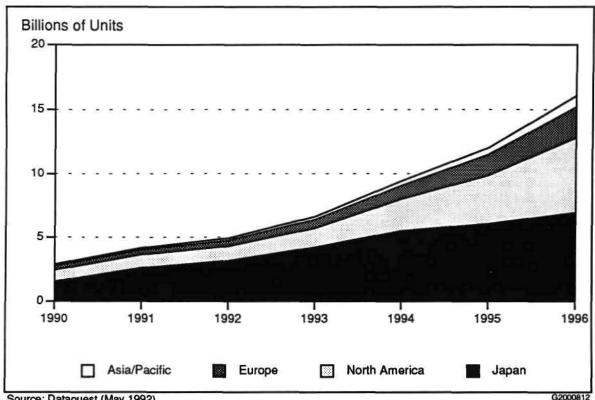

The worldwide packaging forecast is an evaluation of the single-chip package production for active integrated circuit (IC) devices as well as the available bare die shipped from 1990 through 1996, with projections to 2000. The estimated share of available bare die that potentially could be absorbed into varying MCM configurations are projected by region. This data has been provided to illustrate the potential development of new interconnect technology as well as potential displacement or erosion of other competing package technologies.

#### **Package Forecast**

The worldwide forecast shown in Table 2.2.1 represents the total number of single-chip packaged active ICs produced in the four major regions tracked by Dataquest. The forecast is based on the most recent Dataquest IC forecast. The number for bare die represents unpackaged ICs.

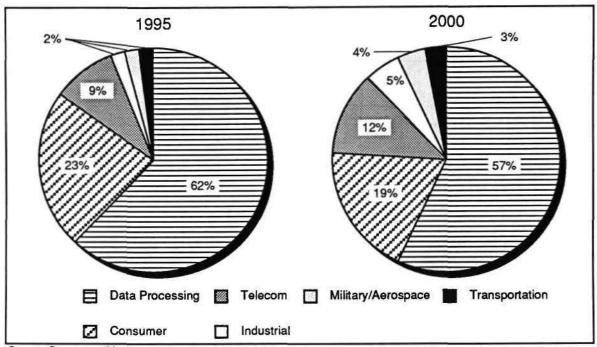

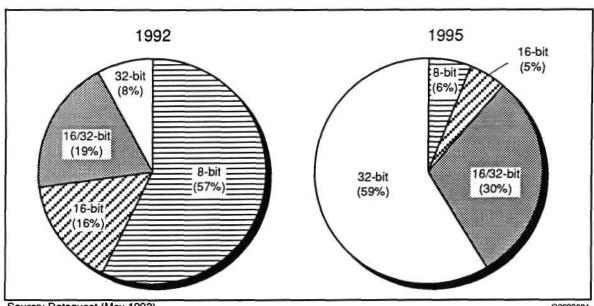

Of the total ICs projected to be shipped in 1992, an estimated 40 percent will still be housed in throughhole (TH) packages, as shown on Figure 2.2.1. TH share will continue its decline dropping to approximately 16 percent of the total share by 1995.

Regionally, as shown in Tables 2.2.2 through 2.2.5, Japan is expected to remain the dominant supplier of both SMT packages as well as bare die to the worldwide markets.

#### **Semiconducctor Component Forecasts**

During the last two years a major divergence in packaging and interconnect technologies has taken place within the Small Outline (SO) and QUAD. Driven by steady increases in microprocessor operating frequencies and bus widths, and reduction in line width geometries, along with the evolution of 3.3 volt systems, whole new families of Thin Small Outline (TSOP), Thin Shrink Small Outline (TSSOP), Thin Quad (TQFP) and Shrink QUAD (SQFP) packages have emerged. For the CMOS and advanced BICMOS logic circuits, as shown in Tables 2.3.1 through 2.3.5 the 25 mil fine pitch package offers the smallest footprint available.

#### ASIC

CMOS continues to be the mainstream technology accounting for over 72 percent of the total market revenue in 1992. The BICMOS gate array forecast has been downgraded from original estimates. Future robust growth is questionable as suppliers of CMOS continue to extend the limits of CMOS and interconnect technology. Challenges for ASIC technology during the next five years will come from 100 MHz clock rates and 600 pin counts. Table 2.4.1 shows the estimated worldwide gate array forecast by region and technology. Tables 2.4.2 through 2.4.5 show the collective gate array package production by region.

Table 2.2.1

Estimated Worldwide Package Production

|                      | <u>1990</u> | <u>1991</u> | <u>1992</u> | <u> 1993</u> | <u> 1994</u> | <u>1995</u> | <u>1996</u> | 2000  |

|----------------------|-------------|-------------|-------------|--------------|--------------|-------------|-------------|-------|

| Plastic DIP          | 20575       | 17549       | 14264       | 11056        | 8120         | 5818        | 4350        | 1880  |

| Ceramic DIP          | 3169        | 2801        | 2616        | 2304         | 2142         | 1922        | 1770        | 1238  |

| QUAD                 | 4068        | 5169        | 7024        | 10140        | 14399        | 16781       | 18550       | 24400 |

| Ceramic Chip Carrier | <b>260</b>  | 271         | 292         | 312          | 350          | 325         | 292         | 140   |

| Plastic Chip Carrier | 431         | 579         | 724         | 834          | 767          | 663         | 613         | 270   |

| so                   | 10602       | 12053       | 13576       | 14809        | 16860        | 19058       | 20811       | 32700 |

| Ceramic PGA          | 265         | 395         | 602         | 762          | 795          | 742         | 660         | 458   |

| Plastic PGA          | 147         | 248         | 512         | 744          | 865          | 850         | 801         | 512   |

| Bare Chip            | 2878        | 4153        | 4905        | 6604         | 9409         | 12011       | 16053       | 39691 |

| Total                | 42395       | 43218       | 44515       | 47565        | 53707        | 58170       | 63900       | 79329 |

Figure 2.2.1 Worldwide Package Share

Source: Dataquest (May 1992)

Table 2.2.2

North America-Estimated Package Production

(Millions of Units)

|                      | <u>1988</u> | <u>1989</u> | <u>1990</u> | <u> 1991</u> | <u>1992</u> | <u>1993</u> | <u>1994</u> | <u>1995</u> | <u>1996</u> | 2000   |

|----------------------|-------------|-------------|-------------|--------------|-------------|-------------|-------------|-------------|-------------|--------|

| Plastic DIP          | 9500        | 9109        | 8400        | 7500         | 6300        | 5100        | 3700        | 2509        | 1840        | 780    |

| Ceramic DIP          | 1487        | 1453        | 1450        | 1322         | 1220        | 1040        | 983         | 872         | 818         | 638    |

| QUAD                 | 181         | 450         | 844         | 1355         | 2149        | 3340        | 4700        | 5300        | 5600        | 6700   |

| Ceramic Chip Carrier | 112         | 170         | 188         | 200          | 221         | 245         | 288         | 270         | 244         | 120    |

| Plastic Chip Carrier | 166         | 222         | 240         | 400          | 530         | 645         | 603         | 511         | 470         | 220    |

| SO                   | 1100        | 1219        | 1600        | 1595         | 1800        | 2100        | 2920        | 3738        | 3727        | 6800   |

| Ceramic PGA          | 78          | 96          | 124         | 185          | 285         | 365         | 335         | 290         | 244         | 159    |

| Plastic PGA          | 22          | 50          | 65          | 115          | 245         | 340         | 396         | 380         | <b>36</b> 0 | 210    |

| Bare Die             | 700         | 750         | 900         | 1029         | 1120        | 1461        | 2504        | 3800        | 5867        | 13600  |

| Total                | 13346       | 13519       | 13811       | 13701        | 13870       | 14636       | 16429       | 17670       | 19170       | 29227  |

| Percent of Total     | 1988        | <u>1989</u> | 1990        | <u>1991</u>  | 1992        | <u>1993</u> | 1994        | 1995        | 1996        | 2000   |

| Plastic DIP          | 71.2%       | 67.4%       | 60.8%       | 54.7%        | 45.4%       | 34.8%       | 22.5%       | 14.2%       | 9.6%        | 2.7%   |

| Ceramic DIP          | 11.1%       | 10.7%       | 10.5%       | 9.6%         | 8.8%        | 7.1%        | 6.0%        | 4.9%        | 4.3%        | 2.2%   |

| QUAD                 | 1.4%        | 3.3%        | 6.1%        | 9.9%         | 15.5%       | 22.8%       | 28.6%       | 30.0%       | 29.2%       | 22.9%  |

| Ceramic Chip Carrier | .8%         | 1.3%        | 1.4%        | 1.5%         | 1.6%        | 1.7%        | 1.8%        | 1.5%        | 1.3%        | 4%     |

| Plastic Chip Carrier | 1.2%        | 1.6%        | 1.7%        | 2.9%         | 3.8%        | 4.4%        | 3.7%        | 2.9%        | 2.5%        | .8%    |

| SO                   | 8.2%        | 9.0%        | 11.6%       | 11.6%        | 13.0%       | 14.3%       | 17.8%       | 21.2%       | 19.4%       | 23.3%  |

| Ceramic PGA          | .6%         | .7%         | .9%         | 1.4%         | 2.1%        | 2.5%        | 2.0%        | 1.6%        | 1.3%        | 5%     |

| Plastic PGA          | .2%         | 4%          | 5%          | .8%          | 1.8%        | 2.3%        | 2.4%        | 2.2%        | 1.9%        | .7%    |

| Bare Die             | 5.2%        | 5.5%        | 6.5%        | 7.5%         | 8.1%        | 10.0%       | 15.2%       | 21.5%       | 30.6%       | 46.5%  |

| Total :              | 100.0%      | 100.0%      | 100.0%      | 100.0%       | 100.0%      | 100.0%      | 100.0%      | 100.0%      | 100.0%      | 100.0% |

Table 2.2.3

Japan-Estimated Package Production

(Millions of Units)

|                      | 1988        | <u>1989</u> | <u>1990</u> | <u>1991</u>  | 1992         | <u>1993</u> | 1994        | <u> 1995</u> | <u>1996</u> | 2000   |

|----------------------|-------------|-------------|-------------|--------------|--------------|-------------|-------------|--------------|-------------|--------|

| Plastic DIP          | 7450        | 6723        | 6000        | 4805         | 3650         | 2300        | 1250        | 950          | 800         | 200    |

| Ceramic DIP          | 1745        | 1333        | 980         | 840          | 800          | 705         | 645         | <b>58</b> 8  | 500         | 265    |

| Quad                 | 1800        | 2100        | 2402        | 2700         | 3100         | 3800        | 4900        | 5500         | 5840        | 5600   |

| Ceramic Chip Carrier | 42          | 38          | 30          | 28           | 26           | 21          | 19          | 14           | 10          | 0      |

| Plastic Chip Carrier | 132         | 144         | 122         | 100          | 89           | 70          | 54          | 32           | 27          | 0      |

| so                   | 3414        | 3723        | 4334        | 5013         | 5935         | 6290        | 7140        | <i>7</i> 920 | 9060        | 15900  |

| Ceramic PGA          | 44          | 59          | 85          | 120          | 195          | 255         | 298         | 300          | 280         | 198    |

| Plastic PGA          | 7           | 22          | 60          | 90           | 180          | 300         | 365         | 370          | 342         | 220    |

| Barc Die             | 894         | 1059        | 1550        | 2620         | 3174         | 4226        | 5492        | 6051         | 6912        | 14726  |

| Total (Single Chip)  | 15528       | 15201       | 15563       | 16316        | 17149        | 17967       | 20163       | 21725        | 23771       | 37109  |

| Percent of Total     | <u>1988</u> | <u>1989</u> | 1990        | <u> 1991</u> | <u> 1992</u> | <u>1993</u> | <u>1994</u> | 1995         | <u>1996</u> | 2000   |

| Plastic DIP          | 48.0%       | 44.2%       | 38.6%       | 29.4%        | 21.3%        | 12.8%       | 6.2%        | 4.4%         | 3.4%        | .5%    |

| Ceramic DIP          | 11.2%       | 8.8%        | 6.3%        | 5.1%         | 4.7%         | 3.9%        | 3.2%        | 2.7%         | 2.1%        | .7%    |

| Quad                 | 11.6%       | 13.8%       | 15.4%       | 16.5%        | 18.1%        | 21.1%       | 24.3%       | 25.3%        | 24.6%       | 15.1%  |

| Ceramic Chip Carrier | .3%         | .2%         | .2%         | .2%          | .2%          | .1%         | .1%         | .1%          | .0%         | .0%    |

| Plastic Chip Carrier | .9%         | .9%         | .8%         | .6%          | .5%          | .4%         | .3%         | .1%          | .1%         | .0%    |

| SO                   | 22.0%       | 24.5%       | 27.8%       | 30.7%        | 34.6%        | 35.0%       | 35.4%       | 36.5%        | 38.1%       | 42.8%  |

| Ceramic PGA          | .3%         | .4%         | 5%          | .7%          | 1.1%         | 1.4%        | 1.5%        | 1.4%         | 1.2%        | .5%    |

| Plastic PGA          | .0%         | .1%         | .4%         | .6%          | 1.0%         | 1.7%        | 1.8%        | 1.7%         | 1.4%        | .6%    |

| Bare Die             | 5.8%        | 7.0%        | 10.0%       | 16.1%        | 18.5%        | 23.5%       | 27.2%       | 27.9%        | 29.1%       | 39.7%  |

| Total                | 100.0%      | 100.0%      | 100.0%      | 100.0%       | 100.0%       | 100.0%      | 100.0%      | 100.0%       | 100.0%      | 100.0% |

Table 2.2.4

Europe-Estimated Package Production

(Millions of Units)

|                      | 1988   | <u> 1989</u> | <u>1990</u> | <u>1991</u> | 1992   | <u>1993</u> | <u>1994</u> | <u>1995</u> | <u> 1996</u> | <u>2000</u> |

|----------------------|--------|--------------|-------------|-------------|--------|-------------|-------------|-------------|--------------|-------------|

| Plastic DIP          | 3900   | 3780         | 3600        | 3100        | 2600   | 2245        | 2070        | 1570        | 1210         | 800         |

| Ceramic DIP          | 777    | 638          | 588         | 510         | 494    | 481         | 466         | 430         | 424          | 318         |

| QUAD                 | 198    | 278          | 710         | 880         | 1020   | 1500        | 2100        | 2600        | 3100         | 5600        |

| Ceramic Chip Carrier | 36     | 37           | 41          | 42          | 44     | 45          | 42          | 40          | 37           | 19          |

| Plastic Chip Carrier | 40     | 42           | 46          | 48          | 51     | 62          | 60          | 57          | 54           | 31          |

| OZ                   | 1300   | 1600         | 2090        | 2180        | 2230   | 2550        | 2700        | 2800        | 2774         | 3500        |

| Ceramic PGA          | 14     | 22           | 52          | 85          | 115    | 132         | 150         | 140         | 122          | 90          |

| Plastic PGA          | 6      | 11           | 20          | 40          | 82     | 95          | 92          | 88          | 85           | <b>7</b> 0  |

| Bare Die             | 172    | 228          | 306         | 367         | 451    | 703         | 1079        | 1634        | 2405         | 5275        |

| Total                | 6443   | 6636         | 7453        | 7252        | 7087   | 7813        | 8759        | 9359        | 10211        | 15703       |

| Percent of Total     | 1988   | 1989         | <u>1990</u> | <u>1991</u> | 1992   | 1993        | 1994        | 1995        | <u> 1996</u> | 2000        |

| Plastic DIP          | 60.5%  | 57.0%        | 48.3%       | 42.7%       | 36.7%  | 28.7%       | 23.6%       | 16.8%       | 11.8%        | 5.1%        |

| Ceramic DIP          | 12.1%  | 9.6%         | 7.9%        | 7.0%        | 7.0%   | 6.2%        | 5.3%        | 4.6%        | 4.2%         | 2.0%        |

| QUAD                 | 3.1%   | 4.2%         | 9.5%        | 12.1%       | 14.4%  | 19.2%       | 24.0%       | 27.8%       | 30.4%        | 35.7%       |

| Ceramic Chip Carrier | .6%    | .6%          | .6%         | .6%         | .6%    | .6%         | 5%          | 4%          | .4%          | .1%         |

| Plastic Chip Carrier | .6%    | .6%          | .6%         | .7%         | .7%    | .8%         | .7%         | .6%         | .5%          | .2%         |

| so                   | 20.2%  | 24.1%        | 28.0%       | 30.1%       | 31.5%  | 32.6%       | 30.8%       | 29.9%       | 27.2%        | 22.3%       |

| Ceramic PGA          | .2%    | .3%          | .7%         | 1.2%        | 1.6%   | 1.7%        | 1.7%        | 1.5%        | 1.2%         | .6%         |

| Plastic PGA          | .1%    | .2%          | .3%         | .6%         | 1.2%   | 1.2%        | 1.1%        | .9%         | .8%          | .4%         |

| Bare Die             | 2.7%   | 3.4%         | 4.1%        | 5.1%        | 6.4%   | 9.0%        | 12.3%       | 17.5%       | 23.6%        | 33.6%       |

| Total :              | 100.0% | 100.0%       | 100.0%      | 100.0%      | 100.0% | 100.0%      | 100.0%      | 100.0%      | 100.0%       | 100.0%      |

Table 2.2.5

Asia Pacific - Estimated Package Production

(Millions of Units)

|                      | <u>1988</u> | <u> 1989</u> | <u> 1990</u> | <u>1991</u> | <u>1992</u> | <u>1993</u> | <u>1994</u> | <u>1995</u> | <u>1996</u> | <u>2000</u> |

|----------------------|-------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Plastic DIP          | 2790        | 2654         | 2575         | 2144        | 1714        | 1411        | 1100        | 789         | 500         | 100         |

| Ceramic DIP          | 148         | 155          | 151          | 129         | 102         | 78          | 48          | 32          | 28          | 17          |

| QUAD                 | 4           | 18           | 112          | 234         | 755         | 1500        | 2699        | 3381        | 4010        | 6500        |

| Ceramic Chip Carrier | 1           | 1            | 1            | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

| Plastic Chip Carrier | 14          | 17           | 23           | 31          | 54          | 57          | 50          | 63          | 62          | 19          |

| so                   | 1285        | 1559         | 2578         | 3265        | 3611        | 3869        | 4100        | 4600        | 5250        | 6500        |

| Ceramic PGA          | 3           | 4            | 4            | 5           | 7           | 10          | 12          | 12          | 14          | 11          |

| Plastic PGA          | 1           | 2            | 2            | 3           | 5           | 9           | 12          | 12          | 14          | 12          |

| Bare Chip            | 60          | 72           | 122          | 137         | 160         | 214         | 334         | 526         | 869         | 6090        |

| Total                | 4306        | 4482         | 5568         | 5949        | 6409        | 7149        | 8356        | 9416        | 10748       | 19250       |

| Plastic DIP          | 64.8%       | 59.2%        | 46.2%        | 36.0%       | 26.7%       | 19.7%       | 13.2%       | 8.4%        | 4.7%        | 5%          |

| Ceramic DIP          | 3.4%        | 3.5%         | 2.7%         | 2.2%        | 1.6%        | 1.1%        | .6%         | .3%         | .3%         | .1%         |

| QUAD                 | .1%         | 4%           | 2.0%         | 3.9%        | 11.8%       | 21.0%       | 32.3%       | 35.9%       | 37.3%       | 33.8%       |

| Ceramic Chip Carrier | .0%         | .0%          | .0%          | .0%         | .0%         | .0%         | .0%         | .0%         | .0%         | .0%         |

| Plastic Chip Carrier | .3%         | .4%          | .4%          | .5%         | .8%         | .8%         | .6%         | .7%         | .6%         | .1%         |

| so                   | 29.8%       | 34.8%        | 46.3%        | 54.9%       | 56.3%       | 54.1%       | 49.1%       | 48.9%       | 48.8%       | 33.8%       |

| Ceramic PGA          | .1%         | .1%          | .1%          | .1%         | .1%         | .1%         | .1%         | .1%         | .1%         | .1%         |

| Plastic PGA          | .0%         | .0%          | .0%          | .1%         | .1%         | .1%         | .1%         | .1%         | .1%         | .1%         |

| Bare Chip            | 1.4%        | 1.6%         | 2.2%         | 2.3%        | 2.5%        | 3.0%        | 4.0%        | 5.6%        | 8.1%        | 31.6%       |

| Total                | 100.0%      | 100.0%       | 100.0%       | 100.0%      | 100.0%      | 100.0%      | 100.0%      | 100.0%      | 100.0%      | 100.0%      |

Table 2.3.1

Estimated Worldwide Standard Logic Package Production

(Millions of Dollars)

|                 | <u>1988</u> | <u>1989</u> | <u>1990</u> | <u> 1991</u> | <u>1992</u>   | <u>1993</u>  | <u> 1994</u> | <u>1995</u> | <u>1996</u> | 2000   |

|-----------------|-------------|-------------|-------------|--------------|---------------|--------------|--------------|-------------|-------------|--------|

| Worldwide Total | 3061.2      | 3055.2      | 3242.5      | 3530.4       | 3739.9        | 3923.85      | 4045.8       | 4117.55     | 4202        | 4148.9 |

| DIP             | 578.3       | 547.7       | 349.3       | 337.3        | 303.0         | 247.7        | 237.3        | 233.4       | 229.3       | 201.2  |

| Plastic         | 404.2       | 379.9       | 215.3       | 205.6        | 186.1         | 155.2        | 147.5        | 142.8       | 139.6       | 117.3  |

| Ceramic         | 147.8       | 142.5       | 112.0       | 110.5        | 98.6          | 78.9         | 76.5         | 76.8        | 76.1        | 70.8   |

| Side Brazed     | 26.3        | 25.3        | 22.0        | 21.2         | 18.3          | 13.6         | 13.3         | 13.8        | 13.6        | 13.2   |

| Flatpack        | 46.4        | 45.0        | 39.9        | 38.7         | 38.4          | 36.6         | 36.4         | 36.4        | 35.7        | 33.2   |

| Ceramic         | 41.9        | 40.7        | 36.1        | 35.0         | 34.8          | 33.2         | 33.0         | 33.0        | 32.4        | 30.3   |

| Side Brazed     | 4.5         | 4.3         | 3.8         | 3.7          | 3.6           | 3.4          | 3.4          | 3.4         | 3.3         | 2.9    |

| Chip Carrier    | 23.0        | 25.2        | 29.3        | 48.3         | 62.8          | 81.6         | 101.5        | 129.5       | 166.4       | 422.4  |

| Plastic         | 6.8         | 6.7         | 5.0         | 5.1          | 5.2           | 5.2          | 5.1          | 5.1         | 5.2         | 4.9    |

| Ceramic         | 16.2        | 18.5        | 24.3        | 43.2         | 57.6          | <b>7</b> 6.4 | 96.4         | 124.3       | 161.2       | 417.5  |

| so              | 2413.4      | 2437.3      | 2404.2      | 2561.9       | 2736.1        | 2922.2       | 3036.7       | 3103.0      | 3173.5      | 3044.2 |

| QUAD/SQFP       | 0.0         | 0.0         | 419.7       | 544.2        | <b>599</b> .6 | 635.8        | 633.9        | 615.3       | 597.1       | 447.9  |

| CMOS            | 844.5       | 892.7       | 694.2       | 715.0        | 709.1         | 720.6        | 737.4        | 743.6       | 742.2       | 663.6  |

| DIP             | 4.3         | 4.6         | 3.2         | 3.1          | 3.0           | 3.0          | 3.1          | 3.1         | 3.1         | 2.8    |

| Plastic         | 3.5         | 3.6         | 2.4         | 2.2          | 2.1           | 2.1          | 2.1          | 2.1         | 2.1         | 1.8    |

| Ceramic         | 0.6         | 0.7         | 0.6         | 0.7          | 0.7           | 0.7          | 0.7          | 0.7         | 0.7         | 0.7    |

| Side Brazed     | 0.2         | 0.3         | 0.2         | 0.3          | 0.3           | 0.3          | 0.3          | 0.3         | 0.3         | 0.3    |

| Flatpack        | 3.3         | 3.5         | 3.3         | 3.5          | 3.6           | 3.7          | 3.8          | 3.9         | 3.9         | 3.6    |

| Ceramic         | 3.1         | 3.3         | 3.2         | 3.3          | 3.4           | 3.5          | 3.6          | 3.7         | 3.7         | 3.5    |

| Side Brazed     | 0.2         | 0.2         | 0.2         | 0.2          | 0.2           | 0.2          | 0.2          | 0.2         | 0.2         | 0.2    |

| Chip Carrier    | 1.9         | 2.0         | 1.8         | 1.9          | 2.0           | 2.0          | 2.1          | 2.1         | 2.1         | 1.9    |

| Plastic         | 1.0         | 1.1         | 0.9         | 0.9          | 1.0           | 1.0          | 1.0          | 1.0         | 1.0         | 0.9    |

| Ceramic         | 0.9         | 1.0         | 0.9         | 1.0          | 1.0           | 1.0          | 1.0          | 1.1         | 1.1         | 1.0    |

| so              | 835.0       | 882.6       | 685.9       | 706.5        | 700.5         | 711.8        | 728.4        | 734.5       | 733.1       | 655.3  |

| Bipolar         | 2203.6      | 2131.3      | 1374.1      | 1316.1       | 1307.7        | 1277.2       | 1246.4       | 1237.5      | 1238.9      | 1122.9 |

| DIP             | 573.9       | 543.0       | 345.7       | 333.7        | 299.3         | 244.1        | 233.9        | 230.0       | 226.2       | 198.4  |

| Plastic         | 400.7       | 376.1       | 212.6       | 203.0        | 183.3         | 152.6        | 145.1        | 140.5       | 137.5       | 115.4  |

| Ceramic         | 147.2       | 141.9       | 111.4       | 109.8        | 97.9          | 78.2         | 75.8         | 76.1        | 75.4        | 70.1   |

| Side Brazed     | 26.0        | 25.0        | 21.7        | 20.9         | 18.0          | 13.3         | 13.0         | 13.5        | 13.3        | 12.9   |

| Flatpack        | 43.1        | 41.4        | 36.4        | 35.0         | 34.5          | 32.6         | 32.2         | 32.0        | 31.0        | 27.6   |

| Ceramic         | 38.8        | 37.2        | 32.8        | 31.5         | 31.1          | 29.3         | 29.0         | 28.8        | 27.9        | 24.9   |

| Side Brazed     | 4.3         | 4.1         | 3.6         | 3.5          | 3.5           | 3.3          | 3.2          | 3.2         | 3.1         | 2.8    |

| Chip Carrier    | 12.1        | 11.7        | 9.3         | 9.1          | 9.3           | 9.3          | 9.2          | 9.4         | 9.6         | 9.4    |

| Plastic         | 5.8         | 5.6         | 4.1         | 4.1          | 4.2           | 4.2          | 4.1          | 4.1         | 4.1         | 4.0    |

| Ceramic         | • 6.3       | 6.1         | 5.1         | 5.0          | 5.1           | 5.1          | 5.1          | 5.3         | 5.4         | 5.4    |

| so              | 1574.5      | 1535.3      | 982.6       | 938.3        | 964.6         | 991.2        | 971.1        | 966.0       | 972.1       | 887.5  |

Table 2.3.1 (cont.)

Estimated Worldwide Standard Logic Package Production

(Millions of Dollars)

|              | 1988 | <u>1989</u> | <u>1990</u> | <u>1991</u> | <u>1992</u> | <u> 1993</u> | 1994   | <u> 1995</u> | <u> 1996</u> | 2000   |

|--------------|------|-------------|-------------|-------------|-------------|--------------|--------|--------------|--------------|--------|

| BICMOS       | 4.0  | 19.6        | 36.8        | 60.8        | 111.3       | 196.5        | 298.4  | 399.0        | 514.4        | 823.4  |

| DIP          | 0.1  | 0.2         | 0.3         | 0.4         | 0,7         | 0.6          | 0.3    | 0.2          | 0.0          | 0.0    |

| Plastic      | 0.1  | 0.2         | 0.3         | 0.4         | 0.7         | 0.6          | 0.3    | 0.2          | 0.0          | 0.0    |

| Ceramic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Side Brazed  | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Flatpack     | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Ceramic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Side Brazed  | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Chip Carrier | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Plastic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Ceramic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| so           | 3.9  | 19.4        | 36.1        | 59.8        | 109.6       | 193.4        | 293.8  | 392.9        | 506.8        | 811.7  |

| QUAD/SQFP    | 0.0  | 0.0         | 0.3         | 0.6         | 1.1         | 2.5          | 4.3    | 5.8          | 7.6          | 11.7   |

| GaAs         | 9.1  | 11.6        | 18.4        | 37.5        | 51.8        | 70.6         | 90.6   | 118.5        | 155.5        | 413.0  |

| DIP          | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Plastic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Ceramic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Side Brazed  | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Flatpack     | 0.1  | 0.1         | 0.1         | 0.2         | 0.3         | 0.3          | 0.4    | 0.5          | 0.7          | 2.0    |

| Ceramic      | 0.1  | 0.1         | 0.1         | 0.2         | 0.3         | 0.3          | 0.4    | 0.5          | 0.7          | 2.0    |

| Side Brazed  | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Chip Carrier | 9.0  | 11.5        | 18.3        | 37.3        | 51.5        | 70.3         | 90.2   | 118.0        | 154.8        | 411.0  |

| Plastic      | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Ceramic      | 9.0  | 11.5        | 18.3        | 37.3        | 51.5        | 70.3         | 90.2   | 118.0        | 154.8        | 411.0  |

| so           | 0.0  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0    | 0.0          | 0.0          | 0.0    |

| Other MOS    | 0.0  | 0.0         | 1119.0      | 1401.0      | 1560.0      | 1659.0       | 1673.0 | 1619.0       | 1551.0       | 1126.0 |

| so           | 0.0  | 0.0         | 699.6       | 857.4       | 961.4       | 1025.7       | 1043.4 | 1009.6       | 961.6        | 689.8  |

| QUAD/SQFP    | 0.0  | 0.0         | 419.4       | 543.6       | 598.6       | 633.3        | 629.6  | 609.4        | 589.5        | 436.2  |

Table 2.3,2

North America-Estimated Standard Logic Package Production

(Millions of Dollars)

|                     | <u>1988</u> | 1989   | <u>1990</u> | <u>1991</u> | <u>1992</u> | <u>1993</u> | <u>1994</u> | <u>1995</u> | <u>1996</u> | 2000              |

|---------------------|-------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------|

| North America Total | 1034.5      | 1029.7 | 1264.9      | 1294.2      | 1373.9      | 1470.0      | 1510.6      | 1552.3      | 1595.6      | 1688.1            |

| DIP                 | 251.7       | 241.8  | 213.3       | 205.2       | 176.6       | 129.1       | 126.6       | 131.7       | 130.0       | 126.5             |

| Plastic             | 125.8       | 121.0  | 106.8       | 102.8       | 88.6        | 64.8        | 63.4        | 65.9        | 64.9        | 63.2              |

| Ceramic             | 100.6       | 96.6   | 85.1        | 81.8        | 70.3        | 51.3        | 50.4        | 52.5        | 51.9        | 50.6              |

| Side Brazed         | 25.2        | 24.2   | 21.4        | 20.6        | 17.7        | 12.9        | 12.7        | 13.2        | 13.1        | 12.7              |

| Flatpack            | 46.4        | 45.0   | 39.9        | 38.7        | 38.4        | 36.6        | 36.4        | 36.4        | 35.7        | 33.2              |

| Ceramic             | 41.9        | 40.7   | 36.1        | 35.0        | 34.8        | 33.2        | 33.0        | 33.0        | 32.4        | 30.3              |

| Side Brazed         | 4.5         | 4.3    | 3.8         | 3.7         | 3.6         | 3.4         | 3.4         | 3.4         | 3.3         | 2.9               |

| Chip Carrier        | 16.2        | 18.3   | 21.1        | 28.1        | 34.2        | 41.6        | 48.4        | 61.8        | 81.0        | 202.8             |

| Plastic             | 3.8         | 3.7    | 3.3         | 3.2         | 3.3         | 3.4         | 3.4         | 3.5         | 3.6         | 3.6               |

| Ceramic             | 12.4        | 14.6   | 17.8        | 24.8        | 30.9        | 38.2        | 45.0        | 58.3        | 77.4        | 199.2             |

| so                  | 720.2       | 724.6  | 820.8       | 833.7       | 917.7       | 1034.4      | 1085.6      | 1130.3      | 1170.9      | 1225.4            |

| QUAD/SQFP           | 0.0         | 0.0    | 169.8       | 188.6       | 206.9       | 228.3       | 213.7       | 192.1       | 178.1       | 100.2             |

| CMOS                | 163.0       | 176.3  | 166.2       | 176.0       | 180.3       | 185.9       | 190.8       | 194.5       | 195.4       | 181.9             |

| DIP                 | 1.6         | 1.8    | 1.7         | 1.8         | 1.8         | 1.9         | 1.9         | 1.9         | 2.0         | 1.8               |

| Plastic             | 0.8         | 0.8    | 0.8         | 0.8         | 0.9         | 0.9         | 0.9         | 0.9         | 0.9         | 0.9               |

| Ceramic             | 0.6         | 0.7    | 0.6         | 0.7         | 0.7         | 0.7         | 0.7         | 0.7         | 0.7         | 0.7               |

| Side Brazed         | 0.2         | 0.3    | 0.2         | 0.3         | 0.3         | 0.3         | 0.3         | 0.3         | 0.3         | 0.3               |

| Flatpack            | 3.3         | 3.5    | 3.3         | 3.5         | 3.6         | 3.7         | 3.8         | 3.9         | 3.9         | 3.6               |

| Ceramic             | 3.1         | 3.3    | 3.2         | 3.3         | 3.4         | 3.5         | 3.6         | 3.7         | 3.7         | 35                |

| Side Brazed         | 0.2         | 0.2    | 0.2         | 0.2         | 0.2         | 0.2         | 0.2         | 0.2         | 0.2         | 0.2               |

| Chip Carrier        | 1.6         | 1.8    | 1.7         | 1.8         | 1.8         | 1.9         | 1.9         | 1.9         | 2.0         | 1.8               |

| Plastic             | 0.7         | 0.8    | 0.7         | 8.0         | 8.0         | 0.8         | 0.9         | 0.9         | 0.9         | 0.8               |

| Ceramic             | 0.9         | 1.0    | 0.9         | 1.0         | 1.0         | 1.0         | 1.0         | 1.1         | 1.1         | 1.0               |

| SO                  | 156.5       | 169.2  | 159.6       | 169.0       | 173.1       | 178.5       | 183.2       | 186.7       | 187.6       | 174.6             |

| lipolar             | 862.0       | 827.1  | 728.7       | 699.9       | 719.6       | 723.7       | 731.2       | 762.0       | 775.8       | <del>7</del> 89.2 |

| DIP                 | 250.0       | 239.9  | 211.3       | 203.0       | 174.1       | 126.6       | 124.3       | 129.5       | 128.0       | 124.7             |

| Plastic             | 125.0       | 119.9  | 105.7       | 101.5       | 87.1        | 63.3        | 62.2        | 64.8        | 64.0        | 62.3              |

| Ceramic             | 100.0       | 95,9   | 84.5        | 81.2        | 69.7        | 50.7        | 49.7        | 51.8        | 51.2        | 49.9              |

| Side Brazed         | 25.0        | 24.0   | 21.1        | 20.3        | 17.4        | 12.7        | 12.4        | 13.0        | 12.8        | 12.5              |

| Flatpack            | 43.1        | 41.4   | 36.4        | 35.0        | 34.5        | 32.6        | 32.2        | 32.0        | 31.0        | 27.6              |

| Ceramic             | 38.8        | 37.2   | 32.8        | 31.5        | 31.1        | 29.0        | 28.8        | 28.8        | 27.9        | 24.9              |

| Side Brazed         | 4.3         | 4.1    | 3.6         | 3.5         | 3.5         | 3.3         | 3.2         | 3.2         | 3.1         | 2.8               |

| Chip Carrier        | 8.6         | 8.3    | 7.3         | 7.0         | 7.2         | 7.2         | 7.3         | 7.6         | 7.8         | 7.9               |

| Plastic             | 3.0         | 2.9    | 2.6         | 2.4         | 2.5         | 2.5         | 2.6         | 2.7         | 2.7         | 2.8               |

| Ceramic             | 5.6         | 5.4    | 4.7         | 4.5         | 4.7         | 4.7         | 4.8         | 5.0         | 5.0         | 5.1               |

| SO                  | 560.3       | 537.6  | 473.7       | 454.9       | 503.7       | 557.2       | 567.4       | 592.8       | 609.0       | 629.0             |

Table 2.3.2. (cont.)

North America-Estimated Standard Logic Package Production

(Millions of Dollars)

|              | <u>1988</u> | <u>1989</u> | <u>1990</u> | <u>1991</u> | <u> 1992</u> | 1993  | <u> 1994</u> | <u>1995</u> | <u> 1996</u> | 2000         |

|--------------|-------------|-------------|-------------|-------------|--------------|-------|--------------|-------------|--------------|--------------|

| BICMOS       | 3.5         | 18.0        | 31.7        | 43.8        | 66.5         | 115.6 | 173.0        | 219.0       | 264.4        | 390.0        |

| DIP          | 0.1         | 0.2         | 0.3         | 0.4         | 0.7          | 0.6   | 0.3          | 0.2         | 0.0          | 0.0          |

| Plastic      | 0.1         | 0.2         | 0.3         | 0.4         | 0.7          | 0.6   | 0.3          | 0.2         | 0.0          | 0.0          |

| Ceramic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Side Brazed  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Flatpack     | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Ceramic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Side Brazed  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Chip Carrier | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Plastic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Ceramic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| so           | 3.4         | 17.8        | 31.1        | 42.9        | 65.2         | 113.3 | 169.5        | 214.6       | 259.1        | 382.2        |

| QUAD/SQFP    | 0.0         | 0.0         | 0.3         | 0.4         | 0.7          | 1.7   | 3.1          | 4.2         | 5.3          | 7.8          |

| GaAs         | 6.0         | 8.3         | 12.3        | 19.5        | 25.5         | 32.8  | 39.6         | 52.8        | 72.0         | 195.0        |

| DIP          | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Plastic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Ceramic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Side Brazed  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Flatpack     | 0.1         | 0.1         | 0.1         | 0.2         | 0.3          | 0.3   | 0.4          | 0.5         | 0.7          | 2.0          |

| Ceramic      | 0.1         | 0.1         | 0.1         | 0.2         | 0.3          | 0.3   | 0.4          | 0.5         | 0.7          | 2.0          |

| Side Brazed  | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |

| Chip Carrier | 5.9         | 8.2         | 12.2        | 19.3        | 25.2         | 32.5  | 39.2         | 52.3        | 71.3         | 193.1        |

| Plastic      | 0.0         | 0.0         | 0.0         | 0.0         | 0.0          | 0.0   | 0.0          | 0.0         | 0.0          | 0.0          |