## **Focus Conference**

# The Productivity Age: Design Alternatives Become Solutions

Sponsored by the CAD/CAM Industry Service

December 9 and 10, 1985 Hyatt Palo Alto Palo Alto, California

1290 Ridder Park Drive San Jose, California 95131-2398 (408) 971-9000 Telex: 171973 Fax: (408) 971-9003

#### Sales/Service offices:

#### UNITED KINGDOM

DATAQUEST UK Limited 144/146 New Bond Street London WIY 9FD United Kingdom (0!) 409-1427 Telex: 266195

FRANCE

DATAQUEST SARL

41, rue Ybry

92522 Neuilly-sur-Seine Cedex

France

(01) 758-1240

Telex: 630842

**GERMANY**

DATAQUEST GmbH Rosenkavalierplatz 17 D-8000 Munich 81 West Germany (089) 91-1064 Telex: 5218070 Fax: (089) 91-2189

#### **JAPAN**

DATAQUEST Japan, Ltd. Azabu Heights, Suite 711 1-5-10, Roppongi, Minato-ku Tokyo 106, Japan (03) 582-1441 Telex: J32768 Fax: (03) 582-7323

The content of this report represents our interpretation and analysis of information generally available to the public or released by responsible individuals in the subject companies, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients.

This information is not furnished in connection with a sale or offer to sell securities, or in connection with the solicitation of an offer to buy securities. This firm and its parent and/or their officers, stockholders, or members of their families may, from time to time, have a long or short position in the securities mentioned and may sell or buy such securities.

Printed in the United States of America. All rights reserved. No part of this publication may be reproduced, stored in retrieval systems, or transmitted, in any form or by any means—mechanical, electronic, photocopying, duplicating, microfilming, videotape, or otherwise—without the prior written permission of the publisher.

## 1985 CAD/CAM INDUSTRY FOCUS CONFERENCE

#### December 9 and 10, 1985 The Hyatt Palo Alto Palo Alto, California

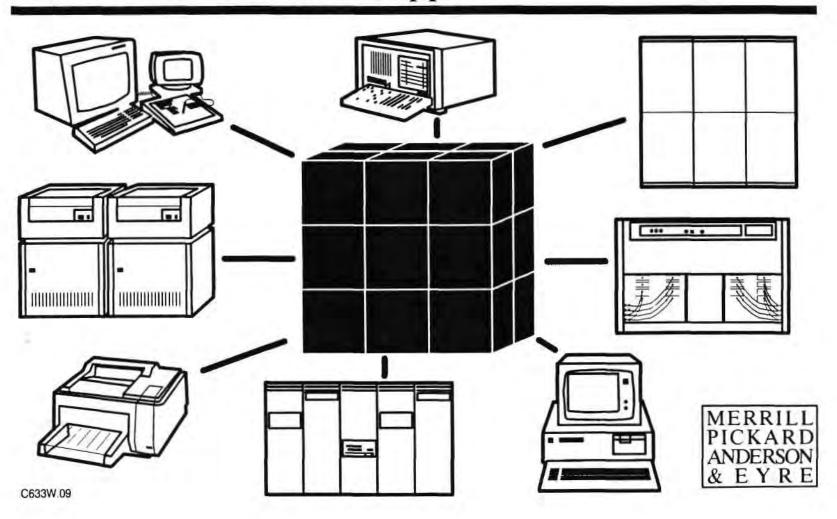

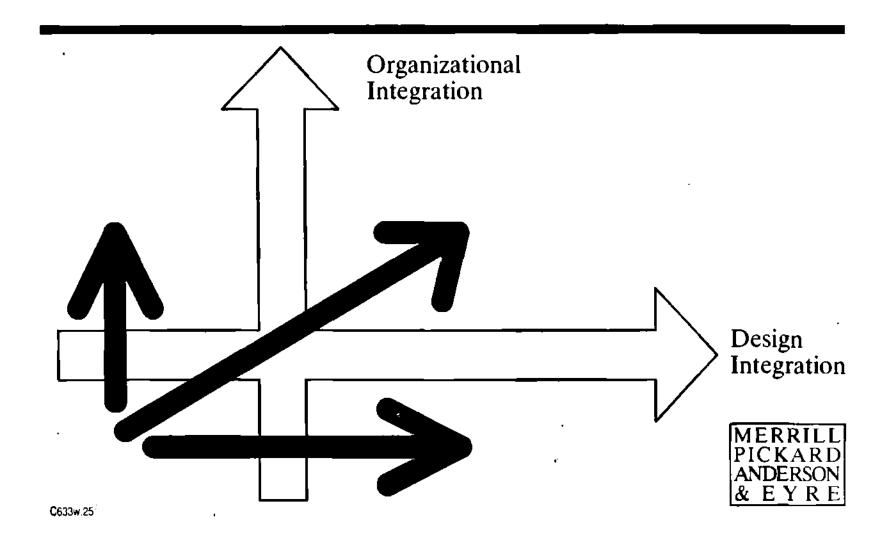

#### MONDAY, December 9 7:30 a.m. to 8:30 a.m. 8:30 a.m. Jim Newcomb Vice President and Group Director Industrial Automation Group Dataquest Incorporated 8:45 a.m. Beth Tucker Senior Industry Analyst **CAD/CAM Industry Service** Dataquest Incorporated 9:30 a.m. Tony Spadarella Research Analyst **CAD/CAM Industry Service** Dataquest Incorporated 10:15 a.m. 10:45 a.m. Kelly Leininger Research Assistant CAD/CAM Industry Service Dataquest Incorporated 11:30 a.m. Sheridan Tateuno Industry Analyst Japanese Semiconductor Industry Service Dataquest Incorporated 12:15 p.m. 1:30 p.m. Terry Zimmerman Vice President, Marketing FutureNet Corporation 2:15 p.m. Peter Whyte Vice President, Strategic Planning E-CAD, Inc. 3:00 p.m. Coffee Break ...... Redwood Foyer 3:15 p.m. John Newkirk Chief Executive Officer Silicon Solutions Corporation 4:00 p.m. Jeff Hotchkiss General Manager Teradyne, Inc. 4:45 p.m. Steven Coit Partner Merrill, Pickard, Anderson, & Eyre 5:30 p.m. to 7:00 p.m.

## TUESDAY, December 10

| 8:30 a.m.  | The PCB Connection                                                                                               |

|------------|------------------------------------------------------------------------------------------------------------------|

| 9:15 a.m.  | Developing an Open Network for IC Design                                                                         |

| 10:00 a.m. | Coffee Break                                                                                                     |

| 10:30 a.m. | User Interfaces Impact Productivity                                                                              |

| 11:15 a.m. | Where are MPUs Going?                                                                                            |

| 12:00 Noon | Lunch                                                                                                            |

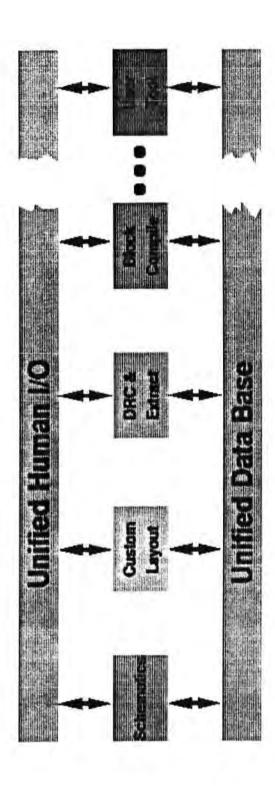

| 1:30 p.m.  | Unified Design—is it for Real?                                                                                   |

| 2:15 p.m.  | ASIC, USIC, or CSIC?                                                                                             |

| 3:00 p.m.  | Coffee Break                                                                                                     |

| 3:15 p.m.  | The Impact of Silicon Compilers on Productivity                                                                  |

| 4:00 p.m.  | The Global Productivity Imperative                                                                               |

| 4:45 p.m.  | Conference Wrap-up Redwood i Beth Tucker Senior Industry Analyst CAD/CAM Industry Service Dataquest Incorporated |

## CAD/CAM INDUSTRY FOCUS CONFERENCE EVALUATION QUESTIONNAIRE

Palo Alto, California December 9-10, 1985

Thank you for attending our CAD/CAM Industry Focus Conference. Would you please assist us in planning our next conference by completing and returning this questionnaire?

1. Please rate each presentation on a scale of 1 to 10 (where 10 is highest in terms of your approval):

|    |                                                    | CONTENT   | DELIVERY   | COMMENTS                        |          |

|----|----------------------------------------------------|-----------|------------|---------------------------------|----------|

|    |                                                    | (1 to 10) | (1 to 10)  | (Use reverse side if necessary) |          |

|    | Tucker, Measuring the Intengibles                  |           |            |                                 |          |

|    | Spadarella, Automatic IC Generation                |           |            | <u> </u>                        | •        |

|    | Leininger, Design Center Survey                    |           |            |                                 | •        |

|    | Tetsuno, Japanese Technology: The Future           |           |            |                                 |          |

|    | Zimmerman, PCs: How Much Can They Really Do        | ?         |            |                                 |          |

|    | Whyte, Software: The Real IC Designer              |           |            |                                 | ,        |

|    | Newfdrk, Fitting in Application Accelerators       |           |            |                                 |          |

|    | Hotchkiss, Linking Design and Test                 | 12        | 10         | TIZEMENDOUS CAPTELTS            | PERIVERS |

|    | Colt, The Golden Egg                               |           | <u>.</u>   |                                 | •        |

|    | Feltman, The PCB Connection                        |           |            |                                 |          |

|    | Bourbon, Developing Open Network for IC Design     |           |            |                                 | ,        |

|    | Balley, User Interfaces Impact Productivity        |           |            |                                 |          |

|    | Thomsen, Where are MPUs Going?                     |           |            |                                 |          |

|    | Solomon, Unified Design—Is it for Reat?            |           |            |                                 |          |

|    | Feirbairn, ASIC, USIC, or CSIC?                    |           |            |                                 |          |

|    | Kuenster, Silicon Compilers/Productivity           |           |            |                                 |          |

|    | Finegold, Global Productivity Imperative           |           |            |                                 | 1        |

| 2. | Overall meeting rating (1 to 10):                  |           |            |                                 |          |

| 3. | How would you rate the conference facilities (1    | to 10)?   |            |                                 |          |

|    | Location Guest Rooms Meat                          | s         | Meeting R  | ooms                            |          |

| 4. | Topics that would be of interest to you for future | 9 CAD/CAI | M Industry | Focus Conferences:              |          |

|    |                                                    | <u> </u>  |            |                                 |          |

|    |                                                    |           |            |                                 |          |

(OVBI)

|            |                |                |               |                | <u> </u> |  |

|------------|----------------|----------------|---------------|----------------|----------|--|

| <u></u>    |                |                | Industry Con- | - Castanasa i  |          |  |

| e. Your pr | imary interest | in the CAD/CAM | industry Focu | 8 Comerence II | 3 as a:  |  |

## **Dataquest**

#### CAD/CAM INDUSTRY SERVICE FOCUS CONFERENCE December 9 through 10, 1985 Palo Alto, California

#### List of Attendees

AWI Surface Mount Technology Ed Bingle, Design Supervisor

Advanced Micro Devices, Inc.

J. Phillip Downing, Vice President,

Corporate Technology

Alpha Partners Brian Grossi, General Partner

Apollo Computer, Inc. Raymond McCann, Market Manager, ECAD

Applied Micro Circuits Corporation Bernie Rosenthal, CAD Marketing Manager

Array Technology

Bill O'Neil, Vice President,

Engineering

Arthur Young & Company Angelo Danna, Partner Mark Nexsen, Principal

Bank of America

Don Cvietusa, Vice President

Alan Jepsen, Corporate Banking

Officer

Sally Otton, Assistant Vice President

Bank of Boston William Parker, Banking Officer

Bitstream, Inc. Ann Roe-Hafer, Director, Marketing

Burr, Egan, Deleage & Company Thomas Winter, Partner

CADAM, Inc. Rhonda Lindsey, CAD/CAM Market

Industry Analyst

CAD/CAM Specialists, Inc. Deniel DeWitt, Psychologist

Organizational Development

Daniel Garms, Executive Vice President

Michael McDonald, President

Cadcor Company David Jewell, Vice President,

Operations

Cadnetix Corporation Buck Feltman, Vice President, Marketing

California Devices, Inc. James Tobias, Vice President

Design Technology

Cambridge Electronic Industries David Cutts, Strategic Planner

Cericor, Inc. David Bailey, President & Chief

Executive Officer

Cirrus Logic, Inc. Suhas Patil, Vice President,

Research & Development

Citicorp Industrial Credit

Mano Appapillai, Vice President

Daisy Systems Corporation

Aryeh Finegold, President

Data General Corporation

Boli Medappa, Competitive Consultant Uday Watwe, Product Manager

Dataquest Incorporated

Irene Barth, Conference Assistant Greg Chagaris, Industrial Marketing Manager Ralph Dickman, Industrial Marketing Manager Kathy Hurley, Research Analyst John Jackson, National Sales Manager Debra Jacob, Conference Assistant Kelly Leininger, Research Assistant Eileen Barth-Lynch, Research Analyst James Newcomb, Vice President & Group Director, CAD/CAM Industry Service Jewel Peyton, Director, Corporate Communications Don Roberts, Manager, Training & Development Tony Spadarella, Research Analyst Lynn Stern, Conference Coordinator Sheridan Tatsuno, Industry Analyst Japanese Semiconductor Industry Mel Thomsen, Associate Director, Semiconductor Industry Service Beth Tucker, Senior Industry Analyst Paul van Dillen, Industrial

Marketing Manager

Digital Equipment Corporation Fanjeev Aggarwal, CAD Strategic Marketing Specialist Bill Goerke, Senior Vice President, E-CAD, Inc. Marketing & Sales Robert Lorentzen, Product Manager Peter Whyte, Vice President, Strategic Planning Edge Computer Corporation Douglas Crawford, Western Regional Manager Engineering Systems Products William Fabel, Program Manager Exar Corporation Yukio Nishikawa, Director, Engineering Ferranti Interdesign Inc. John Doyle, CAD Manager Ford Aerospace & Communications Clayton Showen, Manager Equipment & Corporation Engineering FutureNet Corporation Terry Zimmerman, Vice President, Marketing Development GE Venture Capital Eric Young, Vice President

Russel Craig, Vice President,

Strategic Planning

GenRad, Inc.

General Electric Company

Claire Heiss, Manager, Manufacturing

Gould AMI Semiconductors

Bruce Bourbon, Vice President, Marketing

Grace Ventures Corporation

Susan Woods, Assistant Vice President

Grove Hill Industries, Inc.

Barry Soloway, President & Chief Executive Officer

Hewlett-Packard Company

Gene Barduson, Manager, Marketing Division Curt Dowdy, Product Manager Brad Miller, Marketing Manager John Moss, Marketing Manager Robert Santos, Product Marketing Manager Nick Shain, Application Engineer Jim Stroh, Product Marketing Manager Mark Tolliver, Marketing Manager, Design Systems Group

Hillman Ventures, Inc.

Howard Geiger, Jr., Vice President

IBM Corporatiion

Frank Magistro Christina Schott, Marketing Manager, EDA

ICD Austria

Hubert Gammer, Director Monika Pacher, Director IKOS Systems, Inc.

William Loesch, President

Ing. C. Olivetti & C., S.p.A.

Ugo De Riu, Distributed Data Processing Division Manager Carlo Ronca, Distributed Data Processing Director

Institutional Venture Partners

Mary Jane Elmore, General Partner

Intergraph Corporation

Dennis Addidgo, District Sales Manager

Integrated Logic Systems, Inc.

Jeffrey Jacobsen, Vice President, Marketing & Sales

Intel Corporation

Doug Finke, Marketing Engineer

Intersil, Inc.

Charles Shaw, Director, Computer Aided Design

InterWest Partners

Flip Gianos, General Partner

J.H. Whitney & Company

William Harding, Associate John Larson, Partner

Los Alamos National Laboratories

Bob Morrison, Staff Member

| Mayfield Fund                     | A. Grant Heidrich, General Partner<br>Michael Levinthal, General Partner<br>F. Gibson Myers, General Partner<br>William Unger, Partner |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| McDonnell Douglas, ISG            | Mike Landers, Manager, Marketing<br>Research<br>William White, Product Marketing                                                       |

| Mead Imaging                      | Charles Sharp, Director Printer Product Planning                                                                                       |

| Mentor Graphics Corporation       | Dick Kaiser, Product Manager                                                                                                           |

| Merrill, Pickard, Anderson & Eyre | Stephen Coit, General Partner                                                                                                          |

| Mini Micro Magazine               | Arlette Gaulene                                                                                                                        |

| Monolithic Memories, Inc.         | H.T. Chua. Vice President<br>Carl Hudson, Engineering Support Manager                                                                  |

| NEC Corporation                   | Takayuki Yanagawa, General Manager                                                                                                     |

| Oak Investment Partners           | Jeffrey West, General Partner                                                                                                          |

| Priam Corporation                 | Albert Hartman, Manager, MCAD/CAE                                                                                                      |

R&D Funding Corporation Irv Weiman, Vice President

| Racal-Redac, Inc.                  | Jeil Allison, CAL marketing Group                                   |

|------------------------------------|---------------------------------------------------------------------|

| Ridge Computers                    | Mike Harrigan, Product Marketing                                    |

| Rockwell International Corporation | William Pearce, Director, CAD<br>Development, Advanced Engineering  |

| SDA Systems, Inc.                  | James Solomon, President                                            |

| SGS Semiconductor Corporation      | Giancarlo Ronzi, Director, Design                                   |

| Scientific Calculations, Inc.      | Michael Davin, Director,<br>International & North American<br>Sales |

| Seattle Silicon Technology, Inc.   | Gordon Kuenster, President<br>Diane Kuenster                        |

| Seeq Technology, Inc.              | Larry Bullard, Manager CAD & Tooling                                |

| Siemens Data Systems               | Wolfgang Gnettner, Manager, Product Planning                        |

| Sierra Semiconductor Corporation   | Lawrence Goldstein, Director<br>Design Automation                   |

| Silicon Design Labs, Inc.          | James Hammock, Chief Operating Officer                              |

Racal-Redac, Inc.

Jeff Allison, CAE Marketing Group

David Reiser, Director, Marketing

John Newkirk, Chief Executive Officer Silicon Solutions Corporation Frank Lynch, Director, Marketing Silvar-Lisco Tom Blank, Director, CAD Stanford University Roberta Gray, Market Segment Sun Microsystems, Inc. Manager Doug Bering, Development Engineering Tandem Computers, Inc. Manager Tektronix, CAE Systems Division Robert Harrison, Product Marketing Manager Kelly Rupp, Product Marketing Manager Steve Sapiro, Chief Scientist Telesis Systems Corporation Robert Fulks, Consultant Douglas Hajjar, President & Chief Executive Officer Teradyne, Inc. Jeff Hotchkiss, General Manager

Robert Geissberger, President

Mike Thomas, Partner

The Photo-Tech Company

Thomas Group, Inc.

Union Bank

Dirk Geiger, Loan Officer

Valley Data Sciences

Keith Barnes, Director, Marketing Robert Soto, President

VLSI Technology, Inc.

Douglas Fairbairn, Vice President

Weitek Corporation

Scott Lewis, Director, Strategic Development John Rizzo, Director, Marketing

Xilinix, Inc.

David Lautzenheiser, Director Technical Marketing Kathie Priebe, Director, Software Development

Zycad Corporation

Dave Allenbaugh, Product Marketing Manager Dick Ebert, Director, Marketing John Fahlberg, Senior Vice President, Operations

## **Dataquest**

#### CAD/CAM INDUSTRY SERVICE FOCUS CONFERENCE December 9 through 10, 1985 Palo Alto, California

#### List of Attendees

Dennis Addidgo Intergraph Corporation

Fanjeev Aggarwal Digital Equipment Corporation

Dave Allenbaugh Zycad Corporation

Jeff Allison Racal-Redac, Inc.

Mano Appapillai Citicorp Industrial Credit

David Bailey Cericor, Inc.

Gene Barduson Hewlett-Packard Company

Keith Barnes Valley Data Sciences

Irene Barth Dataquest Incorporated

Doug Bering Tandem Computers, Inc.

Ed Bingle AWI Surface Mount Technology

Tom Blank Stanford University

Bruce Bourbon Gould AMI Semiconductors

Larry Bullard Seeq Technology, Inc.

Greg Chagaris Dataquest Incorporated

H.T. Chua Monolithic Memories, Inc.

Stephen Coit Merrill, Pickard, Anderson & Eyre

Russel Craig GenRad, Inc.

Douglas Crawford Edge Computer Corporation

David Cutts Cambridge Electronic Industries

Don Cvietusa Bank of America

|  | Ange | l٥ | Danna |

|--|------|----|-------|

|--|------|----|-------|

Michael Davin

Ugo De Riu

Daniel DeWitt

Ralph Dickman

Curt Dowdy

J. Phillip Downing

John Doyle

Dick Ebert

Mary Jane Elmore

William Fabel

John Fahlberg

Douglas Fairbairn

Buck Feltman

Arych Finegold

Doug Finke

Robert Fulks

Hubert Gammer

Daniel Garms

Arlette Gaulene

Dirk Geiger

Howard Geiger, Jr.

Robert Geissberger

Flip Gianos

Wolfgang Gnettner

Arthur Young & Company

Scientific Calculations, Inc.

Ing. C. Olivetti & C., S.p.A.

CAD/CAM Specialists, Inc.

Dataquest Incorporated

Hewlett-Packard Company

Advanced Micro Devices, Inc.

Ferranti interdesign Inc.

Zycad Corporation

Institutional Venture Partners

Engineering Systems Products

Zycad Corporation

VLSI Technology, Inc.

Cadnetix Corporation

Daisy Systems Corporation

Intel Corporation

Telesis Systems Corporation

ICD Austria

CAD/CAM Specialists, Inc.

Mini Micro Magazine

Union Bank

Hillman Ventures, Inc.

The Photo-Tech Company

InterWest Partners

Siemens Data Systems

Bill Goerke

Lawrence Goldstein

Roberta Gray

Brian Grossi

Ann Roe-Hafer

Douglas Hajjar

James Hammock

William Harding

Mike Harrigan

Robert Harrison

Albert Hartman

A. Grant Heidrich

Claire Heiss

Jeff Hotchkiss

Carl Hudson

Kathy Hurley

John Jackson

Debra Jacob

Jeffréy Jacobsen

Alan Jepsen

David Jewell

Dick Kaiser

Gordon Kuenster Diane Kuenster

Mike Landers

John Larson

E-CAD, Inc.

Sierra Semiconductor Corporation

Sun Microsystems, Inc.

Alpha Partners

Bitstream, Inc.

Telesis Systems Corporation

Silicon Design Labs, Inc.

J.H. Whitney & Company

Ridge Computers

Tektronix, CAE Systems Division

Priam Corporation

Mayfield Fund

General Electric Company

Teradyne, Inc.

Monolithic Memories, Inc.

Dataquest Incorporated

Dataquest Incorporated

Dataquest Incorporated

Integrated Logic Systems, Inc.

Bank of America

Cadcor Company

Mentor Graphics Corporation

Seettle Silicon Technology, Inc.

McDonnell Douglas, ISG

J.H. Whitney & Company

David Lautzenheiser

Kelly Leininger

Michael J. Levinthal

Scott Lewis

Rhonda Lindsey

William Loesch

Robert Lorentzen

Eileen Barth-Lynch

Frank Lynch

Frank Magistro

Raymond McCann

Michael McDonald

Boli Medappa

Brad Miller

Bob Morrison

John Moss

F. Gibson Myers

James Newcomb

John Newkirk

Mark Nexsen

Yukio Nishikawa

Bill O'Neil

Sally Otton

Monika Pacher

William Parker

Xilinix, Inc.

Dataquest Incorporated

Mayfield Fund

Weitek Corporation

CADAM, Inc.

IKOS Systems, Inc.

E-CAD, Inc.

Dataquest Incorporated

Silvar-Lisco

IBM Corporation

Apollo Computer, Inc.

CAD/CAM Specialists, Inc.

Data General Corporation

Hewlett-Packard Company

Los Alamos National Laboratories

Hewlett-Packard Company

Mayfield Fund

Dataquest Incorporated

Silicon Solutions Corporation

Arthur Young & Company

Exar Corporation

Array Technology

Bank of America

ICD Austria

Bank of Boston

Cirrus Logic, Inc. Subas Patil William Pearce Rockwell International Corporation Jewel Peyton Dataquest Incorporated Xilinix, Inc. Kathie Priebe Silicon Design Labs, Inc. David Reiser Weitek Corporation John Rizzo Don Roberts Dataquest Incorporated Ing. C. Olivetti & C., S.p.a. Carlo Ronca Giancarlo Ronzi SGS Semiconductor Corporation Applied Micro Circuits Corporation Bernie Rosenthal Kelly Rupp Tektronix, CAE Systems Division Robert Santos Hewlett-Packard Company Tektronix, CAE Systems Division Steve Sapiro

Nick Shain Hewlett-Packard Company

Charles Sharp Mead Imaging

Charles Shaw Intersil, Inc.

Christina Schott

Clayton Showen Ford Aerospace & Communications

Corporation

IBM Corporation

James Solomon SDA Systems, Inc.

Barry Soloway Grove Hill Industries, Inc.

Robert Soto Valley Data Sciences

Tony Spadarella Dataquest Incorporated

Lynn Stern Dataquest Incorporated

Jim Stroh Hewlett-Packard Company

Sheridan Tatsuno Dataquest Incorporated

Mike Thomas

Mel Thomsen

James Tobias

Mark Tolliver

Beth Tucker

William Unger

Paul van Dillen

Uday Watwe

Irv Weiman

Jeffrey West

William White

Peter Whyte

Thomas Winter

Susan Woods

Takayuki Yanagawa

Eric Young

Terry Zimmerman

Thomas Group, Inc.

Dataquest Incorporated

California Devices, Inc.

Hewlett-Packard Company

Dataquest Incorporated

Mayfield Fund

Dataquest Incorporated

Data General Corporation

R&D Funding Corporation

Oak Investment Partners

McDonnell Douglas, ISG

E-CAD, Inc.

Burr, Egan, Deleage & Company

Grace Ventures Corporation

NEC Corporation

GE Venture Capital

FutureNet Corporation

WELCOME AND CONFERENCE INTRODUCTION

James R. Newcomb

Vice President and Group Director

Dataquest Incorporated

Mr. Newcomb is a Vice President of Dataquest and Group Director of the Industrial Automation Group, which encompasses the CAD/CAM Industry Service and the Robotics Industry Service. He is responsible for the group's strategic direction, overall planning, operations management, and the establishment of business platforms. Previously, he was employed at Auto-trol Technology Corporation, where he held various positions within the corporate marketing organization. Prior to that, he was employed in the Reprographic Manufacturing Group of Xerox Corporation, in positions involving strategic planning, systems integration, advanced manufacturing engineering, and program planning. Mr. Newcomb's professional experience has provided him with an in-depth knowledge of design and manufacturing automation technologies and markets involving CAD/CAM/CAE, EDA, robotics, artificial intelligence, and automation systems design implementation. Mr. Newcomb received a B.S.M.E. degree from Rochester Institute of Technology. He is a member of the Society of Manufacturing Engineers, Computer Automated Systems Association, Machine Vision, Robotics Industry Association, National Computer Graphics Association, and IEEE.

Dataquest Incorporated

DESIGN AUTOMATION FOCUS CONFERENCE

December 9 and 10, 1985

Palo Alto, California

## **Dataquest**

a company of The Dun & Bradstreet Corporation

**DUN & BRADSTREET**

A.C. NIELSEN COMPANY

DATAQUEST INCORPORATED

## MEMBERS OF DUN & BRADSTREET FAMILY OF INFORMATION COMPANIES

- DUN & BRADSTREET

- LARGEST BUSINESS INFORMATION SERVICE COMPANY IN THE WORLD

- 48,000 EMPLOYEES IN 25 COUNTRIES

- \$2.2 BILLION IN YEARLY REVENUES

# A.C. NIELSEN COMPANY DATAQUEST INCORPORATED

- DATAQUEST INCORPORATED

- SUBSIDIARY OF A.C. NIELSEN COMPANY SINCE 1978

- HIGH-TECHNOLOGY RESEARCH ARM OF A.C. NIELSEN COMPANY

- A.C. NIELSEN COMPANY

- WORLD'S LARGEST MARKET RESEARCH ORGANIZATION

- \$750 MILLION COMPANY--FOUNDED 1923

## CAD/CAM INDUSTRY SERVICE -- 1985

## THE INFORMATION PLATFORM

| MARKET           | TURN-<br>KEY | COMPUTERS     |  |               | PHI<br>RMI - | .  | PERI-<br>PHERAL | SOFTWARE/<br>SERVICES |

|------------------|--------------|---------------|--|---------------|--------------|----|-----------------|-----------------------|

| APPLI-<br>CATION | MECHA        | NICAL AEC     |  | РС            | 8            | IC | EDA             | MAPPING               |

| REGION           | NOF<br>AME   | ···· I FURC   |  | PE            | FAR EAST     |    | EAST            | REST OF<br>WORLD      |

| PRODUCT<br>TYPE  | PERSONAL STA |               |  | ANDALONE HOST |              |    | -DEPENDENT      |                       |

| PRICE            |              | 5 THAN<br>30K |  | \$30K-\$90K   |              |    |                 | MORE THAN<br>\$90K    |

SOURCE DATAQUEST

Dataquest

BB a company of The Dun & Bradstreet Corporation

MEASURING THE INTANGIBLES

Beth W. Tucker Senior Industry Analyst Dataquest Incorporated

Ms. Tucker is a Senior Industry Analyst for Dataquest's CAD/CAM Industry Service. She is responsible for the management of research activities involving all electronic CAD/CAM applications, including integrated circuits, printed circuit boards, and electronic design automation. In addition, she is responsible for managing the service's industry data base, survey activities, and consulting projects. Prior to joining Tucker was Manager of Market Dataquest, Ms. Planning in Microelectronics Division of Calma Company, a subsidiary of General Electric. In that capacity, she was responsibile for identifying market opportunities and strategies for the company's electronic CAD product She also contributed to the development of marketing programs at the corporate level. Earlier, she worked for Monroe Systems, where she was responsible for market research and development of small business computer products. Ms. Tucker received an A.A. degree in Computer Technology from Morris County College in New Jersey, and is doing course work at San Jose State University.

Dataquest Incorporated

DESIGN AUTOMATION FOCUS CONFERENCE

December 9 and 10, 1985

Palo Alto, California

## **AGENDA**

- REVISED FORECAST

- FOCUS RESEARCH GROUP HIGHLIGHTS

## FORECAST CHANGE

- 1985 ECONOMICS

- HOST-DEPENDENT IN DECLINE

- PERSONAL COMPUTER INCREASE

- FALLING ASPs

- SEMICONDUCTOR INDUSTRY

# DECLINING 30% THIS Y THE

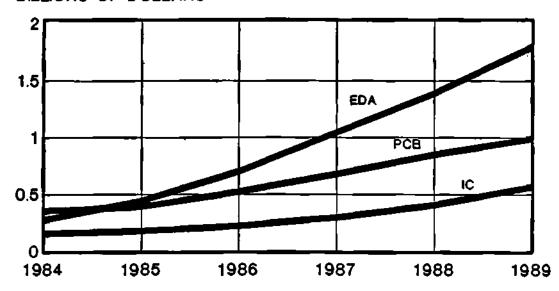

# ESTIMATED ELECTRONIC CAD/CAM MARKET BY APPLICATION

## **BILLIONS OF DOLLARS**

Source: DATAQUEST

## ESTIMATED ECAD MARKET (Millions of Dollars)

|       | 1984              | <u> 1985</u> | <u>1986</u> | 1987    | 1988    | <u>1989</u> | CAGR |

|-------|-------------------|--------------|-------------|---------|---------|-------------|------|

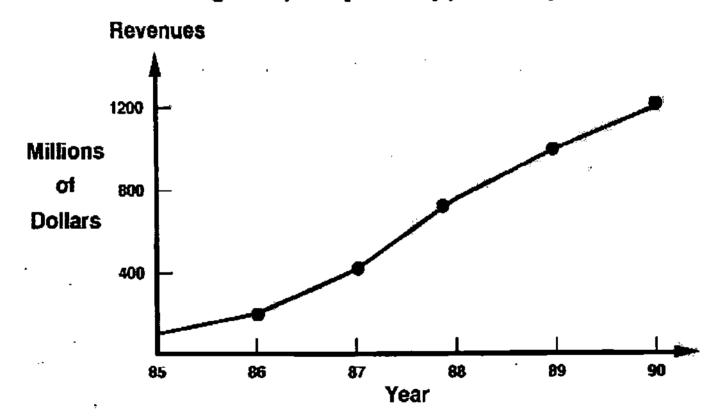

| EDA   | \$ 276            | \$ 442       | \$ 701      | \$1,042 | \$1,387 | \$1,798     | 31%  |

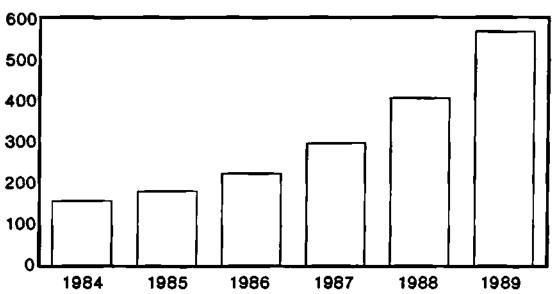

| IC    | 157               | 181          | 224         | 298     | 408     | 571         | 46%  |

| PCB   | 355               | 392          | 525         | 679     | 850     | 991         | 30%  |

| Total | \$ <del>788</del> | \$1,015      | \$1,450     | \$2,019 | \$2,645 | \$3,360     | 34%  |

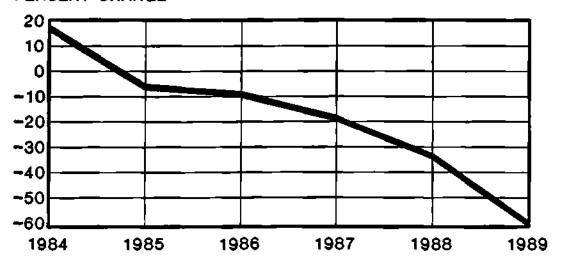

# ELECTRONIC CAD/CAM HOST-DEPENDENT PRODUCT TYPE

## PERCENT CHANGE

## HOST-DEPENDENT PORECAST (Revenue Percent Change)

|                | 1984 | 1985 | <u>1986</u> | <u>1987</u> | 1988 | 1989 |

|----------------|------|------|-------------|-------------|------|------|

| Percent Change | 17   | -,6  | -9          | -19         | -34  | -60  |

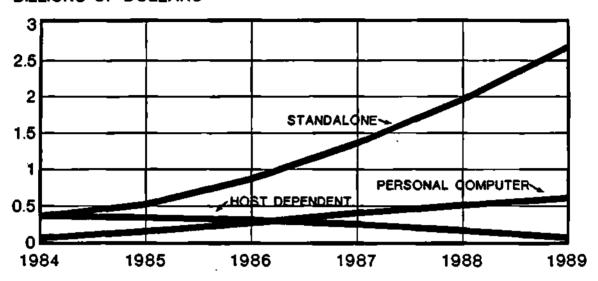

## ESTIMATED ELECTRONIC CAD/CAM MARKET BY PRODUCT TYPE

## **BILLIONS OF DOLLARS**

Source: DATAQUEST

#### ESTIMATED ECAD MARKET BY PRODUCT TYPE (Millions of Dollars)

|                   | <u>1984</u> | 1985    | <u>1986</u> | <u>1987</u> | 1988    | <u>1989</u> | CAGR |

|-------------------|-------------|---------|-------------|-------------|---------|-------------|------|

| Standalone        | \$ 361      | \$ 521  | \$ 873      | \$1,362     | \$1,963 | \$2,686     | 498  |

| Host-Dependent    | 364         | 342     | 310         | 252         | 168     | 67          | -29% |

| Personal Computer | 63          | 152     | <u>2</u> 67 | 405         | 514     | 607         | 57%  |

| Total             | \$ 788      | \$1.015 | \$1.450     | \$2.019     | \$2.645 | \$3.360     | 34 % |

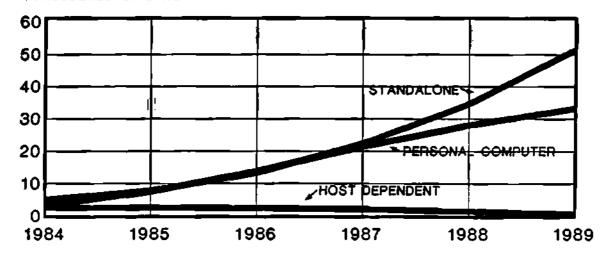

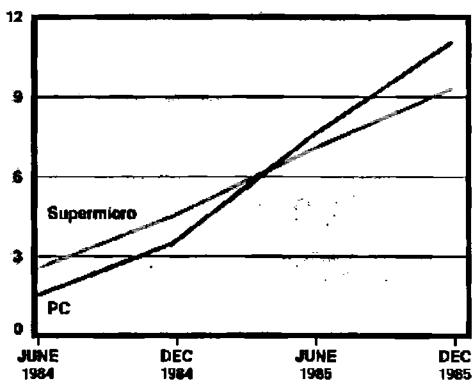

## ESTIMATED ELECTRONIC CAD/CAM MARKET BY PRODUCT TYPE

## WORKSTATION SHIPMENTS (Thousands of Units)

Source: DATAQUEST

#### ESTIMATED ECAD MARKET BY PRODUCT TYPE (Workstation Shipments)

|                   | <u>1984</u> | <u>1985</u> | <u>1986</u> | 1987   | 1988          | <u>1989</u>   | CAGR        |

|-------------------|-------------|-------------|-------------|--------|---------------|---------------|-------------|

| Standalone        | 5,073       | 7,813       |             | 22,251 |               | 51,443        | 59%         |

| Host-Dependent    | 2,553       | 2,517       | · ·         | 2,086  | , –           | 626           | ~25%        |

| Personal Computer |             |             |             |        | <u>28,112</u> | <u>33,282</u> | 60 <u>%</u> |

| Total             | 10,805      | 17,868      | 29,562      | 45,737 | 64,171        | 85,341        | 51%         |

#### "PEOPLE BUY TRUCKERS \$80,000 TRUCKS, YET THEY WON'T SPEND AS MUCH MONEY ON DESIGN AUTOMATION."

Source: Focus Group Participant

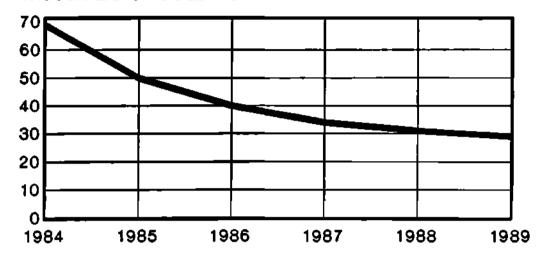

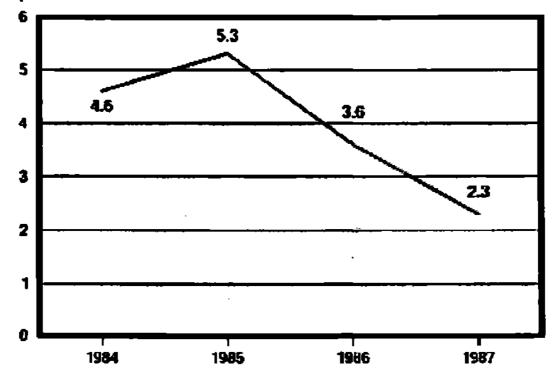

#### ELECTRONIC CAD/CAM ESTIMATED AVERAGE SYSTEMS SELLING PRICE

#### THOUSANDS OF DOLLARS

Source: DATAQUEST

#### ESTIMATED ECAD MARKET AVERAGE SELLING PRICE (Thousand of Dollars)

|     | <u>1984</u> | <u>1985</u> | <u>1986</u> | 1987        | 1988        | <u>1989</u> | CAGR |

|-----|-------------|-------------|-------------|-------------|-------------|-------------|------|

| ASP | \$ 69       | <b>£</b> 50 | \$ 40       | <b>4</b> 34 | <b>e</b> 31 | # 20        | _169 |

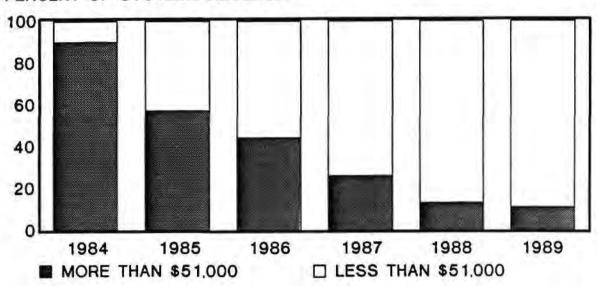

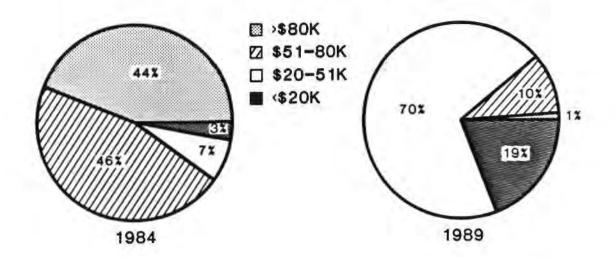

#### ESTIMATED ELECTRONIC CAD/CAM MARKET BY PRICE-PER-SEAT SEGMENTS

#### PERCENT OF SYSTEMS REVENUE

Source: DATAQUEST

#### ESTIMATED ECAD MARKET BY AVERAGE PRICE PER SEAT (Percent of Revenue)

| 199                   | 34 1 | 1985 1 | 986 1 | 987 1 | 988 1989 | 1 |

|-----------------------|------|--------|-------|-------|----------|---|

| Less Than \$51,000    | LO   | 43     | 56    | 74    | 87 89    |   |

| Greater Than \$51,000 | 90   | 57     | 44    | 26    | 13 11    |   |

#### ESTIMATED ELECTRONIC CAD/CAM MARKET BY PRICE-PER-SEAT SEGMENTS

#### PERCENT OF SYSTEMS REVENUE

Source: DATAQUEST

# ESTIMATED ECAD MARKET BY AVERAGE PRICE PER SEAT SEGMENT (Percent of Revenue)

| Price Per Seat        | 1984 | 1985 | 1986 | 1987 | 1988 | 1989 |

|-----------------------|------|------|------|------|------|------|

| Less Than \$20,000    | 3    | 15   | 21   | 23   | 21   | 19   |

| \$20,000-51,000       | 7    | 28   | 35   | 51   | 66   | 70   |

| \$51,000-80,000       | 46   | 39   | 32   | 19   | 10   | 10   |

| Greater Than \$80,000 | 44   | 18   | 12   | 7    | 3    | 1    |

#### FOCUS GROUP HIGHLIGHTS

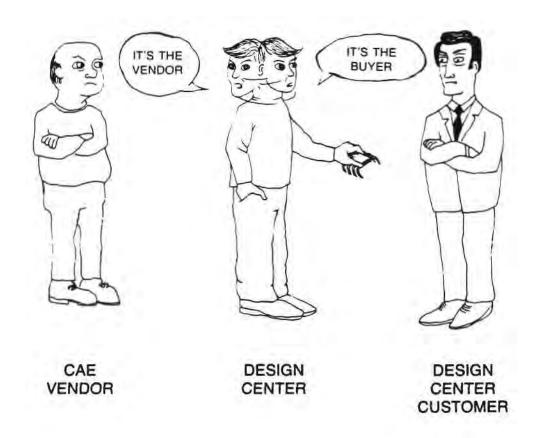

- VENDOR/CUSTOMER RELATIONSHIP

- CHANGING GROUND RULES

- CREATIVITY

- SERVICE AND SUPPORT

- GOALS OF PRODUCTIVE SYSTEMS

# "BECAUSE THE INDIVIDUAL VENDORS THAT ARE VERY STRONG IN ONE AREA MIGHT BE WEAK IN OTHERS, YOU CAN'T AFFORD TO GO WITH THEM ACROSS THE BOARD."

Source: Focus Group Participant

#### TUCKER'S CAD/CAM LAW

- THE CAD VENDOR/CUSTOMER

RELATIONSHIP IS NOT A MARRIAGE,

IT IS AN AFFAIR

- SOMETHING FLASHIER, FASTER, BETTER, AND CHEAPER WILL ALWAYS COME ALONG

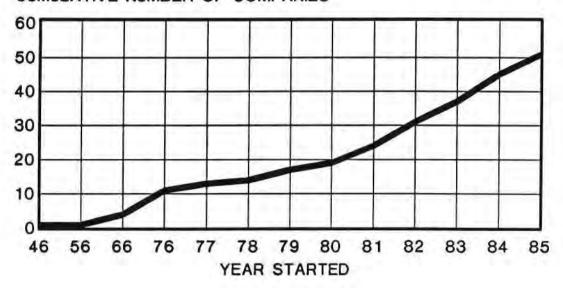

#### **ELECTRONIC CAD/CAM VENDORS**

Source: DATAQUEST

- 51 VENDORS NOW SELLING

ELECTRONIC APPLICATIONS

IN CADICAM

# "IF THE BIG GUYS WERE LAGGING, THEN THERE WOULD BE OPPORTUNITY, AND THE LITTLE GUYS WOULD SPRING UP AGAIN, AND THEY'D SATISFY THE DEMAND."

Source: Focus Group Participant

### **PRESENT**

**BIG GUYS**

'AVIS'

LITTLE GUYS

### **CHANGING GROUND RULES**

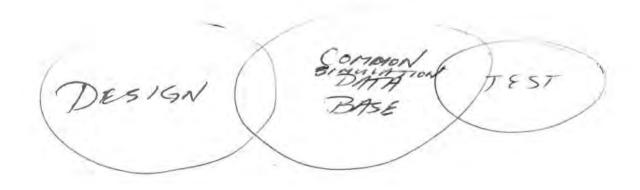

- DATA BASE

- INTEGRATION

- SUPPORT

- FUNCTIONALITY

- PERFORMANCE

- PRICE MUST BE A GIVEN

**PRESENT**

**FUTURE**

**BIG GUYS**

"AVIS"

LITTLE GUYS

LITTLE GUYS

**BIG GUYS**

"AVIS"

# "IT'S THE ART THAT'S VALUABLE, NOT THE MECHANICS."

Source: Focus Group Participant

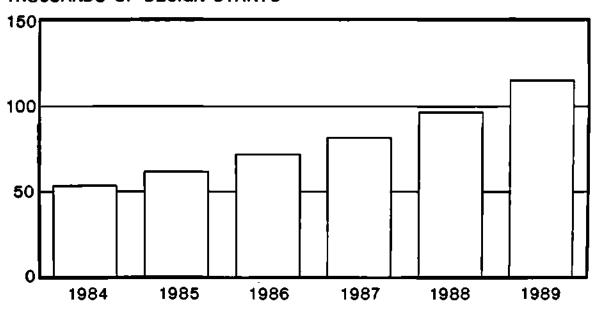

#### ESTIMATED ANNUAL IC DESIGN STARTS

THOUSANDS OF DESIGN STARTS

Source: DATAQUEST

# ESTIMATED ANNUAL IC DESIGN STARTS (Thousands of Designs)

|               | <u>1984</u> | <u>1985</u> | 1986 | 1987 | <u>1988</u> | 1989 | CAGR |

|---------------|-------------|-------------|------|------|-------------|------|------|

| Design Starts | 54          | 62          | 72   | 82   | 97          | 115  | 17%  |

# "IN OUR COMPANY, WE ARE NOT INTERESTED IN BEING CUSTOMER SUPPORT."

Source: Focus Group Participant

#### **ECAD SERVICE REVENUE**

### ESTIMATED ECAD SERVICE REVENUE (Millions of Dollars)

<u>1984</u> <u>1985</u> <u>1986</u> <u>1987</u> <u>1988</u> <u>1989</u> <u>CAGR</u> Service Revenue \$ 84 \$102 \$ 145 \$ 204 \$ 264 \$ 336 32\$

### PRODUCT JUSTIFICATION

- ROI

- DESIGNS PER ENGINEER

- COMPLEXITY

- TIME

- REWORKS

- SUCCESS RATIO

### PRODUCT JUSTIFICATION

- IS AN ITERATIVE PROCESS AND MUST COMPARE ACTUALS VERSUS ESTIMATES

- IS BASED ON COMMON SENSE

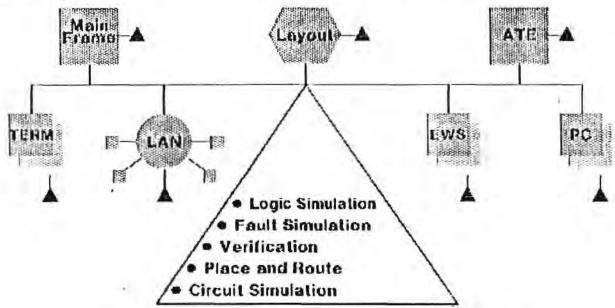

#### PRODUCTIVITY ISSUES

GOAL:

MEET DEADLINES

STRATEGY:

- INTEGRATION

- ACCELERATORS

- SIMULATORS

- PERSONAL COMPUTERS

#### PRODUCTIVITY ISSUES

GOAL:

MEET DEADLINES AND GET

IT RIGHT THE FIRST TIME

STRATEGY:

SIMULATION

• TEST GENERATION

CORRECT BY CONSTRUCTION

COMPILATION

DATA BASE MANAGEMENT AND CONTROL

#### **SUMMARY**

- CHANGING GROUND RULES

- LIVE WITH COMPETITION

- INCREASED AUTOMATION MEANS INCREASED SUPPORT

# "PRODUCTIVITY EQUALS DOLLARS"

Source: Focus Group Participant

PERPOR STABILITY,

THE FOCUS GROUP PERCENTIONS

WHERE DOES 17 PANK?

MBOVE OR BELOW

SYSTEM FUNCTIONARY

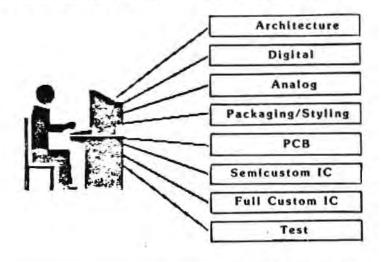

AUTOMATIC IC GENERATION

Tony Spadarella Research Analyst Dataquest Incorporated

Mr. Spadarella is a Research Analyst for Dataquest's CAD/CAM Industry Service. He is responsible for research and analysis of the integrated circuit, printed circuit board, and electronic design automation CAD/CAM segments. He also supports general research activities. Before coming to Dataquest Mr. Spadarella was on the technical staff of Calma Company's Research and Development division, documenting the company's electronic design products, operating systems, and communications products. He also researched automated technical publications systems. Prior to that, he was with Singer-Link's Advanced Products organization, where he designed visual data bases and analyzed training requirements for flight Mr. Spadarella received a B.A. degree in simulation applications. English from Georgetown University in Washington D.C. and an M.A. degree in English from the University of Southern California in Los Angeles. He has done additional post graduate studies in marketing and advertising at Golden Gate University in San Francisco. He also teaches courses in technical writing at San Jose State University.

Dataquest Incorporated

DESIGN AUTOMATION FOCUS CONFERENCE

December 9 and 10, 1985

Palo Alto, California

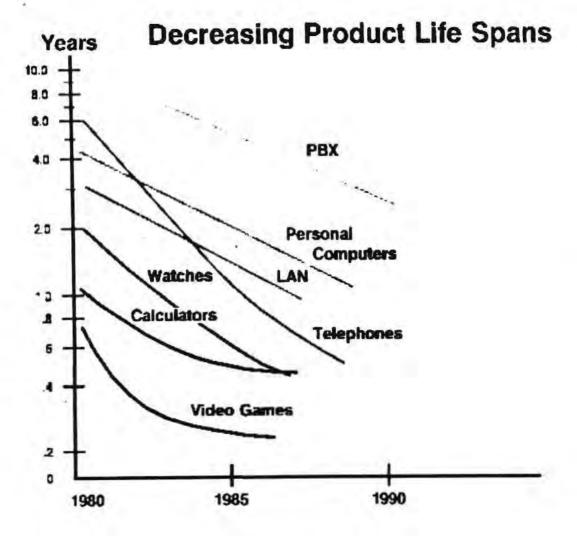

# PRODUCTIVITY = CHANGE

#### **CHANGES IN:**

- ICs

- IC DESIGN TOOLS

- IC DESIGN METHODOLOGY

### **AGENDA**

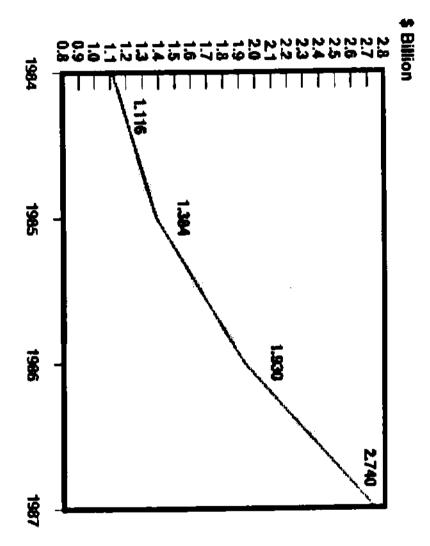

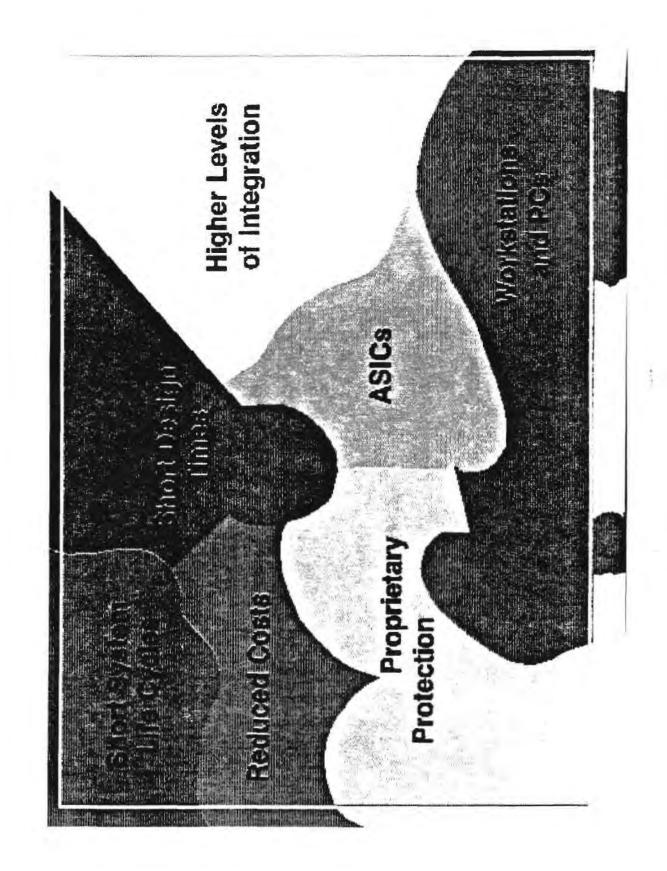

- ASIC MARKET

- AUTO IC LAYOUT

- IC CAD FORECAST

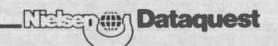

# **ASICs**

A PPLICATIONS PECIFIC

I NTEGRATED

CIRCUITS

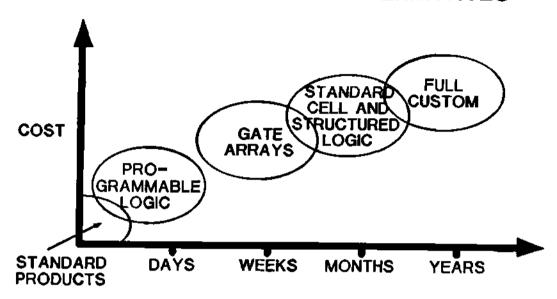

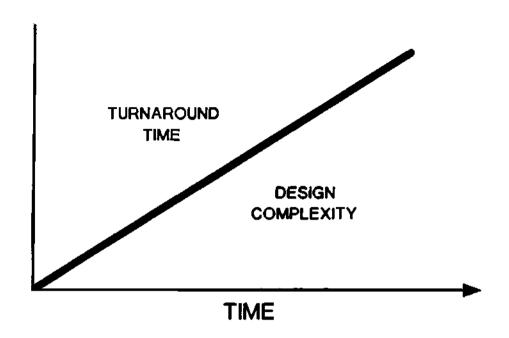

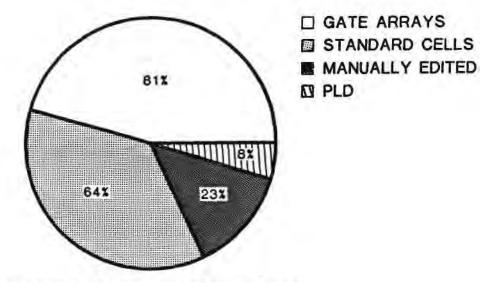

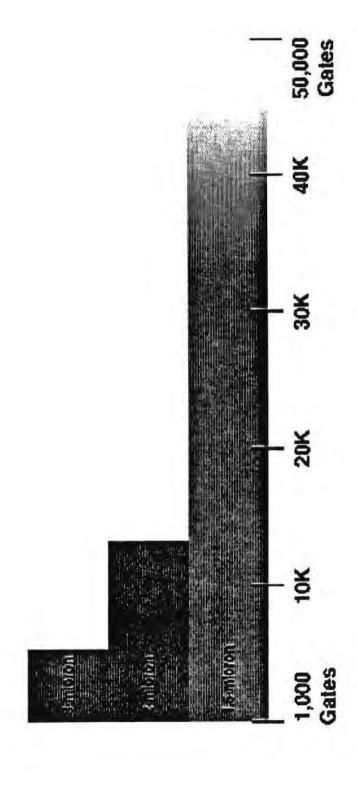

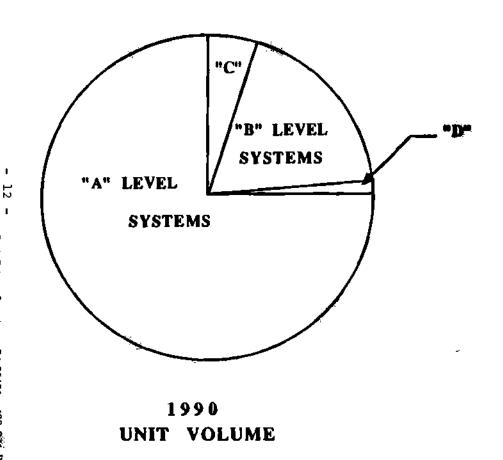

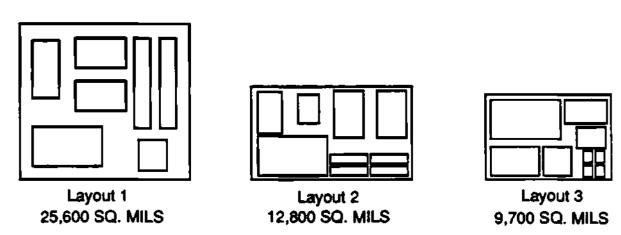

#### ASIC IMPLEMENTATION ALTERNATIVES

# **AVERAGE GATE COUNT**

1985

1987

2,500 - 4,000 8,000 - 13,000

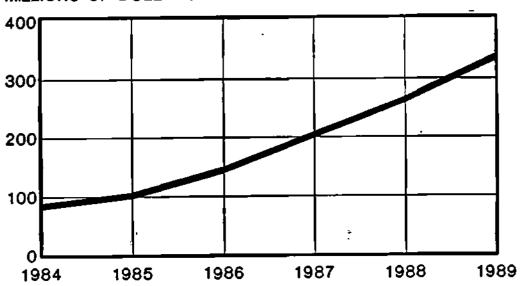

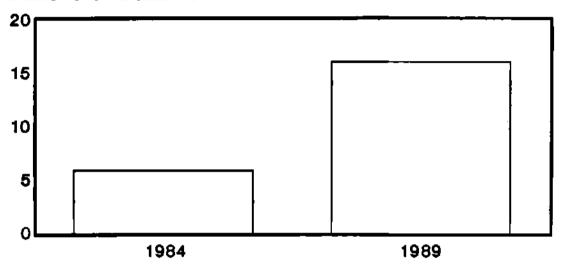

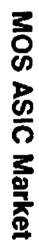

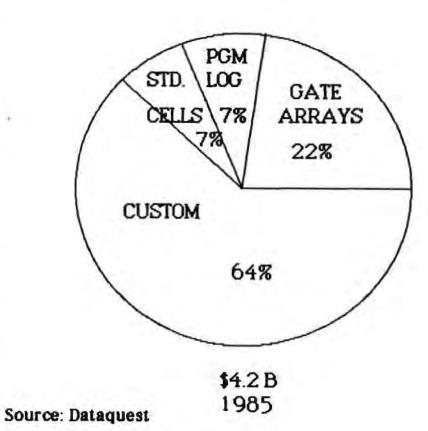

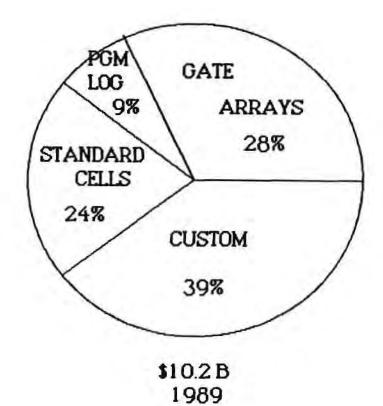

# ESTIMATED TOTAL WORLDWIDE ASIC MARKET

#### **BILLIONS OF DOLLARS**

Source: DATAQUEST

### TOTAL WORLDWIDE ASIC MARKET (Billions of Dollars)

|      | 1984         | 1989   | CAGR |  |

|------|--------------|--------|------|--|

| ASIC | <b>\$5.9</b> | \$16.1 | 22%  |  |

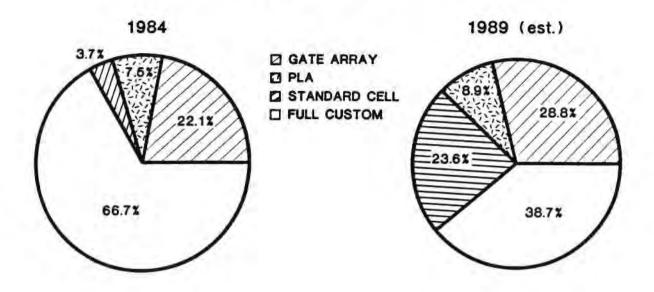

#### ASIC MARKET

Source: DATAQUEST

### ASIC MARKET (Millions of Dollars)

|               | 1984    | 1989     | CAGR  |

|---------------|---------|----------|-------|

| PLA           | \$251.0 | \$ 910.5 | 29.48 |

| Gate Array    | 737.6   | 2932.7   | 31.8% |

| Standard Cell | 122.9   | 2401.9   | 81.2% |

| Full Custom   | 2230.9  | 3950.0   | 12.1% |

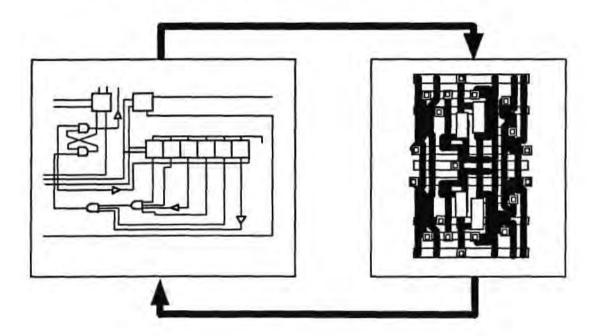

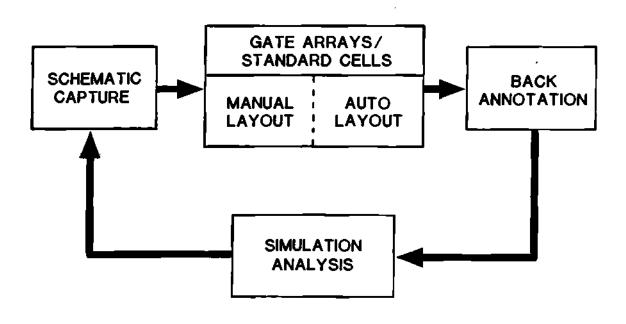

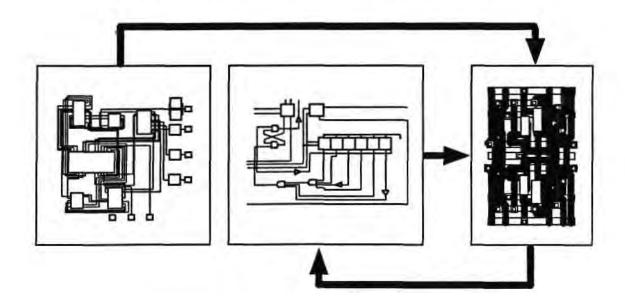

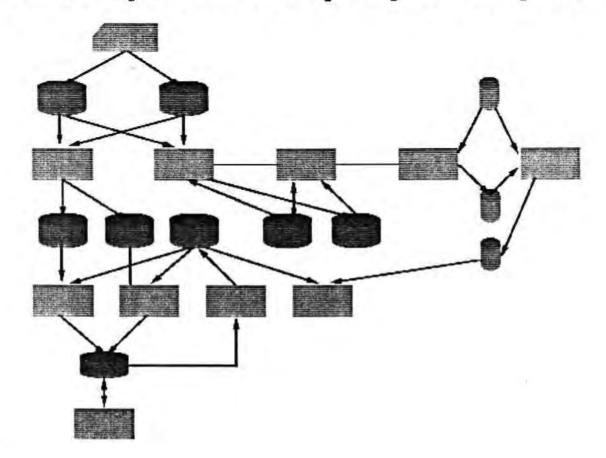

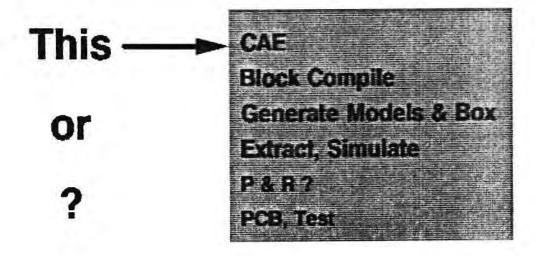

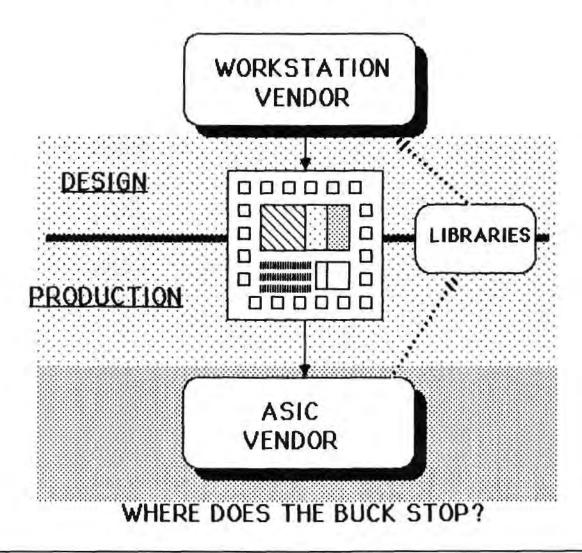

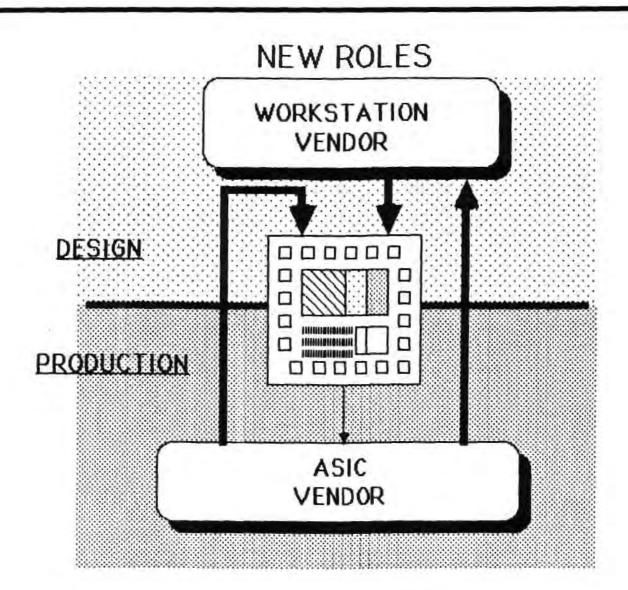

# TRADITIONAL APPROACH

#### **ASIC DESIGN PROCESS**

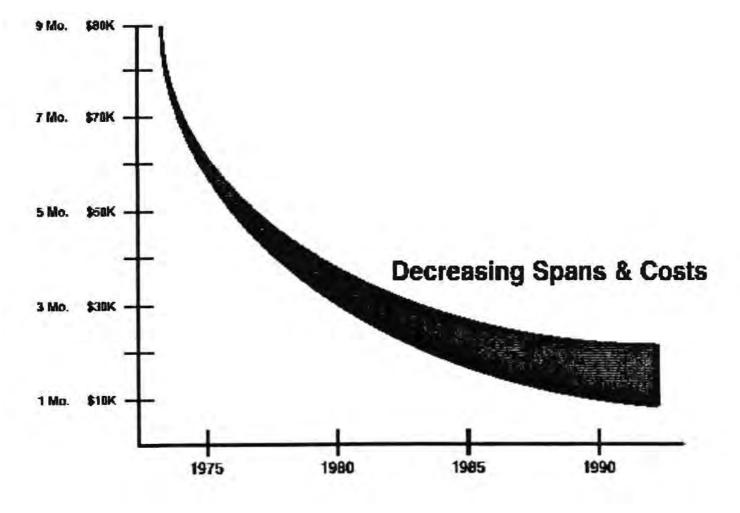

## **AUTO IC LAYOUT**

- QUICKER TURNAROUND

- LOWER NRE COSTS

- PROJECT CONTROL

- BETTER DESIGNS

- SECURITY

#### SCHEMATIC CAPTURE

- TIME INTENSIVE

- INDEPENDENT OF DESIGN RULE CHECKING

- POTENTIAL SOURCE OF ERRORS

- COMPLICATES LAYOUT PROCESS

## **AUTOMATED IC DESIGN**

INTEGRATED SOLUTION -

LOGICAL DESIGN

+

PHYSICAL LAYOUT

#### **IDEAL INTEGRATED SOLUTION:**

- "WHAT IF" ANALYSIS

- DATA BASE MANAGEMENT

- COMMON INTERFACE

- AUTOMATIC LAYOUT

- AUTOMATIC TEST GENERATION

- DESIGN DOCUMENTATION

- DESIGN VERIFICATION AND RULE CHECKING

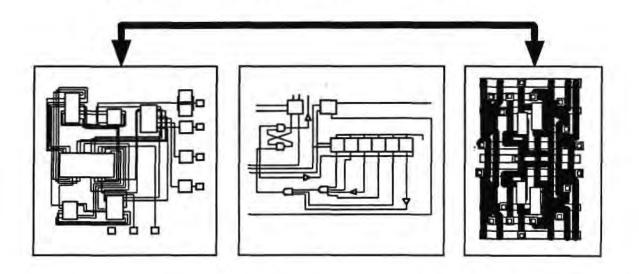

## **AUTOMATED IC DESIGN**

TWO APPROACHES:

- EVOLUTIONARY

- REVOLUTIONARY

## **AUTO IC DESIGN**

#### **EVOLUTIONARY APPROACH**

CURRENT DESIGN TOOLS

+

SILICON COMPILATION TECHNIQUES

## **EVOLUTIONARY APPROACH**

## **AUTO IC DESIGN**

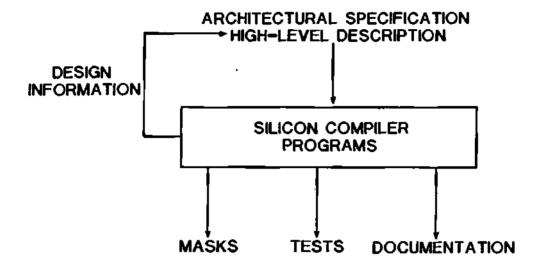

#### REVOLUTIONARY APPROACH

# "TRUE" OR FULL SILICON COMPILATION

## REVOLUTIONARY APPROACH

#### TRUE SILICON COMPILATION

#### SILICON COMPILER PROGRAMS

#### AUTOMATED:

- DETAIL DESIGN

- DESIGN VERIFICATION

- PHYSICAL DESIGN

- BACK-END VERIFICATION/DRC

- MASK GENERATION

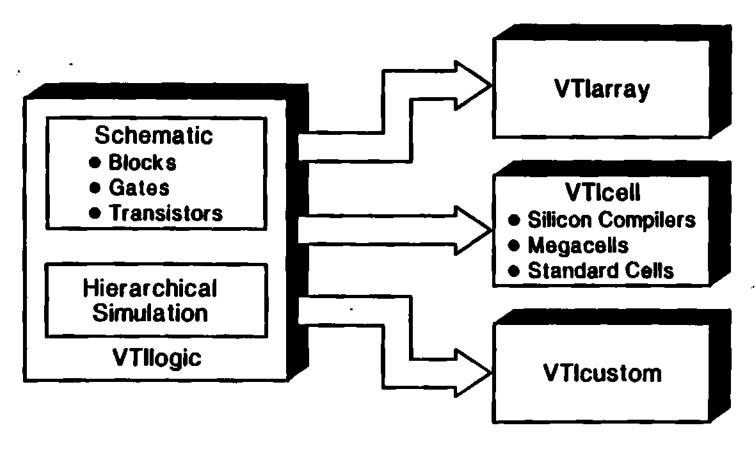

# SILICON COMPILATION--A DESIGN TECHNIQUE

SILICON COMPILER--A CAD PRODUCT

#### **QUESTION:**

WHAT DO SILICON COMPILERS PRODUCE?

**──→** GATE ARRAYS?

→ STANDARD CELLS?

FULL CUSTOM ICs?

## **ANSWER:**

YES ...

- GATE ARRAYS WITH WIRE CHANNEL EXPANSION

- STANDARD CELLS MIXED WITH COMPILED BLOCKS

- FULL CUSTOM ACHIEVED BY BLOCK-LEVEL DESIGN TECHNIQUES

#### SILICON COMPILATION

#### BENEFITS:

- CREATIVITY TOOL

- DATA BASE MANAGEMENT

- STANDARD DESIGN PRACTICE

- REDUCED TURNAROUND TIME

- AUTOMATIC LAYOUT

## SILICON COMPILERS

#### NEEDS:

- AUTOMATED TEST GENERATION

- MORE PARAMETRIC MODELS

- HIGHER COMFORT LEVEL

#### IC CAD WORLDWIDE FORECAST

Source: DATAQUEST

## IC CAD WORLDWIDE FORECAST (Millions of Dollars)

|        | 1984  | <u> 1985</u> | <u>1986</u> | <u>1987</u> | 1988  | 1989  | CAGR  |

|--------|-------|--------------|-------------|-------------|-------|-------|-------|

| IC CAD | \$157 | \$181        | \$224       | \$298       | \$408 | \$571 | 29.5% |

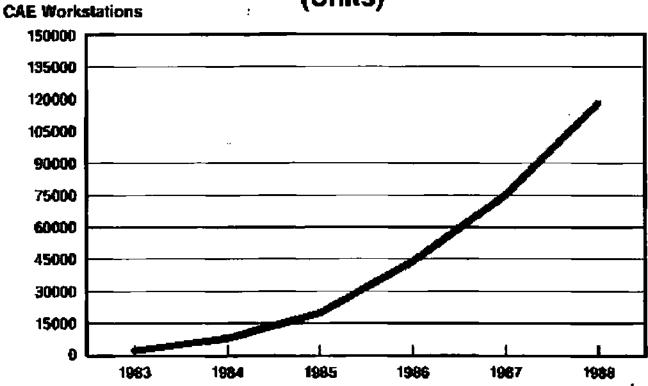

## IC CAD WORKSTATION SHIPMENTS

#### **UNITS**

1984 1989 (Est.) 1,211 8,751

# IC CAD WORKSTATIONS ESTIMATED PERCENT CHANGE

Source: DATAQUEST

IC CAD WORKSTATIONS (Percent Change)

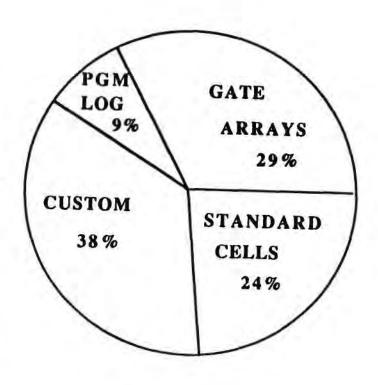

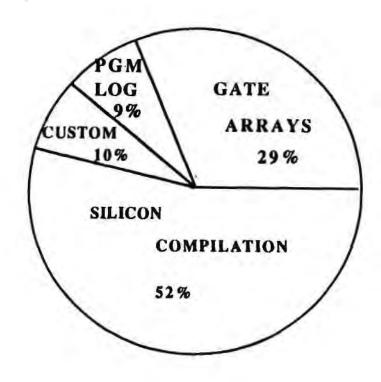

|                   | 1984 | <u>1985</u> | 1986 | 1987 | 1988 | 1989 |

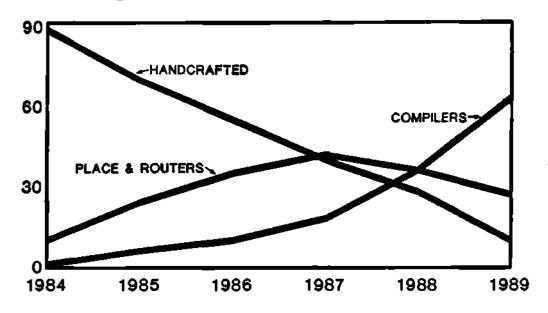

|-------------------|------|-------------|------|------|------|------|

| Compilers         | 1    | 6           | 10   | 18   | 36   | 63   |

| Hand-Crafted      | 89   | 70          | 55   | 40   | 28   | 10   |

| Place and Routers | 10   | 24          | 35   | 42   | 36   | 27   |

| Total             | 100  | 100         | 100  | 100  | 100  | 100  |

# IC WORKSTATIONS ESTIMATED SHIPMENTS

Source: DATAQUEST

## IC WORKSTATIONS ESTIMATED SHIPMENTS (Units)

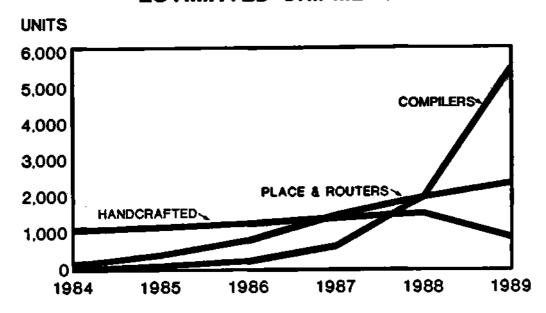

|                   | 1984 | <u>1985</u> | 1986  | <u>1987</u> | <u>1988</u> | <u>1989</u> | CAGR |

|-------------------|------|-------------|-------|-------------|-------------|-------------|------|

| Compilers         | 12   | 99          | 228   | 629         | 1975        | 5513        | 2418 |

| Hand-Crafted      | 1075 | 1155        | 1255  | 1397        | 1536        | 875         | -48  |

| Place and Routers | 124  | 396         | 798   | 1467        | 1975        | 2363        | 80€  |

| Total             | 1211 | 1650        | 2281- | 3493        | 5486        | 8751        | 49%  |

• SILICON COMPILATION IS A REPLACEMENT TECHNOLOGY

- SILICON COMPILATION IS A REPLACEMENT TECHNOLOGY

- THIRD-PARTY AGREEMENTS

- SILICON COMPILATION IS A REPLACEMENT TECHNOLOGY

- THIRD-PARTY AGREEMENTS

- DESIGN SERVICE AND TRAINING

- SILICON COMPILATION IS A REPLACEMENT TECHNOLOGY

- THIRD-PARTY AGREEMENTS

- DESIGN SERVICE AND TRAINING

- COOPERATION WITH ASIC HOUSES AND IC MANUFACTURERS

# CONCLUSION: AUTOMATED IC DESIGN

- SILICON COMPILER REVOLUTION LEADING AN EVOLUTION

- CAD VENDORS DRIVE THIS MARKET

DESIGN CENTER SURVEY

Relly Leininger Research Assistant Dataquest Incorporated

Ms. Leininger is a Research Assistant for the CAD/CAM Industry Service. She is responsible for research assistance in the electronic CAD/CAM segments, company profile research, data base support, and survey research. Ms. Leininger is doing degree work at San Jose State University.

Dataquest Incorporated

DESIGN AUTOMATION FOCUS CONFERENCE

December 9 and 10, 1985

Palo Alto, California

- DEMOGRAPHICS

- DESIGN ENVIRONMENT

- USAGE

- FUTURE PLANS

- BOTTLENECKS

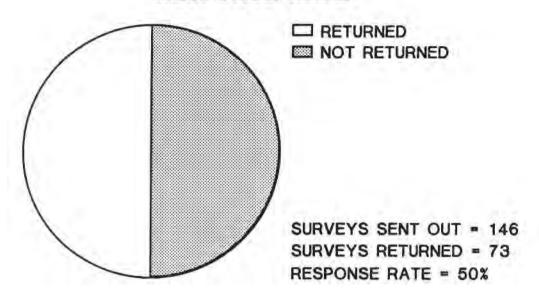

# DESIGN CENTER SURVEY RESPONSE RATE

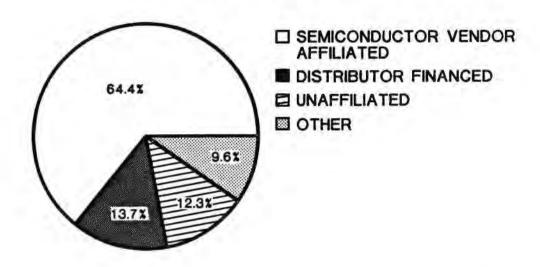

# DESIGN CENTER SURVEY DISTRIBUTION OF RESPONSES BY COMPANY TYPE

#### **DESIGN CENTER SURVEY**

AVERAGE NUMBER OF GATES: 4,900

## DESIGN ENVIRONMENT

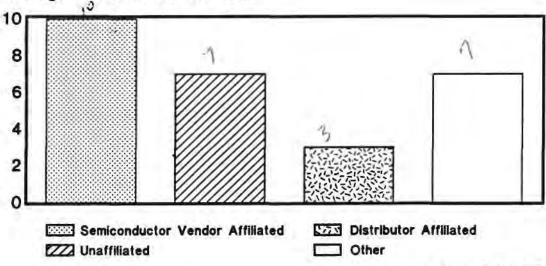

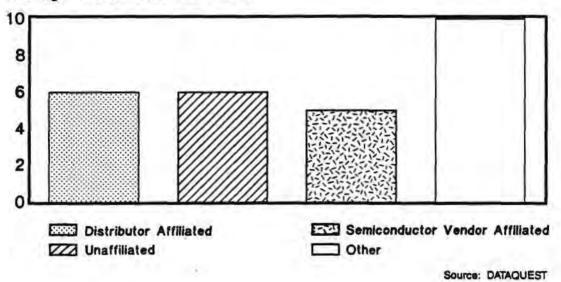

# DESIGN CENTER SURVEY DISTRIBUTION OF INSTALLED BASE BY COMPANY TYPE

Average Workstations Per Site

Source: DATAQUEST

#### DISTRIBUTION OF INSTALLED BASE BY COMPANY TYPE (Average Workstations Per Site)

| Semiconductor | Vendor   | Affiliated | 10 |

|---------------|----------|------------|----|

| Unaffiliated  |          |            | 7  |

| Distributor A | ffiliate | ed         | 3  |

| Other         |          |            | 7  |

Source: DATAQUEST

- 6 -1985 Dataquest Incorporated-Reproduction Prohibited

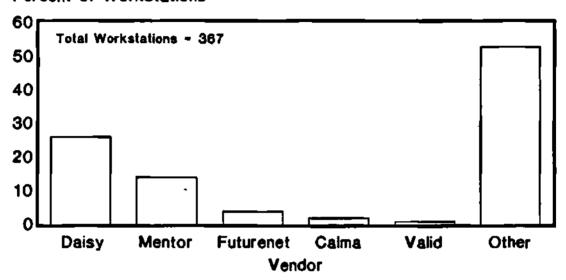

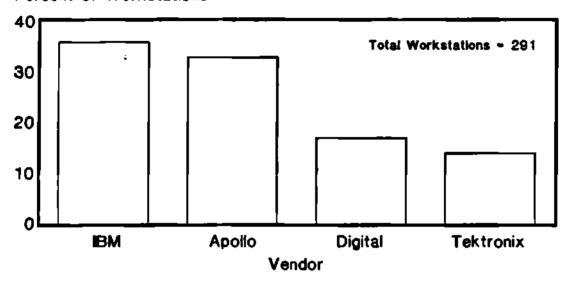

# DESIGN CENTER SURVEY CAD/CAM INSTALLED BASE

#### Percent of Workstations

Source: DATAQUEST

$\langle \gamma_i \rangle$ .

## CAD/CAM INSTALLED BASE (Percent of Workstations)

## DESIGN CENTER SURVEY NON-CAD/CAM INSTALLED BASE

#### Percent of Workstations

Source: DATAQUEST

#### NON-CAD/CAM INSTALLED BASE (Percent of Workstations)

| IBM       | 36 |

|-----------|----|

| Apollo    | 33 |

| Digital   | 17 |

| Tektronix | 14 |

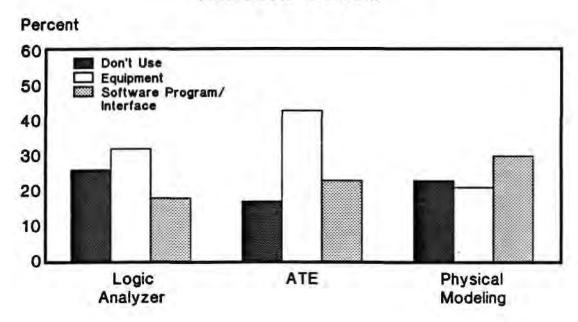

## DESIGN CENTER SURVEY TESTING TOOLS

Source: DATAQUEST

### TESTING TOOLS (Percent)

|                   | Don't Use | Equipment | Software Program/<br>Interface |

|-------------------|-----------|-----------|--------------------------------|

| Logic Analyzer    | 26        | 32        | 18                             |

| ATE               | 17        | 43        | 23                             |

| Physical Modeling | 23        | 21        | 30                             |

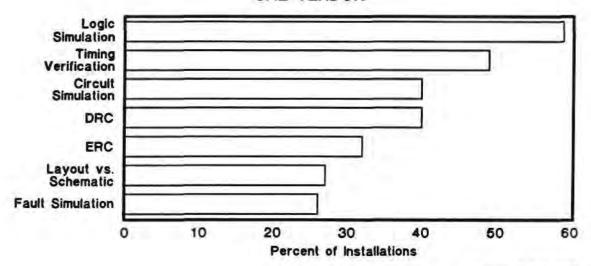

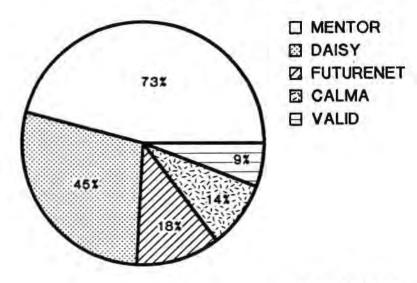

#### DESIGN CENTER SURVEY SOFTWARE ANALYSIS TOOLS INSTALLED BASE

#### CAE VENDOR

Source: DATAQUEST

# SOFTWARE ANALYSIS TOOLS INSTALLED BASE CAE VENDOR (Percent of Installations)

| Logic Simulation     | 59 |

|----------------------|----|

| Timing Verification  | 49 |

| Circuit Simulation   | 40 |

| DRC                  | 40 |

| ERC                  | 32 |

| Layout vs. Schematic | 27 |

| Fault Simulation     | 26 |

Source: DATAQUEST

- 10 -1985 Dataquest Incorporated-Reproduction Prohibited

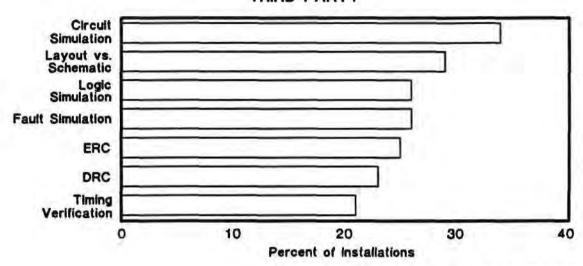

#### DESIGN CENTER SURVEY SOFTWARE ANALYSIS TOOLS INSTALLED BASE

#### THIRD PARTY

Source: DATAQUEST

# SOFTWARE ANALYSIS TOOLS INSTALLED BASE THIRD PARTY (Percent of Installations)

| Circuit Simulation   | 34 |

|----------------------|----|

| Layout vs. Schematic | 29 |

| Logic Simulation     | 26 |

| Fault Simulation     | 26 |

| ERC                  | 25 |

| DRC                  | 23 |

| Timing Verification  | 21 |

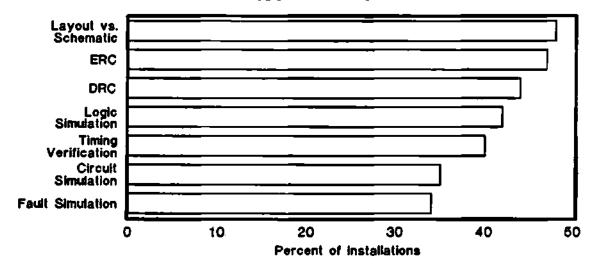

# DESIGN CENTER SURVEY SOFTWARE ANALYSIS TOOLS INSTALLED BASE

#### **DEVELOPED IN-HOUSE**

Source: DATAQUEST

# SOFTWARE ANALYSIS TOOLS INSTALLED BASE DEVELOPED IN-HOUSE (Percent of Installations)

| Layout vs. Schematic | 48 |

|----------------------|----|

| ERC                  | 47 |

| DRC                  | 44 |

| Logic Simulation     | 42 |

| Timing Verification  | 40 |

| Circuit Simulation   | 35 |

| Fault Simulation     | 34 |

Source: DATAQUEST

- 12 - 1985 Dataquest Incorporated-Reproduction Prohibited

### **DESIGN CENTER SURVEY**

- NUMBER OF ENGINEERS: 503

- ENGINEERS PER DESIGN CENTER: 7

- DESIGN STARTS: 3.259

- DESIGN STARTS PER ENGINEER: 7

## **USAGE**

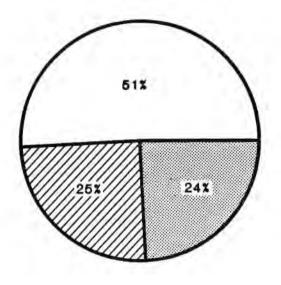

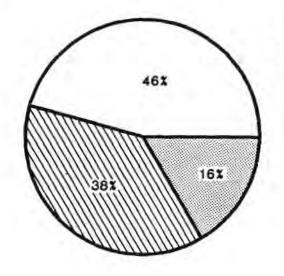

## DESIGN CENTER SURVEY WHO DOES THE DESIGN?

- ☐ IN-HOUSE ENGINEER

- ☑ COMBINATION OF IN-HOUSE ENGINEER AND CUSTOMER ENGINEER

- CUSTOMER ENGINEER

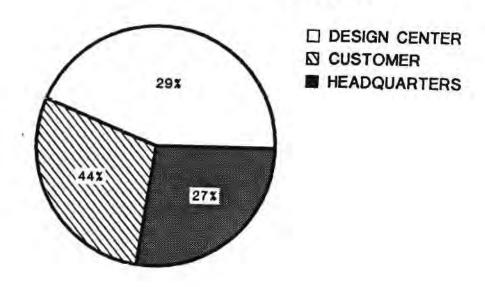

# DESIGN CENTER SURVEY WHO DOES SIMULATION?

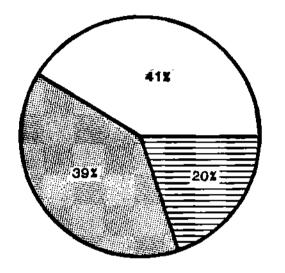

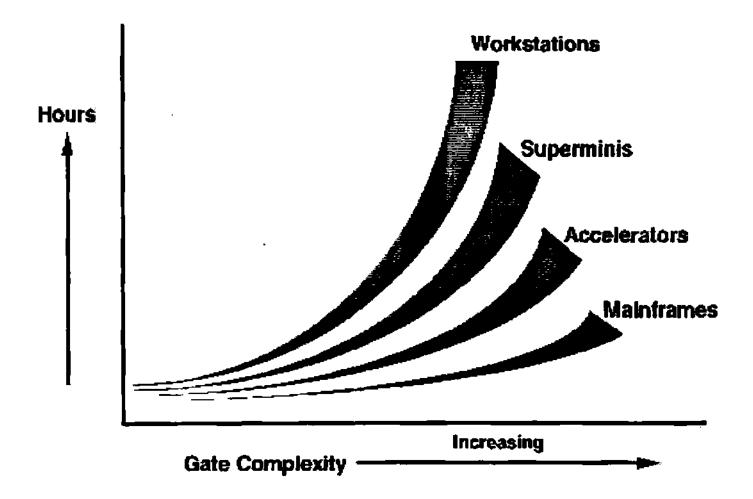

## DESIGN CENTER SURVEY SIMULATION SYSTEM TYPE

- ☐ WORKSTATION

- **MAINFRAME/MINI**

- **ACCELERATOR**

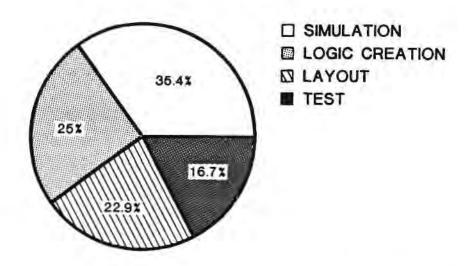

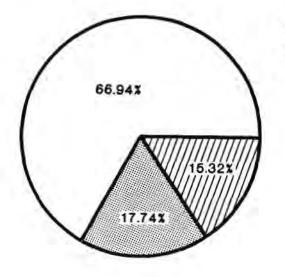

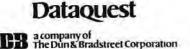

# DESIGN CENTER SURVEY AVERAGE DISTRIBUTION OF TIME PER DESIGN PHASE

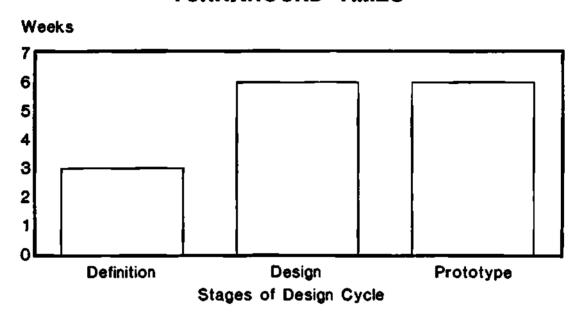

## DESIGN CENTER SURVEY TURNAROUND TIMES

Source: DATAQUEST

### TURNAROUND TIMES (Stages of Design Cycle)

Definition 3 Weeks

Design 6 Weeks

Manufactured For Protype 6 Weeks

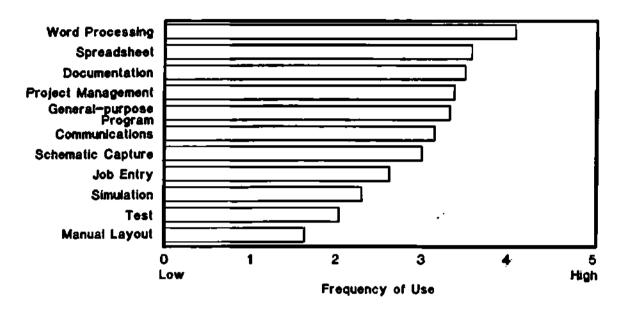

# DESIGN CENTER SURVEY USE OF PERSONAL COMPUTER SOFTWARE TOOLS

Source: DATAQUEST

#### USE OF PERSONAL COMPUTER SOFTWARE TOOLS (Frequency of Use)

| Word Processing         | 4.08 |

|-------------------------|------|

| Spreadsheet             | 3.57 |

| Documentation           | 3.50 |

| Project Management      | 3.38 |

| General-Purpose Program | 3.32 |

| Commnications           | 3.15 |

| Schematic Capture       | 3.00 |

| Job Entry               | 2.62 |

| Simulation              | 2.30 |

| Test                    | 2.03 |

| Manual Layout           | 1.63 |

### **FUTURE PLANS**

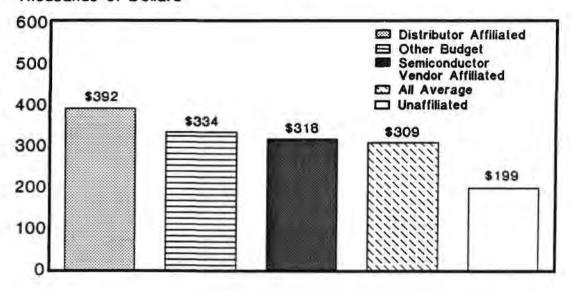

## DESIGN CENTER SURVEY AVERAGE BUDGET PER COMPANY TYPE

Thousands of Dollars

# DESIGN CENTER SURVEY WORKSTATION PURCHASE PLANS BY COMPANY TYPE

Average Workstations Per Site

WORKSTATION PURCHASE PLANS BY COMPANY TYPE

(Average Workstations Per Site)

| Semiconductor Vendor Affiliated | 5  |

|---------------------------------|----|

| Distributor Affiliated          | 6  |

| Unaffiliated                    | 6  |

| Other                           | 10 |

## DESIGN CENTER SURVEY PURCHASE PLANS BY PRODUCT TYPE

- ☐ STANDALONE

- M PC BASED

- M HOST DEPENDENT

# DESIGN CENTER SURVEY WORKSTATION PURCHASE PLANS BY VENDOR

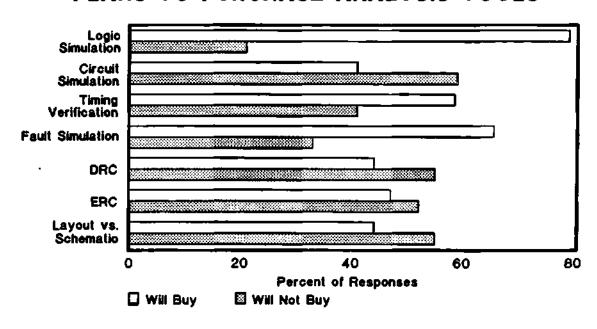

## DESIGN CENTER SURVEY PLANS TO PURCHASE ANALYSIS TOOLS

Source: DATAQUEST

### PLANS TO PURCHASE ANALYSIS TOOLS (Percent of Responses)

|                      | Will Buy | Will Not Buy |

|----------------------|----------|--------------|

| Logic Simulation     | 79       | 21           |

| Circuit Simulation   | 41       | 59           |

| Timing Verification  | 59       | 41           |

| Pault Simulation     | 66       | 34           |

| DRC                  | 45       | 55           |

| ERC                  | 48       | 58           |

| Layout vs. Schematic | 45       | 55           |

Source: DATAQUEST

- 26 - 1985 Dataquest Incorporated-Reproduction Prohibited

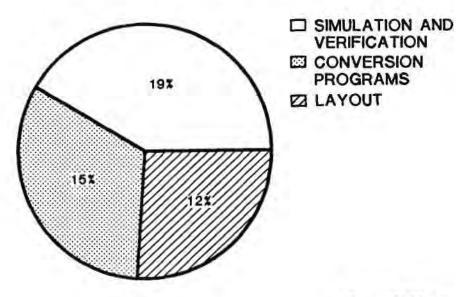

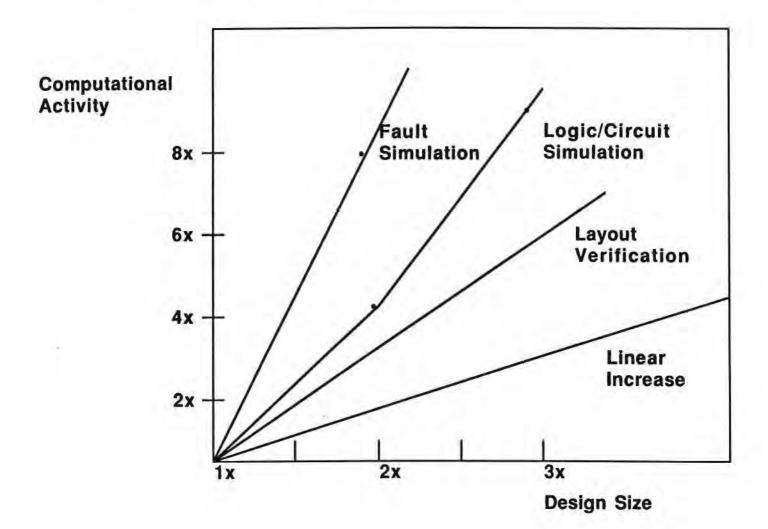

## DESIGN CENTER SURVEY DISTRIBUTION OF SYSTEM ARCHITECTURE

- ☐ WORKSTATION

- **■** HOST

- ACCELERATOR

## BOTTLENECKS

## DESIGN CENTER SURVEY BOTTLENECKS

#### **SUMMARY**

- PERSONAL COMPUTER

- CUSTOMER/VENDOR RELATIONSHIP

- TOOLS DEVELOPED IN-HOUSE

- TUCKER'S CAD/CAM LAW

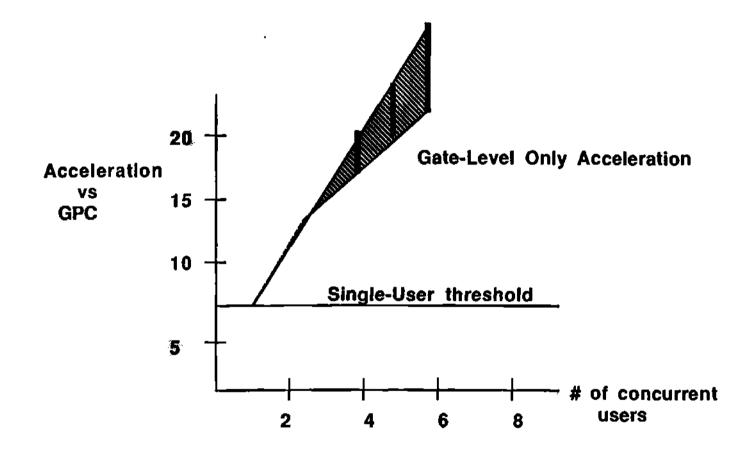

- ACCELERATORS

Dataquest Incorporated

A Subsidiary of A.C. Nielsen Company

1290 Ridder Park Drive

San Jose, California 95131

408/971-9000 / Telex 171973

JAPANESE TECHNOLOGY -- THE FUTURE WAVE

Sheridan M. Tatsuno

Industry Analyst

Japanese Semiconductor Industry Service

Dataquest Incorporated

Mr. Tatsuno is an Industry Analyst for Dataquest's Japanese Semiconductor Industry Service. He is responsible for analyzing trends in Japanese government policies and financial markets. He is also responsible for analyzing technology trends within the industry, and specifically tracks R&D spending, patent applications, and new product developments quarterly. He has seven years of experience in market research, planning, and international finance with Bechtel and Woodward-Clyde Consultants. Mr. Tatsuno has a B.A. degree in Political Science from Yale University and a Master's degree in planning and Policy Analysis from Harvard University's Kennedy School of Government. In addition to these credentials, Mr. Tatsuno is fluent in Japanese, French, and Spanish, and has authored a book called The Technopolis Vision: Japan's High-Tech Strategy for the 1990's and Beyond.

Dataquest Incorporated

DESIGN AUTOMATION FOCUS CONFERENCE

December 9 and 10, 1985

Palo Alto, California

### **OVERVIEW**

- LEADING-EDGE ICs

- JOINT R&D PROJECTS

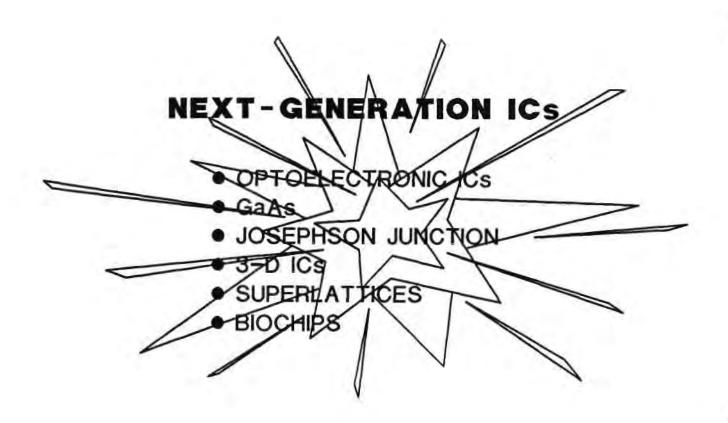

- NEXT-GENERATION ICs

- NEXT-GENERATION COMPUTERS

- MARKET OPPORTUNITIES

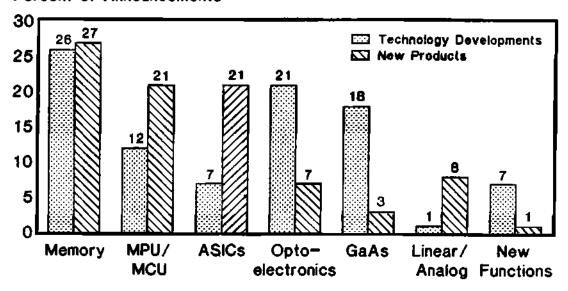

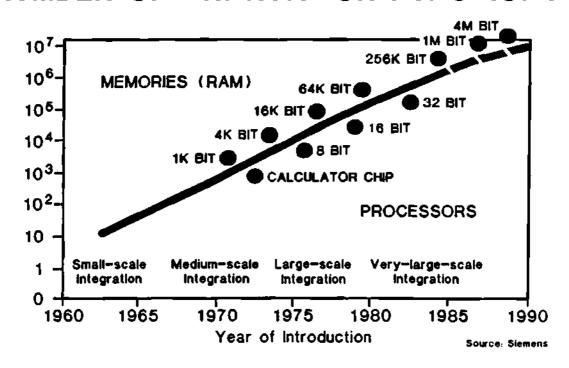

#### JAPANESE SEMICONDUCTOR TECHNOLOGY

1984

Percent of Announcements

#### FORECAST OF NTT RESEARCH PAPERS

#### **MEGABIT DYNAMIC RAM TRENDS**

#### **DESIGN RULE**

| <u>Year</u> | Device        | Start | End  | Technology                                |

|-------------|---------------|-------|------|-------------------------------------------|

| 1983        | 1 <b>M</b> b  | 1.25  | 0.80 | Steppers (5x, 1x)                         |

| 1985        | 4Mb           | 0.80  | 0.50 | Steppers (5x, 1x)                         |

| 1990        | 16Mb          | 0.50  | 0.30 | Synchrotron X-ray                         |

| 1995        | 64 <b>M</b> b | 0.25  | 80.0 | Synchrotron radiation E-beam overexposure |

|             |               |       |      | Bias exposure photolitho                  |

| 1998        | 256Mb         | 0.10  | 0.05 | Synchrotron radiation                     |

| 2000+       | 1Gb           | 0.05  | 0.01 | Bioelectronics                            |

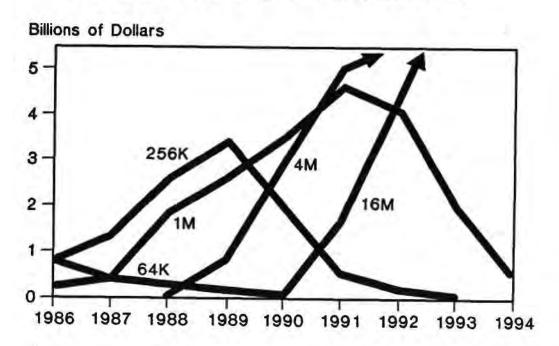

### DRAM MARKET FORECAST

#### **WORLDWIDE EPROM MARKET SHARE**

| Rank                 | <u>64K</u> | 128K       | 256K    | <u>512K</u> |

|----------------------|------------|------------|---------|-------------|

| 1                    | Hitachi    | Hitachi    | Intel   | Intel       |

| 2                    | Mitsubishi | intel      | AMD     | AMD         |

| 3                    | Fujitsu    | Mitsubishi | Hitachi | Hitachi     |

| 4                    | Intel      | AMD        | Toshiba | Fujitsu     |

| 5                    | TI         | Fujitsu    | Fujitsu |             |

| Japanese             |            |            |         |             |

| Share:               | 68%        | 79%        | 41%     | 2%          |

| 1984 Avg.            | 68%        | 56%        | 18%     | 0           |

| 1985 Market<br>Size: | \$286M     | \$249M     | \$ 189M | \$23M       |

| OIZO:                | 4200W      | 42-3III    | 4 103W  | 450IAI      |

### SMART CARDS--THE NEXT PC MARKET?

| Start      | Group Leader    | Application             | IC Device                   |

|------------|-----------------|-------------------------|-----------------------------|

| Dec. 1984  | Mitsui Bank     | Banking and<br>Shopping | 64K EPROM with<br>8-bit MPU |

| March 1985 | Seibu Bank      | Medical                 | 16K EEPROM with CPU         |

| May 1985   | Sumitomo Bank   | Shopping                | 64K EEPROM with CPU         |

| July 1985  | Toyo Trust Bank | Financial  Management   | 64K EPROM with CPU          |

| Aug. 1985  | Dai-Ichi Kangyo | Banking                 | 64K EPROM with CPU          |

| Oct. 1985  | Sanwa Bank      | Shopping                | 64K EEPROM with CPU         |

| Oct. 1985  | Fuji Bank       | Corporate<br>Banking    | 16K EEPROM with CPU         |

| Oct. 1985  | Daiwa Bank      | Shopping                | 16K EEPROM with CPU         |

| Oct. 1985  | Toshiba         | Point-of-Sale           | 64K EEPROM with CPU         |

### JAPANESE EPROMs/EEPROMs

| Company       | EPROM         | EEPROM           |

|---------------|---------------|------------------|

| Fujitsu       | 256K CMOS     | 64K CMOS         |

| Hitachi       | 256K/1Mb CMOS | 64K CMOS         |

| Mitsubishi    | 1Mb NMOS      | 256K CMOS        |

| NEC           | 256K/1Mb CMOS |                  |

| Oki           | 64K NMOS      | 16K CMOS (Exel)  |

| Ricoh         | 256K CMOS     |                  |

| Suwa Seikosha | 64K/128K CMOS |                  |

| Toshiba       | 256K CMOS     | 64K 'Flash' CMOS |

## THE SHIFT TO STANDARD CELLS

## "DESIGN BOUTIQUE" STRATEGY

## JAPANESE 32-BIT MICROPROCESSORS

| Year | Company    | Product Line            | Ties             |

|------|------------|-------------------------|------------------|

| 1986 | NEC        | V60 (first generation)  | Sony and Zilog   |

| 1987 |            | V70 (second generation) | (V20/V30)        |

| 1986 | Hitachi    | 68000Compatible CMOS    | Motorola         |

|      |            | TRON Project            | Tokyo University |

| 1986 | Fujitsu    | 80286 (16-/32-bit MPU)  | Intel -          |

| 1986 | Oki        | Proprietary MPU         | <del></del>      |

| 1987 | Mitsubishi | TRON Project            | Tokyo University |

| 1987 | Toshiba    | Proprietary MPU         | Zilog (Z8000)    |

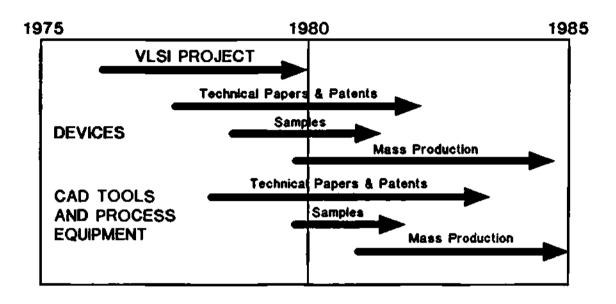

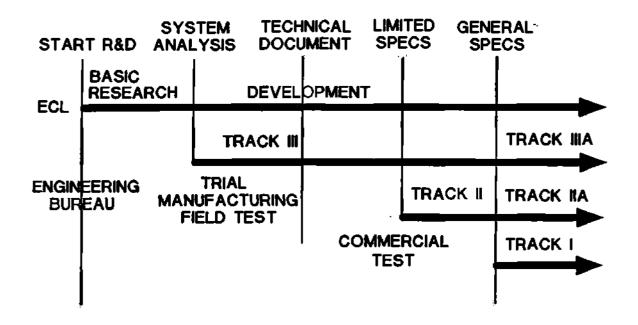

## JAPANESE IC DEVELOPMENT CYCLE

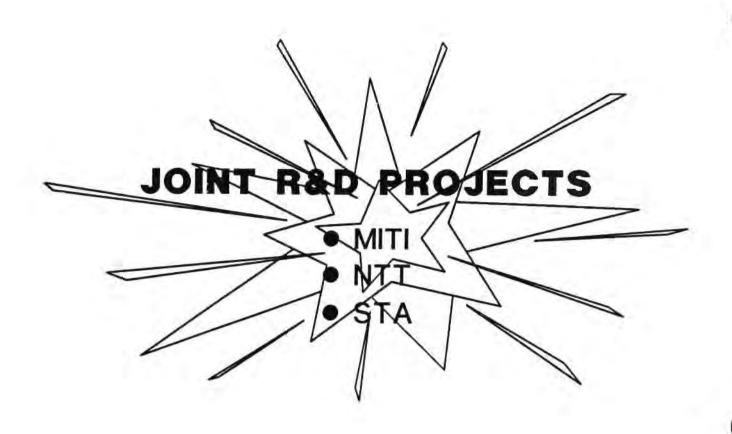

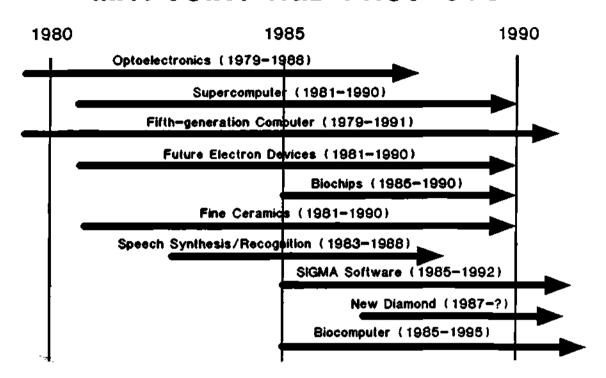

## MITI JOINT R&D PROJECTS

## OTHER GOVERNMENT-SPONSORED R&D PROJECTS

| Agency | Project               | Time Frame |

|--------|-----------------------|------------|

| NTT    | INS computer          | 1984-1990  |

| STA    | Perfect GaAs crystals | 1981-1986  |

| STA    | Amorphous compounds   | 1981-1986  |

| STA    | Nanomechanisms        | 1985-1990  |

| STA    | Solid-state surfaces  | 1985-1990  |

## OPTOELECTRONICS: THE NEXT GENERATION

## GaAs RESEARCH (1985)

| Device           | Company                  | Speed    |

|------------------|--------------------------|----------|

| 4K SRAM          | Fujitsu                  | 1.7 ns   |

|                  | Hitachi                  | 2.2 ns   |

|                  | NEC                      | 2.4 ns   |

| 3.000-gate logic | NEC                      | 30.0 ps  |

| MESFET           | Oki                      | 14.7 ps  |

| Gate arrays      | Toshiba<br>(2,000 gates) | 42.0 ps  |

|                  | Oki<br>(1.000 gates)     | 390.0 ps |

| HEMT             | Fujitsu                  | 0.9 ns   |

## JOSEPHSON JUNCTIONS

| Company | <u>Device</u>                                      | Speed  |

|---------|----------------------------------------------------|--------|

| Hitachi | Control terminal transistor                        | 20 ps  |

| NEC     | 4 x 4-bit parallel multiplier with 249 logic gates | 350 ps |

| NEC     | 4 x 4-bit multiplier                               | 280 ps |

### **FUTURE ELECTRON DEVICES PROJECT**

| Themes                    | 81                                                              | 82       | 83      | 84   | 85                 | 86     | 87      | 88          | 89 | 90 |

|---------------------------|-----------------------------------------------------------------|----------|---------|------|--------------------|--------|---------|-------------|----|----|

|                           |                                                                 | PHA      | SE 1    |      | PHASE 2            |        | PHASE 3 |             |    |    |

| Superlattices<br>(SL)     | Ba                                                              | sic SL   | Structe | ur e | Bas                | ic Dev | ices    | Integration |    |    |

|                           | New Material System                                             |          |         |      |                    |        |         |             |    |    |

| -                         | PHASE 1                                                         |          |         |      | PHASE 2            |        |         | . PHASE 3   |    |    |

| Three-<br>Dimensional ICs | Mu                                                              | Itilayer | Struct  | ure  | Test Element Group |        |         |             |    |    |

| (3-D ICs)                 | Basic Technology Process Technology Device Design System Design |          |         |      |                    |        |         |             |    |    |

|                           | PHASE 1 PHASE 2 PHASE 3                                         |          |         |      |                    |        |         |             |    |    |

| Hardened ICs              | Testing Technique Test Device Integration                       |          |         |      |                    |        |         |             |    |    |

|                           | Device, Process Modification                                    |          |         |      |                    |        |         |             |    |    |

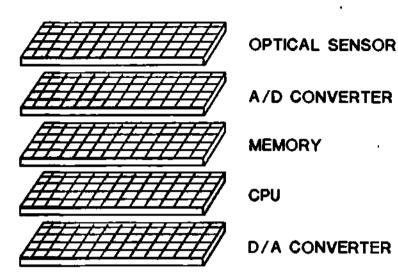

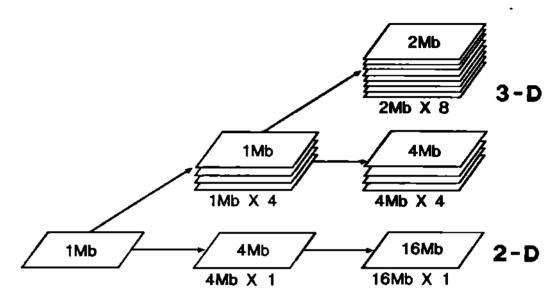

## FIVE-LEVEL 3-D IC

#### **ADVANTAGES**

HIGHER DENSITIES

HIGHER SPEEDS

PARALLEL

PROCESSING

MULTIPLE

FUNCTIONS

## MEGABIT MEMORIES -- THE SHIFT TO 3-D ICs

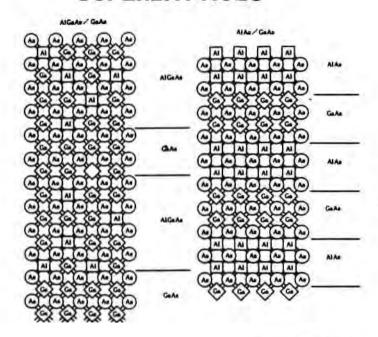

### SUPERLATTICES

#### **BIOCHIP RESEARCH**

#### COMPANY

#### RESEARCH FOCUS

ASAHI CHEMICAL LIGHT-SENSITIVE ORGANIC SEMICONDUCTOR

DOJIN CHEMICAL THIN-FILM BIOCHIP SUBSTRATE

FUJITSU BIOSENSORS, THIN-FILMS, BIOCHIPS HITACHI BIOCHIPS, ARTIFICIAL INTELLIGENCE

KURARAY IMPLANTABLE BIOSENSORS

MITI ORGANIC SUPERCONDUCTORS

MATCHICLETA MATCHICATER SOLUBLE BUOTORSOLUTIONS

MATSUSHITA WATER-SOLUBLE PHOTORESIST

MITSUBISHI ENZYME BIOSENSORS

NEC MEDICAL BIOSENSORS

SHARP

SHARP BIOCHIPS, BIOCOMPUTERS TOSHIBA MULTI-ION BIOSENSORS

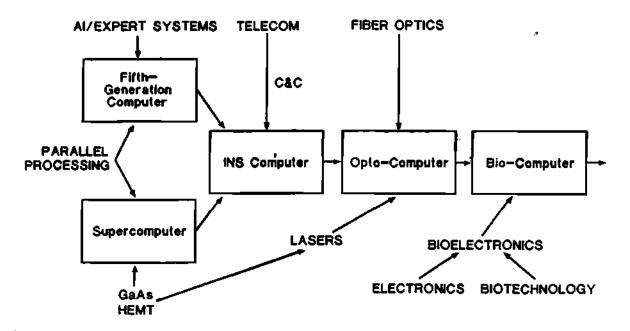

### JAPAN'S NEXT-GENERATION COMPUTERS

## MITI SUPERCOMPUTER PROJECT (1981-1989)

|                        | Fujitsu | Hitachi | Mitsubishi | NEC | <u>Oki</u> | Toshiba |

|------------------------|---------|---------|------------|-----|------------|---------|

| Semiconductors         |         |         |            |     |            | ,       |

| Josephson Junction     | X       | X       |            | X   |            |         |

| GaAs Digital ICs       |         |         | X          | X   |            | X       |

| HEMT                   | X       |         |            |     | X          | •       |

| ECL Logic              |         | X       | X          |     |            |         |

| Systems                |         |         |            |     |            |         |

| Architecture           | X       |         |            |     |            |         |

| Large-Capacity Storage |         |         |            | X   |            |         |

| Parallel Processors    |         |         | X          |     | X          | X       |

| Software               |         | X       |            |     |            |         |

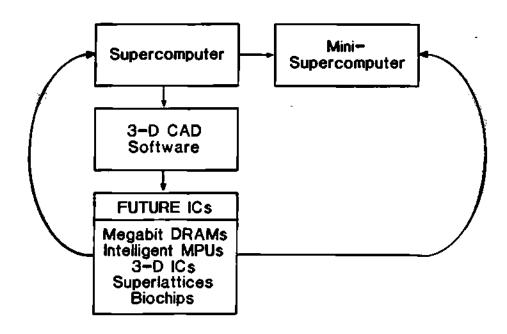

#### **FUTURE SUPERCOMPUTER CAD TOOLS**

## MITI FIFTH-GENERATION COMPUTER CHIPS (1979-1991)

**FUNCTION**

**DEVICE REQUIRED**

Natural language processing

Voice recognition and synthesis chips

Megabit DRAMs and ROMs

D/A and A/D converters

Image processing

Graphics chips

Optoelectronic ICs (OEICs)

Semiconductor lasers CCD image sensors

Parallel processors

32-bit microprocessors (MPUs)

"Intelligent" MPUs with lasers (Si/GaAs)

inference machines and

data flow

GaAs and other III-V devices

Josephson junctions

High-electron mobility transistors (HEMT)

VLSI architecture

VLSI CAD tools

7(%)

VLSI testing equipment

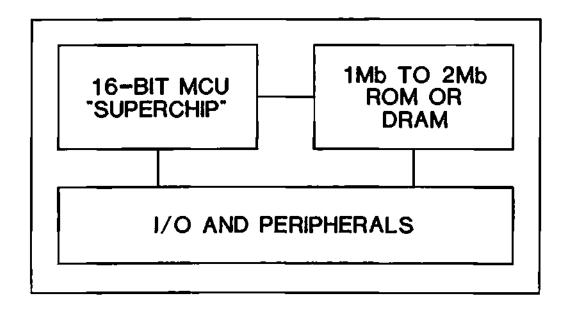

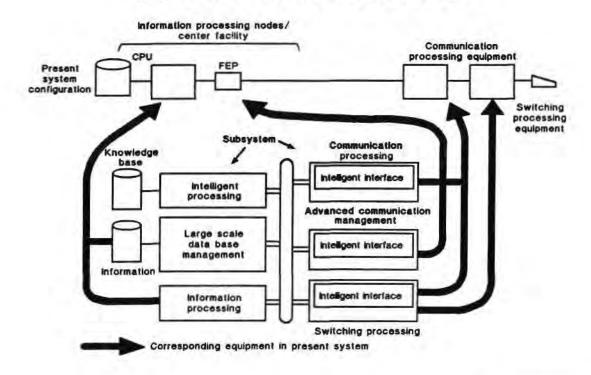

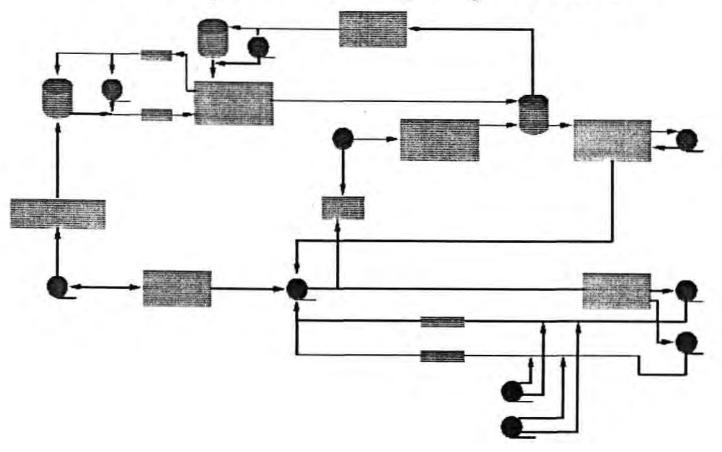

#### CONCEPT OF INS COMPUTER

## IC RESEARCH FOR INS COMPUTER

- MEGABIT MEMORY PROCESSING

(4/16/64Mb) -- E-BEAM FOR SUBMICRON;

SYNCHROTRON OPTICAL RADIATION FOR

SUB-HALF-MICRON

- HIGH SPEED LOGIC--GaAs ICs, JOSEPHSON JUNCTIONS, BALLISTIC TRANSISTORS

- OPTICAL TRANSMISSION--SEMICONDUCTOR LASERS AND OPTOELECTRONIC ICs (OEICs)

### IC RESEARCH FOR INS COMPUTER

- MOBILE AND SATELLITE TRANSMISSION—— GaAs MICROWAVE

- ELECTRONIC SWITCHING AND DIPS COMPUTER--16-BIT AND 32-BIT MPUs

- VIDEO PROCESSING——CCD SENSORS, WAFER SCALE VIDEO CHIPS

- DIGITAL SUBSCRIBER LOOPS—AUDIO AND VIDEO CODES

- TELEPHONE CIRCUITS—SUBSCRIBER LINE INTERFACE CIRCUITS (SLICs) AND ONE—CHIP TELEPHONE LSIS

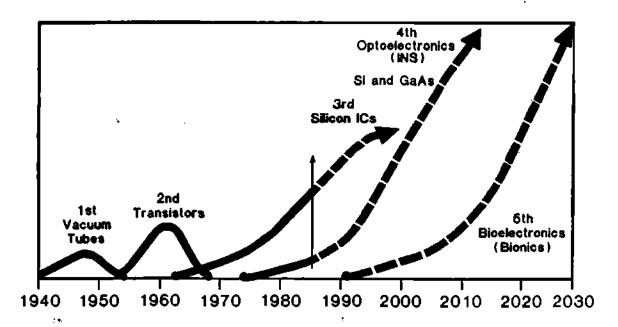

## THE SIXTH-GENERATION COMPUTER -MITI'S BIO-COMPUTER PROJECT

- \$40 MILLION FUNDING (1985-1995)

- MIMICS HUMAN BRAIN FUNCTIONS (PATTERN RECOGNITION, REASONING, AND LEARNING)

- FOUR RESEARCH AREAS:

- NEW COMPUTER ARCHITECTURE

- BIOCHIP DEVELOPMENT

- NEURAL SYSTEMS OF LOWER ANIMALS

- NONDESTRUCTIVE, NONCONTACT METHODS FOR MEASURING HUMAN BRAIN ACTIVITY

## **WORLDWIDE SEMICONDUCTOR REVENUES**

(Millions of Dollars)

|         | 1984   | 1985   | PERCENT<br>CHANGE | 1986   | PERCENT<br>CHANGE |

|---------|--------|--------|-------------------|--------|-------------------|

| U.S.A.  | 13,333 | 9,729  | (27.0)            | 10,513 | 8.1               |

| JAPAN , | 8,687  | 8,186  | ( 5.8)            | 9,172  | 12.0              |

| EUROPE  | 4.805  | 4,700  | ( 2.2)            | 5,454  | 16.0              |

| ROW     | 2.073  | 1,433  | (30.9)            | 1,612  | 12.5              |

|         |        |        |                   |        |                   |

| TOTAL   | 28,898 | 24,048 | (16.8)            | 26,751 | 11.2              |

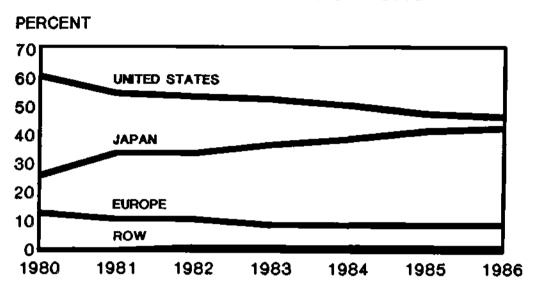

## **REGIONAL MARKET SHIFTS**

## **TOTAL SEMICONDUCTORS**

## **REGIONAL MARKET SHIFT**

## REGIONAL MANUFACTURERS' SHARE OF TOTAL SEMICONDUCTORS (Percent)

|               | 1980 | 1981 | 1982 | 1983 | 1984 | 1985 | 1986 |

|---------------|------|------|------|------|------|------|------|

| WORLD         | 100  | 100  | 100  | 100  | 100  | 100  | 100  |

| UNITED STATES | 61   | 55   | 54   | 53   | 51   | 48   | 47   |

| JAPAN         | 26   | 34   | 34   | 37   | 39   | 42   | 43   |

| EUROPE        | 13   | 11   | 11   | 9    | 9    | 9    | 9    |

| ROW           | 0    | 0    | 1    | 1    | 1    | 1    | 1    |

## CAPITAL SPENDING BY JAPANESE SEMICONDUCTOR COMPANIES

(Millions of Dollars)

|            | CAPITAL | EXPENDITURES | PERCENT OF SEMICONDUCTOR SALE |                |  |

|------------|---------|--------------|-------------------------------|----------------|--|

|            | 1984    | 1985 (Est.)  | PERCENT<br>CHANGE             | 1985 (Est.)    |  |

| NEC        | 591     | 420          | (28.9)                        | 23             |  |

| HITACHI    | 548     | 297          | (45.8)                        | 20             |  |

| TOSHIBA    | 624     | 480          | (23.1)                        | 35             |  |

| FUJITSU    | 527     | 280          | (46.9)                        | 38             |  |

| MATSUSHITA | 401     | 340          | (15.2)                        | 39             |  |

| MITSUBISHI | 295     | 224          | (24.1)                        | 28             |  |

| SHARP      | 118     | 160          | 35.6                          | 47             |  |

| SANYO      | 148     | 184          | 24.3                          | 37             |  |

| OKI        | 118     | 100          | (15.3)                        | <u>34</u>      |  |

| TOTAL      | 3,370   | 2.485        | (26.3)                        | <del>301</del> |  |

## STRATEGIC ALLIANCES (1985)

| U.S. FIRM                                        | JAPANESE FIRM              | RESEARCH FOCUS                                  |

|--------------------------------------------------|----------------------------|-------------------------------------------------|

| Hewlett-Packard                                  | Toshiba                    | VLSI technology exchange                        |

| LSI Logic                                        | Toshiba                    | 'Sea of Gates' development                      |

| Westinghouse,<br>General Electric                | Mitsubishi                 | Diodes, power transistors                       |

| Tektronix                                        | Sony                       | MPU development support system for NEC series   |

| Veeco                                            | Kanematsu<br>Semiconductor | lon implanters                                  |

| Vitelic                                          | NMB Semiconductor          | CMOS 1Mb DRAM                                   |

| Tektronix,<br>Digital Research,<br>HP (Yokogawa) | NEC                        | MPU development support system for NEC V series |

#### NTT RESEARCH AND DEVELOPMENT

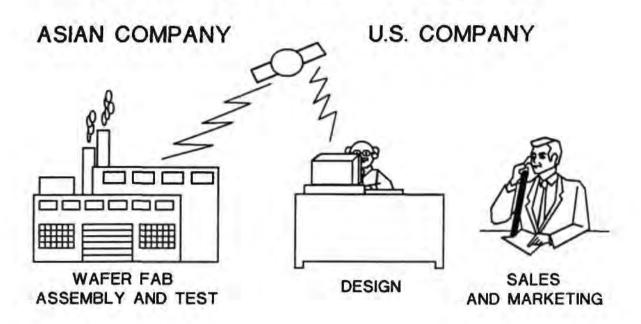

## JOINT R&D WITH NTT

| U.S. COMPANY      | RESEARCH FOCUS                      |

|-------------------|-------------------------------------|

| IBM               | LINK-UP OF IBM'S SYSTEM NETWORK     |

|                   | ARCHITECTURE WITH NTT NETWORK       |

| AT&T              | JOINT VAN DEVELOPMENT AND MARKETING |

| EATON             | JOINT DEVELOPMENT OF OXYGEN         |

|                   | ION IMPLANTERS                      |

| MOTOROLA          | JOINT IC RESEARCH FOR INS COMPUTER  |

| TEXAS INSTRUMENTS | JOINT IC RESEARCH FOR INS COMPUTER  |

| ENERGY CONVERSION | JOINT DEVELOPMENT OF AMORPHOUS      |

| DEVICES (ECD)     | MEMORIES                            |

A semimonthly report on Japanese and Asian High-Technology Industries

# I.C. ASIA

Compiled by DATAQUEST's Japanese Semiconductor Industry Service

12/04/85

I.C. ASIA 1985-30

Subscription Information on Back Page I.C. ASIA is a news digest published semimonthly by DATAQUEST's Japanese Semiconductor Industry Service (JSIS). To order a one-year subscription (22 issues), mail your check or money order for \$430 to:

I.C. ASIA 1290 Ridder Park Drive, M.S. 2-305 San Jose, CA 95131-2398

#### MAJOR EVENTS

SEMICONDUCTOR MAKERS REVISE PLANS FOR FY85, Pg. 2 YAMAGUCHI NIPPON PLANS TO PRODUCE 1Mb DRAM, Pg. 4 SEIKO EPSON TO BEGIN 256K SRAM PRODUCTION, Pg. 5 TOSHIBA REVISES GATE ARRAY SALES PLAN, Pg. 6

The exchange rate used in this issue is ¥206/US\$.

Each month I.C. Asia presents indicators on the IC industry in Asia. This set covers exports of integrated circuits from Japan to the ten largest countries of destination. The data shown below cover only finished goods at export value.

#### EXPORTS OF INTEGRATED CIRCUITS FROM JAPAN\* SEPTEMBER 1985

|        |              |                    | Sep                  | September 1985                |                                            |                      | Total (JanSep. 1985)          |                                             |      |  |  |

|--------|--------------|--------------------|----------------------|-------------------------------|--------------------------------------------|----------------------|-------------------------------|---------------------------------------------|------|--|--|

| -      | king<br>Aug. | Country            | Units<br>(Thousands) | Volue<br>(Millions<br>of Yen) | Value<br>Change<br>from<br>Sep. 184<br>(%) | Units<br>(Thousands) | Value<br>(Millions<br>of Yen) | Value<br>Change<br>from<br>Jan.—Sep.<br>(光) |      |  |  |

| -      | -            | United States      | 25,984               | 11,874                        | -60                                        | 285,860              | 170,011                       | -31%                                        | _    |  |  |

| 2      | 2            | West Germony       | 11,675               |                               | -377                                       |                      |                               | 14%                                         |      |  |  |

| 234567 | 3            | Hong Kong          | 24,573               |                               | -513                                       |                      | 45,237                        | -29%                                        |      |  |  |

| 4      | 5            | Taiwan             | 21,474               |                               | -3                                         |                      | 28,599                        | 13%                                         |      |  |  |

| 5      | 4            | Korea              | 21,226               | 3,868                         | -113                                       |                      | 28,707                        | 145                                         |      |  |  |

| 6      | 6            | Singapore          | 8,645                | 1,626                         | -569                                       | 97,339               | 14,381                        | -29%                                        |      |  |  |

|        | 7            | United Kingdom     |                      | 865                           | -32                                        |                      |                               | -25%                                        |      |  |  |

| 8      |              | Brazil             | 1,296                | 542                           | 23                                         |                      | 6,371                         | -6%                                         |      |  |  |

| 9      | 9            | China              | 3,195                | 465                           | 2369                                       |                      | 3,883                         | 332%                                        |      |  |  |

| 10     | 12           | Italy              | 1,238                |                               | 869                                        | 10,563               | 4,218                         | 88%                                         |      |  |  |

|        | Subt         | otal (top 10)      | 121,701              | 29,524                        |                                            | 1,251,730            | 364,247                       |                                             |      |  |  |

| -      | Total        | (163 countries)    | 138,292              | 31,713                        | -688                                       | 1,337,014            | 390,135                       |                                             | -17% |  |  |

|        |              | a percen-<br>total | 9.3                  | 930                           |                                            | 949                  | 9.36                          | D.                                          |      |  |  |

·Excludes hybrids

Source: Japanese Ministry of Finance: DATACLEST

#### INDUSTRY

64K DRAMs and 128K EPROMs in Short Supply

Semiconductor Makers Revise Plans for FY85 There have been shortages of 64K DRAMs and 128K EPROMs recently due to makers' rapid reductions in production. Major makers' 64K DRAM production, which reached 10 million units per month late last year, has declined to 1 million to 2 million units monthly. Some manufacturers have stopped production altogether. Inventories of 64K DRAMs are down sharply, and it is expected that the shortage of supply will become critical toward the end of this year.

Major semiconductor manufacturers have announced their financial statements for the first half of fiscal 1985, which started in April. Since their sales during the period decreased dramatically from the year before, sales and capital expenditure plans for fiscal 1985 have been revised downward. Major makers' revised production and investment plans are shown in the following table.

## MAJOR JAPANESE SEMICONDUCTOR MANUFACTURERS' REVISED FISCAL 1985 PLANS (Billions of Yen)

|                                                | Production      |                             |                                   |                 |                        | Capital Expenditure |         |                        |

|------------------------------------------------|-----------------|-----------------------------|-----------------------------------|-----------------|------------------------|---------------------|---------|------------------------|

|                                                | Initial<br>Plan | Pirst<br>Halt<br>Production | Change from<br>First Half<br>FY84 | Revised<br>Plan | Change<br>from<br>FY84 | Initial<br>Plan     | Revised | Change<br>from<br>FY84 |

| N&C                                            | 650             | 236                         | (190)                             | 510             | (144)                  | 140                 | 120     | (246)                  |

| Hitachi                                        | 540             | 215                         | (204)                             | 430             | (20%)                  | 130                 | 9.0     | 13181                  |