**Computer Structures: Readings and Examples**

#### McGraw-Hill computer science series

RICHARD W. HAMMING Bell Telephone Laboratories

EDWARD A. FEIGENBAUM Stanford University

Bell and Newell Computer Structures: Readings and Examples

Cole Introduction to Computing

Gear Computer Organization and Programming

Givone Introduction to Switching Circuit Theory

Hellerman Digital Computer System Principles

Kohavi Switching and Finite Automata Theory

Liu Introduction to Combinatorial Mathematics

Ralston Introduction to Computer Science

Rosen Programming Systems and Languages

Salton Automatic Information Organization and Retrieval

Watson Timesharing System Design Concepts

Wegner Programming Languages, Information Structures, and Machine

Organization

# **Computer Structures: Readings and Examples**

C. Gordon Bell

Professor of Computer Science and Electrical Engineering

Carnegie-Mellon University

Allen Newell

University Professor

Carnegie-Mellon University

New York St. Louis San Francisco Düsseldorf

London Mexico Panama Rio de Janeiro

Singapore Sydney Toronto

# To Brigham, Laura, Paul

#### Computer Structures: Readings and Examples

Copyright © 1971 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Library of Congress Catalog Card Number 75-109245

07 - 004357 - 4

$1\,2\,3\,4\,5\,6\,7\,8\,9\,0\quad HDBP\quad 7\,9\,8\,7\,6\,5\,4\,3\,2\,1\,0$

This book was set in News Gothic by Graphic Services, Inc., printed on permanent paper by Halliday Lithograph Corporation, and bound by The Book Press, Inc. The designer was Elliot Epstein; the drawings were done by John Cordes, J. & R. Technical Services, Inc. The editors were Richard Dojny and J. W. Maisel. William P. Weiss supervised production.

## **Preface**

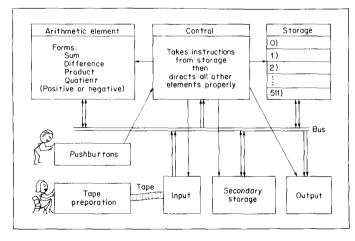

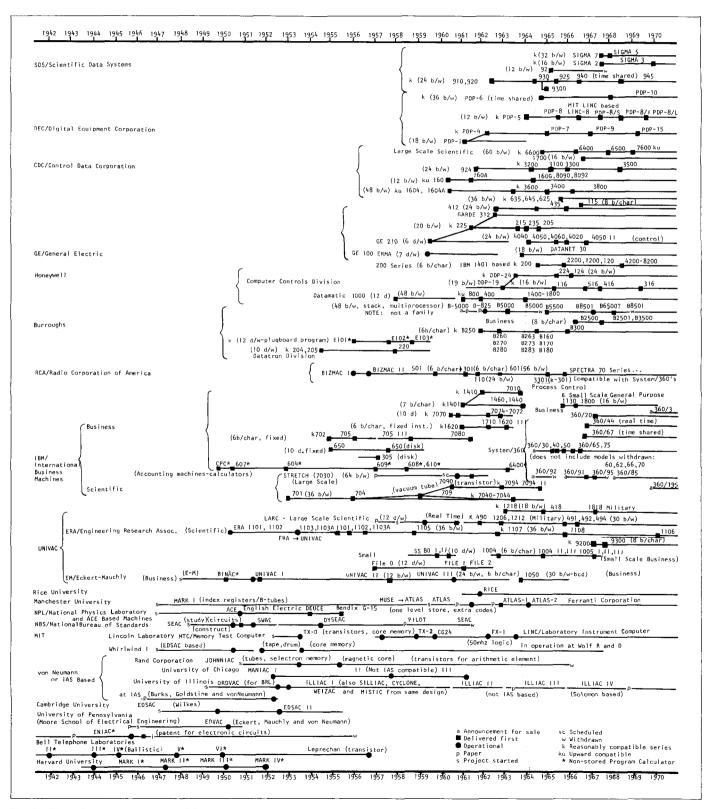

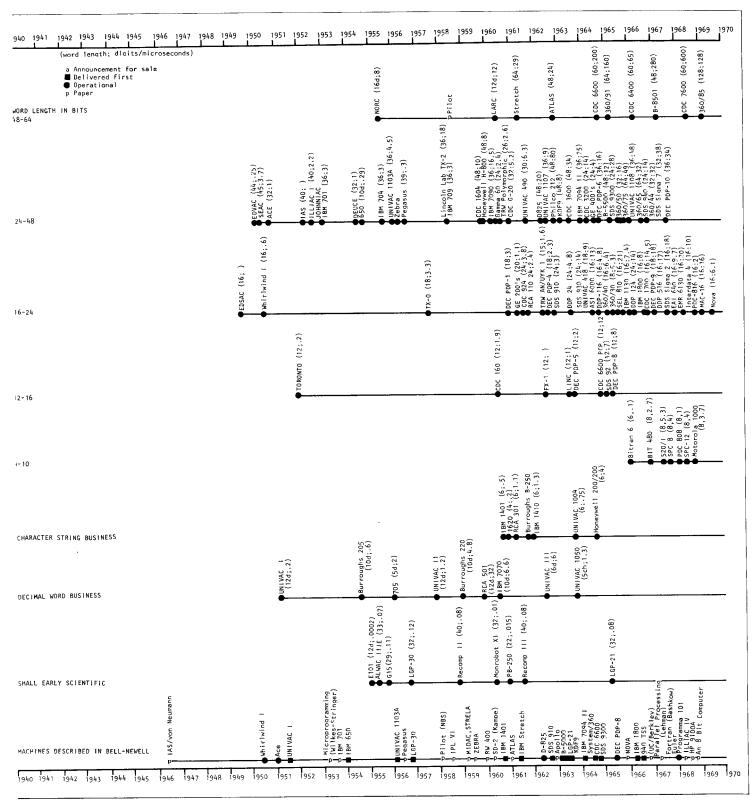

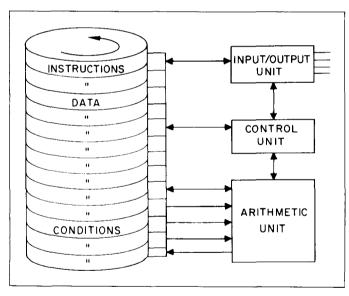

The structures that we call computer systems continue to grow in complexity, in size, and in diversity. This book is linked firmly to the nature of this growth. The book is about the upper levels of computer structure: about instruction sets, which define a computer system at the programming level; and about organizations of processors, memories, switches, input-output devices, controllers, and communication links, which provide the ultimate functioning system. These levels are just emerging into well-defined systems levels—with developed symbolic techniques of analysis and synthesis and accumulated engineering know-how, all expressed in a crystallized representation. These aspects of computer systems have always existed, of course, but only in rudimentary form. The classical four-box picture of a computer (arithmetic unit, memory, input-output, and control) is certainly an effective organization of components to process information. But multiple-processors hierarchies of memories and remote communications force the top level of organization into a distinct level, requiring analysis and rational design. Similarly, the 25 instructions of the IBM 701 computer (developed around 1953) is certainly an instruction set-indeed one worthy of study. But processors with dozens of registers and almost unlimited logical circuitry, again force the instruction set to become a topic of rational analysis and design.

This book is tied to the emergence of these upper levels of organization: eight years ago (a computer engineer's half dozen) would have been too early to write this book; eight years hence would be too late. Eight years ago the diversity and complexity of computer structures was not sufficient to justify the attention this book provides. This book would have been too thin. Eight years hence textbooks will exist that treat these levels systematically. This book will then appear too descriptive.

But right now, as these aspects of computer structure are emerging, and with systematic treatment still precluded, there is a need to make available material on these levels for systematic reference and study. Our choice has been to present a large set of examples, which illustrate the various design options and structural possibilities, both in instruction sets and in overall configurations. These examples are descriptions of actual computer systems, taken from the technical literature or from technical reports and manuals. Descriptions of actual systems are to be much preferred over idealized abstractions. The latter can reflect the real issues only after successful systematization.

Not only are the chapters about actual computers, they present much detail. The complexity of computers resides in part in their size and the multiplicity of their parts—e.g., to their having 200 instructions rather than 20, or having to service 50 Teletypes rather than 2. It seems essential to describe computer systems in their entirety, rather than via simplified vignettes. Again, this view stems from the existing state of the art. Eight years hence, it will not necessarily hold.

We fall from grace on all the above principles, providing occasionally descriptions of paper machines and partial descriptions of partial systems. But our feeling that detail and reality is important remains. This is why this book is so large; and fit for study rather than for reading.

The book presents a large number of examples. Variation needs to be presented along all the major dimensions that instruction sets and system configurations currently exhibit. Thus, as a glance at the table of contents will show, the examples in the book are hardly picked at random. The variation is empirical. It exists in the population of computers that have actually been built. This characteristic of the book stems, again, from our assessment that the upper levels of computer structure are still in an essentially descriptive and empirical state of development. However, as the book documents, ample variation occurs in existing computer systems. The evidence presented here should finally lay to rest the remarks—once echoed almost universally and still heard occasionally—that nothing has happened in computer structure since the von Neumann machine.

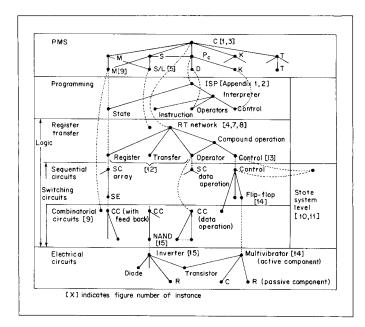

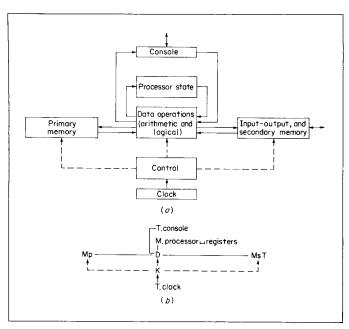

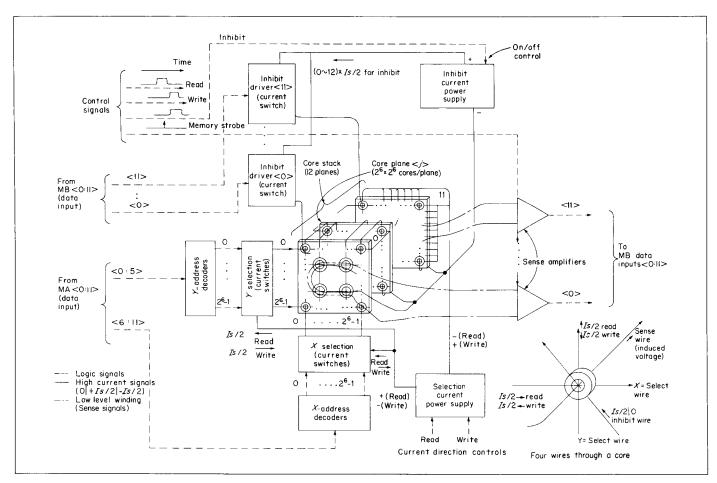

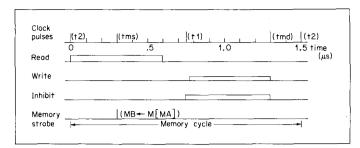

Dimensions of variations imply a framework, for dimensions do not by themselves arise from a population of systems. They require the aid, witting or not, of a conceptual framework. As the first three chapters of the book testify, we have most wittingly created a framework, and have had no hesitation in imposing it throughout the book. However, in keeping with our view already expressed, this framework is primarily descriptive. It has come inductively from the common lore, from our own experiences as designers, and from the effort of putting this book together. This attempt at systematization has given rise to two notations: one for instruction sets (ISP) and the other for configurations of major components (PMS). But, again, these notations are primarily descriptive.

So much for what the book actually tries to provide. What are our goals for it? The first is educational. There are three distinct populations of professionals whose education is to be served by this book: the computer engineer, who will design physical computer systems; the computer scientist, who is concerned primarily with the programming level and with various abstract views of information processing; and the electrical engineer, who sees computer systems simply as one part of a larger technology.

For all of these, we see no sense in talking of elementary versus advanced treatments of computer structure. There is surely "less" versus "more," but consistent with our view of the current art, no vertical stratification of education is possible in instruction sets and device configurations. It is sufficient, in the present day, for these aspects of computer systems to become accepted as worthy of study in their own right.

This book will hardly make easy fare for undergraduate students, who do not have an instructor somewhat skilled in the art that is being taught. However, this book is meant for study. A good instructor can, we feel, develop an excellent course (or part thereof) in computer structures, taking this book as the basic material. In addition to the three introductory chapters, Chapter 5 (on the DEC PDP-8), by providing a complete example of a computer system with descriptions at all systems levels, helps to tie the aspects of computer structure discussed in this book to the view students will pick up from a traditional course in logical design.

It goes without saying that for the computer engineer and designer, the material of this book should be fully assimilated. In designing a new computer system, or subsystem thereof, he should be familiar with all that this book has to offer—the design choices, the structural variations possible, the experiments of the past and

the design needs they attempted to satisfy. Given that systematic analysis does not yet exist, there is no substitute for extensive, critical understanding of the existing examples of designed systems. We assume the student of computer engineering comes to this book with a working knowledge of logical design. He should find it possible to realize many of the systems described in this book at the next lower levels of logic structure.

For the computer scientist, the levels of computer structure discussed in this book constitute a substantial part of what he should know about the physical devices that underlie his science. As we pass downward from these levels to lower ones—to register-transfer systems, sequential logic circuits, combinatory circuits, continuous circuits and on down—the relevance of each level gradually fades. The levels of this book, along with the register-transfer level constitute the main aspects of computer structure that the computer scientist must understand. It does not matter that they are, as yet, basically empirical and descriptive. The computer scientist undoubtedly will not be able to carry through the design of the systems described in this book in terms of the lower logic levels, but this is not necessary for an appropriate grasp of these upper levels of computer structure. Indeed, this is what it means for distinct systems levels to exist.

For the electrical engineer, this book undoubtedly presents more examples than he cares to know (or needs to). But an appropriate sampling, plus the overview presented in the first three chapters, is appropriate to give him some insight into the elaborate growth that has occurred on top of the basic digital technology created within electrical engineering.

The student of systems engineering may also find the material presented here useful, as an example of a class of complex systems which has evolved several distinct levels of representation. Again, the book undoubtedly presents too massive a dose of detail for him, but the overview in the first chapters, plus a sampling throughout the space of computer systems, should prove highly instructive.

We have goals for the book in addition to the educational ones. We think the book can serve as a useful reference for the practicing computer engineer. The time is past when every computer engineer knows about all computer systems because he has lived through all of computer history. That position is now reserved for those of us who are past forty (and still active). For the rest, a source book that provides the cumulated design experience of the field is a useful substitute, especially so if it contains enough detail so that a designer can reasonably evaluate the actual computer systems that embody a particular design alternative.

Behind the goal of the book as a guide for the practicing computer designer lies the feeling that the field of computer engineering needs to develop a sense of history and of looking to the past for guidance. The fantastic advance in basic logic technology—in speed, cost, and reliability— makes each day seem an absolutely new one. But, of course, it is not. Many alternative designs have been tried out in past systems, in ways relevant to current design. Thus, we have the goal of saving some of the past in a form accessible to the future needs of computer design. This goal is mixed with a certain archival feeling. Many of the systems in this book have never been documented, other than in manuals and various elementary how-to programming books.

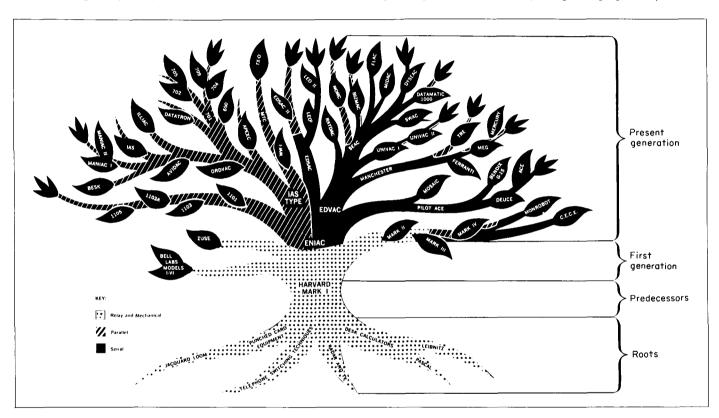

A final goal comes from our feelings as computer scientists that the variety of computer systems is a phenomena worthy of study in its own right. This book carries, therefore, an invitation to taxonomy—to asking how to classify the diversity of forms of computer systems that are coming into existence. Taxonomic endeavors usually take place in a field of natural systems, particularly biological systems. It may seem strange that a domain of artificial systems calls for taxonomic activity. But the demand for empirical classification exists whenever there is a population of significant size and rich structure. Rudimentary classification efforts have occurred for many populations of artifacts—for ships, for aircraft, for houses. This book should amply confirm that computer systems are complex and diverse enough—and undergoing enough continual proliferation and evolution—to command significant taxonomic endeavor.

Enough is said in the first two chapters about the new notations introduced in the book, so that nothing substantive need be added here. We apologize for inflicting new notation on the reader. We feel that good notations are really quite important for the aspects of computer structure described in this book. Much would be gained by the whole field of computers—by users, programmers, engineers, planners, buyers, sellers, manufacturers, students, and scientists—if relatively uniform notations came into common use. Although we have no illusions about the perfection of the notations we have introduced, we would be most happy if they cause a rise in concern for standard notations and nomenclature.

A large number of distinct systems are described in substantial detail. We have redescribed many of the systems in the common notation introduced in the book. The accuracy of all these descriptions is a major problem. Even where the papers are reproduced from the literature, this problem of accuracy remains—although then it is not ours alone. Even though we have taken pains to obtain accurate information on the systems and to portray them faithfully in our various descriptions and figures, there is no way we can be responsible for their ultimate accuracy. The PMS and ISP figures, in particular, cannot be guaranteed to be accurate representations of the systems they purport to describe. Ultimately, one would like to have simulation languages for such notations and to verify (up to the usual criteria of a debugged program) that a system given by, say, an ISP description, simulates the behavior of the target machine. But that day is still far off.

Our most fundamental acknowledgment is to the contributors to this volume, not only for the articles they have written, but for the computers they have designed and built, thereby creating a population of fascinating artifacts worthy of study. An additional reason for reprinting their articles rather than simply describing their computer systems is the importance of having available the views of the designers themselves about the nature of their systems.

The research on the basic ideas underlying the notations was supported by Advanced Research Projects Agency of the Office of the Secretary of Defense (F 44620-67-C-0058) and is monitored by the Air Force Office of Scientific Research.

We would like to extend an acknowledgment to the organizations that have produced all of these computers, oftentimes it would seem in defiance of the laws of economics. Perhaps, as the old saw has it, a computer manufacturer is simply a computer's way of breeding another computer. This might account for the tenacity

shown by computer manufacturers in spawning the vast numbers of computer systems that provide our field of study. Within this general acknowledgment, we would like to extend a very specific one to all the people in these organizations who helped make information available to us—the manuals, photographs, dates, etc., that this book has demanded in such great quantity.

We are indebted to the students who have read and criticized the various PMS and ISP figures: Richard Dove, Wayne Kohl, Michael Knudsen, Paul Mobus, and Charles Pfferkorn. Ken Fitzgerald and Anita Jones of IBM were kind enough to read the introduction to the IBM System/360.

Professor David L. Parnas initially reviewed the text and contents, thus providing many helpful suggestions. Our other colleagues, especially Professors Angel Jordan, Alan Perlis, Herbert Simon and Everard M. Williams deserve a special thanks for their patience and encouragement.

Finally, we would like to thank those who were a part of the machine that assembled the book: the editors of McGraw-Hill; Mrs. Mary Ross who assembled the bibliography, figures, and contributor articles; Mrs. Mildred Sisko who typed the PMS and ISP Appendix; and especially Mrs. Dorothy Josephson who not only typed nearly all drafts of the book, but also the final PMS figures, and ISP Appendices.

C. Gordon Bell Allen Newell

# **Acknowledgments**

R. H. Allmark and J. R. Lucking: Design of an Arithmetic Unit Incorporating a Nesting Store, Proceedings of the International Federation of Information Processing Congress 1962, pp. 694–698, North Holland Publishing Co., Amsterdam, Holland, by permission from American Federation of Information Processing Societies (AFIPS), Spartan Books, Washington, D.C.

R. L. Alonso, H. Blair-Smith, and A. L. Hopkins: Some Aspects of the Logical Design of a Control Computer, A Case Study, *Transactions on Electronic Computers*, vol. EC-12, no. 6, pp. 687-697, December, 1963, by permission of the authors and the Institute of Electrical and Electronics Engineers (IEEE).

James P. Anderson, Samuel A. Hoffman, Joseph Shifman, and Robert J. Williams: D825—A Multiple Computer System for Command and Control, Proceedings of the AFIPS Fall Joint Computer Conference, vol. 22, pp. 86–96, 1962, by permission from AFIPS, Spartan Books, Washington, D.C. The authors acknowledge:

The authors wish to acknowledge the outstanding efforts of their many colleagues at Burroughs Laboratories who have contributed so well and in so many ways to all stages of D825 design, development, fabrication, and programming. It would be impossible to cite all of these efforts. The authors also wish to acknowledge the contributions of Mr. William R. Slack and Mr. William W. Carver, also of Burroughs Laboratories. Mr. Slack has been closely associated with the D825 from its original conception to its implementation in hardware and software. Mr. Carver made important contributions to the writing and editing of this paper.

George H. Barnes, Richard M. Brown, Maso Kato, David J. Kuck, Daniel L. Slotnick, and Richard A. Stokes: The ILLIAC IV Computer, Transactions on Computers, vol. C-17, no. 8, pp. 746–757, August 1968, by permission of the authors and the IEEE. The authors acknowledge:

This work was supported in part by the Department of Computer Science, University of Illinois, Urbana, Illinois, and in part by the Advanced Research Projects Agency as administered by the Rome Air Development Center, Griffiss Air Force Base, Rome, New York, under Contract USAF 30 (602)4144.

The authors are pleased to acknowledge their indebtedness to the group at the Westinghouse Electric Corporation that initiated the parallel computer effort. The work of W. C. Borck, A. B. Carroll,

J. R. Hudson, W. H. Leonard, R. C. McReynolds, and G. Shapiro formed the basis for the subsequent efforts. Of particular importance is the work of J. G. Gregory in tuning the conceptual design to the real world of technology.

Theodore R. Bashkow, Azra Sasson, and Arnold Kronfeld: System Design of a FORTRAN Machine, Transactions on Electronic Computers, vol. EC-16, no. 4, pp. 485–499, August 1967, by permission of the authors and the IEEE. The authors acknowledge:

This research is supported by the Air Force Office of Scientific Research Contract AF19(628)—2798.

G. A. Blaauw and F. P. Brooks, Jr.: The Structure of System/360, Part I—Outline of the Logical Structure, IBM Systems Journal, vol. 3, no. 2, pp. 119–135, 1964, by permission from the IBM Systems Journal.

Erich Bloch: The Engineering Design of the Stretch Computer, Proceedings of the Eastern Joint Computer Conference, 1959, pp. 48–58, by permission of the author and the Institute of Electrical and Electronics Engineers. The author acknowledges:

The efforts and contributions of many people have gone into the engineering design of the Stretch computer. To mention all would be impossible. However, the following individuals and their groups were responsible for the units indicated; Mr. R. T. Blosk for the Instruction Unit, Mr. J. F. Dirac for the Look-ahead Units, Messrs. J. A. Hipp and O. L. MacSorley for the Arithmetic Units, and Mr. L. O. Ulfsparre for the Memory Bus. The Systems Development was under the guidance of Messrs. S. W. Dunwell and R. E. Merwin.

Arthur W. Burks, Herman H. Goldstine, and John von Neumann: Preliminary Discussion of the Logical Design of an Electronic Computing Instrument, "Collected Works of John von Neumann," vol. V, pp. 34–79, General Editor: A. H. Taub, Macmillan Company, by permission from Pergamon Press, New York, 1963. The authors acknowledge:

This report has been prepared in accordance with the terms of Contract W-36-034-0RD-7481 between the Research and Development Service, Ordnance Department, U.S. Army and the Institute for Advanced Study.

The authors wish to express their thanks to Dr. John Tukey, of Princeton University, for many valuable discussions and suggestions.

John W. Carr III: UNIVAC Scientific (1103A) Instruction Logic, pp. 77–83; IBM 650 Instruction Logic, pp. 93–98; Instruction Logic of the Soviet  $Strela\ (Arrow),\ pp.\ 111-115;\ Instruction\ Logic\ of\ the\ MIDAC,\ pp.\ 115-121,$ chap. 2, Programming and Coding, "Handbook of Automation, Computation, and Control," vol. 2, edited by Eugene M. Grabbe, Simon Ramo, and Dean Wooldridge, Copyright © 1959 John Wiley & Sons, Inc., New York, reprinted by permission.

J. Presper Eckert, Jr., James R. Weiner, H. Frazer Welsh, and Herbert F. Mitchell: The UNIVAC System, American Institute of Electrical Engineers-Institute of Radio Engineers Conference, pp. 6-16, December, 1951, by permission of the authors and the IEEE. The authors acknowledge:

The UNIVAC System has been an over-all company project and hundreds of people have participated. It is, therefore, difficult to acknowledge the contributions of individuals. However, special mention must be made of the contributions of Mr. H. Lukoff, Mr. E. I. Blumenthal, Mr. L. D. Wilson, and Mr. J. D. Chapline, Jr. To the Census Bureau a great debt of gratitude is owed for their continuous support of the project.

W. S. Elliott, C. E. Owen, C. H. Devonald, and B. G. Maudsley: The Design Philosophy of Pegasus, A Quantity-production Computer, Proceedings of the Institution of Electrical Engineers, London, Pt. B, vol. 103, Supplement 2, pp. 188-196, 1956, by permission of the Institution of Electrical Engineers. The authors acknowledge:

The authors would like to acknowledge the contributions that Mr. C. Strachey and Dr. D. B. Gillies, of the National Research Development Corporation, and Dr. J. M. Bennett and Mr. T. G. H. Braunholtz, of Ferranti, Ltd., made to the logical design of Pegasus: particular thanks are due to Mr. C. Strachey for originating the order code.

They also thank Ferranti, Ltd., and the National Research Development Corporation for permission to publish the paper.

R. R. Everett: The Whirlwind I Computer, Review of Electronic Digital Computers, Joint Computers American Institute of Electrical Engineers-Institute of Radio Engineers Conference, pp. 70-74, February, 1952, by permission of the author and the IEEE.

Thomas W. Kampe: The Design of a General-purpose Microprogramcontrolled Computer with Elementary Structure, Institute of Radio Engineers, Transactions on Electronic Computers, vol. EC-9, no. 2, pp. 208-213, June, 1960, by permission of the author and the IEEE. The author acknowledges:

The author wishes to thank his co-designers, R. Compton and T. Hayata, for their assistance during the design of the SD-2 computer and for their suggestions on this paper.

T. Kilburn, D. B. G. Edwards, M. J. Lanigan, and F. H. Sumner: Onelevel Storage System, Institute of Radio Engineers Transactions, vol. EC-11, no. 2, pp. 223–235, April, 1962, by permission of the authors and the IEEE. The authors acknowledge:

The authors gratefully acknowledge the contributions made to this work by all members of the Atlas computer team at both Manchester University and Ferranti Ltd.

B. W. Lampson, W. W. Lichtenberger, and M. W. Pirtle: A User Machine in a Time-sharing System, Proceedings of the Institute of Electrical and Electronics Engineers, vol. 54, no. 12, pp. 1766-1774, December, 1966, by permission of the authors and the IEEE. The authors acknowledge:

The work for this paper was supported in part by the Advanced Research Projects Agency, Department of Defense, Contract SD-185.

The software portion of the system was designed and written in part by L. P. Deutsch, who is entitled to equal credit with the authors for the ideas in this paper. L. Barnes also contributed significantly to the final result.

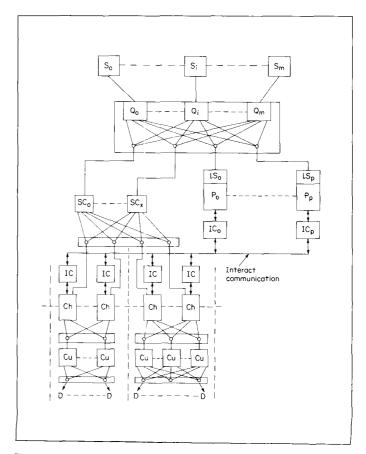

M. Lehman: A Survey of Problems and Preliminary Results Concerning Parallel Processing and Parallel Processors, Proceedings of the Institute of Electrical and Electronics Engineers, vol. 54, no. 12, pp. 1889-1901, December, 1966, by permission of the author and the IEEE. The author acknowledges:

This paper reports on a group activity in which each individual member had his own specific assignments and in addition participated in regular discussions on all aspects of the project. Credit is therefore due to all members of the group which, during the period covered by the contents of this paper, included G. C. Driscoll, J. M. Lee, A. P. Mullery, J. L. Rosenfeld, H. P. Schlaeppi, and M. Weitzman. I should also like to express my sincere thanks to Dr. H. A. Ernst for the constructive criticism, advice, and encouragement offered during preparation of this paper. My sincere thanks are also due to members of the Graphics and Design Department at the Thomas J. Watson Research Center, and in particular to G. Massi and Mrs. M. J. LaMarre for their preparation of the charts and figures. Last, my thanks to Mrs. J. Galto for her infinite patience in the repeated retypings of the manuscript.

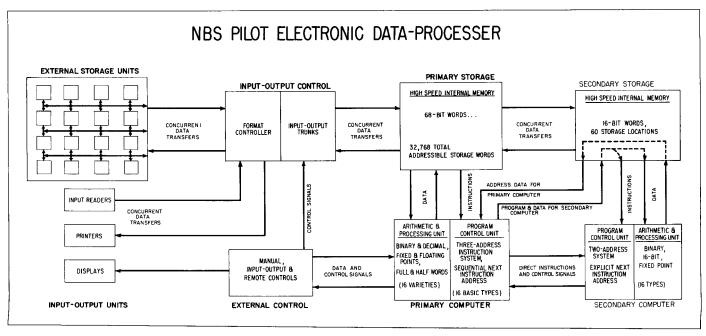

A. L. Leiner, W. A. Notz, J. L. Smith, and A. Weinberger: PILOT, The NBS Multicomputer System, Proceedings of the Eastern Joint Computer Conference, 1958, pp. 71-75, by permission of the authors and the IEEE. The authors acknowledge:

The authors wish to acknowledge the valuable contributions of their colleagues H. Loberman and W. Youden, who helped to develop the logical design and programming procedures for this system.

William Lonergan and Paul King: Design of the B 5000 System, Datamation, vol. 7, no. 5, pp. 28-32, May, 1961, by permission of, published and Copyrighted © 1961 by F. D. Thompson Publications, Inc., Greenwich, Conn.

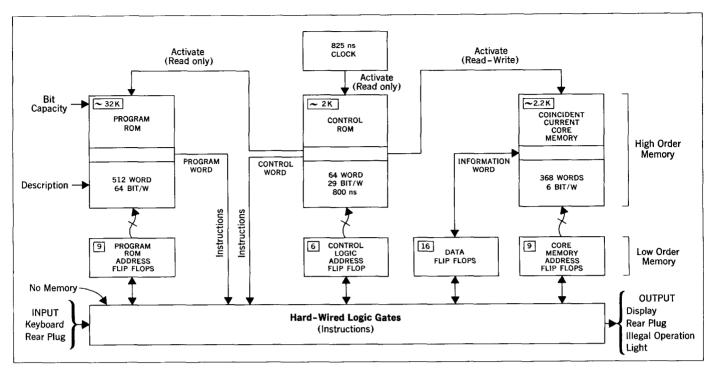

Richard E. Monnier, Thomas E. Osborne, and David S. Cochran: The HP Model 9100A Computing Calculator. This chapter is a compilation of three articles: A New Electronic Calculator with Computerlike Capabilities, by Richard E. Monnier, pp. 3–9; Hardware Design of the Model 9100A Calculator, by Thomas E. Osborne, pp. 10–13; and Internal Programming of the 9100A Calculator, by David S. Cochran, pp. 14–16, which appeared in the Hewlett-Packard Journal, volume 20, no. 1, September, 1968, by permission of the Hewlett-Packard Journal.

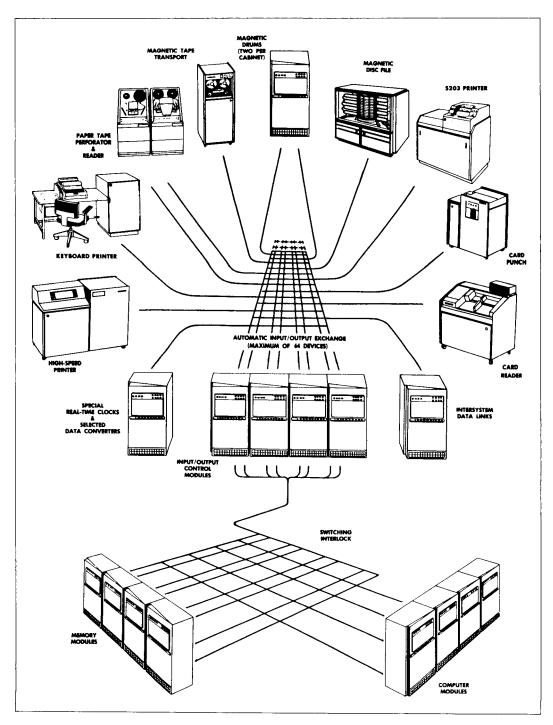

R. E. Porter: The RW-400—A New Polymorphic Data System, Datamation, vol. 6, no. 1, pp. 8–14, January/February, 1960, by permission of, published and Copyrighted © 1960 by F. D. Thompson Publications, Inc., Greenwich, Conn.

J. C. Shaw, A. Newell, H. A. Simon, and T. O. Ellis: A Command Structure for Complex Information Processing, Western Joint Computer Conference 1958, by permission of the authors and the IEEE.

W. Y. Stevens: The Structure of System/360, Part II—System Implementations, *IBM Systems Journal*, vol. 3, no. 2, pp. 136–143, 1964, by permission from the *IBM Systems Journal*.

James E. Thornton: Parallel Operation in the Control Data 6600, Proceedings of the AFIPS Fall Joint Computer Conference, Pt. II, vol. 26, pp. 33–40, 1964, by permission from AFIPS, Spartan Books, Washington, D.C.

W. L. van der Poel: ZEBRA, A Simple Binary Computer, Proceedings of an International Conference on Information Processing, Paris, UNESCO House, June, 1959, pp. 361–365, by permission from AFIPS, Spartan Books, Washington, D.C.

Helmut Weber: A Microprogrammed Implementation of EULER on IBM System/360 Model 30, Communications of the Association for Computing Machinery, vol. 10, no. 9, pp. 549–558, September, 1967, Copyright © 1967 Association for Computing Machinery, Inc., by permission of the author and the Association for Computing Machinery, Inc. The author acknowledges:

I wish to thank Jack Carman, who wrote the I/O Control Program and the Operating System linkage for the EULER system and Miss Sheila Morrison who helped prepare the figures. I am also grateful for the valuable criticism offered by the referee, W. C. McGee, as well as by Professor N. Wirth and E. Satterthwaite.

J. H. Wilkinson: The Pilot ACE, by permission from Automatic Digital Computation, pp. 5-14, National Physical Laboratory, Teddington, England, March 25-28, 1953.

M. V. Wilkes and J. B. Stringer: Micro-programming and the Design of the Control Circuits in an Electronic Digital Computer, *Proceedings of the Cambridge Philosophical Society*, Pt. 2, vol. 49, pp. 230–238, April, 1953, by permission of the authors and the Cambridge Philosophical Society, Cambridge, England. The authors acknowledge:

The authors wish to express their thanks to Mr. A. L. Freedman and Mr. W. Renwick for assisting them in clarifying a number of points, and to Professor D. R. Hartree, F.R.S., for his generous help with the preparation of the paper.

Joseph E. Wirsching: NOVA: A List-oriented Computer, Datamation, vol. 12, no. 12, pp. 41–43, December, 1966, by permission of, published and Copyrighted © 1966 by F. D. Thompson Publications, Inc., Greenwich, Conn. The author acknowledges:

This work was performed under the auspices of the U.S. Atomic Energy Commission.

Several organizations have contributed to the writing and production of this book by giving us permission to use material from their publications. In many cases they have also supplied us with original copies. We have credited their text, tables, pictures, and diagrams when they are used. This cooperation has been invaluable. The specific organizations are:

Adams's Associates: Computer Characteristics Quarterly. (Adams, 1966–1968)

Computers and Automation magazine

Control Data Corporation, 8100 34th Avenue South, Minneapolis, Minnesota

Datamation magazine

Digital Equipment Corporation, 146 Main Street, Maynard, Massachusetts

Hewlett-Packard Company, 1501 Page Mill Road, Palo, California

International Business Machines Corporation, White Plains and Pough-keepsie, New York

Massachusetts Institute of Technology, Cambridge, Massachusetts

National Science Foundation

Olivetti Underwood Corporation, 1 Park Avenue, New York, New York

Scientific Data Systems, 1649 Seventeenth Street, Santa Monica, California

# **Contributors**

R. H. Allmark R. L. Alonso James P. Anderson Theodore R. Bashkow George H. Barnes G. A. Blaauw H. Blair-Smith Erich Bloch F. P. Brooks, Jr. Richard M. Brown Arthur W. Burks John W. Carr III David S. Cochran C. H. Devonald D. B. G. Edwards J. Presper Eckert, Jr. W. S. Elliott T. O. Ellis R. R. Everett Herman H. Goldstine Samuel A. Hoffman A. L. Hopkins Thomas W. Kampe Maso Kato T. Kilburn Paul King David J. Kuck Arnold Kronfeld B. W. Lampson M. J. Lanigan A. L. Leiner M. Lehman

W. W. Lichtenberger William Lonergan J. R. Lucking B. G. Maudsley Herbert F. Mitchell Richard E. Monnier W. A. Notz Thomas E. Osborne C. E. Owen M. W. Pirtle R. E. Porter Azra Sasson J. C. Shaw Joseph Shifman H. A. Simon Daniel L. Slotnick

J. L. Smith W. Y. Stevens Richard A. Stokes J. B. Stringer F. H. Sumner James E. Thornton W. L. van der Poel John von Neumann Helmut Weber A. Weinberger James R. Weiner H. Frazer Welsh M. V. Wilkes J. H. Wilkinson Robert J. Williams Joseph E. Wirsching

|        | Preface<br>Contributors    |                                           | v<br>xiii   | Acknowledgments |                                   |     |  |

|--------|----------------------------|-------------------------------------------|-------------|-----------------|-----------------------------------|-----|--|

| Part 1 | The Structure of Computers |                                           |             |                 |                                   |     |  |

|        | Chapter 1<br>Chapter 2     | Introduction The PMS and ISP Descriptive  | 3           | Chapter 3       | The Computer Space                | 37  |  |

|        | •                          | Systems                                   | 15          |                 |                                   |     |  |

| Part 2 | The Instructi              | ion-set Processor: Main-line compute      | rs          |                 |                                   |     |  |

|        | Section 1                  | Processors with One Address per Ins       | truction 89 |                 |                                   |     |  |

|        | Chapter 4                  | Preliminary Discussion of the Logi-       |             | Chapter 16      | The LGP-30 and LGP-21             |     |  |

|        | -                          | cal Design of an Electronic Com-          |             | Chapter 17      | IBM 650 Instruction Logic—John W. |     |  |

|        |                            | puting Instrument—Arthur W.               |             |                 | Carr III                          |     |  |

|        |                            | Burks, Herman H. Goldstine, and           |             | Chapter 41      | The IBM 7094 I, II                |     |  |

|        |                            | John von Neumann                          | 92          | Chapter 8       | The UNIVAC System—J. Presper      |     |  |

|        | Chapter 5                  | The DEC PDP-8                             | 120         |                 | Eckert, Jr., James B. Weiner,     |     |  |

|        | Chapter 6                  | The Whirlwind I Computer—                 |             |                 | H. Frazer Welsh, and Herbert F.   |     |  |

|        |                            | R. R. Everett                             | 137         |                 | Mitchell                          | 157 |  |

|        | Chapter 33                 | The IBM 1800                              |             | Chapter 23      | One-level Storage System—T.       |     |  |

|        | Chapter 7                  | Some Aspects of the Logical Design        |             |                 | Kilburn, D. B. G. Edwards, M. J.  |     |  |

|        |                            | of a Control Computer: A Case             |             |                 | Lanigan, and F. H. Summer         |     |  |

|        |                            | Study—R. L. Alonso, H. Blair-Smith,       | 1.40        | Chapter 34      | The Engineering Design of the     |     |  |

|        | Chapter 42                 | and A. L. Hopkins The SDS 910-9300 Series | 146         |                 | Stretch Computer—Erich Bloch      |     |  |

|        | Section 2                  | Processors with a General-register St     |             |                 |                                   |     |  |

|        | Chapter 9                  | The Design Philosophy of Pegasus,         |             |                 | Structure—G. A. Blaauw and F. P.  |     |  |

|        |                            | A Quantity-production Computer—           |             |                 | Brooks, Jr.                       |     |  |

|        |                            | W. S. Elliott, C. E. Owen, C. H.          |             | Chapter 10      | An 8-bit-character Computer       | 184 |  |

|        | <i>(</i> 1)                | Devonald, and B. G. Maudsley              | 171         | Chapter 39      | Parallel Operation in the Control |     |  |

|        | Chapter 43                 | The Structure of System/360,              |             |                 | Data 6600—James E. Thornton       |     |  |

|        |                            | Part I—Outline of the Logical             |             |                 |                                   |     |  |

<sup>&</sup>lt;sup>1</sup>This is a "virtual" contents, which means that because many of the computers are relevant to more than one part and section, we have used italic type to indicate a nonsequential mapping for computers placed out of "physical" order. The reader might read (reference) the book according to the virtual order.

| Section 1  | Section 1 Processors with Greater than One Address per Instruction 191        |                 |                |                                                                      |             |  |  |  |

|------------|-------------------------------------------------------------------------------|-----------------|----------------|----------------------------------------------------------------------|-------------|--|--|--|

| Chapter 11 | •                                                                             | 193             | Chapter 14     | Instruction Logic of the MIDAC—                                      |             |  |  |  |

| Chapter 12 | <ul><li>ZEBRA, A Simple Binary Computer</li><li>—W. L. van der Poel</li></ul> | 200             | Chapter 15     | John W. Carr III  Instruction Logic of the Soviet                    | 209         |  |  |  |

| Chapter 13 |                                                                               | 200             | Chapter 13     | Strela (Arrow)—John W. Carr III                                      | 213         |  |  |  |

| Omptor 1   | tion Logic—John W. Carr III                                                   | 205             |                | January John VV. Carr III                                            | 210         |  |  |  |

| Chapter 38 |                                                                               |                 |                |                                                                      |             |  |  |  |

| •          | Data System—R. E. Porter                                                      |                 |                |                                                                      |             |  |  |  |

| Section 2  | Processors Constrained by a Cyclic,                                           | Primary Memory  | 216            |                                                                      |             |  |  |  |

| Chapter 18 | The OLIVETTI Programma 101 Desk<br>Calculator                                 |                 | Chapter 9      | The Design Philosophy of Pegasus, A<br>Quantity-production Computer— |             |  |  |  |

| Chapter 12 | <ul><li>ZEBRA, A Simple Binary Computer</li><li>—W. L. van der Poel</li></ul> |                 |                | W. S. Elliott, C. E. Owen, C. H. Devonald, and B. G. Maudsley        |             |  |  |  |

| Chapter 1  | The LGP-30 and LGP-21                                                         | 217             | Chapter 17     | IBM 650 Instruction Logic—                                           |             |  |  |  |

| Chapter 1  | I The Pilot ACE—J. H. Wilkinson                                               |                 |                | John W. Carr III                                                     | 220         |  |  |  |

| Chapter 8  | ·                                                                             |                 | Chapter 26     | NOVA: A List-oriented Computer—                                      |             |  |  |  |

|            | Eckert, Jr., James R. Weiner,                                                 |                 |                | Joseph E. Wirsching                                                  |             |  |  |  |

|            | H. Frazer Welsh, and Herbert F.<br>Mitchell                                   |                 |                |                                                                      |             |  |  |  |

| Section 3  | Processors for Variable-length-string                                         | Data 224        |                |                                                                      |             |  |  |  |

| Chapter 1  | 8 The IBM 1401                                                                | 225             | Chapter 10     | An 8-bit-character Computer                                          |             |  |  |  |

| Section 4  | Desk Calculator Computers: Keyboar                                            | d Programmable  | Processors w   | vith Small Memories 235                                              |             |  |  |  |

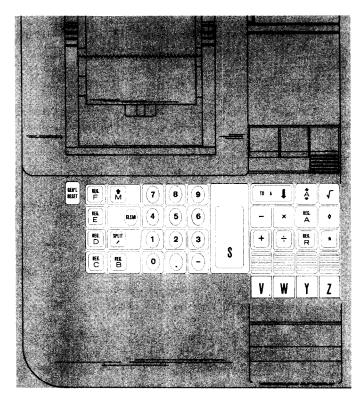

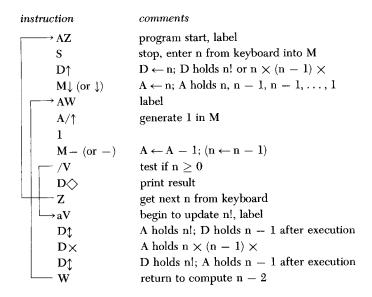

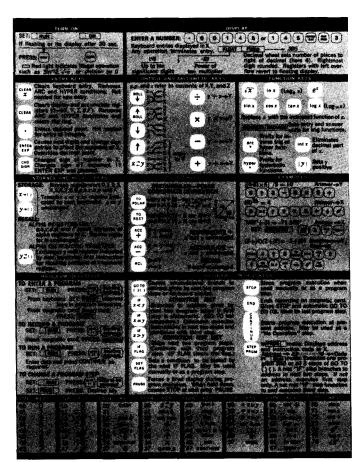

| Chapter 1  | 9 The OLIVETTI Programma 101                                                  |                 |                | Calculator—Richard E. Monnier,                                       |             |  |  |  |

|            | Desk Calculator                                                               | 237             |                | Thomas E. Osborne, and David S.                                      |             |  |  |  |

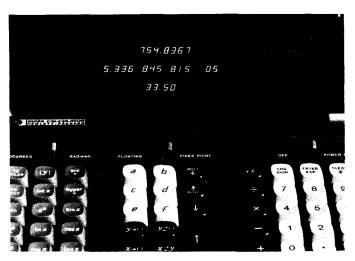

| Chapter 2  | 0 The HP Model 9100A Computing                                                |                 |                | Cochran                                                              | <b>24</b> 3 |  |  |  |

| Section 5  | Processors with Stack Memories (Ze                                            | ro Addresses pe | r Instruction) | 257                                                                  |             |  |  |  |

| Chapter 2  | 1 Design of an Arithmetic Unit In-<br>corporating a Nesting Store—R. H.       |                 |                | Joseph Shifman, and Robert J.<br>Williams                            |             |  |  |  |

|            | Allmark and J. R. Lucking                                                     | 262             | Chapter 30     | A Command Structure for Complex                                      |             |  |  |  |

| Chapter 2  | 2 Design of the B 5000 System—                                                |                 |                | Information Processing—J. C. Shaw,                                   |             |  |  |  |

| ompter -   |                                                                               |                 |                |                                                                      |             |  |  |  |

|            | William Lonergan and Paul King                                                | 267             | _              | A. Newell, H. A. Simon, T. O. Ellis                                  |             |  |  |  |

Chapter 36 D825—A Multiple-computer System

$for\ Command\ and\ Control {\color{red} \color{red} - James\ P.}$

Anderson, Samuel A. Hoffman,

Chapter 32 Microprogrammed Implementation of

30—Helmut Weber

EULER on IBM System/360 Model

|        |                                                    | NAME OF THE PARTY |                 |                 |                                                                                                   |     |  |  |

|--------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------|-----|--|--|

|        | Section 6                                          | Processors with Multiprogramming A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bility 274      |                 |                                                                                                   |     |  |  |

|        | Chapter 23                                         | burn, D. B. G. Edwards, M. J. Lanigan, and F. H. Sumner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 276             | Chapter 24      | William Lonergan and Paul King<br>A User Machine in a Time-sharing<br>System—B. W. Lampson, W. W. |     |  |  |

|        | Chapter 21                                         | Design of the B 5000 System—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                 | Lichtenberger, and M. W. Pirtle                                                                   | 29. |  |  |

| Part 4 | The Instruct                                       | ion-set Processor Level: Special-func                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | tion Processors |                 |                                                                                                   |     |  |  |

|        |                                                    | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                 |                                                                                                   |     |  |  |

|        | Section 1                                          | Processors to Control Terminals and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Secondary Mem   | ories (Input-or | utput Processors) 303                                                                             |     |  |  |

|        | Chapter 41                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | Chapter 33      | The IBM 1800                                                                                      |     |  |  |

|        | Chapter 43                                         | The Structure of System/360,<br>Part I—Outline of the Logical<br>Structure/G. A. Blaauw and F. P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | Chapter 25      | The DEC 338 Display Processor                                                                     | 305 |  |  |

|        | Section 2                                          | Processors for Array Data 315                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                 |                                                                                                   |     |  |  |

|        | <del></del>                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                 |                                                                                                   |     |  |  |

|        | _                                                  | NOVA: A List-oriented Computer— Joseph E. Wirsching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 316             |                 | Brown, Maso Kato, David J. Kuck,<br>Daniel L. Slotnick, and Richard E.                            | 22  |  |  |

|        | Chapter 27                                         | The ILLIAC IV Computer—George H. Barnes, Richard M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                 | Stokes                                                                                            | 320 |  |  |

|        | Section 3 Processors Defined by a Microprogram 334 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                 |                                                                                                   |     |  |  |

|        | Chapter 28                                         | of the Control Circuits in an Elec-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | Chapter 20      | Calculator—Richard E. Monnier,                                                                    |     |  |  |