THE BUNKER-RAMO CORPORATION

# II 340 SYSTEM MANUAL

| SDO6411<br>JUNE 1964                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SYSTEM MAR | NUAL                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------|

| the second of th | the party of the p |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

| Company of the Compan |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | \$ 1111   25 1111   25 1111                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | THE RESERVE OF THE PERSON NAMED IN COLUMN TWO IS NOT THE PERSON NAMED IN COLUMN TWO IS NAMED IN COL |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MICHAEL STREET, STREET |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | \$ <b>\  \  \  \  \  \  \  \  \  \  \  \  \  \</b> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | \$ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | \$ [ ]   \$ [ ]   \$ [ ]                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 事 [ ]                                              |

THE BUNKER-RAMO CORPORATION

SYSTEM MANUAL

SD06411 JUNE 1964

FOR ADDITIONAL INFORMATION, OR FOR THE ADDRESS OF YOUR NEAREST BUNKER-RAMO OFFICE, CONTACT:

INFORMATION SERVICES PROCESS CONTROL SYSTEMS THE BUNKER-RAMO CORPORATION

8433 FALLBROOK AVENUE CANOGA PARK, CALIFORNIA 91304 TELEPHONE 213-346-6000

The Bunker-Ramo Corporation reserves the right to modify this equipment in order to improve its performance and operational flexibility.

#### TABLE OF CONTENTS

#### INTRODUCTION

| SECTION  | I      | SUMMARY OF SYSTEM CHARACTERISTICS             |

|----------|--------|-----------------------------------------------|

| SECTION  | II     | DESIGN FEATURES                               |

| SECTION  | III    | HARDWARE CONFIGURATIONS 6                     |

| SECTION  | IV     | SOFTWARE FEATURES10                           |

| SECTION  | v      | PROGRAMMING FEATURES                          |

| SECTION  | VI .   | INTRODUCTION TO 340 SUBSYSTEMS27              |

| SECTION  | VII    | BASIC COMPUTER29                              |

| SECTION  | VIII . | MEMORY SUBSYSTEM                              |

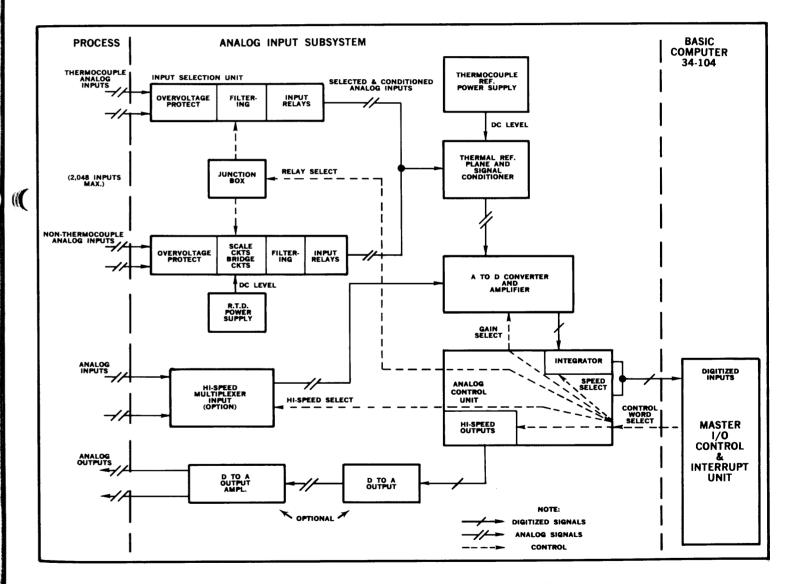

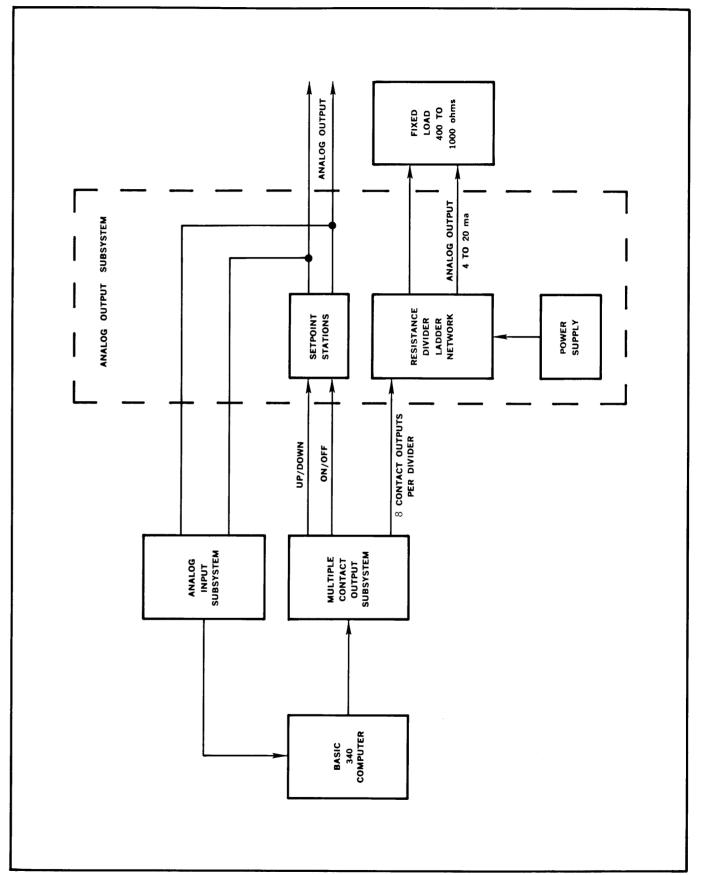

| SECTION  | IX     | ANALOG INPUT SUBSYSTEM41                      |

| SECTION  | х      | ANALOG OUTPUT SUBSYSTEM 46                    |

| SECT ION | XI     | CONTACT INPUT SUBSYSTEM49                     |

| SECTION  | XII    | CONTACT OUTPUT SUBSYSTEM 53                   |

| SECTION  | XIII   | INTERRUPT SUBSYSTEM55                         |

| SECTION  | XIV    | OPERATOR'S CONSOLE AND FAIL-SAFE OPERATION 59 |

| SECTION  | xv     | INPUT/OUTPUT PERIPHERAL DEVICES64             |

| SECTION  | XVI    | TYPICAL OPERATING INSTRUCTIONS                |

|          |        | SHMMARY OF OPERATIONS                         |

©1964 THE BUNKER-RAMO CORPORATION

### LIST OF ILLUSTRATIONS

| Figure Number | Title                                                              | Page  |

|---------------|--------------------------------------------------------------------|-------|

| Frontispiece  | Typical 340 Control Computer System Frontis                        | piece |

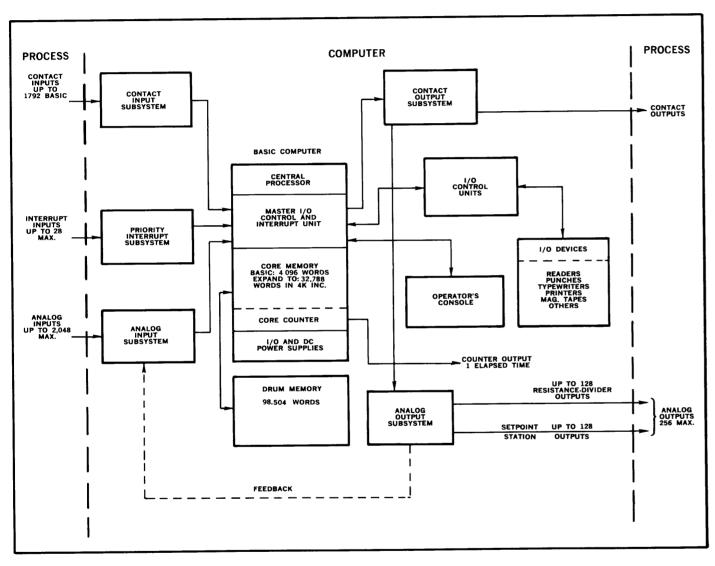

| 3-1 (1 of 3)  | 340 Hardware Configurations                                        | 7     |

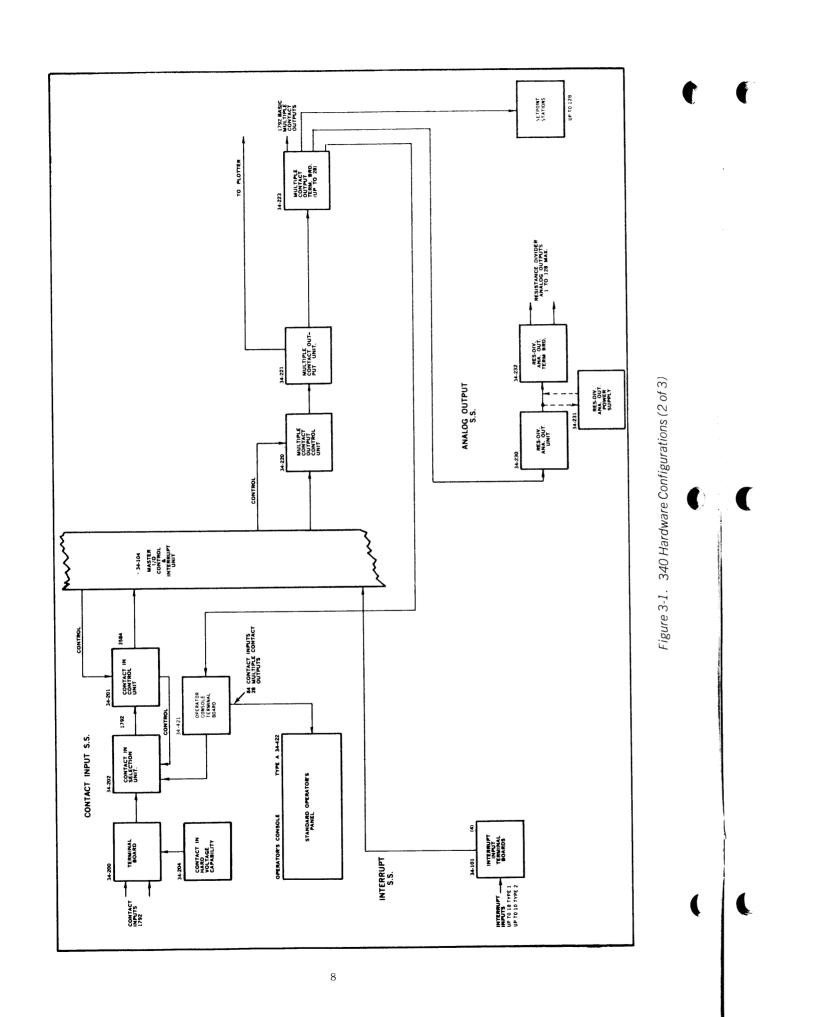

| 3-1 (2 of 3)  | 340 Hardware Configurations                                        | 8     |

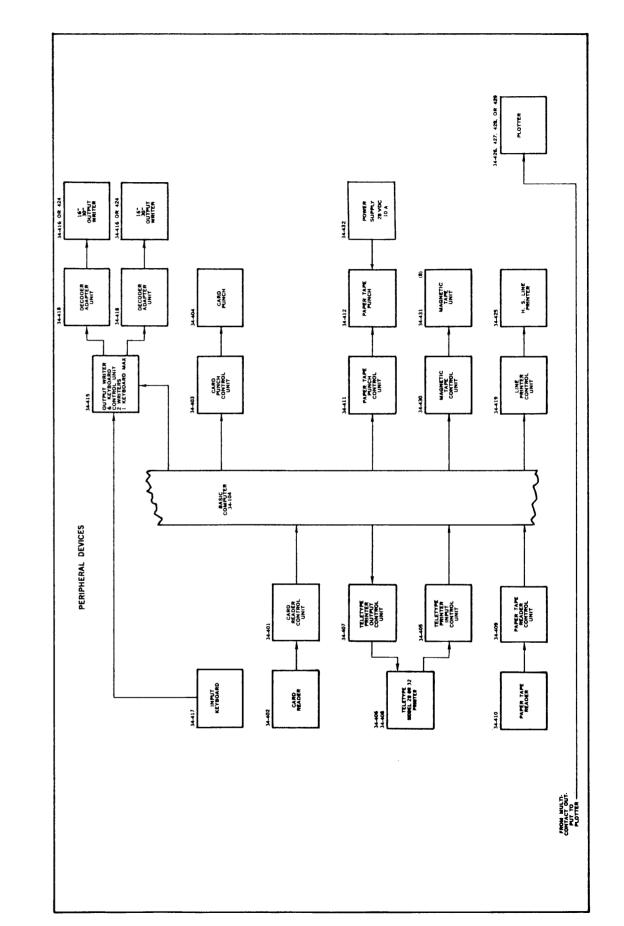

| 3-1 (3 of 3)  | 340 Hardware Configurations                                        | 9     |

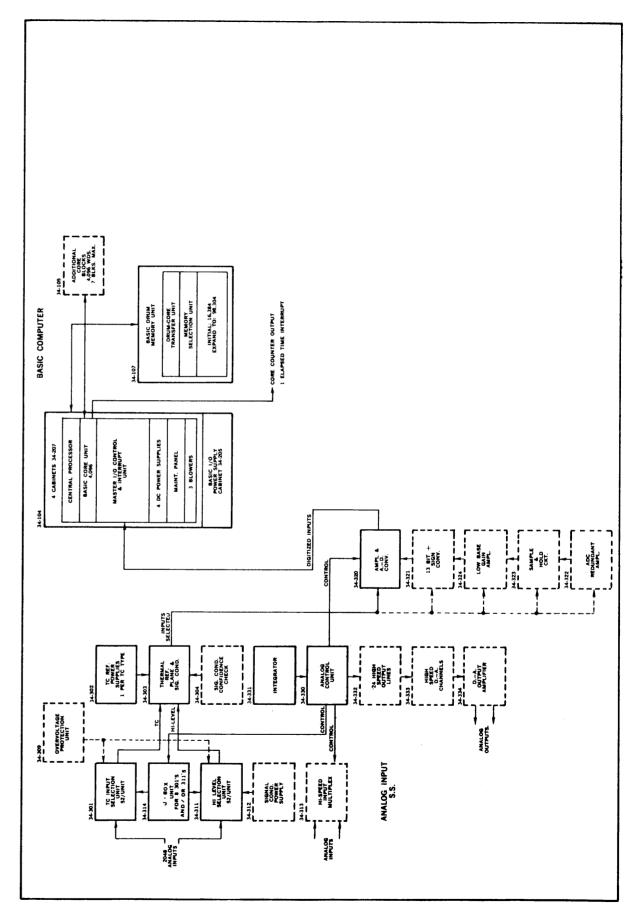

| 6 - 1         | 340 System, Simplified Block Diagram                               | 28    |

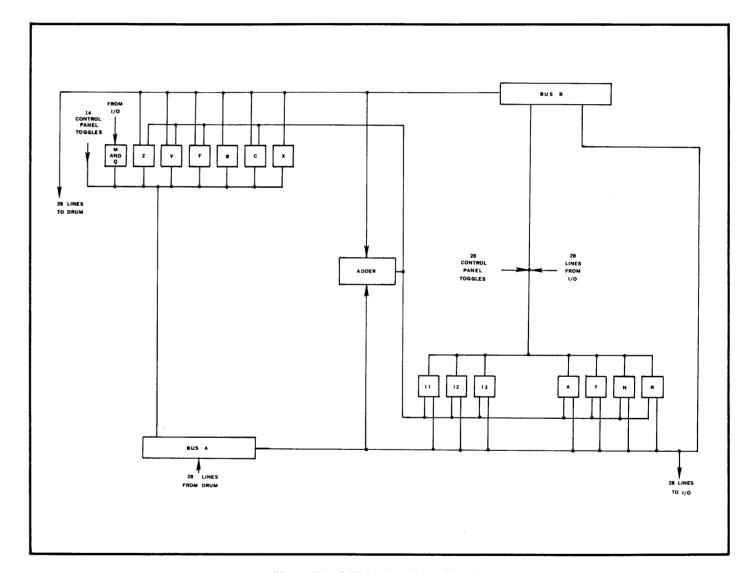

| 7 - 1         | 340 Register Data Flow Diagram                                     | 33    |

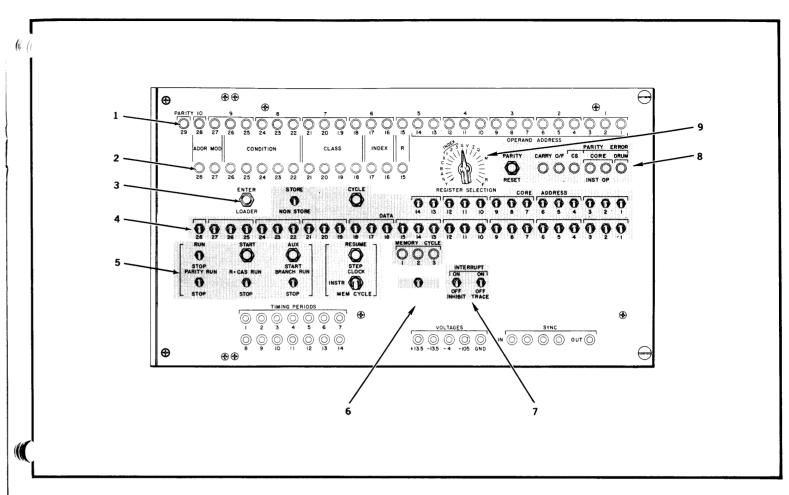

| 7-2           | 340 Maintenance Panel                                              | 35    |

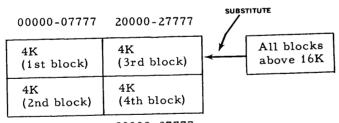

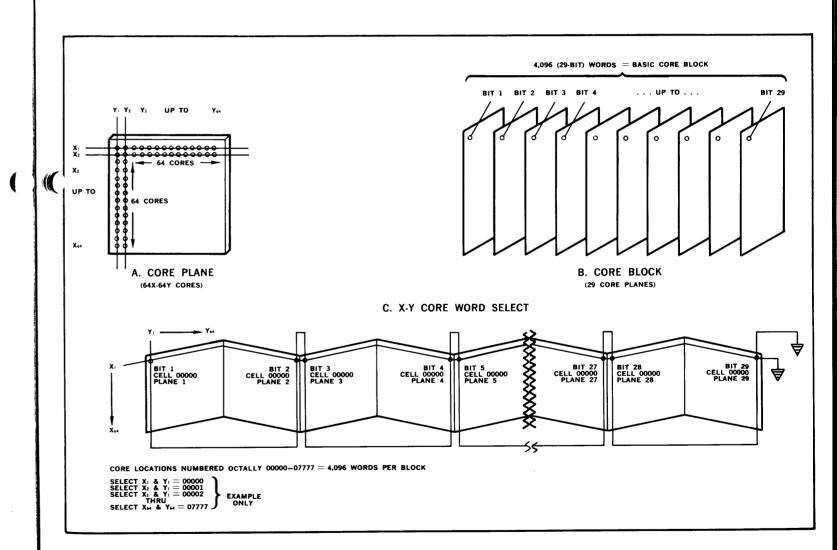

| 8-1           | Core Memory Organization                                           | 37    |

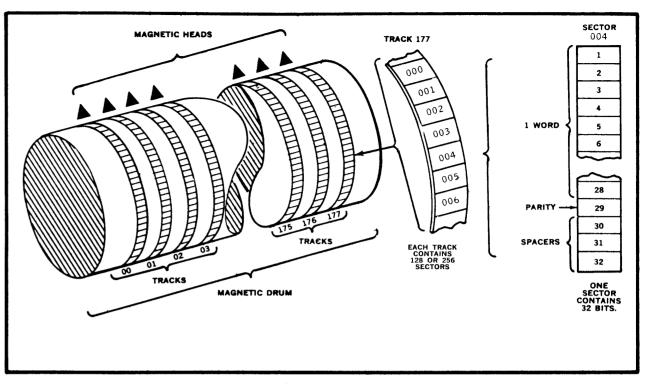

| 8-2           | Drum Memory Organization                                           | 39    |

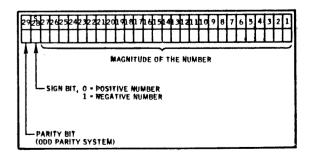

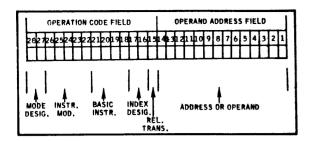

| 8-3           | Data Word Format                                                   | 39    |

| 8-4           | Instruction Word Format                                            | 40    |

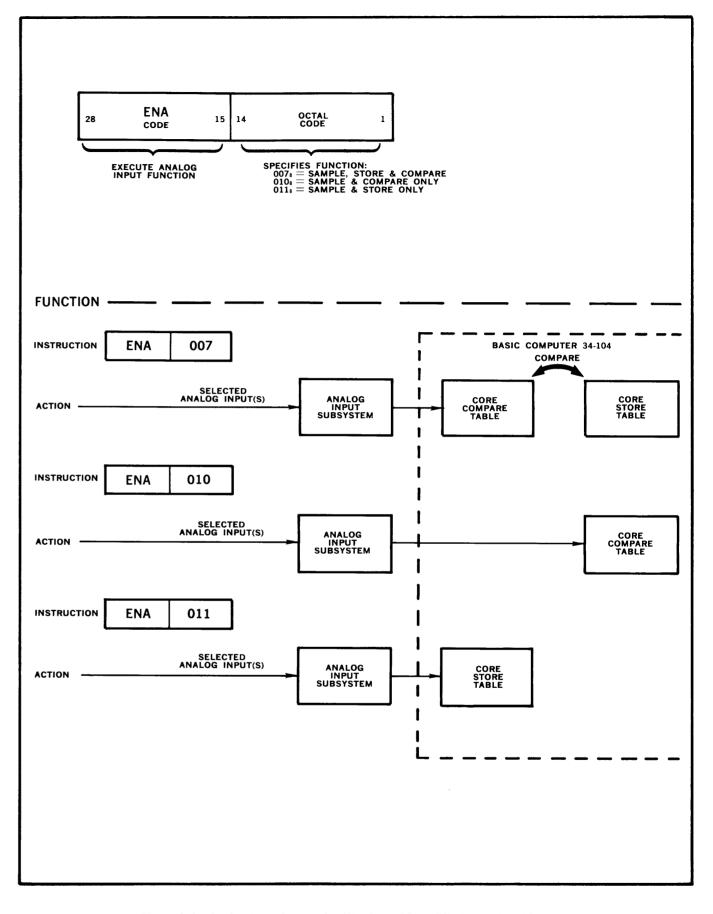

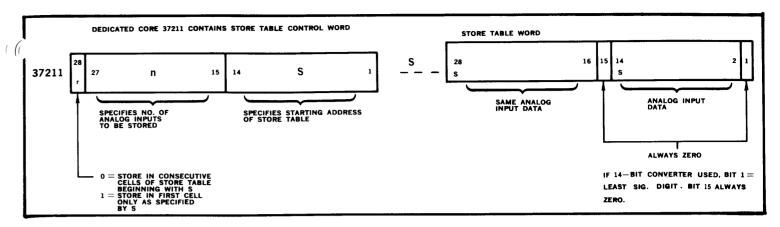

| 9-1           | Analog Input Instruction Words and Simplified Functional Diagram   | 43    |

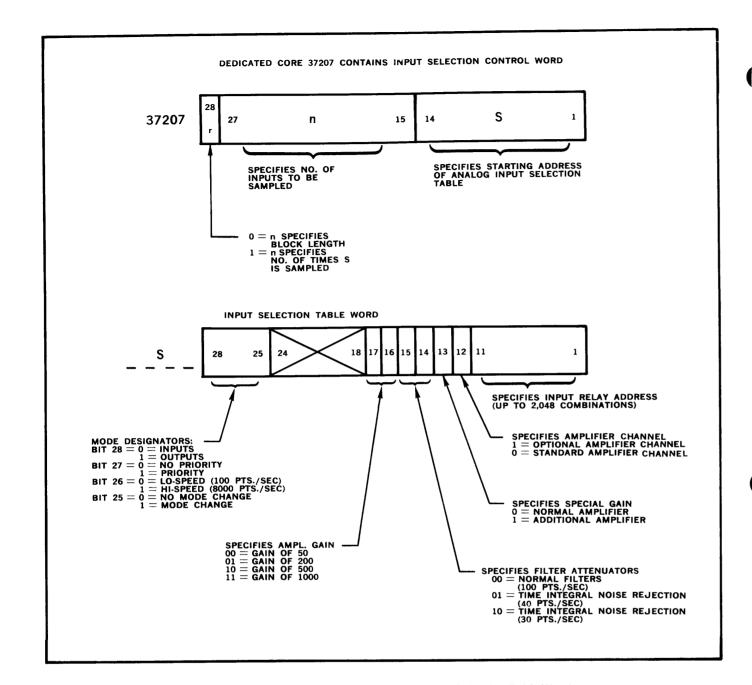

| 9-2           | Analog Input Selection Control and Selection Table Words           | 44    |

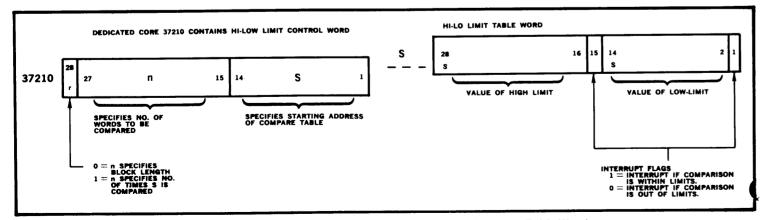

| 9-3           | Analog Input Compare Table Control and Compare Table Words         | 44    |

| 9-4           | Analog Input Store Table Control and Store Table Words             | 45    |

| 9-5           | Analog Input Subsystem, Simplified Functional Diagram              | 45    |

| 10-1          | Analog Output Subsystem, Simplified Diagram                        | 47    |

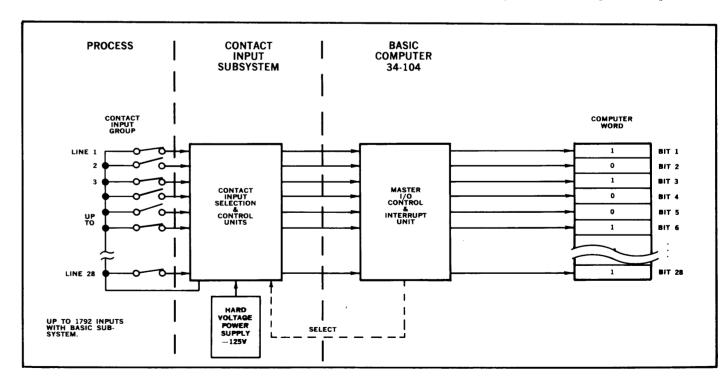

| 11-1          | Basic Contact Input Subsystem and Group Input Handling             | 49    |

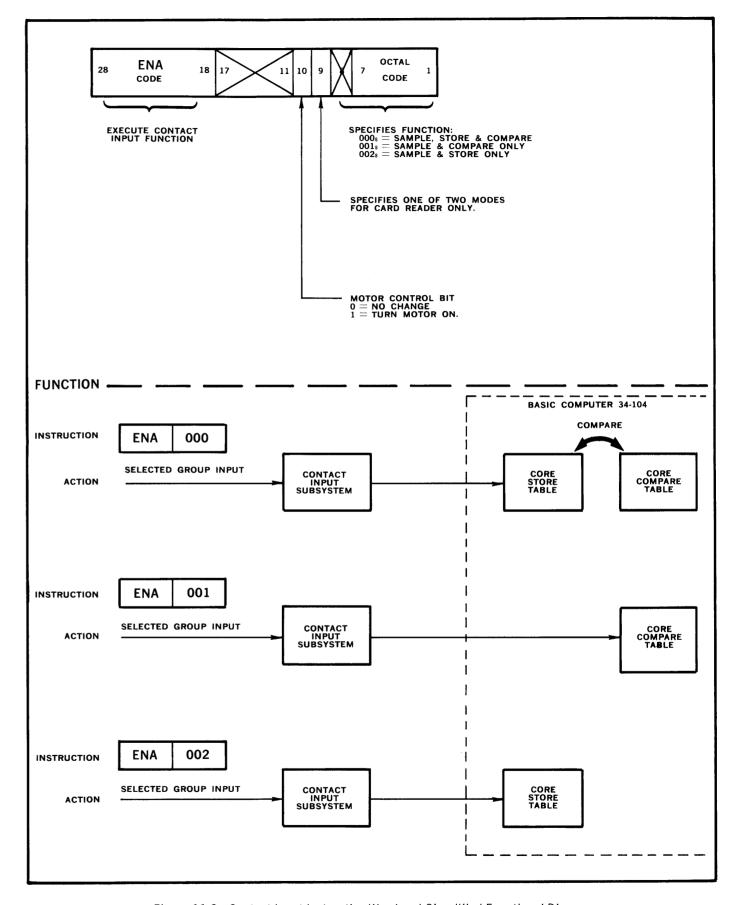

| 11-2          | Contact Input Instruction Word and Simplified Functional Diagram   | 51    |

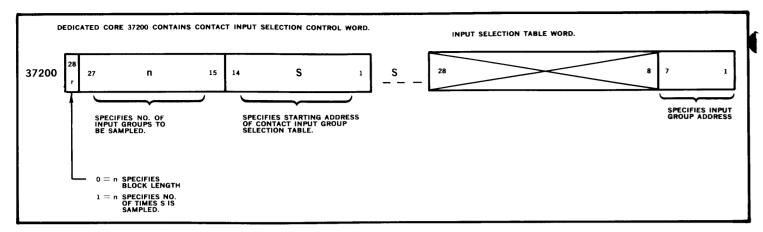

| 11-3          | Contact Input Selection Control and Selection Table Words          | 52    |

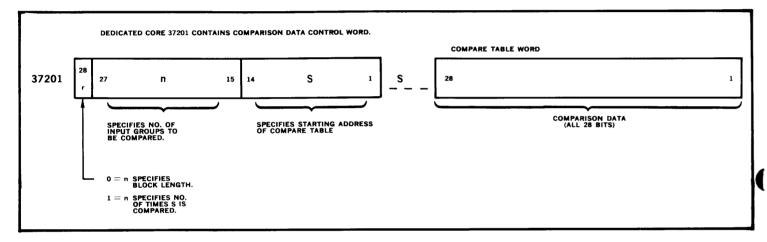

| 11-4          | Contact Input Compare Table Control and Compare Table Words        | 52    |

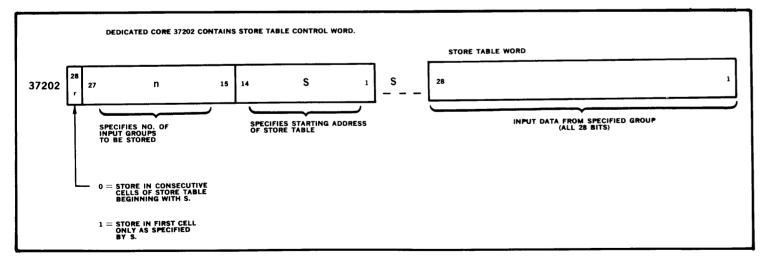

| 11-5          | Contact Input Store Table Control and Store Table Words            | 52    |

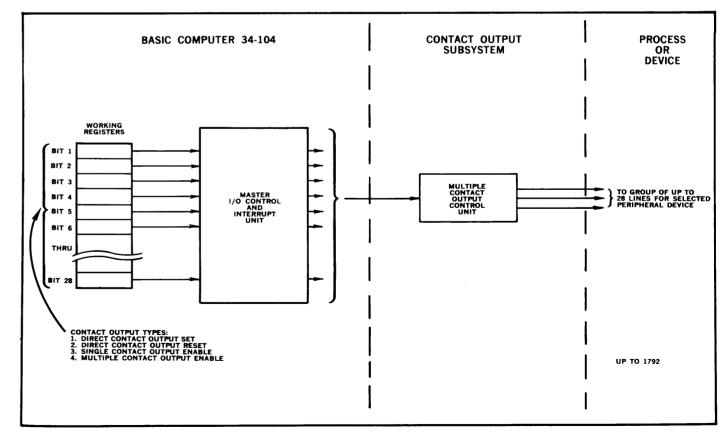

| 12-1          | Basic Contact Output Subsystem and Group Output Handling           | 53    |

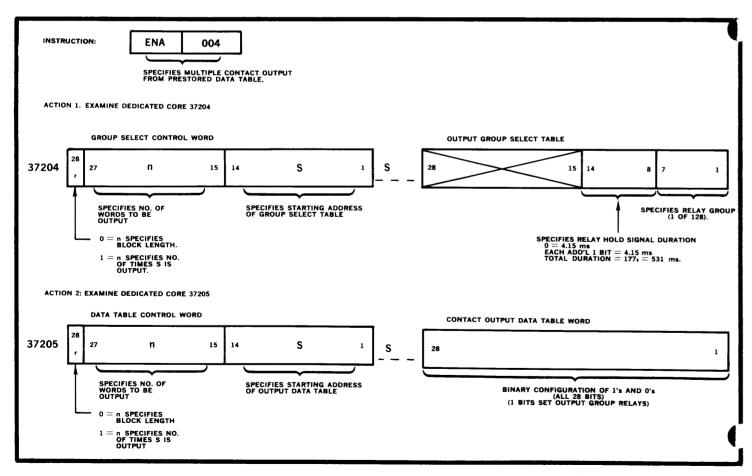

| 12-2          | Multiple Contact Output Enable Control and Data Table Words        | 54    |

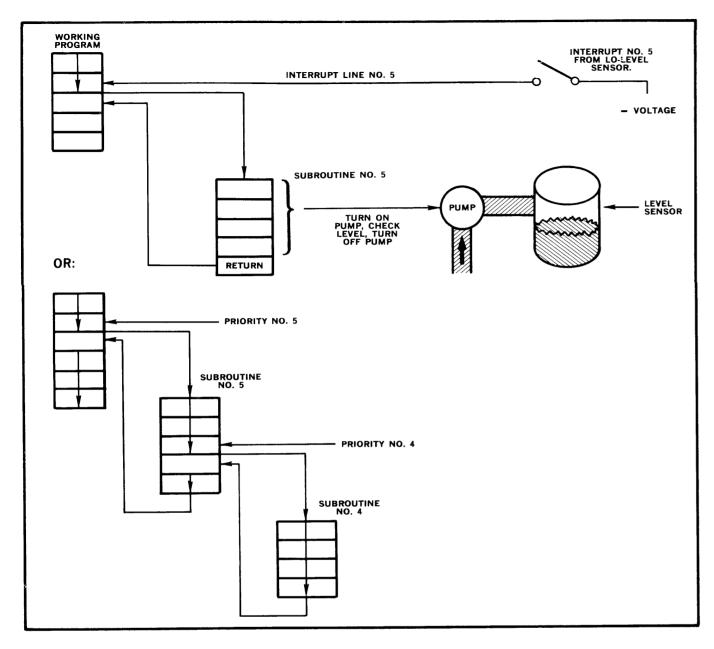

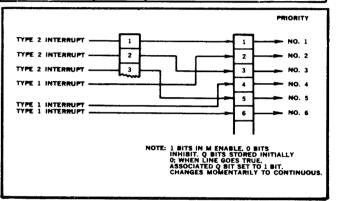

| 13-1          | Simplified Interrupt Action                                        | 56    |

| 13-2          | Simplified Interrupt Priority Establishment                        | 57    |

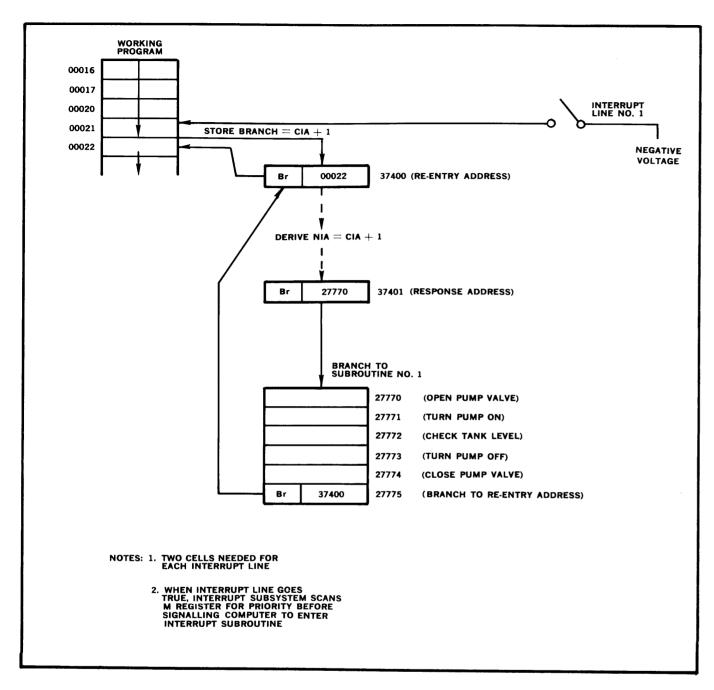

| 13-3          | Interrupt Re-entry and Response Address Techniques                 | 58    |

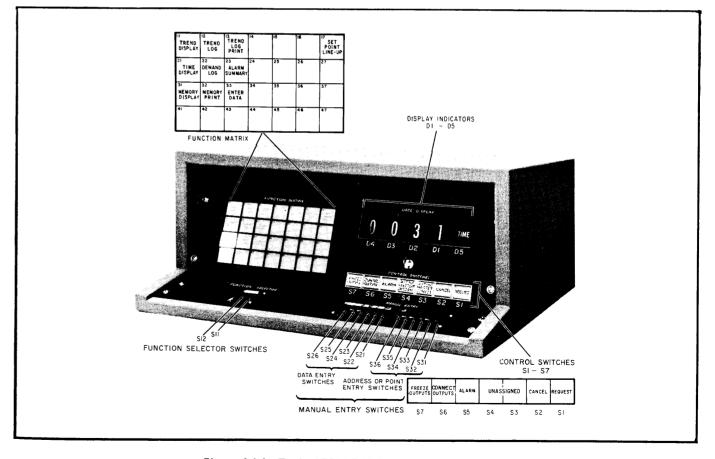

| 14-1          | Typical 340 Operator's Control Panel                               | 61    |

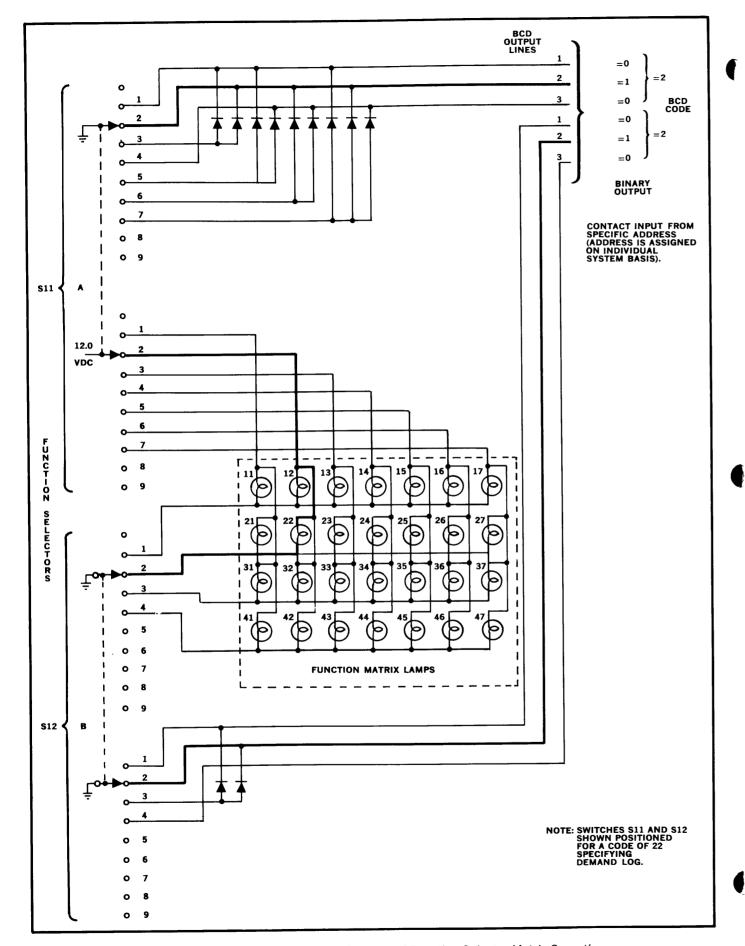

| 14-2          | Simplified Schematic Diagram of Function Selector-Matrix Operation | 62    |

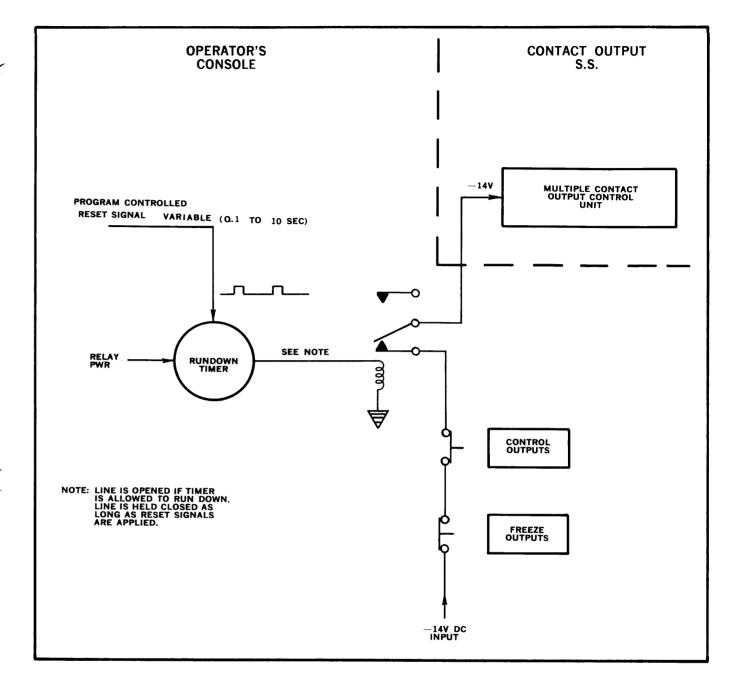

| 14-3          | Simplified Fail-Safe and Reset Timer Operation                     | 63    |

|  | , |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

### INTRODUCTION

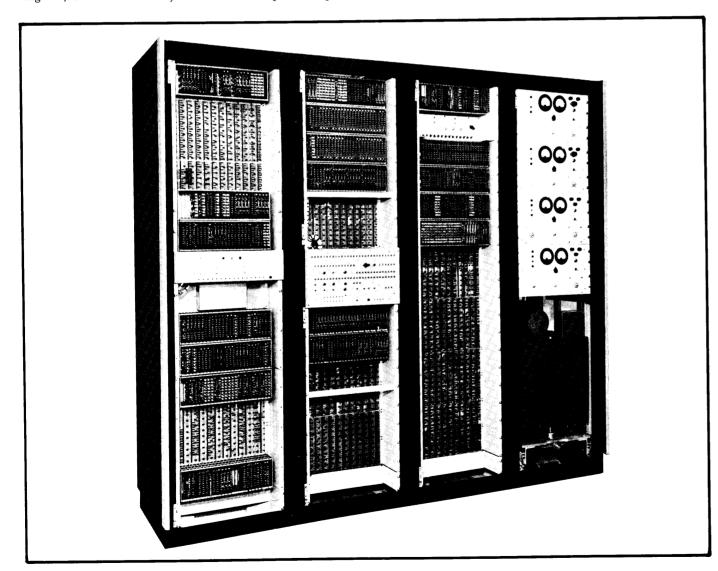

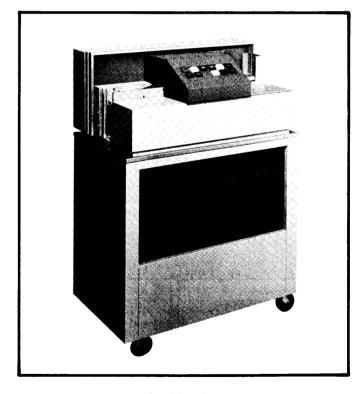

The Bunker-Ramo Model 340 Control Computer System is a 28-bit word, parallel-operated, digital computer designed specifically for use in process control applications. This system combines the most recent advances in computer technology with the present day requirements of high-speed automatic control. Design of the 340 is based on experience gained from successful Bunker-Ramo control computer installations and field-proven techniques.

The 340 employs solid-state components, modular construction, and plug-in circuit cards. This balanced design provides protected and expandable memory, special operations for on-line control problems, and analog and contact input/output flexibility. These and other features simplify and reduce requirements for programming and maintaining a digital control computer system.

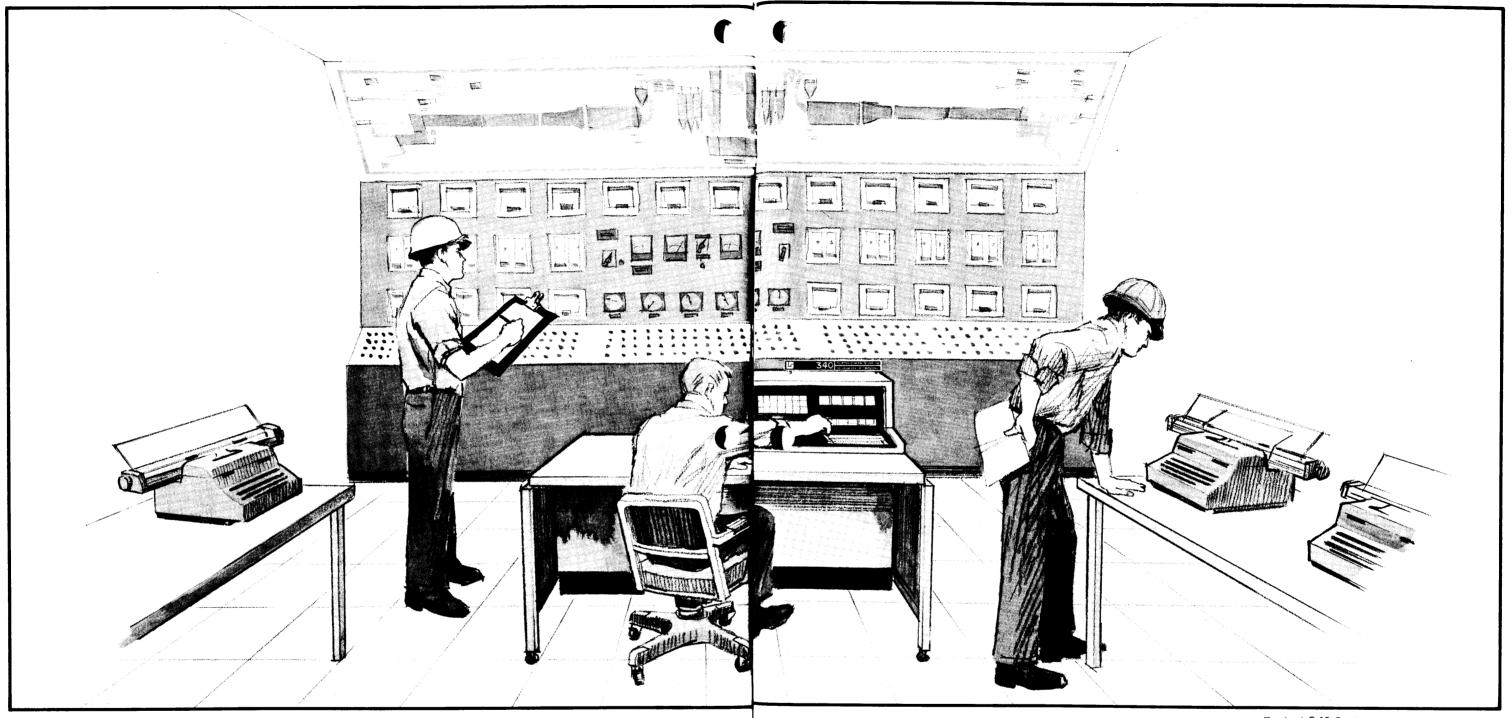

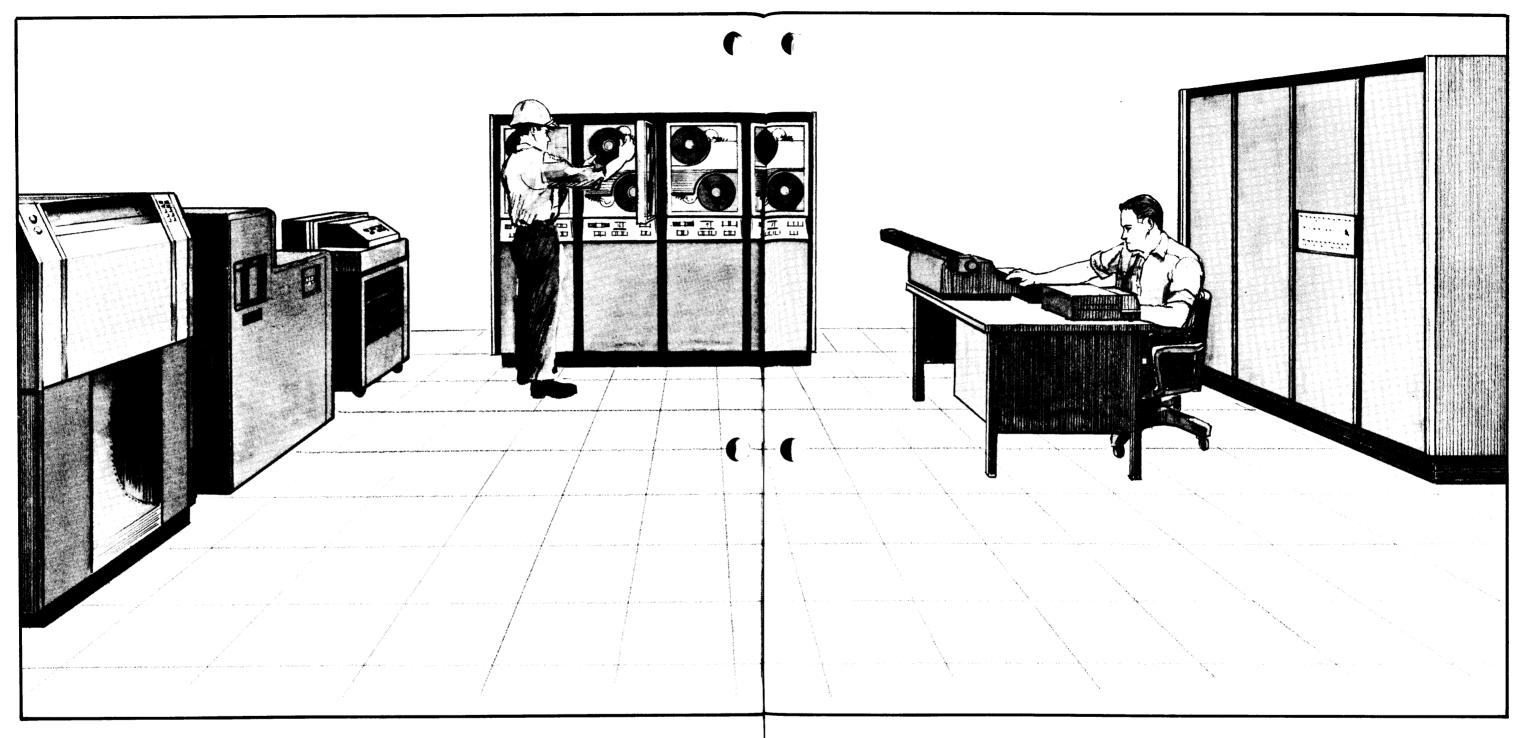

Typical 340 Control Computer System (Operations Control Room)

Rack-and-panel construction of the 340 equipment permits a system to be assembled in a variety of forms in order to satisfy any process control requirement. 340 systems may be field-expanded as necessary to accommodate an expanding plant or a more extensive control system.