June 12, 1959 HG Kolsky Original Boot personal Copy

# **PRODUCT PLANNING**

Jechnical Report

DATE\_June 12, 1959\_\_\_\_

NUMBER P-17

The STRETCH Virtual Memory Concept and Timing Simulation Program

AUTHOR \_\_\_\_ John Cocke\* and Harwood G. Kolsky

LOCATION Poughkeepsie

\*(Present location: IBM Research, Poughkeepsie)

This report is company confidential

# TABLE OF CONTENTS

|     |             |                                                                                 | Page          |

|-----|-------------|---------------------------------------------------------------------------------|---------------|

| I.  | Introductio | on                                                                              | 1             |

| п.  | General De  | escription of the System                                                        | 1-4           |

| ш.  | Detailed D  | escription of Virtual Memory Operation                                          | 5-24          |

|     | А.          | General Conditions to be Considered                                             | 5             |

|     | в.          | Definitions                                                                     | 5-9           |

|     | C.          | Logic of the Virtual Memory                                                     | 9-24          |

| IV. | Description | n of Timing Simulation Program                                                  | 24-28         |

|     | Α.          | General Considerations                                                          | 24-25         |

|     | в.          | Logic of the Simulator                                                          | 26-28         |

| v.  | Some Resu   | lts of the Simulation Studies                                                   | 29-60         |

|     | Α.          | General Description                                                             | 29-32         |

|     | в.          | Test Problems Used                                                              | 32-33         |

|     | c.          | Results of Simple Parameter Studies                                             | 33-48         |

|     | D.          | The Effect of the Half-Microsecond Instruction Memory<br>on STRETCH Performance | <b>4</b> 8-55 |

|     | E.          | A Study of Branching on Arithmetic Results in STRETCH                           | 56-60         |

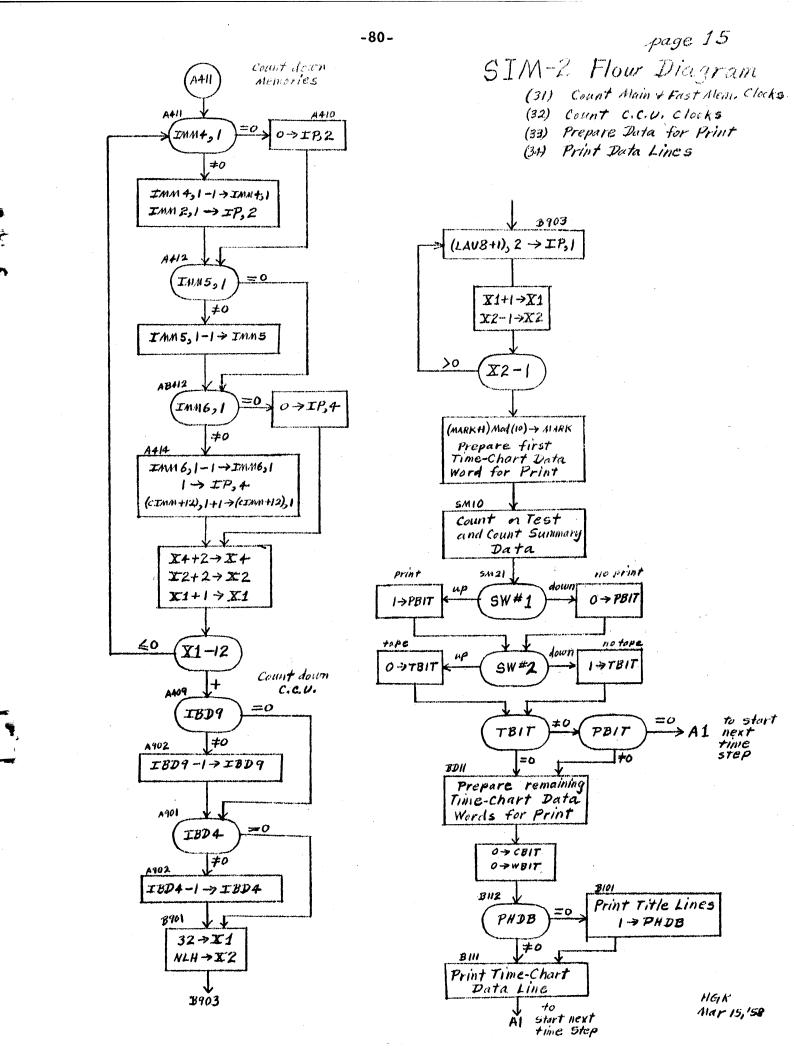

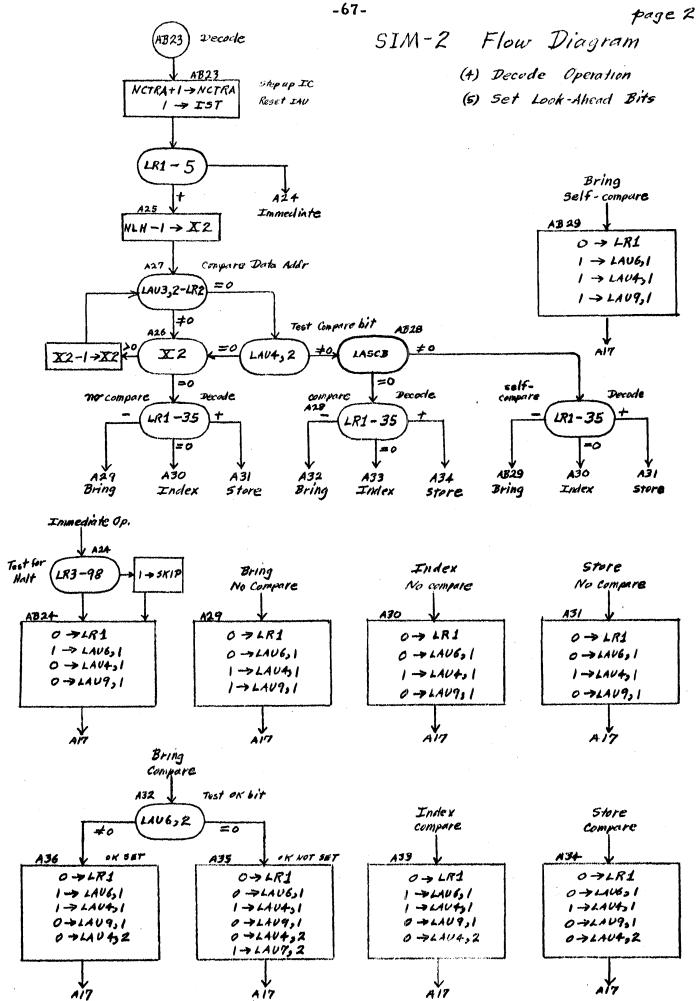

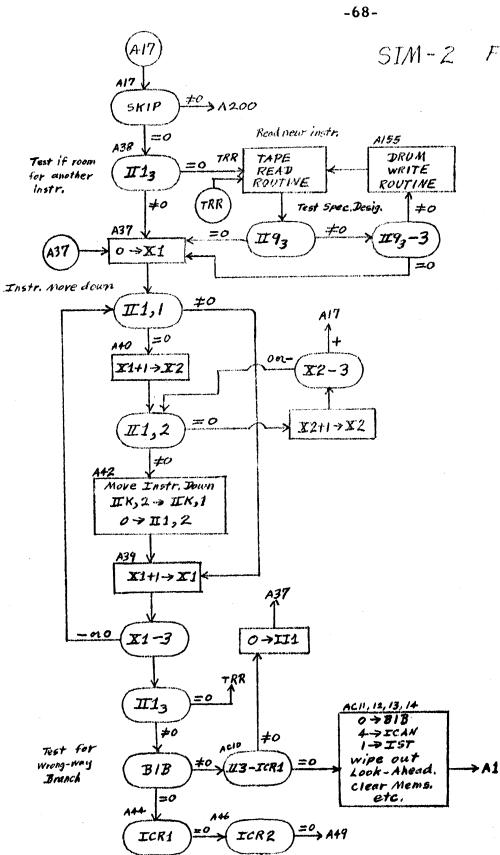

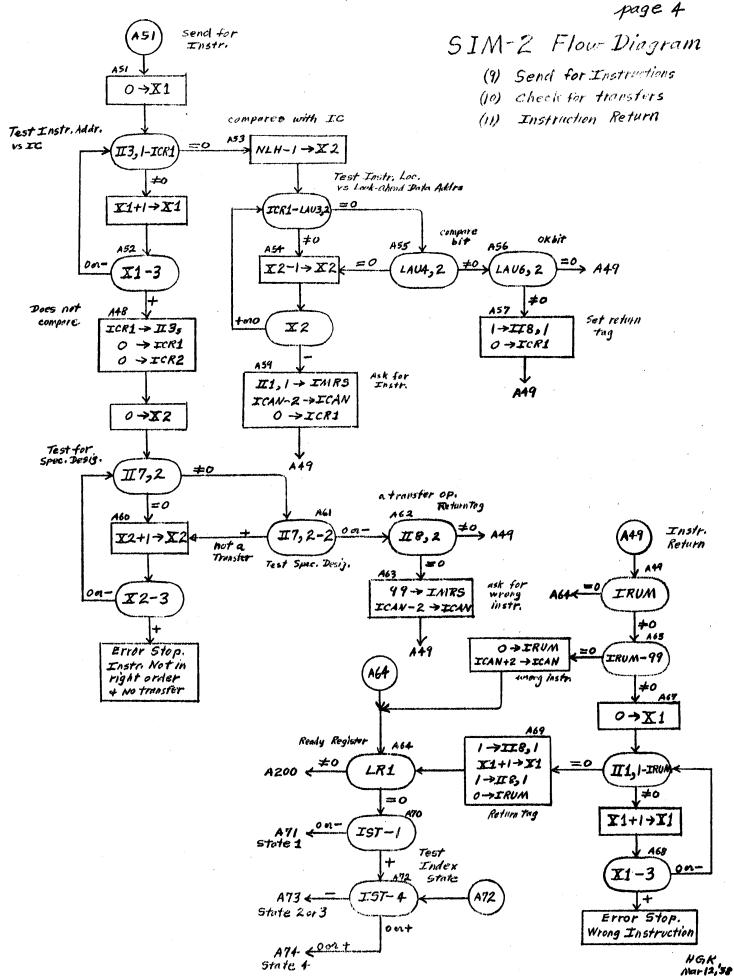

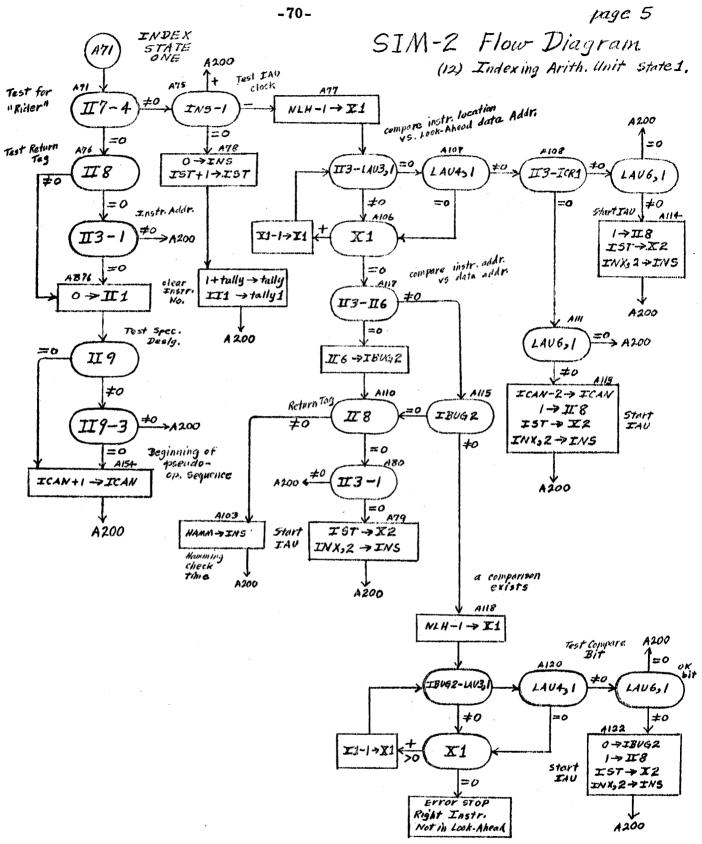

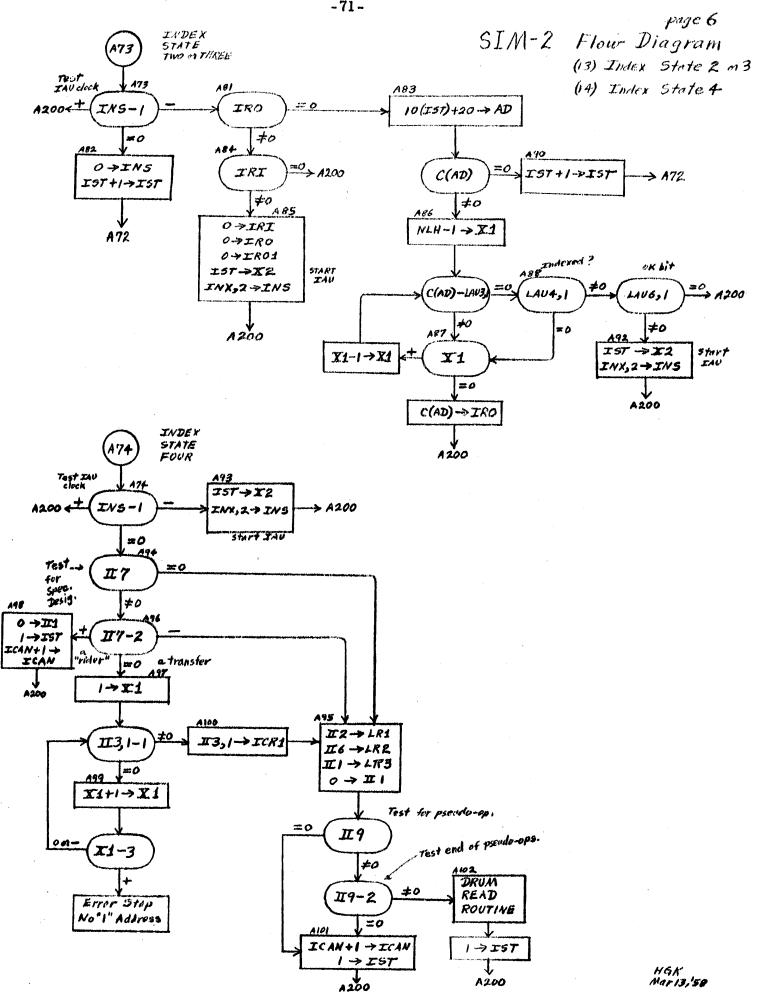

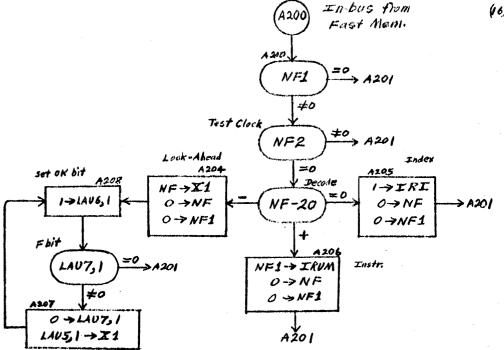

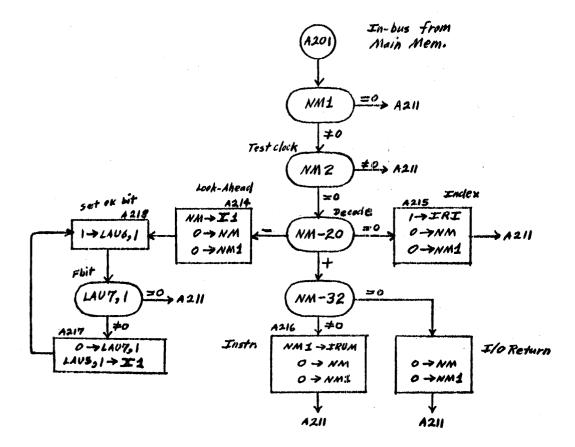

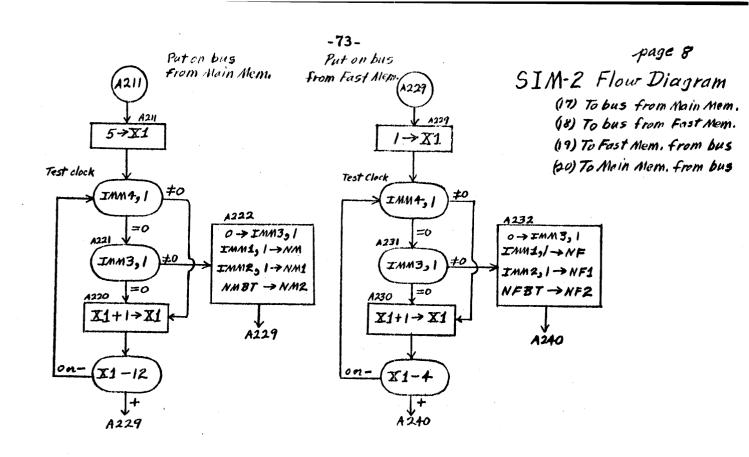

| VI  | APPENDIX    | C: Details of Timing Simulation Program SIM-2                                   | 61-80         |

# TABLE OF FIGURES

۴.

ł

٩.,

|           | Title                                                      | Page |

|-----------|------------------------------------------------------------|------|

| Figure 1  | Schematic of STRETCH Computer                              | 2    |

| Figure 2  | Contents of a Virtual Memory Level                         | 6    |

| Figure 3  | Virtual Memory Interlocks                                  | 8    |

| Figure 4  | Instruction Fetch Procedure                                | 10   |

| Figure 5  | Indexing Procedure                                         | 11   |

| Figure 6  | Procedure for Placing Instructions into the Virtual Memory | 13   |

| Figure 6A | Logical Conditions for Bring Type Operations               | 14   |

| Figure 6B | Logical Conditions for Store Type Operations               | 16   |

| Figure 6C | Logical Conditions for Immediate Type Operations           | 18   |

| Figure 7  | Data Fetch Procedure                                       | 19   |

| Figure 8  | Data Store Procedure                                       | 20   |

| Figure 9  | Procedure for Placing Data into Virtual Memory             | 21   |

| Figure 10 | Procedure for Removing Instruction from Virtual Memory     | 23   |

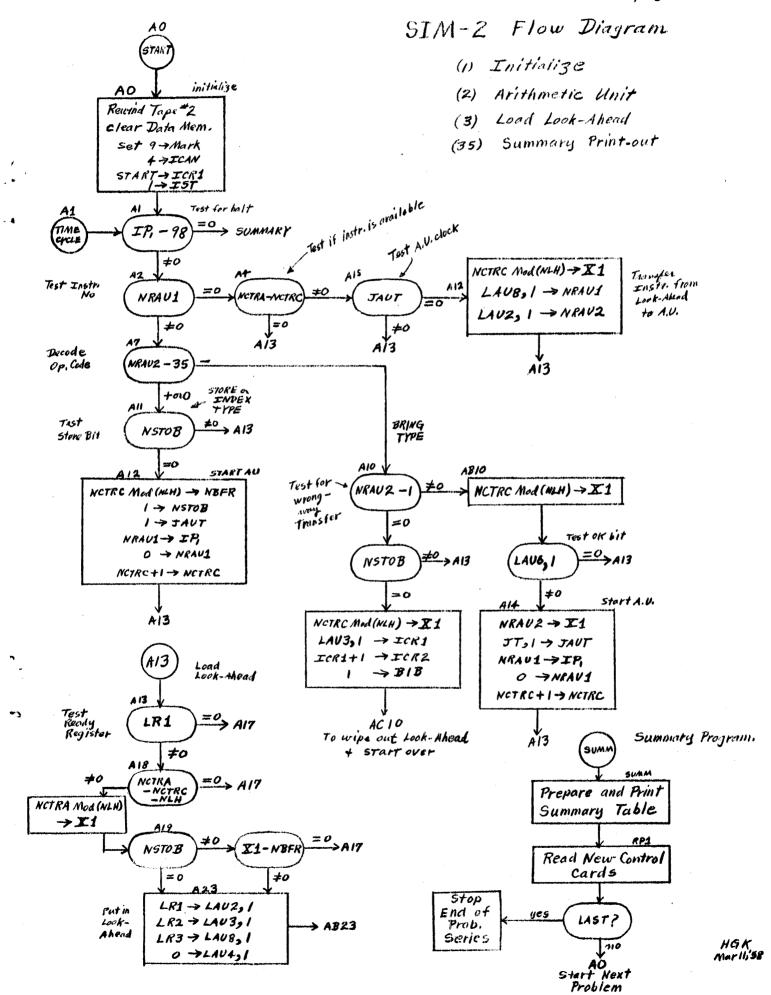

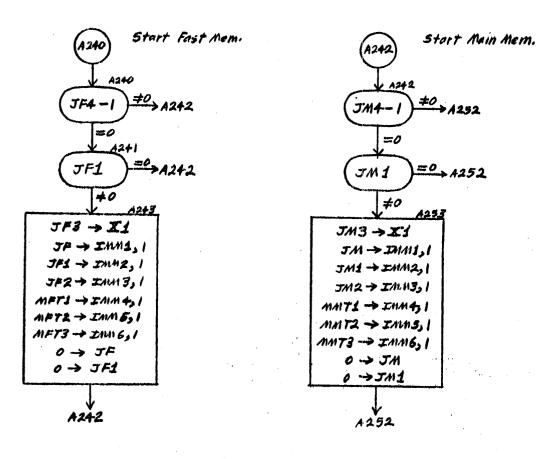

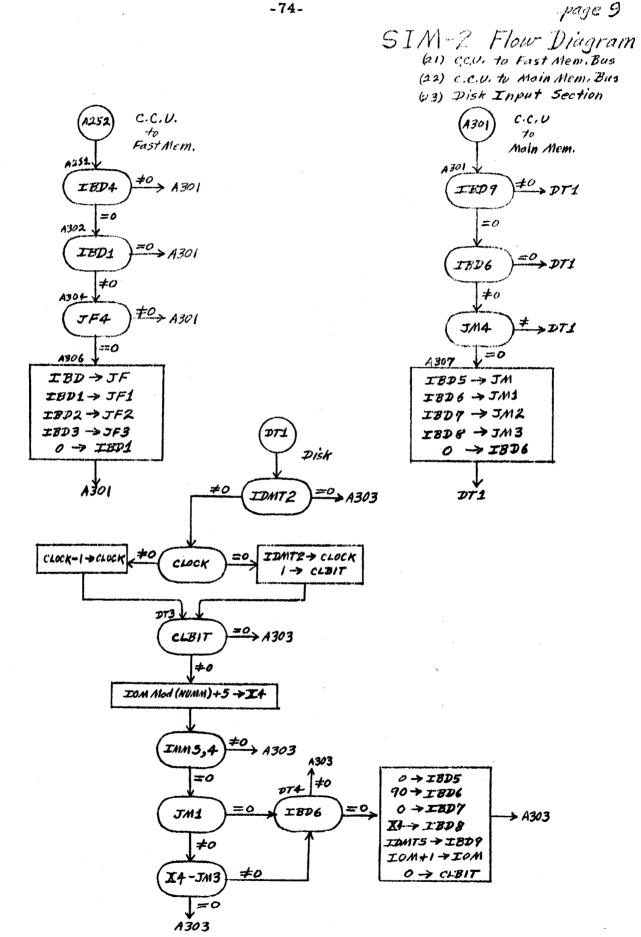

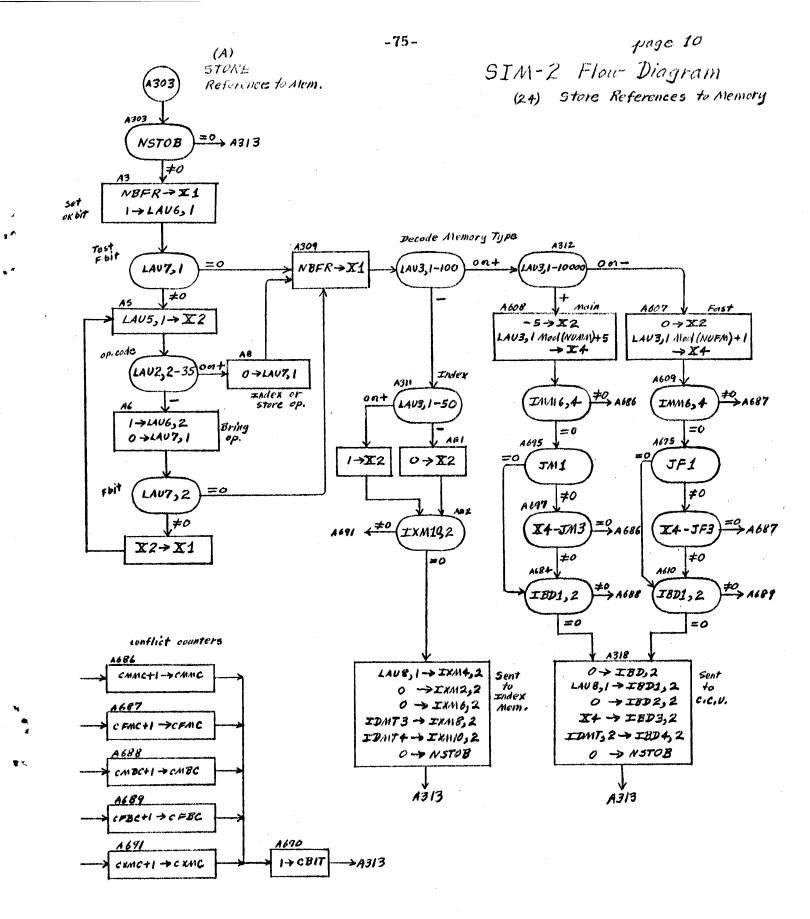

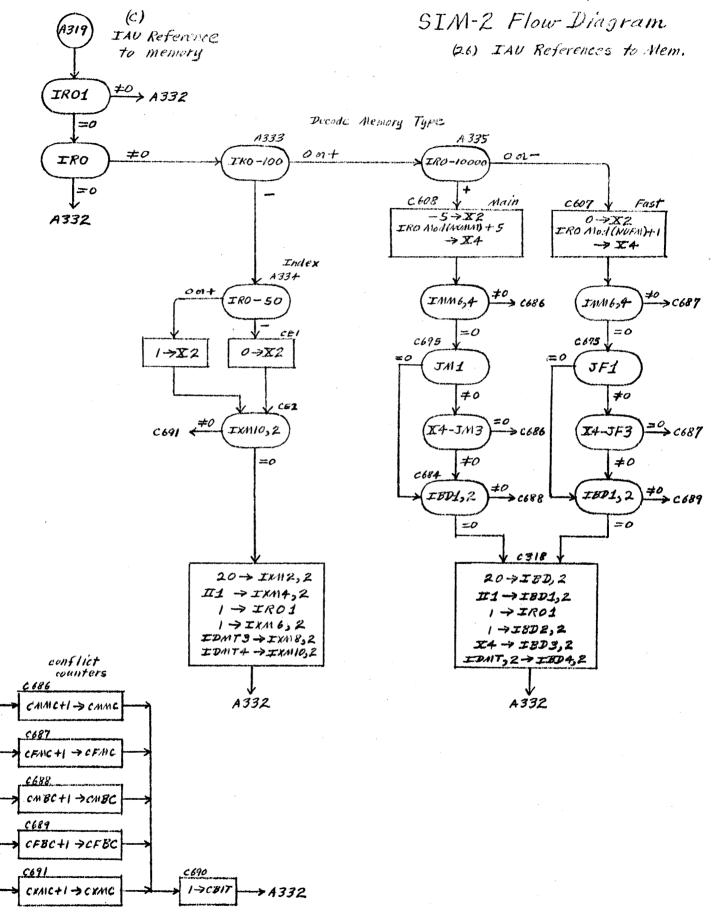

| Figure 11 | SIM-2 Simplified Flow Diagram                              | 28   |

| Figure 12 | Listing of Simulator Print-Out                             | 30   |

| Figure 13 | Listing of Simulator Summary Print-Out                     | 31   |

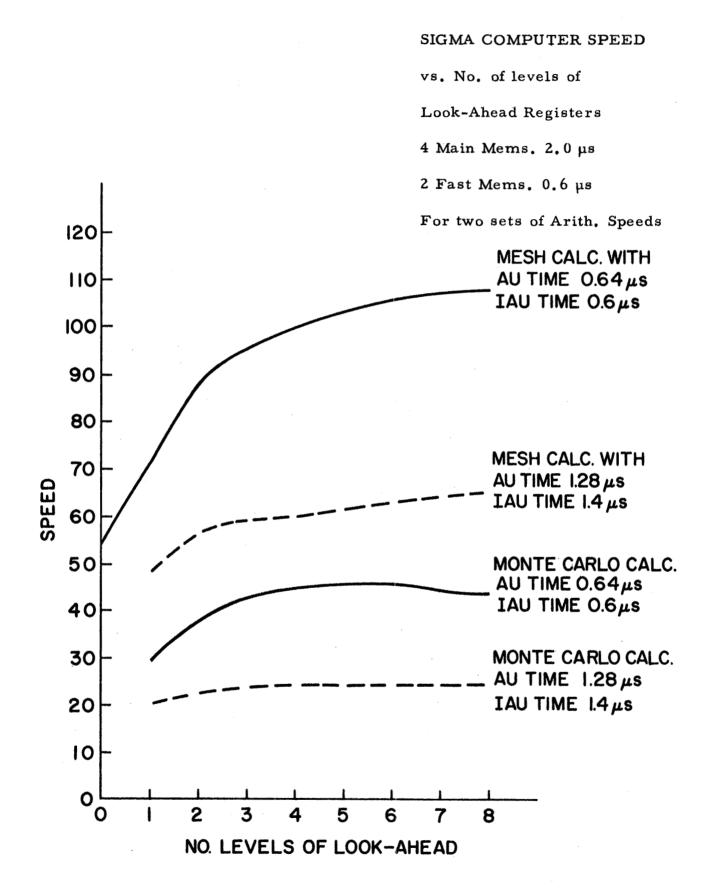

| Figure 14 | Computer Speed vs. no. Levels of Virtual Memory            | 36   |

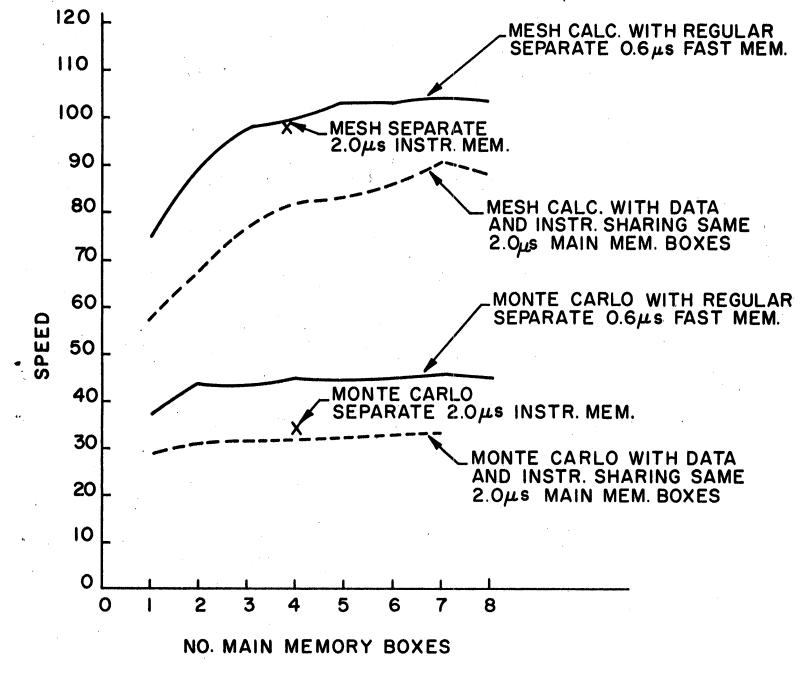

| Figure 15 | Computer Speed vs. no. of Main Memory Boxes                | 38   |

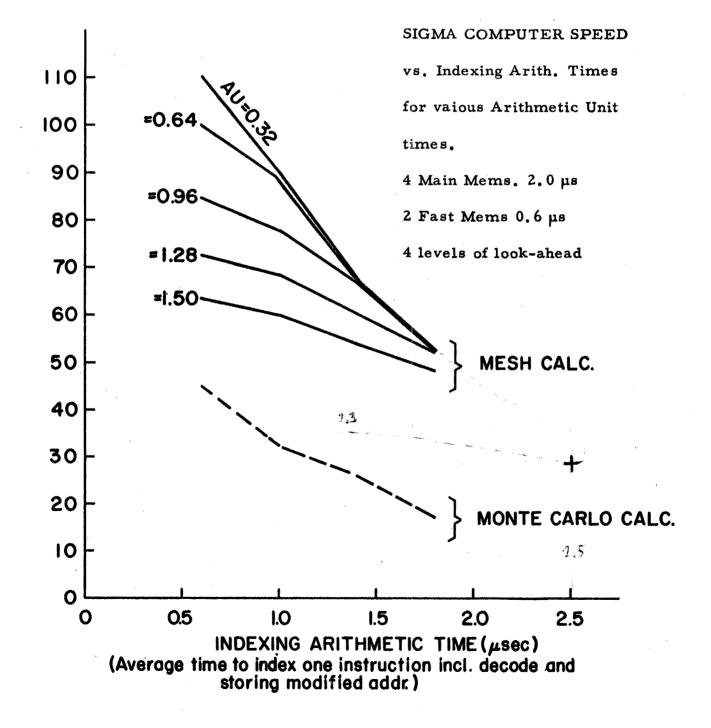

| Figure 16 | Computer Speed vs. Indexing Arithmetic Time                | 39   |

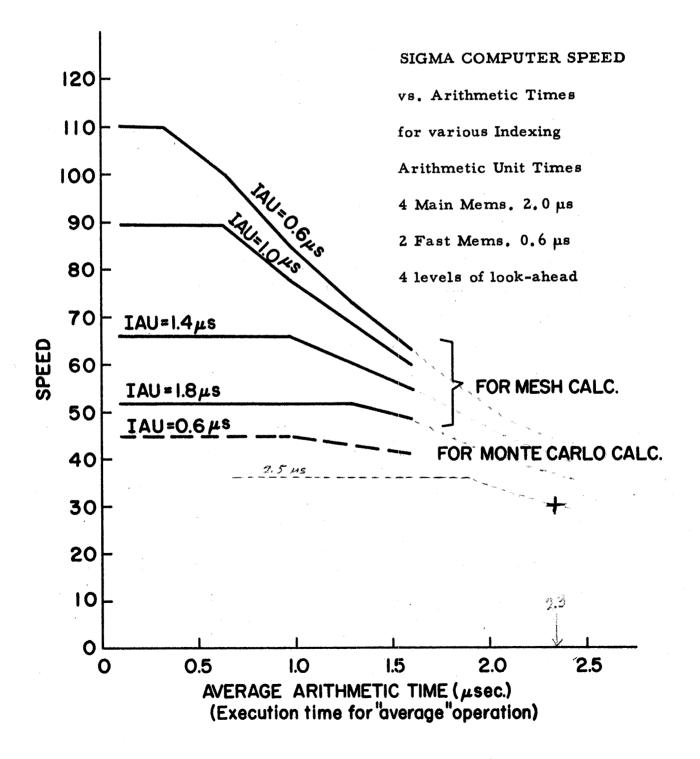

| Figure 17 | Computer Speed vs. Average Arithmetic Time                 | 40   |

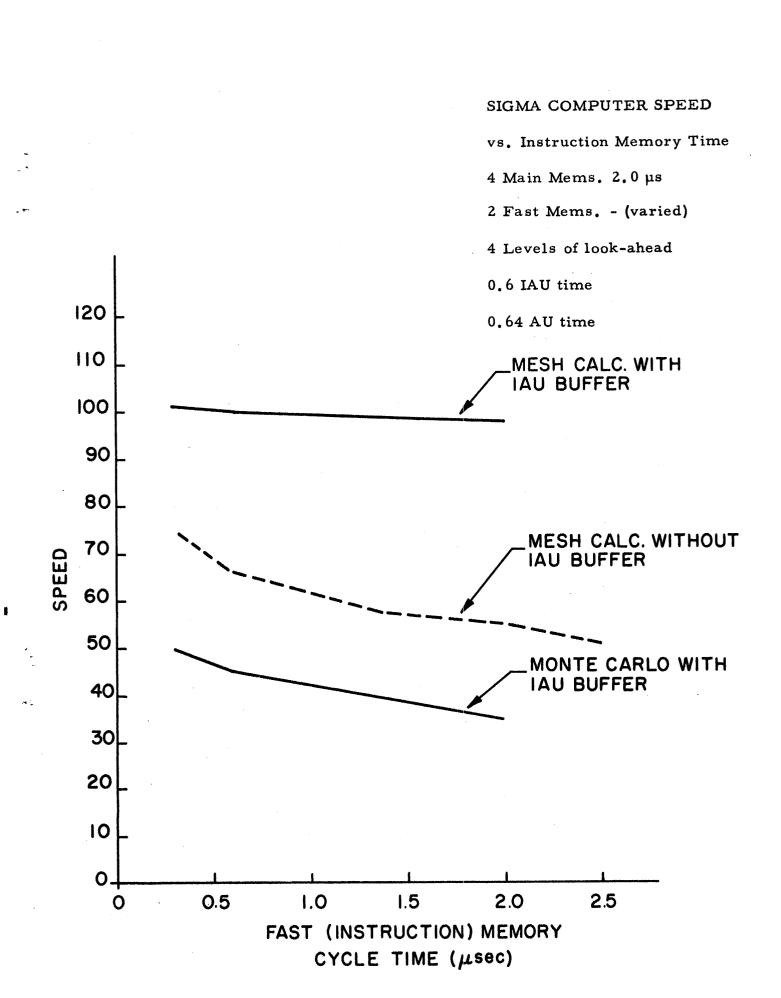

| Figure 18 | Computer Speed vs. Instruction Memory Cycle Time           | 42   |

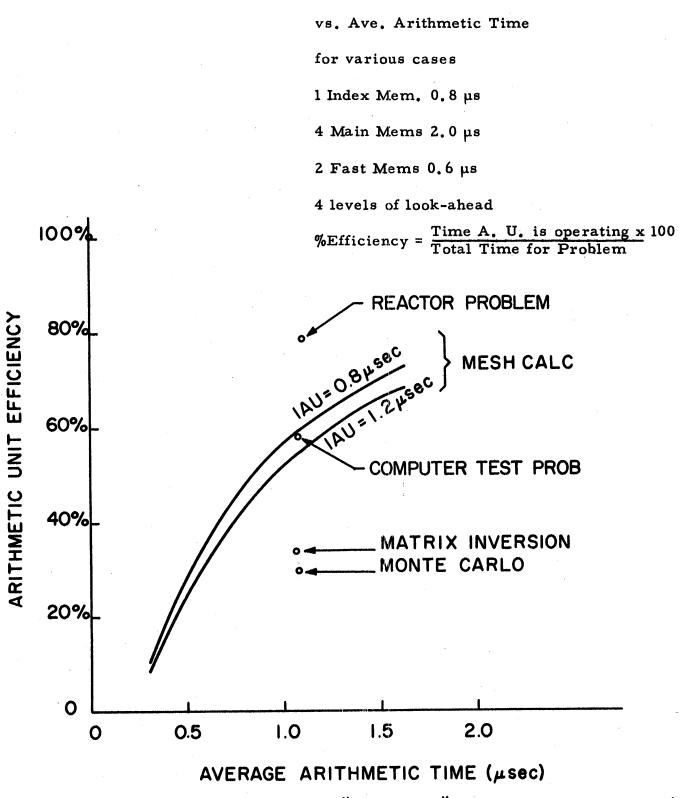

| Figure 19 | Arithmetic Unit Efficiency vs. Average Arithmetic Time     | 43   |

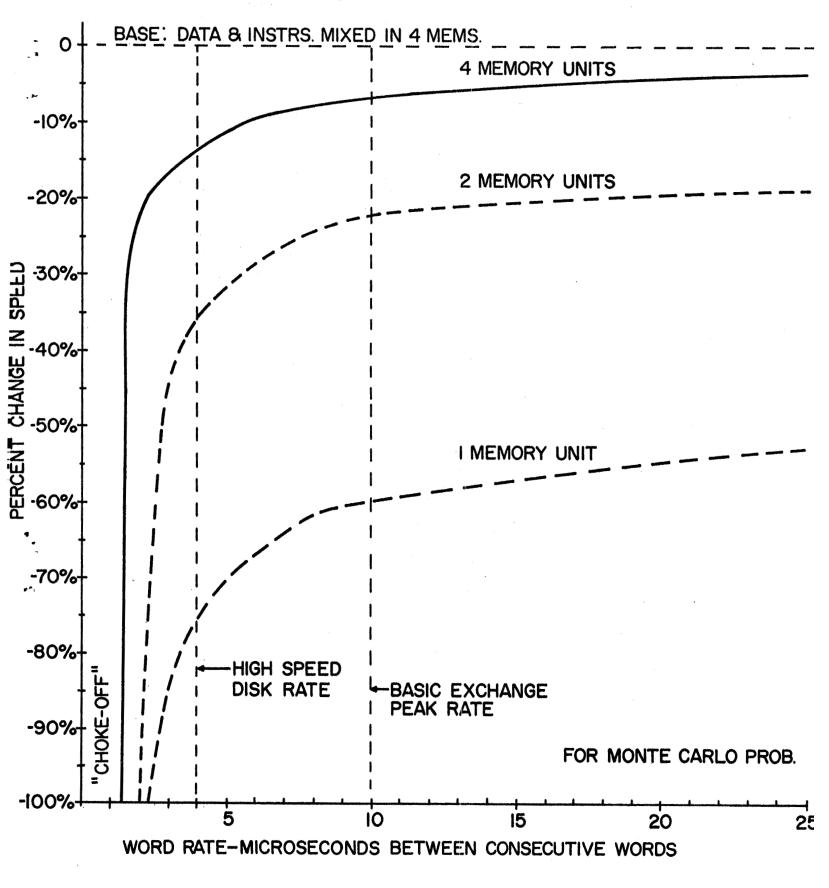

| Figure 20 | Computing Speed vs. I/O Word Rate                          | 45   |

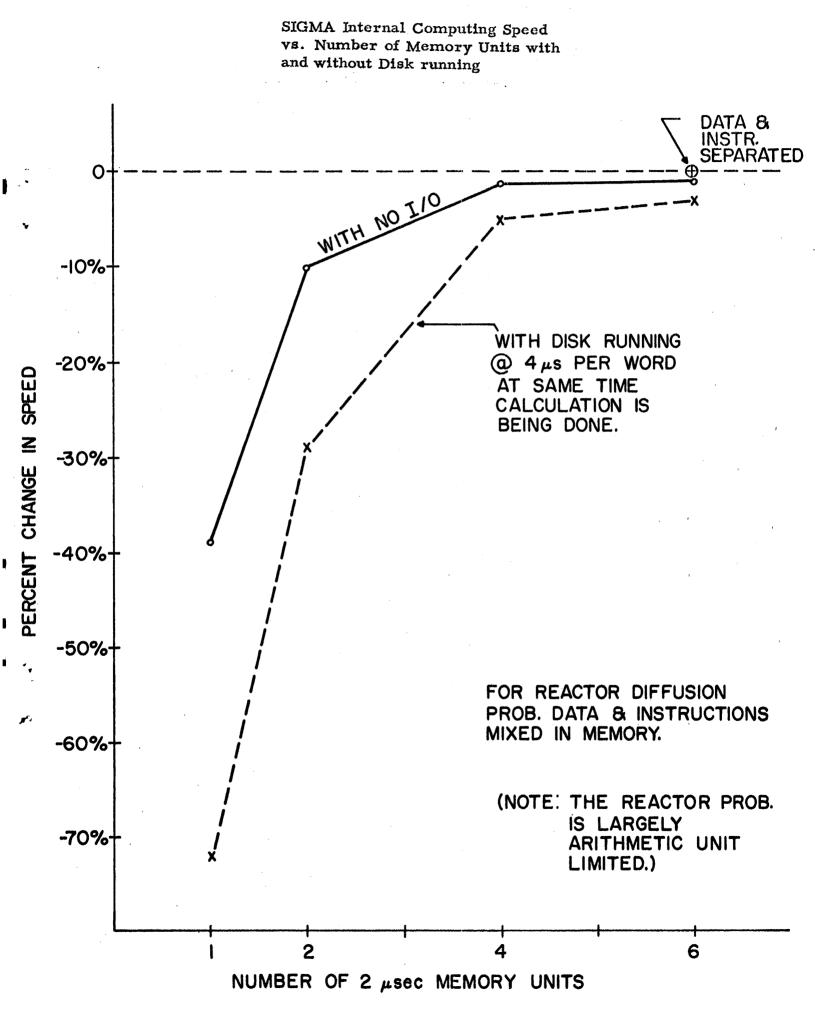

| Figure 21 | Computing Speed vs. Number of Memory Units 1               | 46   |

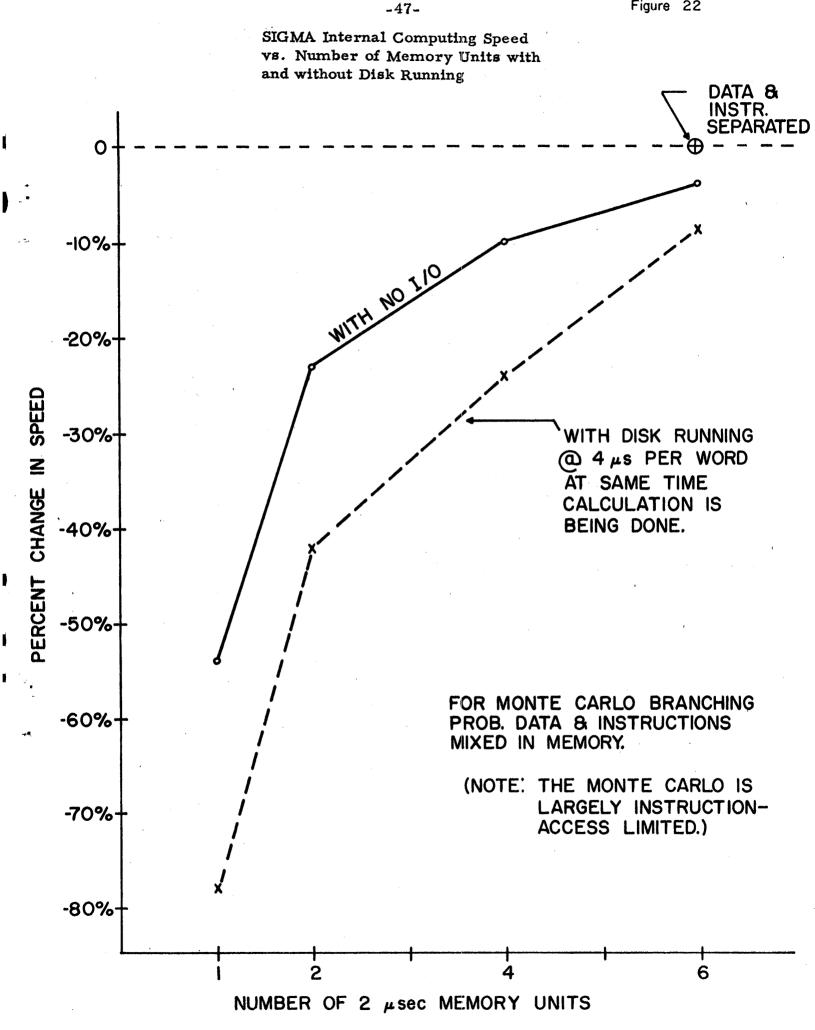

| Figure 22 | Computing Speed V <sup>8</sup> , Number of Memory Units 2  | 47   |

#### I. INTRODUCTION

Early in the planning of the STRETCH computer it was seen that by using the latest solid state components in sophisticated circuits that it would be possible to increase the speed of floating point arithmetic by almost two orders of magnitude over that in existing computers. However, there seemed to be no possibility of developing on the same time-scale economically feasible large memories with more than a factor of ten or perhaps twenty increase in speed. As a result, the proposed system appeared to be in danger of being seriously memoryaccess limited.

Moreover, as the speed of the floating point operations increases, a larger and larger percentage of the computer's time is spent on "parasitic operations", i.e., operations whose only function is program control and data selection. It was obvious that a radically new machine organization was necessary in order to capitalize upon the possibilities opened up by the high arithmetic speeds in the presence of relatively slow memories.

At this time, the possibility of a "look-ahead" device was suggested in which an independent indexing arithmetic unit would prepare the effective addresses of instructions and initiate memory references to a multiplicity of memory boxes. The data thus fetched would be held in high speed buffer registers until needed by the arithmetic unit. This device would serve two desirable purposes; (1) some of the parasitic operations would be done in parallel and thus not delay the principal calculations, and (2) several memory boxes could be running simultaneously, giving the effect of higher memory speed.

#### II. GENERAL DESCRIPTION OF THE SYSTEM

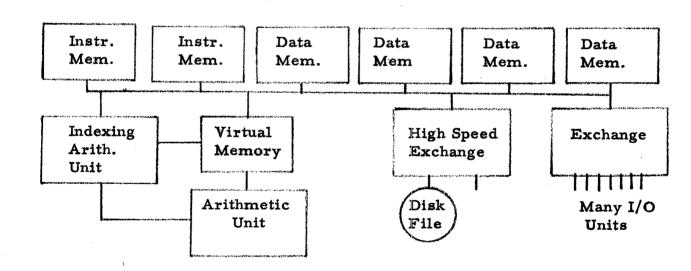

The major logically-independent blocks of the STRETCH computer are shown in Figure 1. Each of the units pictured may be considered as operating asynchronously. That is, each does its tasks as fast as possible independently of the others. In theory, each box could have its own clocking circuits and still operate properly. In practice, for economy's sake they are all timed by the same master oscillator, but this does not destroy their logical independence. The bus control unit serves as a routing agent between the memories and the various data processing units. If two or more units make a request simultaneously the control unit assigns priorities in the following order: (1) High speed Exchange, (2) Basic Exchange, (3) Virtual Memory, and (4) Indexing Arithmetic Unit.

The Indexing Arithmetic Unit fetches instructions, performs all necessary indexing operations and sends the instructions to be executed to the Virtual Memory.

1

The Virtual Memory fetches and receives the data required by the instruction and holds this data until the arithmetic unit is ready for it. The Virtual Memory also performs all store operations. It holds the data generated by the Arithmetic Unit or Indexing Arithmetic Unit until the memory to which the data must be sent is available. Thus the Virtual Memory acts not only as a'look-ahead" for instructions to be fed to the arithmetic unit, but also acts as a 'look-behind" storage buffer.

#### FIGURE 1

#### SCHEMATIC OF SIGMA COMPUTER

The actual design of such a "look-ahead" device posed a number of logical problems, particularly in connection with conditional branches. In colaboration with John Griffith, a device was proposed later named "virtual memory", which answered these logical problems and served as guide for the actual organization of STRETCH.

However, a machine organization of this complexity requires a detailed timing analysis in order to determine the value of adding hardware in the form of the "virtual memory". This is especially true since the sole function of the "virtual memory" is to increase machine speed, by increasing the efficiency of other devices. It was also felt that the timing analysis could not be made on the basis of a few trivial examples (e.g. matrix multiply). Machine performance obtained in this fashion can be extremely deceptive. Since a detailed timing analysis of a computer of this complexity is extremely tedious to carry out by hand, it became clear that if the job were to be done, it would be necessary to simulate the proposed machine on another computer. This prompted us to write the simulation program described below.

With the above general organization in mind, let us discuss some of the logical problems posed by such a system. The first problem is a result of the very concept which enables us to obtain such great benefits from the stored program computer--the ability to treat instructions as data. In a system such as we have proposed there is a large amount of simultaneous operation. For example, the indexing arithmetic unit may be busy preparing an instruction before previous instructions have been completed or even started by the arithmetic unit. One of these previous instructions may modify the instruction which is presently being indexed. The virtual memory must recognize this situation and allow the intervening instructions to be completed before doing the modified instruction.

A similar problem exists with respect to ordinary data. In order to operate several memories simultaneously, it is necessary to start obtaining data from these memories before the preceding operations have been completed. Yet, one of these operations may be a store into one of the data locations. The virtual memory must make provisions to insure that each instruction obtains the most up-to-date data as implied by the order of the program. One of the novel features of the STRETCH computer is its elaborate interrupt system. Under this system whenever some unexpected occurrence arises, the program will be interrupted and control will pass to a special routine which is designed to take care of the case in question, then return control to the original program. In this situation the virtual memory must have provisions to retain enough information so that when an interrupt occurs we can resume the computation exactly where we left off. It must be able to recognize which of the changes that have been made in advance are not desired and should be obliterated and which are exact solutions that must be restored.

Another special case arises when a conditional branch on arithmetic results occurs. Here we will not know which of the two branches we should have taken until the preceeding instruction is executed. In the case the wrong path has been selected, the virtual memory must be prepared to drop the intermediate results which have been computed and pick up the correct branch in a way very similar to that of an interrupt.

Summing up all these logical problems, we may state that the fundamental rule for the Virtual Memory is that it must make the asynchronous and non-sequential computer give results identical to those which would be obtained by performing the program one instruction at a time in the order in which they are written.

Since our original work on the virtual memory and simulation in 1957-58, a large number of detailed changes have been made in the actual hardware design of STRETCH. These necessitated several modifications in the Simulation program to estimate their effect on the overall system performance. In this report we are omitting many of these changes for expository reasons since our purpose is to describe the virtual memory and timing simulation concepts not to describe the STRETCH hardware exactly. The result is that the system described below imbodies a more general system than that found in the Simulator which in turn is more general than that found in the actual computer.

-4-

#### III. DETAILED DESCRIPTION OF VIRTUAL MEMORY OPERATION

#### A. General Conditions to be Considered

The conditions which occur in the following situations must be considered in some detail:

- 1. The fetching of instructions by the Indexing Arithmetic Unit.

- 2. The indexing of instructions and modification of Index registers.

- 3. The loading of the Virtual Memory and the setting of its conditions by the IAU.

- 4. The action of the Virtual Memory in fetching data.

- 5. The action of the Virtual Memory in storing data.

- 6. The communication between the Virtual Memory and the main arithmetic unit.

- 7. Special situations such as conditional branching on arithmetic results, etc.

#### **B.** Definitions

Some of the terms we will use are defined as follows:

#### 1. Operations

Operations are considered to be of three types:

- (1) Bring or fetch type All instructions requiring data to be transmitted from external memory to the Virtual Memory

- (2) Store Type Instructions requiring the transmission of data from the Virtual Memory to external memory or index memory.

- (Note: We consider all indexing instructions to be of the Store Type, although the store may be to either external memory or index memory.)

- (3) Immediate Type All operations not requiring data transmission.

- 2. Virtual Memory Quantities

- Virtual Memory A number of Virtual Memory (or lookahead) levels (numbered 0 to N-1).

- (2) Level of Virtual Memory A collection of registers and control bits. The contents of the jth level is shown in Figure 2.

| <br>Ij                                                                                                          | OPj | S <sub>j</sub><br>Bit | B <sub>j</sub><br>Bit | F <sub>j</sub><br>Bit <sup>j</sup> | FAj | OK j<br>Bit j                                                                                                  | ${}^{C}_{Bit}$        | Dj                     | DA j |  |

|-----------------------------------------------------------------------------------------------------------------|-----|-----------------------|-----------------------|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|------|--|

| And a passion of the second |     |                       |                       |                                    |     | Construction of the owner of the | CALIFORNIA CONTRACTOR | factor indemnities the |      |  |

Figure 2 Contents of a Virtual Memory Level

- (3) Instruction Address Register (I<sub>j</sub>) Contains the address of the instruction currently in the jth level.

- (4) Operation Code Register (OP<sub>j</sub>) Contains the operation to be performed by the arithmetic unit.

- (5) Store Bit (S<sub>j</sub>) A one bit trigger which indicates the level contains a Store type instruction.

- (6) Bring Bit (B<sub>j</sub>) A one bit trigger which indicates the level contains a fetch type instruction for which the data access has not been started.

- (7) Forwarding Bit (F<sub>j</sub>) A one bit trigger which indicates that the jth level must transmit data to another level.

- (8) Forwarding Address (FA<sub>j</sub>) A register which contains the number of the level to which the data must be sent if F<sub>j</sub> is set.

- (9) O.K. Bit (OK<sub>j</sub>) A trigger which when set indicates that the correct data for the instruction to be executed is present in the jth Data Field.

- (10) Data Field  $(D_j)$  A register which contains the operand data for the instruction.

- (11) Data Address  $(DA_j)$  The operand data address (already indexed by the IAU) for  $D_j$ .

- (12) Compare Bit  $(C_j)$  A trigger which if not set indicates the address in DA<sub>j</sub> should not be included in any address comparisons being made.

#### 3. Counters

The Virtual Memory is controlled by a set of counters which countmod (N), where N is the number of Virtual Memory levels.

- (1) Counter one (C1) Indicates the level into which the next instruction may be placed.

- (2) Counter two (C<sub>2</sub>) Indicates the level from which the next bring type instruction may be initiated.

- (3) Counter three (C3) Indicates the level from which the next store type instruction may be initiated.

- (4) Counter four (C<sub>4</sub>) Indicates the level from which the arithmetic unit will get its next operation and data.

#### 4. Interlocks

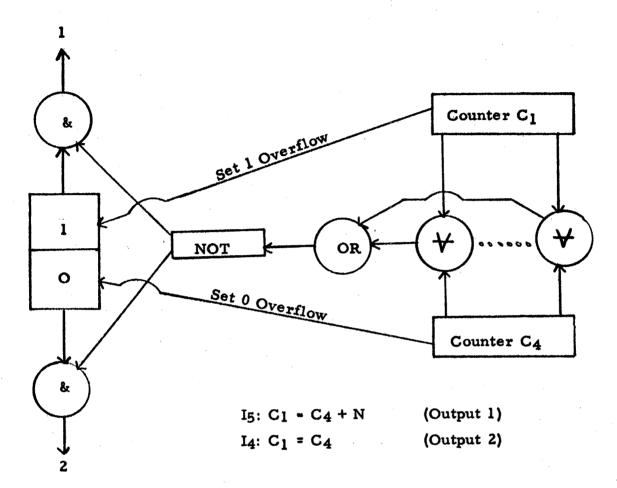

The above counters must be interlocked in the following manner to assure proper sequential operation of the computer (see figure 3):

- Interlock one (I1): C1 = C3 + N Prevents the IAU from placing the next operation into the level indicated by C1 because an unexecuted store is still in the level.

- (2) Interlock two  $(I_2)$ :  $C_1 = C_3$  Prevents a store from being initiated from the level indicated by C<sub>3</sub> because the store has already been done.

- (3) Interlock three (I3): C1 = C2 Similar to I2, prevents a fetch from being initiated.

- (4) Interlock four(I4):  $C_1 = C_4$  Prevents the arithmetic unit from executing an old instruction.

Interlocks I4 and I5 are as shown, the other interlocks are done in a similar manner.

# Figure 3. Virtual Memory Interlocks

(5) Interlock five  $(I_5)$ :  $C_1 = C_4 + N$  Prevents the IAU from placing the next instruction into the level indicated by  $C_1$  because the instruction there has not been executed yet.

#### C. Logic of the Virtual Memory

#### 1. General

There are two basic precepts which must be kept in mind to understand the operation of the Virtual Memory:

- (1) The OK bit  $(O_j)$  being set in the j th level indicates that the contents of  $D_j$  is the correct data called for by  $DA_j$ . All operations will be performed only under this condition and logical decisions will be made in such a manner as to make sure this is the case.

- (2) Addresses can be compared by the IAU with every  $DA_j$  address simultaneously.  $DA_j$  is not used for any level which does not have its  $C_j$  bit set. If a comparison exists between a new  $DA_j$  being placed in the Virtual Memory and an old  $DA_k$ , the compare bit  $C_k$  is turned off and the address of level j is placed in FA<sub>k</sub>. This insures a unique meaning for the comparison. If this were not done, another instruction address  $DA_e$  might compare against two levels and thus cause an ambiguity.

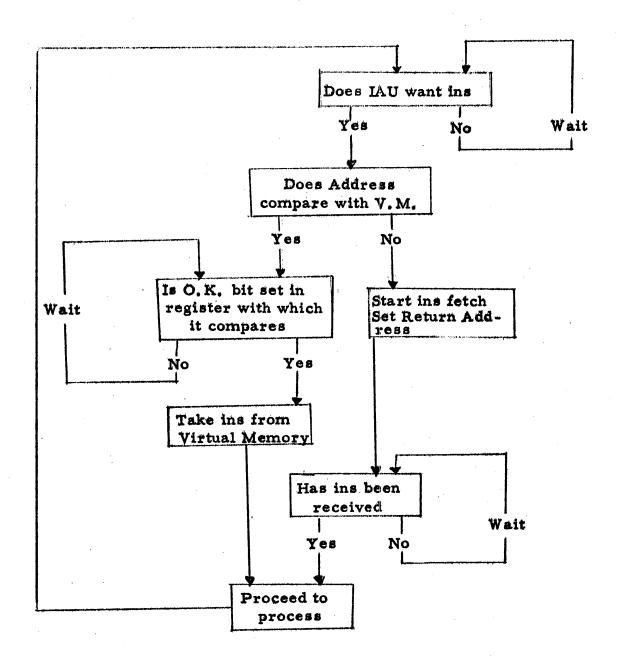

#### 2. Instruction Fetch Logic

Figure 4 is a flow diagram of the IAU Instruction Fetch Procedure. The logic is as follows: If the IAU is ready to fetch another instruction, it compares the instruction address with all the  $DA_j$ 's of Virtual Memory. If there is no comparison, the instruction fetch is initiated. If there is a comparison the IAU must take its instruction from the Virtual Memory provided the OK bit is set, otherwise, it must wait until the OK bit is set.

Note: This procedure prevents the logical difficulty mentioned earlier which would occur if the Virtual Memory contained a store order into the instruction presently being fetched.

For Example: a STORE Address a+2 a+1 LOAD M, i a+2 ADD N, i a+3 ----

The store to a + 2 must be done in sequence or the old value N would be used for the address instead of the quantity being set by a.

3

Figure 4, Instruction Fetch Procedure

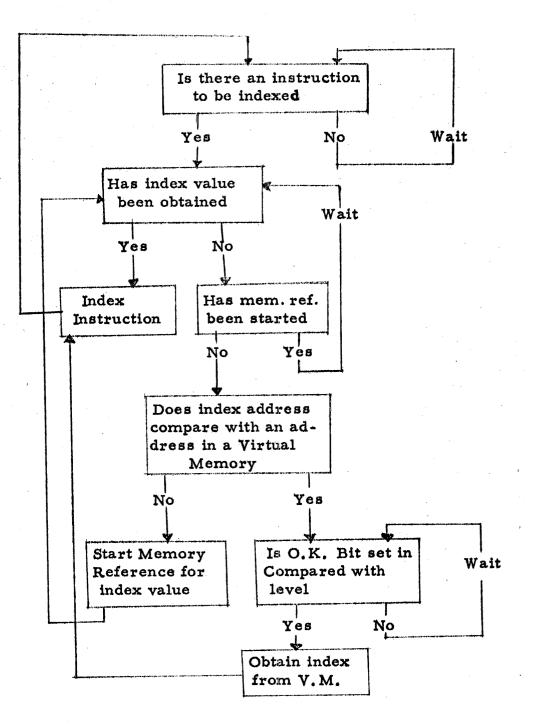

Figure 5, Indexing Procedure

#### 3. Indexing Logic

Figure 5 shows the flow for instruction indexing. After determining that an instruction is ready to be indexed, the IAU tests whether or not the index value is available. If it is, the indexing operation is started, if not the memory reference is started and the IAU waits until the data returns before proceeding. If the index-fetch has not been started, the IAU compares the index address against all the data addresses in Virtual Memory. If none compare, the index value is fetched normally. If one does compare, the index fetch is held up until the OK bit is set for the data. This value from the Virtual Memory is then used for indexing the instruction.

## 4. Logic of Putting Instructions in the Virtual Memory

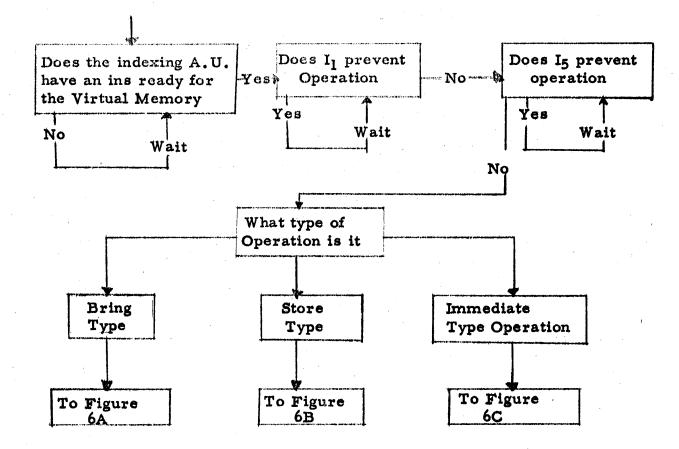

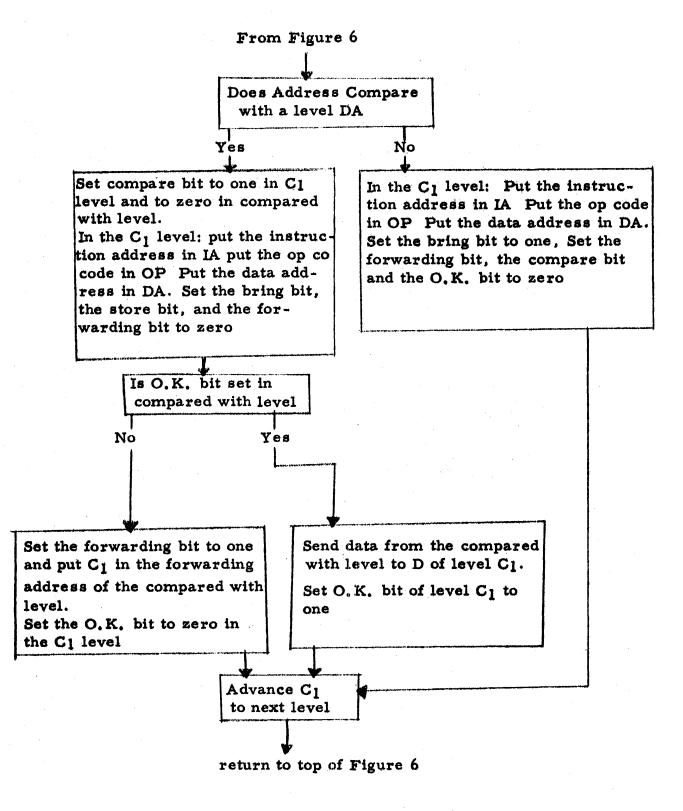

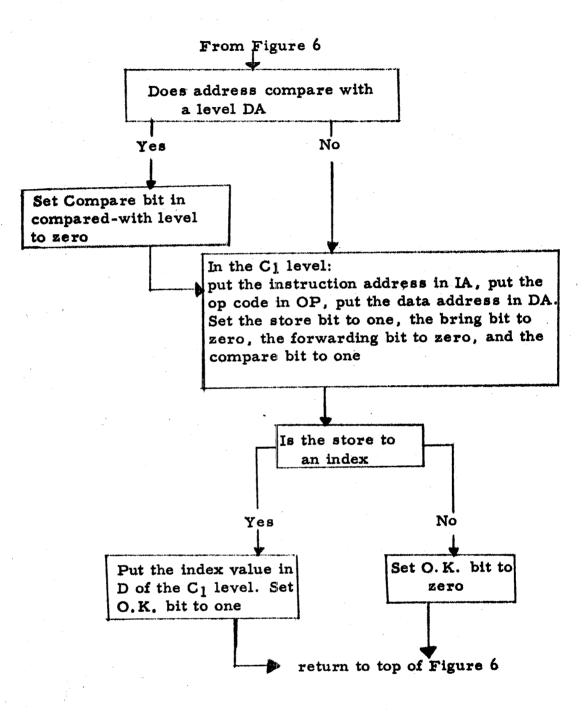

- (1) Figures 6, 6A, 6B, 6C represent the logical flow for putting instructions into the Virtual Memory. If the indexing arithmetic unit has an instruction prepared for the Virtual Memory, it may transmit the instruction into the Virtual Memory if interlocks one and five do not forbid it. These interlocks prohibit a new instruction from destroying an old one which has not been executed as yet, whether an arithmetic operation (I5) or an unexecuted store (I1). The handling of the instructions vary depending on whether they are of the bring type, store type, or immediate type.

- (2) The bring type, as described in Figure 6A, proceeds as follows: If the effective data address of the instruction compares with the DA address in some level, the instruction, its op code, and effective data address are loaded into the level marked by  $C_1$ . The compare bit for level  $C_1$  is set to one while the compare bit for the compared-with level is set to zero. If the O.K. bit in this compared-with level is set, meaning that the data located there is correct, the data is transmitted directly to the  $C_1$  level and its O.K. bit is also set. If the O.K. bit is not set, we must tag the compared-with level of  $C_1$  into its Forwarding address, the bring bit for level  $C_1$  is also set to zero since no further data fetch is required.

If the effective data address does not compare with any Virtual Memory level, the instruction is put directly into level  $C_1$ , its OK. bit is set to zero, and its bring bit is set to one, indicating that a fetch must be started.

Figure 6, Procedure for placing Instructions into the Virtual Memory

-13-

(3) Figure 6B shows the Store type procedure. If the effective address of the instruction does not compare with the DA address in some level, the instruction is placed into the level marked by  $C_1$ . The store bit is set to one indicating that a store will be required. The level's bring bit and forwarding bit are set to zero, its compare bit is set to one. If on the other hand the addresses do compare, the same procedure is followed but in addition, the compare bit in the level compared-with is set to zero so that future comparisons will not use it.

The OK bit has not yet been set. It is set to one if the operation is an index store and set to zero if it is an ordinary store. For the ordinary store it is clear that the OK bit should be zero since the data must come from the arithmetic unit after the preceeding instruction is executed.

As was mentioned in the definition on page 5, we treat all indexing instructions as store type and place the new value of the indexed quantity into the Virtual Memory. This is done because the Indexing Arithmetic Unit is going ahead of the normal order of instruction execution and an interruption may occur before this indexing instruction should have been done. In this case, the old value of the index is still in the index register. On the other hand the Indexing Arithmetic Unit compares with the Virtual Memory and extracts the most recent value of the index for indexing succeeding instructions. The OK bit is set to one since the appropriate data is in the above level. Both the new and old index values must be carried along to give logically correct conditions in the case of an interrupt.

A situation very similar to interrupt occurs in branches on arithmetic results where the Indexing Arithmetic Unit "guesses" which branch will be taken and proceeds with fetching and processing the instructions on this branch subject to being wiped out if the guess proved to be wrong. (See the discussion on "Wrong way Branches" below.)

Figure 6B, Logical Conditions for Store Type Operations

(4) Immediate Type instructions are the simplest type because they essentially carry their data with them. Figure 6C shows the logic in this case. The instruction is placed in the Virtual Memory level marked by  $C_1$ . The address field of the instruction is placed in the data field of  $C_1$ . The OK bit is set to one indicating the data is present. The bring and store bits are both set to zero. The compare bit is set to zero since the DA address field has no meaning for immediate type ops. (The data address of the last instruction which occupied this level still remains in DA so it has no relation to the present D field.)

#### 5. Logic of Data Fetching

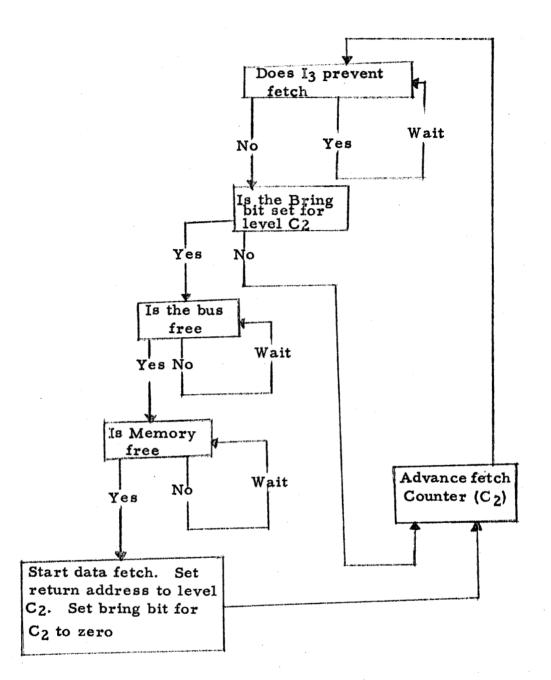

See Figure 7: When an instruction of the bring type has been placed in the Virtual Memory, the data required by the instruction in general will not be present (unless a comparison exists as was described above) and thus the data must be obtained from core storage. The fetch cannot be started if interlock I<sub>3</sub> holds which means all the fetches corresponding to the instructions presently in the Virtual Memory have been started. If a fetch is possible, the bring bit at level  $C_2$  indicates whether or not a fetch is necessary. If necessary the fetch may be started if the memory bus and memory unit corresponding to the data address are not already being used. When the fetch is started, the bring bit for level C<sub>2</sub> is set to zero. The counter C<sub>2</sub> is then stepped forward to the next level.

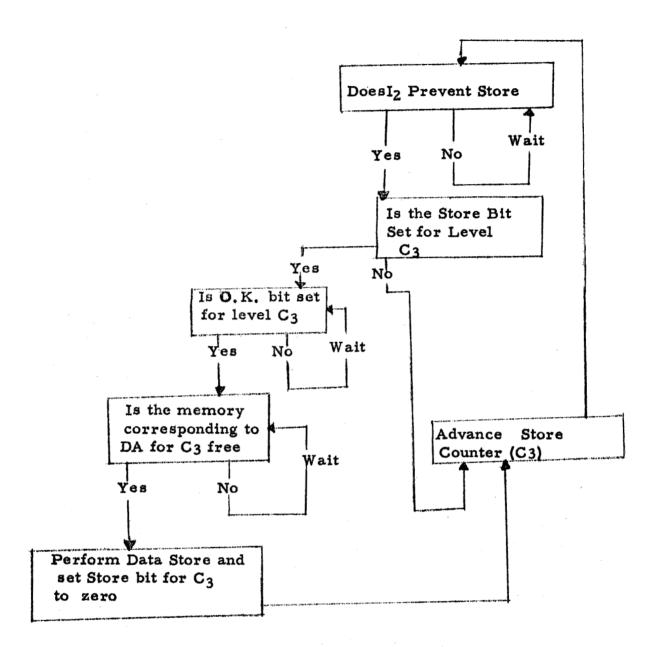

## 6. Logic of Data Storing

Figure 8 shows the Data Store logic, which is very similar to that for data fetching just described. The only significant difference is that the O.K. bit must be set before the operation can be started.

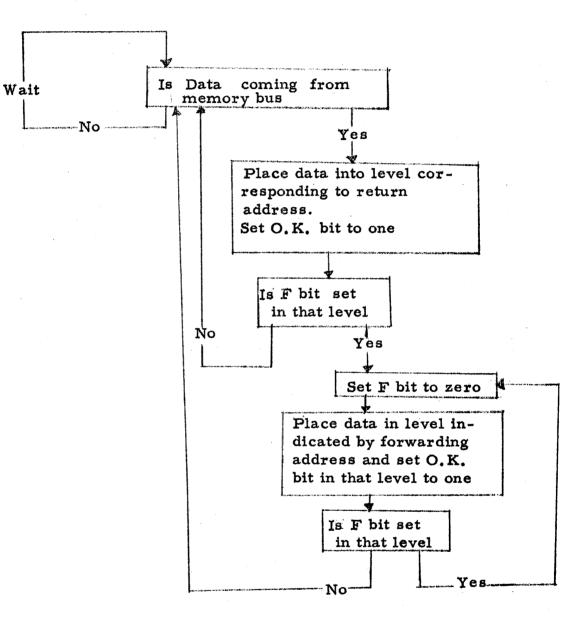

#### 7. Logic for Placing Data into the Virtual Memory

In Figure 9, we see the logical conditions which must be satisfied by the data returning from Memory addressed to the Virtual Memory. The return address which was supplied when the fetch was started selects the level into which the data will be placed. The O.K. bit is then set to one indicating that the proper data is in the level. The operation is complete at this point unless

From Figure 6

In the  $C_1$  level: Put the instruction address in IA, put the op code in OP, Put the data address into D (Note this) Set O.K. bit to one Set forwarding bit, the bring bit and and store bit to zero. Set the compare bit to zero (Note)

return to top of Figure 6

Figure 6C, Logical Conditions for Immediate Type Operations

Figure 8, Data Store Procedure

# Figure 9, Procedure for Placing Data into Virtual Memory

the Forwarding bit is set. In this case, the data must be forwarded to the level designated by the Forwarding address. This procedure continues from level to level as long as the data continues to arrive into a level whose Forwarding bit is set. This procedure automatically supplies all operands present having identical data addresses with the proper data without additional memory references.

8.

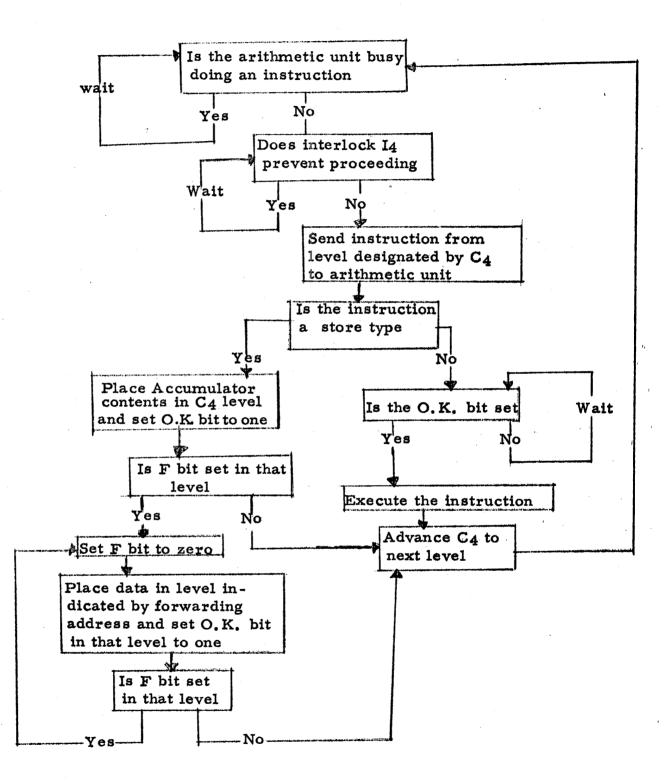

## Logic of Removing Instructions from the Virtual Memory

Observing Figure 10, we notice that as the arithmetic unit completes an instruction it checks to see if the next instruction in the Virtual Memory is ready to be executed (indicated by interlock I4). Note: The operation may be an unconditional branch, a conditional branch, or an index type store as well as a normal bring or store type instruction involving the accumulator. Figure 10 shows only the cases which involve the universal accumulator. The index and unconditional branches and the index store operations are merely ignored at this point. They are carried along only to provide the data for recovery in the event an interrupt occurs. The execution of the conditional branches on arithmetic results are described in the next section.

If the next instruction marked by counter C4 is ready, it is fed into the arithmetic unit. If it is a store type, the data is gated from the accumulator into the data field of level C4, and the OK bit is set to one. If the Forwarding bit of the level is set, a forwarding procedure in this case is essential for the proper logical operation of the computer, whereas in the bring case it is a time-saver only.

If the instruction is not a store type, the arithmetic unit must hold up until the O.K. bit for the level is set. When the O.K. bit is set, the instruction is gated into the arithmetic unit and executed.

### 9. Logic of Interrupt Procedure

If for any cause an interrupt (or trap) from a special condition occurs, the instruction which is being executed in the arithmetic unit is completed. However, the next instruction is not executed in spite of the fact all the data preparation for it may have been completed. The address in the IA (instruction address) field will serve as the value to reset the instruction counter if it is desired.

# Figure 10, Procedure for Removing Instructions from Virtual Memory

The Vitual Memory is initialized, i.e., set to the starting conditions of an interrupt, with the exception that all store orders which have already received data from the accumulators must be executed first. Note: If the interrupt is of such a nature that the normal flow of instructions is not resumed, the procedure of storing the modified values of the index registers in the Virtual Memory gives logically correct results, i.e., the same as if the interrupt had occurred before the indexing took place.

#### IV. DESCRIPTION OF TIMING SIMULATION PROGRAM

#### A. General Considerations

During the logical design of STRETCH it was necessary to prove the value of the Virtual Memory concept and to assist in the selection of optimum values of various system design parameters. Examples of such parameters are: The number of memory boxes, interlace and allocation of memory addresses, and numbers of Virtual Memory levels. Also of interest were trade-off factors for speeds of indexing arithmetic unit, arithmetic unit, memories, etc.

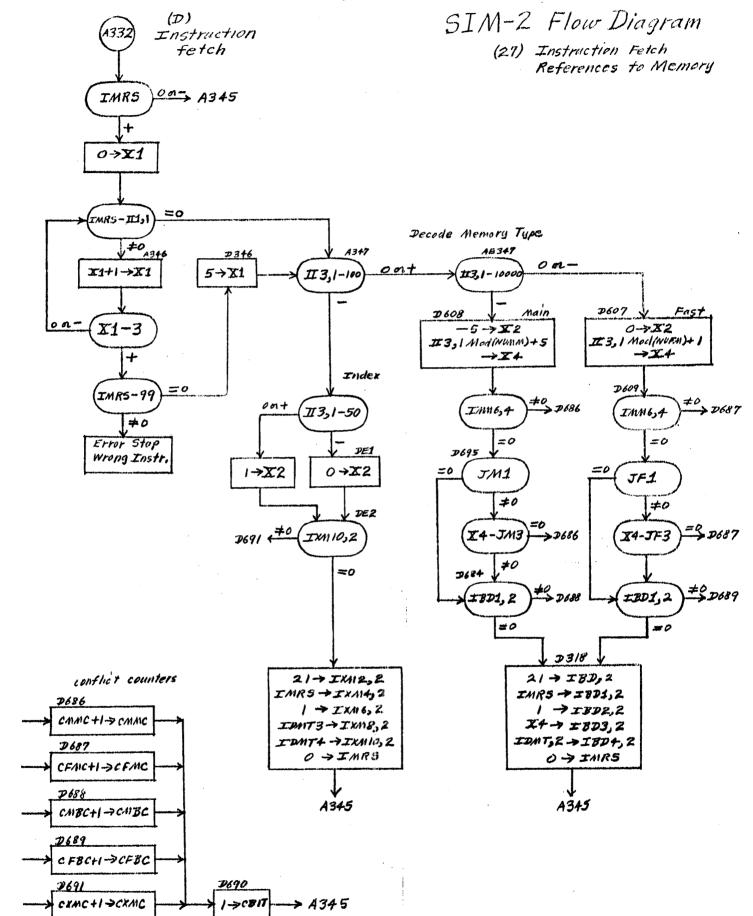

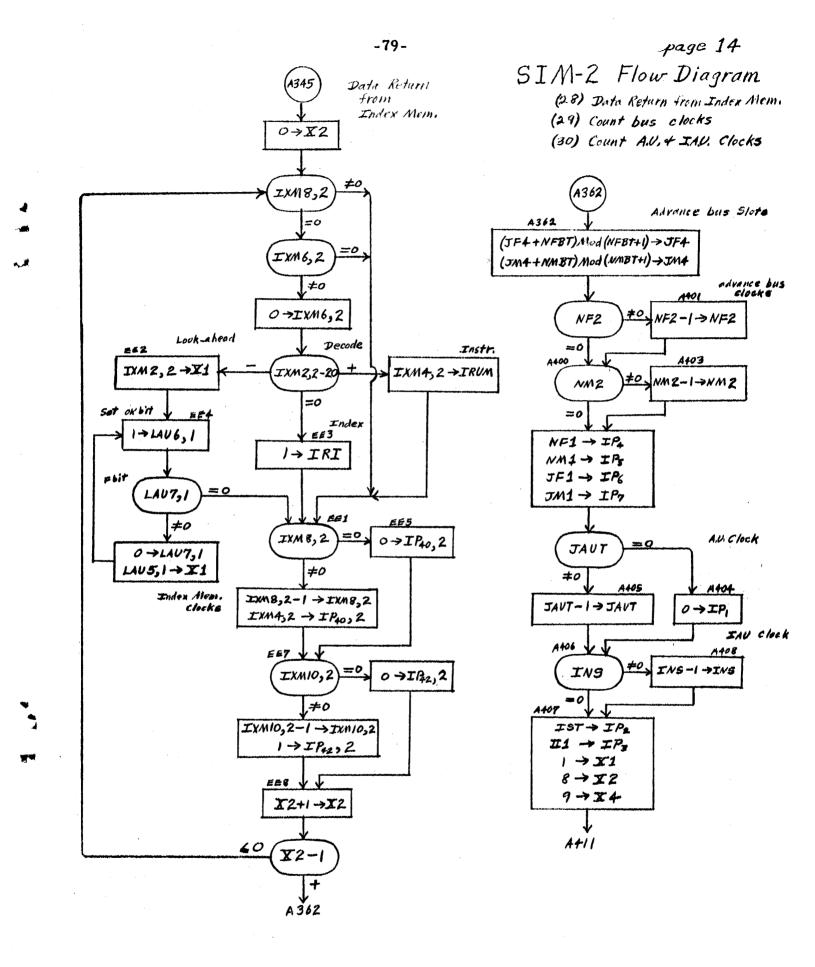

In November 1957 the Timing Simulator (SIM-2) described here was written for the IBM 704. This program attempted to answer such questions quantitatively by simulating the time-wise operation of STRETCH on typical test programs coded in STRETCH language.

The basic logic of the 704 program follows the principles just described in the preceeding section for the Virtual Memory. It should be stressed that the Simulator is a Timing Simulator and does not execute the instructions in an arithmetic sense. It traces the time-wise progress of the instructions through the components of the computer observing all the interlocks and time delays necessary for correct representation of the behavior of the machine.

One of the fundamental concepts in the STRETCH design is that of <u>asynchronous</u> operation of the components. This means that there are a large number of logical steps being executed at any one time in the computer, each of them proceeding at its own rate. To simulate this flow of many parallel continuous operations, we have broken the continuous time variable into finite time steps. The basic time step is taken as 0.1 microsecond in the Simulator. Several reasons prompted us to select this time interval. Some are relatively simple, such as the desire to have the results come out in microseconds and decimal fractions thereof. Taking a coarse time interval makes a given problem run faster on the Simulator since the running time is almost inversely proportional to the time step being used.

More fundamentally, the "natural" internal time scales of the computer are represented on one hand by the cycle time of the main memories (2 microsec) and on the other hand by the time required for signals to traverse one logical level in the circuits (5 to 20 millimicroseconds). The external time scale of the computer, as given by the I/O devices, is in the order of milliseconds for start up time and tens of microseconds for data flow rates.

Most internal macro logical processes require 0.1 microseconds or more since they usually require at least 10 logical levels. These represent the scale of quantities we wished to study in this simulator. Other scales could have been chosen. For example, one could write a program which followed the operation of every logical "and" and "or" circuit in the computer. (In fact, the authors have written such a program for a small experimental study.) The simulation program is simpler on this scale but the specification of a computer such as STRETCH would be an enormous task-- equivalent to laying out the whole circuit design. Another difficulty, would be that changing a gross parameter such as the multiply time might require the changing of thousands of "and" and "or" blocks in the circuit specification.

By taking 0.1 microsec as our quantum of time, we are automatically setting the scale of the smallest circuit entities which we will consider as being those which accomplish complete functions in a 0.1 microsec or few multiples thereof. Thus by using this philosophy, and considering many of the components of the computer as "black boxes", we greatly simplify the details which must be considered without introducing serious timing inaccuracies.

Our experience has indicated that more information was gained by making a large number of fast parameter studies using different configurations and programs that could have been obtained by a very slow, detailed simulation of a few runs with more precision per run. Even so our time scale is too fine to make serious Input-Output applications studies. These would require a simpler Simulator having at least a factor of 10 coarser basic time interval.

#### B. Logic of the Simulator

In the asynchronous organization of STRETCH there can be many major components operating at any one time. To achieve this parallel effect in the Simulator we essentially "hold time still" and scan the entire machine representation at each time step. Although every major block of the program is traversed at each time step, if there is no activity required in a given block, only a few tests need be made by the code.

If in this process it is determined that a given logical unit should do an operation, the time interval required for the operation is obtained from a table of constants. The speed of the various logical units can thus be changed parametrically by changing the values in the tables. A constant obtained from the tables is inserted into a memory location called the time counter for that unit. At each time step the program reduces this counter by one until it reaches zero. Thus the fact that the counter is non-zero can be used to indicate that the particular logical unit is busy and not available to service other requests. When the counter is zero the unit can consider a new input.

In addition to the time counters many of the logical blocks contain other conditions or interlocks which effect the operation of the block. These conditions are stored in the program and tested before action is undertaken. As an example, the 'O.K. bit" described in the previous section is stored as a "one" or "zero" in a memory location associated with each Virtual Memory level (called LAU6, i in the program, where i is the Virtual Memory level). The "O.K." bit indicates that the data in the level is the correct value for the operation. In the program the "OK bit" is set by storing a one in location LAU6, i.

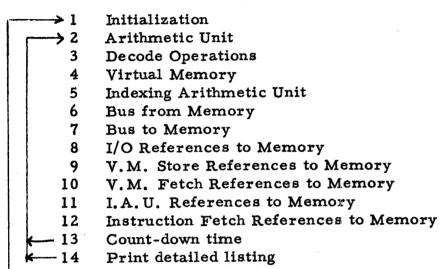

Each logical unit when it completes its operation may have data available to start another unit. The other unit may be notified that the data is available in two possible ways. Either (1) The subroutine corresponding to the receiving logical unit searches all possible inputs to determine if any of them has data for it, or (2) the sending unit sets logical constants within the receiving unit which indicate that the data is available. For example, the "O.K. bit" is set for a given level by the memory in-bus subroutine. While on the other hand, the arithmetic unit subroutine tests the O.K. bit to determine whether or not data is available for it. The simplified Flow Diagram in Figure 11, indicates the order in which the subroutines for the various logical units are executed at each time step. Using the types of techniques just described above, the logical subroutines simulate the action of the components of the computer such as the Virtual Memory, arithmetic Unit,etc.

The details of the Simulator are described by Tables 1 through 4 and in the detailed flow diagrams at the end of this report. These flow diagrams can be corrolated in the obvious way with those given in the section which describes the Virtual Memory. The Simulator also contains several other subroutines which do such things as initialize the program at the beginning of a run, set up the timing diagrams and summarize the results of the run. (see discussion in the Result Section).

The STRETCH instructions being simulated are read into the 704 from tape as required. The instructions are put on tape from cards at the beginning of a run. (The input quantities read in for each operation are listed in Table I, column 1.) It is interesting to note that since the Simulator simulates timing only, not the arithmetic or indexing functions, the sequence of instructions to be executed must be furnished as a "string" with all loops unwound. However, to make the computer behave as it actually would, the loops must be furnished with "wrong way" paths given for the cases where the computer would take such paths. Also one must furnish <u>more</u> than enough information along such paths since it is difficult to predict in advance how far the computer will get down the wrong path before it is called back.

Parameters are changed from one run to another by use of control cards. The control cards are set up in such a way that any number of parameters may be changed between runs.

Results are given either as detailed timing charts or as summary listings for each problem. The usual procedure has been to print only summary results while making a series of parameter studies. At the end of each run the new control card or cards are read in, the problem tape is rewound, and the Simulator reruns the problem with the new constants.

15 Summarize and print

Figure 11. SIM - 2 Simplified Flow Diagram

#### V. SOME RESULTS OF THE SIMULATION STUDIES

#### A. General Description

#### 1. Introduction

During 1958 a number of reports were written giving results of runs made with the SIM-2 program. We will not attempt to record here all of the results thus presented because many of them were superseded by later reports or were concerned with specific problems in the design of STRETCH. The results quoted here were chosen for their general interest as parametric studies and are not intended to represent STRETCH as it is actually designed.

#### 2. Output Listings of Simulator

Figures 12 and 13 show examples of the type of output listings given by the Simulator. Figure 12 is a piece of a long timing chart with each line of printing representing 0.1 microsecond of time. The columns represent the various components of the computer. On the left and right are timing counts subdividing each microsecond. On the far right are conflict indicators ("C" on the charts) and waiting indicators, "W" which indicate when interlocks prevent operations from proceeding.

The 2nd column, II, gives the number of the instruction being indexed. The 4th column, AU, gives the number of the instruction using the arithmetic unit. The next four columns represent the instructions using the memory buses. The columns labeled X-,F-, and M- represent the index, fast, and main memories. A string of "X's" in the columns represents the cycle time of the memory. The number indicates the instruction using the memory and number of times which it is repeated gives the read-out time of the memory. The columns L- indicate which instruction is located in the Virtual Memory levels. The other columns are for details in analysis and need not be considered here.

Figure 13 gives an example of a series of summary listings. Each set of numbers represents a total problem run. The quantities listed are given in Tables III and IV. As was mentioned earlier, for most of the runs made in the Simulator studies, only summary runs were made.

# -30A-Figure 12 Listing of Simulator Print-Out

PROJECT 7000 SIMULATOR '2 COCKE + KOLSKY NOV 57

|                                                 | T 7000 SIMULATOR 42 COCKE + KOLSKY NOV 57                     | <b>.</b>                                                                                                            | * LO #5 M/S M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ······                      |

|-------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| $\begin{array}{c} 1 \\ 1 \\ 2 \\ 1 \end{array}$ | IS AU IF IM OF OM X1 X2 F1 F2 F3 F4 M1 M2 M3 M4 M5 M6 M7 M8 U | LI LZ LJ L4 LJ LO L                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 1                         |

| 3 1<br>4 1                                      |                                                               |                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 2                         |

| 5 1                                             | 1                                                             |                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 4<br>1 5                  |

| <u>6 1</u><br>7 1                               | <u>1X</u><br>3 1X                                             | <br>20 - Maria (1947) - Maria Maria (1947) - Maria (194 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u>6</u><br>2 7             |

| 8 <u>1</u><br>91                                | <u> </u>                                                      |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\frac{1}{1}$ $\frac{8}{9}$ |

| $\frac{0}{1}$                                   | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$         | nen a men sekara kan sekara kan sekara kan sekara kan sekara sekara sekara sekara sekara kan sekara kan sekara      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 10                        |

| $\frac{1}{2}$ $\frac{1}{3}$ $\frac{1}{1}$       | 3X                                                            | 999 1 1993 9 1999 19 19 1 19 19 19 19 19 19 19 19                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 1 2                       |

| 4 1                                             | 3 X<br>1 3 X                                                  |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23<br>14                    |

| 5 1<br>5 1                                      | 1                                                             | <b>Man a a Balance a san an a</b>                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                           |

| 71                                              | 4                                                             | n i na haf man ann an                                                                 | and the set of the second set of the second s | 2017                        |

| 2                                               | 1                                                             | 1                                                                                                                   | ·····                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>8</u><br>2 9             |

| 2                                               | <u>2</u><br>4 1 X                                             | 1                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\frac{1}{1}$               |

| 3                                               | 1                                                             | <u>1</u><br>21                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\frac{2}{1}$ $\frac{2}{3}$ |

| 3                                               | 2<br>4 2 5 X                                                  | 2 '1                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                           |

|                                                 | <u>1</u> 5                                                    | 2 1 2 1                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25<br><u>16</u>             |

| 4                                               | 1 5X<br>2 5X                                                  | 3 2 1<br>3 2 1                                                                                                      | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7<br>28                     |

| 4                                               | 2 3 X 5X<br>4 5X                                              | 3 2 1<br>3 2 1                                                                                                      | ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 9                         |

|                                                 | 1 5 X<br>1 5 X                                                | 3 2 1                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 1                         |

|                                                 | 1                                                             | 4     3     2       4     3     2                                                                                   | 747                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                           |

|                                                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$          | <u>4 3 2 1</u><br>4 3 2 1                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24<br>15                    |

| ····· E ·····                                   | 2 7X 4X<br>4 7X 4X                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 6<br>. 7                  |

| 6                                               | 1 7X 4X<br>1 7X 4X                                            | <u>4 3 2 1</u><br><u>4 3 2 5</u>                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 8                         |

| 6                                               | <u>2 7 × 4X</u>                                               | 4 3 2 5                                                                                                             | 5<br>5 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9<br>2 10                   |

|                                                 | 14X                                                           | 4 3 2 5<br>4 3 2 5                                                                                                  | 5 1<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 1                         |

|                                                 | 1 5 4X<br>2 4 5 X                                             | 4 3 6 5<br>4 3 6 5                                                                                                  | 9 2<br>9 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 2                         |

| 7                                               | 2 4 X 5X<br>4 9 X 5X                                          | 4 3 6 5<br>4 3 6 5                                                                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                           |

| 8                                               | 1 4 9 X 5X                                                    | 4 3 6 5                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 7                         |

| 8                                               | 2 9X X 5X                                                     | 4 7 6 5                                                                                                             | 7 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8<br>2<br>9<br>1 10         |

| 8                                               | 2 X 9X X 5X<br>2 9X X 5X                                      | 4 7 6 5                                                                                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 10                        |

|                                                 | <u>4 9 7 X X 5X</u><br>1 9 5 7 X X X                          | <u>4 7 6 5</u><br>4 7 6 5                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 2<br>1 3                  |

|                                                 | 1 5 X X 7X                                                    | 8 7 6 5<br>8 7 6 5                                                                                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                           |

| 9 2                                             | 2 <u>5</u> X 7X                                               | 8 7 6 5                                                                                                             | 11 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | l 6                         |

|                                                 | <u>1 5 11 X 7X</u>                                            | 8 7 6 5<br>8 7 6 5                                                                                                  | 11 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |

| 10 $10$ $2$                                     | <u>2 5 11X X 7X</u>                                           | 8769<br>8769                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 9<br>10                   |

| 10 2                                            | <u>2 7 11X X X</u>                                            | 8769<br>8769                                                                                                        | <b>2</b><br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                           |

| 10 4                                            | 4 6 7 X 11X X X                                               | 8769                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                           |

|                                                 | 1 7 11 X X                                                    | 8 7 10 9                                                                                                            | 2<br>13 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |

| 5 :                                             | 1 7 ×                                                         | 8 7 10 9                                                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                           |

Figure 12 Listing Of Simulator Print-Out

| 7 11 1                                                                                                          |                       |                         | ×            | 8 7                   |                 |          |               | CW<br>CW   |

|-----------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|--------------|-----------------------|-----------------|----------|---------------|------------|

| 8 11 2                                                                                                          |                       |                         | <u> </u>     | 8 7                   |                 |          |               |            |

| 9 11 2                                                                                                          | X                     | 13X                     | X            |                       | 10 9<br>10 9    |          | 2 10          |            |