# PLANNING A COMPUTER SYSTEM

# PROJECT STRETCH

# PLANNING A

#### CONTRIBUTORS

Richard S. Ballance Robert W. Bemer Gerrit A. Blaauw Erich Bloch Frederick P. Brooks, Jr. Werner Buchholz Sullivan G. Campbell John Cocke Edgar F. Codd Paul S. Herwitz Harwood G. Kolsky Edward S. Lowry Elizabeth McDonough James H. Pomerene Casper A. Scalzi

# COMPUTER SYSTEM

## PROJECT STRETCH

## Edited by WERNER BUCHHOLZ

SYSTEMS CONSULTANT CORPORATE STAFF, RESEARCH AND ENGINEERING INTERNATIONAL BUSINESS MACHINES CORPORATION

New York Toronto London 1962

MCGRAW-HILL BOOK COMPANY, INC.

#### PLANNING A COMPUTER SYSTEM

Copyright © 1962 by the McGraw-Hill Book Company, Inc. Printed in the United States of America. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publishers. Library of Congress Catalog Card Number 61-10466

THE MAPLE PRESS COMPANY, YORK, PA.

08720

## FOREWORD

The electronic computer has greatly contributed to scientific research; it has reduced costs, shortened time scales, and opened new areas of investigation. Increased use of computers, in turn, has created a need for better computers. What is desired most often is a general-purpose design with the best achievable memory capacity, speed, and reliability.

User experience has shown the need for considering more than these fundamental properties in the design of a new computer. Unlike earlier machines, whose capabilities were mainly functions of the properties of individual components and units and not to any marked extent of their organization or the user's requirements, the Stretch computer is based on a comprehensive joint planning effort involving both users and designers. Their combined experience brought in many new considerations. The term *general purpose* was given a broader definition in Stretch. Areas of special concern included the vocabulary of the computer, parallel operation for greater speed and efficiency, error detection and correction, and recovery from errors and other exceptional events.

The design phase for a new-generation computer is always a difficult one. The potential user cannot predict accurately how the new tool will be used or what new areas of research will open up. The designers have to work with components for which such important data as how these components behave en masse are lacking. The Stretch project, in design as well as construction, has been successfully concluded. The degree of success, however, can only be ascertained as experience in using Stretch is accumulated.

This book forms a record of what is probably the first really comprehensive design effort for a new computer. It was written and edited by a very competent group from the technical staff of the IBM Corporation, including most of the principal designers of Stretch.

There is no doubt that still better computers will be needed. Although

#### vi Foreword

the Stretch computer is now solving problems that could not be solved a few months ago, many problems are known to exist for which even Stretch is inadequate. This book will be invaluable as a guide and reference source for computer development in the future.

Bengt Carlson

Los Alamos Scientific Laboratory September 1961

### PREFACE

Planning a computer system ideally consists of a continuous spectrum of activity, ranging from theoretically analyzing the problems to be solved to evaluating the technology to be used for the components. When dealing with an electronic digital computer of more than modest size that is intended to be used for fairly complex applications, one is forced to split the planning spectrum into arbitrary segments, each segment being developed with due regard for its neighbors. This book is mainly concerned with that segment that has to do with the selection of an instruction set and related functional characteristics of a computer. Except for cost and speed, these are the characteristics that do most to distinguish one computer from the next.

This book is about the planning of a specific computer. Being specific has both advantages and drawbacks. On one hand, the book reflects the thoughts of one group, not the entire state of the art. It cannot be a compendium of all the ideas, features, and approaches that have proved interesting and useful in various computers. On the other hand, concentration on one design serves to crystallize the concepts in a way that would be difficult to do with a hypothetical computer designed for the sake of exposition. Moreover, a specific computer represents compromises in bringing diverse and complex considerations together into a coherent working entity, and these practical compromises are instructive in themselves.

Although the discussion is in terms of a specific computer, the concepts discussed are quite general. The computer chosen is the IBM 7030. It is a recently developed computer incorporating many of the latest advances in machine organization, and a number of these advances are original or greatly improved over earlier versions. It is also a very large and very fast computer. There is an advantage in choosing such a large computer for examination, for it is practical to include quite a rich vocabulary in large computers, and this affords an opportunity to examine features which may not all be so readily incorporated in a single com-

#### viii Preface

puter of smaller size. The 7030, in particular, combines computing and data-processing facilities that were previously available only in separate computers. Thus a large computer may serve as a model from which to select or adapt features for use in a smaller computer.

The 7030 computer was the outcome of *Project Stretch*, an IBM research and development project aimed at a major advance in computer technology and organization. To achieve a substantially improved computer organization required more than a mere compilation of the best features in existing machines and of new features already known. In the hope of stimulating ideas for substantial improvements it was decided to explore very thoroughly the basic structure of computers. Several of the participants in these studies published papers, from time to time, on computer organization in general and on particular conclusions drawn for Project Stretch. This book consists partly of such material, updated and edited for continuity. Much previously unpublished material has been added to fill in major gaps.

The book is intended to complement the reference manual for the 7030,<sup>1</sup> although enough of the details of the 7030 are summarized in the text or in the Appendix that the 7030 Reference Manual is not required for understanding the material in this book. Where the manual recites in as much detail as possible *what* the system does, this book is aimed at shedding light on *how* it is done and *why* the system was designed the way it is, as well as describing some alternative courses that were examined and rejected.

The book does not attempt to deal adequately with details of the design and construction of the computer and its components, since these might well fill another volume. Nor does it cover the programming techniques used in the extensive compiling and supervisory programs written for the system.

The book is aimed at a reader who already has a reasonably good knowledge of how a stored-program computer is organized and programmed. It may also serve as an advanced text to follow an elementary course on digital computers.

#### Contents of Book

Chapter 1 is a short history of Project Stretch. Chapter 2 outlines the philosophy that guided the design of the system. It emphasizes the need for a consistent point of view among those responsible for the basic plan of as complex a system as this computer.

A summary of the system in narrative form is given in Chap. 3. This is intended to give the reader a fairly complete picture of the forest before

<sup>1</sup> "Reference Manual, 7030 Data Processing System," IBM Data Processing Division, White Plains, N.Y. he looks at the trees. Most of the material in this chapter is covered again in detail in later chapters.

Chapter 4 discusses different classes of data and the need for different ways of specifying each class. Chapter 5 gives the reasons for designing what is basically a binary structure, although there are provisions for both binary and decimal arithmetic.

Chapter 6 considers the choice of a new character set and code for the 7030, which provides 120 characters, including many not available before, such as those of the lower-case alphabet. It may be noted that the 7030 system is quite flexible with regard to character sets and is not tied to the set described here. One reason for writing this chapter is that the reasoning is pertinent to current industry-wide code standardization efforts, and it may be found useful as input to these important deliberations.

Chapter 7 covers the extensive variable-field-length features of the 7030, which are used for fixed-point binary and decimal arithmetic, for alphanumeric processing, and for Boolean logic. Chapter 8 describes the floating-point-arithmetic operations, which deserve much more than the routine treatment they so often receive if numerous pitfalls are to be avoided. Between them, Chaps. 7 and 8 bridge the traditionally separate domains of the "business" and "scientific" computers.

In Chap. 9, the reason for the rather complex instruction formats used in the 7030 is explained. Chapter 10 deals with various methods available to the programmer for specifying the logical sequence of instructions. (This should be distinguished from the internal rearrangement of this sequence to achieve overlapped operation, as described in Chaps. 14 and 15.) Included in Chap. 10 are original techniques for program interruption and for executing instructions outside the current instruction sequence. This *execute* feature, incidentally, is one of several examples where a new technique developed originally on Project Stretch came to light first in another IBM computer (here the 709) that happened to be built on an earlier schedule.

Chapter 11 covers a thorough investigation of indexing, which resulted in the development of the control-word technique for processing records and for controlling program loops. A general method for controlling input-output units that is independent of the precise nature of the device is discussed in Chap. 12.

Chapter 13 gives an introduction to the fairly recent subject of *multi-programming*, which is the simultaneous execution of several problem programs. It shows how the design of the 7030 was heavily influenced by the desire to exploit multiprogramming for more efficient utilization of the computer and for better man-machine communication.

The next three chapters give a brief survey of the construction of major

parts of the system to round out the picture. Chapter 14 deals with the various parts of the central processing unit, the circuits, and the method of construction. One part of the central processing unit, which has been called the *look-ahead*, receives more detailed treatment in Chap. 15, since it represents a major departure from the design of earlier computers. Chapter 16 explains the input-output *exchange* which controls the independent operation of a number of input-output channels.

Chapter 17 describes the IBM 7951 Processing Unit, which extends but is not a part of the Stretch system, having been developed under a separate contract. The 7951 introduces a completely new concept of nonarithmetical processing, which is a much more powerful tool for operating on nonnumerical data than previous techniques. The complete system includes an entire 7030 computer, all of whose facilities are available for more conventional procedures. It seemed appropriate to include in this book at least a brief account of a contemporary project related to Stretch.

#### Acknowledgments

As part of a contractual agreement with the Los Alamos Scientific Laboratory, the first recipient of a Stretch computer, a joint Los Alamos-IBM mathematical planning group was set up to coordinate, advise, and assist in the planning stage. Project Stretch owes a great deal to the many invaluable contributions of the Los Alamos members, a group which collectively represents as great a wealth of practical experience in all phases of the application of large computers to large mathematical problems as can be found anywhere. The Los Alamos group, ably led by B. G. Carlson, included R. M. Frank, M. Goldstein, H. G. Kolsky (now with IBM), R. B. Lazarus, E. A. Voorhees, M. B. Wells, D. F. Woods, and W. J. Worlton. A second group was formed later to work with IBM Applied Programming personnel on creating programming systems for Stretch.

It is impossible to acknowledge individually the work of all the IBM personnel who have made significant contributions to the material in this book. All except one of the fifteen coauthors of the chapters participated directly in Project Stretch.

Some other individuals should be mentioned in connection with specific chapters. The character set reported in Chap. 6 was developed jointly by a group including E. G. Law, H. J. Smith, and F. A. Williams. W. Wolensky contributed substantially to the variable-field-length system outlined in Chap. 7. A great deal of the credit for the floating-point system of Chap. 8 should go to D. W. Sweeney. Much of the early development of the control-word concept covered in Chap. 11 was stimulated by discussion with G. M. Amdahl, E. M. Boehm, J. E. Griffith, and

R. A. Rahenkamp. J. D. Calvert was in charge of the design of the input-output control system described in Chap. 12. Engineering responsibility for major units described in Chap. 14 rested with R. T. Blosk (instruction unit), J. F. Dirac (look-ahead unit), J. A. Hipp and O. L. MacSorley (arithmetic units), and L. O. Ulfsparre (memory bus unit), while R. E. Merwin and E. Bloch (the author of the chapter) had over-all engineering direction for Project Stretch. The description of the input-output exchange in Chap. 16 was based in part on an oral paper by H. K. Wild,<sup>1</sup> who was in charge of the design of this unit and is responsible for much of its logic. T. C. Chen contributed material for programming examples shown in the Appendix.

Important work was contributed during the early stages of the project by several whose names have not been mentioned so far, including J. W. Backus, N. P. Edwards, P. E. Fox, L. P. Hunter, J. C. Logue, and B. L. Sarahan.

The editor wishes to acknowledge particularly the encouragement and advice he received from S. W. Dunwell, who headed Project Stretch from beginning to end.

Werner Buchholz

<sup>1</sup> H. K. Wild, The Organization of the Input-Output System of the Stretch Computer, presented at the Auto-Math Sessions, Paris, June, 1959.

# CONTENTS

| Fore      | word   | ••••                        |                        | •      | •     | •    | •     | •    | • | • | • | • | • | v         |

|-----------|--------|-----------------------------|------------------------|--------|-------|------|-------|------|---|---|---|---|---|-----------|

| Preface . |        |                             |                        |        |       | •    | •     | •    | • | • | • | • | • | vii       |

| 1.        | Projec | t Stretch .                 |                        | •      | •     | •    | •     | •    | • | • | • | • | • | 1         |

| 2.        | Archi  | tectural Philo              | osophy                 | •      |       |      |       |      |   |   | • | • | • | 5         |

|           | 2.1.   | The Two (                   | Objectiv               | ves of | Pro   | ject | t Sti | retc | h |   |   |   |   | 5         |

|           | 2.2.   | Resources                   | · .                    |        |       |      |       |      |   |   |   |   |   | 6         |

|           | 2.3.   | Guiding P                   |                        |        |       |      |       |      |   |   |   |   |   | 7         |

|           | 2.4.   | Contempor                   |                        |        |       |      |       |      |   |   |   |   |   | 10        |

|           | 2.5.   | $\operatorname{Hindsight}$  |                        |        |       |      |       |      |   |   |   |   |   | 15        |

| 3.        | Syste  | n Summary c                 | of IBM                 | 7030   | )     |      |       |      |   |   | • | • | • | 17        |

|           | 3.1.   | System Or                   | ganizat                | ion .  |       |      |       |      |   |   |   |   |   | 17        |

|           | 3.2.   | Memory U                    |                        |        |       |      |       |      |   |   |   |   |   | 17        |

|           | 3.3.   | Index Mer                   |                        |        |       |      |       |      |   |   |   |   |   | 19        |

|           | 3.4.   | Special Re                  |                        |        |       |      |       |      |   |   |   |   |   | 19        |

|           | 3.5.   | Input and                   |                        |        |       |      |       |      |   |   |   |   |   | 19        |

|           | 3.6.   | High-speed                  | -                      |        |       |      |       |      |   |   |   |   |   | 20        |

|           | 3.7.   | Central Pr                  |                        |        |       |      |       |      |   |   |   |   |   | 20        |

|           | 3.8.   | Instruction                 | 1 Contr                | ols .  |       |      |       |      |   |   |   |   |   | 21        |

|           | 3.9.   | Index-arith                 |                        |        |       |      |       |      |   |   |   |   |   | 21        |

|           | 3.10   | Instruction                 | 1 Look-                | ahead  | ł.    |      |       |      |   |   |   |   |   | 21        |

|           | 3.11   | Arithmetic                  | $\mathbf{Unit}$        |        |       |      |       |      |   |   |   |   |   | 22        |

|           | 3.12   | Instruction                 | n Set                  |        |       |      |       |      |   |   |   |   |   | <b>24</b> |

|           | 3.13   | Data Arith                  | $\operatorname{metic}$ |        |       |      |       |      |   |   |   |   |   | <b>24</b> |

|           | 3.14   | Radix-conv                  | version                |        |       |      |       |      |   |   |   |   |   | 27        |

|           | 3.15   | $\operatorname{Connective}$ |                        |        |       |      |       |      |   |   |   |   |   | 27        |

|           | 3.16   | Index-arith                 | $\mathbf{metic}$       | Opera  | ation | ıs.  |       |      |   |   |   |   |   | 27        |

|           | 3.17   | Branching                   | Operat                 | ions   |       |      |       |      |   |   | , |   |   | 28        |

| xiv | Contents |

|-----|----------|

|     |          |

|     | 3.18.        | Transmission Operations                       | <b>28</b> |

|-----|--------------|-----------------------------------------------|-----------|

|     | 3.19.        | Input-Output Operations                       | 29        |

|     | 3.20.        | New Features                                  | 29        |

|     | 3.21.        |                                               | 32        |

|     |              |                                               |           |

| 4.  | Natura       | Il Data Units                                 | 33        |

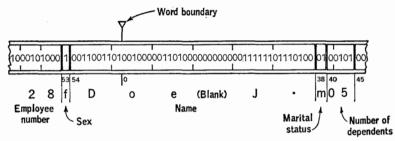

|     | 4.1.         | Lengths and Structures of Natural Data Units  | 33        |

|     | 4.2.         | Procedures for Specifying Natural Data Units. | 36        |

|     | 4.3.         | Data Hierarchies                              | 39        |

|     | 4.4.         | Classes of Operations                         | 40        |

| 5.  | Choosi       | ing a Number Base                             | 42        |

| ••• |              | -                                             |           |

|     | 5.1.         | Introduction                                  | 42        |

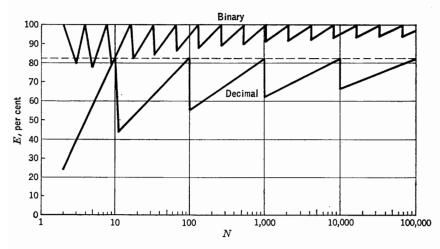

|     | 5.2.         | Information Content                           | 45        |

|     | 5.3.         | Arithmetic Speed                              | 49        |

|     | 5.4.         | Numerical Data                                | 50        |

|     | 5.5.         | Nonnumerical Data                             | 51        |

|     | 5.6.         | Addresses                                     | 52        |

|     | 5.7.         | Transformation                                | 53        |

|     | 5.8.         | Partitioning of Memory                        | 54        |

|     | 5.9.         | Program Interpretation                        | 56        |

|     | 5.10.        | Other Number Bases                            | 58        |

|     | 5.11.        | Conclusion                                    | 58        |

| 6.  | Charac       | :ter Set                                      | 60        |

|     | 6.1.         |                                               | 60        |

|     | 6.1.<br>6.2. |                                               | 60<br>62  |

|     | 6.2.<br>6.3. |                                               |           |

|     | 0.0.         | Subsets                                       | 62        |

|     | 6.4.         | Expansion of Set                              | 63        |

|     | 6.5.         | Code                                          | 63        |

|     | 6.6.         | Parity Bit                                    | 66        |

|     | 6.7.         | Sequence                                      | 66        |

|     | 6.8.         | Blank                                         | 67        |

|     | 6.9.         | Decimal Digits                                | 68        |

|     | 6.10.        | - 31                                          | 68        |

|     | 6.11.        |                                               | 69        |

|     | 6.12.        |                                               | 69        |

|     | 6.13.        | Signs                                         | 70        |

|     | 6.14.        |                                               | 71        |

|     | 6.15.        |                                               | 71        |

|     | 6.16.        | List of 7030 Character Set                    | 72        |

| 7.  | Variat       | ble-field-length Operation                    | 75        |

|     | 7.1.         | • •                                           | 75        |

|     | 7.1. 7.2.    | Introduction                                  | 75<br>76  |

|     | 1.2.         | Addressing of variable-neig-length Data       | 10        |

| Contents | X |

|----------|---|

|    | 7.3.     | Field Length                                  | 77         |

|----|----------|-----------------------------------------------|------------|

|    | 7.4.     | Byte Size                                     | 78         |

|    | 75       | Universal Accumulator                         | 79         |

|    | 7.6.     | Accumulator Operand                           | 79         |

|    | 7.7.     | Binary and Decimal Arithmetic                 | 80         |

|    | 7.8.     | Integer Arithmetic                            | 81         |

|    | 7.9.     | Numerical Signs                               | 82         |

|    | 7.10.    | Indicators                                    | 84         |

|    | 7.11.    | Arithmetical Operations                       | 85         |

|    | 7.12.    | Radix-conversion Operations                   | 87         |

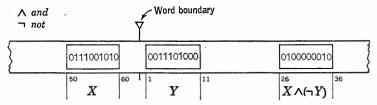

|    | 7.13.    | Logical Connectives of Two Variables          | 87         |

|    | 7.14.    | Connective Operations                         | 89         |

| 8. | Floatin  | g-point Operation                             | 92         |

|    |          | General Discussion                            |            |

|    | 8.1.     | Problems of Fixed-point Arithmetic            | 92         |

|    | 8.2.     | Floating-point Arithmetic                     | 94         |

|    | 8.3.     | Normalization                                 | 97         |

|    | 8.4.     | Floating-point Singularities                  | 98         |

|    | 8.5.     | Range and Precision                           | <b>9</b> 9 |

|    | 8.6.     |                                               | 100        |

|    | 8.7.     | Significance Checks                           | 101        |

|    | 8.8.     |                                               | 103        |

|    | 8.9.     | Structure of Floating-point Data              | 104        |

|    |          | Floating-point Features of the 7030           |            |

|    | 8.10.    |                                               | 106        |

|    | 8.11.    | Floating-point Data Formats                   | 106        |

|    | 8.12.    |                                               | 108        |

|    | 8.13.    | Indicators                                    | 112        |

|    | 8.14.    |                                               | 113        |

|    | 8.15.    |                                               | 114        |

|    | 8.16.    | Floating-point-arithmetic Operations          | 114        |

|    | 8.17.    | Fixed-point Arithmetic Using Unnormalized     |            |

|    |          | Floating-point Operations                     | 118        |

|    | 8.18.    | Special Functions and Forms of Arithmetic     | 119        |

|    | 8.19.    | Multiple-precision Arithmetic                 | 119        |

|    | 8.20.    | General Remarks                               | 121        |

| 9. | Instruct | ion Formats                                   | 22         |

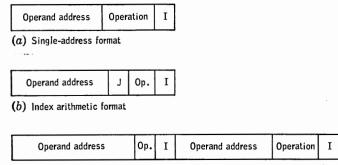

|    | 9.1.     | Introduction                                  | 122        |

|    | 9.2.     | Earlier Instruction Languages                 | 122        |

|    | 9.3.     | Humor mor detion Humgunges                    | 124        |

|    | 9.4.     | Literation of the single databols monuclion . | 125        |

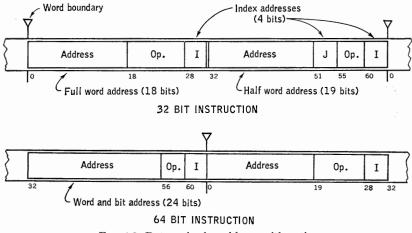

|    | 9.5.     | Basic 7030 Instruction Formats                | 126        |

|    | 9.6.     |                                               | 127        |

|    |          |                                               |            |

v

### xvi Contents

|     | 9.7.             | The Simplicity of Complexity                                               | 131          |

|-----|------------------|----------------------------------------------------------------------------|--------------|

|     | 9.8.             | Relationship to Automatic Programming Languages .                          | 132          |

| 10. | Instruct         | tion Sequencing                                                            | 133          |

|     | 10.1.            | Modes of Instruction Sequencing                                            | 133          |

|     | 10.2.            | Instruction Counter                                                        | 134          |

|     | 10.3.            | Unconditional Branching                                                    | 135          |

|     | 10.4.            | Conditional Branching                                                      | 136          |

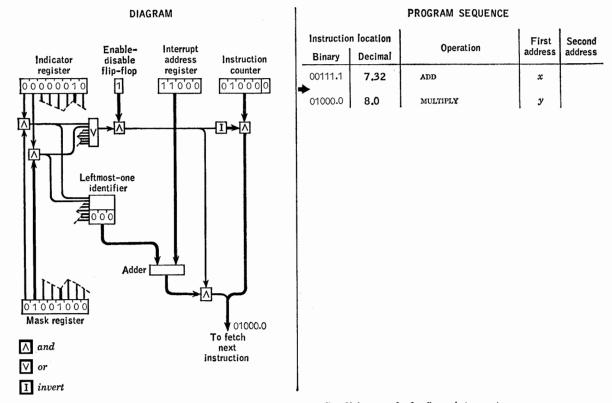

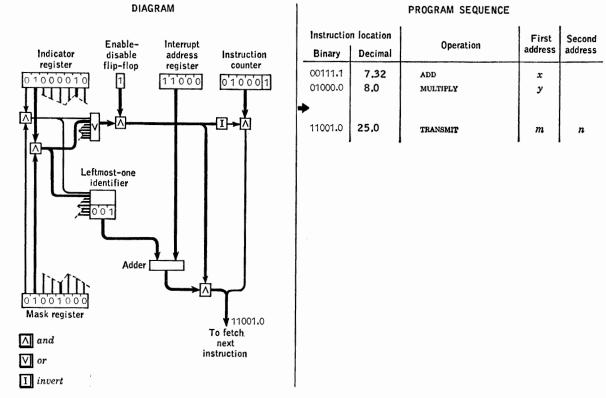

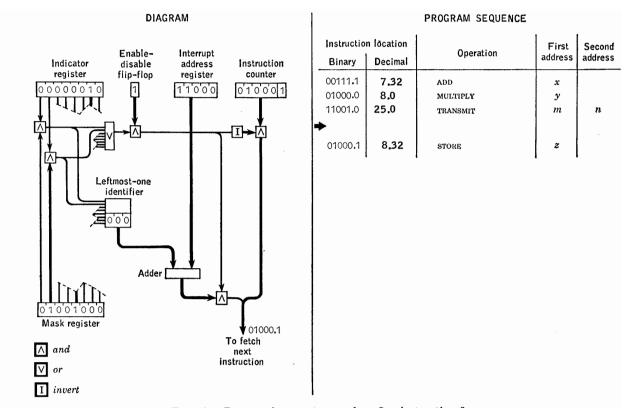

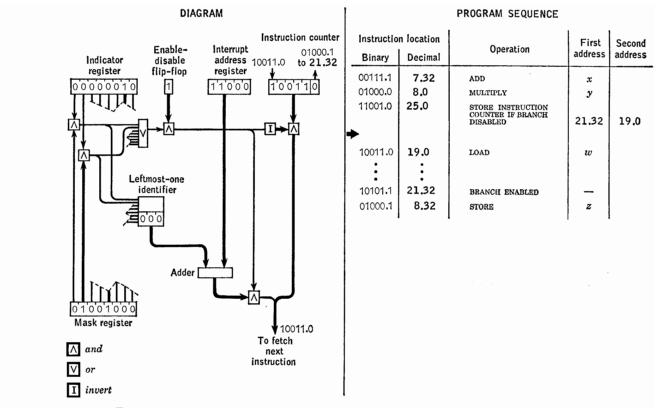

|     | 10.5.            | Program-interrupt System                                                   | 136          |

|     | 10.6.            | Components of the Program-interrupt System                                 | 137          |

|     | 10.7.            | Examples of Program-interrupt Techniques                                   | 140          |

|     | 10.8.            |                                                                            | 146          |

|     | 10.9.            | Execute Instructions                                                       | 148          |

| 11. | Indexi           | ng                                                                         | 150          |

|     | 11.1.            | Introduction                                                               | 150          |

|     | 11.2.            | Indexing Functions                                                         | 151          |

|     | 11.3.            | Instruction Format for Indexing                                            | 155          |

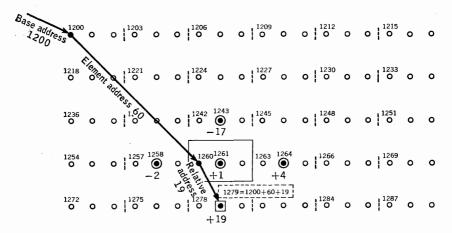

|     | 11.4.            |                                                                            | 157          |

|     | 11.5.            | Incrementing                                                               | 159          |

|     | 11.6.            | Advancing by One                                                           | 161          |

|     | 11.0.<br>11.7.   | Progressive Indexing                                                       | 161          |

|     | 11.8.            | Data Transmission                                                          | 162          |

|     | 11.8.            | Data Ordering                                                              | 162          |

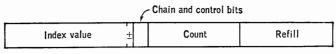

|     | 11.10.           | Refilling                                                                  | $105 \\ 165$ |

|     | 11.10.           | Indirect Addressing and Indirect Indexing                                  | 167          |

|     | 11.11.<br>11.12. | Indexing Applications                                                      | 169          |

|     | 11.12.<br>11.13. |                                                                            | 103          |

|     |                  |                                                                            |              |

|     | 11.14.           | File Maintenance                                                           | 175          |

|     | 11.15.           | Subroutine Control                                                         | 177<br>178   |

|     | 11.16.           | Conclusion                                                                 | 178          |

| 12. | Input-0          | Output Control                                                             | 179          |

|     | 12.1.            | A Generalized Approach to Connecting Input-Output<br>and External Storage. | 179          |

|     | 12.2.            | Input-Output Instructions                                                  | 180          |

|     | 12.3.            | Defining the Memory Area                                                   | 181          |

|     | 12.0.<br>12.4.   | Writing and Reading                                                        | 182          |

|     | 12.4.<br>12.5.   | Controlling and Locating                                                   | 182          |

|     | 12.5.<br>12.6.   | An Alternative Approach                                                    | 185          |

|     | 12.0.<br>12.7.   |                                                                            | 184          |

|     | 12.7.<br>12.8.   |                                                                            | 184          |

|     | 12.8.<br>12.9.   |                                                                            | 180          |

|     | 12.9.<br>12.10.  |                                                                            | 188          |

|     | 12.10.           | Operator Control of Input-Output Units                                     | 190          |

Contents xvii

| 13. | Multip         | programming                                    | • | 192         |

|-----|----------------|------------------------------------------------|---|-------------|

|     | 13.1.          | Introduction                                   |   | 192         |

|     | 13.2.          | Multiprogramming Requirements                  |   | 193         |

|     | 13.3.          | 7030 Features that Assist Multiprogramming .   |   | 195         |

|     | 13.4.          | Programmed Logic.                              |   | 197         |

|     | 13.5.          | Concluding Remarks                             |   | 200         |

|     | 13.6.          | References                                     |   | 201         |

| 14. | The Ce         | entral Processing Unit                         | • | 202         |

|     | 14.1.          | Concurrent System Operation                    |   | 202         |

|     | 14.2.          | Concurrency within the Central Processing Unit |   | 204         |

|     | 14.3.          | Data Flow                                      |   | 204         |

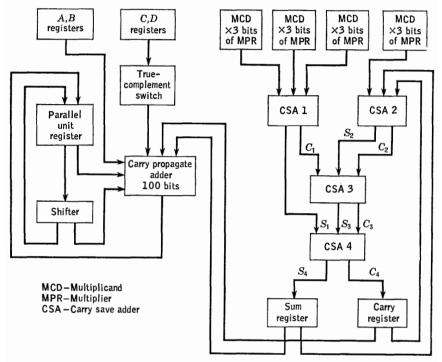

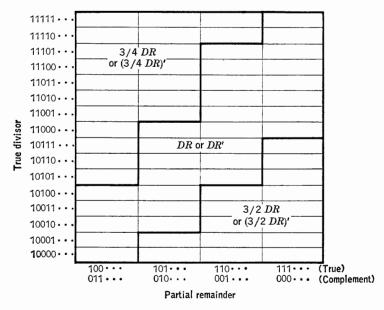

|     | 14.4.          | Arithmetic Unit                                |   | 208         |

|     | 14.5.          | Checking                                       |   | <b>216</b>  |

|     | 14.6.          | Component Count                                |   | <b>216</b>  |

|     | 14.7.          | Performance                                    |   | 217         |

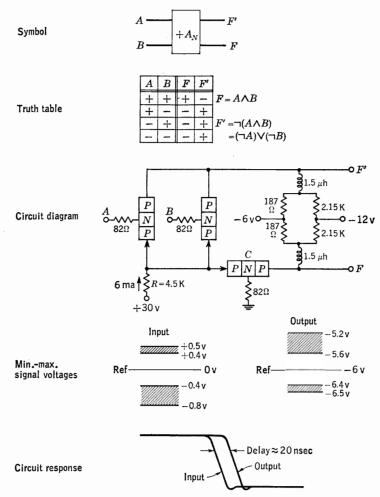

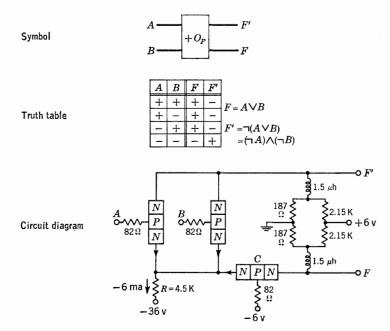

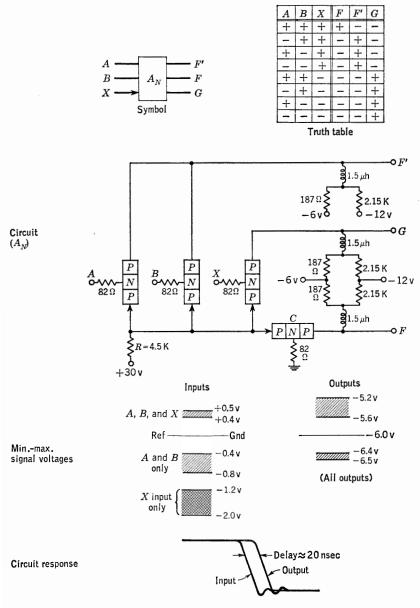

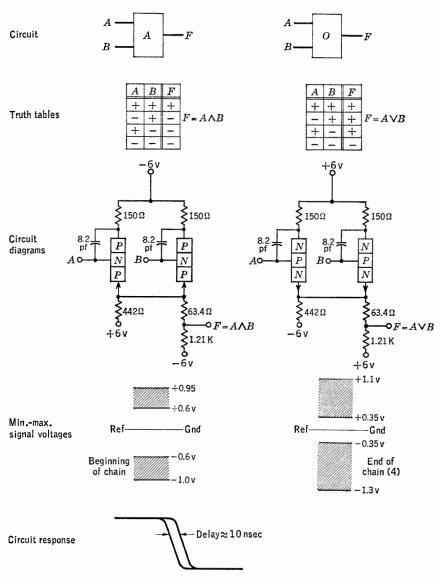

|     | 14.8.          | Circuits                                       |   | 218         |

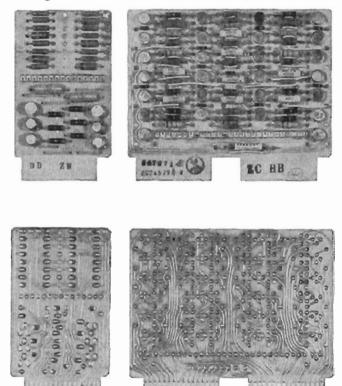

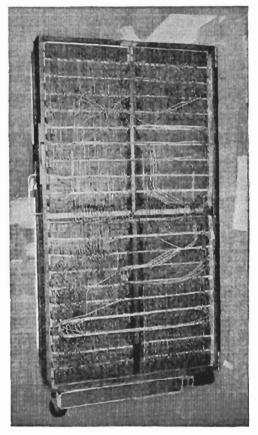

|     | 14.9.          | Packaging                                      |   | 223         |

| 15. | The Lo         | ook-ahead Unit                                 |   | 228         |

|     | 15.1.          | General Description                            |   | 228         |

|     | 15.2.          | Timing-simulation Program                      |   | 230         |

|     | 15.3.          | Description of the Look-ahead Unit             |   | 238         |

|     | 15.4.          | Forwarding                                     |   | 240         |

|     | 15.5.          | Counter Sequences.                             |   | 241         |

|     | 15.6.          | Recovery after Interrupt                       |   | 246         |

|     | 15.7.          | A Look-back at the Look-ahead                  |   | 247         |

| 16. | The Ex         | xchange                                        |   | 248         |

|     | 16.1.          | General Description                            |   | 248         |

|     | 16.2.          | Starting a WRITE OF READ Operation             |   | 250         |

|     | 16.3.          | Data Transfer during Writing                   |   | 250         |

|     | 16.4.          | Data Transfer during Reading                   |   | 251         |

|     | 16.5.          | Terminating a WRITE OF READ Operation          |   | 252         |

|     | 16.6.          | Multiple Operations                            |   | 252         |

|     | 16.7.          | CONTROL and LOCATE Operations.                 |   | 252         |

|     | 16.8.          | Interrogating the Control Word                 | • | 253         |

|     | 16.9.          | Forced Termination                             |   | <b>2</b> 53 |

| 17. | A No           | onarithmetical System Extension                |   | 254         |

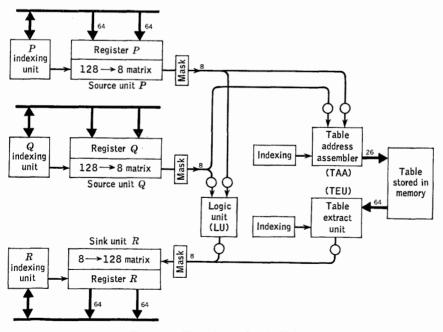

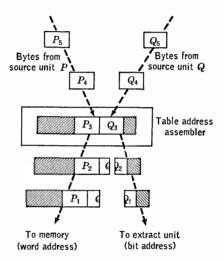

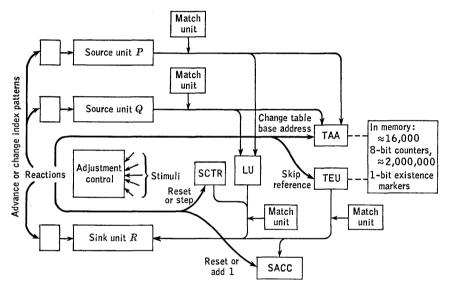

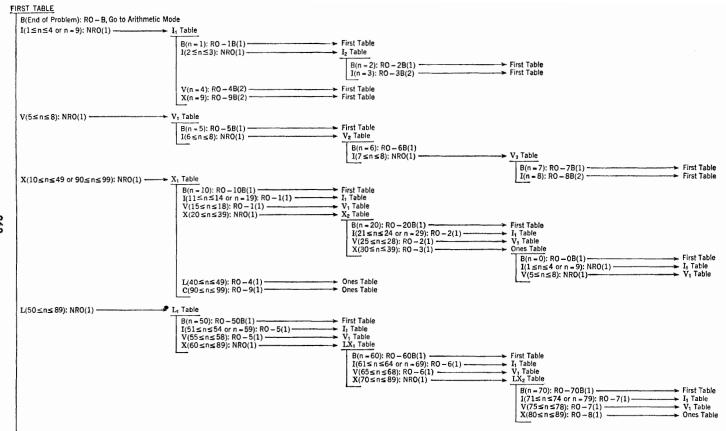

|     | 17.1.          | Nonarithmetical Processing                     |   | 254         |

|     | 17.2.          | The Set-up Mode                                |   | 258         |

|     | 17.2.<br>17.3. | Byte-sequence Formation                        |   | 259         |

|     | 11.0.          | Dyte-bequence roumation                        | • | 200         |

| 17.4.      | Pattern Selection                                 | 260 |

|------------|---------------------------------------------------|-----|

| 17.5.      | Transformation Facilities                         | 261 |

| 17.6.      | Statistical Aids                                  | 263 |

| 17.7.      | The BYTE-BY-BYTE Instruction                      | 263 |

| 17.8.      | Monitoring for Special Conditions                 | 264 |

| 17.9.      | Instruction Set                                   | 265 |

| 17.10.     | Collating Operations                              | 266 |

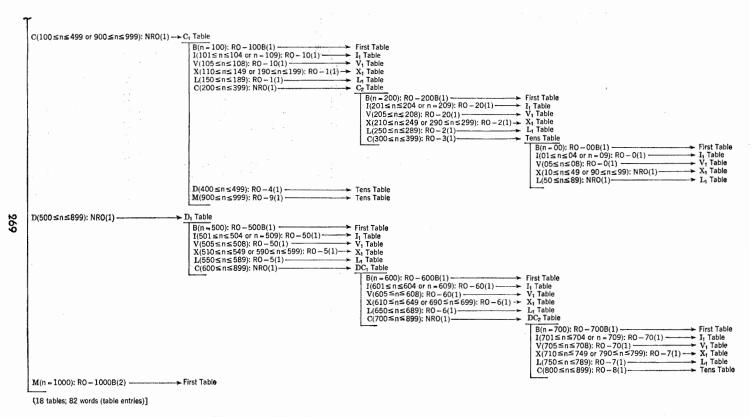

| 17.11.     | Table Look-up Operations                          | 267 |

| 17.12.     | Example                                           | 267 |

| Appendix A | N. Summary Data                                   | 273 |

| A.1.       | List of the Larger IBM Stored-program Computers . | 273 |

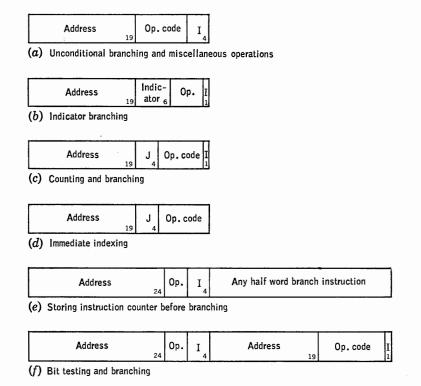

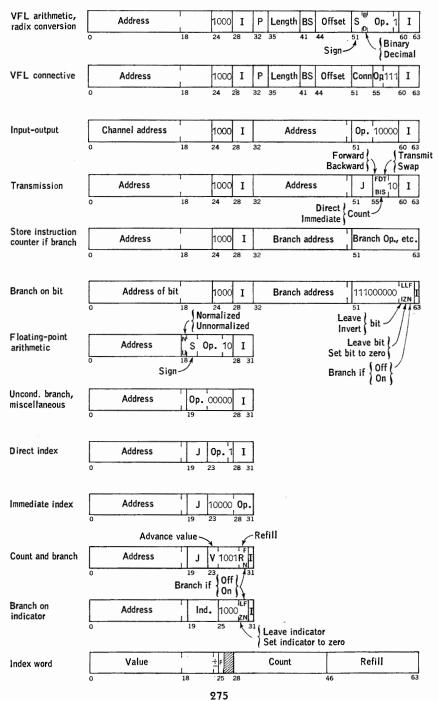

| A.2.       | Instruction Formats                               | 275 |

| A.3.       | List of Registers and Special Addresses           | 276 |

| A.4.       | Summary of Operations and Modifiers               | 277 |

| A.5.       | Summary of Indicators                             | 287 |

| Appendix B | . Programming Examples                            | 292 |

|            | Notation                                          | 292 |

| B.1.       | Polynomial Evaluation                             | 295 |

| B.2.       | Cube-root Extraction .                            | 296 |

| B.3.       | Matrix Multiplication                             | 298 |

| B.4.       | Conversion of Decimal Numbers to a Floating-point |     |

| _          | Normalized Vector                                 | 299 |

| B.5.       | Editing a Typed Message                           | 301 |

| B.6.       | Transposition of a Large Bit Matrix               | 303 |

| Index      |                                                   | 305 |

# PLANNING A COMPUTER SYSTEM

## PROJECT STRETCH

## Chapter 1 PROJECT STRETCH

#### by W. Buchholz

The computer that is discussed in this book was developed by the International Business Machines Corporation at Poughkeepsie, N.Y., under Project Stretch. The project started toward the end of 1954. By then IBM was producing several stored-program digital computers: the IBM 650, a medium-sized computer; the IBM 704, a large-scale computer primarily for scientific applications; and the IBM 705, a largescale computer primarily for business data processing. The 704 and 705 had already superseded the 701 and 702, which were IBM's first commercial entries into the large-computer field. Since the entire field was still new, there had been little experience on which to base the design of these machines, but by 1954 such experience was building up rapidly. This experience showed that the early computers were basically sound and eminently usable, but it was also obvious that many of the early decisions would have been made quite differently in 1954 and that many improvements had become possible.

At the same time, solid-state components were rapidly being developed to the point where it appeared practical to produce computers entirely out of transistors and diodes, together with magnetic core memories. A computer made only of solid-state components promised to surpass its vacuum-tube predecessors with higher reliability, lower power consumption, smaller size, lower cost made possible by automatic assembly, and eventually greater speed. The imminence of new technology, together with the knowledge of shortcomings in existing designs, gave impetus to a new computer project.

In 1955 the project was directed more specifically toward achieving, on very large mathematical computing problems, the highest performance possible within certain limits of time and resources. If mostly on-the-shelf components were used, a factor-of-10 improvement over the IBM 704, the fastest computer then in production, appeared feasible. Although this level of improvement would have been a respectable achievement, it was rejected as not being a large enough step. Instead, an over-all performance of 100 times that of the 704 was set as the target.

The purpose of setting so ambitious a goal was to stimulate innovation in all aspects of computer design. The technology available in 1955 was clearly not adequate for the task. New transistors, new cores, new logical features, and new manufacturing techniques were needed, which, although they did not yet exist, were known to be at least physically possible. Even though the goal might not be reached in all respects, the resultant machine would set a new standard of performance and make available the best technology that could be achieved by straining the technical resources of the laboratory. Hence the name *Project Stretch*.

The need for a computer of the power envisioned was clear. A number of organizations in the country had many important computing problems for which the fastest existing computers were completely inadequate, and some had other problems for which even the projected computer of 100 times the speed of the existing ones would not be enough. Negotiations with such organizations resulted in a contract with the U.S. Atomic Energy Commission in late 1956 to build a Stretch system for the Los Alamos Scientific Laboratory.

The early design objectives were described in 1956<sup>1</sup> in terms of certain technological and organizational goals:

#### Performance

An over-all performance level of 100 times that of the fastest machines then in existence was the general objective. (It has since become evident that speed comparisons of widely different machines are very difficult to make, so that it is hard to ascertain how well this target has been achieved. Using the IBM 704 as the reference point, and assuming problems that can easily be fitted to the shorter word size, the smaller memory, and the more limited repertoire of the 704, the speed ratio for the computer actually built falls below the target of 100. On the other hand, for large problems which strain the facilities of the 704 in one or more ways, the ratio may exceed 100.)

#### Reliability

Solid-state components promised the much higher reliability needed for satisfactory operation of a necessarily complex machine.

#### Checking

Extensive automatic checking facilities were intended to detect any errors that occurred and to locate faults within narrow limits. Storage devices were also to be equipped with error-correction facilities to ensure

<sup>1</sup>S. W. Dunwell, Design Objectives for the IBM Stretch Computer, Proc. Eastern Joint Computer Conf., December, 1956, pp. 20-22.

#### Снар. 1]

that data could be recovered in spite of an occasional error. The purpose was again to increase performance by reducing the rerun time often needed in unchecked computers.

#### Generality

To broaden the area of application of the system and to increase the effectiveness of the system on secondary but time-consuming portions of any single job, it was felt desirable to include in one system the best features of scientific, data-processing, and real-time control computers. Furthermore, the input-output controls were to be sufficiently general to permit considerable future expansion and attachment of new input-output devices.

#### High-speed Arithmetic

A high-speed parallel arithmetic unit was to execute floating-point additions in 0.8 microsecond and multiplications in 1.4 microseconds. (The actual speeds are not as high, see Chap. 14.) This unit would not be responsible for instruction preparation, indexing, and operand fetching, which were to be carried out by other sections of the system whose operation would overlap the arithmetic.

#### Editing

A separate serial computer unit with independent instruction sequencing was visualized to edit input and output data of variable length in a highly flexible manner. (It was later found desirable to combine the serial and parallel units to a greater degree, so that they are no longer independent, but the functional capability of both units was retained.)

#### Memory

The main memory was to have a cycle time of only 2 microseconds. (All but the early production memories will indeed be capable of working at 2.0  $\mu$ sec, but computer timing dictates a slightly longer cycle of 2.1  $\mu$ sec.) The capacity was to be 8,192 (later raised to 16,384) words per unit.<sup>1</sup>

#### Input-Output Exchange

A unit resembling somewhat a telephone exchange was to provide simultaneous operation of all kinds of input-output, storage, and datatransmission devices.

<sup>1</sup> A second set of faster, though smaller, memory units was also postulated, but it was later omitted because the larger units were found to give about the same over-all performance with a greater capacity per unit cost. These units are still used, however, to satisfy more specialized requirements of the 7951 Processing Unit described in Chap. 17.

#### 4 PROJECT STRETCH

#### High-speed Magnetic Disks

Magnetic disk units were to be used for external storage to supplement the internal memory. The target was a capacity of 1 (later raised to 2) million words with a transfer rate of 250,000 (later lowered to 125,000) words per second. These disk units permit a very high data flow rate (even at the lower figure) on problems for which data cannot be contained in memory.

As the understanding of the task deepened, this tentative plan was modified in many ways. The functional characteristics of the actual computer were developed in the years 1956 to 1958. This planning phase, which is likened in Chap. 2 to the work of an architect planning a building, culminated in a detailed programmer's manual late in 1958. During the same period the basic technology was also established. A number of changes were subsequently made as design and construction progressed, but the basic plan remained as in 1958.

The Stretch computer is now called the IBM 7030. It was delivered to Los Alamos in April, 1961. Several other 7030 systems were under construction in 1961 for delivery to other organizations with a need for very large computers. We shall leave it to others to judge, on the basis of subsequent operating experience, how close the computer comes to satisfying the original objectives of Project Stretch.

# Chapter 2 ARCHITECTURAL PHILOSOPHY

by F. P. Brooks, Jr.

Computer architecture, like other architecture, is the art of determining the needs of the user of a structure and then designing to meet those needs as effectively as possible within economic and technological constraints. Architecture must include engineering considerations, so that the design will be economical and feasible; but the emphasis in architecture is upon the needs of the user, whereas in engineering the emphasis is upon the needs of the fabricator. This chapter describes the principles that guided the architectural phase of Project Stretch and the rationale of some of the features of the IBM 7030 computer which emerged.

#### 2.1. The Two Objectives of Project Stretch

#### High Performance

The objective of obtaining a major increase in over-all performance over previous computers had a triple motivation.

1. There were some real-time tasks with deadlines so short that they demanded very high performance.

2. There were a number of very important problems too large to be tackled on existing computers. In principle, any general-purpose computer can do any programmable problem, given enough time. In practice, however, a problem can require so much time for solution that the program may never be "debugged" because of machine malfunctions and limited human patience. Moreover, problem parameters may change, or a problem may cease to be of interest while it is running.

3. Cost considerations formed another motivation for high performance. It has been observed that, for any given technology, performance generally increases faster than cost. A very important corollary is that, for a fully utilized computer, the cost per unit of computation declines with increasing performance. It appeared that the Stretch computer would show accordingly an improved performance-to-cost ratio over

#### 6 Architectural Philosophy

earlier computers. It appeared, further, that some computer users did indeed have sufficient work to occupy fully an instrument of the proposed power and could, therefore, obtain economic advantage by using a Stretch computer.<sup>1</sup>

#### Generality

In addition to being fast, the Stretch computer was to be truly a general-purpose computer, readily applicable to scientific computing, business data processing, and various large information-processing tasks encountered by the military. In 1955 and 1956, when the general objectives of Project Stretch were set, it was apparent that there existed a few applications for a very-high-performance computer in each of these areas. There is no question that the new computer could have been made at least twice as fast, with perhaps no more hardware, if it had been specialized for performing a very few specific computing algorithms. This possibility was rejected in favor of a general-purpose computer for four reasons, each of which would have sufficed:

1. No prospective user had all his work confined to so few programs, nor could any user be sure that his needs would not change significantly during the life of the machine.

2. If a computer were designed to perform well on the entire class of problems encountered by any one user, the shift in balance required to make it readily applicable to other users would be quite small.

3. Since there existed only a few applications in each specialized area and since the development costs of a computer of very high performance are several times the fabrication costs, each user would in fact be acquiring a general-purpose computer (containing some hardware he did not especially need) more cheaply than he could have acquired a machine more precisely specialized for his needs.

4. Since there are real limitations on the skilled manpower and other facilities available for development efforts, it would not have been possible to develop several substantially different machines of this performance class at once, whereas it was possible to meet a variety of needs for very-high-performance computers with a single machine.

In sum, then, Project Stretch was to result in a very-high-performance, general-purpose information-processing system.

#### 2.2. Resources

A sharp increase in computer performance does not spring solely from a strong justification for it; new technology is indispensable. It appeared that expected technological advances would permit the design to be based

<sup>1</sup> W. C. Sangren, Role of Digital Computers in Nuclear Design, *Nucleonics*, vol. 15, no. 5, pp. 56-60, May, 1957.

#### Guiding Principles 7

#### SEC. 2.3]

upon new core memories with a 2-microsecond cycle time, new transistor circuits with delays of 10 to 20 nanoseconds (billionths of a second) per stage, and corresponding new packaging techniques. The new transistor technology offered not only high speeds but a new standard of reliability, which made it not unreasonable to contemplate a machine with hundreds of thousands of components.

In order to complete the computer within the desired time span, it was decided to accept the risks that would be involved in (1) developing the technology and (2) designing the machine simultaneously.

The new circuits would be only ten to twenty times as fast as those of the 704, and the new memories would be only six times as fast. Obviously, a new system organization was required if there was to be a major increase in performance. It was clear that the slow memory speed would be the principal concern in system design and the principal limitation on performance. This fact influenced many decisions, among them the selection of a long memory word, and prompted the devotion of considerable effort to maximizing the use of each instruction bit.

Project Stretch benefited greatly from practical experience gained with the first generation of large-scale electronic computers, such as the IBM 700 series. Decisions made in the design of these earlier computers had necessarily been made without experience in the use of such machines. At the beginning of Project Stretch the design features of earlier machines were reviewed in the light of subsequent experience. It should not be surprising that a number of features were found inadequate: some considerations had increased in significance, others had diminished. Thus it was decided not to constrain Stretch to be program-compatible with earlier computers or to follow any existing plan. A completely fresh start meant extra architectural effort, but this freedom permitted many improvements in system organization.

A wealth of intensive experience in the application of existing computers was made available by the initial customers for Stretch computers. From these groups came ideas, insight, counsel, and often, because the groups had quite diverse applications, conflicting pressures. The diversity of these pressures was itself no small boon, for it helped ensure adherence to the objective of general applicability.

#### 2.3. Guiding Principles

The universal adoption of several guiding principles helped ensure the conceptual integrity of a plan whose many detailed decisions were made by many contributors.

#### **Over-all Optimization**

The objective of economic efficiency was understood to imply minimizing the cost of answers, not just the cost of hardware. This meant repeated consideration of the costs associated with programming, compilation, debugging, and maintenance, as well as the obvious cost of machine time for production computation. A consequent objective was to make programming easier—not necessarily for trivial problems, but for problems worthy of the computer, problems whose coding in machine language would usually be generated automatically by a *compiler* from statements in the user's language.

A corollary of this principle was the recognition that complex tasks always entail a price in information (and therefore money) and that this price is minimized by selecting the proper form of payment-sometimes extra hardware, sometimes extra instruction executions, and sometimes harder thought in developing programming systems. For example, the price of processing data with naturally diverse lengths and structures is easily recognized (see Chap. 4). This price appeared to be paid most economically in hardware; so very flexible hardware for this purpose was provided. Similarly, protection of memory locations from unwanted alteration was accomplished much more economically with equipment than it would have been with programming. A final minor example is the STORE VALUE IN ADDRESS<sup>1</sup> operation, which inserts index values into addresses of different lengths; by using address-length-determining hardware already provided for other reasons, this instruction performs a task that would be rather painful to program. For other tasks, such as program relocation, exception-condition fix-up, and supervisory control of input-output, hardware was considered, but programming techniques were selected as more economical.

#### Power instead of Simplicity

The user was given power rather than simplicity whenever an equalcost choice had to be made. It was recognized in the first place that the new computer would have many highly sophisticated and experienced users. It would have been presumptuous as well as unwise for the computer designers to "protect" such users from equipment complexities that might be useful for solving complex problems. In the second place, the choice is asymmetric. Powerful features can be ignored by a user who wishes to confine himself to simple techniques. But if powerful features were not provided, the skillful and motivated user could not wring their power from the computer.

For these reasons, the user is given programmed access to the hardware

<sup>1</sup> Names of actual 7030 operations are printed in SMALL CAPS in this book. When a name is used to denote a class of operations of which this operation is a member, it is printed in *italics*; also italicized are operations that exist in some computers but not in this one. For example, operations of the *add* type built into the 7030 include ADD, ADD TO MEMORY, ADD TO MAGNITUDE, etc., but not *add absolute*, which is provided in a different manner by modifier bits. wherever possible. He is given, for example, an interruption and addressprotection system whose use can be simple or very complex. He is given an indexing system that can be used simply or in some rather complex ways. If he chooses and if his problems are simple, he can write programs using floating-point arithmetic without regard for precision, overflow, or underflow; but if he needs to concern himself with these often complex matters, he is given full facilities for doing so.

#### **Generalized Features**

Wherever specific programming problems were considered worthy of hardware, *ad hoc* solutions were avoided and general solutions sought. This principle came from a strong faith that important variants of the same problem would surely arise and that generality and flexibility would amply repay any extra cost. There was also certainty that the architects could hardly imagine, much less predict, the many unexpected uses for general operations and facilities. This principle, for example, explains the absence of special operations to edit output: the problem is solved by the general and powerful logical-connective operations. Similarly, a single uniform interruption technique is used for input-output communication, malfunction warning, program-fault indication, and routine detection of expected but rare exceptional conditions.

#### Specialized Equipment for Frequent Tasks

There is also an antithetical principle. For tasks of great frequency in important applications, specialized equipment and operations *are* provided in addition to general techniques. This, of course, accounts for the provision of floating-point arithmetic and automatic index modification of addresses.

To maximize instruction density, however, specialized operations of less than the highest frequency are specified by extra instructions for such operations rather than by extra bits in all instructions. In short, the information price of specifying a less usual operation is paid when it is used rather than all the time. For example, indirect addressing, multiple indexing, and instruction-counter storing on branching each require half-word instructions when they are used, but no bits in the basic instructions are used for such purposes. As a result of such detailed optimization, the 7030 executes a typical scientific program with about 20 per cent fewer instructions of 32 bits than does the 704 with 36-bit instructions on a corresponding program.

#### Systematic Instruction Set

Because the machine would be memory-limited, it was important to provide a very rich instruction set so that the memory accesses for an instruction and its operand would accomplish as much as possible. As it has developed, the instruction set contains several thousand distinguishable operations. Such a wealth of function could be made conceptually manageable only by strong systematization. For example, there is only one conditional *branch* instruction for testing the machine indicators, but this is accompanied by a 6-bit code to select any one of the 64 machine indicators, a bit to specify testing for either the *on* or the *off* condition, and another bit to permit resetting of the indicator. Thus there are only a few basic operations and a few modifiers. In all, the number of operations and modifiers is less than half the number of operations in the IBM 709 (or 7090), although the number of different instruction actions is over five times that of the 709.

Such systematization, of course, implies symmetry in the operation code set—each modifier can be validly used with all the operations for which it can be indicated in the instruction, and, for most operations, the logical converses or counterparts are also provided. Thus the floatingpoint-arithmetic set includes not only the customary DIVIDE where the addressed operand constitutes the divisor, but also a RECIPROCAL DIVIDE which addresses the dividend.

#### Provision for New Operating Techniques

Experience with the IBM 650 and 704 computers had demonstrated that two computers whose speeds differ by more than one order of magnitude are different in kind as well as in degree. This confirmed the suspicion that the 7030 would be more than a super-704 and would be operated in a different way. An early effort was made, therefore, to anticipate some of the operating techniques appropriate for such an instrument, so that suitable hardware could be provided.

The most significant conclusion from these investigations was that an important operating technique would be *multiprogramming*, or timesharing of the central computer among several independent problem programs. This now familiar (but yet unexploited) concept was new in 1956 and viewed widely with suspicion.

A second conclusion was that the proposed high-capacity, high-datarate disk storage would contribute substantially to system performance and would permit the 7030 to be operated as a scientific computer without very-high-speed magnetic tapes.

#### 2.4. Contemporary Trends in Computer Architecture

Over the years computer designs have gone through a constant and gradual evolution shaped largely by experience gained in many active computing centers. This experience has heavily influenced the architecture of Stretch. In several instances the attack on a problem exposed

#### SEC. 2.4] CONTEMPORARY TRENDS IN COMPUTER ARCHITECTURE 11

by experience with existing computers differs in Stretch from the solution presently adopted in most computer installations. For example, with existing large computers the only way to meet the high cost of human intervention is to minimize such intervention; in the Stretch design the attempt has been, instead, to make human intervention much cheaper.

The effect of several of these contemporary design trends on the Stretch architecture will be examined here.

#### Concurrency

Most new computer designs achieve higher performance by operating various parts of the computer system concurrently. Concurrent operation of input-output and the central computer has been available for some years, but some contemporary designs go considerably beyond this and allow various elements of the central computer to operate concurrently.<sup>1</sup>

A distinction may be made (see Chap. 13) between local concurrency, providing overlapped execution of instructions that are immediate neighbors in the instruction stream of a single program, and nonlocal concurrency, where the overlap is between nonadjacent instructions that may belong to different programs. The usual input-output concurrency is of the nonlocal type; since the instructions undergoing simultaneous execution are not closely related to one another, the need for interlocks and safeguards is not severe and may, to a large extent, be accomplished by supervisory programming.

Local concurrency is used extensively in the central processing unit of the 7030 to achieve a high rate of instruction flow within a single instruction sequence. Unlike another scheme,<sup>2</sup> in which each specialized unit performs its task and returns its result to memory to await call by the next unit, the 7030 uses registers; this is because memory speed is the main limitation on 7030 computer speed. Several of these registers form a high-speed virtual memory (the look-ahead unit of Chap. 15), which receives instructions and operands from the real memory in advance of execution by the arithmetic unit and receives the results for storing while the arithmetic unit proceeds with the next operation. Up to eleven successive instructions may be in the registers of the central processing unit at various stages of execution: undergoing address modification, awaiting access to operands in memory, waiting for and being executed by the arithmetic units, or waiting for a result to be returned to memory.

Considerable effort was expended on automatic interlocks and safeguards, so that the programmer would not have to concern himself with

<sup>1</sup> P. Dreyfus, Programming Design Features of the GAMMA 60 Computer, Proc. Eastern Joint Computer Conf., December, 1958, pp. 174-181. <sup>2</sup> Ibid.

#### 12 Architectural Philosophy

the intricate logic of local concurrency. The programmer writes his program as if it were to be executed sequentially, one instruction at a time.

To make a computer with automatic program-interruption facilities behave this way was not an easy matter, because the number of instructions in various stages of processing when an interrupting signal occurs may be large. The signal may have been the result of one of these instructions, requiring interruption before the next instruction is executed. Since the next several instructions may already be under way, it must be possible to go back and cancel their effects. The amount of overlap varies dynamically and may even be different for two executions of the identical instruction sequence; so it would be almost impossible for the programmer to do the backtracking. Therefore, the elaborate safeguards provided to ensure sequential results from nonsequential operation do more than satisfy a desire to simplify programming; the programmer would be lost without them.

#### *Multiprogramming*

Time-sharing (as of a computer by multiprogramming) and concurrency are two sides of one coin: to overcome imbalance in a computer system, faster elements are time-shared and slower elements are made to operate concurrently. In the 7030, for example, the single central computer uses several concurrently operating memory boxes, and the single computer-memory system may control in turn many concurrently operating input-output devices.

Even though per-operation cost tends to decrease as system performance increases, per-second cost increases, and it therefore becomes more important to avoid delaying the calculator for input-output. To take full advantage of concurrent input-output operation for a computer of very high performance demands that input data for one program be entered while a preceding program is in control of calculation and that output take place after calculation is complete. For this reason alone, it was apparent from the beginning that multiprogramming facilities would be needed for Project Stretch.

A second motivation for multiprogramming is the need for a closer manmachine relationship. As computers have become faster, the increasing cost of wasted seconds has dictated increasing separation between the problem sponsor and the solution process. This has reduced the over-all efficiency of the problem-solving process; for, in fact, the more complex problems solved on faster calculators are harder, not easier, for the sponsor to comprehend and therefore need more, not less, dynamic interaction between solution process and sponsor. There can be no doubt that much computer time and more printer time has been wasted because the problem sponsor cannot observe and react as his program is being run on large computers like the IBM 704. This difficulty promised to become more acute with the even more complex problems for which Stretch was needed.

With multiprogramming it becomes economically practical for a person seated at a console to observe his program during execution and interrupt it while considering the next step. Since the computer can immediately be switched to another waiting program, the user is not charged with the cost of an idle computer. Thus the extension of multiprogramming to manual operation offers, once the technique has been mastered, a tremendous economic breakthrough: it provides a general technique for solving the problem of loss of contact between sponsor and solution. A sponsor can now interact with his problem at his own speed, paving only the cost of delaying the problem, not that of delaying the machine. This should materially accelerate that large proportion of scientific computation which is expended on continual and perpetual refinement and debugging of mathematical models and the programs that embody them. The solution of most such problems is characterized more closely by a fixed number of interactions between computer and sponsor than by a fixed amount of computer time.

Multiprogramming also makes it economically practical to enter new data and to print or display results *on line*, that is, via directly connected input and output devices; whereas the economics of previous computers forced card-to-tape and tape-to-printer conversion *off line*, that is, with physically separate devices, so that only the fastest possible medium, magnetic tape, would be used on the computer. On-line operation of input and output is emphasized in the Stretch philosophy, because it removes much of the routine operator intervention and reduces the overall elapsed time for each run of a problem.

Multiprogramming makes several demands upon system organization. Most obvious is the requirement of ample and fast storage, both internal and external. Of equal importance is an adequate and flexible interruption system. Also, in the real world, time-sharing of a computer among users with ordinary human failings requires memory protection, so that each user can feel secure within his assigned share of the machine. Debugging is difficult enough at best, and most users would sacrifice efficiency rather than tolerate difficulties caused by the errors in other programs. It proved possible in the 7030 to provide a rudimentary but sufficient form of memory protection without affecting speed and with a modest amount of hardware.

The equipment for multiprogramming was, however, limited to two essential features: program interruption and address monitoring, and these were designed to be as flexible as possible. Other multiprogramming functions are left to the supervisory program, partly because that arrangement appeared to be efficient, but primarily because no one could be sure

13

#### 14 Architectural Philosophy

which further facilities would prove useful and which would prove merely expensive and overly rigid inconveniences. Several years of actual multiprogramming experience will undoubtedly demonstrate the value of other built-in features.

If multiprogramming is to be an operating technique, a radically different design is needed for the operator's console. If several independent programs are to be run, each with active operator intervention, there must be provision for multiple independent consoles. Each console must be incapable of altering any program other than the associated problem program. For active intervention by the problem sponsor (rather than by a special machine operator), the console must be especially convenient to use. Finally, if a supervisory program is to exercise complete control in scheduling programs automatically, it must be able to ignore unused console facilities. Although intelligent human intervention is prized highly, routine human intervention is to be minimized, so as to reduce delays and opportunities for error.

The operating console was designed to be simply another input-output device with a convenient assortment of switches, keys, lights, digital displays, and a typewriter. A console interpretive program assigns meaning to the bits generated by each switch and displayed by each light. There are no maintenance facilities on the operator's console, and completely separate maintenance consoles are provided.

#### Automatic Programming

Undoubtedly the most important change in computer application technique in the past several years has been the appearance of symbolic assemblers and problem-language compilers. Studies showed that for Stretch at least half of all computer time would be used by compilerproduced programs; all programs would be at least initially translated by an assembler.

A most important implication of symbolic-language programming is that the addressing radix and structure need not be determined for coder convenience. Fairly complex instruction formats can be used without causing coding errors, and operation sets with hundreds of diverse operations can be used effectively.

Many proposals for amending system architecture to simplify compilers were considered. The most far-reaching of these concerned the number of index registers, which should be infinity or unity for greatest ease of assignment during compilation. The alternatives were investigated in considerable detail, and both turned out to reduce computer performance rather sharply. Indeed, reduced performance was implied by most such proposals. These studies resulted in a belief which is not shared by all who construct compilers; this is that total cost to the user is

#### Sec. 2.5]

minimized not by restricting system power to keep compilers simple but by enhancing facilities for the task of compilation itself, so that compilers can operate more rapidly and efficiently.

#### Information Processing

The arithmetic power of a computer is often only ancillary to its power of assembling, rearranging, testing, and otherwise manipulating information. To an increasing extent, bits in even a scientific computer represent things other than numerical quantities: elements of a program metalanguage, alphabetic material, representations of graphs, bits scanned from a pattern, etc. In the light of this trend, it was therefore important to match powerful arithmetical with powerful manipulative facilities. These are provided in the variable-field-length arithmetic and, in unique form, in the variable-field-length connective operations, which operate upon bits as entities rather than components of numbers. Good variable-field-length facilities are, of course, particularly important for business and military data processing.

#### 2.5. Hindsight

As the actual shape of the 7030 began to emerge from the initial planning and design stages, it became apparent that some of the earlier thoughts had to be revised. (Some of these changes have already been noted parenthetically in Chap. 1.) The bus unit for linking and scheduling traffic between many memory boxes and many memory-using units turned out to be a key part of the design. The original algorithms for multiplication and division proved inadequate with available circuits, and new approaches were devised. It became clear that division, especially, could not be improved by the same factor as multiplication. Serial (variable-field-length) operation turned out to be considerably slower than expected; so serial multiplication and division operations were redesigned to use the faster parallel unit.

The two separate computer sections that were postulated originally were later combined (see Chap. 1), and both sets of facilities were placed under the control of one instruction counter. Although the concept of multiple computing units, closely coupled into one system, was not found practical for the 7030 system, this concept still seems promising.<sup>1</sup> In fact, the input-output exchange coupled to the main computer in the 7030 is a simplified example, since the exchange is really another computer, albeit a highly specialized one with an extremely limited instruction vocabulary.

<sup>1</sup> A. L. Leiner, W. A. Notz, J. L. Smith, and A. Weinberger, PILOT: A New Multiple Computer System, J. ACM, vol. 6, no. 3, pp. 313-335, July, 1959.

Some architectural features proved unworkable. Rather late in the design period, for example, it became clear that the method of handling zero quantities in floating-point arithmetic was ill-conceived; so this method was abandoned, and a better concept was devised.

Two excellent features, each of which contributes markedly to system performance, were found to have inherently conflicting requirements; their interaction prevents either feature from realizing its full potential. The program-interrupt system is intended to permit unpredicted changes in instruction sequencing. The instruction look-ahead unit, on the other hand, depends for its effectiveness on the predictability of instruction sequences; each interruption drains the look-ahead and takes time to recover. This destroyed the usefulness of the interrupt system for frequent one-instruction fix-ups and required the addition of built-in exception handling in such cases as floating-point underflow.

On the other hand, some improvements became possible as the design progressed. It turned out, for example, that the equipment for performing variable-field-length binary multiplication with the parallel arithmetic unit could easily be made to do binary-decimal and format conversions; so this facility was added.

There are in the 7030 architectural features whose usefulness is still unmeasured. A few are probably mistakes. Others seem to be innovations that will find redefinition and refinement in future computers, large and small. Still other features appear now to be wise for very-highperformance computers, but must be considerably scaled down for more modest machines. Experience has, however, reinforced the system architects' belief in the guiding principles of the design and in the general applicability of these principles to other computer-planning projects.

# Chapter 3 SYSTEM SUMMARY OF IBM 7030

by W. Buchholz

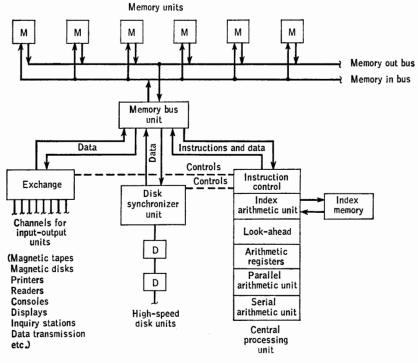

# 3.1. System Organization

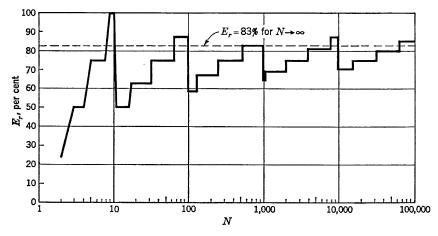

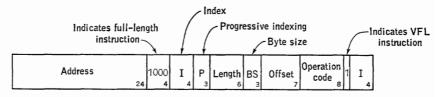

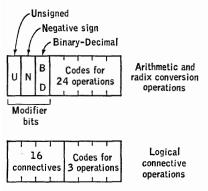

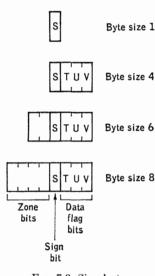

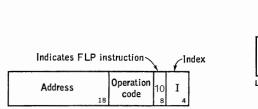

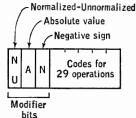

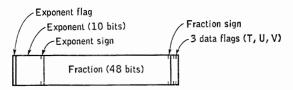

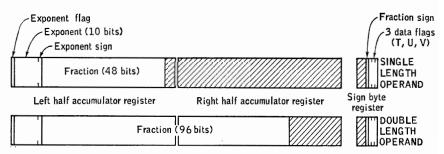

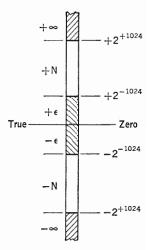

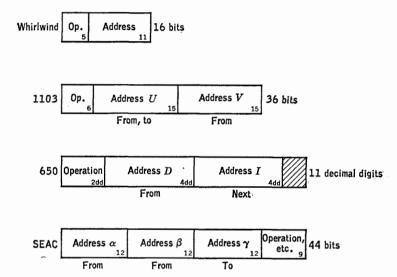

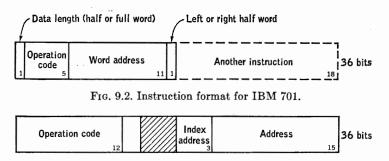

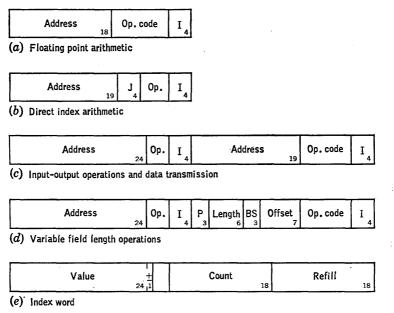

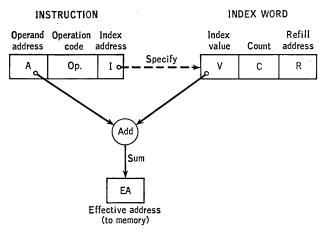

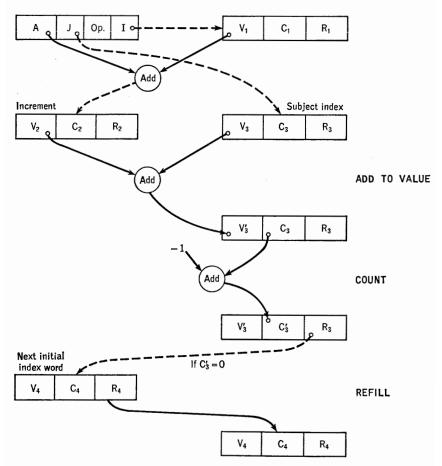

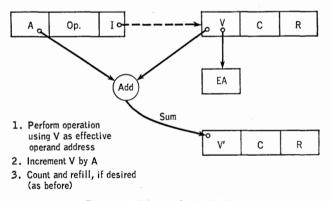

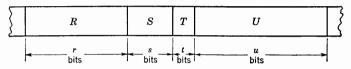

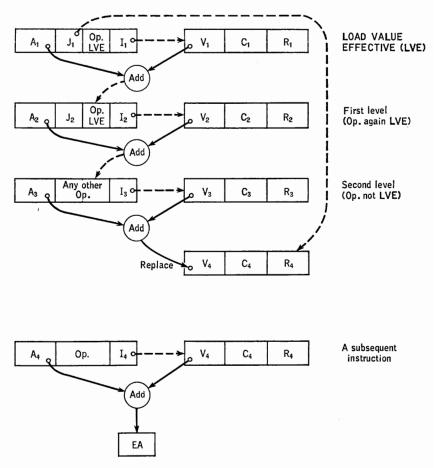

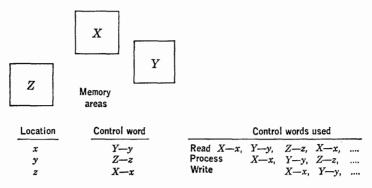

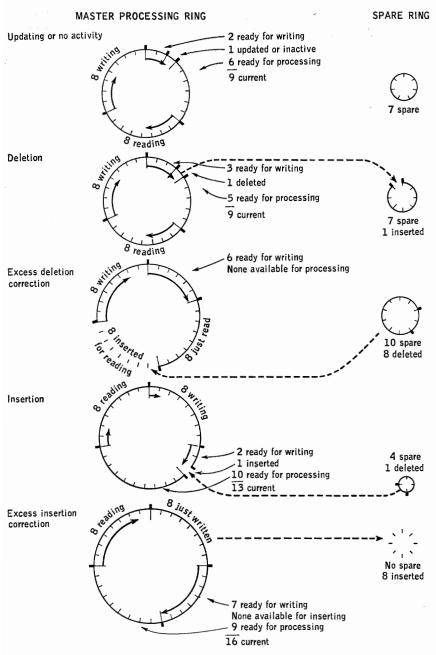

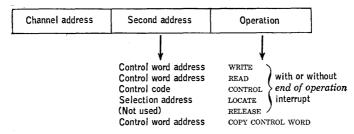

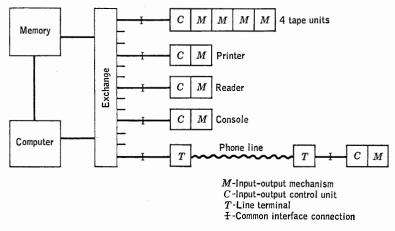

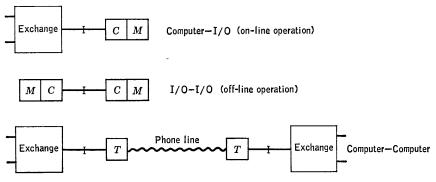

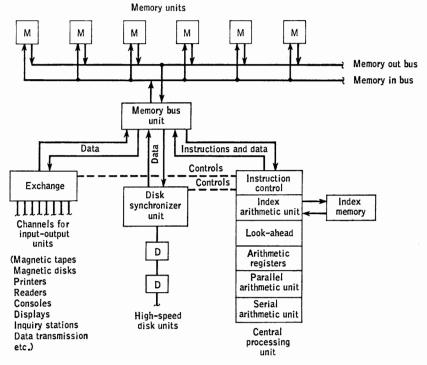

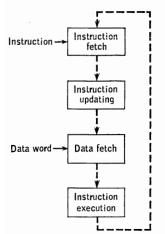

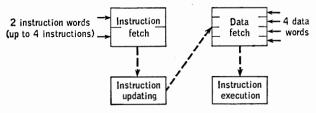

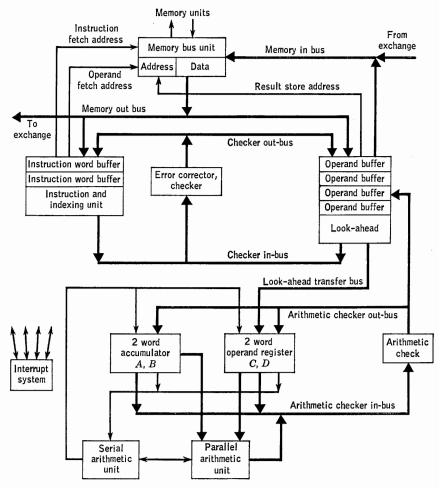

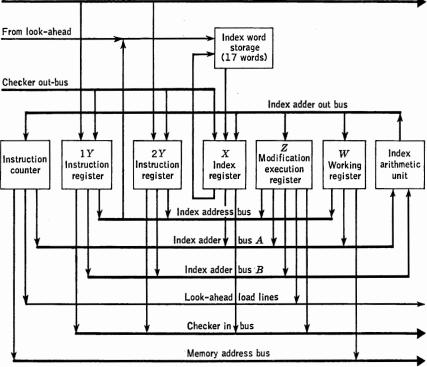

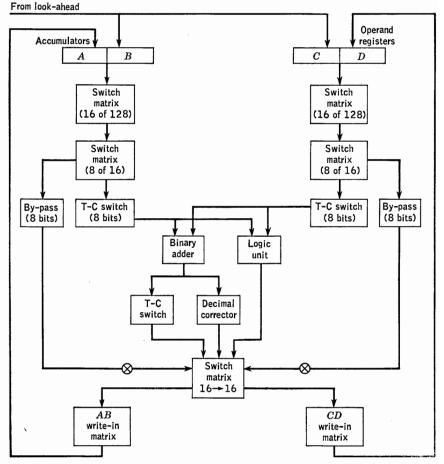

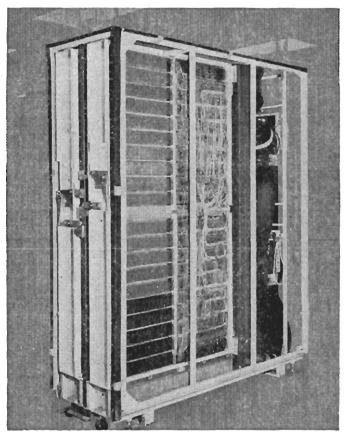

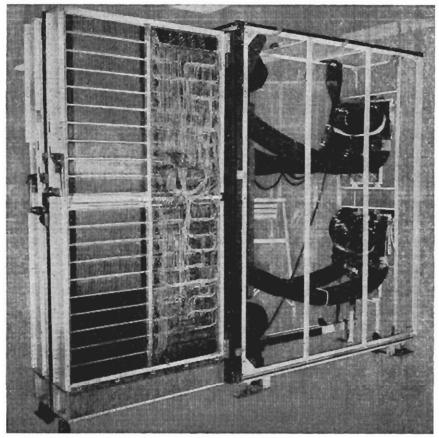

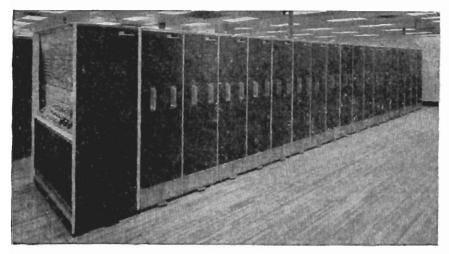

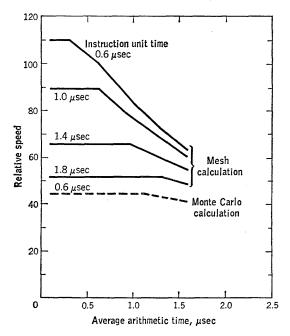

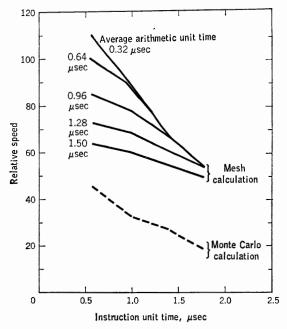

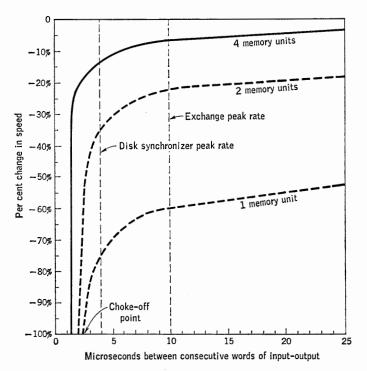

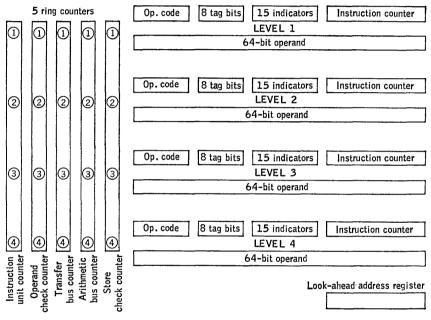

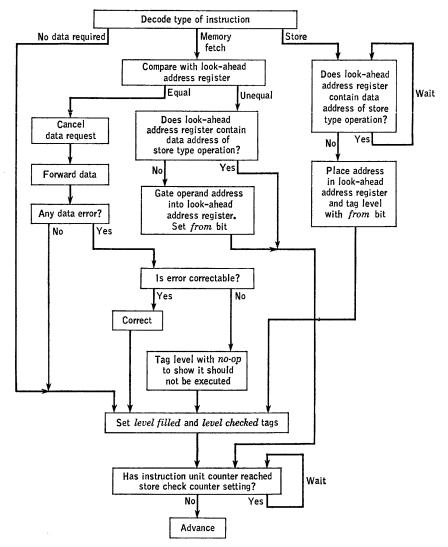

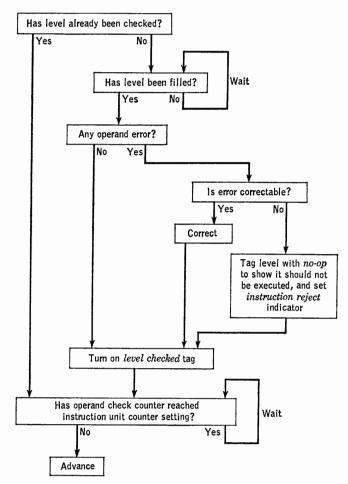

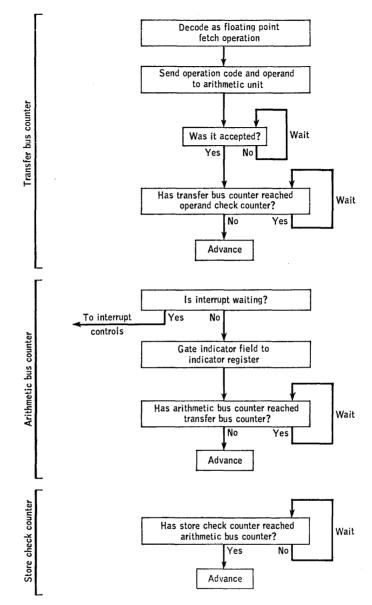

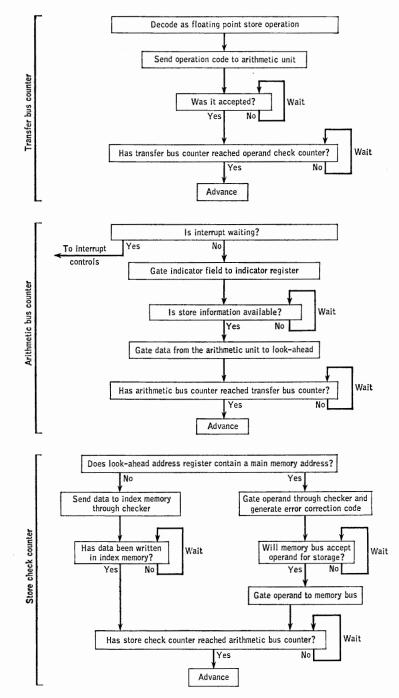

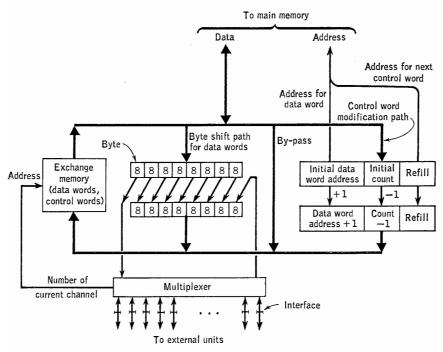

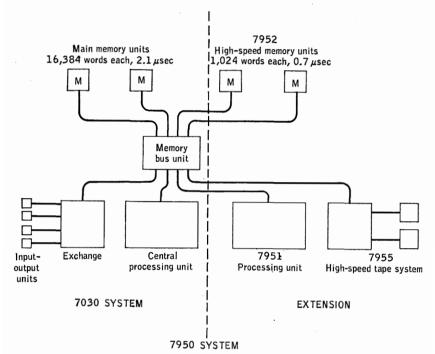

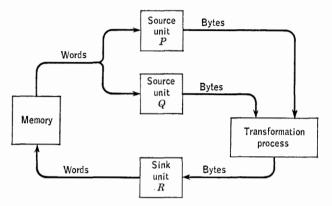

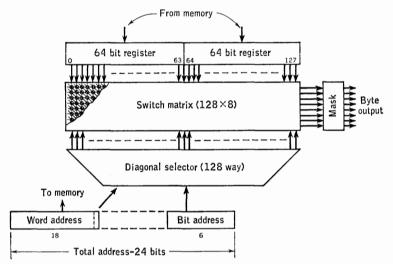

The IBM 7030 is composed of a central processing unit, one or more memory units, a memory bus unit, an input-output exchange, and inputoutput devices. Optionally, high-speed magnetic disk storage units and a disk control unit may be added for external storage. A typical system configuration is shown in Fig. 3.1.