NULTISTABLE CIRCUIT

Filed Sept.

# **United States Patent Office**

Patented Sept. 27, 1966

1

3,275,848

MULTISTABLE CIRCUIT

Chester Gordon Bell, Concord, Mass., assignor to Digital

Equipment Corporation, Maywerd, Mass.

Filed Sept. 19, 1963, Ser. No. 319,044

8 Cinims. (Cl. 367—88.5)

This invention relates to a novel electrical circuit having logic properties particularly suited for use in digital data processing systems. More specifically, it relates to a 10 multistable circuit in which an input pulse applied to one of three or more control terminals causes an output signal in the form of a voltage level to persist exclusively at that terminal. The subsequent arrival of an input pulse at another control terminal switches the circuit so that 15 the output signal is present only at the second control terminal.

It is an object of the invention to provide an improved multistable circuit having three or more stable states.

More particularly, it is an object of the invention to 20 provide a multistable circuit having a simple construction and saited for use in digital data processing systems.

Another object of the invention is to provide a multistable circuit of the above character having rapid response to an input signal.

Other objects of the invention will in part be obvious and will in part appear hereinafter.

The invention accountagly comprises the features of construction, cambination of elements, and arrangement of particular section, and the scope of the invention will be indicated at the claims.

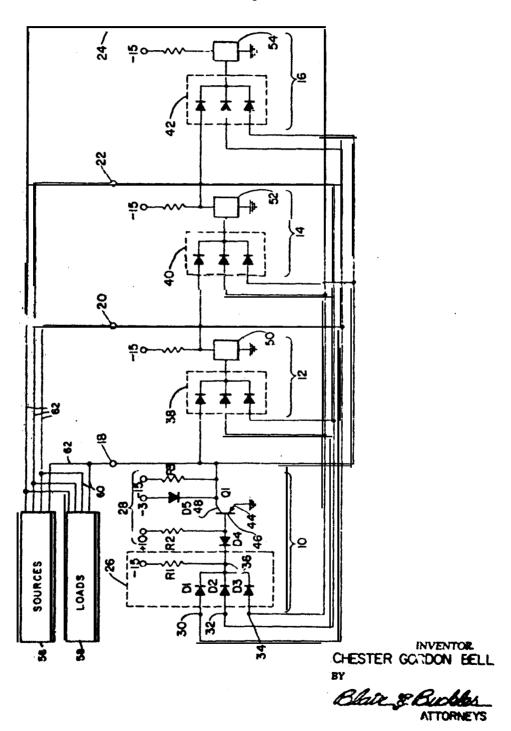

For a fuller understanding of the nature and objects of the invention, reference should be had to the following detailed description, takes in connection with the accompanying drawing, which is a schematic diagram partly in block form of a multistable circuit embodying the invention.

In general, the multistable circuit of the present invention comprises a logic unit for each stable state the circuit can assume. The logic units are internamented so that application of an input signal to a first logic unit causes the remaining units to assume a first state. This, in turn, causes the first unit to assume a second state, so that the output signal therefrom differs from that of the remaining units. The circuit remains in this condition until snother logic unit receives an input signal, which causes the second logic unit to assume the necond state and exclude the other units from this state.

The drawing shows a multistable circuit embodying the investion and having four stable states. The multistable circuit comprises four ider-ical logic units 10, 12, 14 and 16, associated with contrus terminals 18, 20, 22 and 24, respectively.

The first logic unit 10, typical of the other units, has a coincidence circuit 26 whose cutput is connected to a transister inverter 28. The output of the inverter 28 is applied to the courtof terminal 18, associated with the logic unit 10. For the four-stable circuit shown, the coincidence circuit 26 has three input terminals 30, 32, and 34 connected to the control terminals 20, 22 and 24 exociated with the other logic units.

As described in detail below, in the illustrated embodiment, the coincidence circuit 26 responds to the application of negative voltage levels to all its input terminals to defiver a negative voltage level to the inverter 28. This courses the in-crier to deliver a new volt level to the control terminal 18. Conversely, the logic unit 10 gelivers a negative level to its control terminal 20 when one or 70 more zero volt levels are applied to its coincidence circuit input terminals 26-34.

2

The control terminal of each logic unit is connected to one coincidence circuit input terminal in each of the other logic units. Accordingly, the control terminal 18 of the logic units 10 is connected to input terminals of the logic units 12, 14 and 16, and the control terminal 20 of the second logic unit 12 is connected to input terminals of the units 10, 14 and 16. Similarly, the control terminal 22 is connected to input terminals of units 10, 12 and 16 and the fourth logic unit control terminal 24 is connected to input terminals of the first, second and third units, 10, 12 and 14, respectively.

During operation, when a zero volt level, preferably in the form of a short pulse from sources 56, is applied to the control terminal 18, it is delivered to input terminals of the coincidence circuits 38, 40 and 42. Accordingly, the logic units 12, 14 and 16 develop negative levels at their control terminals 20, 22 and 24 and at the three coincidence input terminals 30, 32 and 34 of the logic unit 10.

In response to the coircidence of negative levels at all its input terminals, the caincidence circuit 26 enables the inverter 28 to apply a zero volt level to the control terminal 18. This ground level is applied to the other logic units, constanining them to have negative voltage levels at their control terminals 20, 22 and 24. Thus, the multistable circuit maintains a zero volt level at the control terminal 18 and negative levels at the remaining control terminals. These levels are suitably applied to loads 58 k:ving input leads 60, each of which is connected to a control terminal on a different stage 10-16.

Subsequent application of a zero wolt level to the fourth unit control terminal 24, for example, rapidly switches the circuit to maintain the zero level at that terminal and the negative level at the control terminals 18, 20 and 22.

the negative level at the control manimals \$2, 20 and 22.

Canadaning, the detailed canatamation of the illustrated coincidence circuit 26, the input terminals 30, 32 and 34 are connected respectively to the anode of diodes D1, D2 and D3, whose cathodes are connected at a junction 36 and a voltage source (not shown) providing a possetial of —15 volts. Also connected to the iunction 36 is the cathode of a diode D4, whose anode is connected to the base 46 of a manimum Q1. A resistor B2 is connected between the base 46 and a voltage source (not shown) having a potential of +10 volts.

Assume, in the illustrated example, that the voltage level at each input terminal 39-34 can be either —3 volts or zero. With zero voltage at any one of these terminals the diode receiving this voltage change the potential at the junction 36 essentially to zero (assuming selection of the resistors R1 and R2 to provide negative potential at the junction 36 in the absence of current through the diodes D1-D3). With a small voltage — op across the diode D4 resulting from current between the resistors R1 and R2, the base 46 is positive with respect to the ground emitter 44 and the transistor Q1 is cut off.

21 and R2, the base 46 is positive with respect to the ground emitter 44 and the transistor Q1 is cut off.

On the other head, when the negative voltage level is applied to all three of the terminals 30-32, the junction 36 is classped to the negative level. With the small drop across the diode D4, a substantial negative potential is applied to the bese 46, causing the transister to conduct.

The inverter 28 incluies, in addition to the transistor Q1, a diode D5 connected between the transister collector 45 and a voltage source (not shown) providing the —3 volt level. Also included in a resistor R3 connected between the collecter and the -15 volt source. When the transistor Q1 conducts, as a result of the application of the —3 volt level to all three terminals 30-34, the collecter 46 is grounded and the agree volt level therefore appears at the terminals 18. When any one of the terminals 30-34 is at the zero volt level, and the transistor Q1 is

accordingly cut off, the diode D5 clamps the terminal 18 to the -3 volt level.

Accordingly, it will be apparent that with the zero volt level at the terminal 18, the units 12, 14 and 16 have the -3 volt leve! at their terminals 20, 22 and 24. Thus all the inputs to the coincidence circuit 26 are at the -3 level to maintain the zero volt level at the terminal 18 as described above. A zero volt pulse at any of the terminals 20-24 will then result in the -3 volt level at the terminal 18. This, in turn, will bring about conditions 10 in the respective logic units providing the zero volt level at the pulsed control terminal and the -3 volt level at all the other control terminals.

In summary, I have described a novel multistable circuit that can be simply constructed at low cost with any 15 desired number of stable states. The circuit is operated by applying a signal, suitably a pulse, to a selected control terminal In response, the circuit maintains the selected terminal at a selected voltage different from the voltages at the off or control terminals.

The invention is clearly not limited to operation with the voltage levels specified above for the illustrated embodiment. For example, the negative and zero volt levels discussed above can both be positive or negative, depending on the choice of operating voltages.

It will thus be seen that the objects set forth above among those made apparent from the preceding uescription, are efficiently attained and, since certain changes may be made in the above construction without departing matica, it is intended that all 30 from the scope of the matter contained in the above description or shown in the accompanying drawing shall be interpreted as illustrative and not in a limiting sense.

are intended to cover all of the generic and specific features of the invention herein described, and all statem of the scope of the invention, which, as a matter of language, might be said to fall therebetween.

Having described the invention, what is claimed as new and secured by Letters Patent is:

1. An electronic circuit comprising

(A) at least three logic circuits, each of which

- (1) has a plurality of input term nais not exceeding the number of logic circuits and an output terminal.

- (2) develops a second-level output signal only when all said input terminals receive first-level

- (3) develops said first-level signal at its output terminal when any one or more of said input 50 terminals receives a second-level nignal,

- (4) has its output terminal connected to an input nal of each of the other logic circuits so that each input terminal of each logic circuit is nocted to an output terminal of another dif- 55 ferent logic circuit, an

(5) is arranged to develop a higher output imace at its output terminal when it develops said first-level signal than when it develops said

- second-level signal,

(B) whereby in response to application of an input signal of said second level to a first output terminal and, alternatively, application of an input signal of said first level to all output terminals except said first one, said circuit develops at said first output 65 terminal a persisting second-level signal and constrains the signals at the other output terminals to said first level.

- 2. An electronic circuit according to claim 1 wherein there are only (n-1) logic circuits, where (n) is an intoger greater then can, and wherein each logic circuit has only (n) input terminals and a single output terminal.

3. A circuit comprising, in combination,

(A) (n+1) coincidence circuits, each having only (n) 75

input terminals and an output terminal, where (n) is an integer greater than one,

- (1) said coincidence circuits being numbered in an ordered sequence.

- (B) (n+1) inverters, each having an input terminal and an output terminal,

- (1) said inverters being numbered in said ordered ecquence,

- (2) said input terminal of each inverter being conconnected to receive only the signal developed at the output terminal of the same-numbered coincidence circuit, and

- (3) said output terminal of each inverter being connected in circuit with an input terminal of each of the different-numbered coincidence cir-

- (C) each coincidence input terminal being connected within said circuit exclusively to inverter output terminak.

- 4. An electronic circuit according to claim 3 in which each inverter is arranged to present to said second-level signal a higher output impedance at the output terminal thereof when it develops said first-level signal than when it develops said second-level signal.

- 5. A multistable circuit comprising, in combination (A) (n+1) AND circuits numbered in an ordered sequence and each having a single output terminal and only (n) input terminals, where (n) is an integer greater than one,

(1) each AND circuit responding to the coincidence of first-level signals at all its input terminals to develop a third-level signal at its output terminal, and

- (2) developing a fourth-level signal at its output terminal when a recond-level signal is present at at least one of its input terminals, where said first-level and third-level signals may be the same and where said second-level and fourthlevel signals may be the same

- (B) (n+1) inverters numbered in said ordered sequence and each having a single input terminal and a single output terminal.

- (1) each inverter developing at its output terminal said second-level signal in response to application of said third-level signal to a input ter-

- (2) developing at its output terminal said first-level signal in response to application of said fourthlevel to its input terminal,

- (3) each inverter having its input terminal connected to the output terminal of the same-numbered AND circuit

- (C) (n+1) control terminals numbered in said ordered водисись,

- (1) each control terminal being connected to the output terminal of the same-numbered circuit and to an input terminal of each of the different-numbered AND circuits,

- (D) whereby application of a second-level input signal to one control terminal causes each different-a bered AND circuit to deliver a fourth-level signal to the inverter connected to it, thereby producing first-level signals at all the input terminals of the same-numbered AND circuit so that said secondlevel signal persists exclusively at said one control termine

A multistable circuit comprising

(A) (n+1) coincidence circuits sumbered in an ordered sequence and each having an output terminal and no more than (n) input terminals, where (n) is an integer greater than one,

(1) each coincidence circuit responding to the

coincidence of first-level signals at all its input terminals to develop a third-level signal at its output terminal, and

terminals,

(3) developing at its output terminal when one or to its input terminals, and (4) having its output terminal connected to an input terminal of each of the other logic circuit.

6

(B) source means having a plurality of output lines each of which is connected to a different one of said multistable circuit output terminals, and

(C) output means having a plurality of input lines each of which is connected to 8 different one of said multistable circuit output terminals,

(D) so that when said source means conditions one output line therefrom to have said second-level signal, said multistable circuit Jevelops at its output terminal connected to said conditioned line a persisting second-level signal and constrains the signals at the other output terminals thereof to said first level.

8. Apparatus according to claim 7 in which each logic circuit

(A) includes a grounded-emitter transistor inverter in which the transistor collector is the logic circuit output terminal, and

(B) produces said second-level signal when the transistor of the inverter therein is in a conducting state.

## References Clied by the Examiner

## UNITED STATES PATENTS

| 3,012,155 | 12/1961 | Jagger 307—88.5         |

|-----------|---------|-------------------------|

| 3,079,513 | 2/1963  | Yokelson 307—88.5       |

| 3,166,715 | 1/1965  | Cogar                   |

| 3,178,590 | 4/1965  | Heilweil et al 307-88.5 |

| 3,210,569 | 10/1965 | Reek 328-49             |

ARTHUR, GAUSS, Primary Examiner.

R. H. EPSTEIN, Assistent Exeminer.

Sept. 27, 1966

C. G. BELL

3,275,848

NULTISTABLE CIRCUIT

Filed Sept. 19. 1963

# **United States Patent Office**

Patented Sept. 27, 1966

1

3,275,848

MULTISTABLE CIRCUIT

Chester Gordon Bell, Concord, Mass, assignor to Digital

Equipment Corporation, Maynerd, Mass.

Filed Sept. 19, 1963, Ser. No. 318,844

8 Claims. (Cl. 367—88.5)

This invention relates to a novel electrical circuit having logic properties particularly suited for use in digital data processing systems. More specifically, it relates to a multistable circuit in which an input pulse applied to one of three or more control terminals causes an output signal in the form of a voltage level to persist exclusively at that terminal. The subsequent arrival of an input pnive at another control terminal switches the circuit so that 15 the output signal is present only at the second control terminal.

It is an object of the invention to provide an improved multistable circuit having three or more stable states.

More particularly, it is an object of the invention to 20 provide a multistable circuit having a simple construction and suited for use in digital data processing systems.

Another object of the invention is to provide " multistable circuit of the above character having rapid response to an input signal.

Other objects of the invention will in part be obvious and will in part appear hereinafter.

The invention accountary comprises the features of construction, combination of elements, and arrangement of particular will be exemplified in the construction hereisalter see........., and the scope of the invention will be indicated in the claims.

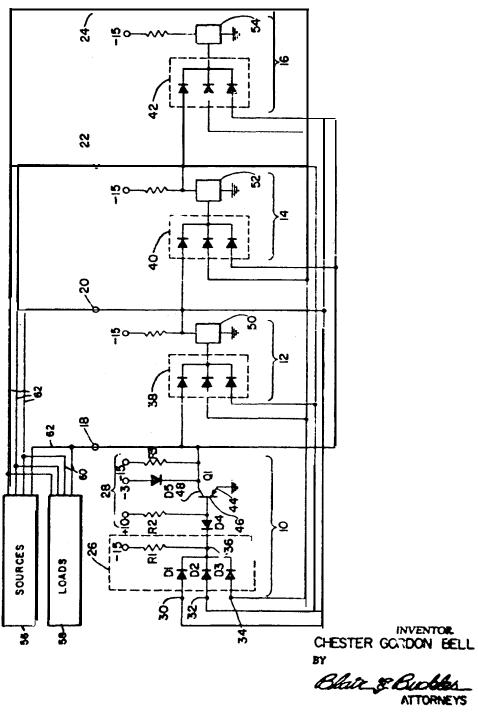

For a faller understanding of the nature and objects of the invention, reference should be had to the following detailed densities, takes in connection with the accompanying drawing, which is a schematic diagram partly in block form of a multistable circuit embodying the invention.

In general, the multistable circuit of the present invention comprises a logic unit for each stable state the circuit can assume. The logic units are interconnected so that application of an input signal to a first state. This, in turn, causes the first unit to assume a first state. This, in turn, causes the first unit to assume a second state, so that the output signal therefrom differs from that of the remaining units. The circuit remains in this condition until another logic unit receives an input signal, which causes the second logic unit to assume the second state and exclude the other units from this state.

The drawing shows a multistable carcuit embodying the immution and having four stable states. The multistable circuit comprises four iderrical logic units 10, 12, 14 and 16, associated with contrasterminals 18, 20, 22 and 24, sespectively.

The first logic unit 10, typical of the other units, has a commission circuit 26 whose output is connected to a transistor inverter 28. The output of the inverter 28 is applied to the control terminal 13, associated with the legic unit 10. For the four-stable circuit shown, the coincidence circuit 26 has there input terminals 30, 32, and 34 connected to the control terminals 20, 22 and 24 associated with the other logic units.

As described in detail below, in the illustrated embodiment, the coincidence circuit 26 responds to the application of negative voltage levels to all its input terminals to deliver a negative voltage level to the inverter 28. This causes the inverter to deliver a zero volt level to the control terminal 28. Conversely, the logic unit 36 estivers a negative level to its seated terminal 28 when one or yoursely levels are applied to its esineldcare circuit input terminal 29-36.

2

The control terminal of each logic unit is connected to one coincidence circuit input terminal in each of the other logic units. Accordingly, the control terminal 18 of the logic unit 10 is connected to input terminals of the logic units 12, 14 and 16, and the control terminal 20 of the second logic unit 12 is connected to input terminals of the units 10, 14 and 16. Similarly, the control terminal 22 is connected to input terminals of units 10, 12 and 16 and the fourth logic unit control terminal 24 is connected to input terminals of the first, second and third units, 16, 12 and 14, respectively.

During operation, when a zero volt level, preferably in the form of a short pulse from sources 56, is applied to the control terminal 18, it is delivered to input terminals of the coincidence circuits 38, 40 and 42. Accordingly, the logic units 12, 14 and 16 develop negative levels at their control manifels 20, 22 and 24 and at the three coincidence input terminals 30, 32 and 34 of the logic mait 18.

In response to the coircidence of negative levels at all its input terminals, the coincidence circuit 26 enables the inverter 28 to apply a zero volt level to the control terminal 18. This ground level is applied to the other logic traits, constraining them to have negative voltage levels at their control terminals 28, 22 and 24. Thus, the multistable circuit maintains a zero volt level at the control terminal 18 and negative levels at the remaining control terminals. These levels are suitably applied to londs 58 k:ving input leads 60, each of which is connected to a control terminal on a different stage 10–16.

Subsequent application of a zero wolt level to the fourth unit control terminal 24, for example, rapidly switches the circuit to maintain the zero level at that terminal and the negative level at the control terminals 18, 28 and 22.

the negative level at the control terminals 18, 20 and 22.

Considering, the detailed constraints of the illustrated coincidence circuit 26, the imput terminals 30, 32 and 34 are connected respectively to the anode of diodes D1, D2 and D3, whose cathodes are connected at a junction 36. A resistor R1 is connected between the junction 36 and a voltage source (not shown) providing a potential of —15 volts. Also connected to the inaction 36 is the cathode of a diode D4, whose anode is connected to the base 46 of a terminater Q1. A resistor R2 is connected between the base 46 and a voltage source (not shown) having a potential of +10 volts.

Assume, in the illustrated example, that the voltage level at each input terminal 30-34 can be either --3 volts or zero. With zero voltage at any one of these terminals the diode receiving this voltage clamps the potential at the junction 36 essentially to zero (manusing zelection of the resistors R1 and R2 to provide negative potential at the junction 36 in the absence of current through the diode D1-D3). With a small voltage op across the diode D4-resulting from current between the resistors R1 and R2, the base 46 is positive with respect to the ground emitter 44 and the transistor Q1 is cut off.

On the other hand, when the negative voltage level is applied to all three of the terminals 39-52, the junction 36 is clamped to the negative level. With the small drop across the diods D4, a substantial negative potential is applied to the bess 46, causing the transister to conduct.

The inverter 28 includes, in addition to the transistor Q1, a diode D5 connected between the transistor collector 42 and a voltage source (not about) providing the —3 volt level. Also included is a resistor R3 connected between the collector and the —15 volt source. When the transistor Q1 conducts, as a result of the application of the —3 volt level to all three terminals 30-34, the collector 46 is grounded and the auro volt level therefore appears at the terminal 28. When any one of the terminals 20-34 is at the zero volt level, and the transistor Q1 is

Accordingly, it will be apparent I volt level at the terminal 18, the units 12, 14 and 16 have the -3 volt leve! at their terminals 20, 22 and 24. Thus 5 all the inputs to the coincidence circuit 26 are at the -3 level to maintain the zero volt level at the terminal 18 as described above. A zero volt pulse at any of the termins 28-24 will then result in the -3 voit level at the terminal 18. This, in turn, will bring about conditions 10 in the respective logic units providing the zero volt level at the pulsed control terminal and the -3 volt level at all the other control terminals.

In summary, I have described a novel multistable circuit that can be simply constructed at low cost with any 15 desired number of stable states. The circuit is operated by applying a signal, suitably a pulse, to a selected control terminal In response, the circuit maintains the selected terminal at a selected voltage different from the voltages at the offer control terminals.

The invention is clearly not limited to operation with the voltage levels specified above for the illustrated embodiment. For example, the negative and zero volt levels discussed above can both be positive or negative, depending on the choice of operating voltages.

It will thus be seen that the objects set forth above among those made apparent from the preceding uescription, are efficiently attained and, since certain changes may be made in the above construction without departing from the scope of the immedian, it is intended that all matter contained in the above description or shown in the accompanying drawing shall be interpreted as illustrative and not in a limiting sense

It is also up a monitored that the following claims are intended to cover all of the generic and specific features of the immution herein described, and all statements of the scope of the invention, which, as a matter of language, might be said to fall therebetween.

Having described the immetics, what is claimed as 40 new and secured by Letters Patent is:

1. An electronic circuit comprising

(A) at least three logic circuits, each of which

- (1) has a plurality of input term nais not exceeding the number of logic circuits and an output

- (2) develops a second-level output signal only when all said input terminals receive first-level

- (3) develops said first-level signal at its output terminal when any one or more of said input 50 terminals receives a second-level signal,

- (4) has its output terminal connected to an input terminal of each of the other logic circuits so that each input terminal of each logic circuit is connected to an output terminal of another dif- 55 ferent logic circuit, an

(5) is arranged to develop a higher output imdance at its output terminal when it develops said first-level signal then when it develops said

- second level signal,

(B) whereby in response to application of an input signal of said second level to a first output terminal and, alternatively, application of an input signal of said first level to all output terminals except said first one, said circuit develops at said first output 65 terminal a persisting second-level signal and constrains the signals at the other output terminals to said first level.

- 2. An electronic circuit according to claim 1 wherein 70 there are only (n+1) logic circults, where (n) is an intoger greater than one, and wherein each logic circuit has only (n) input terminals and a single output terminal.

3. A circuit comprising, in combination,

(A) (n) (1) colorate an electric contraction.

(A) (n+1) coincidence circuits, each having only (n) 75

input terminals and an output terminal, where (n) is an integer greater than one,

- (1) said coincidence circuits being numbered in an ordered sequence

- (B) (n+1) inverters, each having an input terminal and an output to minal.

- (1) said inverters being numbered in said ordered sequence,

- (2) said input terminal of each inverter being conconnected to receive only the signal developed at the output terminal of the same-numbered coincidence circuit, and

- (3) said output terminal of each inverter being connected in circuit with an input terminal of each of the different-numbered coincidence cir-

- (C) each coincidence input terminal being connected within said circuit exclusively to inverter output terminak.

- 4. An electronic circuit according to claim 3 in which each inverter is arranged to present to said second-level signal a higher output impedance at the output terminal thereof when it develops said first-level signal than when it develops said second-level signal.

- 5. A multistable circuit comprising, in combination (A) (n+1) AND circuits numbered in an ordered sequence and each having a single output terminal and only (x) input terminals, where (x) is an integer greater than one,

(1) each AND circuit responding to the coincidence of first-level signals at all its input terminals to develop a third-level sisual at its cutput terminal, and

(2) developing a fourth-level signal at its output terminal when a recond-level signal is present at at least one of its input terminals, where said first-level and third-level signels may be the same and where said second-level and fourthlevel signals may be the st

(B) (n+1) inverters annihered in said ordered sequence and each having a single input terminal and a single output terminal,

- (1) each inverter developing at its output terminal said second-level signal in response to application of said third-level signal to as input terminal and

- (2) developing at its output terminal said first-level signal in response to application of said fourthlevel to its input terminal.

- (3) each inverter having its input terminal connected to the output terminal of the same-numbered AND circuit

- (C) (π+1) control terminals numbered in said ordered

- (1) each control terminal being connected to the output terminal of the same-aumbered circuit and to an input terminal of each of the different-numbered AND circuits,

- (D) whereby application of a second-level input signal to one control terminal causes each different-a bered AND circuit to deliver a fourth-level signal to the inverter connected to it, thereby producing first-level signals at all the input terminals of the same-numbered AND circuit so that said secondlevel signal persists exclusively at said one control terminal.

A multistable circuit comprising

(A) (n+1) coincidence circuits numbered in an ordered sequence and each having an output terminal and no more than (n) input terminals, where (n) is an integer greater than one,

(1) each coincidence circuit responding to the coincidence of first-level signals at all its input terminals to develop a third-level signal at its output tecesions, and

10

(2) developing a fourth-kvel signal at its output terminal when a

at at least one of it:, input terminals

(a) where said first-level and third-kvel signals may be the same and where said xc- 5 ond-kvel and fourth-kvel signals may be the same,

(B) (n+1) inverters numbered in said ordered  $\infty$ quence and each having an input terminal and an output terminal,

(1) each inverter having a transistor

(a) the base of which is connected to the inverter input terminal and

(b) the collector of connected to the inverter output terminal,

(2) said transistor in each inverter being arrang d (a) to have a relatively large collector-emitter resistance where it receives said fourthlevel signal at its base and

(b) to have a relatively small collector-emit- 20 ter resistance when it receives said third-

level signal at its base,

(3) each inverter having its input terminal connected to the output terminal of the same-numbered coincidence circuit, and

(C) (n+1) control terminals numbered in said or-

dered sequence,

(1) each control terminal being connected to the output terminal of the same-numbered inverter circuit and to an input terminal of each of the 30 different-numbered coincidence circuits.

7. Logical electrical apparatus comprising

(A) a multistable circuit comprising at least three mits, each

(1) having a plurality of input terminals and an 35

output terminal,

(2) developing a second-level outr t signal only in response to first-level signals at all its input terminak.

(3) developing said at its output terminal when one or more second-level signab are applied to its input terminals, and

(4) having its output terminal connected to an input terminal of each of the other logic cir-

(B) source a plurality of output lines each of which is connected to a different one of said multistable circuit output terminals, and

(C) output means having a plurality of input lines each of which is connected to a different one of

said multistable circuit output terminals,

(D) so that when said source means conditions one output line therefrom to have said second-level signal, said multistable circuit develops at its output terminal connected to said conditioned line a persisting second-level signal and constrains the signals at the other output terminals thereof to said first level.

8. Apparatus according to claim 7 in which each logic

circuit

(A) includes a grounded-emitter transistor inverter in which the transistor collector is the logic circuit output terminal, and

(B) produces said second-level signal when the transistor of the inverter therein is in a conducting state.

#### References Clied by the Exami

#### UNITED STATES PATENTS

| 3,012,155 | 12/1961 | Jagger         | 307-88.5 |

|-----------|---------|----------------|----------|

| 3,079,513 | 2/1963  | Yokelson       | 307-88.5 |

| 3,166,715 | 1/1965  | Cogar          | 30788.5  |

| 3,178,590 | 4/1965  | Heilweil et al | 307-88.5 |

| 3,210,569 | 10/1965 | Reek           | _ 32849  |

ARTHUR, GAUSS, Primary Examiner.

R. H. EPSTEIN, Assistant Examiner.