# Seahorse Central Processing Unit Technical Description

First Draft - May 1983

#### May 1983

This manual describes the KD32-AA central processing unit used in Seahorse.

NOTE: This manual is the property of Digital Equipment Corporation and is Company Confidential. It may not be distributed to other reviewers without authorization.

# KD32-AA Central Processing Technical Description

Document Order Number: XX-12345-XX

Version: 0.0

digital equipment corporation maynard, massachusetts

#### First Draft Printing, May 1983

The material in this manual is for informational purposes and is subject to change without notice. The information in this document should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

#### Copyright © 1983 by Digital Equipment Corporation All rights reserved. Printed in U.S.A.

The postage-paid READER'S COMMENTS form on the last page of this document requests your critical evaluation to assist us in preparing future documentation.

#### The following are trademarks of Digital Equipment Corporation:

| CTI BUS??    | DIBOL        | QBUS??    | VMS            |

|--------------|--------------|-----------|----------------|

| DEC          | [dec logo]   | Q22 bus?? | VT             |

| DECmate      | MASSBUS      | Rainbow   | Work Processor |

| DECsystem-10 | microVAX??   | RSTS      |                |

| DECSYSTEM-20 | PDP          | RSX       |                |

| DECUS        | P/OS         | UNIBUS    |                |

| DECwriter    | Professional | VAX       |                |

#### COMPANY CONFIDENTIAL

# Contents

# Chapter 1: Introduction

System Overview 1 KD32-AA CPU 2 Q22 Bus 2 **RODX1** Controller 5 **RX50 Floppy Disk Drive 5** RD51 and RDXX Fixed Disk Drives 5 Memory 6 MSV11-P Memory 6 MSV11-J Memory 7 **Console Terminal 7 Front Control Panel 8** Power Supply 8 Backplane 11 Patch Panel Assembly 12 System Architecture 13 System Timing 17 System Bus Summary 21

# Chapter 2: Functional Overview Data Path 25

Data Path Chip 26 Control Store 26 Microsequencer 29 Internal Data Bus 29 Boot PROM 29 Console Interface 29

### Memory Controller 30

Cache 31 Translation Buffer 31 Memory Controller Micromachine 31 Q22 Bus Interface Logic 32

# Q22 Bus Interface 32

# Macroprogram Level Instruction Flow 33

No Operation 33 Move Byte 37 Subtract One and Branch 43

Microcode 50

### Chapter 3: Data Path Microcode

# **Microinstruction Format 53**

Parity Field 53 Condition Code/Data Type Field 54 Data Path Control Field 55 Next Address Control Field 59 Jump and Jump to Subroutine 63 Branch 63 Case 64

Branch to Subroutine 64 Trap 64 Return 65 Instruction Register Decode 65 Operand Specifier Decode 66

# Data Path Microinstructions 67

ALU Microinstructions 67 Shift Microinstructions 67 Move Microinstructions 68 Other Microinstructions 68 Decode 69 Restore 71 Multiply Step 72 Memory Request 73 I-stream Request 75

### Operand Field Encoding 76

# Memory Controller Interface Microcode 79

Memory Function Encoding 79 Memory Functions 82 READ.VECTOR 82 VREAD.RCHECK 82 VREAD.WCHECK 83 VWRITE.WCHECK 83 VREAD.LOCK 84 IB.REFILL 84 PREAD 85 PWRITE 85 XLATE.RCHECK 86

**XLATE.WCHECK 86 IB.READ 87 REPEAT.FIRST 87 REPEAT.SECOND 88 READ.CACHE 89** WRITE.CACHE 90 READ.MCT 90 WRITE.MCT 90 READ.TB 91 WRITE TB 91 **INVALID.SINGLE 91 INVALID.MULTIPLE 92 RCHECK 92** WCHECK 93 Memory Controller Status 93 **Microverify 95 Console Microcode 95**

# **Chapter 4: Data Path Module**

**Overview of DAP Functions 97**

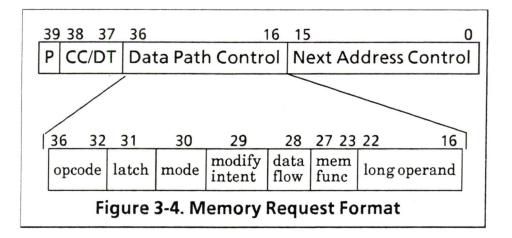

Controlling the Microinstruction Flow 97 Clock Signals 98 Control Store 101 Control Store Address Register 103 Parity Checker 103 Index Register 104 Microsequencer 104

Page Register and Microprogram Counter 107 Conditional Decrementer 107 Jump Register 107 OR MUX 107 Jump Mux 108 Next Microaddress MUX 109 Microstack 111 Microstack Pointer 112

### Decoding Macroinstructions 113

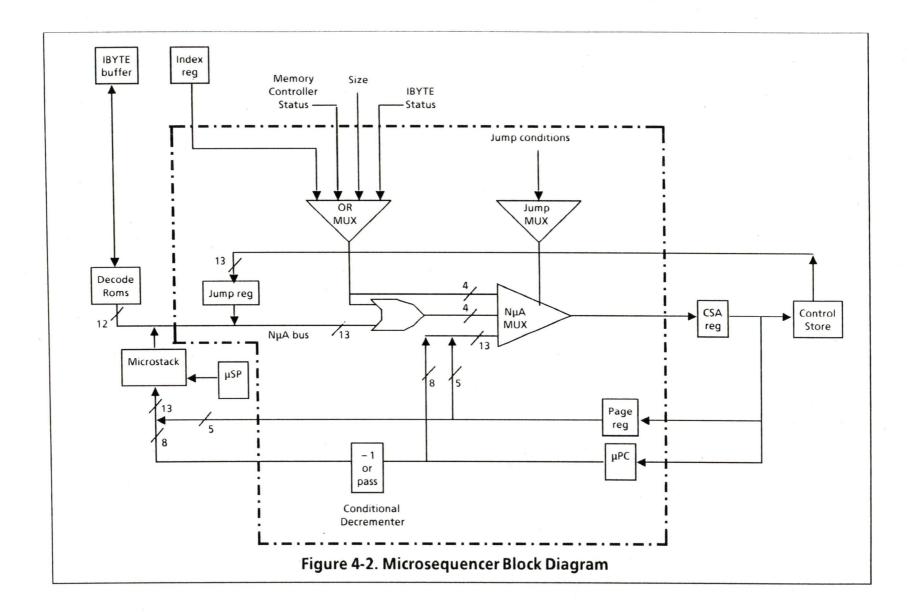

IBYTE Register 113 IBYTE Control 114 Decode ROMs 121 ALU and PSL Condition Codes 122 Condition Code Control 123 Condition Code Class Register 123 Condition Code PALs 124 Macrolevel Branch Control 129 PSL Enable 130 Size Register 130

# **Executing Microinstructions 131**

Clock Signal 132 Control Store Register 139 Parity Generator 139 Size Control 139 Data Path Chip Buses 141 Arithmetic and Logic Unit 142 Barrel Shifter 142 Register File 143 Program Counter 147

Result Registers 147 ROM 148 Register Save Stack 148 Pointer Registers 149 Shift Count Register 149 Interval Timer and TMRCSR 149 Condition Codes 150 I/O Port 152

# **Transferring Data 155**

Internal Data Bus 155 Data Bus 156 Sign-Extension 156 ID Bus Latch 157 ID MUX 157 IBYTE Buffer 157 Miscellaneous Register 158 ID Bus Address Decode Logic 159 Zero-Generator 165

### Processing Interrupts 165

IPL Register 165 Interrupt Control Logic 166 Priority Encoder 166 Interrupt Source Register 167

# Communicating with the Console Terminal 168

Console UART 169 Console UART Registers169 UART Data Register 170 UART Status Register 171

UART Mode Registers 172 UART Command Register 173 Initializing the UART 174 UART Buffer 174 Option Switches 175 – 12 Volt Generator 176 Break and Halt Detection 176

## Powering Up 178

Power Up Signals 178 Power Failure 179 Initialization State 183 Initialization Signals on Power Up 183 Option Switches 187 Boot PROM 187 System Identification Register 188

# Communicating with the MCT 189

Data Interface 189 Control Interface 190 Interface Control Signals 191 Stalls 192 MD Bus Latches 193 Memory Function Latches 194 Memory Function Control 195 PSL.MODE Register 197 Sign-Extenders 198 Memory Request Timing 198

# Microprogram Level Flow: ADDW3 207

Evaluating the Opcode: Decode A1 209 Evaluating the First Operand Specifier 211

Decode 41 211 Shift by 2 213 Shift by 1 215 Decode A0 215 Add 217 **Move 218** Add 219 Memory Request 220 **Move 222 Move 223 Evaluating the Second Operand Specifier 224** Decode 95 224 **Move 226** Move 227 Add 228 Memory Request 229 **Move 230 Move 231** Memory Request 233 **Move 234 Move 235** Adding the Operands 236 Add 236 Decode 52 238 Move 239

# Chapter 5: Memory Controller Microcode

Memory Controller Function Parameters

# 249

**Microinstruction Format 252** MCA Bus Source Field 252 **Q22** Bus Function Request 253 Merge Register Output Enable 254 PAR Output Enable 254 Adder Output Enable 254 **Register File Output Enables 255 Transceiver Control 255 Functional Block Control Field 256** Prefetch FIFO Control 259 **Q22 Bus Control 259** PAR Latch Enable 261 **Reverse Pass Output Enable 262 Reverse Pass Latch Enable 262** Merge Register Selects 262 **Byte Rotate Select 263** TB/Cache RAM Control 264 TB/Cache Valid 264 **TB/Cache Access Select 265** Adder Latch Enable 266 Adder Subtract Enable 266 Adder Constant Select 266 **Register File Write Enables 267 Register File Address Field 268** Microprogram Control Field 269 **Busy Control 269 Microsequencer Control 270 Branch Control 271**

Next Address 271 **Branch Conditions 272 NO.MAP 275** DATAFLOW 275 MCA <1> and MCA <0> 275 PAGE.CROSS 276 MODIFY 276 **QBUS.BLOCK 276 QBUS.SYNCH 276 QBUS.BUSY 277** TB.ERROR 277 MCA <29 or 28> 277 **QBUS.TIMEOUT 278 QBUS.ERROR 278** TBC.MISS 278 PREFETCH.DIS 279 **IB.ERROR 279** <sup>-</sup>

# Q22 Bus Controller Interface 279

Interface Microcode 280 Q22 Bus Controller Status 281

# **Chapter 6: Memory Controller Module**

**Overview of MCT Functions 283**

# Generating the Clock Signals 283

MCT Clocks 284 Timing 287

Controlling the MCT Microinstruction Flow

### 288

Memory Request Latch 288 CSA Bus 289 Pull-up Resistors 289 MCT Control Store 289 Microinstruction Clock Gating 290 Branch Condition Logic 290 MCT Microsequencer 292 Microinstruction Decode Logic 292 CSA PAL 296 Save Address Register 297 Next Address Buffer 297 Branch MUX 298

# **Translating Virtual Addresses 298**

Index MUX 299 Tag MUX 300 Tag RAM 300 TB/Cache RAM 302 Write Isolation Buffer 304 TB/Cache Comparator 304 Physical Address Register 305 Register File 305 Adder and Adder Register 307 Translation Buffer Operations 307 Address Sources 307 TB Reads 308 TB Writes 308 TB Invalidates 308

### Accessing the Cache 309

Index MUX 310 Tag MUX 310 Tag RAM 311 TB/Cache RAM 312 Write Isolation Buffer 313 TB/Cache Comparator 313 Cache Operations 313 Address Sources 313 Cache Reads 314 Cache Writes 314 Conditional Cache Invalidates 315

# Transferring Data 316

MCA Bus 316 MCD Bus 318 Memory Data Bus Transceiver 319 Memory Control Bus 319 Merge Register and Rotate Logic 319 Reverse Pass Latch 320

# Prefetching Instruction Stream Bytes 320

Prefetch FIFO 321 Prefetch FIFO Control Logic 321 Prefetch Program Counter 322 Prefetch Operation 322

# **Tracking and Reporting Status 324**

Control and Status Registers 324 Map Enable Control Register 325

Cache Enable Control Register 325 Error Flag Status Register 325 IB Error Status Register 326 Access Protection Latch 326 Access Violation PAL 327

# Communicating with the Q22 Bus Interface 331

Q22 Bus Controller 331 Q22 Bus Write Register 331 Q22 Bus Read Register 332

Microprogram Level Flow: MOVW 333 **Evaluating the Opcode 335 Evaluating the First Operand Specifier 335 Obtaining the Operand 338** TB Access 339 Cache Access 340 Q22 Bus NOP 341 Set Error Code 342 TB Read 343 TB Write 345 **TB Access Retried 350 Cache Access Retried 351 Incorrect Data Returned 353** Q22 Bus Go 354 First Block Read 354 Clear Q22 Bus Function 356 Second Block Read 357 **Return Correct Data 358**

Prepare for Cache Write 359 Cache Write 360 Move Data 361 Evaluating the Second Operand Specifier 362

# Chapter 7: Q22 Bus Controller

Q22 Bus Controller Function Parameters 365

## Control Store Addresses 366 OBUS BUSY Asserted 367

Bus State Field 368 Function Code Field 369 State Bits 369 QBUS BUSY Not Asserted 369

# **Microinstruction Format 370**

Busy 371 Enable Parity 371 SDMGO 371 SSYNC Hold 371 Enable SIAKO 372 SDOUT 372 Enable SDIN 372 Enable SSYNC 375 Enable Data 375 Address OK 376 Request Clear 376 SYNC/READY 377

Microstate Bits 377

Overview of Q22 Bus Controller Functions 377

Controlling the Microinstruction Flow 378

Servicing MCT Function Requests 379 Q22 Bus Control PAL 379

Q22 Bus Transceivers 381

### Arbitrating the Q22 Bus 382

Q22 Bus Controller Microsequencer 382 Cache Invalidate Logic 383 Bus Error Logic 384

### Communicating with the MCT 385

Block Mode 385 SYNC/READY 386 Q22 Bus Busy 387 Q22 Bus Timeout 387 Q22 Bus Error 387 Cache Invalidate 388

# Q22 Bus Operations 388

Write Byte 388 Write Word 388 Write Block 389 Read Word 389 Read Block 389 Read Interrupt Vector 389 Interlock Request 389

# **List of Figures**

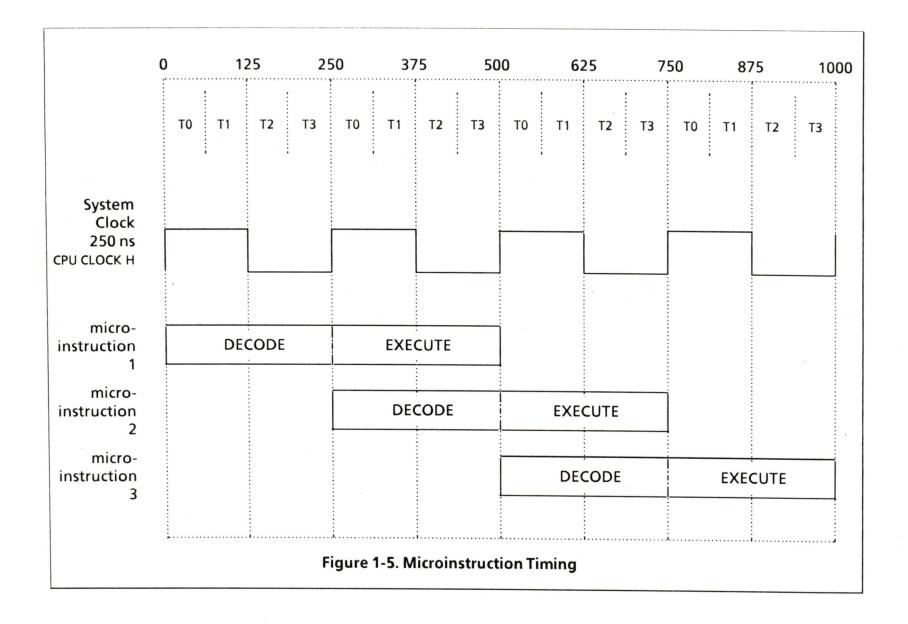

Figure 1-1. Seahorse System 3 Figure 1-2. Seahorse Front Panel 9 Figure 1-3. Seahorse Backplane 12 Figure 1-4. Seahorse Physical Memory 15 Figure 1-5. Microinstruction Timing 19

Figure 2-1. CPU Block Diagram 27

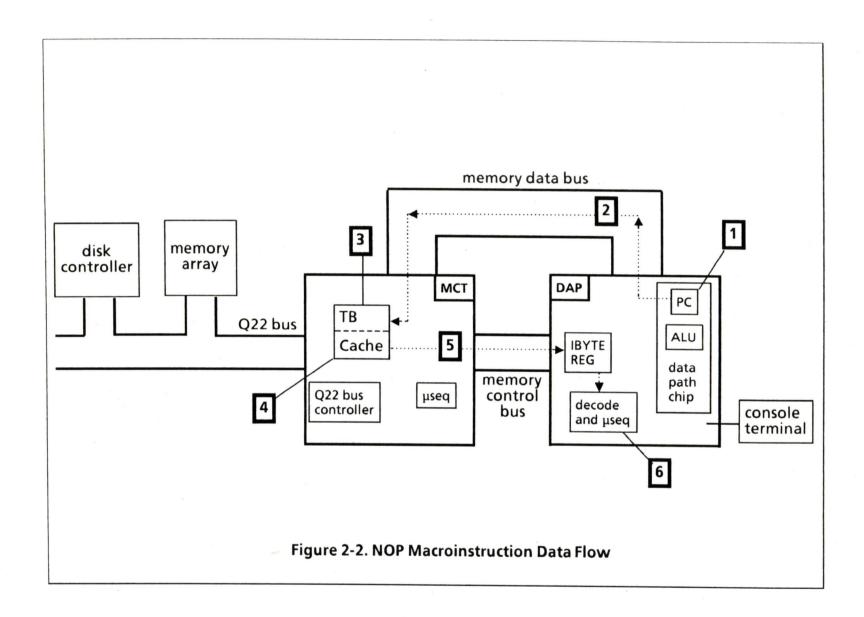

Figure 2-2. NOP Macroinstruction Data Flow 35

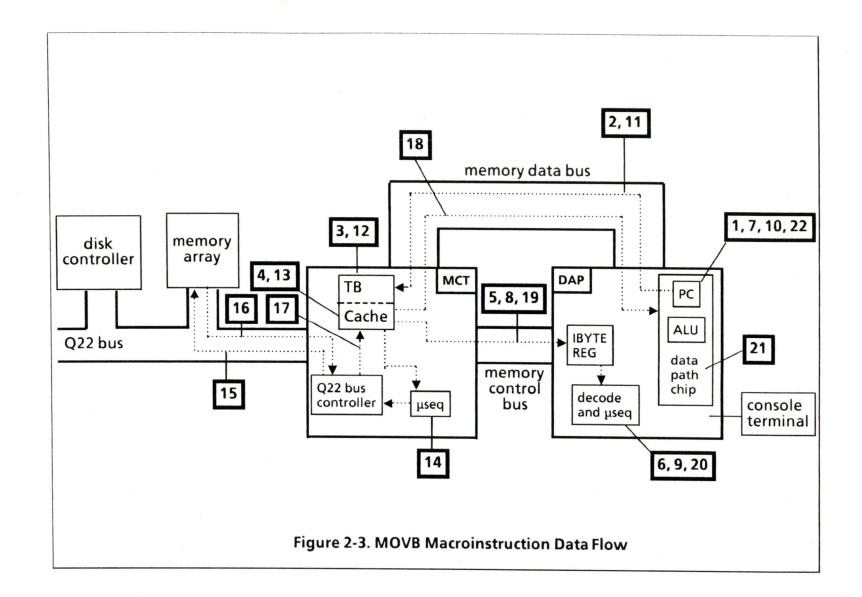

Figure 2-3. MOVB Macroinstruction Data Flow 39

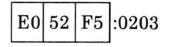

Figure 2-4. SOBGTR Macroinstruction Data Flow 45

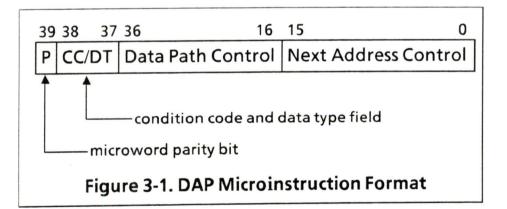

Figure 3-1. DAP Microinstruction Format 53

Figure 3-2. Data Path Control Field 55

Figure 3-3. Next Address Control Field Formats 61

Figure 3-4. Memory Request Format 81

Figure 4-1. Data Path Block Diagram 99

Figure 4-2. Microsequencer Block Diagram 105

Figure 4-3. IBYTE Register Loading 119

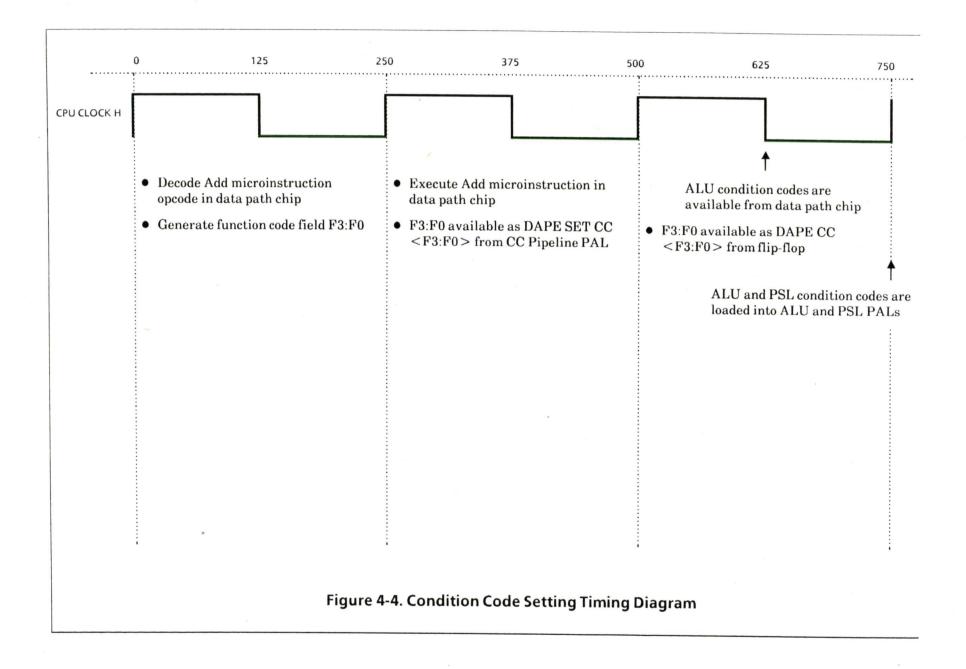

Figure 4-4. Condition Code Setting Timing Diagram 127

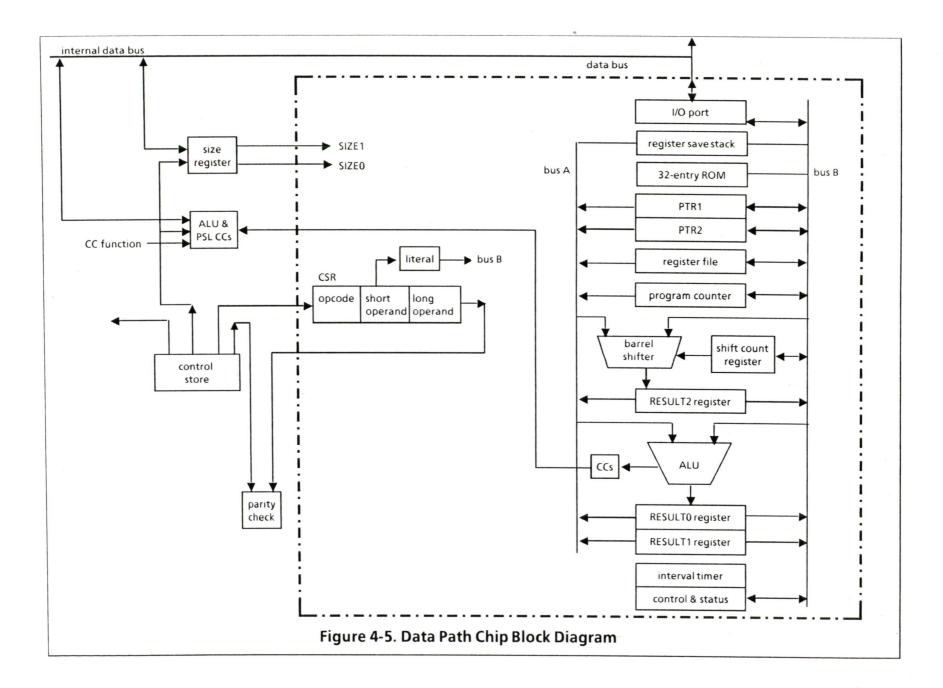

Figure 4-5. Data Path Chip Block Diagram 135

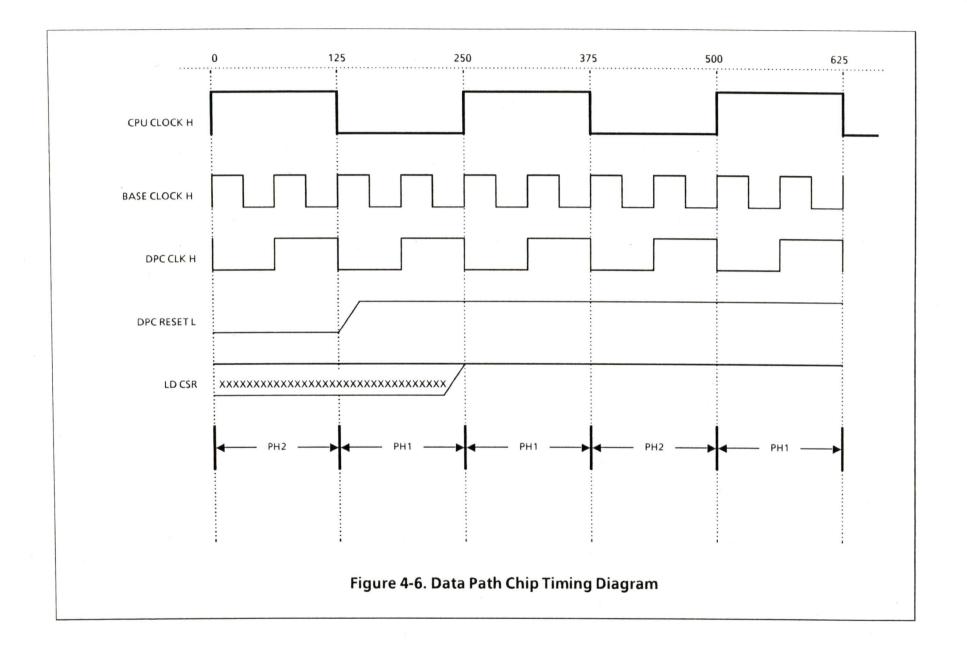

Figure 4-6. Data Path Chip Timing Diagram

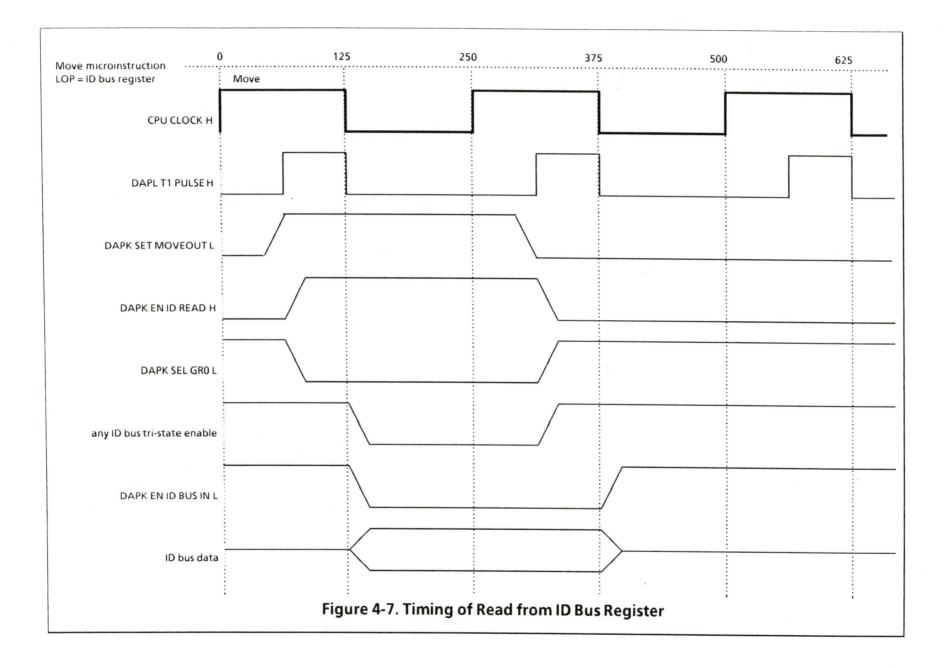

Figure 4-7. Timing of Read from ID Bus Register 161

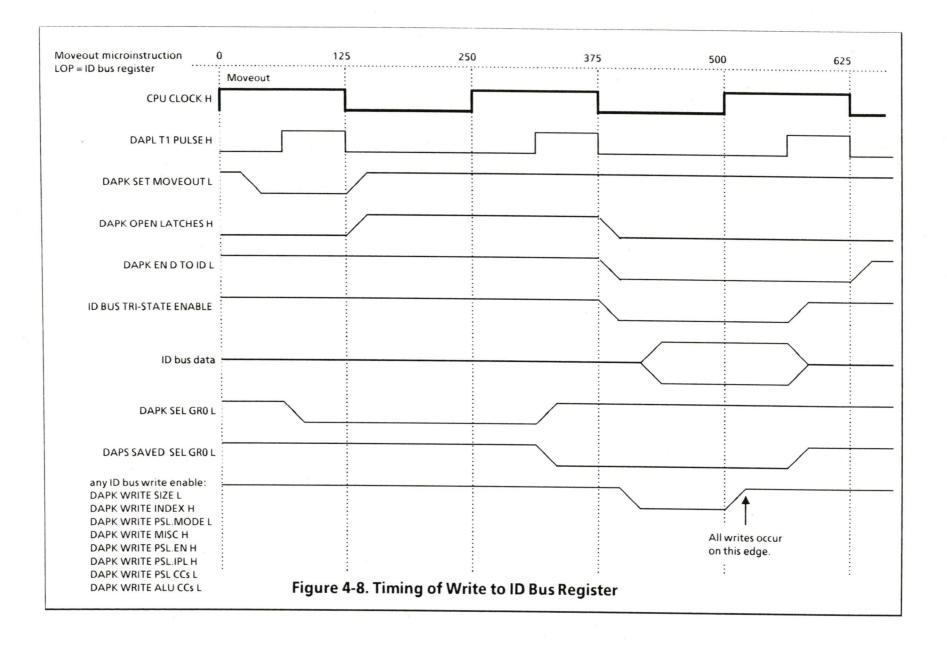

Figure 4-8. Timing of Write to ID Bus Register 163

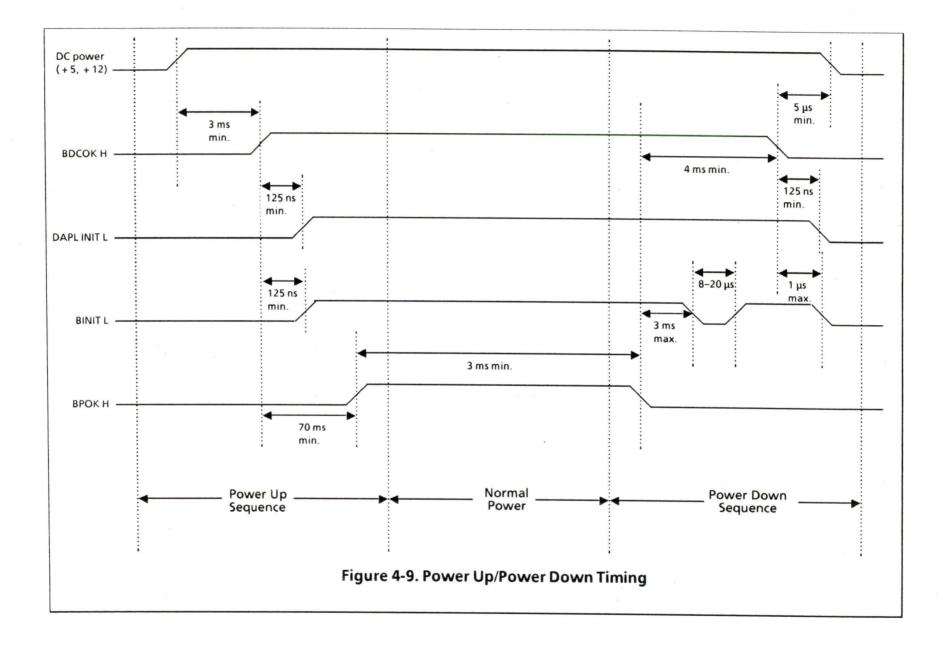

Figure 4-9. Power Up/Power Down Timing 181

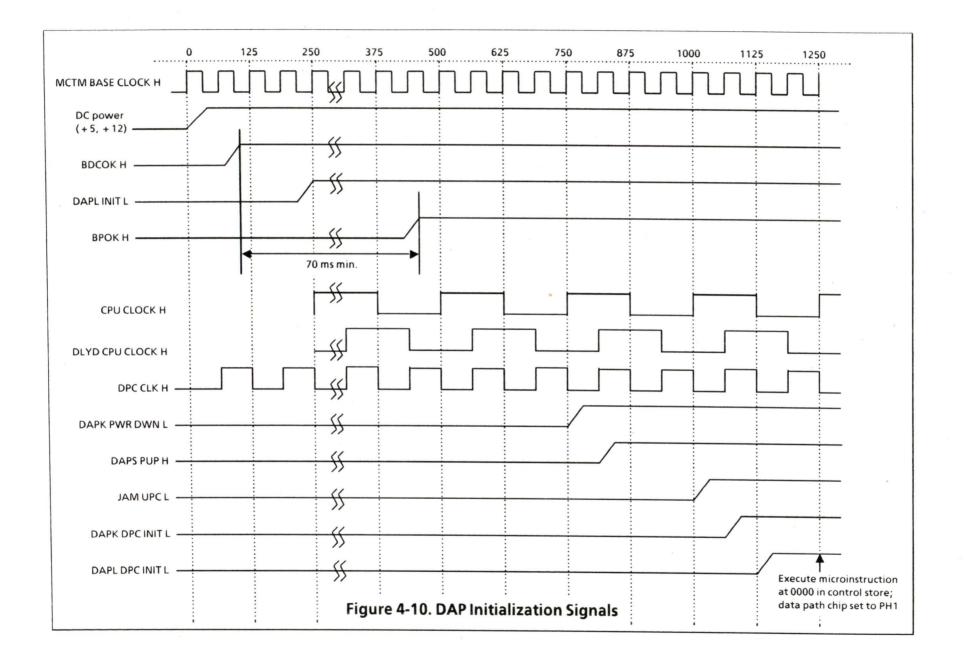

Figure 4-10. DAP Initialization Signals 185

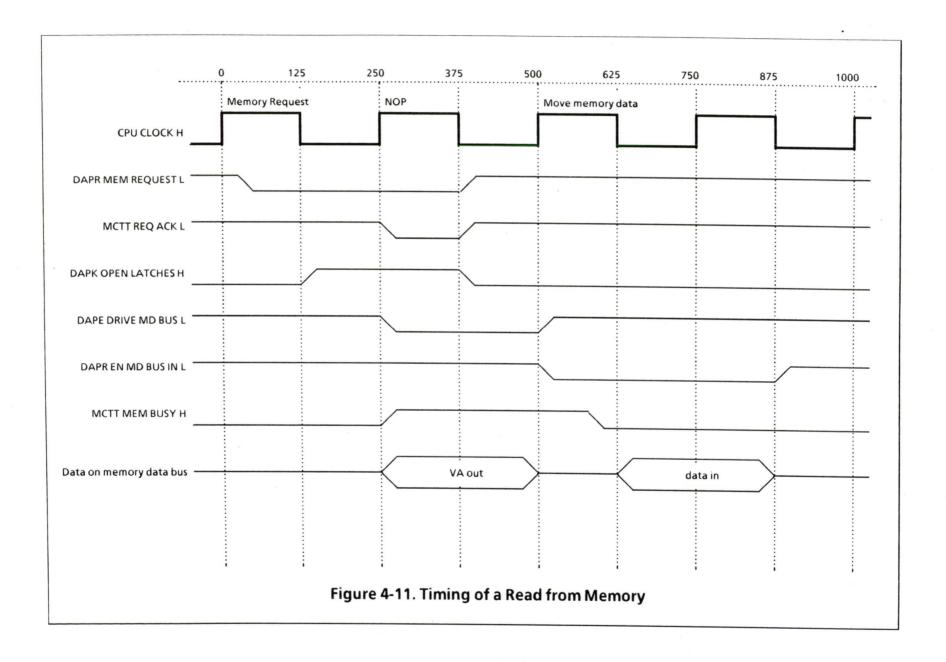

Figure 4-11. Timing of a Read from Memory 201

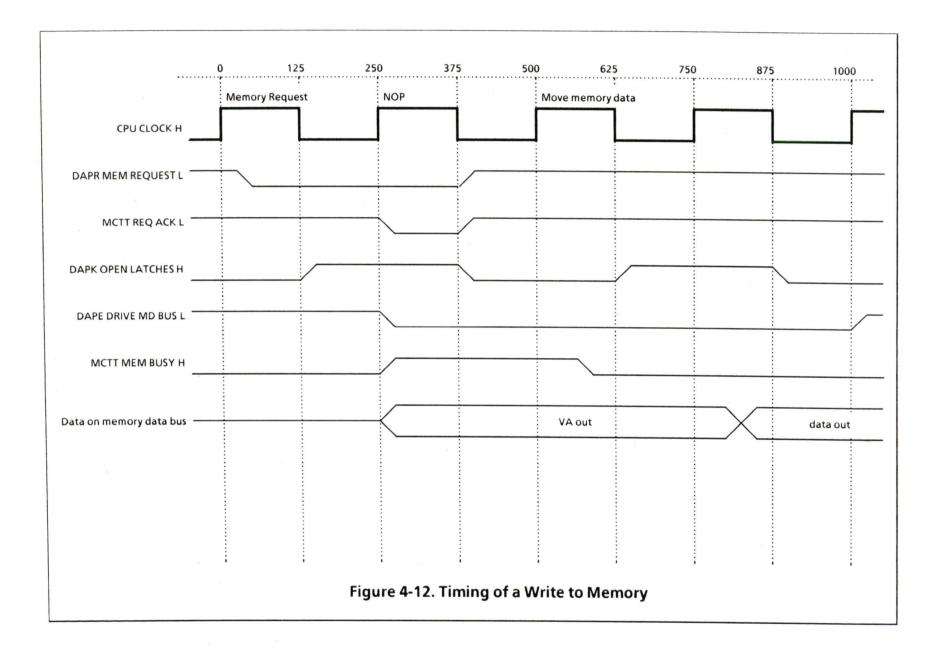

Figure 4-12. Timing of a Write to Memory 203

Figure 4-13. ADDW3 Microinstructions

241–247

Figure 5-1. MCT Microaddress Format 251

Figure 5-2. MCT Microinstruction Format 252

Figure 5-3. MCA Bus Source Field 253

Figure 5-4. Functional Block Control Field 257

Figure 5-5. Q22 Bus Control Field 259

Figure 5-6. Microprogram Control Field 270

Figure 5-7. Branch Control Field and Next Address Field Formats 273

Figure 6-1. Memory Controller Block Diagram 285

Figure 6-2. MCT Microsequencer Block Diagram 293

Figure 6-3. Organization of Tag RAM 301

Figure 6-4. Translation Buffer Tag 301

Figure 6-5. Organization of TB/cache RAM 303

Figure 6-6. Translation Buffer PTE 304

Figure 6-7. Cache Tag 311

Figure 7-1. Microaddress Format, BUSY Asserted 367

Figure 7-2. Microaddress Format, BUSY Not Asserted 370

Figure 7-3. Q22 Bus Controller Microinstruction Format 373

# **List of Tables**

Table 1-1. Front Panel Switches 9 Table 1-2. Front Panel Indicators 9

Table 3-1. Opcode Assignments 57 Table 3-2. Jump Control Field 61 Table 3-3. OR <2:0> 61 Table 3-4. Decode Microinstruction Short Operand 69 Table 3-5. Register Address Organization 77

Table 4-1. Forced Zeros on NuA MUX

Output 110

Table 4-2. Condition Code Class Register Encoding 124

Table 4-3. CC Function Field Encoding 125

Table 4-4. Barrel Shifter Functions 143

Table 4-5. DPC Registers 145

Table 4-6. Data Path Chip Condition Codes

Table 4-7. External Registers 153

Table 4-8. Interrupt Source Register Encoding 168

Table 4-9. UART Registers 170

Table 4-10. DAP/MCT Interface Signals and Timing 205

Table 5-1. Transceiver Control Field 256 Table 5-2. Function Code Field 260 Table 5-3. Merge Register Selects 263 Table 5-4. Byte Rotate Select 263 Table 5-5. TB/Cache RAM Control 264 Table 5-6. TB/Cache Access Select 265 Table 5-7. Adder Control 267

Table 5-8. Register File Address Space 268 Table 5-9. Busy Control Field Encoding 270 Table 5-10. Microsequencer Control Field Encoding 273

Table 6-1. MCA Bus Sources and **Destinations 317** 6-2. Sources and Table MCD Bus **Destinations 318** Table 6-3. MCT Error Codes 325 Table 6-4. Protection Codes 329

Table 7-1. Bus State Field Encoding 368 Table 7-2. Function Code Field 369

1

í

Í

# Preface

# Manual Scope

This manual is a technical description of the KD32-AA central processing unit (CPU) used in the Seahorse system. It is intended as a field reference for DIGITAL Field Service personnel and a resource for training programs conducted by Educational Services and Manufacturing. A knowledge of VAX architecture is assumed.

Chapter 1 is a general description of the Seahorse system. The remaining chapters describe the microcode and the hardware for the two modules that make up the CPU board set:

- Data Path Module M7135

- Memory Controller Module M7136

# **Related Documentation**

The Seahorse Central Processing Unit Technical Description is part of the hardware documentation set for the Seahorse system. Related manuals that may be of interest are:

- Seahorse Owner's Manual. This book contains site preparation, installation, operation, diagnostics, and system configuration information for the Seahorse system.

- NPM Handbook. This book contains?

- VAX Architecture Handbook. The Seahorse

system design is based on the VAX architecture described in this handbook.

- Microcomputer Interfaces Handbook. This handbook is a reference guide for the interface and peripheral hardware options that can be installed on the Extended LSI-11 Bus used in Seahorse.

- Microcomputers and Memories. This manual contains a detailed description of the Extended LSI-11 Bus.

- Seaboard Manuals?

- MicroVMS Manuals?

# Chapter 1 Introduction

Chapter 1 is a general description of the Seahorse system. It contains information about the system necessary for understanding the Seahorse central processing unit (CPU). The remaining chapters provide a detailed technical description of the KD32-AA CPU.

### System Overview

The Seahorse system is a 32-bit, high-performance, microprogrammed computer. The processor executes a subset of the native VAX instruction set and contains an interface to the extended LSI-11 bus (Q22 bus). PDP-11 compatibility mode is not supported.

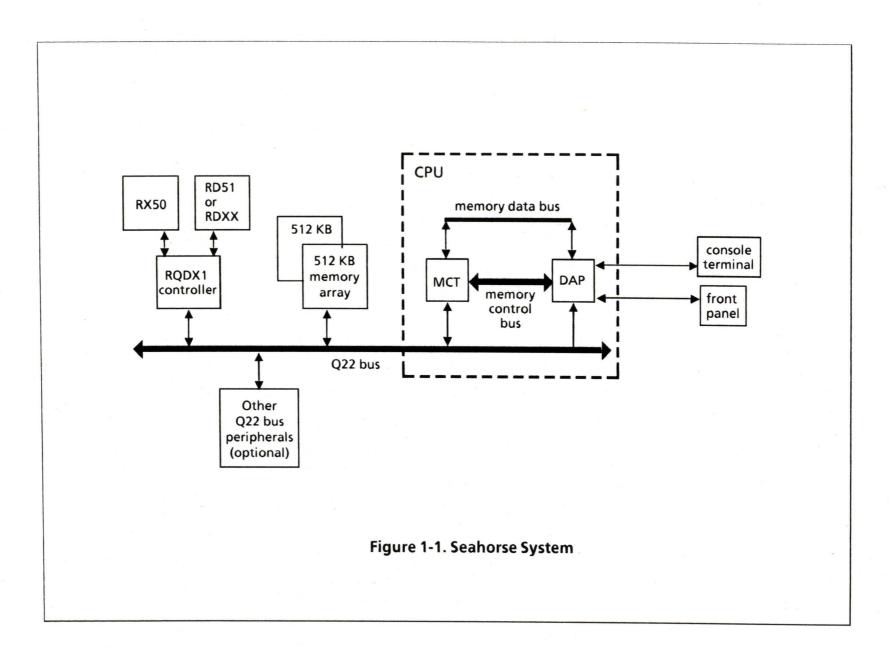

The major components of the Seahorse system, shown in Figure 1-1, are:

- KD32-AA CPU:

- memory controller (MCT)

- data path (DAP)

- Q22 bus

- RQDX1 controller

- RX50 floppy disk drives

- RD51 or RDXX fixed disk

- Q22 memory, with block mode capability

- console terminal

- front control panel

1

#### KD32-AA CPU

The KD32-AA CPU implements the MicroVAX architecture on two quad-height modules, and provides an interface to the Q22 bus. As such, it contains:

- an interface to the Q22 bus which supports block mode transfers and up to four megabytes of physical memory

- an 8 KB direct-mapped cache

- a 512 entry (longword) translation buffer

- a 10 ms interval timer

- a console serial line unit

- an 8 KB boot PROM

#### Q22 Bus

The Seahorse system backplane uses the extended LSI-11 bus (also called the Q22 bus), which has 22bit addressing. The Q22 bus consists of 42 bidirectional and 2 unidirectional signal lines. These are the lines along which the processor, memory, and I/O devices communicate with each other. Seahorse performs the following Q22 bus data transfer functions:

| DATI   | read word                |  |

|--------|--------------------------|--|

| DATO   | write word               |  |

| DATOB  | write byte               |  |

| DATIO  | read, modify, write word |  |

| DATIOB | read, modify, write byte |  |

| DATBI  | read block               |  |

1: Introduction

#### DATBO write block

#### **RQDX1** Controller

The RQDX1 controller (M8639) is a quad-height module that occupies the last-used slot in the backplane. It is the interface between the Q22 bus and the disk drives (floppy and fixed). The controller is a direct memory access (DMA) interface and uses mass storage control protocol (MSCP).

#### **RX50 Floppy Disk Drive**

The RX50 is a random access storage device with two floppy disk drives. It uses single-sided 5.25 inch (13.34 cm) diskettes. The total drive capacity is 800K bytes of formatted data. Each drive has an access door and slot for inserting and removing diskettes. A head load LED for each diskette slot informs the user when that unit is busy.

The RX50 is a field replaceable unit (FRU) that mounts in the Seahorse system box. One cable (part number xxxx) connects the RX50 to the RQDX1 controller. Another cable (part number xxxxx) connects the RX50 to the power supply. See the Seahorse Owner's Manual for removal and replacement procedures.

#### **RD51 and RDXX Fixed Disk Drives**

The RD51 is a random access storage device which uses two nonremovable 5.25 inch (13.34 cm) disks as storage media. One movable head per disk surface services 153 data tracks. The total formatted capacity of the four heads and surfaces is 10 megabytes.

The RDXX is a random access storage device which uses one nonremovable 5.25 inch (13.34 cm) disk as storage media. The total formatted capacity is 25 MB.

The RD51 and RDXX are field replaceable units (FRUs) that mount in the Seahorse system box. One cable (part number xxxx) connects the RD51 or RDXX drive to the RQDX1 controller. Another cable (part number xxxx) connects the RD51 or RDXX drive to the power supply. See the Seahorse Owner's Manual for removal and replacement procedures.

#### Memory

Seahorse relies on block mode Q22 bus data transfer functions to realize its performance goals. Therefore, although the KD32-AA CPU is compatible with other extended LSI-11 bus memories, Seahorse systems support only those Q22 memories that have block mode capability. Both the MSV11-P and the MSV11-J memory families offer this capability.

#### MSV11-P Memory

The MSV11-P family of memory modules are quadheight modules that implement an 18-bit wide random access memory array (16 data bits and 2 parity bits), parity generation and detection, and on-board refresh circuitry. There are three variations:

| MSV11-PL | 512 KB of storage using 64K<br>MOS RAMs |

|----------|-----------------------------------------|

| MSV11-PK | 256 KB of storage using 64K<br>MOS RAMs |

1: Introduction

#### MSV11-PF 128 KB of storage using 16K MOS RAMs

#### MSV11-J Memory

The MSV11-J memory is a quad-height module that implements two 22-bit blocks of random access memory (16 data bits and 6 ECC bits). Both blocks of memory are read simultaneously on reads (so that each access retrieves a longword of data from the array), and the requested word is transferred on the bus, while the other word is latched on the memory module. This provides the potential for a reduction in access time if this word is subsequently requested. On a write, only one block is accessed. The MSV11-J also implements ECC (single-bit correction) and on-board refresh logic. There are two variations:

| MSV11-JA | 512 KB of storage using 64K<br>RAMs |

|----------|-------------------------------------|

| MSV11-JB | 2 MB of storage using 256K<br>RAMs  |

An MSV11-J memory module must be plugged into a Q22/CD slot in the backplane.

#### **Console Terminal**

The console terminal may be any member of the VT100 or VT200 family of terminals. A cable connects the terminal to a serial line unit (SLU) connector on the rear of the Seahorse system box. A terminal interface UART and an RS232 driver and receiver pair are located on the data path module (M7135). The baud rate is set by DIP switches on the data path module; the choices are 300, 1200, 9600, and 19.2K baud.

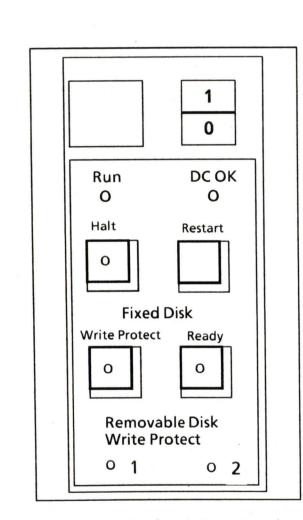

#### Front Control Panel

The front panel provides control and status of the various components of the system. The switches and indicators are shown in Figure 1-2. The switches and their functions are listed in Table 1-1. The indicators and their meanings are listed in Table 1-2.

#### Power Supply

The power supply (H7864) is a modular, 230-watt power supply that supplies from 4.5 amps minimum to 36 amps maximum at +5 volts, and 0 to 6 amps at +12 volts. There are also two outputs designed to accommodate DC brushless fans, not included in the 230-watt power specification. These outputs supply 0.45 amps at +12 volts and +9 volts.

Additional power supply features include thermal shut down, overvoltage and overcurrent protection, AC input transient suppression, and three Q22 bus signals (BPOK H, BDCOK H, BEVNT L).

The power supply includes connectors that provide the necessary power and signal interfaces to the logic backplane, mass storage units, front panel, and fans.

The power supply is a field replaceable unit (FRU). See the *Seahorse Owner's Manual* for removal and replacement procedures.

1: Introduction

Figure 1-2. Seahorse Front Panel

| Table 1-1. Front Panel Switches |                                                     |                                                                                                                                                                   |  |  |

|---------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Switch                          | Position                                            | Function                                                                                                                                                          |  |  |

| 1,0                             | 1                                                   | Turns on the system power.                                                                                                                                        |  |  |

|                                 | 0                                                   | Turns off the system power.                                                                                                                                       |  |  |

| Halt                            | In (LED lit)                                        | The processor halts and responds to console commands.                                                                                                             |  |  |

|                                 | Out                                                 | Enables the processor to run.                                                                                                                                     |  |  |

| Restart                         | In<br>(momentary<br>switch)                         | When the halt switch is out (LED off)<br>the processor carries out a power-up<br>sequence.<br>When the halt switch is in (LED lit),<br>this button has no effect. |  |  |

| <b>RD</b> Protect               | In (LED lit)                                        | Write protects the fixed disk.                                                                                                                                    |  |  |

|                                 | Out (LED off)                                       | Enables writing to the fixed disk.                                                                                                                                |  |  |

| RD Ready                        | In (LED off)                                        | Places the fixed disk off-line.                                                                                                                                   |  |  |

|                                 | Out (LED lit)                                       | Places the fixed disk on-line.                                                                                                                                    |  |  |

|                                 | Table 1-2. Fro                                      | nt Panel Indicators                                                                                                                                               |  |  |

| LED                             | Function                                            | Function                                                                                                                                                          |  |  |

| Run                             | The Run LED is<br>the LED goes off<br>instructions. | The Run LED is on when the processor is operating;<br>the LED goes off when the processor is not executing<br>instructions.                                       |  |  |

| DC OK                           |                                                     | This LED is on when the power supply is generating correct DC power output voltages.                                                                              |  |  |

| Removable Dis                   | k Write Protect                                     |                                                                                                                                                                   |  |  |

| 1                               | When lit indicat                                    | When lit indicates the floppy in drive 1 is write protected.                                                                                                      |  |  |

| 2                               | When lit indicat                                    | When lit indicates the floppy in drive 2 is write protected                                                                                                       |  |  |

#### Backplane

The backplane (H9278-A) is a four-row by eight slot backplane capable of accepting either quad- or double-height modules. The backplane uses the Q22 bus structure in the A and B connectors of slots 1 through 8, and in the C and D connectors of slots 4 through 8. A slot-to-slot interconnection scheme (referred to as the CD interconnect) is wired in the C and D connectors of slots 1 through 3. The CD interconnect connects selected side two pins in rows C and D of a given slot to side one pins of the slot immediately following. There are 32 such connections per slot.

The backplane receives and distributes two voltages and ground. Maximum ratings are +5 volts at 36 amps, and +12 volts at 6 amps.

The backplane includes four connectors, J1 through J4, which are mounted on side two of the backplane. J1 (eighteen pins), J3 (four pins), and J4 (four pins), connect power supply outputs to the backplane. J2 (ten pins) connects the backplane to the front panel.

The backplane also includes provision for the insertion of four resistor packs (p/n 1318110-00) into positions XZ1, XZ2, XZ3, and XZ4. In a Seahorse system (single backplane), these resistor packs are inserted to terminate the Q22 bus lines. (Characteristic impedance is 220 ohms).

Figure 1-3 shows the backplane organization. The numbers in the parentheses following the Q22 designations show the path of interrupt and direct memory access grant continuity for options installed in the backplane; increasing value denotes lower priority. The BIAKO L/BIAKI L

and BDMGO L/BDMGI L signals are daisychained. Therefore, each slot requires the insertion of a module to pass these grant signals on, as no jumpers are provided on the backplane for this purpose.

| J1<br>1                        | J3         |           |     | J4        |    |

|--------------------------------|------------|-----------|-----|-----------|----|

|                                | А          | В         | С   | D         |    |

|                                | SLOT 1 Q22 | Q22 (P1)  | CD  | CD        |    |

|                                | SLOT 2 Q22 | Q22 (P2)  | CD  | CD        |    |

|                                | SLOT 3 Q22 | Q22 (P3)  | CD  | CD        |    |

| 18                             | SLOT 4 Q22 | Q22 (P4)  | Q22 | Q22 (P5)  |    |

| J2                             | SLOT 5 Q22 | Q22 (P7)  | Q22 | Q22 (P6)  |    |

| 10                             | SLOT 6 Q22 | Q22 (P8)  | Q22 | Q22 (P9)  |    |

|                                | SLOT 7 Q22 | Q22 (P11) | Q22 | Q22 (P10) |    |

| 1 2                            | SLOT 8 Q22 | Q22 (P12) | Q22 | Q22 (P13) |    |

|                                |            |           |     |           |    |

|                                |            |           | XZ1 | XZ2 XZ3 X | Z4 |

| Figure 1-3. Seahorse Backplane |            |           |     |           |    |

# Patch Panel Assembly

External option cables and serial lines connect to Seahorse through the patch panel assembly. The patch panel provides shielding for EMI and accommodates a variety of connectors by providing four inlay patch panel areas. Connectors are

1: Introduction

mounted to these patch panels, and the patch panels screw to the back of the patch panel sheetmetal frame.

The four inlay patch panel areas are configured as follows:

Patch Panel 1 Two 25-pin EIA connectors and two rotary switches for baud rate selection (M8189). **Note:** The baud rate select switches are disabled. Baud rate is set by DIP switches on the data path module.

Patch Panel 2 Four 25-pin EIA connectors

Patch Panel 3

- el 3 The post between two of the patch panel areas may be removed to install three 40or 50-pin EIA connectors.

- Patch Panel 4 Two more cutouts are present to accommodate one 40- or 50-pin EIA connector each.

# System Architecture

Seahorse implements the MicroVAX architecture which is a strict subset of the VAX architecture. The MicroVAX architecture features are:

- a 4 gigabyte virtual address space

- 32-bit word size

- sixteen 32-bit general purpose registers

- 32 interrupt levels

- vectored hardware and software interrupts

- 21 addressing modes

- variable instruction size

- full memory management

- virtual to physical address translation

- page protection mechanism

- stack processing

- emulation support for the full VAX instruction set (except PDP-11 compatibility mode)

The differences between the VAX and MicroVAX architectures are as follows.

- MicroVAX supports a subset of VAX data types:

- no D\_floating data type

- no H\_floating data type

- no octaword data type

- no numeric string data types

- no packed decimal data type

- MicroVAX supports a subset of the VAX instruction set and provides emulation support for nonimplemented instructions (except compatibility mode):

- no decimal string instructions

- no character string instructions (except LOCC, MOVC3, MOVC5, SCANC, SKPC, and SPANC)

- no EDITPC or CRC instructions

- no compatibility mode instructions

- no D\_floating or H\_floating instructions

1: Introduction

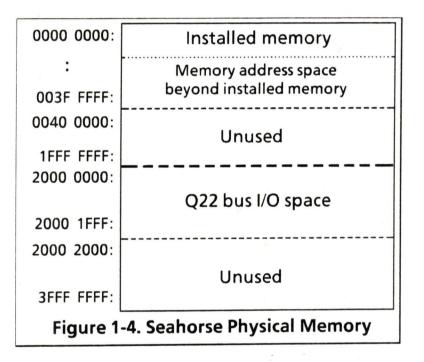

MicroVAX physical addresses can be up to 30 bits long. A physical address on Seahorse is 23 bits long, allowing a physical address space of eight megabytes; four megabytes are in memory space (low-addressed half), and four megabytes are in I/O space (high-addressed half).

• MicroVAX supports a subset of VAX processor registers. The following eleven internal processor registers (IPRs) are not implemented by the MicroVAX architecture:

| interval clock control/status<br>register |

|-------------------------------------------|

| next interval count register              |

| interval count register                   |

| time of year register                     |

|                                           |

| RXCS  | console receive control<br>status       |

|-------|-----------------------------------------|

| RXDB  | console receive data buffer             |

| TXCS  | console transmit control<br>status      |

| TXDB  | console transmit data buffer            |

| TBIS  | translation buffer invalidate<br>single |

| PMR   | performance monitor enable              |

| TBCHK | translation buffer check                |

Of these eleven IPRs, Seahorse implements the following six as defined by the VAX architecture:

| RXCS | console receive control<br>status    |

|------|--------------------------------------|

| RXDB | console receive data buffer          |

| TXCS | console transmit control<br>status   |

| TXDB | console transmit data buffer         |

| TBIS | translation buffer invalidate single |

TBCHK translation buffer check

Seahorse implements the following registers uniquely:

| ICCS  | interval clock control/status<br>register |

|-------|-------------------------------------------|

| CADR  | cache disable                             |

| MCESR | machine check error<br>summary            |

1: Introduction

# IORESET initialize bus

The differences between the VAX and MicroVAX architectures have been pointed out here. For more information about the VAX architecture, see the VAX Architecture Handbook, EB-19580-20.

# System Timing

The Seahorse system clocks are generated on the CPU memory controller module (MCT). A basic clock with a 64 Mhz frequency is generated by a crystal oscillator. All the other clocks in the data path (DAP) and memory controller (MCT) modules are derived from this basic clock.

The system clock (CPU CLOCK H) has a symmetrical 250 nanosecond period. The start of a microcycle is defined as occurring on the leading edge of this clock and is referred to as T0. The trailing edge of the clock occurs 125 ns later.

microprogrammed Seahorse is а pipelined, machine. The basic microcycle is 250 ns, and the pipeline is one deep. A new microinstruction is accessed every 250 ns, and requires two 250 ns The first 250 ns is microcycles to complete. DECODE, and the second 250 ns is EXECUTE. of the first microcycle EXECUTE The microinstruction is overlapped with the DECODE microcycle of the next microinstruction. Thus, one microinstruction is retired every 250 ns. This timing is illustrated in Figure 1-5.

17

1: Introduction

# System Bus Summary

The system buses which interconnect the modules in the Seahorse system are the memory data bus (MDB), the memory control bus (MCB), and the extended LSI-11 bus (Q22 bus). (Those buses that are completely contained within a module are not discussed in this section.)

The memory data bus and the memory control bus connect the two CPU modules (DAP and MCT). The memory data bus is implemented using an over-the-top 50-pin cable. It is a 32-bit bidirectional data bus. The 8-bit memory control bus is implemented using the CD interconnect on the backplane. The remaining lines on the CD interconnect are used for clock distribution, status, and miscellaneous control logic. Slots 1 and 2 on the backplane are reserved for the two CPU modules as both must be placed in Q22/CD slots (see Figure 1-3).

The Q22 bus connects the CPU to the system's peripheral I/O devices. Four basic kinds of transactions take place on the bus:

- power up/down signal sequencing

- transfer of bus mastership from the CPU to a direct memory access (DMA) device

- transfer of data between a bus master and a slave

- interrupts to the CPU

Most of the bus interface logic is located on the memory controller module. The data path module contains logic to handle power up and down signal sequencing and interrupts.

The 42 signal lines used in the Q22 bus are:

- Sixteen data/address lines—BDAL < 15:00 >

- Two address/parity lines—BDAL<17:16>

- Four extended address lines—BDAL<21:18>

- Six data transfer control lines—BBS7, BDIN, BDOUT, BRPLY, BSYNC, BWTBT

- Six system control lines—BHALT, BREF, BEVNT,BINIT, BDCOK, BPOK

- Eight interrupt control and direct memory access control lines—BIAKO/BIAKI, BIRQ4, BIRQ5, BIRQ6, BIRQ7, BDMGO/BDMGI, BDMR, BSACK

All Q22 bus signals are asserted low and negated high, except BPOK and BDCOK, which are asserted high and negated low to indicate an event such as impending loss of power.

With the exception of DMA grant and interrupt acknowledge signals, Q22 bus signals are bidirectional; that is, they can be driven or received at any point along the signal line. When driven, bidirectional signals travel from the driver to the near end terminator, and from the driver to the far end terminator. The exceptions are BIAKO L, BIAKI L, BDMGO L, AND BDMGI L.

BIAKI L (interrupt acknowledge) is received by a bus device on one pin and conditionally transmitted out on a different pin as BIAKO L to the next bus device. (The signal is not transmitted to the next bus device if the receiving bus device has the highest priority interrupt pending.)

Bus wiring connects BIAKO L as output from one device to BIAKI L as input to the next device on

1: Introduction

the bus. BDMGI L and BDMGO L form a similar priority daisy chain for Bus Mastership Grant.

Devices connect to all Q22 bus lines through high impedance receivers and gated, high current, opencollector drivers. Receivers and drivers are considered part of the bus.

For more information about extended LSI-11 bus signals and protocols, see the *Microcomputers and Memories* handbook, EB-20912-20.

This chapter presented a brief overview of the Seahorse system components. For more detail about the Seahorse system, see the Seahorse Field Maintenance Print Set. The remaining chapters describe the KD32-AA CPU.

1

ľ

1: Introduction

# Chapter 2 Functional Overview

This chapter is a functional overview of the major CPU components. The macroprogram flow is discussed using several instructions as examples.

Figure 2-1 is a high-level block diagram of the Seahorse CPU.

# **Data Path**

The data path module (M7135) contains the data path, instruction decode, microsequencer and miscellaneous logic needed to implement the MicroVAX instruction set. It is contained on a single quad-height printed circuit board and has connectors to interface to the memory controller and the console terminal.

The major data path components are:

- a 32-bit-wide data path implemented as a custom VLSI chip

- an 8K by 40-bit-wide control store

- a 13-bit-wide microsequencer

- a byte-wide internal data path which provides visibility to various processor states

- an 8K by 8-bit-wide boot PROM

- a console interface

Each of these components is discussed briefly in the following paragraphs.

25

# Data Path Chip

The execution of each microinstruction takes place in the data path chip. This 68-pin custom VLSI chip contains the main 32-bit data path. The chip is controlled by the microprogram. Twenty-one bits of the 40-bit microword control the chip operations. The chip consists of:

- a 21-bit control store register

- a 32-bit bidirectional I/O port

- two 32-bit internal buses

- a 32-bit ALU

- a 64-bit barrel shifter (32-bit output)

- forty-eight 32-bit registers

- thirty-two 32-bit constants

- a 10 ms interval timer

- two register file pointer registers

- hardware to accomplish parallel program counter and register maintenance

- hardware support for multiply

The chip is pipelined; each microinstruction requires 500 ns to execute, but microinstructions are retired every 250 ns (see Figure 1-5).

# **Control Store**

The data path microword is 40 bits wide, implemented in five 8K by 8 PROMs. This provides 8K microwords. The control store is used as follows.

Figure 2-1. CPU Block Diagram

27

| 0–4K | MicroVAX base microcode  |

|------|--------------------------|

| 4–6K | floating point microcode |

| 6–7K | console microcode        |

| 7–8K | microverify              |

### Microsequencer

The microsequencer controls the execution flow of the microcode in the CPU. It decodes the microinstructions, performs condition testing and branching, and generates the microaddress of the next microinstruction to be executed. Thus, it generates a 13-bit microaddress every 250 ns. The functions provided by the microsequencer are described further in the next chapter.

# Internal Data Bus

The internal data bus is an 8-bit-wide bus completely contained within the data path module. This bus is the interface between the main data path elements in the data path chip, and control and status information which must be available to the remainder of the machine. The internal data bus is also used during instruction decode to pass operand specifier information to the data path chip.

# **Boot PROM**

The boot PROM is 8K by 8-bits-wide, and stores the VAX macrocode necessary to boot the system. The boot PROM is accessible only to the microcode.

# **Console Interface**

The data path module contains the hardware and the microcode to provide the interface to a single

console terminal. The hardware is a standard EIA RS232 line interface. The external connection to this interface is a 10-pin Berg cable mounted on the data path board.

A UART is connected through a buffer to the internal data bus and can be read or written directly by the microcode. The baud rate is selectable from a switch pack and can be set for 300, 1200, 9600, or 19.2K baud. Both transmitter and receiver always operate at the same speed. The microcode reads the switch pack on power up and programs the UART for the selected baud rate.

# Memory Controller

The memory controller module (M7136) is the interface between the main data path and micromachine, and the Q22 I/O and memory subsystem. The memory controller is an asynchronous subsystem that provides the following services to the data path micromachine.

- The memory controller disguises the 16-bit Q22 bus data path by implementing commands that allow memory to be accessed as byte, word, or longword without regard to data alignment; I/O devices can also be accessed for byte and word data transfers without regard to data alignment.

- It controls and maintains a translation buffer and a data and instruction cache to reduce the number of memory accesses and increase the effective speed of those accesses.

- It maintains a 16-byte instruction prefetch buffer to allow data path opcode and operand specifier decodes to occur rapidly and at the

#### same time as memory accesses.

The memory controller is contained on a single quad-height printed circuit board and has connectors to interface to the data path module and the Q22 bus. The major memory controller components are:

- an 8 KB direct-mapped cache

- a 512-entry translation buffer

- a microsequencer and 1K by 64 control store

- Q22 bus interface logic.

Each of these components is discussed briefly in the following paragraphs.

# Cache

The data and instruction cache consists of a 2K by 32-bit-wide data store, and a 2K by 16-bit-wide tag store. The cache is the main element of the mechanism that transparently translates 16-bit data from the Q22 bus into 32-bit data that the data path micromachine needs. The cache also provides increased system throughput. The cache is a direct-mapped, write-through cache, and is implemented in the same 4K by 4 RAMs that contain the translation buffer.

# **Translation Buffer**

The translation buffer contains the corresponding physical addresses for recently used virtual addresses. It has a total of 512 entries: 256 entries for mapping system space addresses and 256 entries for mapping process space addresses.

# **Memory Controller Micromachine**

The memory controller micromachine consists of a 1K by 64 control store and a simple microsequencer which, in most instances, generates microaddresses directly from the previous microword. The memory controller microsequencer accepts memory request commands issued by the data path micromachine and sequences the memory controller data path to carry out the command. A wide, parallel microword allows several memory controller functions to take place at the same time.

# Q22 Bus Interface Logic

The Q22 bus interface logic allows the Seahorse CPU to communicate with the Q22 bus. Although it is physically located on the memory controller module, it is discussed as a separate controller in the next section.

# Q22 Bus Interface

The Q22 bus interface consists of a state sequencer, a write register and a read register. The sequencer handles the bus sequencing and arbitration, freeing the memory controller from this task.

Interrupts from Q22 bus devices are arbitrated according to their interrupt priority levels (IPLs), but reported to the data path module as IPL 17 (hex). Software may subsequently lower the IPL to the level of the interrupting device.

Seahorse allows only byte and aligned-word accesses to Q22 I/O space. All other attempted accesses result in a machine check. Additionally, aligned-longword writes to memory are atomic; that is, no other bus operations are allowed

2: Functional Overview

between the two 16-bit-writes executed on the Q22 bus to accomplish an aligned longword write.

Seahorse does not check parity on the Q22 bus. However, memory parity errors are reported to the CPU via the Q22 bus.

# Macroprogram Level Instruction Flow

This section takes three instructions as examples, and describes the data transfers on a macroprogram level. This should illustrate how the major functional components, described above, interact.

# No Operation

A no operation (NOP) macroinstruction is one byte long; it consists only of an opcode: 01. The following steps describe the data transfers that take place as this instruction is fetched and executed. Figure 2-2 illustrates the data paths that correspond to the steps.

- 1. The program counter (PC), located on the data path chip, contains the virtual address of the NOP instruction.

- 2. The virtual address is transferred to the memory controller along the memory data bus (MDB).

- 3. The translation buffer on the memory controller translates the virtual address to a physical address.

- 4. The physical address is sent to the cache. (It is also copied into a Q22 bus register in case the address is not in the cache and Q22 memory must be accessed to obtain the

data.) Assume a cache hit; that is, the cache contains the data for that physical address: the NOP opcode, 01.

- 5. The cache data (in this case, the instruction byte, 01) is sent through the merge/rotate logic to the prefetch logic (see Figure 2-1), and out onto the memory control bus to the IBYTE register.

- 6. From the IBYTE register, the instruction byte is sent to the decode logic and the data path microsequencer for decoding. The proper microinstructions are invoked to execute the NOP macroinstruction. The hardware on the data path chip increments the program counter (PC) by one. This cycle ends with the PC containing the virtual address of the next byte in the instruction stream; in this case, the virtual address of the next macroinstruction (because NOP is only one byte long).

2: Functional Overview 34

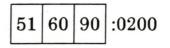

### Move Byte

A move byte (MOVB) macroinstruction copies the byte at the address specified by the first operand into the location specified by the second operand. A sample move byte instruction is: MOVB (R0), R1. This instruction means: locate the byte of data at the address contained in R0 (general processor register 0), and move it to R1 (general processor register 1). At an assigned virtual address in memory, say 0200, the instruction looks like this:

where 90 is the opcode for move byte, 60 is the operand specifier for register deferred mode specifying R0, and 51 is the operand specifier for register mode specifying R1. The following steps describe the data transfers that take place as this instruction is fetched and executed. Figure 2-3 illustrates the data paths that correspond to the steps.

- 1. The program counter (PC), located on the data path chip, contains the virtual address of the MOVB opcode (0200).

- 2. The virtual address is transferred to the memory controller along the memory data bus (MDB).

- 3. The translation buffer on the memory controller translates the virtual address to a physical address.

- 4. The physical address is sent to the cache. (It is also copied into a Q22 bus register in case the address is not in the cache and Q22 memory must be accessed to obtain the

data.) Assume a cache hit; that is, the cache contains the data for that physical address: the MOVB opcode, 90. The cache actually contains the entire MOVB instruction plus some adjacent bytes of data because each cache entry is 32 bits wide, and the address is longword-aligned.

The cache data (in this case, the entire MOVB instruction: 516090) is sent through the merge/rotate logic to the prefetch logic (see Figure 2-1). The prefetch logic actually holds up to eleven bytes at a time to facilitate rapid instruction stream decoding. From the prefetch logic, the first byte of the MOVB instruction (the opcode) is sent out the memory control bus to the IBYTE register. As the opcode is clocked into the IBYTE register, the prefetch logic drives the next instruction byte (60) onto the memory control bus.

- 6. From the IBYTE register, the opcode (90) is sent to the decode logic and the data path microsequencer for decoding. The proper microinstructions are invoked to execute the MOVB opcode.

- 7. The hardware on the data path chip increments the program counter (PC) by one. The PC now contains the virtual address of the next byte in the instruction stream; in this case, the virtual address (0201) of the first operand specifier (60).

2: Functional Overview

5.

- 8. On the next clock edge, the instruction byte sitting on the memory control bus (in this case, 60), is loaded into the IBYTE register and the prefetch logic drives the next instruction byte (51) onto the memory control bus. Since the IBYTE register now contains the next instruction byte (60), there is no need to send its virtual address (0201) from the PC to the memory controller for translation.

- 9. From the IBYTE register, the operand specifier (60) is sent to the decode logic and the data path microsequencer. The proper microinstructions are invoked to execute it.

- 10. The hardware on the data path chip increments the PC so that it now contains the virtual address (0202) of the second operand specifier, 51.

- 11. Decoding and executing the operand specifier 60 causes the contents of R0 to be examined. R0 is located on the data path chip and contains some virtual address, say 0100. The 0100 is sent over the memory data bus to the memory controller for translation.

- 12. The translation buffer on the memory controller translates the virtual address to a physical address.

- 13. The physical address is sent to the cache. (It is also copied into a Q22 bus register in case the address is not in the cache and memory must be accessed to obtain the data.) This time, assume a cache miss; that is, the cache does not contain the data at that physical

address.

- 14. The memory controller microsequencer detects the cache miss condition and informs the Q22 bus controller that a data transfer operation is needed.

- 15. Since the physical address is already conveniently stored in a Q22 bus register, the Q22 bus controller takes over and initiates two read word data transfers (DATI), sending the physical address over the Q22 bus to the memory array. (Two read word data transfers are necessary to retrieve the 32 bits needed to fill the cache.)

- 16. Two words of data at the physical address are located in the memory array and sent over the Q22 bus, one word at a time, to the Q22 bus read register on the memory controller module.

- 17. From the Q22 bus read register, the data are sent to the rotate/merge logic (see Figure 2-1). The Q22 bus read register is 16 bits wide, so as each word is read, it is passed to the rotator, rotated, and held in the merge register (the merge/rotate logic includes a rotator and a 32-bit-wide merge register). The purpose of the rotation is to position the requested byte of data (the first operand) in the low-order byte of the merge register. Once both words are latched in the merge register in the proper order, all 32 bits are written into the cache.

- 18. In parallel with the cache write operation, the two words are moved from the merge register over the memory data bus to the data path chip on the DAP module. Because

2: Functional Overview

this is a move byte instruction, only the loworder byte on the memory data bus (the first operand) is saved in the data path chip. Steps 11 through 18 have all happened as a result of the microinstructions invoked from decoding and executing the first operand specifier, 60.

- 19. Now that the byte to be moved into R1 has been obtained from memory and stored in a temporary register on the data path chip, the next instruction byte, 51, which was sitting on the memory control bus, is clocked into the IBYTE register.

- 20. From the IBYTE register, the second operand specifier (51) is sent to the decode logic and the data path microsequencer. The proper microinstructions are invoked to execute it.

- 21. Decoding and executing the operand specifier 51 causes the byte of data stored in the temporary register to be moved into R1. The move byte macroinstruction is now complete.

- 22. The hardware on the data path chip increments the PC to point at the next byte in the instruction stream (in this case, the opcode of the next instruction).

# Subtract One and Branch

The subtract one and branch on greater (SOBGTR) macroinstruction maintains a loop count and a branch address, causing the macroprogram to loop on a set of instructions a desired number of times. The loop count is decremented by 1 and a branch taken to the starting address of the loop until the

loop count is less than or equal to 0. As long as the loop count is greater than 0, the sign-extended branch displacement is added to the PC and the PC replaced by the result to cause the branch to the first instruction in the loop.

At an assigned virtual address in memory, say 0203, a SOBGTR instruction might look like this:

where F5 is the opcode for SOBGTR, 52 is the operand specifier for register mode specifying R2, and E0 is the number -32. R2 contains the loop count that is decremented each time the loop is executed. The -32 is sign-extended and added to the PC to cause the branch back to the start of the loop. Assume that the SOBGTR instruction follows right behind the MOVB instruction in the instruction stream, and that the entire SOBGTR instruction is also in the prefetch logic.

The following steps describe the data transfers that now take place as the SOBGTR instruction is fetched and executed. Figure 2-4 illustrates the data paths that correspond to the steps.

1. From the prefetch logic, the first byte of the SOBGTR instruction (the opcode, F5) is sent out the memory control bus to the IBYTE register. As the opcode is clocked into the IBYTE register, the prefetch logic drives the next instruction byte (52) onto the memory control bus.

2: Functional Overview

- 2. From the IBYTE register, the opcode (F5) is sent to the decode logic and the data path microsequencer for decoding. The proper microinstructions are invoked to execute the SOBGTR opcode.

- 3. The hardware on the data path chip increments the program counter (PC) by one. The PC now contains the virtual address of the next byte in the instruction stream; in this case, the virtual address (0204) of the first operand specifier (52).

- 4. On the next clock edge, the instruction byte sitting on the memory control bus (in this case, 52), is driven into the IBYTE register and the prefetch logic drives the next instruction byte (E0) onto the memory control bus. Since the IBYTE register now contains the next instruction byte (52), there is no need to send its virtual address (0204) from the PC to the memory controller for translation.

- 5. From the IBYTE register, the first operand specifier (52) is sent to the decode logic and the data path microsequencer. The proper microinstructions are invoked to execute it.

- 6. The hardware on the data path chip increments the PC to 0205 (the virtual address of E0, the next instruction byte), and E0 is loaded into the IBYTE register from the memory control bus.

- 7. Decoding operand specifier 52 and executing its microinstructions causes the contents of R2 to be decremented by 1, and the condition codes to be cleared (set to zeros).

:

- 8. From the IBYTE register, E0 is driven over the internal data bus (see Figure 2-1), and sign extended on the data bus. From the data bus, E0 is sent to the data path chip.

- 9. The microinstructions invoked from the opcode decode (step 5) compute the virtual address for the start of the loop as: PC + 1 + E0 = 01E6. This branch destination address is stored in a result register on the data path chip.

- Next, the condition codes are tested. Since 10. condition codes Z and N are clear, the loop count contained in R2 is still greater than 0. (Z is set when the loop count equals 0; N is set when the loop count is less than 0.) Therefore, the virtual address 01E6 stored in a result register is moved into the PC to cause the program to branch back to the beginning of the loop.

- The virtual address 01E6 is sent to the 11. memory controller over the memory data bus.

- The translation buffer on the memory 12. controller translates the virtual adddress to a physical address.

- The physical address is sent to the cache. (It 13. is also copied into a Q22 bus register in case the address is not in the cache and memory must be accessed to obtain the data.) Assume a cache hit; that is, the cache contains the instruction bytes at the physical address for the start of the loop.

- The cache data is sent through the merge-14. rotate logic to the prefetch logic. The first

2: Functional Overview

instruction byte is then sent out onto the memory control bus to the IBYTE register.

- 15. From the IBYTE register, the instruction byte is sent to the decode logic and the data path microsequencer for decoding. The proper microinstructions are invoked for executing the instruction byte.

- 16. This flow continues: moving the next byte from the instruction stream into the IBYTE register, decoding and executing it, until the opcode for the SOBGTR instruction, F5, is once again loaded into the IBYTE register. Steps 2 through 15 are repeated until the loop count, when decremented at step 7, is zero. When this occurs, condition code Z is set.

- 17. The hardware on the data path chip increments the PC to 0205 (the virtual address of E0, the next instruction byte), and E0 is driven off the memory control bus into the IBYTE register.

- 18. The microinstructions invoked from the most recent decode of operand specifier 52 compute the virtual address for the start of the loop as: PC+1+E0=01E6. This branch destination address is stored in a result register on the data path chip.

- 19. Next, the condition codes are tested. Since condition code Z is set, the loop count contained in R2 is equal to 0. Therefore, the branch destination address, 01E6, is left in the result register and *not* moved into the PC. Instead, the hardware on the data path chip increments the PC to 0206. This is the virtual address of the next byte in the

9 Subtract One and Branch

49

instruction stream; in this case, the opcode of the macroinstruction that follows the SOBGTR instruction.

20. The opcode is moved off the memory control bus into the IBYTE register, and the process of decoding and executing continues.

# Microcode

The microcode controls all the functions on both modules. Each macroinstruction in the microVAX instruction set is implemented by an associated routine of microinstructions. All of the macroinstruction data transfers described above, for example, happen as a result of their associated microinstructions.

The microinstruction routines are stored in three places: the control store on the DAP module, the control store on the MCT module for the memory controller, and the control store on the MCT module for the Q22 bus controller. The flow from one microinstruction to the next is controlled by three microsequencers, one for each control store: the data path microsequencer, the memory controller microsequencer, and the Q22 bus microsequencer. Understanding these three microsequencers and the microinstructions they execute is the key to understanding the Seahorse CPU.

The data path microsequencer and control store are the master source of control. The microinstructions in the data path control store are invoked to execute the decoded macroinstruction. The data path microsequencer controls the microinstruction flow.

2: Functional Overview

The memory controller microsequencer acts as a slave receiving commands from the data path microsequencer, performing the desired function, and delivering data or status back to the data path micromachine. The control store for the MCT microsequencer contains the microinstructions that enable the MCT microsequencer to perform the desired memory control function.

The Q22 bus microsequencer accepts commands for data from the MCT microsequencer and handles the bus sequencing and arbitration to get the requested data. The Q22 bus microsequencer returns data and status back to the MCT microsequencer. The control store for the Q22 bus microsequencer contains the microinstructions that enable the Q22 bus microsequencer to perform the desired data transfer functions.

The following chapters describe these three micromachines, and the hardware that implements and surrounds them, in detail.

# 2: Functional Overview

# Chapter 3 Data Path Microcode

All of the functions that happen in the KD32-AA CPU happen as the result of microinstructions. This chapter describes the microinstructions that run the data path module.

# **Microinstruction Format**

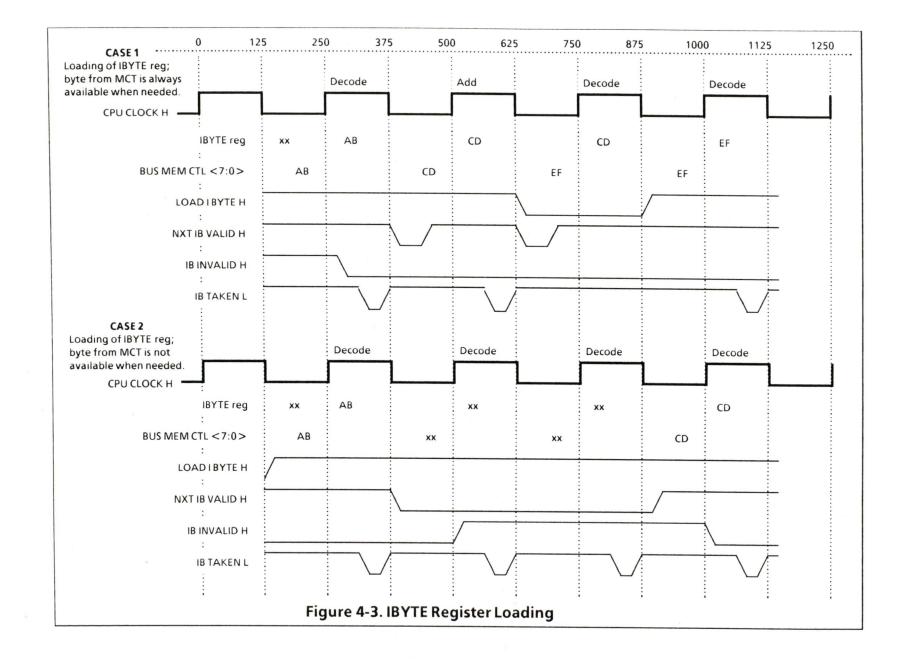

The data path microinstruction is forty bits wide. The bits are divided into four fields that accomplish different functions. These fields are parity, condition code/size control, data path control, and next address control. Memory controller functions are encoded within the data path control field.

The following sections describe each of these fields in more detail.

**Parity Field**

The highest order bit (bit 39) of the microinstruction contains the parity bit. It is used to detect single bit errors across the entire microinstruction. Odd parity is used; that is, the parity bit is a one when the sum of the one bits in the remainder of the microinstruction is even.

# **Condition Code/Data Type Field**

This field has two functions. It controls the setting of the condition codes, and it determines the data type to be used for the current operation. (Data type is also referred to as size.) Which function this field is used for in any given microinstruction depends on the purpose of the microinstruction. For example, if the microinstruction is a Move or a Moveout, bits <38:37> are interpreted as data type. If the microinstruction is an Add, this field controls the setting of the condition codes. Table 3-1 shows all the microinstruction types and which way the CC/DT field is interpreted for each.

When bits <38:37> are interpreted as the condition code field, the encoding is as follows:

| CC FUNCTION                                                        |

|--------------------------------------------------------------------|

| condition codes are<br>unaffected; data type is long               |

| set ALU condition codes;<br>data type is long                      |

| set ALU and PSL condition codes; data type is long                 |

| set ALU and PSL condition<br>codes; data type is size<br>dependent |

|                                                                    |

When bits <38:37> are interpreted as the data

type field, the encoding is as follows:

| < 38:37 > | DATA TYPE         |

|-----------|-------------------|

| 0         | byte              |

| 1         | word              |

| 2         | use size register |

| 3         | longword          |

# Data Path Control Field

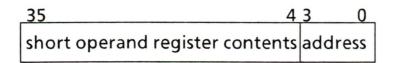

The data path control field is the 21 bits that are sent to the data path chip to control its functions. These 21 bits are also referred to as the data path chip microinstruction, or DPC microinstruction. The data path control field for all microinstructions (except Memory Requests and I-stream Requests) is divided into six function fields, as shown in Figure 3-2. (The encoding of the data path control field for Memory Request and Istream Request microinstructions is shown in Figure 3-4 later in this chapter.)

|       |    |    |    |   | 28    | 23      | 22   | 16      |

|-------|----|----|----|---|-------|---------|------|---------|

| Opcoc | de | R1 | RS | L | Short | Operand | Long | Operand |

# Figure 3-2. Data Path Control Field

The opcode field, bits <36:32>, defines the microinstruction type. Table 3-1 shows the available opcodes and their functions.

The result register bit, bit  $\langle 31 \rangle$ , selects the destination result register for the current ALU operation. The result of any ALU operation is

stored in one of two result registers on the data path chip: result register 0 or result register 1. If bit <31> is clear, the result of the current ALU operation is stored in result register 0. If bit <31> is set, the result of the current ALU operation is stored in result register 1.

The register save bit, bit  $\langle 30 \rangle$ , determines whether or not a register save operation occurs. (This is true unless the microinstruction is a NOP, Decode, Restore, Clear Save Stack, Multiply Step, I-stream Request, or Memory Request; bit  $\langle 30 \rangle$ is ignored in these microinstructions.) The data path chip contains a register save stack, which is a pushdown stack capable of holding seven 36-bit items. When bit  $\langle 30 \rangle$  is set, the contents of the register specified by the short operand plus the low 4 bits of the register address are pushed onto the register save stack. When bit  $\langle 30 \rangle$  is clear, no register save operation occurs.

The literal bit, bit  $\langle 29 \rangle$ , determines the interpretation of the short operand field. If bit  $\langle 29 \rangle$  is clear, the short operand field specifies a register. If bit  $\langle 29 \rangle$  is set, the short operand field is literal data. If the short operand is literal data, the data path chip zero-extends the data to 32 bits for use inside the chip.

The short operand field, bits <28:23>, is the first operand of the DPC microinstruction. The short operand field can specify address locations 0 to 63 and may designate a register directly or indirectly. If the literal bit is set, the short operand field is a 6bit literal value.

# Table 3-1. Opcode Assignments

| Opcode | CC/DT         | Function                | Interpretation                                                                                          |

|--------|---------------|-------------------------|---------------------------------------------------------------------------------------------------------|

| 0      | CC            | NOP                     | no operation                                                                                            |

| 1      | CC            | AND                     | dest ← short operand AND long operand                                                                   |

| 2      | CC            | OR                      | dest $\leftarrow$ short operand OR long operand                                                         |

| 3      | CC            | XOR                     | dest ← short operand XOR long operand                                                                   |

| 4      | CC            | Mask                    | dest $\leftarrow$ (NOT short operand) AND long operand                                                  |

| 5      | CC            | <b>Reverse Mask</b>     | dest $\leftarrow$ short operand AND (NOT long operand)                                                  |

| 6      | CC            | NOT                     | dest $\leftarrow$ NOT short operand                                                                     |

| 7      | CC            | <b>Reverse NOT</b>      | $dest \leftarrow NOT long operand$                                                                      |

| 8      | CC            | Add                     | $dest \leftarrow short operand + long operand$                                                          |

| 9      | CC            | Add + 1                 | dest $\leftarrow$ short operand + long operand + 1                                                      |

| 10     | CC            | Addwc                   | dest $\leftarrow$ short operand + long operand + carry                                                  |

| 11     | CC            | Sub                     | $dest \leftarrow short operand - long operand$                                                          |

| 12     | CC            | Sub - 1                 | $dest \leftarrow short operand - long operand - 1$                                                      |

| 13     | CC            | Reverse Sub             | $dest \leftarrow long operand - short operand$                                                          |

| 14     | CC            | Reverse Sub-1           | $dest \leftarrow short operand - long operand - 1$                                                      |

| 15     | CC            | Compare                 | $CCs \leftarrow short operand - long operand$ (The result registers are unaffected.)                    |

| 16     | CC            | Shift Left              | dest $\leftarrow$ long operand shift left logical by shift count register                               |

| 17     | CC            | Shift Right             | dest $\leftarrow$ long operand shift right logical by shift count register                              |

| 18     | CC            | Shift Right Arithmetic  | dest $\leftarrow$ long operand shift right arithmetic by shift count register                           |

| 19     | CC            | Double Shift            | dest ← 32 bits from 64-bit quantity formed from SOP and LOP, shift right by shift count register        |

| 20     | CC            | Shift Left Literal      | dest $\leftarrow$ long operand shift left logical by literal                                            |

| 21     | CC            | Shift Right Literal     | dest ← long operand shift right logical by literal                                                      |

| 22     | CC            | Shift Right Arith. Lit. | dest $\leftarrow$ long operand shift right arithmetic by literal                                        |

| 23     |               | reserved                | undefined                                                                                               |

| 24     | DT            | Decode                  | Decode generates a new microaddress for the current macroinstruction opcode or operand specifier.       |

| 25     | DT            | Restore                 | The top entry in the register save stack is moved to the register whose address is stored in the entry. |

| 26     | DT            | <b>Clear Save Stack</b> | All entries in the register save stack are marked as being empty.                                       |

| 27     | $\mathbf{DT}$ | Multiply Step           | Multiply Step controls the "shift and add" algorithm for multiplication.                                |

| 28     | $\mathbf{DT}$ | I-stream Request        | A memory request in which the long operand specifies IB.BYTE, IB.WORD, IB.LONG, or IB.SIZE.             |

| 29     | DT            | Move                    | Move from long operand to short operand.                                                                |

| 30     | DT            | Memory Request          | A memory request in which the long operand is the memory address of the desired data.                   |

| 31     | DT            | Move Out                | Move from short operand to an external destination specified by the long operand.                       |

The long operand field, bits  $\langle 22:16 \rangle$ , is the second operand of the DPC microinstruction. It can specify any address location that the short operand can, and in addition, specify addresses 64 to 127. Thus, the long operand can designate any internal or external register, or any constant (the constants are implemented as ROM on the data path chip).

The encodings for long and short operands are described further in the section titled "Operand Field Encoding" in this chapter.

## Next Address Control Field

The next address control field determines the next microinstruction address. As each microinstruction is retrieved from control store, the microsequencer decodes this field and generates the next microaddress. The next microaddress is used to access control store to retrieve the next microinstruction.

The control store address space is divided into 32 pages; each page is 256 words. The next address control field of some microinstructions specifies an address within the current page. Other next address control fields specify a full 13-bit address. The next address control field always has one of the nine formats shown in Figure 3-3.

A next address control field must be specified for every microinstruction. In the microcode listing, there are microinstructions with no explicit next address control field given. For these instances, an unconditional jump to the current microaddress plus 1 is supplied by default.

Six of the nine formats shown in Figure 3-3 have

jump control fields, either JC < 3:0 > or JC < 1:0 >. corresponding to next address control field bits <11:8> and <9:8>, respectively. The return format has a split jump control field, consisting of JC < 2> (bit 12), and JC < 1:0> (bits 9:8). The jump control field is used to specify conditions which are being tested by the microcode. If the condition is not met, the next microaddress is the current microaddress plus 1. If the condition is met. the next address is within the current page at the 256 word offset specified by J < 7:0>. The jump control field encoding is shown in Table 3-2. A jump control field value of 0 means there are no jump conditions to be tested and the next microaddress is conditioned only by the output of the OR MUX. (Note: A jump control field value of 0 is meaningless when the next address control field format is a branch.)

Five of the nine formats shown in Figure 3-3 use the OR field, either OR < 2:0 > or OR < 1:0 >, corresponding to next address control field bits < 12:10 > and < 11:10 >, respectively. The OR bits control the OR MUX, one of the hardware components of the data path microsequencer. The OR MUX is discussed in Chapter 4, but some information about it is called for here.