R. L. Best B-129

Page 1 of 29

Memorandum 6M-3284 Sup. #2

Division 6 – Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

# SUBJECT: DISPLAY LINE DRIVER (THEORETICAL ANALYSIS)

To: C. L. Corderman

From: Henry E. Zieman and Joseph Kriensky

Date: July 20, 1956 Approved:

C. L. Corderman

Abstract:

The orignal M note described the operation of the display line driver in general terms. The first supplement analyzed the individual stages within the amplifier thoroughly. This note combines the analysis of supplement 1 to develop the behavior of the amplifier as complete entity. Several results are obtained from the theretical analysis which are useful for adjustment of the amplifier.

The amplifier common mode square-wave response should not be adjusted for any faster response time than is absolutely necessary because of a loss in the common mode rejection properties of the amplifier.

The amplifier should not be used to drive loads under 500 ohms without an appropriate reduction of maximum output swing. Failure to do so will cause excessive power dissipation in the output tubes resulting in reduced life.

## Distribution List

\*Barrett, B. W. \*Best, R. L. \*Callahan, R. J. \*Corderman, C. L. \*Flanagan, M. J. \*Gould, R. H. \*Gurley, B. M. \*Hingston, A \*Kriensky, J. \*O'Brien, J. A. \*Paddock, R. B. \*Santlemann, W. F. \*Zieman, H. E.

IBM Building F \*Dawson, R. L. \*Delmege, J. W. \*Iannotti, J. D. \*Seeland, J. J.

Group 62 and 63 staff to recieve abstract only except as noted.

\*Recipent of complete Memorandum.

This document is issued for internal distribution and use only by and for Lincoln Laboratory personnel. It should not be given or shown to any other individuals or groups without express authorization. It may not be reproduced in whole or in part without permission in writing from Lincoln Laboratory. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No. AF 19(122)-458.

#### General

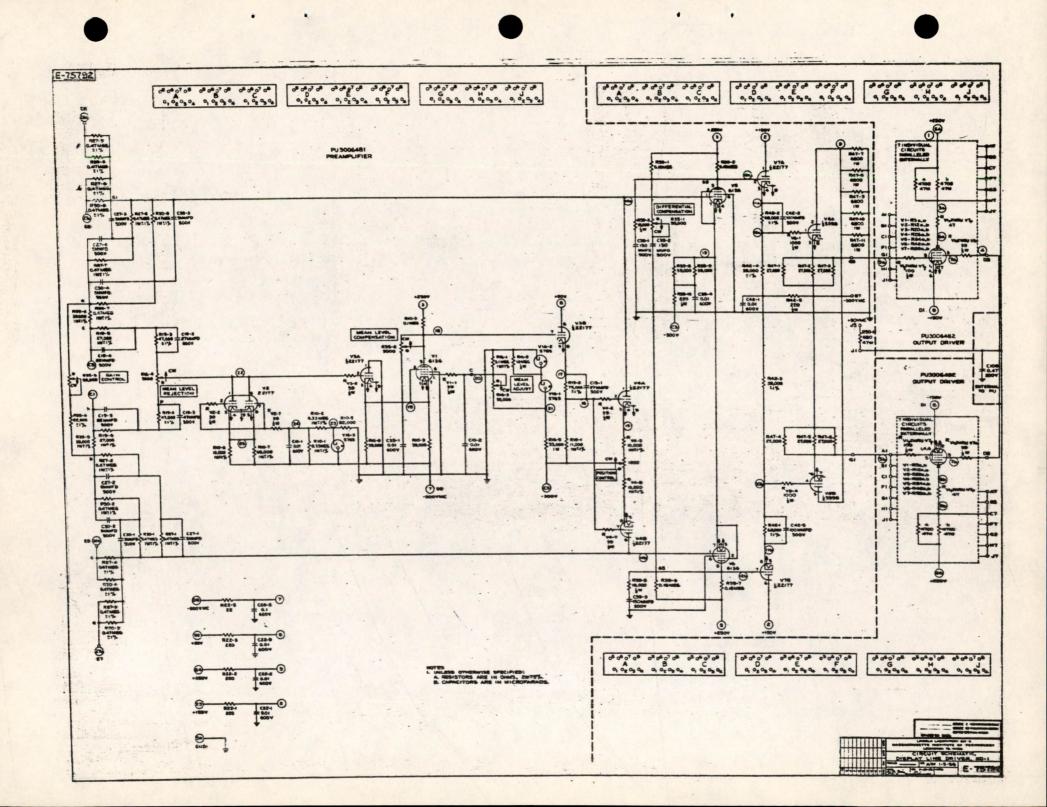

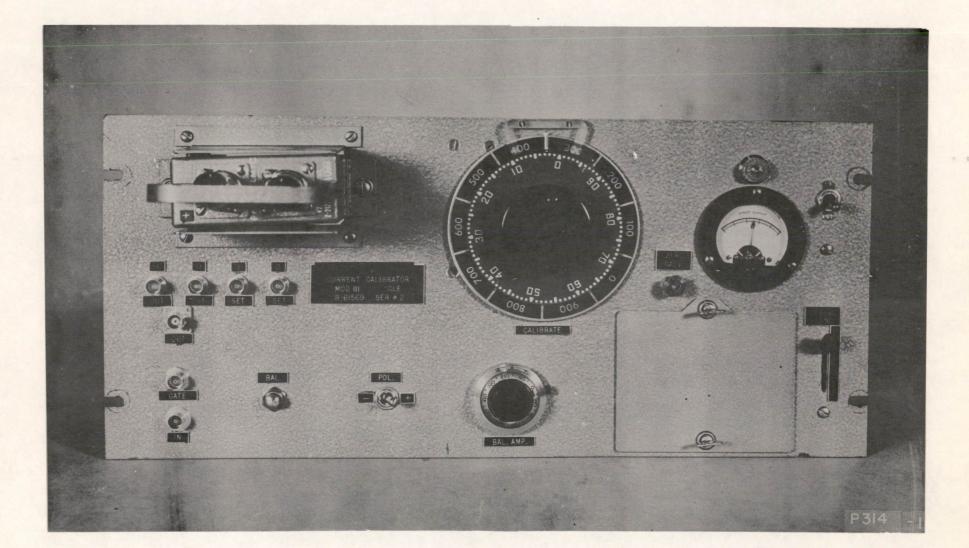

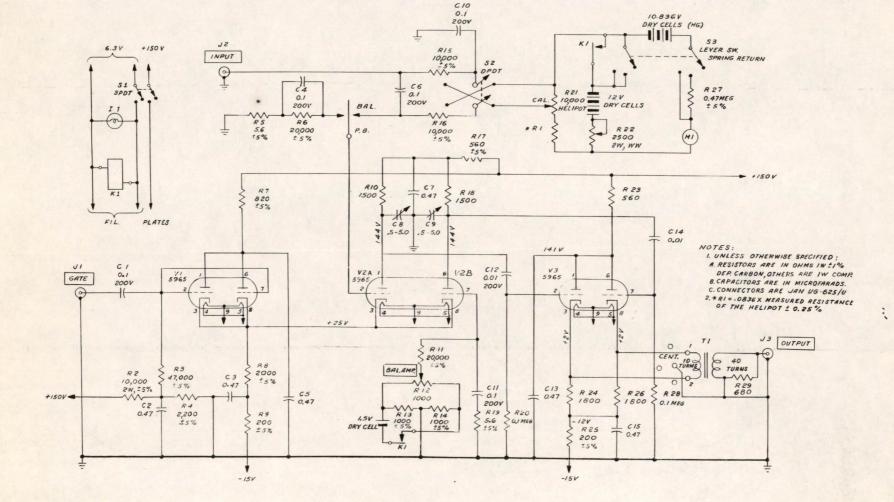

The complete line driver was described in very general terms in the original note. The first supplement described and analyzed the individual stages as separate entities. This paper analyses the complete amplifier theoretically. Drawing E75792 (Fig. 0.1) is a complete circuit schematic.

#### 1.1 Differential Mode Analysis

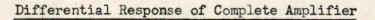

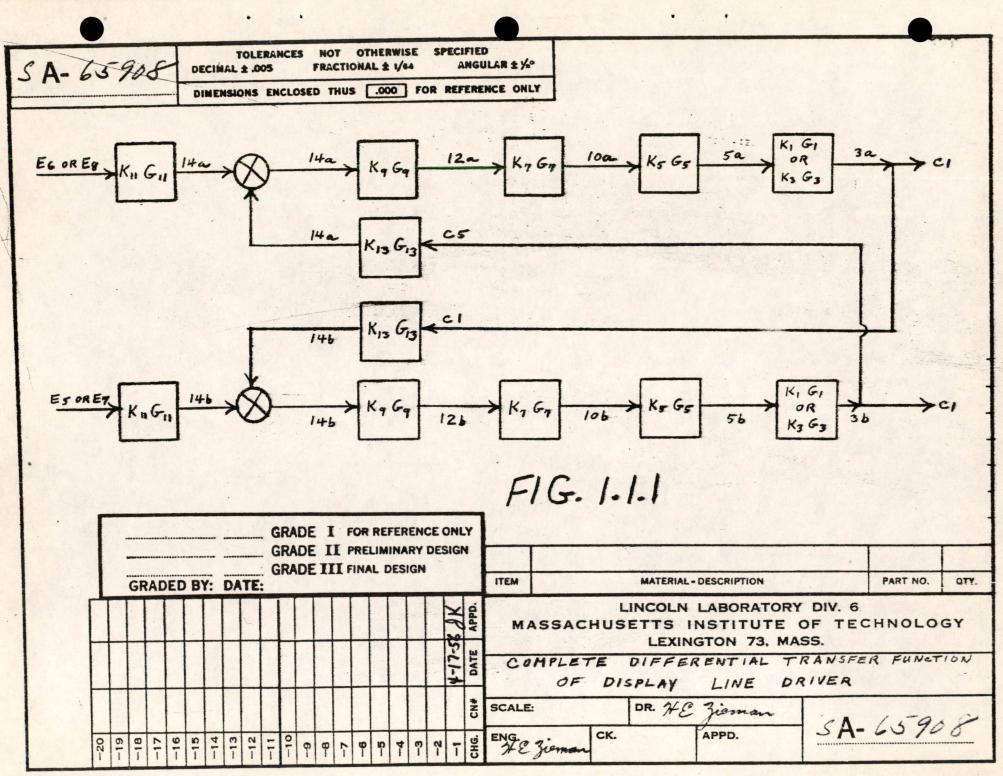

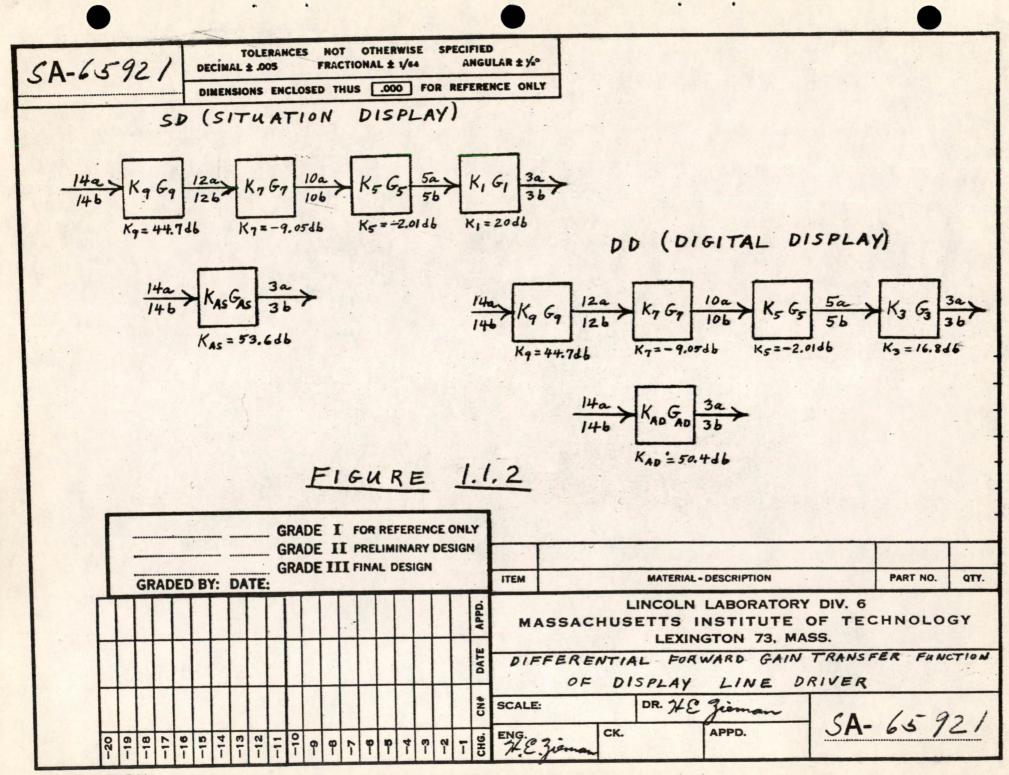

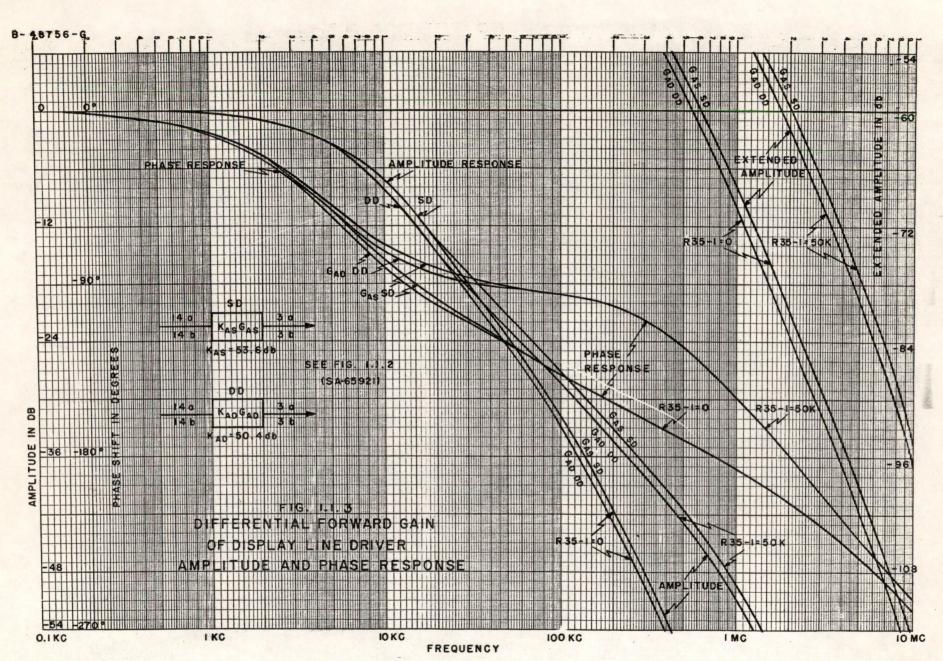

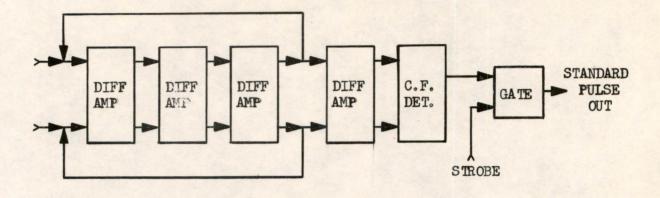

Figure 1.1.1 (SA-65908) is a block diagram showing the complete signal flow path for the differential amplifier. All KG numbers refer to previously derived transfer functions given in supplement one. The numbers and letters between the KG functions refer to corresponding voltage test points shown in E75792. If the four transfer functions in the forward path, K9 G9 (Fig. 3.4.2, supplement #1 SB-48744-G), K9 G7 (Fig. 3.3.2, supplement #1, SB-48743-G), K5 G5 (Fig. 3.2.2, supplement #1, SB-48742-G), and K1 G1 or K3 G3 (Fig. 3.1.2, supplement #1, SB-48741-G), are multiplied together (db magnitudes and phase angles added) as shown in Fig. 1.1.2 (SA-65921), they can be replaced by a single forward gain transfer function KA GA. Since the transfer function of the output stage differs for SD and DD, two separate functions are required and will be differentiated by a second subscript, KAS GAS for SD and KAD GAD for DD. Figure 1.1.3 (B-48756-G) is a plot of these two transfer functions.

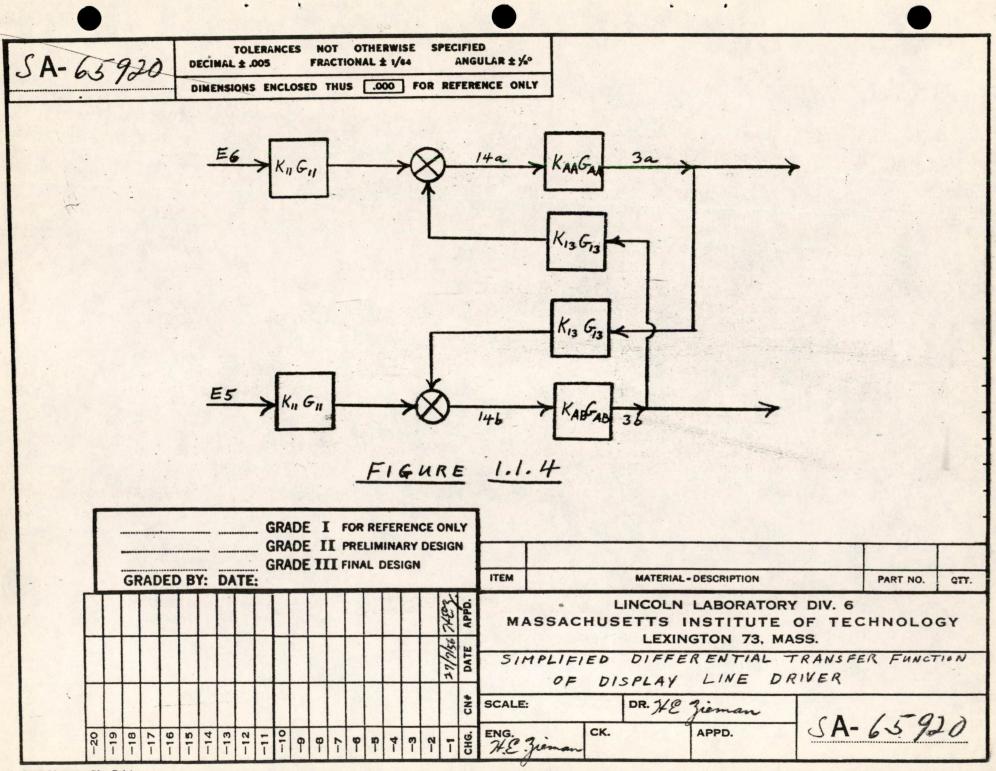

Figure 1.1.4 (SA-65920) repeats Figure 1.1.1 with the simplified forward gain transfer function. It can be shown for this diagram (see Eq. A-11) that the overall differential transfer function is:

Eq. 1.1.1

$$K G_{DIFF} = \frac{K_{II} G_{II} K_A G_A}{I + K_{I3} G_{I3} K_A G_A}$$

This function can more easily be evaluated if it is rewritten as:

Eq. 1.1.2

$$K G_{DIFF} = \frac{K_{II} G_{II} K_B G_B}{K_{I3} G_{I3}}$$

where

Eq. 1.1.3

$$K_B G_B = \frac{K_{I3} G_{I3} K_A G_A}{I + K_{I3} G_{I3} K_A G_A}$$

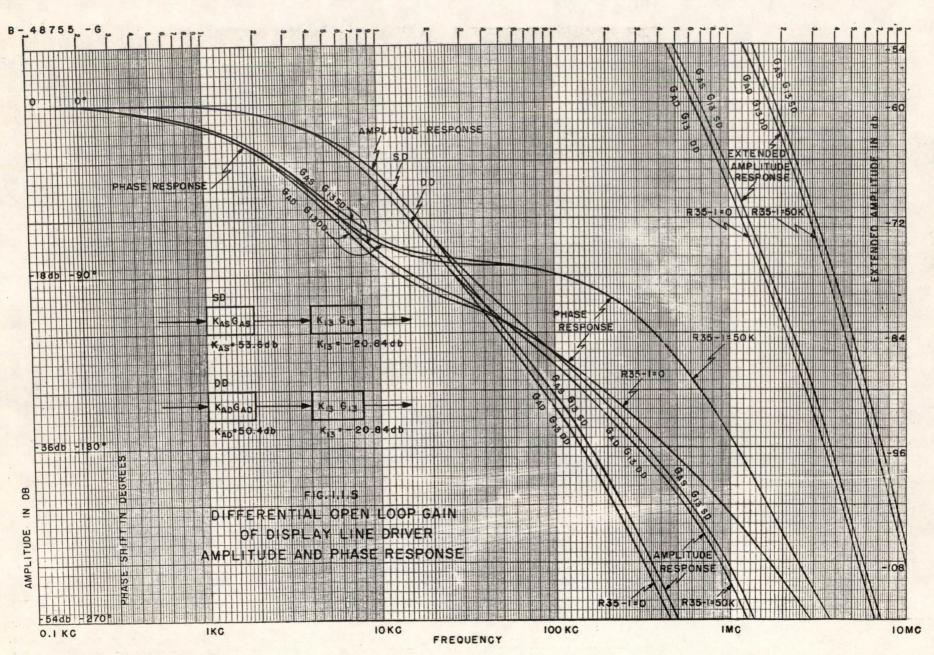

The function  $K_{13}$  G<sub>13</sub>  $K_A$  G<sub>A</sub>is the differential open loop gain of the line driver and is plotted in Fig. 1.1.5 (B-48755-G). It is obtained by multiplying the separate  $K_{13}$  G<sub>13</sub> and  $K_A$  G<sub>A</sub> functions (db magnitudes and phase angles of Fig. 3.5.2 supplement #1, SB-48754-G, and Fig. 1.1.3 of this supplement added together).

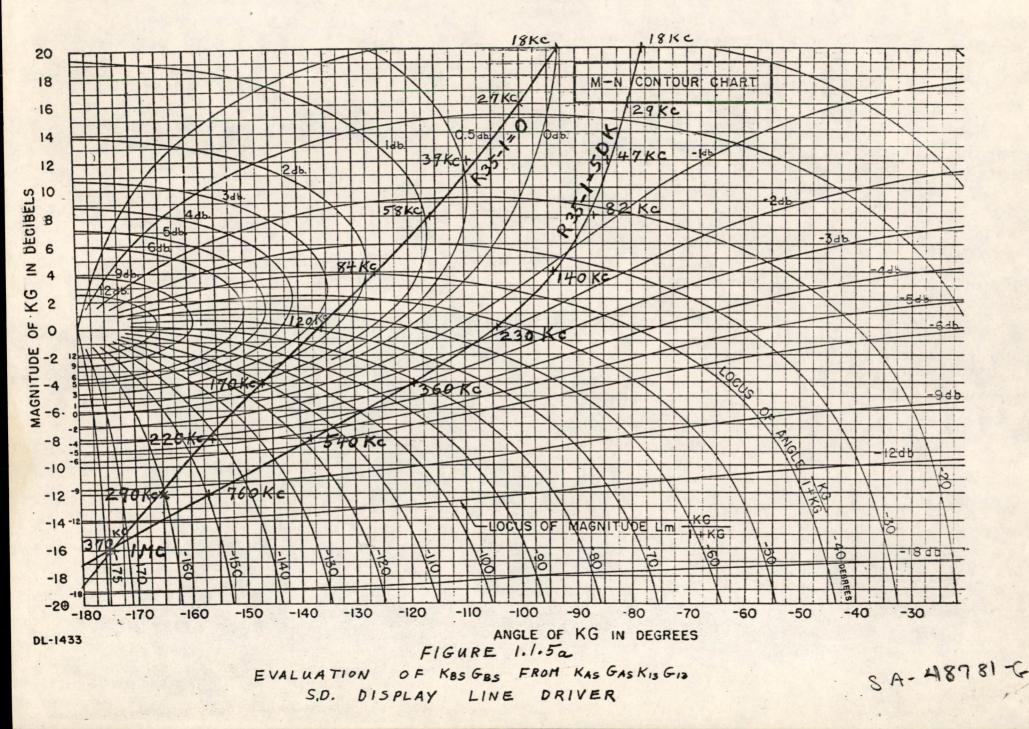

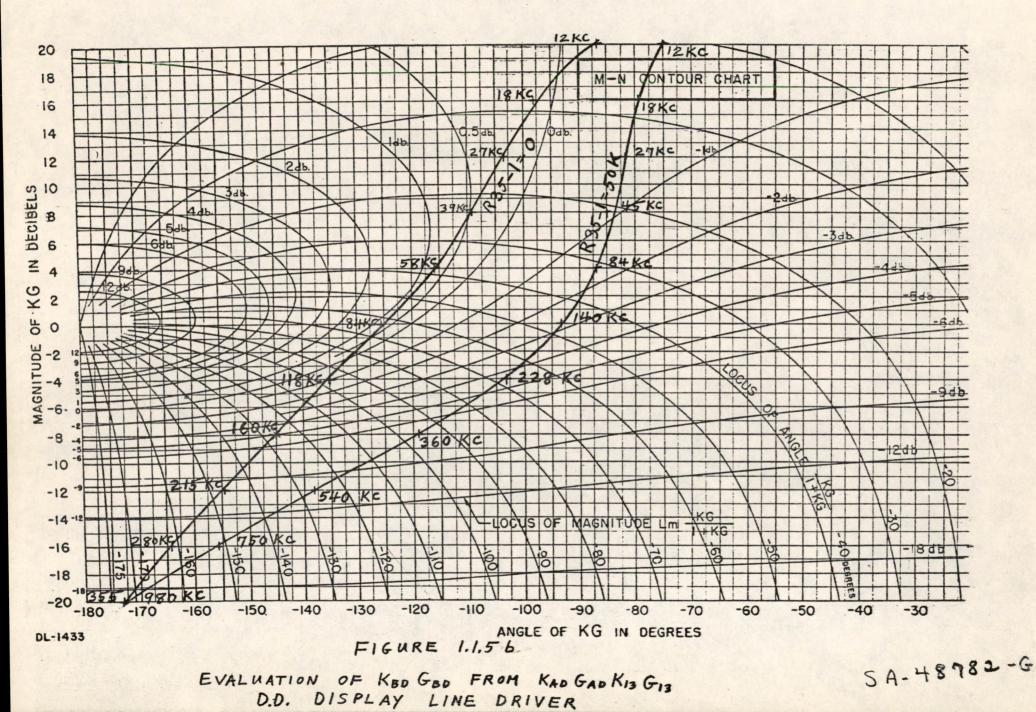

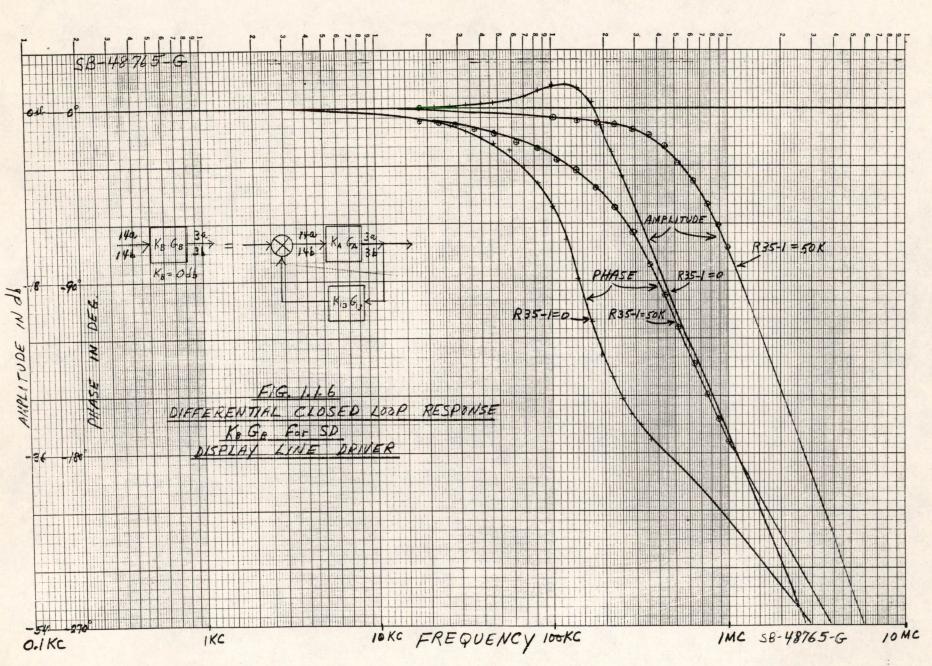

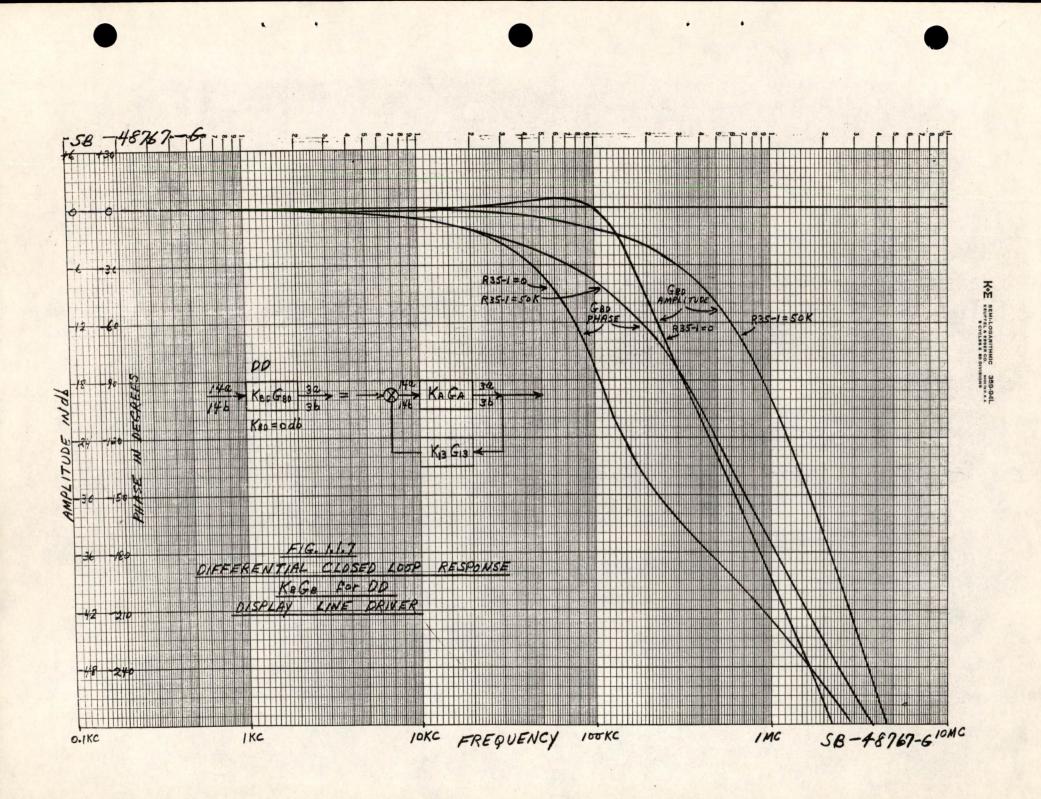

The function  $K_B G_B$  is the differential closed loop response of the line driver and is plotted in Fig. 1.1.6 (SB-48765-G) for SD, and Fig. 1.1.7 (SB-48767-G) for D.D. This function is obtained by plotting  $K_{13} G_{13} K_A G_A$ on an M-N contour chart Fig. 1.1.5a (SA-48781-G) and Fig. 1.1.5b (SA-48782-G) and replotting from a new set of coordinates the function K<sub>B</sub> G<sub>B</sub> (the M-N contour chart DL-1433 permits the graphical evaluation of the function A when A is known graphically as a complex variable).

1 + A

Page 3

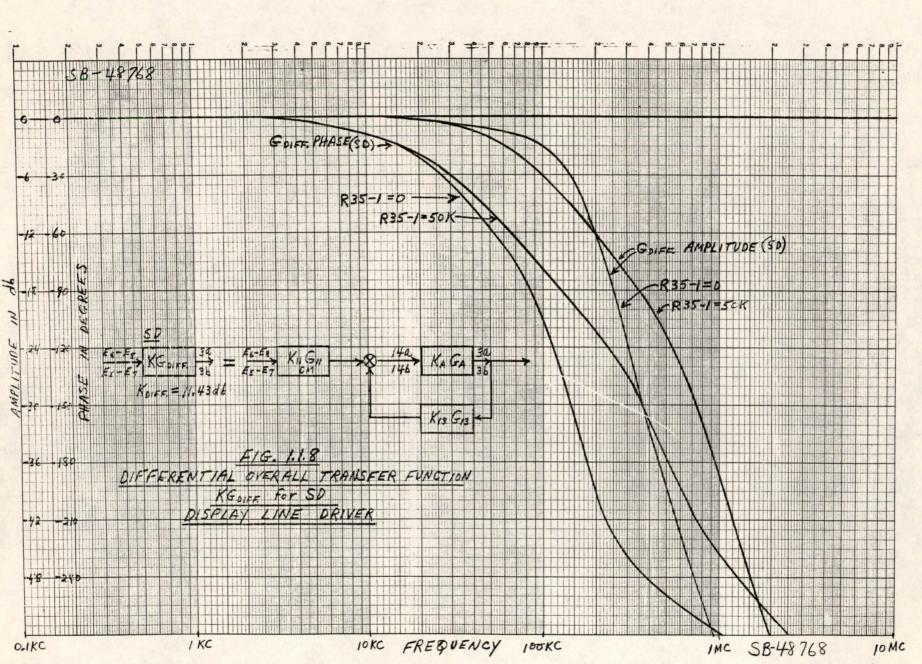

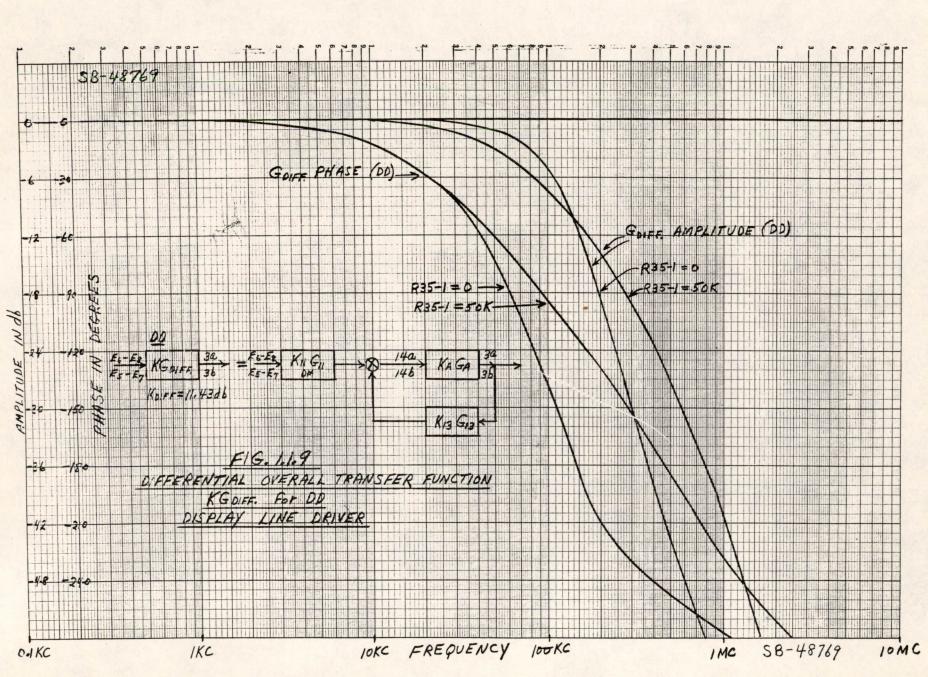

On Fig. 3.5.2 supplement #1, SB-48754-G the curves for G13 are subtracted from the curves for G11 and the results added to KB GB (Figs. 1.1.6 or 1.1.7 of this supplement). The result is the overall transfer function KGDIFF (Eq. 1.1.2) which is plotted in Fig. 1.1.8 (SB-48768-G) for SD, and Fig. 1.1.9 (SB-48769-G) for DD. It will be noticed that the addition of the input characteristic  $K_{11} \ G_{11}/K_{13} \ G_{13}$  decreased the frequency response of the total differential amplifier.<sup>3</sup> The addition of speed-up capacitors across the input resistors R3, R4, R11 and R12 in Fig. 3.5.1 of the first supplement could have caused a rising characteristic in the vicinity of 100KC and extended this frequency response. This was not done in the present amplifier because non-linearities (discussed in section 1.3 of this supplement) cause a considerable peaking of the frequency response in this vicinity under certain differential input conditions and the addition of the speed-up capacitors would have accentuated the peaking more severely. Although a slight peaking is desirable to speed-up the square-wave response of the amplifier, too severe a peaking causes undesirable ringing of the square wave. R35-1 is supplied to control the roll-off of the frequency response and thus control the rise time characteristic of a square-wave response.

# 1.2 Common Mode Analysis

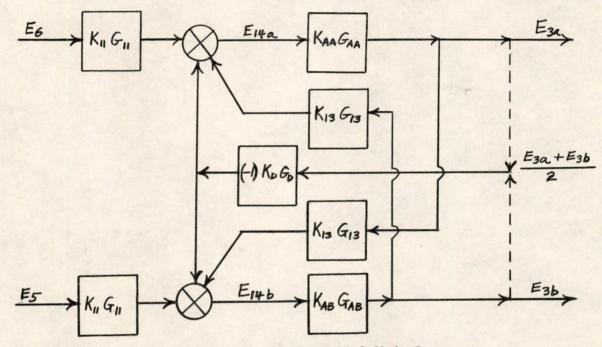

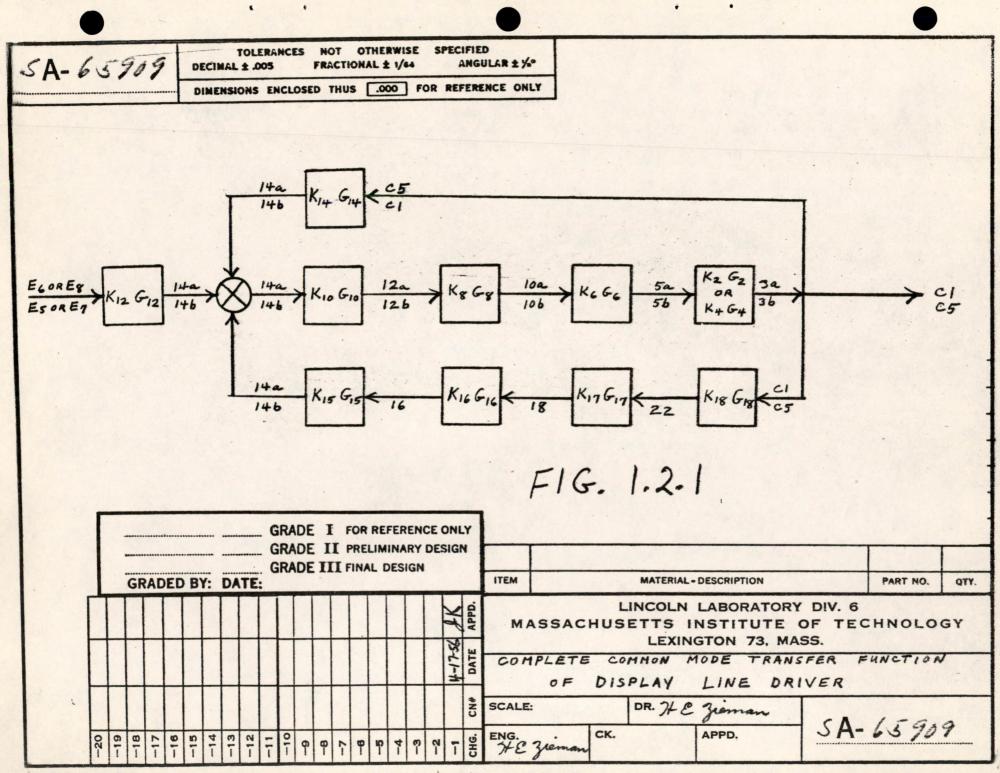

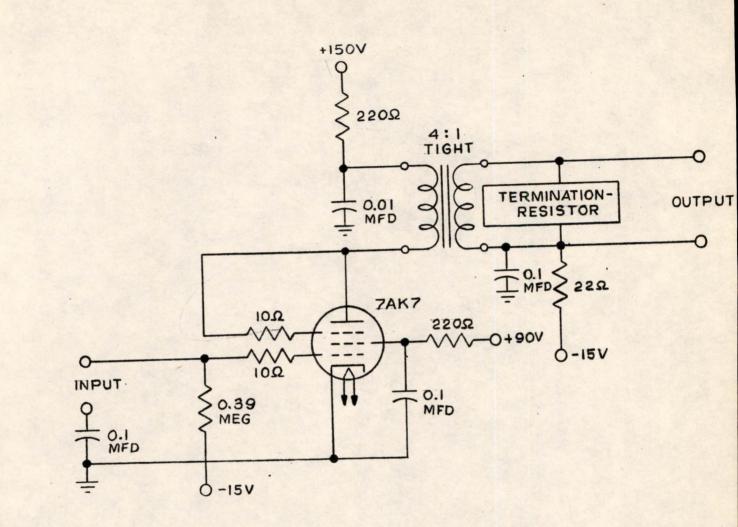

Fig. 1.2.1 (SA-65909) is a block diagram showing the complete signal flow path for the common mode response of the line driver. As in section 1.1 all KG numbers refer to transfer functions derived in supplement one, and numbers and letters between KG functions refer to voltage test points on E75792.

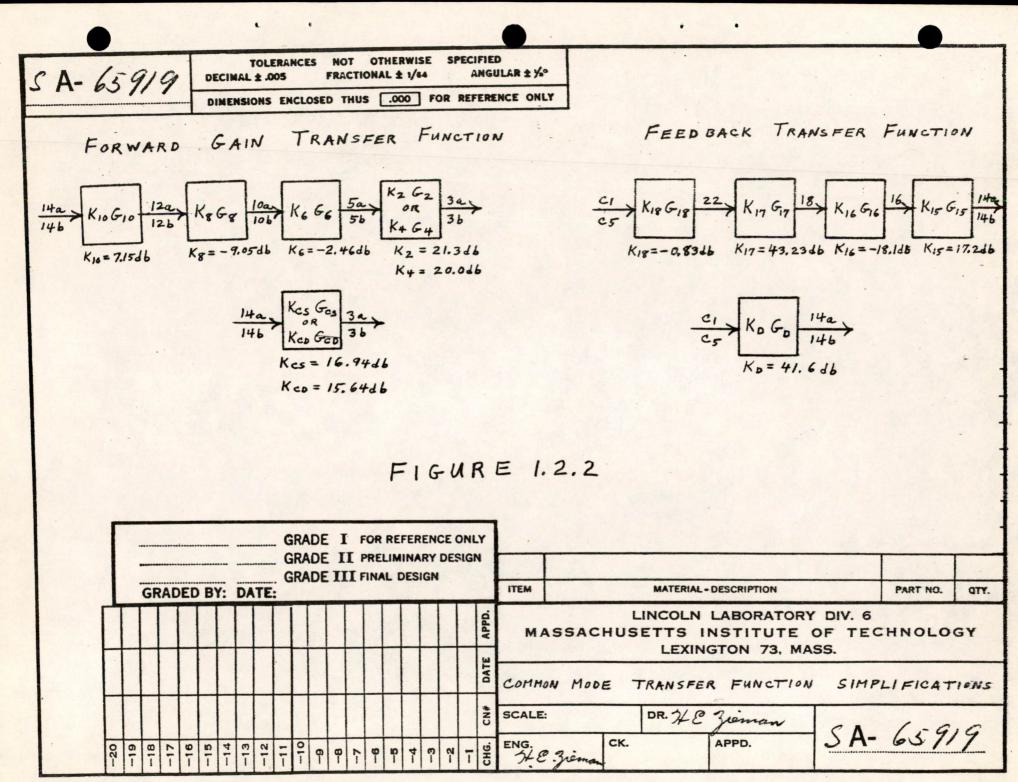

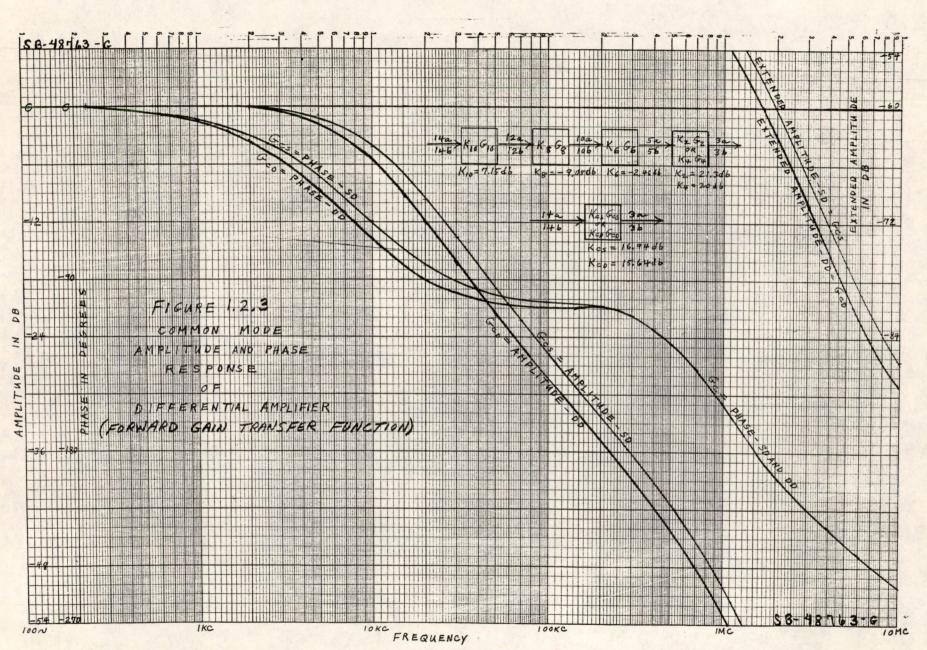

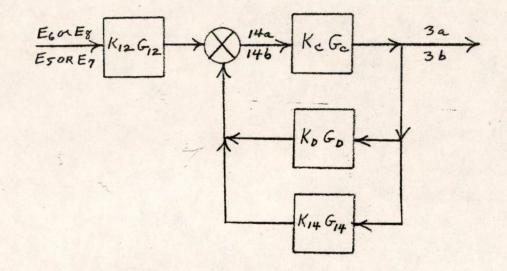

Fig. 1.2.2 (SA-65919) shows two simplifications which can be made in the complete diagram. The four transfer functions in the forward gain can be combined to a single forward gain transfer function K<sub>C</sub> G<sub>C</sub> (K<sub>10</sub> G10 Fig. 3.4.3 supplement #1, SB-48745-G, K8 G8 Fig. 3.3.2 supplement #1, SB-48743-G; K<sub>6</sub> G<sub>6</sub> Fig. 3.2.2 supplement #1, SB-48742-G; and K<sub>2</sub> G<sub>2</sub> or K<sub>4</sub> G<sub>4</sub> Fig. 3.1.2 supplement #1, SB-48741-G). This new function (K<sub>C</sub> G<sub>C</sub>) is plotted in Fig. 1.2.3 (SB-48763-G). Since this function differs for the type of display the amplifier is used for, a second subscript is added to differentiate for the two uses. Thus K<sub>CS</sub> G<sub>CS</sub> is the forward gain transfer function for SD, and K<sub>CD</sub> G<sub>CD</sub> for DD.

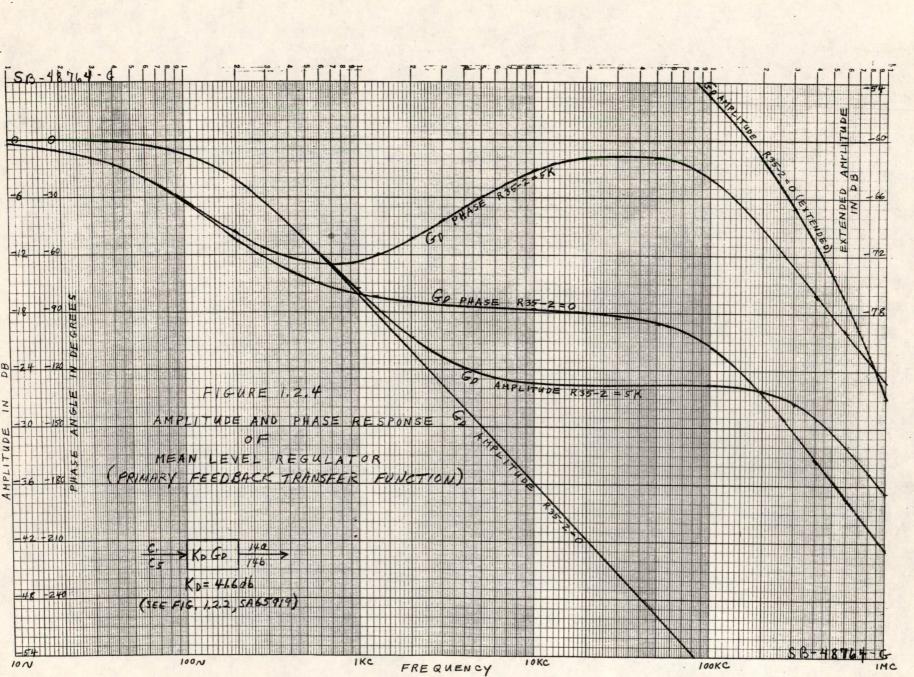

The second simplification is obtained by combining the four feedback transfer functions into a single function Kp Gp (K18 G18 Fig. 3.8.2 supplement #1, SB=48759-G; K17 G17 Fig. 3.7.2 supplement #1, SB=48758-G; K16 G16 Fig. 3.6.2 supplement #1, SB=48757-G: and K15 G15 Fig. 3.5.3 supplement #1, SB=48753-G). This function is plotted in Fig. 1.2.4 (SB=48764-G).

Fig. 1.2.5 (SA-65925) is the simplified common mode transfer diagram of the line driver. The overall common mode transfer function for this circuit (see appendix B, Eq. B-12 is)

Eq. 1.2.1

$$KG_{cm} = \frac{K_{12} G_{12} K_c G_c}{1 + K_c G_c (K_b G_b - K_{14} G_{14})}$$

#### Page 4

This transfer function can be solved more easily if it is rewritten:

Eq. 1.2.2

$$K G_{cm} = \frac{K_{12} G_{12} K_E G_E}{K_F G_F}$$

where

Eq. 1.2.3

$$K_E G_E = \frac{K_F G_F K_C G_e}{1 + K_E G_F K_C G_e}$$

and

Eq. 1.2.4

$$K_F G_F = K_D G_D - K_{14} G_{14}$$

Several methods are available for evaluating  $K_F G_F$ . The most obvious, and most time consuming, would be to obtain both  $K_D G_D$  and  $K_{14} G_{14}$  algebraically from their composite equations from suplement #1. The second method would consist of evaluating  $K_D G_D$  and  $K_{14} G_{14}$  at several points from their graphs, obtaining their vector difference and replotting. The method chosen was a strict graphical manipulation. If equation 1.2.4 is rewritten in the form:

Eq. 1.2.5

$$K_F G_F = \frac{K_P G_P}{K_H G_H}$$

where

Eq. 1.2.6

$$K_H G_H = \frac{(-K_0 G_0/K_{14} G_{14})}{1 + (-K_0 G_0/K_{14} G_{14})}$$

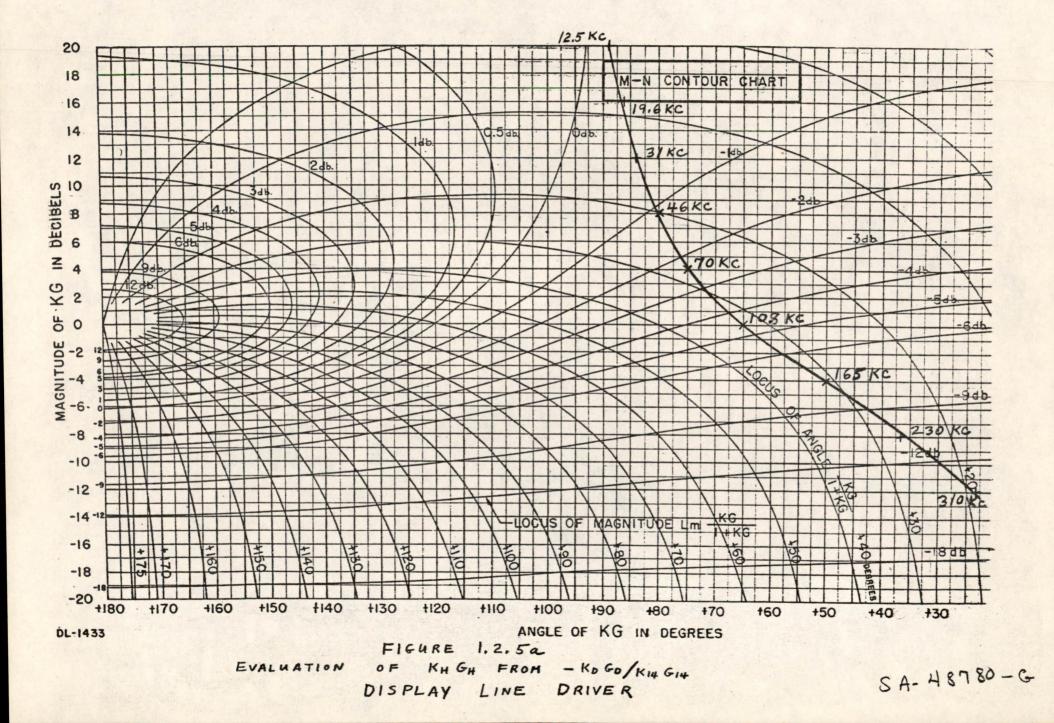

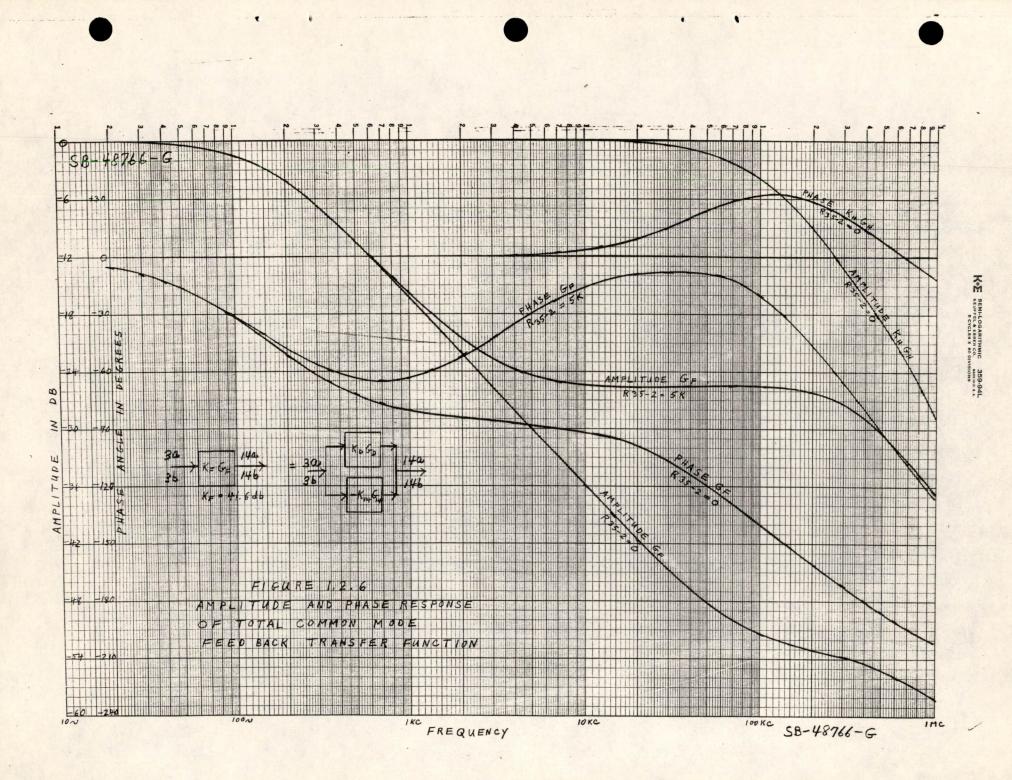

the entire solution can be obtained graphically. First the curve for K14 G14 (Fig. 3.5.4 supplement #1, SB-48762-G) is subtracted from KD GD (Fig. 1.2.4 of supplement #2 SB-48764-G) and the phase angle shifted +180°. This gives -KD GD / K14 G14. This curve is transferred to an M-N contour chart (Fig. 1.2.5a SA-48780-G) and K<sub>H</sub> G<sub>H</sub> is read off directly. Since KD GD is much greater than K14 G14 in the region below one megacycle for R35-2 equal to five kilohms, K<sub>H</sub> G<sub>H</sub> is approximately unity for this band. For R35-2 equal to zero KD GD does approach K14 G14 within this band and there is some interaction between the positive feedback of K14 G14 and the negative feedback of KD GD. This causes a variation in the gain and phase of K<sub>H</sub> G<sub>H</sub> in the vicinity where this happens. The resultant K<sub>H</sub> G<sub>H</sub> are then subtracted from KD GD and the result is K<sub>F</sub> G<sub>F</sub> (also plotted in Fig. 1.2.6) for the two extreme values of R35-2.

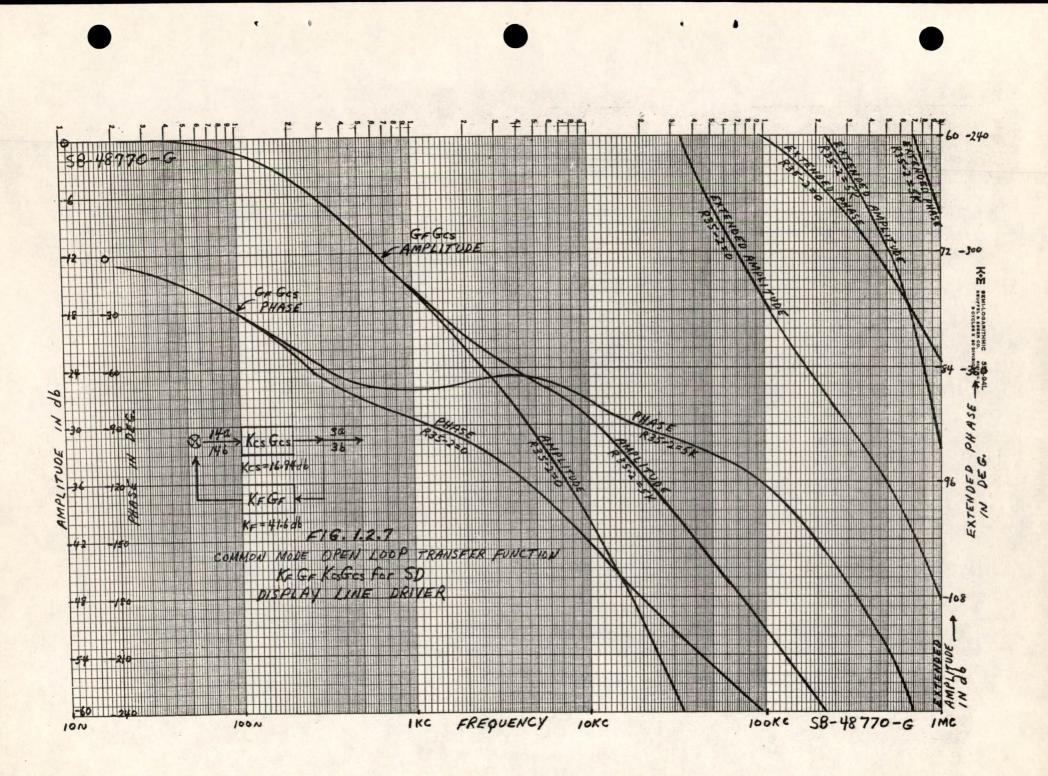

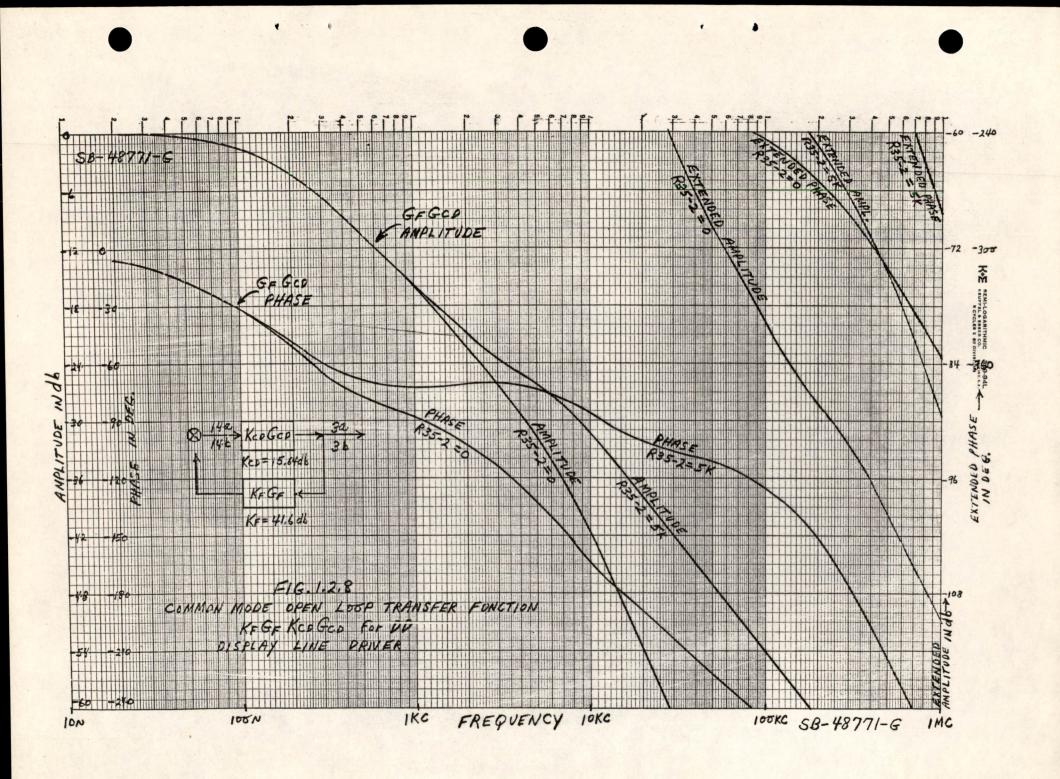

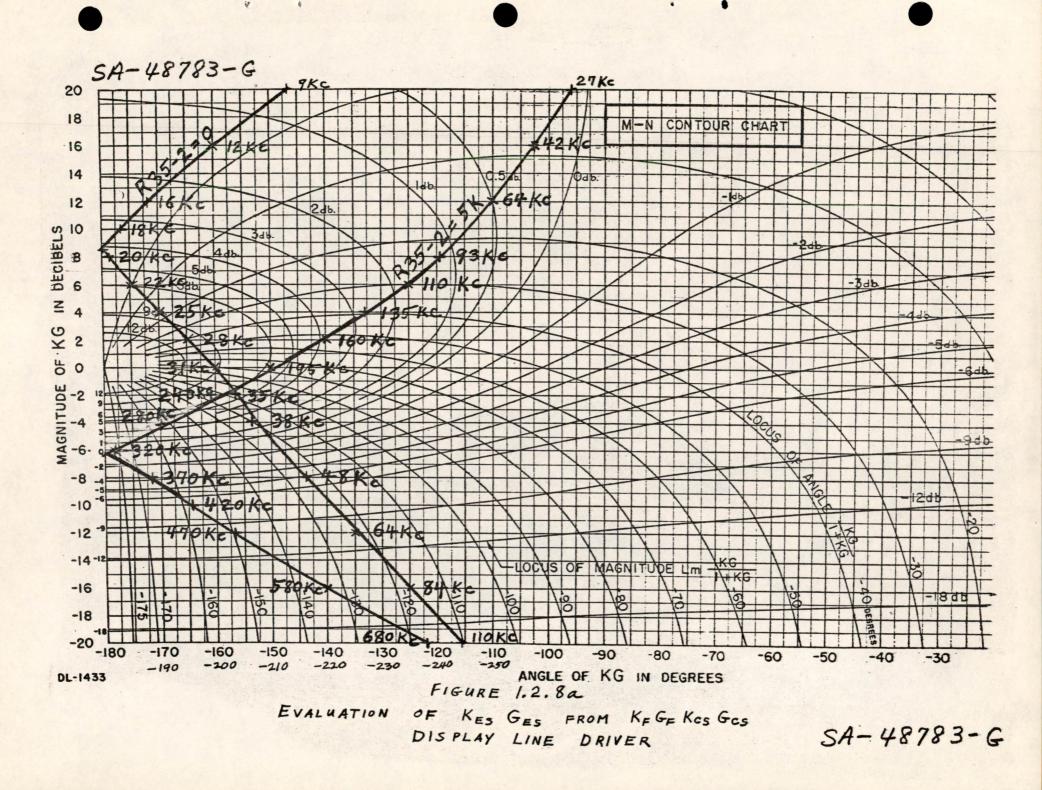

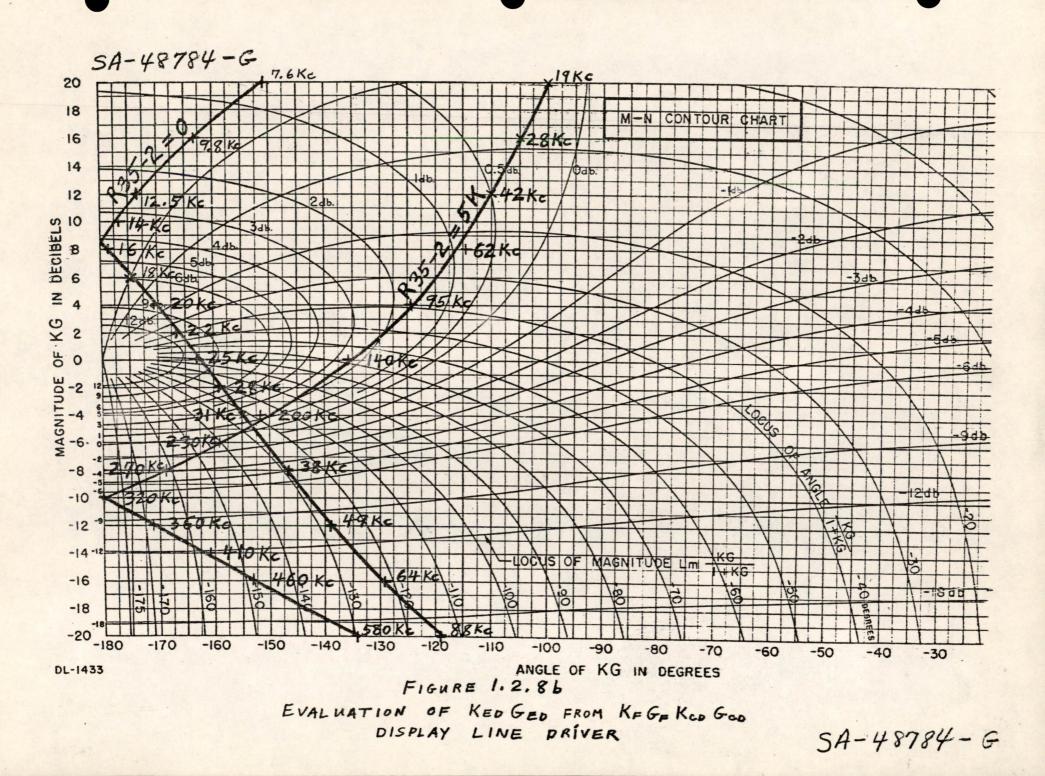

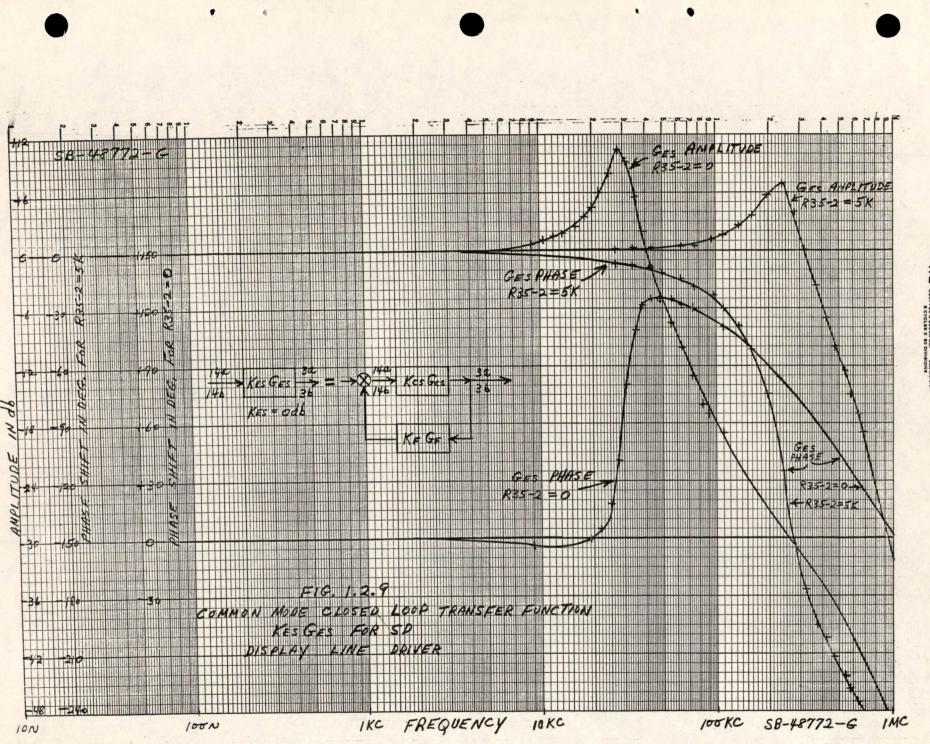

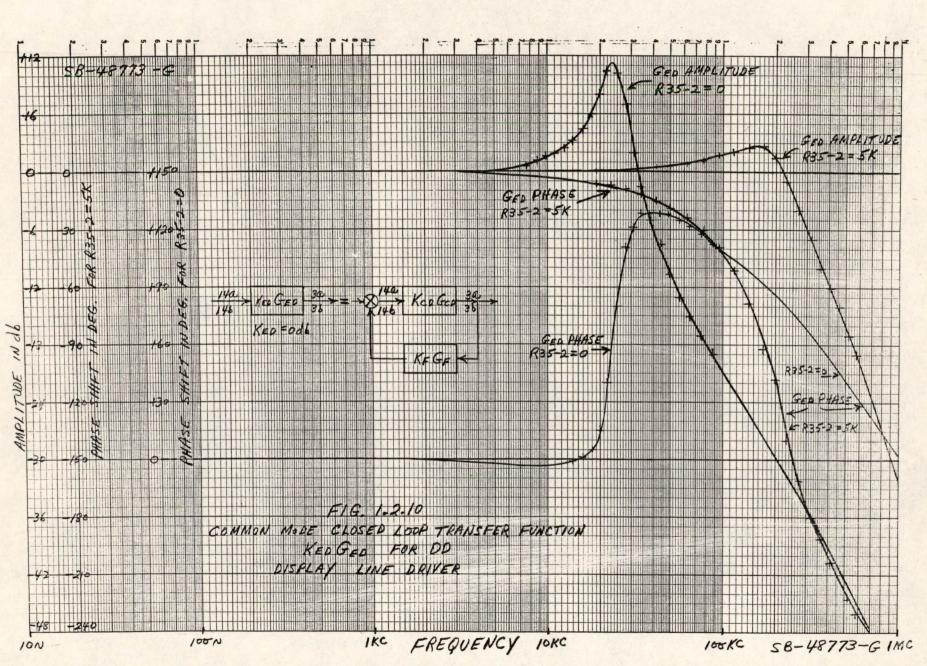

$K_E G_E$  (Eq. 1.2.3) is obtained by first adding the curves for  $K_F G_F$ (Fig. 1.2.6) and  $K_C G_C$  (Fig. 1.2.3) to obtain the product  $K_F G_F K_C G_C$ .  $K_F G_F K_{CS} G_{CS}$  is plotted in Fig. 1.2.7 (SB-48770-G) and  $K_F G_F K_{CD} G_{CD}$  is plotted in Fig. 1.2.8 (SB-48771-G). These product curves are next transferred to the M-N contour charts Fig. 1.2.8a SA-48783-G and Fig. 1.2.8b SA-48784G and separate curves for  $K_E G_E$  replotted.  $K_{ES} G_{ES}$  for SD is plotted in Fig. 1.2.9 (SB-48772-G), and  $K_{ED} G_{ED}$  for DD is plotted in Fig. 1.2.10 (SB-48773-G).

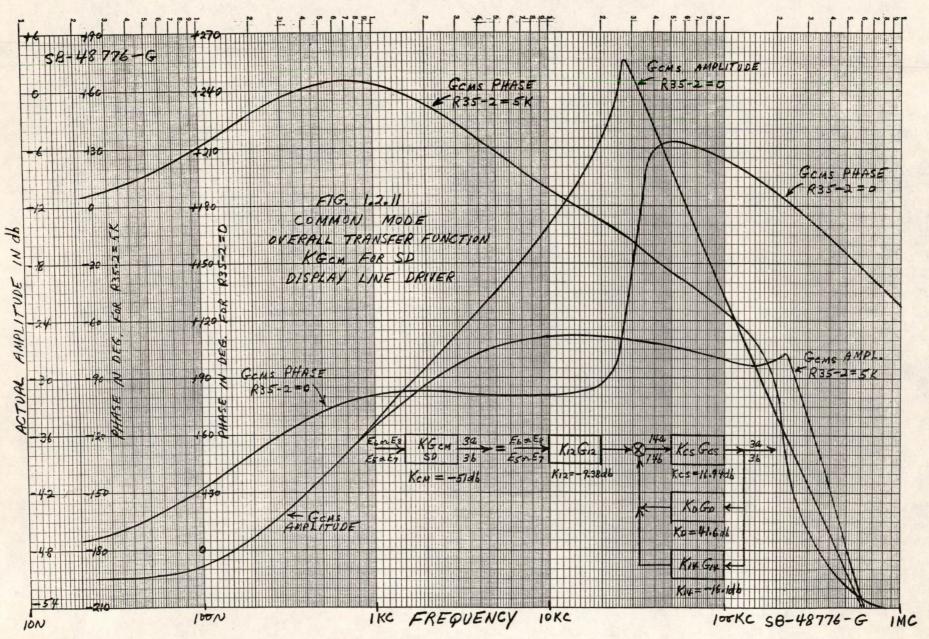

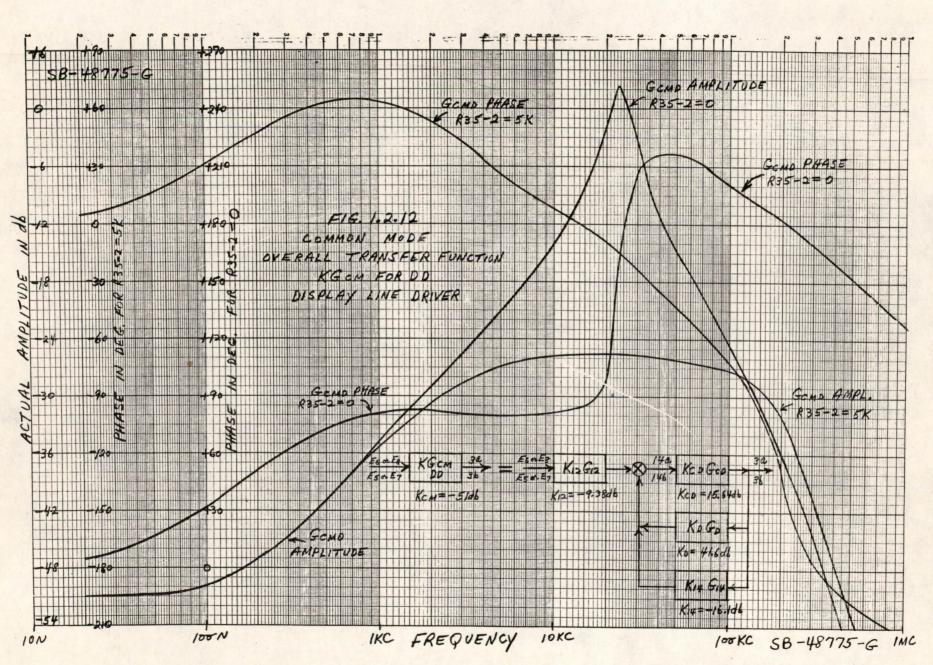

The overall transfer function for the common mode,  $KG_{cm}$ , is finally obtained by adding the curves for  $K_{12}$  G<sub>12</sub> (Fig. 3.5.4 supplement #1, SB-48762-G) and  $K_E$  G<sub>E</sub> (Fig. 1.2.9 or 1.2.10, and subtracting the curve

Page 5

for  $K_F G_F$  (Fig. 1.2.6). The two overall transfer functions (one for SD and one for DD) are plotted separately in Figs. 1.2.11 (SB-48776-G), and 1.2.12 (SB-48775-G).

In Figs. 1.2.8a and 1.2.8b it will be noticed that when R35-2 is set to zero, the gain of  $K_F \ G_F \ K_C \ G_C$  is greater than unity as the phase shift crosses the 180° axis. This indicates that the amplifier is oscillating, and the curves in Figs. 1.2.9 and 1.2.10 are not valid for this condition. However, they are carried through to Figs. 1.2.11 and 1.2.12 merely to indicate the direction in which the magnitude and phase characteristics of the frequency response will change as R-35-2 is varied from its maximum value of five kilohms to zero.

An analysis of Eq. 1.2.2 and the calculated DC gains of the various transfer function shows that the common mode gain of this amplifier at very low frequencies is -51db. In other words the attenuation to common mode signals on the input terminals of the amplifier is 51db (approximately 350:1).

Figs. 1.2.11 and 1.2.12 indicate that as the frequency increases the attenuation decreases to approximately 25 db (18:1) in the range from 10Kc to 100Kc with R35-2 set at its maximum value. As R35-2 is decreased the rise time characteristic of the common mode response are improved but at a further loss of attenuation to common mode variations. In adjusting the amplifier common mode response, care must be taked not to attempt to improve the rise time characteristics anymore than necessary because of the loss of this attenuation.

It will also be noticed that even though much attenuation can be lost in the 10Kc to 100Kc region by varying R35-2, relatively no change is produced in the high attenuation of the amplifier to 60 or 180 cycle power supply ripple.

# 1.3 Non-linear Effects In Line Driver

The previous two sections have analyzed the amplifier for both differential and common mode signals from a purely linear balanced approach. Because of the tolerances in components it can not be guaranteed that the two sides of the amplifier are balanced. However, even if perfect components are assumed, considerable non-linearity exists because of the large voltage swings involved in the output stage. As the differential output voltage swing increases, the operating points of the two sides of the output stage begin to separate, the amount of separation being a function of the differential output voltage. As these operating points separate, they enter regions of increased and decreased gm simultaneously causing the gain and frequency response of the two sides to differ. Since the voltage swings within the preamp are considerably smaller, it can be assumed that all the existing non-linearity is caused by the output stage. From this consideration it can be seen that the analyses in sections 1.1 and 1.2 apply only for very small signal excursions in a region where the gains of the two sides of the amplifier are identical.

Page 6

In the differential mode analysis of section 1.1 the differential transfer function was given as

Eq. 1.1.1

$$KG_{DIFF} = \frac{K_{II} G_{II} K_A G_A}{1 + K_{I3} G_{I3} K_A G_A}$$

However, if it cannot be assumed that the forward gains of the two sides are equal, that is  $K_{AA} \ G_{AA} \neq K_{AB} \ G_{AB}$ , where  $K_{AA} \ G_{AA}$  is the gain of the A side and  $K_{AB} \ G_{AB}$  is the gain of the B side, then a more complicated expression must be used. If the two unequal gains are related to the balanced gain some simplication can be achieved. Thus, letting

$$K_{AA} G_{AA} = K_A G_A (1 + \delta_A)$$

$$K_{AB} G_{AB} = K_A G_A (1 - \delta_B)$$

where both  $\delta$  and  $\delta$  are themselves complex functions of frequency relating the two gains, Eq. A-12 of appendix A gives the complete differential response of the amplifier, E<sub>OD</sub> is the differential output voltage, and E<sub>D</sub> and E<sub>c</sub> are the differential and common mode input voltages respectively.

Eq. A-12

$$E_{od} = \frac{K_{II}G_{II}K_{A}G_{A}\left\{E_{D}\left[\frac{2+\delta_{A}-\delta_{B}}{2}+K_{A}G_{A}(K_{O}G_{O}-K_{I3}G_{I3})(1+\delta_{A})(1-\delta_{B})\right]+E_{C}(\delta_{A}+\delta_{B})\right\}}{1+K_{A}G_{A}K_{O}G_{O}\left(\frac{2+\delta_{A}-\delta_{B}}{2}\right)+K_{I3}G_{I3}(K_{A}G_{A})^{2}(K_{O}G_{O}-K_{I3}G_{I3})(1+\delta_{A})(1-\delta_{B})}$$

It will be noticed that now the amplifier produces a differential response from both differential and common mode inputs ( $E_D$  and  $E_C$ ). If these responses are separated by superposition, the variation of each response can be compared to the linear balanced gain. This has been done in Appendix A in Eq. A-14 and A-16.

Eq. A-14

$$\frac{E_{\sigma D}/E_{D}}{KG_{DIFF}} = \frac{(I+K_{I3}G_{I3}K_{A}G_{A})\left[I+\frac{\delta_{A}-\delta_{B}}{2}+K_{A}G_{A}(K_{D}G_{D}-K_{I3}G_{I3})(I+\delta_{A})(I-\delta_{B})\right]}{(I+K_{A}G_{A}K_{D}G_{D}(I+\frac{\delta_{A}-\delta_{B}}{2})+K_{I3}G_{I3}(K_{A}G_{A})^{2}(K_{D}G_{D}-K_{I3}G_{I3})(I+\delta_{A})(I-\delta_{B})}$$

Eq. A-16

$$\frac{E_{ob}/E_{c}}{KG_{DIFF}} = \frac{(I+K_{I3}G_{I3}K_{A}G_{A})(\delta_{A}+\delta_{B})}{I+K_{A}G_{A}K_{D}G_{D}(I+\frac{\delta_{A}-\delta_{B}}{2}) + K_{I3}G_{I3}(K_{A}G_{A})^{2}(K_{D}G_{D}-K_{I3}G_{I3})(I+\delta_{A})(I-\delta_{B})}$$

In this present amplifier it can be shown that  $K_D \xrightarrow{G_D \times K_{13}} \xrightarrow{G_{13}} \xrightarrow{K_{10}} \xrightarrow{G_{10}} \xrightarrow{K_{10}} \xrightarrow{G_{13}} \xrightarrow{K_{10}} \xrightarrow{G_{10}} \xrightarrow{K_{10}} \xrightarrow{G_{13}} \xrightarrow{K_{10}} \xrightarrow{G_{13}} \xrightarrow{K_{10}} \xrightarrow{G_{10}} \xrightarrow{K_{10}} \xrightarrow{K_{10$

Eq. A-17

$$\frac{E_{OD}/E_{D}}{KG_{DIFF}} = 1$$

Eq. A-18  $\frac{E_{OD}/E_{C}}{KG_{DIFF}} = \frac{K_{13}G_{13}K_{A}G_{A}(S_{A}+S_{B})}{1+K_{D}G_{D}K_{13}G_{13}(K_{A}G_{A})^{2}(1+S_{A})(1-S_{B})}$

Equation A-17 shows that under the conditions that  $K_D \ G_D \gg K_{13} \ G_{13}$  and  $K_A \ G_A \ K_{13} \ G_{13} \gg 1$ , the differential response of the amplifier to differential inputs remains virtually unchanged despite any unbalance in the forward gain of the amplifier. However, Eq. A-18 shows that as the unbalance increases the differential response becomes more and more susceptible to

S# Jnemelqqu2 482E-W9

Page 7

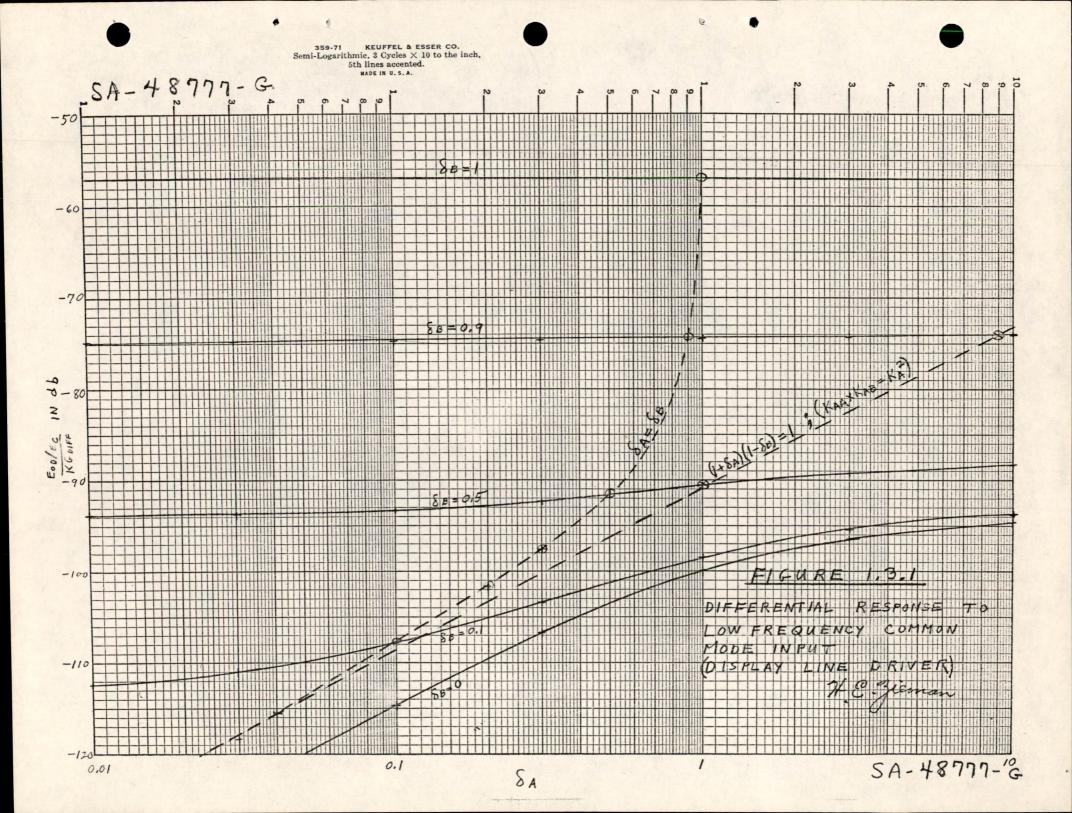

common mode inputs. amplifier over a similiar single-sided amplifier for the rejection of of a single-sided amplifier and shows the improvement of this differential generally fall between these two cases. The curve for B=1 is the case  $X_{A}G_{A}$  then  $X_{A}B$   $G_{A}B = \frac{1}{2}X_{A}G_{A}$ . The expected variations in the gains will as the reciprocal of the gain change on the other (that is if KAA GAA = for  $\int A = \int B^3$  the other for the case where the gain on one side changes variations to simplify the plot. Two special cases are also shown, one factors  $\delta_A$  and  $\delta_B$  vary. The plot shows primarily the response for independent variation of  $\delta$  and  $\delta$  using only the real portion of the  $\boldsymbol{\delta}$ this response under the conditions existing for f < 10Kc as the unbalance to told a swork (D-77784-A2) 1.5.1 (SA-48777 and a plot of

with the transfer function given as The common mode response of the amplifier was treated in section 1.2

by the complex unbalance factors &A and B gives respectively, assume KCA GCA + KCB GCB. Relating these unbalanced gains KCB GCB be the forward gain to common mode signals for the A and B sides balanced forward gain to common mode signals be KC GC, and KCA GCA and must also be reanalyzed for unbalanced conditions. Letting the normal For the same reasons stated in the differential analysis, this equation

the amplifter. Equation B-14 of Appendix B gives the complete common mode response of

$$E^{d^{\circ}} B^{-}I^{\dagger} E^{o^{\circ}} = \frac{1 + K^{\circ} e^{c} K^{0} e^{0} [1 + 2^{\vee} - 2^{\vee} + K^{\circ} e^{c} K^{0} e^{0} (1 + 2^{\vee}) (1 - 2^{\vee})] - (K^{\circ} e^{c} K^{0} e^{0} + 2^{\vee}) (1 - 2^{\vee})] - (K^{\circ} e^{c} K^{0} e^{0} + 2^{\vee}) (1 - 2^{\vee})] + E^{o} K^{\circ} e^{c} K^{0} e^{0} K^{0}$$

to the balanced transfer function gives Eq. B-15 and B-18 of Appendix B. Breaking this equation by superposition and relating the components

$$E^{d_{\circ}} B^{-12} \frac{Ke^{c_{M}}}{E^{\circ\circ}/e^{\varepsilon}} = \frac{1 + K^{\varepsilon}e^{\varepsilon}(K^{0}e^{0}-K^{m}e^{m})[1 + \chi^{\varepsilon}e^{\varepsilon}(K^{m}e^{m}(1+\chi^{0})(1-\chi^{0})] - (K^{\varepsilon}e^{\varepsilon}K^{m}e^{m})(1-\chi^{0})}{[1 + K^{\varepsilon}e^{\varepsilon}(K^{0}e^{0}-K^{m}e^{m})][1 + \chi^{0}-\chi^{0}} + K^{\varepsilon}e^{\varepsilon}(K^{m}e^{m}(1+\chi^{0})(1-\chi^{0})]$$

$$\mathbb{E}^{d^{\circ}} \mathbb{B}^{-18} \frac{K \mathcal{C}^{c^{\prime\prime}}}{\mathbb{E}^{\circ c^{\prime}} \mathbb{E}^{p}} = \frac{1 + K^{c} \mathcal{C}^{c} \left[1 + \frac{5}{2^{4} - g^{0}} + K^{c} \mathcal{C}^{c} \left[1 + \frac{5}{2^{4} - g^{0}}\right] - \left(K^{c} \mathcal{C}^{c} \left[1 + \frac{5}{2^{4}}\right] - \left(K^{c} \mathcal{C}^{c^{\prime\prime}} + \frac{1}{2^{4}}\right) - \left(1 + \frac{5}{2^{4}}\right) - \left(1 + \frac{5}{2^{4}}\right)$$

$$E^{d^{\circ}} B^{-18} \frac{Ke^{c^{\prime\prime}}}{c^{9}c^{1}F^{2}} = \frac{1 + K^{c}e^{c}K^{b}e^{b}[1 + \frac{5}{2^{N}-2^{B}} + K^{c}e^{c}K^{\dagger}e^{(1+2^{N})}(1-2^{N})}{[1 + K^{c}e^{c}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^{b}e^{-2}(K^$$

The plot of

$$K_{H} G_{H} (F_{2} K_{0} G_{p} [] + \frac{2}{2} + K_{c} G_{c} K_{\mu} G_{\mu} (] + \frac{1}{2} G_{p} X_{1\mu} G_{1\mu} H_{1} (] + \frac{1}{2} G_{p} (] + \frac{1}{2} H_{1} (] +$$

indicates that Kc Gc KD GD71 in the region f 210Kc. Using these inequalities simplifies equations B-15 and B-17 and B-20 of Appendix B. the region f (100Kc. Similarly the plot of KE GE (Fig. 1.2.9 and 1.2.10)

6M-3284

Supplement #2

Page 8

Eq. B-17

$$\frac{\frac{E_{oc}/E_{c}}{KG_{cM}} = 1}{\frac{E_{oc}}{E_{oc}} = \frac{\delta_{A} + \delta_{B}}{\frac{E_{oc}}{KG_{cM}}} = \frac{\delta_{A} + \delta_{B}}{4\left[1 + \frac{\delta_{A} - \delta_{B}}{2} + K_{c}G_{c}K_{i4}G_{i4}(1 + \delta_{A})(1 - \delta_{B})\right]}$$

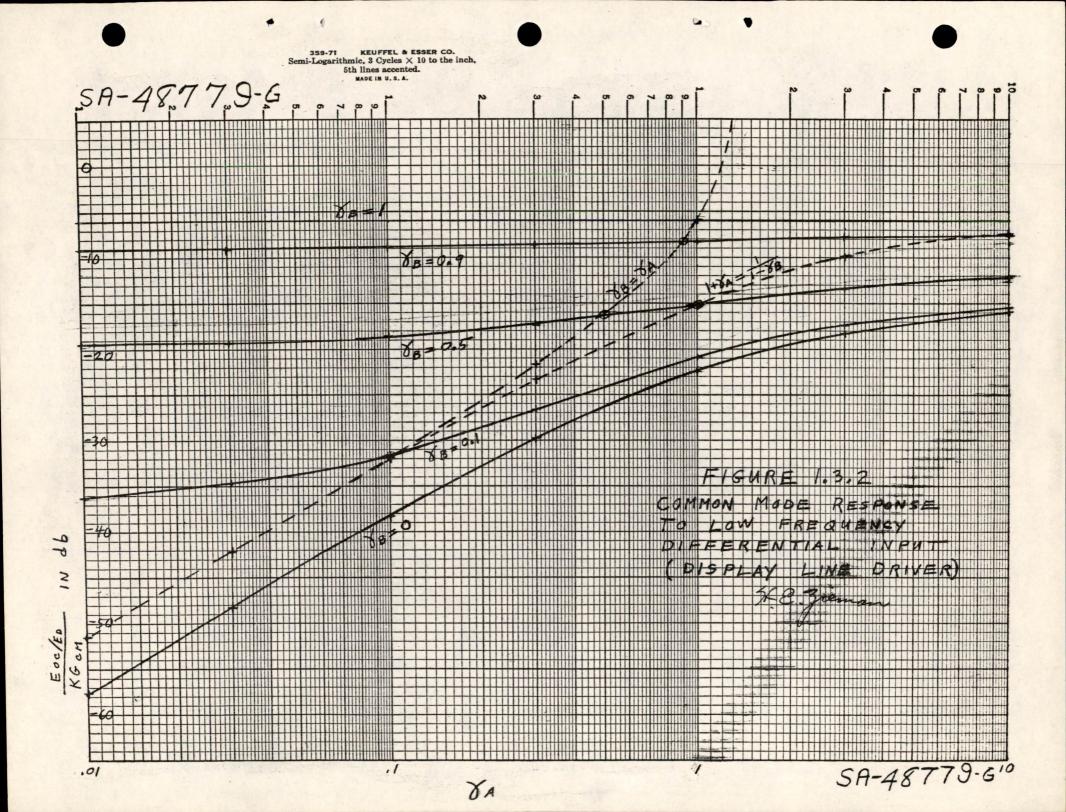

Equation B-17 indicates that the common mode response of the amplifier to common mode signals remains constant for frequencies less than 10Kc despite any degree of unbalance. Equation B-20 indicates that as the unbalance factors increase the susceptibility of the common mode response to differential input signals increases. Figure 1.3.2 (SA-48779-G) shows a plot of this response as the unbalance factors vary. The two special cases are again plotted ( $\forall_A = \forall_B$  and 1+  $\forall_A = \underline{1}$ ) with the actual amplifier generally varying between these two  $\underline{1-\forall_B}$  cases. The case of  $\forall_B=1$ is the case of a single-sided amplifier and indicates the advantage of this amplifier over a single-sided amplifier in rejecting common mode inputs.

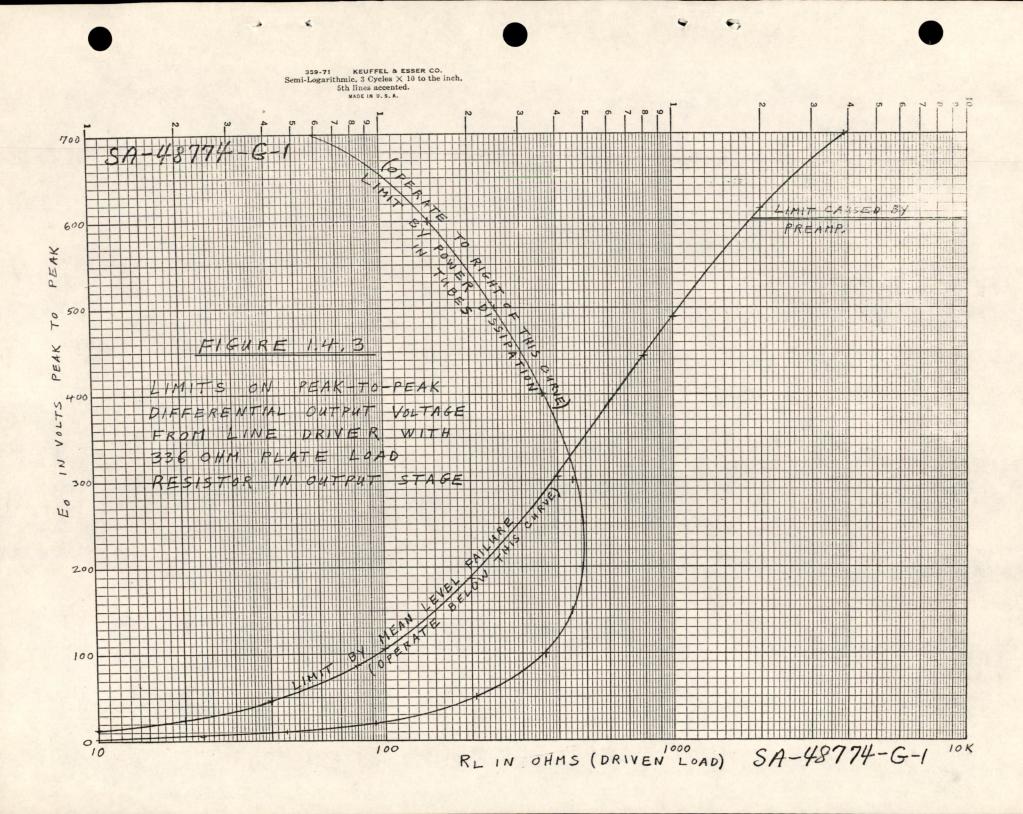

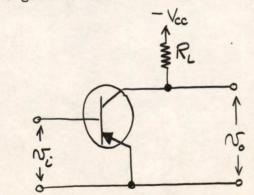

#### 1.4 Maximum Allowable Differential Swing from Line Driver

The maximum differential output swing available from the line driver is determined by the output stage. Two separate considerations are necessary: first, the necessity to maintain a fixed mean level, and secondly to stay within the allowable dissipation ratings of the stage.

#### 1.4.1 Maximum Output Fixed by Mean Level Requirement

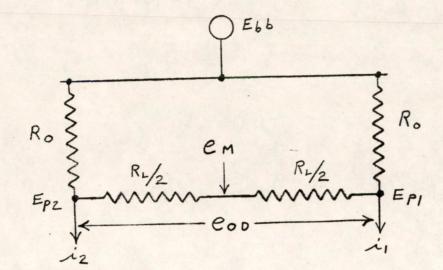

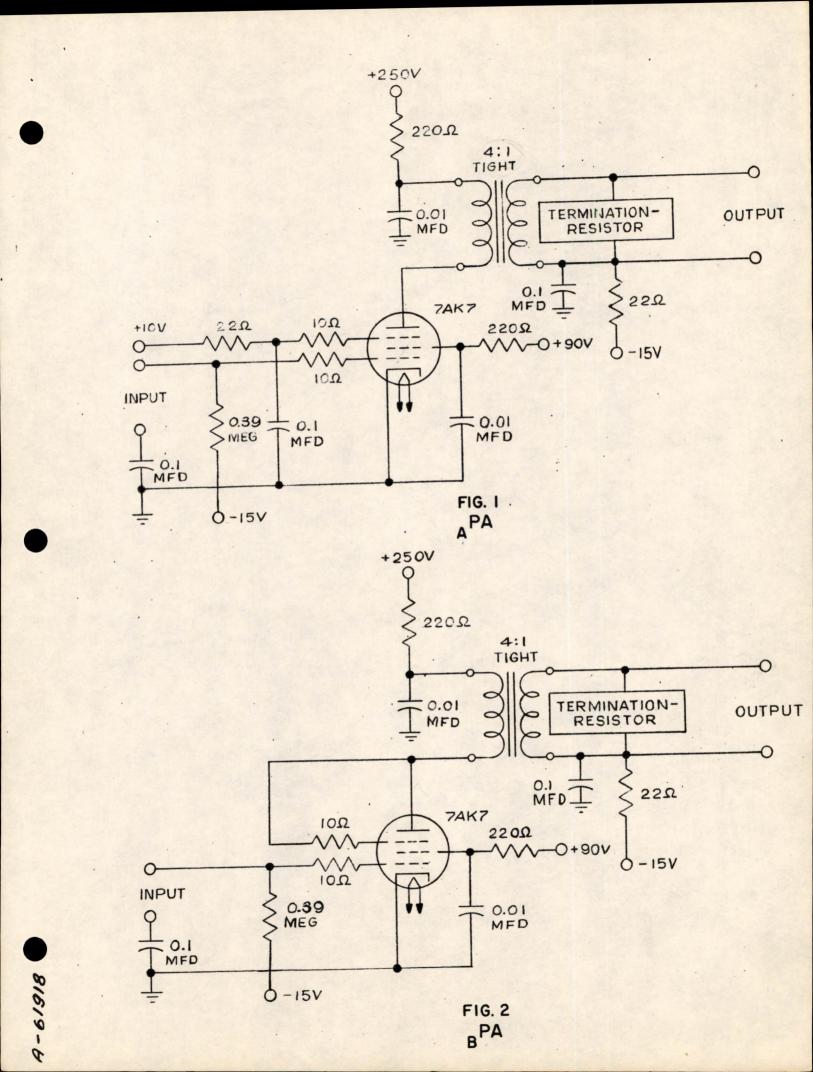

Figure 1.4.1 (SA-66073) is a much simplified configuration of the line driver output stage.  $R_0$  is the total resistance of the plate load resistors of the output stage,  $R_L$  is the equivalent resistance of all consoles being driven by the output stage,  $E_{bb}$  is the supply voltage,  $e_m$  is the mean level of the output referred to ground,  $e_{od}$  is the differential output swing,  $E_{p1}$  and  $E_{p2}$  are the voltages at the plates of the output tubes, and  $i_1$  and  $i_2$ , are the currents being drawn by the output tubes.

The maximum swing in one direction will occur when one side of the output stage is completely cut-off, and the other side is drawing its maximum current. Assuming that  $i_1$  is cut-off completely, then  $E_{p1}$ , the voltage on the plate of the "1" side is:

Eq. 1.4.1a

$$E_{PI} = e_m + \frac{e_{od}}{2}$$

The differential output voltage at this time is

Eq. 1.4.1b

$$Cod = (E_{bb} - E_{Pl}) \frac{R_L}{R_o}$$

Solving equations a and b simultaneously for eod gives

Eq. 1.4.1c

$$Cod = \frac{Ebb - Cm}{\frac{R_o}{R_L} + 0.5}$$

For  $E_{bb} = 250V$  and  $e_m = 45V$  this output becomes:

Eq. 1.4.1d  $Cod = \frac{205}{\frac{R_o}{R_c} + 0.5}$

Page 9

Since eod can swing this amount in both directions, the total maximum differential peak to peak output voltage becomes twice this value:

Eq. 1.4.1e

$$Cod(PP) = \frac{410}{\frac{R_0}{R_L} + 0.5}$$

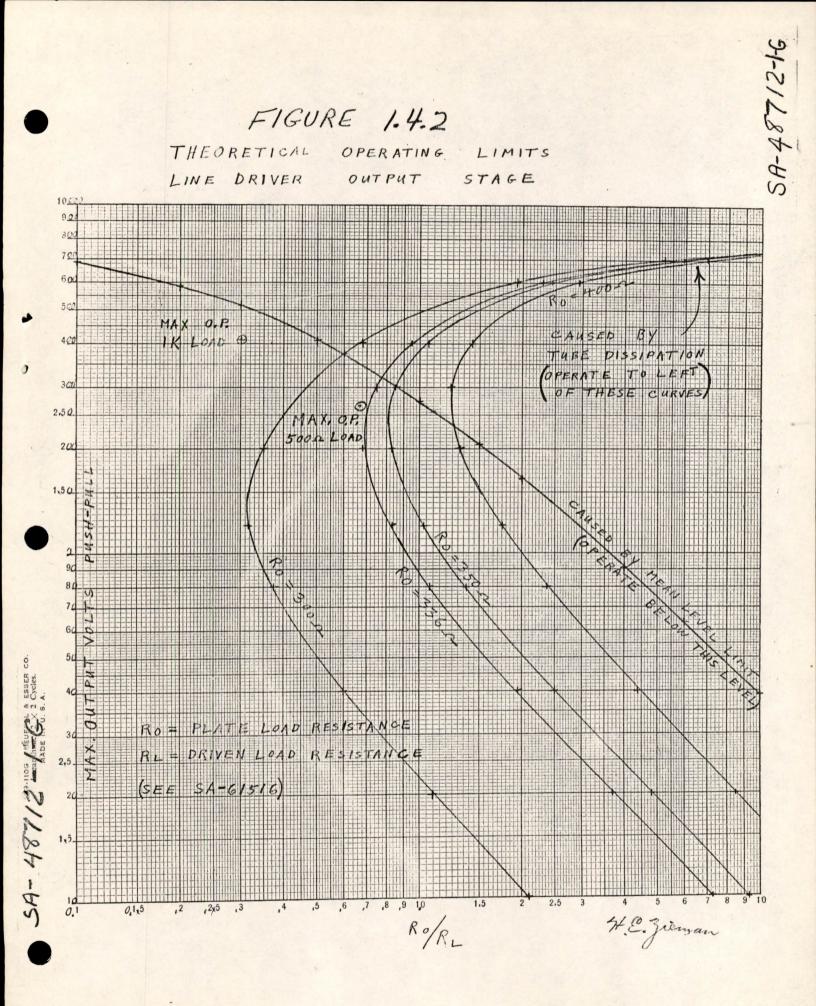

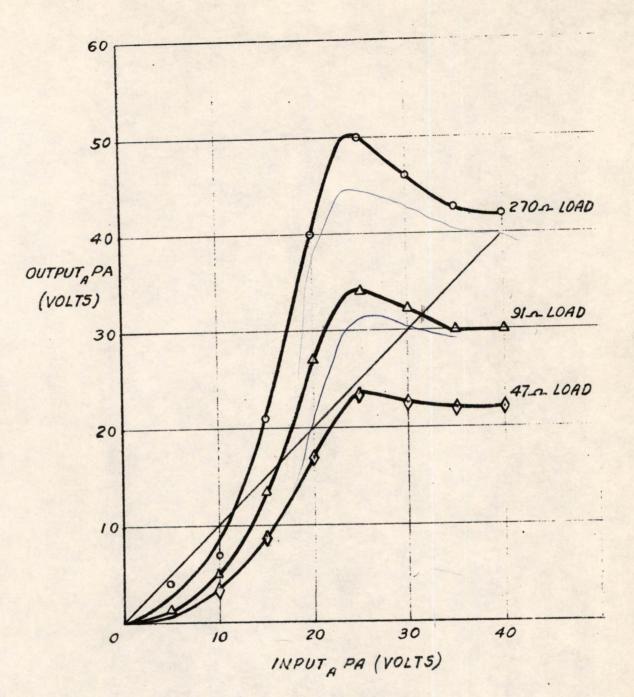

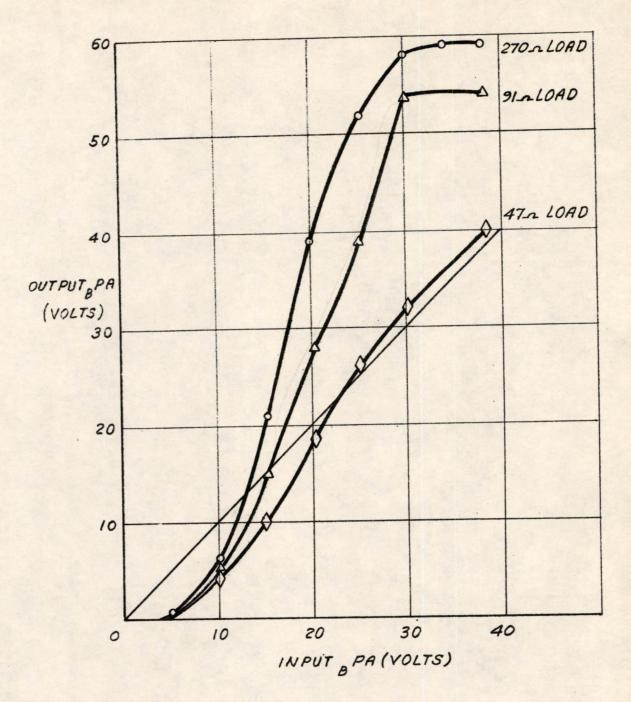

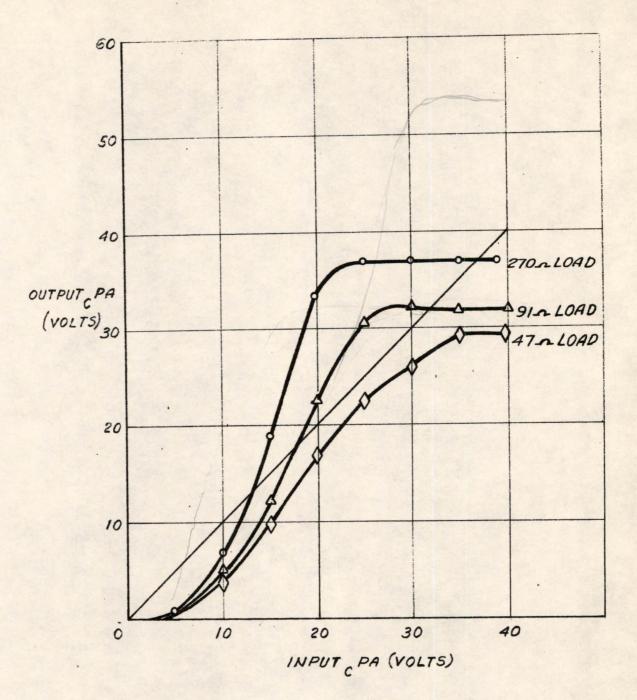

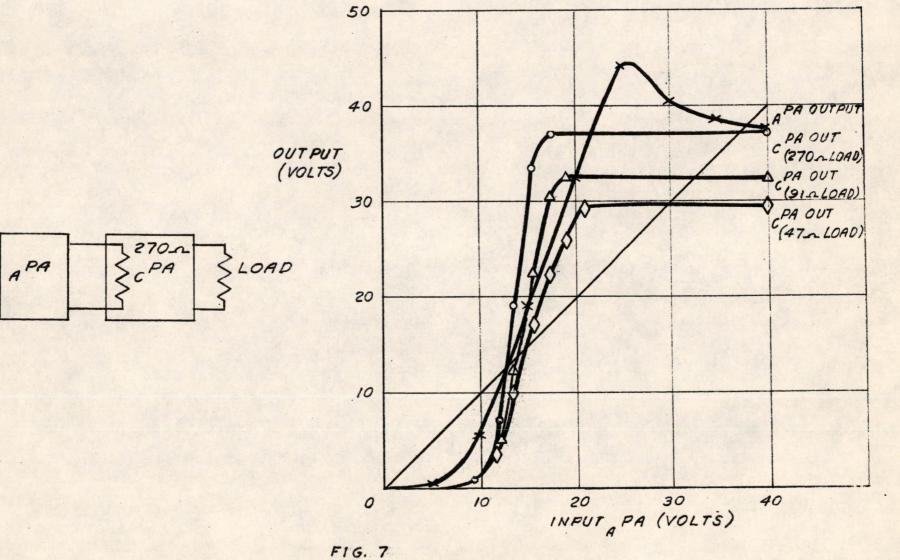

This equation is plotted in Fig. 1.4.2 (SA-48712-G) for a mange of  $0.1/\frac{R_0}{R_L}$  (10. As  $R_L$  approaches an open circuit this value approaches 820V output. For any given ratio  $R_0/R_L$  the amplifier must be operated below this calculated value or the mean level control circuit will fail to function.

#### 1.4.2 Maximum Output Fixed by Tube Dissipation

Considering Fig. 1.4.1 again, Ep1 is the plate voltage of the output stage at any given output voltage and can be expressed as:

Eq. 1.4.2a

$$E_{P_1} = e_m - \frac{e_{od}}{2}$$

The current through this side is then

Eq. 1.4.2b

$$i_1 = \frac{E_{bb} - E_{Pl}}{R_o} + \frac{e_{od}}{R_L}$$

Solving equations a and b simultaneously gives:

Eq. 1.4.2c

$$\lambda_1 = \frac{1}{R_0} \left[ E_{bb} - e_m + e_{od} \left( \frac{R_0}{R_L} + 0.5 \right) \right]$$

The voltage across the output tubes is

Eq. 1.4.2d

$$e_{b} = e_{m} - \frac{e_{od}}{2} - E_{K}$$

where  $E_K$  is the cathode voltage referred to ground. Under these conditions the plate power dissipated in the output tubes is  $e_{\rm pl}$ .

Eq. 1.4.20

$$P_{L} = \frac{1}{R_{o}} \left[ E_{Lb} - e_{m} + e_{od} \left( \frac{R_{o}}{R_{L}} + 0.5 \right) \right] \left[ e_{m} - \frac{e_{od}}{2} - E_{K} \right]$$

For any fixed value of R<sub>o</sub> and for a given maximum power dissipation of the output stage.

Eq. 1.4.2f

$$P_{L_{MAX}} R_{o} = \begin{bmatrix} E_{bb} - e_m + e_{od} \left( \frac{R_o}{R_L} + 0.5 \right) \end{bmatrix} e_m - \frac{e_{od}}{2} - E_K$$

Solving this inequality for  $R_o/R_L$  gives:

Eq. 1.4.2g

$$\frac{R_o}{R_L} \leqslant \frac{\frac{P_{bMax} R_o}{e_m - E_K - e_{od/2}} + e_m - E_{bb}}{e_{od}} = 0.5$$

From the circuit in Fig. E75792 and known operating conditions the following values can be substitued:

$$E_{bb} = 250 V$$

$e_m = 45 V$

$E_K = -150 V$

# Appendix A

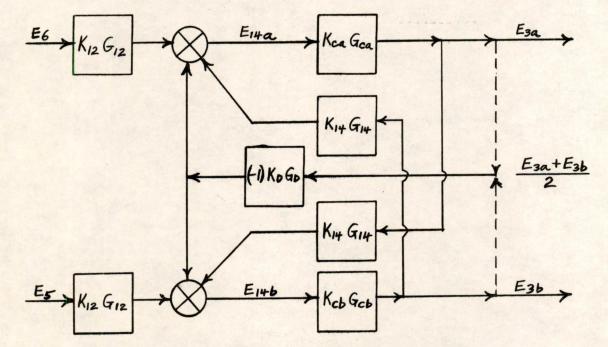

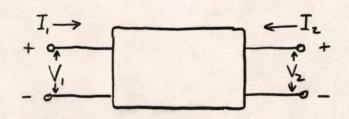

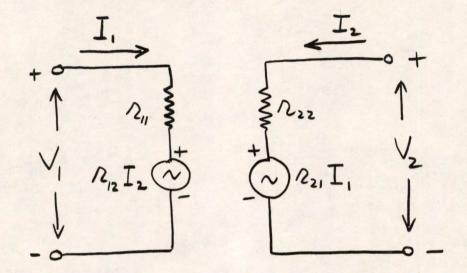

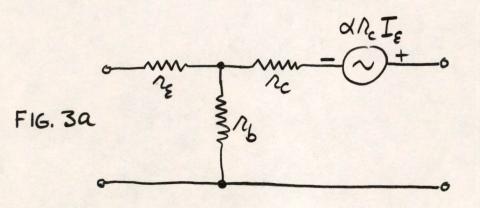

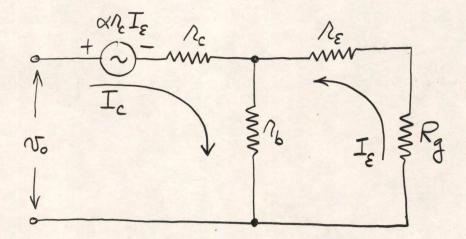

Consider the Above Circuit for Differential Mode Response:

(All Kn Gn Functions Will Be Written as Kn to Simplify Notation)

A-1

$$\begin{cases}

E_{3a} = E_{14a} K_{AA} \\

E_{3b} = E_{14b} K_{AB}

\end{cases}$$

A-2

$$\begin{cases}

E_{14a} = E_6 K_{11} + E_{3b} K_{13} - \frac{E_{3a} + E_{3b}}{2} K_0 \\

E_{14b} = E_5 K_{11} + E_{3a} K_{13} - \frac{E_{3a} + E_{3b}}{2} K_0

\end{cases}$$

$$E_{3a} = E_{6} K_{11} K_{AA} + E_{3b} K_{AA} (K_{13} - \frac{K_{0}}{2}) - E_{3b} \frac{K_{AA} K_{0}}{2}$$

A-3

A

-4

$$E_{3b} = E_5 K_{11} K_{AB} + E_{3a} K_{AB} (K_{13} - \frac{K_0}{2}) - E_{3b} \frac{K_{AB} K_0}{2}$$

Solving Equations A-3 and A-4 For E3a and E3b:

Page 12

A-5

$$E_{3a} = \frac{K_{AA} K_{II} \left[ E_6 \left( 1 + \frac{K_{AB} K_D}{2} \right) + E_5 K_{AB} \left( K_{I3} - \frac{K_D}{2} \right) \right]}{\left( 1 + \frac{K_{AA} K_D}{2} \right) \left( 1 + \frac{K_{AB} K_D}{2} \right) - K_{AA} K_{AB} \left( K_{I3} - \frac{K_D}{2} \right)^2}$$

A-6

$$E_{3b} = \frac{K_{AB} K_{II} \left[ E_{5} \left( 1 + \frac{K_{AA} K_{D}}{2} \right) + E_{6} K_{AA} \left( K_{I3} - \frac{K_{D}}{2} \right) \right]}{\left( 1 + \frac{K_{AA} K_{D}}{2} \right) \left( 1 + \frac{K_{AB} K_{D}}{2} - K_{AA} K_{AB} \left( K_{I3} - \frac{K_{D}}{2} \right)^{2} \right)}$$

The Differential Output Voltage Can Be Defined As:

A-7 EOD = E3a - E3b

A-8

$$E_{od} = \frac{K_{11} \left[ E_{6} K_{AA} - E_{5} K_{AB} + K_{AA} K_{AB} \left( K_{0} - K_{13} \right) \left( E_{6} - E_{5} \right) \right]}{\left( 1 + \frac{K_{AA} K_{0}}{2} \right) \left( 1 + \frac{K_{AB} K_{0}}{2} \right) - K_{AA} K_{AB} \left( K_{13} - \frac{K_{0}}{2} \right)^{2}}$$

The Input Voltage Can Be Defined in Terms of Its Differential And Common Mode Components:

$$A-9 \begin{cases} E_6 = E_c + E_0/2 \\ E_5 = E_c - E_0/2 \end{cases}$$

A-10

$$E_{OD} = \frac{K_{II} \left\{ E_{D} \left[ \frac{K_{AA} + K_{AB}}{2} + K_{AA} K_{AB} (K_{D} - K_{I3}) \right] + E_{c} (K_{AA} - K_{AB}) \right\}}{\left( 1 + \frac{K_{AA} K_{D}}{2} \right) \left( 1 + \frac{K_{AB} K_{D}}{2} \right) - K_{AA} K_{AB} \left( K_{I3} - \frac{K_{D}}{2} \right)^{2}}$$

Letting  $K_{AA} = K_{AB} = K_A$

1

A-11

$$KG_{DIFF} = \frac{E_{ob}}{E_{p}} = \frac{K_{II} K_{A}}{I + K_{I3} K_{A}}$$

$$\frac{E_{ob}}{E_{e}} = 0$$

LET

$$\begin{cases} K_{AA} = K_A (1 + S_A) \\ K_{AB} = K_A (1 + S_B) \end{cases}$$

A-12

$$E_{od} = \frac{K_{II} K_{A} \left\{ E_{D} \left[ 1 + \frac{\delta_{A} - \delta_{B}}{2} + K_{A} (K_{0} - K_{I3}) (1 + \delta_{A}) (1 - \delta_{B}) \right] + E_{c} (\delta_{A} + \delta_{B}) \right\}}{1 + K_{A} K_{D} (1 + \frac{\delta_{A} - \delta_{B}}{2}) + K_{A}^{2} K_{I3} (K_{D} - K_{I3}) (1 + \delta_{A}) (1 - \delta_{B})}$$

EOD is the superposition of two components, one due to the differential input, and one due to the common input. These two components will be analyzed separately.

A-13

$$\frac{E_{oP}}{E_{O}} = \frac{K_{11}K_{A}\left[1 + \frac{\delta_{A} - \delta_{B}}{2} + K_{A}(K_{O} - K_{13})(1 + \delta_{A})(1 - \delta_{B})\right]}{1 + K_{A}K_{O}(1 + \frac{\delta_{A} - \delta_{B}}{2}) + K_{A}^{2}K_{13}(K_{O} - K_{13})(1 + \delta_{A})(1 - \delta_{B})}$$

A-14

$$\frac{E_{OD}/E_{D}}{KG_{DIFF}} = \frac{(I+K_{I3}K_{A})\left[I+\frac{\delta_{A}-\delta_{B}}{2}+K_{A}(K_{D}-K_{I3})(I+\delta_{A})(I-\delta_{B})\right]}{I+K_{A}K_{D}(I+\frac{\delta_{A}-\delta_{B}}{2})+K_{A}^{2}K_{I3}(K_{D}-K_{I3})(I+\delta_{A})(I-\delta_{B})}$$

A-15

$$\frac{E_{oD}}{E_c} = \frac{K_{11}K_A(\delta_A + \delta_B)}{1 + K_A K_D(1 + \frac{\delta_A - \delta_B}{2}) + K_A^2 K_{13}(K_D - K_{13})(1 + \delta_A)(1 - \delta_B)}$$

A-16

$$\frac{E \circ D / E_{c}}{K G_{DIFF}} = \frac{(I + K_{I3} K_{A})(\delta_{A} + \delta_{B})}{I + K_{A} K_{D} (I + \frac{\delta_{A} - \delta_{B}}{2}) + K_{A}^{2} K_{I3} (K_{D} - K_{I3})(I + \delta_{A})(I - \delta_{B})}$$

Page 13

.

A-17

$$\frac{E_{oD}/E_{D}}{KG_{DIFF}} = 1$$

A-18

$$\frac{E_{oD}/E_{C}}{KG_{DIFF}} = \frac{K_{I3}K_{A}\left(\delta_{A} + \delta_{B}\right)}{1 + K_{A}^{2}K_{I3}K_{D}\left(1 + \delta_{A}\right)\left(1 - \delta_{B}\right)}$$

Under low frequency operation

$$K_A \approx 52 db$$

$K_{13} = -21 db$   $K_o \approx 42 db$

Thus for  $\delta_A \gg 0$  AND  $1 \gg (1 - \delta_B) > 10^{-4}$

A-19

$$\frac{E_{ob}/E_{c}}{KG_{blFF}} = \frac{\delta_{A} + \delta_{B}}{K_{A}K_{b}(1 + \delta_{A})(1 - \delta_{B})}$$

For

$$\delta_B = 1$$

-

A-20

$$\frac{E_{ob}/E_c}{KG_{DIFE}} = \frac{2K_{13}}{K_0} \approx -57db$$

Page 14

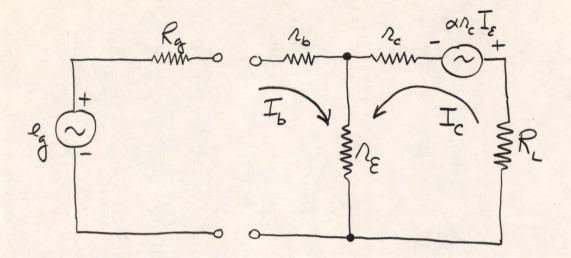

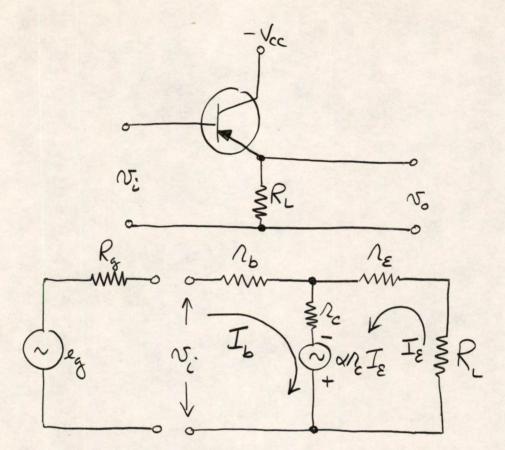

# Appendix B

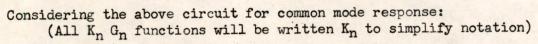

Common Mode Response of Complete Amplifier

$$B-2 \qquad \begin{cases} E_{14a} = E_6 K_{12} - E_{3a} \frac{K_0}{2} + E_{3b} \left( K_{14} - \frac{K_0}{2} \right) \\ E_{14b} = E_5 K_{12} - E_{3b} \frac{K_0}{2} + E_{3a} \left( K_{14} - \frac{K_0}{2} \right) \end{cases}$$

6M-3284

Supplement #2

Page 16

$$B-3 \quad E_{3a} = \frac{E_6 \, K_{12} \, K_{ca} + E_{3b} \, K_{ca} \left( K_{14} - \frac{K_0}{2} \right)}{1 + \frac{K_{ca} \, K_0}{2}}$$

$$B-4 \quad E_{3b} = \frac{E_5 \ K_{12} \ K_{cb} + E_{3a} \ K_{cb} \left(K_{14} - \frac{K_{b}}{2}\right)}{1 + \frac{K_{cb} \ K_{b}}{2}}$$

Solving equations B-3 and B-4 for  $E_{3a}$  and  $E_{3b}$  gives:

B-5

$$E_{3a} = \frac{E_6 K_{12} K_{ca} \left( 1 + \frac{K_0 K_{cb}}{2} \right) + E_5 K_{12} K_{ca} K_{cb} \left( K_{14} - \frac{K_0}{2} \right)}{\left( 1 + \frac{K_0 K_{ca}}{2} \right) \left( 1 + \frac{K_0 K_{cb}}{2} \right) - K_{ca} K_{cb} \left( K_{14} - \frac{K_0}{2} \right)^2}$$

$$E_{3b} = \frac{E_{5} K_{12} K_{cb} \left( 1 + \frac{K_{b} K_{cb}}{2} \right) + E_{6} K_{12} K_{ca} K_{cb} \left( K_{14} - \frac{K_{b}}{2} \right)}{\left( 1 + \frac{K_{b} K_{ca}}{2} \right) \left( 1 + \frac{K_{b} K_{cb}}{2} \right) - K_{ca} K_{cb} \left( K_{14} - \frac{K_{b}}{2} \right)^{2}}$$

The common mode variation of the output, Eoc, can be defined as:

$$B-7 \qquad E_{oc} = \frac{E_{3a} + E_{3b}}{2}$$

1

$$E_{\sigma c} = \frac{E_{6} K_{12} K_{ca} (1 + K_{14} K_{cb}) + E_{5} K_{12} K_{cb} (1 + K_{14} K_{ca})}{2 \left[ \left( 1 + \frac{K_{b} K_{ca}}{2} \right) \left( 1 + \frac{K_{b} K_{cb}}{2} \right) - K_{ca} K_{cb} \left( K_{14} - \frac{K_{b}}{2} \right)^{2} \right]}$$

If the input voltages are redefined in terms of the differential input, ED, and the common mode input, EC:

B-9

$$\begin{cases} E_6 = E_c + E_0/2 \\ E_5 = E_c - E_0/2 \end{cases}$$

6M-3284

Supplement #2

Page 17

B-10

$$E_{oc} = \frac{E_{c} K_{12} (K_{ca} + K_{cb} + 2K_{14} K_{ca} K_{cb}) + \frac{E_{D}}{2} K_{12} (K_{ca} - K_{cb})}{2 \left[ 1 + \frac{K_{D}}{2} (K_{ca} + K_{cb} + 2K_{14} K_{ca} K_{cb}) - K_{ca} K_{cb} K_{14}^{2} \right]}$$

Letting  $K_{ca} = K_{cb} = K_c$

B-11

$$E_{oc} = \frac{E_c K_{12} K_c (1 + K_{14} K_c)}{1 + K_c K_b (1 + K_{14} K_c) - K_c^2 K_{14}^2}$$

B-12

$$K G_{cm} = \frac{E_{oc}}{E_{c}} = \frac{K_{12} K_c}{1 + K_c (K_p - K_{14})}$$

B-13

$$E_{oc}/E_{b} = 0$$

LET

$$K_{ca} = K_c (1 + \delta_a)$$

$K_{cb} = K_c (1 - \delta_b)$

$$B-14 \qquad E_{oc} = \frac{E_{c} K_{12} K_{c} \left[ 1 + \frac{\delta_{a} - \delta_{b}}{2} + K_{14} K_{c} (1 + \delta_{a}) (1 - \delta_{b}) \right] + E_{o} K_{12} K_{c} (\delta_{A} + \delta_{B}) / 4}{1 + K_{o} K_{c} \left[ 1 + \frac{\delta_{a} - \delta_{b}}{2} + K_{14} K_{c} (1 + \delta_{a}) (1 - \delta_{b}) \right] - K_{c}^{2} K_{14}^{2} (1 + \delta_{A}) (1 - \delta_{B})}$$

$$B-15 \qquad \frac{E_{oe}/E_{e}}{KG_{cm}} = \frac{\left[1 + K_{e}(K_{b}-K_{l}+)\right] \left[1 + \frac{Va^{-\delta b}}{2} + K_{l}+K_{e}(1+\delta a)(1-\delta b)\right]}{1 + K_{o}K_{e}\left[1 + \frac{Va^{-\delta b}}{2} + K_{l}+K_{e}(1+\delta a)(1-\delta b)\right] - K_{e}^{2}K_{l}^{2}(1+\delta a)(1-\delta b)}$$

The normal values of specific transfer functions at low frequencies are:

Letting  $K_D \gg K_{14}$  first gives

Page 18

$$B-16 \qquad \frac{E_{oc}/E_{c}}{KG_{cm}} = \frac{(1+K_{c}K_{b})\left[1+\frac{\delta_{a}-\delta_{b}}{2} + K_{14}K_{c}(1+\delta_{a})(1-\delta_{b})\right]}{1+K_{c}K_{b} + K_{c}K_{b}\left[\frac{\delta_{a}-\delta_{b}}{2} + K_{14}K_{c}(1+\delta_{a})(1-\delta_{b})\right]}$$

$$\frac{E_{oc}/E_{c}}{KG_{cm}} = \frac{1 + \frac{\aleph_{a} - \aleph_{b}}{2} + K_{14}K_{c}(1 + \aleph_{a})(1 - \aleph_{b})}{1 + \frac{K_{c}K_{o}}{1 + K_{c}K_{o}}\left[\frac{\aleph_{a} - \aleph_{b}}{2} + K_{14}K_{c}(1 + \aleph_{a})(1 - \aleph_{b})\right]}$$

KeKo»1 Then letting

$$\frac{K_c K_b}{1 + K_c K_b} \approx 1$$

$$B-17 \qquad \frac{E_{oc}/E_{c}}{KG_{cm}} \approx 1$$

$$\frac{E_{oc}/E_{o}}{K_{G}} = \frac{\left[I + K_{c}(K_{o} - K_{H})\right](\delta_{a} + \delta_{b})/4}{I + K_{o}K_{c}\left[I + \frac{\delta_{a} - \delta_{b}}{2} + K_{H}K_{c}(I + \delta_{a})(I - \delta_{b})\right] - K_{c}^{2}K_{H}^{2}(I + \delta_{a})(I - \delta_{b})}$$

FOR Koskin

$$B-19 \quad \frac{E_{oc}/E_{D}}{KG_{cm}} = \frac{(I+K_{c}K_{D})(8a+8b)/4}{I+K_{c}K_{D} + K_{c}K_{D}\frac{8a-8b}{2} + K_{c}^{2}K_{D}K_{I4}(I+8a)(I-8b)}$$

$$\frac{E_{oc}/E_{D}}{KG_{cm}} = \frac{\left(\sqrt[3]{a} + \sqrt[3]{b}\right)/4}{1 + \frac{K_{c}K_{D}}{1 + K_{c}K_{b}}\left[\frac{\sqrt[3]{a} - \sqrt[3]{b}}{2} + K_{c}K_{i4}(1 + \sqrt[3]{a})(1 - \sqrt[3]{b})\right]}$$

$$B-20 \quad \frac{E_{oc}/E_{o}}{KG_{cm}} = \frac{\delta_{a}+\delta_{b}}{4\left[1+\frac{\delta_{a}-\delta_{b}}{2}+K_{o}K_{14}(1+\delta_{a})(1-\delta_{b})\right]}$$

Page 19

Considering two special cases:

First:  $\forall a = \forall b = \forall$

$B-21 \quad \frac{E_{oc}/E_{D}}{KG_{cm}} = \frac{\chi}{2\left[1 + K_{c}K_{14}\left(1 - \chi^{2}\right)\right]} = \frac{\chi}{2 K_{c}K_{14}\left(\frac{1 + K_{c}K_{14}}{K_{c}K_{14}} - \chi^{2}\right)}$

$$B-22 \quad \frac{E_{oc}/E_{o}}{KG_{cm}} = \frac{\delta}{1.78(2.12-\delta^2)}$$

Secondly:

$$(1 + \delta_a)(1 - \delta_b) = 1$$

$$\delta b = \frac{\delta a}{1+\delta a}$$

;  $\delta a + \delta b = \frac{\delta a (2+\delta a)}{1+\delta a}$ ;  $\delta a - \delta b = \frac{\delta a^2}{1+\delta a}$

$$B-23 \quad \frac{E_{oc} / E_{o}}{KG_{cm}} = \frac{\chi_{a} (2 + \chi_{a}) / 2}{2 (1 + K_{c} K_{14}) (1 + \chi_{a}) + \chi_{a}^{2}}$$

For Kc K14 = - 126 = . 891

$$\frac{B-24}{KG_{cm}} = \frac{\delta_a \left(2 + \delta_a\right)}{2\left[3.78\left(1 + \delta_a\right) + \delta_a^2\right]}$$

Page 20

Appendix C

| Glossary of Symbols |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DD                  | - | Digital display. The portion of the entire display system which<br>is exhibited on the typotron tubes.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| E <sub>3a</sub>     | - | Voltage of amplifier output terminal, marked $3_a$ in Fig. 0.1 (E75792), measured with respect to ground.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| E <sub>3b</sub>     | - | Voltage of amplifier output terminal, marked 3b in Fig. 0.1 (E75792), measured with respect to ground.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| E <sub>5</sub>      | - | Voltage of amplifier input terminal $E_5$ , marked $26_b$ in Fig. 0.1 (E75792), measured with respect to ground.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| E6                  | - | Voltage of amplifier input terminal $E_6$ , marked $26_a$ in Fig. 0.1 (E75792), measured with respect to ground.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| E <sub>7</sub>      | - | Voltage of amplifier input terminal $E_7$ , marked 27b in Fig. 0.1 (E75792), measured with respect to ground.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| E <sub>8</sub>      | - | Voltage of amplifier input terminal E8, marked 27a in Fig. 0.1 (E75792), measured with respect to ground.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| EC                  | - | Common mode input voltage to amplifier terminals $E_5$ : $E_6$ ,<br>or $E_7$ : $E_8$ . It is defined as $(E_5 + E_6)/2$ , or $(E_7 + E_8)/2$ .                                                                                                                                                                                                                                                                                                             |  |  |  |

| ED                  | - | Differential mode input voltage to amplifier terminals $E_5 : E_6$ , or $E_7 : E_8$ . It is defined as $(E_5 - E_6)$ , or $(E_7 - E_8)$ .                                                                                                                                                                                                                                                                                                                  |  |  |  |

| E <sub>OC</sub>     | - | Common mode output voltage from amplifier output points $3_a$ and $3_b$ . It is defined as $(E_{3a} + E_{3b})/2$ .                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| EOD                 | - | Differential mode output voltage from amplifier output points $3_a$ and $3_b$ . It is defined as $(E_{3a} - E_{3b})$ .                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| G                   | - | The frequency variant portion of a circuit transfer function.<br>If the transfer function is a complex number in the form $KG = \frac{(a_1 + jfb_1)(a_2 + jfb_2) \cdots (a_n + jfb_n)}{(c_1 + jfd_1)(c_2 + jfd_2) \cdots (c_m + jfd_m)}$ where $a_n$ , $b_n$ , $c_m$ , and $d_m$ are all constant terms, thenG is defined as:<br>$G = \frac{(1 + jfb_1/a_1)(1 + jfb_2/a_2) \cdots (1 + jfb_m/a_m)}{(1 + jfd_1/c_1)(1 + jfd_2/c_2) \cdots (1 + jfd_m/c_m)}$ |  |  |  |

| K                   | - | The constant portion of a circuit transfer function. If<br>the transfer function is a complex number in the form<br>shown above, then K is defined as:<br>$K = \frac{a_1 a_2 \cdots a_n}{c_1 c_2 \cdots c_m}$                                                                                                                                                                                                                                              |  |  |  |

- K<sub>1</sub> G<sub>1</sub>

- The differential mode gain of the output stage (Fig. 3.1.1 of supplement 1) when this stage is loaded with a standard S. D. load. It is the ratio of the differential output at terminals 3a and 3b to the differential input at 5a and 5b. Its equation is given in Eq. 3.1.1 of supplement 1.  $K_1$  G<sub>1</sub> is plotted in Fig. 3.1.2 of supplement 1.

K2 G2

- The common mode gain of the output stage (Fig. 3.1.1 of supplement 1) when this stage is loaded with a standard S.D. load. It is the ratio of the common mode output at terminals 3a and 3b to the common mode input at points 5a and 5b. Its equations is given in Eq. 3.1.2 of supplement 1,  $K_2$  G<sub>2</sub> is plotted in Fig. 3.1.2 of supplement 1.

- K<sub>3</sub> G<sub>3</sub> The differential mode gain of the output stage (Fig. 3.1.1 of supplement 1) when this stage is loaded with a standard D.D. load. It is the ratio of the differential mode output at terminals 3a and 3b to the differential input at points 5a and 5b. Its equation is given in Eq. 3.1.3 of supplement 1. K<sub>3</sub> G<sub>3</sub> is plotted in Fig. 3.1.2 of supplement 1.

- K<sub>4</sub> G<sub>4</sub> The common mode gain of the output stage (Fig. 3.1.1 of supplement 1) when this stage is loaded with a standard D.D load. It is the ratio of the common mode output at terminals 3a and 3b to the common mode input at points 5a and 5b. Its equation is given in Eq. 3.1.4 of supplement 1. K<sub>4</sub> G<sub>4</sub> is plotted in Fig. 3.1.2 of supplement 1.

- K<sub>5</sub>G<sub>5</sub> The differential mode gain of the output driver stage (Fig. 3.2.1 of supplement 1). It is the ratio of the differential mode output at points 5a and 5b to a differential mode input at points 10a and 10b. Its equation is given in Eq. 3.2.1 of supplement 1. K<sub>5</sub>G<sub>5</sub> is plotted in Fig. 3.2.2 of supplement 1.

- K<sub>6</sub>G<sub>6</sub> The common mode gain of the output driver stage (Fig. 3.2.1 of supplement 1). It is the ratio of common mode output at points 5a and 5b to the common mode input at points 10a and 10b. Its equation is given in Eq. 3.2.2 of supplement 1. K<sub>6</sub>G<sub>6</sub> is plotted in Fig. 3.2.2 of supplement 1.

- K<sub>7</sub> G<sub>7</sub> The differential mode gain of the buffer cathode follower (Fig. 3.3.1 of supplement 1). It is the ratio of the differential mode output at points 10a and 10b to the differential mode inputs at points 12a and 12b. Its equation is given in Eq. 3.3.1 of supplement 1. K<sub>7</sub> G<sub>7</sub> is plotted in Figs. 3.3.2 of supplement 1.

- K<sub>8</sub> G<sub>8</sub> The common mode gain of the buffer cathode follower (Fig. 3.3.1 of supplement 1). It is the ratio of the common mode output voltage at points 10a and 10b to the common mode input at points 12a and 12b. Its equation is given in

6M-3284

Eq. 3.3.2 of supplement 1. Kg Gg is plotted in Fig. 3.3.2 of supplement 1.

K9<sub>a</sub> G9<sub>a</sub> - The differential mode gain of the differential amplifier stage (Fig. 3.4.1 of supplement 1) with R35-1 equal to zero ohms. It is the ratio of the differential mode output at points 12a and 12b to the differential mode inputs at points 14a and 14b. Its equation is given in Eq. 3.4.1 of supplement 1. K9<sub>a</sub> G9<sub>a</sub> is plotted in Fig. 3.4.2 of supplement 1.

- K9<sub>b</sub> G9<sub>b</sub> The differential mode gain of the differential amplifier stage (Fig. 3.4.1 of supplement 1) with R35-1 equal to 50K. It is the ratio of the differential mode output at points 12a and 12b to the differential mode inputs at points 14a and 14b. Its equation is given in Eq. 3.4.2 of supplement 1.K9<sub>b</sub> G9<sub>b</sub> is plotted in Fig. 3.4.2 of supplement 1.

- K10 G10 The common mode gain of the differential amplifier stage (Fig. 3.4.1 of supplement 1). It is the ratio of the common mode output at points 12a and 12b to the common mode input at points 14a and 14b. Its equation is given in Eq. 3.4.3 of supplement 1. K10 G10 is plotted in Fig. 3.4.3 of supplement 1.

- K11 G11 The differential mode transfer function of the input circuit to the differential amplifier (Fig. 3.5.1 of supplement 1). It is the ratio of the differential mode output at points 14a and 14b to the differential mode input at points E5 and E6, or E7 and E8. Its response is given in equation 3.5.1 in supplement 1 and is plotted in Fig. 3.5.2, also in supplement 1.

- K12 G12 The common mode transfer functions of the input circuit to the differential amplifier (Fig. 3.5.1 of supplement 1). It is the ratio of the common mode output at points 14a and 14b to the common mode input at points E5, E6, E7 and E8. Its response is given in Eq. 3.5.5 of supplement 1 and is plotted in Fig. 3.5.4 also in supplement 1.

- K13 G13 The differential mode transfer function of the input circuit to the differential amplifier (Fig. 3.5.1 of supplement 1). It is the ratio of the differential mode output at points 14a and 14b to the differential mode input at points C1 and C5. Its response is given in Eq. 3.5.2 in supplement 1 and is plotted in Fig. 3.5.2 also in supplement 1.

- K14 G14 The common mode transfer function of the input circuit to the differential amplifier (Fig. 3.5.1 of supplement). It is the ratio of the common mode output at points 14a and

Page 23

- 14b to the common mode input at points C1 and C5. Its response is given in Eq. 3.5.4 of supplement 1 and is plotted in Fig. 3.5.4 also in supplement 1.

- K15 G15 The common mode transfer function of the input circuit to the differential amplifier (Fig. 3.5.1 of supplement 1). It is the ratio of the common mode output at points 14a and 14b to the input at point 16. Its response is given in Eq. 3.5.3 in supplement 1 and is plotted in Fig. 3.5.3 also in supplement 1.

- K16 G16 The transfer function of the reference driver cathode follower Fig. 3.6.1 of supplement 1. It is the ratio of the output at point 16 to the input at point 18. Its response is given in Eq. 3.6.1 of supplement 1 and is plotted in Fig. 3.6.2 also in supplement 1.

- K17a G17a-The transfer functions of the reference amplifier Fig. 3.7.1 of supplement 1 with R35-2 equal to zero. It is the ratio of the output at point 18 to the input at point 22. Its response is given in Eq. 3.7.1 of supplement 1 and is plotted in Fig. 3.7.2 also in supplement 1.

- K17<sub>b</sub> G17<sub>b</sub> The transfer function of the reference amplifier Fig. 3.7.1 of supplement 1 with R35-2 equal to 5K. It is the ratio of the output at point 18 to the input at point 22. Its response is given in Eq. 3.7.2 of supplement 1 and is plotted in Fig. 3.7.2 also in supplement 1.

- K18 G18 The transfer function of the input circuit to the reference amplifier Fig. 3.8.1 of supplement 1. It is the ratio of the output at point 22 to the common mode input at points C1 and C5. Its response is given in Eq. 3.8.1 of supplement 1 and is plotted in Fig. 3.8.2 also in supplement 1.

- K<sub>A</sub> G<sub>A</sub> The differential forward gain transfer functions of the balanced differential amplifier for small signals. It is the ratio of the differential output at points 3a and 3b to the differential input at points 14a and 14b. It is generally specified with a 2nd subscript to designate a specific use.

- KAA GAA The forward gain transfer function to small signals in side A of the differential amplifier. It is the ratio of the output signal at point 3a to an input signal at point 14a when the signal at points 14b is equal but of opposite phase to the signal at 14a.

- K<sub>AB</sub> G<sub>AB</sub> The forward gain transfer function to small signals in side B of the differential amplifier. It is the ratio of the output signal at point 3b to an input signal at

6M-3284

point 14b when the signal at point 14a is equal but of opposite phase to the signal at 14b.

- K<sub>AD</sub> G<sub>AD</sub> The differential forward gain transfer function of the balanced differential amplifier for small signals when the amplifier is used to drive the D.D. display lines. It is the ratio of the differential output at points 3<sub>a</sub> and 3<sub>b</sub> to the differential input at points 14a and 14b. K<sub>AD</sub> G<sub>AD</sub> is shown to be the product of K3 G3, K5 G5, K7 G7, and K9 G9. It is shown schematically in Fig. 1.1.2 and its response is plotted in Fig. 1.1.3.

- $K_{AS} G_{AS}$  The differential forward gain transfer function of the balanced differential amplifier for small signals when the amplifier is used to drive the S.D. display lines. It is the ratio of the differential output at points  $3_a$  and  $3_b$  to the differential input at points  $14_a$  and  $14_b$ .  $K_{AS} G_{AS}$  is shown to be the product of  $K_1 G_1$ .  $K_5 G_5$ ,  $K_7 G_7$ , and  $K_9 G_9$ . It is shown schematically in Fig. 1.1.2 and its response is plotted in Fig. 1.1.3.

- K<sub>B</sub> G<sub>B</sub> The differential closed loop response of the differential amplifier. It is generally specified with a 2nd subscript to designate a specific use.

- K<sub>BD</sub> G<sub>BD</sub> The differential closed loop response of the differential amplifier for small signals when the amplifier is used to drive the DD display lines. It is the ratio of the differential output at points 3a and 3b to the differential input at points 14a and 14b when the output is closed to the input through K13 G13. Its response is given by Eq. 1.1.3 and is plotted in Figs. 1.1.5b and 1.1.7.

- K<sub>BS</sub> G<sub>BS</sub> The differential closed loop response of the differential amplifier for small signals when the amplifier is used to drive the SD display lines. It is the ratio of the differential output at points 3a and 3b to the differential input at points 14a and 14b when the output is closed to the input through K<sub>13</sub> G<sub>13</sub>. Its response is given by Eq. 1.1.3 and is plotted in Figs. 1.1.5a and 1.1.6.

- K<sub>C</sub> G<sub>C</sub> The common mode forward gain transfer function of the balanced differential amplifier for small signals. It is the ratio of the common mode output at points 3a and 3b to the common mode input at points 14a and 14b. It generally specified with a 2nd subscript to designate a specific use.

- K<sub>CA</sub> G<sub>CA</sub> The forward gain transfer function to small signals in side A of the differential amplifier. It is the ratio of the output signal at point 3a to the input signal at

Page 25

14a when the signals at points 14a and 14b are equal.

K<sub>CB</sub> G<sub>CB</sub> - The forward gain transfer function to small signals in side B of the differential amplifier. It is the ratio of the output signal at point 3b to the input signal at point 14b when the signals at point 14a and 14b are equal.

$K_{CD}$  G<sub>CD</sub> - The common mode transfer function of the balanced differential amplifier for small signals when the amplifier is used to drive the D.D. display lines. It is the ratio of the common mode output at points 3<sub>a</sub> and 3<sub>b</sub> to the common mode input at points 14<sub>a</sub> and 14<sub>b</sub>. K<sub>CD</sub> G<sub>CD</sub> is shown to be the product of K<sub>4</sub> G<sub>4</sub>, K<sub>6</sub> G<sub>6</sub>, K<sub>8</sub> G<sub>8</sub>, and K<sub>10</sub> G<sub>10</sub>. It is shown schematically in Fig. 1.2.2 and its response is plotted in Fig. 1.2.3.

$K_{CS} G_{CS}$  - The common mode transfer function of the balanced differential amplifier for small signals when the amplifier is used to drive the S.D. display lines. It is the ratio of the common mode output at points 3a and 3b to the common mode input at points 14a and 14b. K<sub>CS</sub> G<sub>CS</sub> is shown to be the product of K<sub>2</sub> G<sub>2</sub>, K<sub>6</sub> G<sub>6</sub>, K<sub>8</sub> G<sub>8</sub> and K<sub>10</sub> G<sub>10</sub>. It is shown schematically in Fig. 1.2.2 and its response is plotted in Fig. 1.2.3.

- $K_D G_D$  The total feed-back transfer function between points  $C_1$ ,  $C_5$  and  $14_a$  and  $14_b$ . It is shown to be the product of  $K_{15} G_{15}$ ,  $K_{16} G_{16}$ ,  $K_{17} G_{17}$ ,  $K_{18} G_{18}$ . It is shown schematically in Fig. 1.2.2 and is plotted in Fig. 1.2.4.

- KE G<sub>E</sub> Composite transfer function used to simplify the solution of the common mode transfer function of the amplifier. Its mathematical expression is given in Eq. 1.2.3. It is generally specified with a second subscript to denote its use.

- K<sub>ED</sub> G<sub>ED</sub> The expression for K<sub>E</sub> G<sub>E</sub> when the amplifier is used to drive the D.D. lines. Its solution is obtained by using Figs. 1.2.8 and 1.2.8b to solve Eq. 1.2.3. Its final solution is plotted in Fig. 1.2.10.

- K<sub>ES</sub> G<sub>ES</sub> The expression for K<sub>E</sub> G<sub>E</sub> when the amplifier is used to drive the S.D. lines. Its solution is obtained by using Figs. 1.2.7 and 1.2.8a to solve Eq. 1.2.3. Its final solution is plotted in Fig. 1.2.9.

K<sub>F</sub> G<sub>F</sub> - Composite transfer function is used to simplify the solution of the total common mode transfer function of the amplifier. Its mathematical expression is given in Fig. 1.2.5. Its final solution is plotted in Fig. 1.2.6.

- KG<sub>CM</sub> The overall common mode transfer function of the display line driver. Its mathematical solution is given in Eq. 1.2.1. Its behavior is plotted in Fig. 1.2.11 when the amplifier is used in driving the S.D. lines and in Fig. 1.2.12 when used for D.D. lines.

- KG<sub>DIFF</sub> The overall differential transfer function of the display line driver. Its mathematical expression is given in Eq. 1.1.1. Its behavior is plotted in Fig. 1.1.8 when the amplifier is used to drive the S.D. lines and Fig. 1.1.9 for the D.D. lines.

- S.D. Situation display. The portion of the entire display system which is exhibited on Charactron tubes.

- $\lambda$  A frequency dependant complex variable used to compare the common mode forward gain transfer function of the line driver ( $K_C$  G<sub>C</sub>) under large signal behavior. It is defined in appendix B prior to Eq. B-14.  $\lambda$  relates the large signal gain of side A to the balanced small signal gain.

- $\lambda$ B A frequency dependant complex variable used to compare the common mode forward gain transfer functions of the line driver ( $K_C$  G<sub>C</sub>) under large signal behavior. It is defined in appendix B prior to Eq. B-14.  $\lambda$ B relates the large signal gain of side B to the balanced small signal gain.

- $S_A$  A frequency dependant complex variable used to compare the differential transfer function of the line driver  $(K_A G_A)$  under large signal behavior. It is defined in appendix A prior to Eq. A-12. It relates the large signal gain of side A to the small signal balance gain.

- $S_B$  A frequency dependant complex variable used to compare the differential transfer function of the line driver  $(K_A G_A)$  under large signal behavior. It is defined in appendix A prior to Eq. A-12. It relates the large signal gain of side B to the small signal balance gain.

List of Illustrations

| Fig. | 0.1    | E-75792      | Complete Schematic of Display Line Driver                                                                                                      |

|------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. | 1.1.1  | (SA-65908)   | Complete Differential Transfer Function of<br>Display Line Driver                                                                              |

| Fig. | 1.1.2  | (SA-65921)   | Differential Forward Gain Transfer Function<br>of Display Line Driver                                                                          |

| Fig. | 1.1.3  | (B-48756-G)  | Differential Forward Gain of Display Line<br>Driver                                                                                            |

| Fig. | 1.1.4  | (SA-65920)   | Simplified Differential Transfer Function<br>of Display Line Driver                                                                            |

| Fig. | 1.1.5  | (B-48755-G)  | Differential Open Loop Gain of Display Line .<br>Driver                                                                                        |

| Fig. | 1.1.5a | (SA-48781-G) | Evaluation of K <sub>BS</sub> G <sub>BS</sub> from K <sub>AS</sub> G <sub>AS</sub> K <sub>13</sub> G <sub>13</sub><br>S.D. Display Line Driver |

| Fig. | 1.1.5b | (SA-48782-G) | Evaluation of KBD GBD from $K_{AD}$ G <sub>AD</sub> K <sub>13</sub> G <sub>13</sub> D.D. Display Line Driver                                   |

| Fig. | 1.1.6  | (SB-48765-G) | Differential Closed Loop Response K <sub>B</sub> G <sub>B</sub><br>for S.D. Display Line Driver                                                |

| Fig. | 1.1.7  | (SB-48767-G) | Differential Closed Loop Response $K_B$ GB for D.D. Display Line Driver                                                                        |

| Fig. | 1.1.8  | (SB-48768-G) | Differential Overall Transfer Function<br>KG <sub>DIFF</sub> for S.D. Display Line Driver                                                      |

| Fig. | 1.1.9  | (SB-48769-G) | Differential Overall Transfer Function<br>KG <sub>DIFF</sub> for D.D. Display Line Driver                                                      |

| Fig. | 1.2.1  | (SA-65909)   | Complete Common Mode Transfer Function<br>of Display Line Driver                                                                               |

| Fig. | 1.2.2  | (SA-65919)   | Common Mode Transfer Function Simplifications                                                                                                  |

| Fig. | 1.2.3  | (SB-48763-G) | Common Mode Amplitude and Phase Response                                                                                                       |

| Fig. | 1.2.4  | (SB-48764-G) | of Differential Amplifier<br>Amplitude and Phase Response of Mean Level<br>Regulator (Primary Feedback Transfer Function).                     |

| Fig. | 1.2.5  | (SA-65925)   | Simplified Common Mode Transfer Function<br>of Display Line Driver                                                                             |

| Fig. | 1.2.5a | (SA-48780-G) | Evaluation of $K_H G_H$ from $-K_D G_D/K_{14} G_{14}$<br>-Display Line Driver                                                                  |

| 6M-3284 Sup | oplement #2          | Page 28                                                                                                                                  |

|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2.6  | (SB-48766-G)         | Amplitude and Phase Response of Total Common<br>Mode Feedback Transfer Function                                                          |

| Fig. 1.2.7  | (SB-48770-G)         | Common Mode Open Loop Transfer Function<br>K <sub>F</sub> G <sub>F</sub> K <sub>CS</sub> G <sub>CS</sub> for S.D. Display Line Driver    |

| Fig. 1.2.8  | (SB-48771-G)         | Common Mode Open Loop Transfer Function $K_F \ G_F \ K_{CD} \ G_{CD}$ for D.D. Display Line Driver                                       |

| Fig. 1.2.8a | (SA-48783-G)         | Evaluation of K <sub>ES</sub> G <sub>ES</sub> from K <sub>F</sub> G <sub>F</sub> K <sub>CS</sub> G <sub>CS</sub> for Display Line Driver |

| Fig. 1.2.8b | (SA=48784-G)         | Evaluation of $K_{ED}$ G <sub>ED</sub> from K <sub>F</sub> G <sub>F</sub> K <sub>CD</sub> G <sub>CD</sub> for Display Line Driver        |

| Fig. 1.2.9  | (SB-48772-G)         | Common Mode Closed Loop Transfer Function<br>K <sub>ES</sub> G <sub>ES</sub> for S.D. Display Line Driver                                |

| Fig. 1.2.10 | (SB_48773-G)         | Common Mode Closed Loop Trnasfer Function<br>K <sub>ED</sub> G <sub>ED</sub> for D.D. Display Line Driver                                |

| Fig. 1.2.11 | (SB-48776-G)         | Common Mode Overall Transfer Function KG <sub>CM</sub><br>for S.D. Display Line Driver                                                   |

| Fig. 1.2.12 | (SB-48775-G)         | Common Mode Overall Transfer Function KG <sub>CM</sub><br>for D.D. Display Line Driver                                                   |

| Fig. 1.3.1  | (SA-48777-G)         | Differential Response to Low Frequency<br>Common Mode Input (Display Line Driver)                                                        |

| Fig. 1.3.2  | (SA-48779-G)         | Common Mode Response to Low Frequency<br>Differential Input (Display Line Driver)                                                        |

| Fig. 1.4.1  | (SA-66073)           | Equivalent Output of Line Driver                                                                                                         |

| Fig. 1.4.2  | <b>(SA-</b> 48712-G) | Theoretical Operating Limits Line Driver<br>Output Stage                                                                                 |

| Fig. 1.4.3  | (SA-48774-G)         | Limits on Peak-to-Peak Differential<br>Output Voltage from Line Driver with<br>336 ohm Plate Load Resistor in Output                     |

Stage

Signed: Henry E. Zieman Henry E. Zieman Joseph Kriensky Jøseph Kriensky

HEZ: JK:ec

| 6M-3284                                                                                                                                                                                                                                                                                                                                                   | Supplement #2                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 6M-3284<br>Attachments<br>Fig. 0.1<br>Fig. 1.1.1<br>Fig. 1.1.2<br>Fig. 1.1.3<br>Fig. 1.1.5<br>Fig. 1.1.5<br>Fig. 1.1.5a<br>Fig. 1.1.5b<br>Fig. 1.1.6<br>Fig. 1.1.6<br>Fig. 1.1.7<br>Fig. 1.1.7<br>Fig. 1.1.8<br>Fig. 1.1.9<br>Fig. 1.2.1<br>Fig. 1.2.2<br>Fig. 1.2.3<br>Fig. 1.2.4<br>Fig. 1.2.5<br>Fig. 1.2.5a<br>Fig. 1.2.6<br>Fig. 1.2.7<br>Fig. 1.2.8 | E 75792<br>SA 65908<br>SA 65921<br>B 48756-G<br>SA 65920<br>B 48755-G<br>SA 48781-G |

| Fig. 1.2.8                                                                                                                                                                                                                                                                                                                                                | SB 48771-G                                                                          |

| Fig. 1.2.8a                                                                                                                                                                                                                                                                                                                                               | SA 48783-G                                                                          |

| Fig. 1.2.9                                                                                                                                                                                                                                                                                                                                                | SB 48772-G                                                                          |

| Fig. 1.2.10                                                                                                                                                                                                                                                                                                                                               | SB 48773-G                                                                          |

| Fig. 1.2.11                                                                                                                                                                                                                                                                                                                                               | SB 48776-G                                                                          |

| Fig. 1.2.12                                                                                                                                                                                                                                                                                                                                               | SB 48775-G                                                                          |

| Fig. 1.3.1                                                                                                                                                                                                                                                                                                                                                | SA 48777-G                                                                          |

| Fig. 1.3.2                                                                                                                                                                                                                                                                                                                                                | SA 48779-G                                                                          |

| Fig. 1.4.1                                                                                                                                                                                                                                                                                                                                                | SA 66073                                                                            |

| Fig. 1.4.2                                                                                                                                                                                                                                                                                                                                                | SA 48712-G                                                                          |

| Fig. 1.4.3                                                                                                                                                                                                                                                                                                                                                | SA 48774-G                                                                          |

|                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |

Page 29

8M-7-54-Boston Blue Print

KANTEL & ESER CO. BARINU. S.A.

8M-7-54-Boston Blue Print

K-E SEMI-LOGARITHMIC 309-94L

SA-48781-G

KOE SEMI-LOGARITHMIC 359-94L

KOE SEMI-LOGARITHMIC 359-94L

1

.

.

KOE SEMI-LOGARITHMIC 359-94L

8M-7-54-Boston Blue Print

Key SEMI-LOGARITHMIC 359-94L

| SA-65925 | TOLERANCES NOT OTHERWISE SPECIFIED<br>DECIMAL ± .005 FRACTIONAL ± 1/64 ANGULAR ± 1/69 |

|----------|---------------------------------------------------------------------------------------|

| 5 M -    | DIMENSIONS ENCLOSED THUS                                                              |

.

.

FIGURE 1.2.5

|     |     |     |     |     |     |     |     |     | G   | RA  | DE | I | I F | RE | LIM | INA | ARY | DE |   |       |        |       |     |        |        |          |      |      |    |          |      |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|---|-----|----|-----|-----|-----|----|---|-------|--------|-------|-----|--------|--------|----------|------|------|----|----------|------|

| L   |     | GR  | AD  | ED  | B   | Y:  | DA  | TE  | :   |     |    | - |     |    |     | _   | -   | _  |   | -     | ITEM   |       |     | MATER  | RIAL - | DESCRIPT | FION |      |    | PART NO. | QTY. |

|     |     |     |     |     |     |     |     |     |     |     |    |   |     |    |     |     |     |    |   | APPD. | ма     | SSAC  |     |        | i II   |          | TUTE | E OF | TE | CHNOLO   | ĠΥ   |

|     |     |     |     | •   |     |     |     |     |     |     |    |   |     |    |     |     |     |    |   | DATE  | SIM    |       |     | COMM   |        |          |      |      |    | R FUNCT  |      |

|     |     |     |     |     |     |     |     |     |     |     |    |   |     |    |     |     |     |    |   | CN#   | SCALE: |       |     | DR. 74 | 18     | Ziem     | an   |      | CA |          |      |

| -20 | -19 | -18 | -17 | -16 | -15 | -14 | -13 | -12 | -11 | -10 | Ŷ  | φ | -7  | 9  | 10  | 4-  | 6   | 2  | ī | CHG.  | ENG. g | ilman | СК. |        | Ľ      | APPD.    |      |      |    | 659      |      |

8M-7-54-Boston Blue Print

5 A - 48780 - G

.

KENFIL & REER CO. MORTHULLA

KEDFFLLAESER CO. MILITIANS A CYCLES X 60 DIVISIONS

KEUFFEL & ESER CO. MANTHU. A.

KON SEMI-LOGARITHMIC 359-94L

| SA-66073  | TOLERANCES NOT OTHERWISE SPECIFIED<br>DECIMAL ± .005 FRACTIONAL ± 1/64 ANGULAR ± 1/64 |

|-----------|---------------------------------------------------------------------------------------|

| 011 00010 | DIMENSIONS ENCLOSED THUS                                                              |

. .

0

FIGURE 1.4.1

|     |     | GR  |     |     |     |     |     |     | G   | RA  | DE | I  | I P | REI | IMI | NA | RY | DES |   |          | ITEM   |       |     | MATERIAL | L-DI | ESCRIPT | ION          |     | <u>.</u>   | PART NO. | QTY. |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|----|----|-----|---|----------|--------|-------|-----|----------|------|---------|--------------|-----|------------|----------|------|

|     |     |     |     |     |     |     |     |     |     |     |    |    |     |     |     |    |    |     |   | TE APPD. |        | di.   | HUS | LEXIN    | IN   | STIT    | UTE<br>73, M | OF  | т те<br>5. | CHNOLO   |      |

|     |     |     |     |     |     |     |     |     |     |     |    |    |     |     |     |    |    |     |   | DA       | EQU    | IVALI | ENT | OUTF     | PU.  | TO      | F            | LII | VE         | DRIVEI   | 2    |

|     |     |     |     |     |     |     |     |     |     |     |    |    |     |     |     |    |    |     |   | CN#      | SCALE: |       |     | DR. 74   | 8    | 9       | man          | _   | SA.        | .660     | 73   |

| -20 | -19 | -18 | -17 | -16 | -15 | -14 | -13 | -12 | -11 | -10 | 6- | -8 | -7  | 9-  | ŝ   | 4- | 6- | -2  | ī | CHG.     | ENG. E | 3.    | ск. |          | ľ    | APPD.   |              |     |            |          | ~    |

8M-7-54-Boston Blue Print

Page 1 of 1

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

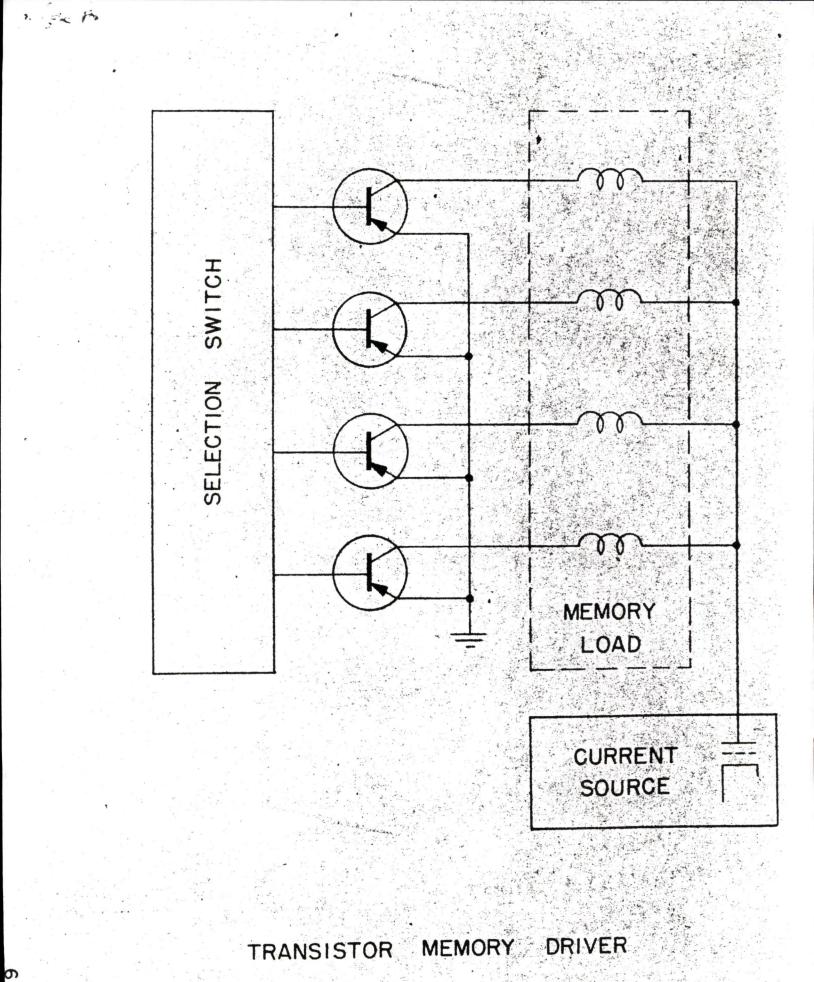

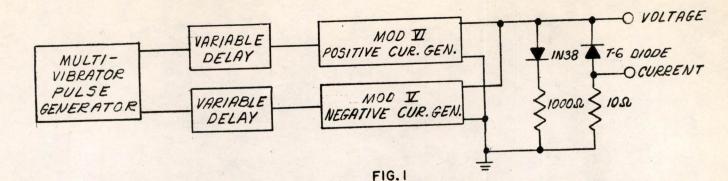

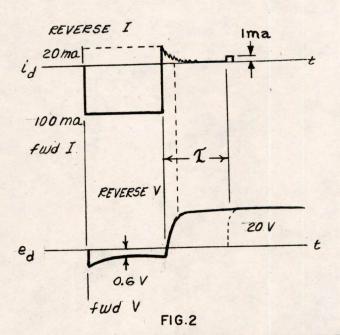

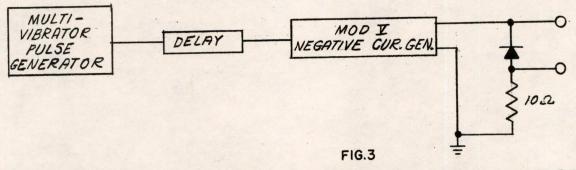

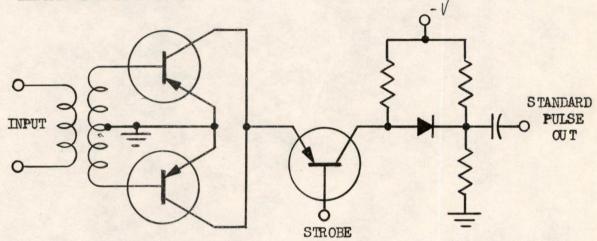

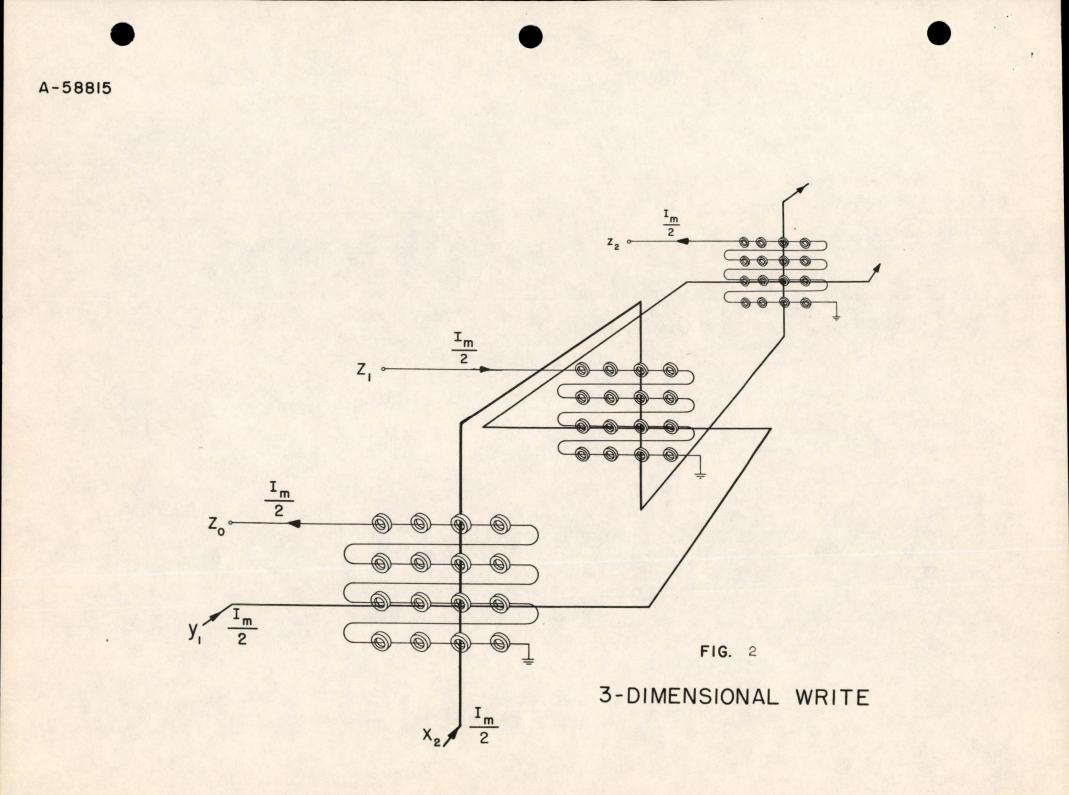

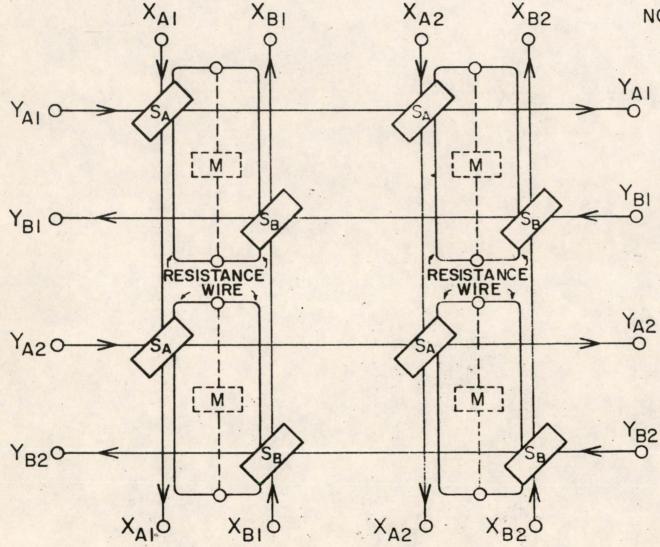

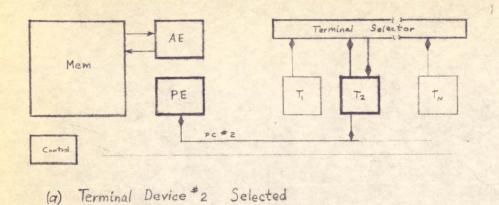

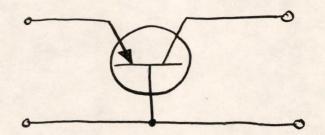

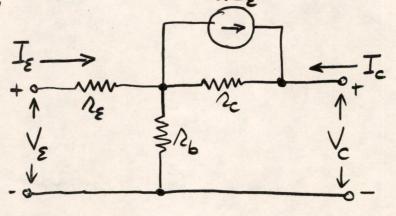

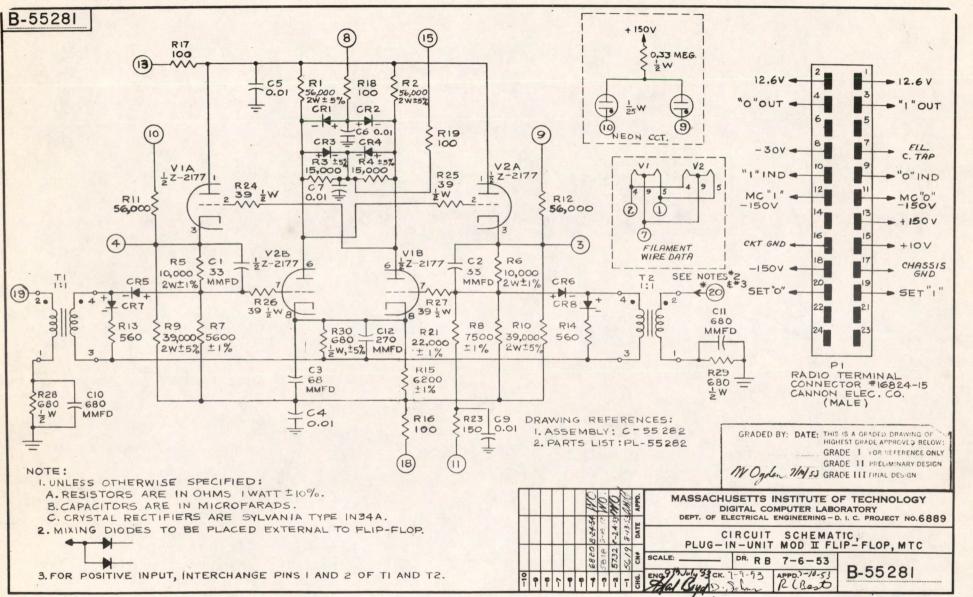

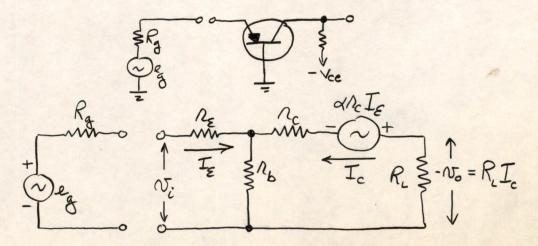

SUBJECT: TRANSISTOR CIRCUITS FOR DRIVING COINCIDENT CURRENT MEMORIES To: Memory Section, R. R. Everett. Fromt Kenneth H. Olsen Date: 21 January 1955 Approved: id R. Brown

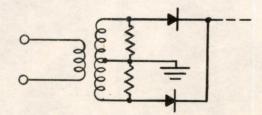

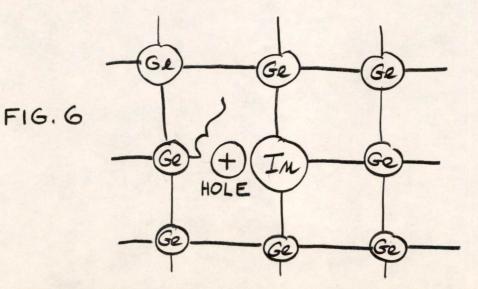

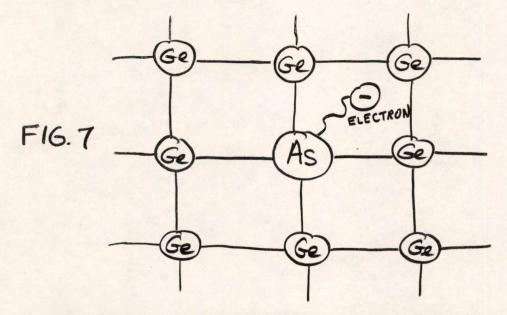

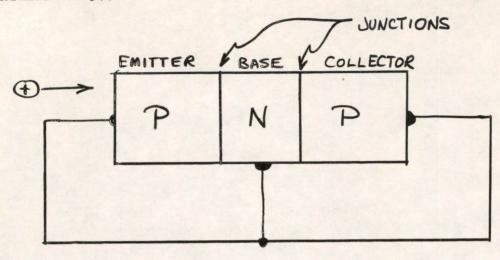

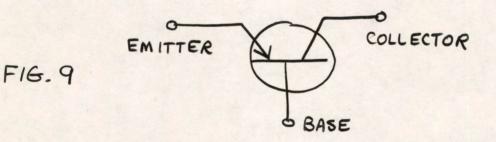

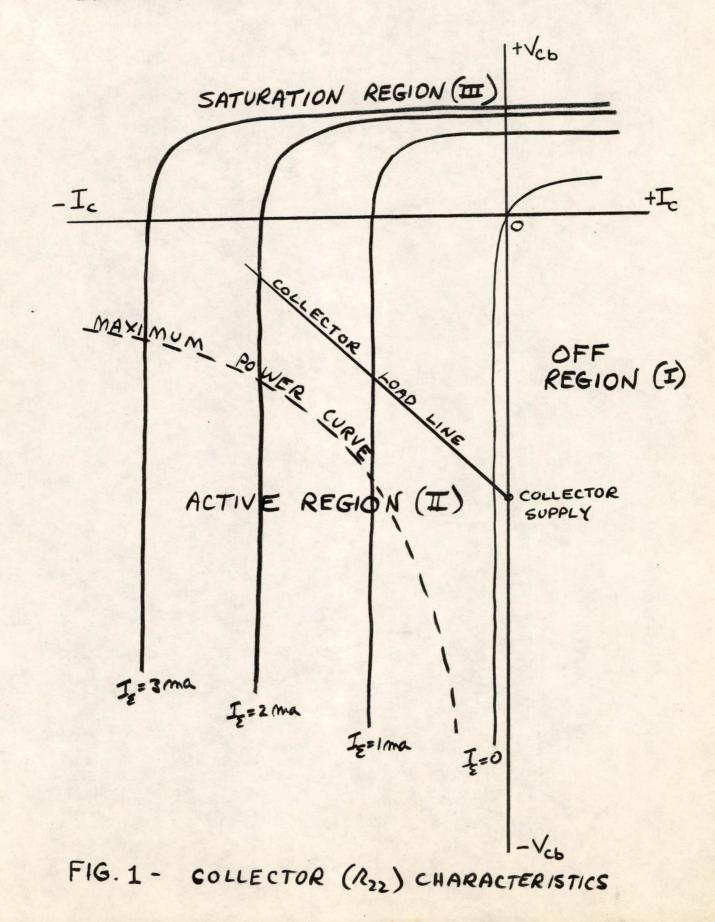

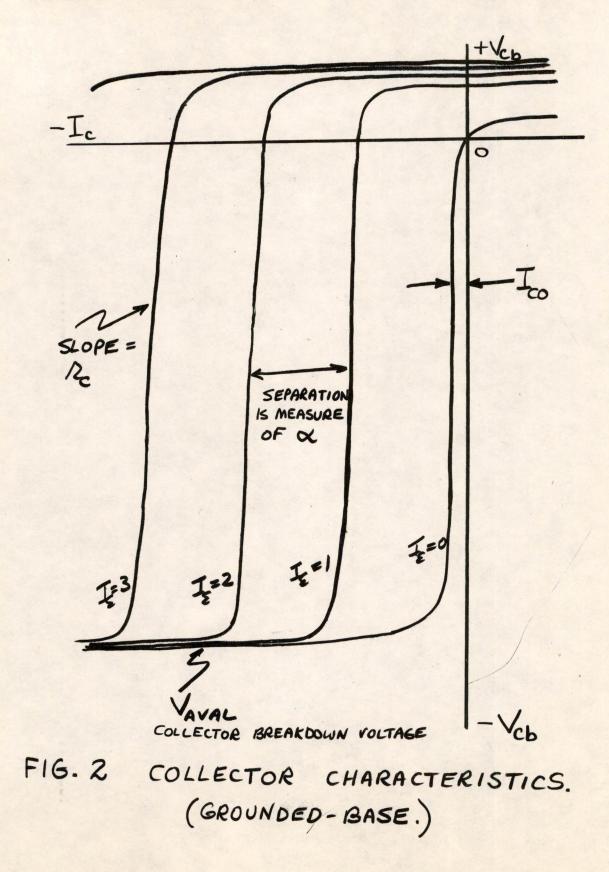

Abstract: Transistors can be made to pass large currents as needed in magnetic memories by turning off the currents while the transistors are being switched.

Some transistors have the very useful property of being able to pass large currents with only very low voltage drops across the transistor - and therefore, only low power dissipation. Although at the present time the allowed dissipation of fast transistors is small compared to the peak power needed to drive a large coincident-current memory, we may be able to drive memories, if we are careful to pass the large currents only when there is very low voltage across the transistor.