Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

SUBJECT: MAGNETIC CORE SHIFT REGISTER EVALUATOR

To: N. H. Taylor

From: Carl J. Schultz

Date: May 3, 1954

ABSTRACT: The problem of evaluation of magnetic core shift register is presented from the point of view of minimizing the time required to determine operating margins. A brief description of the operation of a shift register is given, together with the procedure involved in determining the operating margins. The method of evaluation used in the system is outlined and an example of the results obtained is shown. No attempt is made to establish criteria for optimizing shift register operating margins - that is a judgment which is reserved for a consideration of the shift register application and requirements.

#### A. Introduction

The realization of working magnetic core shift registers in the 100 KC range has been in the past a product of the art of combining engineering calculations with intuitively guided experimentation. The determination of the goodness of the product has been a particularly difficult job of evaluation because of the large number of variables involved. Every element in a magnetic core shift register is a factor which affects its operation, and in order that a useful register be born out of the labor of almost endless substitutions and time consuming investigations, it is desirable that a rapid method of experimentation be used. The automatic Evaluator described in this note performs the task of furnishing operating margins for a particular shift register in a small fraction of the time that would be required to find the information under the guidance of a human operator.

#### B. Shift Register Characteristics

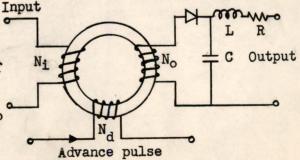

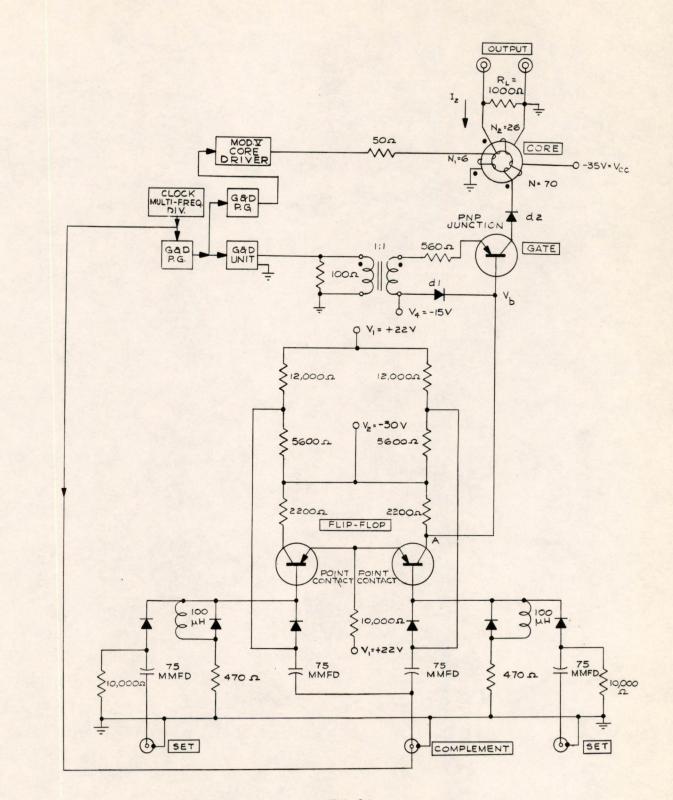

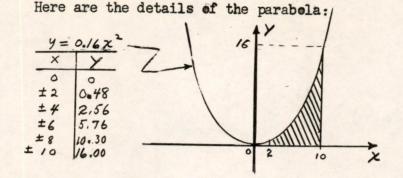

The type of register that is currently being investigated consists of

the elements shown in Fig. 1 for the typical stage. The magnetic material that is used for operation at shifting frequencies of 100 KC and above is Mo-Permalloy tape. The magnetic flux of the core must first be set in one direction by a flow of current through the input winding, which is connected to the output winding terminals of the previous stage.

Then an advance current pulse applied through the advance winding will set the magnetic flux in the opposite direction and will induce a voltage in the output winding. This voltage will cause current to flow in the forward direction of the diode. The capacitor will become charged through the forward resistance of the diode and the core output winding. However, it will discharge through the inductor, resistor, and the input winding of the succeeding stage of the shift register, thereby setting the magnetic flux of that core to the direction that may be defined as "zero". The condition of a core may be sensed at the time of application of the advance pulse. If the core had previously been set to "one," then the voltage induced in the output winding will be large during the advance pulse. If the core had been set to "zero" previously, only a small voltage will be induced in the output winding. The advance current pulse must be of such a duration that it will have ended soon enough in a particular stage of the register to allow the input current supplied from the coupling circuit of the preceding stage to be of sufficient amplitude and duration to set the flux to "one". This depends upon the capacitor discharge current magnitude and duration, which in turn is related to the selected values of R, L, C, the diode, the number of turns on the windings, and upon the previous advance current pulse amplitude and length. The coupling circuit serves to transfer the energy required to switch the succeeding core, and also to prevent energy from flowing in the backward direction to set the previous core to "one".

# C. Shift Register Operating Margins

The successful operation of the register depends upon the effective transfer of information from the core originally containing either a "one" or "zero" to the succeeding core. This transfer must be realized by means of the coupling circuit between the two cores. Every element in the coupling circuit, in addition to the advance pulse characteristics and the magnetic core characteristics, becomes a variable which makes the operation of the register either more or less successful. The timeconsuming task of combining these variables into an optimized working register can be resolved into a procedure which involves the following steps: (a) Design a coupling circuit for use with cores having particular flux change and switching time characteristics; (b) Construct at least four stages, connected so that the information circulates in the register; (c) Change the advance current pulse amplitude, length, and rise time and observe the limits for which the register continues to store and transfer all combinations of information successfully; (d) Decide whether the resulting margins represent a register which might be useful in a particular application (upon consideration of (1) the effects of advance pulse current driver tube deterioration, and (2) the required operating speed; (e) In the event that the operating margins do not represent a useful register, then, judicious changes of the variables should be made in order to shift the margins in the direction to fulfill the desired requirements, and (f) Retrace parts b, c, d, and e as many times as are necessary to obtain satisfactory limits of operation.

#### D. Methods of Iteration

One method of obtaining the data outlined in the preceding paragraph involves the complete manual manipulation of all variables, in addition to the manual injection into the register of all possible combinations of "ones" and "zeros" that constitute the storage and transfer pattern of information. This primitive method, when associated with the necessary changing of many patterns of information and of many variables in many stages of the register, places considerable strain upon the mental and physical capabilities of the human control element during the long period of time involved.

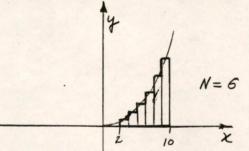

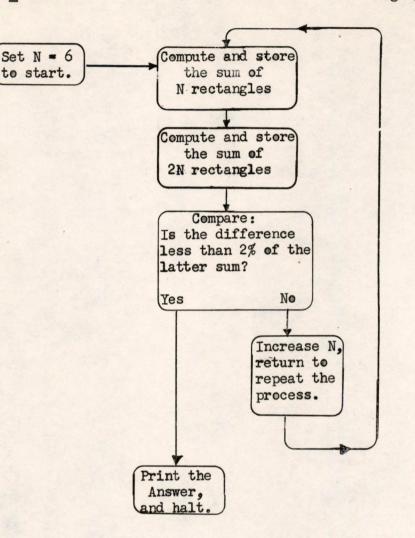

Another method involves the use of an electronic control system, which brings about an appreciable reduction in the time consumed and in operator fatigue. The system automatically varies the advance current pulse amplitude and length at a rapid rate and presents, on an oscilloscope, a matrix pattern of intensified spots to indicate successful operations of the shift register. Patterns of information are also changed automatically. All other parameters must still be varied manually, but since that part of the total data-accumulation time is small, little could be gained by further automatizing the procedure.

E. Automatic Evaluation

E.l System timing

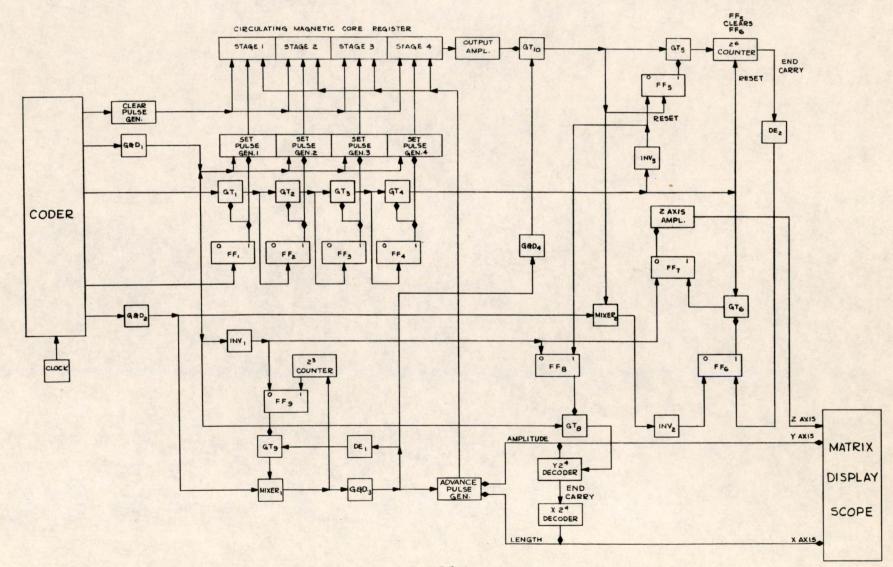

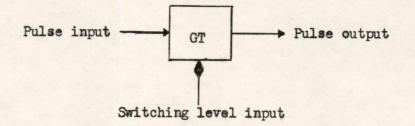

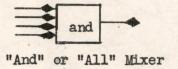

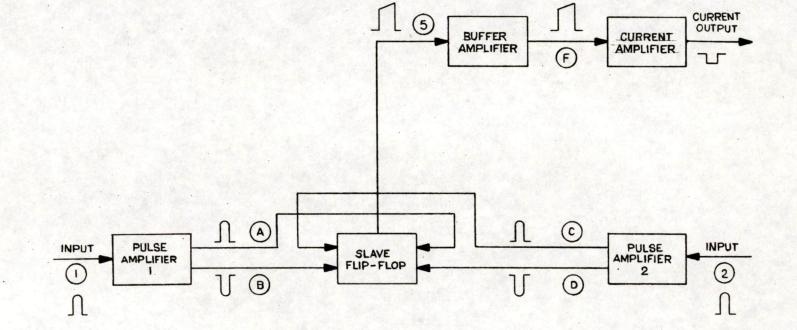

Figure 2 shows the block diagram of the system. An outline of the kind and the order of events that occur after each clock pulse is as follows (numbers indicate events displaced in time, and letters indicate events occurring simultaneously).

1. Time t<sub>1</sub> (clock pulse)

(A) "Clear" pulse occurs - this places the four cores of the register in the "zero" flux condition.

(B) Information "set" counter changes

$(FF_1-GT_1, FF_2-GT_2, FF_3-GT_3, FF_h-GT_h)$

- (a) Counter end carry pulse occurs if the previous counter number was llll and the display scope intensifies if the register output counter (FF5-GT5, 2<sup>6</sup> counter) had sensed the proper number (2<sup>6</sup>) of "ones" shifted out of the register during all the combinations of binary numbers since the previous llll.

- (b) "Set" pulse generators 1, 2, 3, and 4 (standard 7AK7 gate tube circuit) are open or closed according to the configuration of "ones" held by the Information "Set" counter flip-flops.

2. Time  $t_1 + t_2$  ( $t_2$  determined by  $G + D_1$ )

(A) "Set" pulse generators drive into the magnetic core register and set the cores to the same configuration of "ones" as contained in the Information "Set" counter.

(B) "Advance" pulse burst generator ring (MX<sub>1</sub>, G + D<sub>3</sub>, DE<sub>1</sub>, GT<sub>0</sub>) closes as a result of the change of state of  $FF_0$ .

(C) "Y" Decoder is pulsed if the last number held by the Information "Set" counter was llll and the end carry from that counter had opened  $GT_8$ . The change of output of the "Y" decoder then causes the following.

(a) Matrix Display'scope y-position is changed.

(b) "Advance" current pulse amplitude is changed to its next highest value, or to its minimum value if the Y decoder is reset (in this case, the Y decoder produces an end carry and changes the X decoder output, which in turn controls the advance current pulse width and also the Matrix Display 'scope x-position).

(D) Z axis amplifier input is changed by FF. - this ends the 'scope intensification pulse which presented a visual indication (on the Matrix Display 'scope) of the successful transfer and storage of information in the shift register.

3. Time  $t_1 + t_3$  ( $t_3 > t_2$ ,  $t_3$  determined by  $G + D_2$ )

(A) A pulse passes through MX, and INV, and appears at the zero input of FF. This closes  $GT_6$  at the beginning of each burst of eight advance current pulses.

(B) A series of eight pulses is generated in the advance pulse burst generator ring. This pulse burst serves two functions:

- (1) It initiates eight advance current pulses that transfer information twice around the 4-stage register (two complete cycles provide greater assurance of successful operation than only one cycle).

- (2) After the delay due to  $G + D_1$ , the pulses are used as strobe pulses which sense the presence of "one" and "zero" output signals from the shift register as they appear at the grid of  $GT_{10}$ . The output of  $GT_{10}$  then goes to the register output counter (FF<sub>5</sub>, GT<sub>5</sub>, 2<sup>6</sup> counter) and through MX<sub>2</sub> and INV<sub>2</sub> to FF<sub>6</sub>.

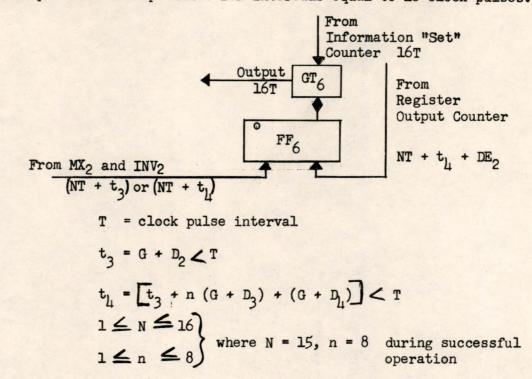

# E.2 Error Detection

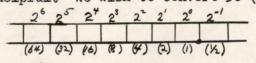

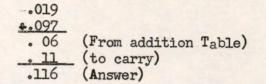

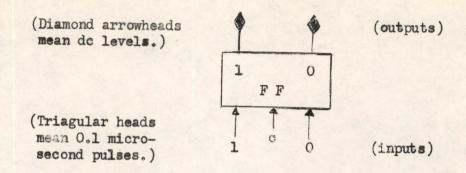

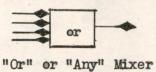

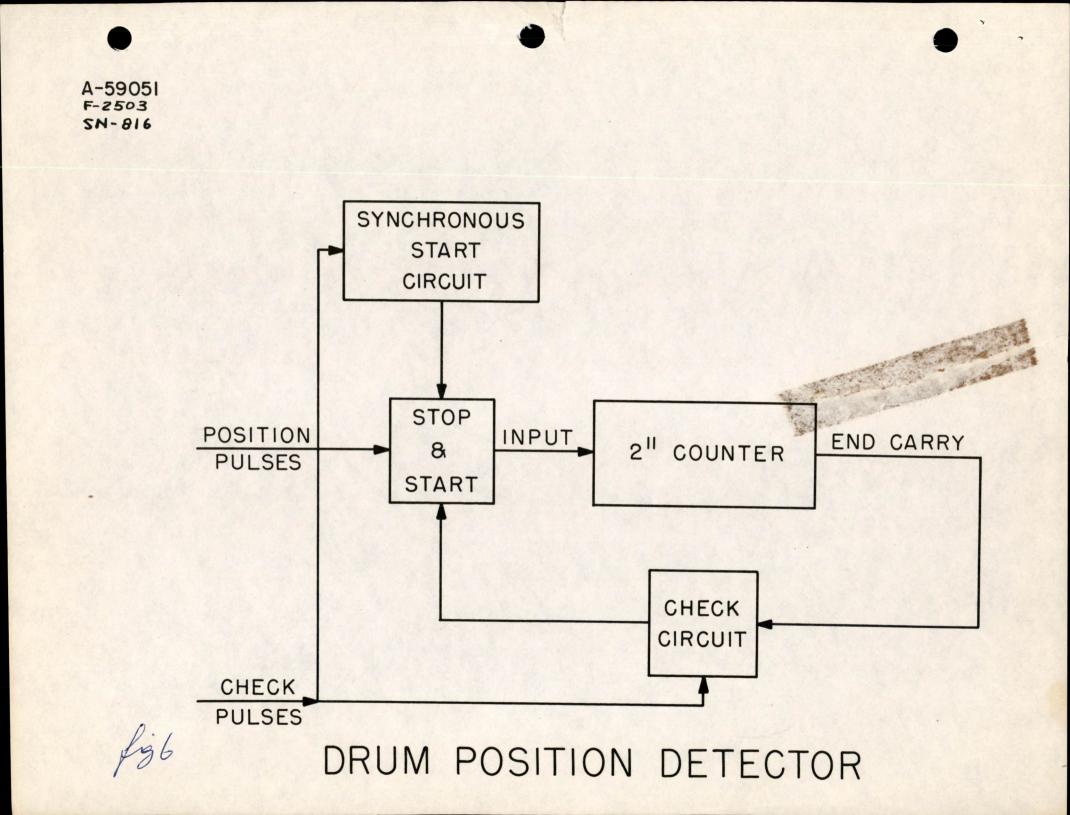

The successful transfer and storage of information in the shift register is determined by the occurrance of an end carry pulse from the Register Output counter just preceding an end carry pulse from the Information "Set" counter. The figure below shows the error detection system with its three inputs, one output, and associated timing. The cycle of operation is repetitive for intervals equal to 16 clock pulses.

The above arrangment assures that out of any number of shift register output pulses up to  $2^{12}$  - 1, only a precise count of  $2^6$  at the proper time will be detected and converted into an intensifying pulse on the Matrix Display 'scope. The occurance of  $2^{12}$  shift register output pulses is eliminated from becoming an indication of a successful operation by a toggle switch setting on the  $2^6$  lowspeed counter (Register Output Counter) by which FF5 clears FF6 and does not permit the generation of more than a single end carry from the Register Output Counter.

### F. Alternate Use of Evaluator

The application of the Evaluator has been extended to include the testing of a magnetic core counter employing the previously described shift register circuitry plus other circuits which perform the logical functions necessary for counting. This application eliminates the use of the Information "Set" counter and three of the "Set" pulse generators, since the number which is held by the magnetic core counter must be changed by a count of "l" for each operation and that is done by the core circuitry. In the testing of the circulating shift register, it is

necessary to change the information by control external to the register in order to completely determine the successful operation for all patterns of binary information. The magnetic core counter is tested for the successful storage and progressive counting through all the combination of four bits of information. If 25 "ones" are properly shifted out of the counter, the Matrix Display 'scope will indicate a successful operation for a particular value of current pulse length and amplitude.

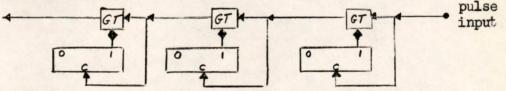

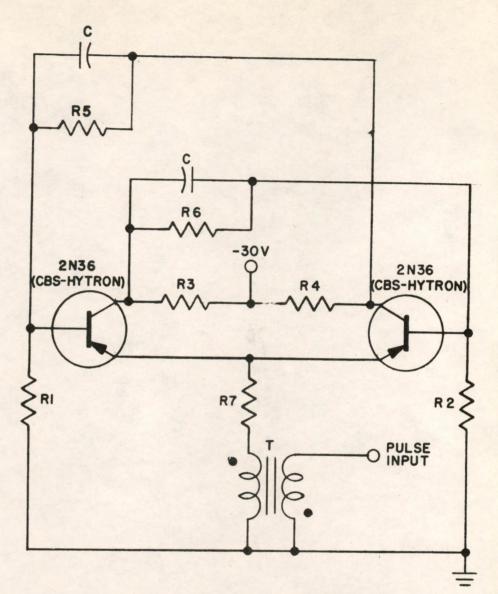

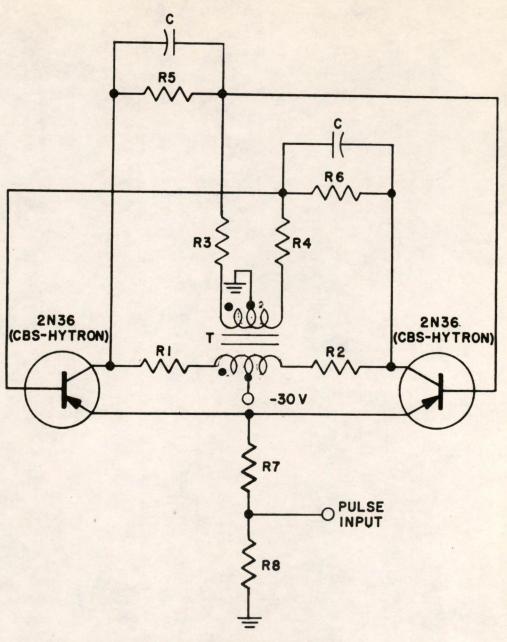

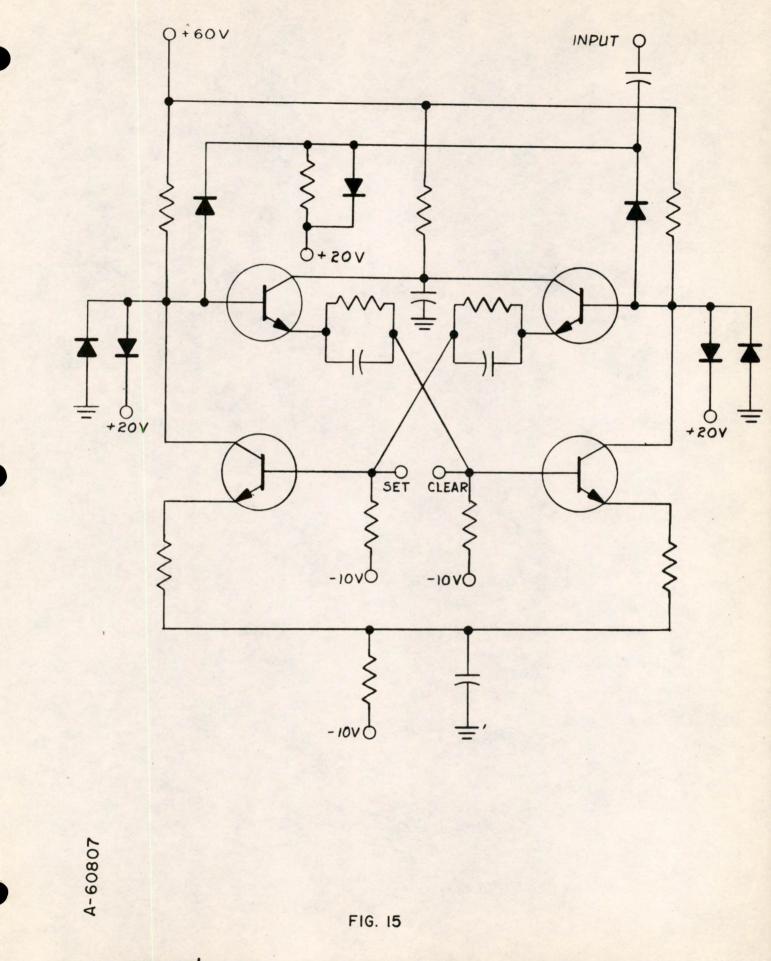

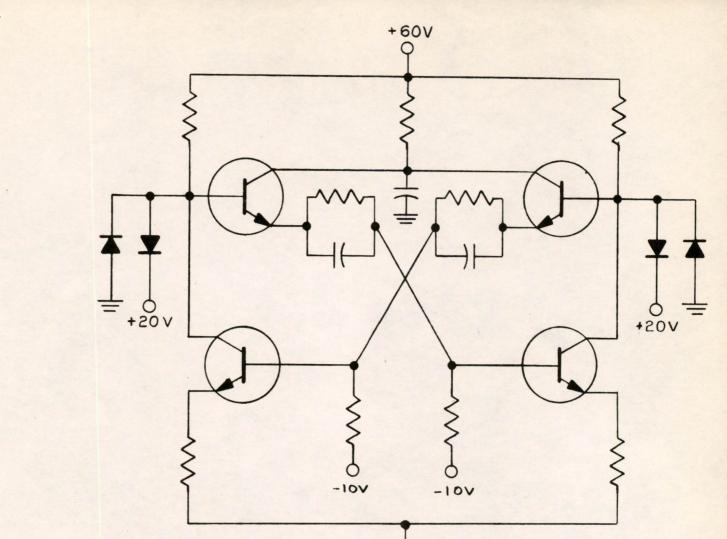

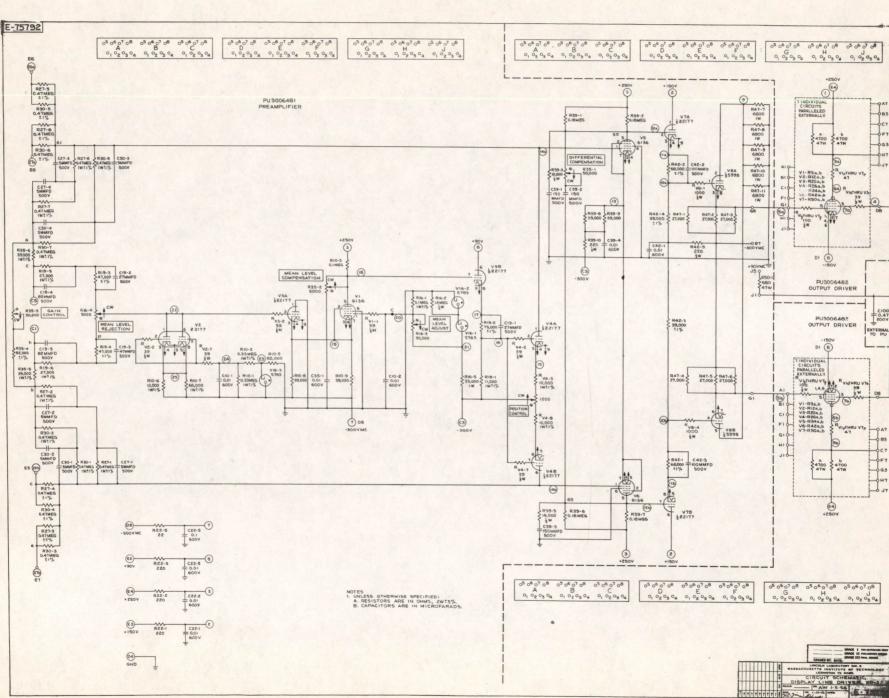

#### G. Equipment

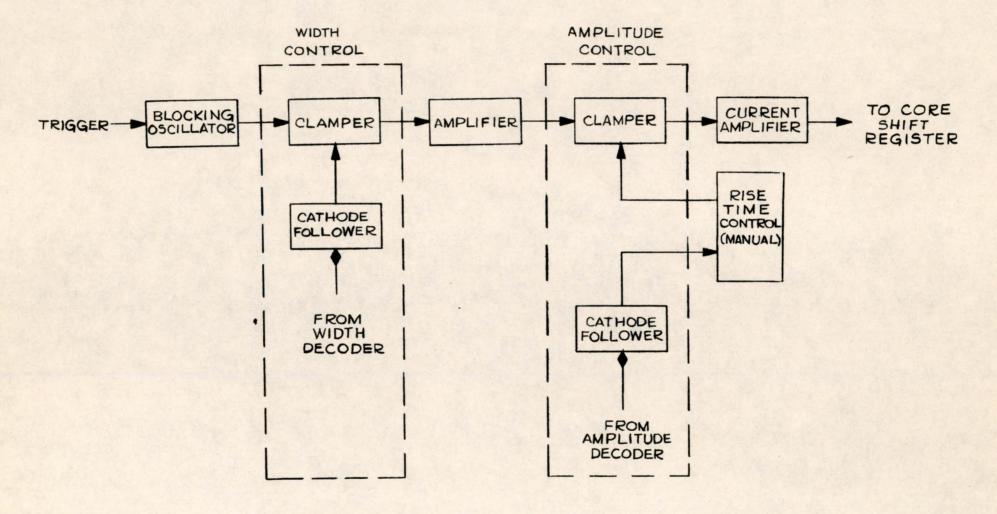

Standard test equipment is used for gate and delayed pulse generators, mixers, delays, 2<sup>6</sup> lowspeed counters, flip-flops and gates. The Matrix display 'scope is a DuMont 304-H. The "X" and "Y" decoders are made of plug-in type flip-flops. The Advance Pulse Generator is shown in block diagram form in Figure 3. The Clear Pulse Generator is similar to Figure 3, except that the "X" and "Y" decoder inputs and associated cathode followers are substituted for by manually operated amplitude and width controls. The Set Pulse Generators are similar to the Clear Pulse Generator, except that they contain 7AK7 current amplifiers rather than 6CD6's.

A feature of the Evaluator which increases its value as a time saver is the flexible arrangement of R, L, and C components. A wide range of values of each of the components has been assembled on rotary selector switches. Values of Resistance can be varied between 33 and 15,000 ohms with 26 intermediate values, C between 220 and 169,000  $\mu\mu$ fd, and L between 0.033 and 25 mh. This adequately covers the widest range of values of these components that can be presently expected to be used. Connections between components are made through plug-in type terminal boards and leads. Magnetic cores and associated windings are mounted on minature tube socket assemblies, and diodes are mounted in spring clips. All of these connections and assemblies allow easy replacement and rearrangement of the component parts.

# H. Results

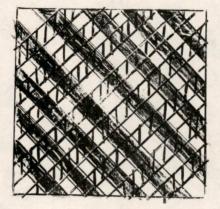

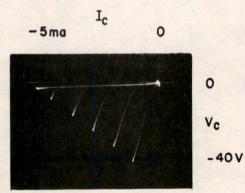

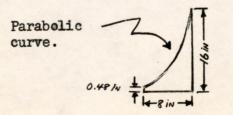

The sketch below shows a sample pattern that appeared in the Matrix Display 'scope during the testing of a 4-stage shift register made of 1/8 mil Mo-Permalloy cores (5/16" diameter, 1/8" wide, 20 wraps). The coupling circuit is of the same configuration as that shown in Figure 1. The component values are:

> C = 1000  $\mu\mu$ fd, L = 15 mh, R = 4700 ohms, N<sub>o</sub> = 100 turns, N<sub>i</sub> = 150 turns, N<sub>d</sub> = 25 turns.

The rise time of the pulse was  $0.3 \ \mu$ sec and the fall time was  $0.4 \ \mu$ sec. The intensified spots indicate the coordinates at which the shift register successfully stores and transfers all combinations of four bits of binary information. The shifting rate was 100 KC and a complete display of the matrix appeared at minimum intervals of approximately two seconds.

|       | 10 | 5. | • | • | • | • | •  | • |   | 0 |   |    | •  |    | •  | ٠  | •  |

|-------|----|----|---|---|---|---|----|---|---|---|---|----|----|----|----|----|----|

|       | 15 | 5. | • | • | • | • | •• |   |   |   | • |    |    | •  | •  |    | •  |

| 4     | 14 | !. |   | • | • |   |    |   |   | 0 |   |    |    |    | •  | •  | •  |

| a     | 13 | ?. |   |   |   |   |    |   |   |   |   |    |    |    |    |    |    |

| 5     | 12 |    |   |   |   |   |    |   |   | • |   |    |    |    |    |    |    |

| 5     | 11 |    |   |   |   |   |    |   |   |   |   |    | 6  |    |    |    |    |

| K     | 10 |    |   |   |   |   |    |   |   |   |   |    |    |    |    |    |    |

| 11    | 9  |    |   |   |   |   |    |   |   |   | - | -  |    |    |    |    |    |

| 5     | 8  |    |   |   | - | - | -  | - |   | - | - | -  | -  |    |    |    |    |

| Y     |    |    |   | - | - | - | -  |   | - | - |   |    |    |    |    |    |    |

|       | 2  |    |   |   |   | - | -  |   | - | - |   | •  |    | •  |    |    | •  |

| W     | 6  | •  | • |   | - | • |    | • |   |   | • | •  | •  | •  | •  | •  | •  |

| PULSE | 5  |    | • |   |   | • | •  | • | • | • | • | •  | •  | •  | •  | •  | •  |

| 2     | 4  | •  | • | • | • | • | •  | • | • | • | • | •  | •  | •  | •  | •  | •  |

| Y     | 3  | •  | • | • | • | • | •  | • | • | • | • | •  | •  | •  | •  | •  | •  |

|       | 2  | •  | • | • | • | • | •  | • | • | • | • | •  | •  | •  | •  | •  | •  |

|       | 1  | •, | : | : | : | • | :  | : | : | : | : | :  | :  | 13 | :  | in | :  |

|       |    | 1  | 2 | 3 | 4 | 5 | 0  | 1 | 0 | 9 | N | // | 12 | 13 | 14 | 15 | 10 |

|                                      | Pulse                                               | Pulse                                                    |

|--------------------------------------|-----------------------------------------------------|----------------------------------------------------------|

| Unit                                 | Length                                              | Amplitude                                                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 1.3 μsec.<br>1.5<br>1.8<br>2.1<br>2.4<br>2.8<br>3.2 | 2.8 Amp. Turns<br>3.7<br>4.5<br>5.6<br>6.8<br>8.2<br>9.6 |

|                                      | 3.6                                                 | 10.9                                                     |

| 9<br>10<br>11<br>12                  | 4.0<br>4.4<br>4.9<br>5.4                            | 11.8<br>13.2<br>14.4<br>16.3                             |

| 13<br>14<br>15<br>16                 | 5.9<br>6.4<br>6.9<br>7.3                            | 18.0<br>19.8<br>21.3<br>22.5                             |

#### CONVERSION TABLE

#### I. Discussion of Results

Upon consideration of the results presented on the display 'scope there might arise the question: "How reliable is the information?" The degree of reliability is dependent upon the accuracy of the method of detecting the successful operation of the shift register. That is done in the Evaluator by counting the number of "ones" that are shifted serially past a particular point in the register during the storage and transfer of all possible combinations of four bits of binary information. The error detection system shown on page 5 then allows an indication of successful operation only when precisely the correct number of "ones" have been counted. Although this method does not preclude the possibility that a correct count might occur upon the transfer of one or several incorrect patterns of information during a cycle of operation, the possibility appears to be an extremely remote one. The observer can easily verify the successful operation at any particular value of advance pulse amplitude and width by (a) stopping the X and Y decoders from changing with each clock pulse, (b) displaying the 16 groups of shift register binary outputs during a cycle of operation, and (c) visually checking the number, sequence, and arrangments of the output pulses.

Signed: C.J. Schultz

Approved: J.F. Jacobs

CJS/rb Drawings: C-47094 A-47095 C-47094

7

FIG. 2 MAGNETIC CORE SHIFT REGISTER EVALUATOR

.

# A-47095

ADVANCE CURRENT PULSE GENERATOR

Distribution List for N. Taylor (When M-Notes are addressed to him)

# Internal Distribution

D. Arden The author R. Best

\* . . .

- D. Brown

- C. Corderman

- R. Çallahan

- W. Thomas A. Heineck

- J. Jacobs

- W. Linvill

- R. Mayer-

- P. Bagley

- R. Nelson

- K. Olsen

- W. Papian

- N. Taylor

- R. von Buelow

H. Wainwright C. W. Watt

J. W. Forrester R. R. Everett S. H. Dodd A. F. Falcione Division 6-Library (15 to 20 Copies) M's by B.Paine--1 copy to V. Savio A's--1 copy to R. Nelson

#### External Distribution

A. P. Kromer (10 Copies of M-Notes for I.B.M.)

Bldg. 32 - Library

Air Force Gambridge Research Center Attention: Document, Room--CRQ-SL-1. 230 Albany Street

R. Best #

Page 1 of 6

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

SUBJECT: BLOCKING OSCILLATOR CORE DRIVERS FOR USE IN DISPLAY GENERATOR BUFFER STORAGE

To: N.H. Taylor

From: Eli Anfenger

Date: 11 May 1954

Abstract: A cheap core driver has been built which is a blocking oscillator triggered from a standard pulse. The output pulse lengths are determined by lumped constant delay lines, the amplitude by the B# to bottoming of the tube excursions. For high current sources the pulse is amplified by a power pentode whose plate is driven from B+ to bottoming and transformed to the desired level.

#### Introduction

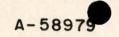

It was desired to develop a cheap drive for use in a display generator buffer storage as illustrated in Fig. 1. In this figure each winding represents the output transformer of a driver. The drivers are returned to voltages such that each core winding is held from conduction because of the switch action of the diode in series with it. The bit and word drivers are 40 volt pulse sources; the bit driver pulsing negatively and the word driver pulsing positively. Either driver alone will reduce the bias on the diode to zero, whereas the coincident operation of both drivers will give a 40 volt source to drive current through the core winding. Read is accomplished by a 150-volt pulse on a second core winding. The read windings are connected in series as dictated by the logical use of the information. A third winding on the core is the output terminals for read.

The requirements for the above circuits are as follows:-

- 1) Bit Driver

- a) Isolated 40-volt pulse max., 35-volt minimum at 28 ma.

- b) 3 µsec pulse.

- c) Driver must trigger from positive standard pulses +20 v. to +40 v.

- d) Driver must be capable of operating in a burst of 8 pulses spaced 10 µsec apart, with a burst repetition rate of 1000 cycles.

- 2) Word Driver

- a) Isolated 40-volt pulse max., 35-volt minimum zero to 800 ma.

- b) Good regulation from no load (no cores) to full load (32 cores)

- c) 4 µsec pulse.

- d) Driver must trigger from positive standard pulses of 10 to 40 volts.

- e) Repetition rate 1000 cycles.

- 3) Read Driver

- a) Isolated 150-volt pulse at 1 amp.

- b) 1 µsec pulse.

- c) Driver must trigger from positive standard pulse 20 to 40 volts.

- d) Repetition rate 1000 cycles.

#### Circuits

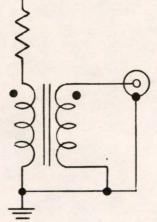

### 1) Bit Driver

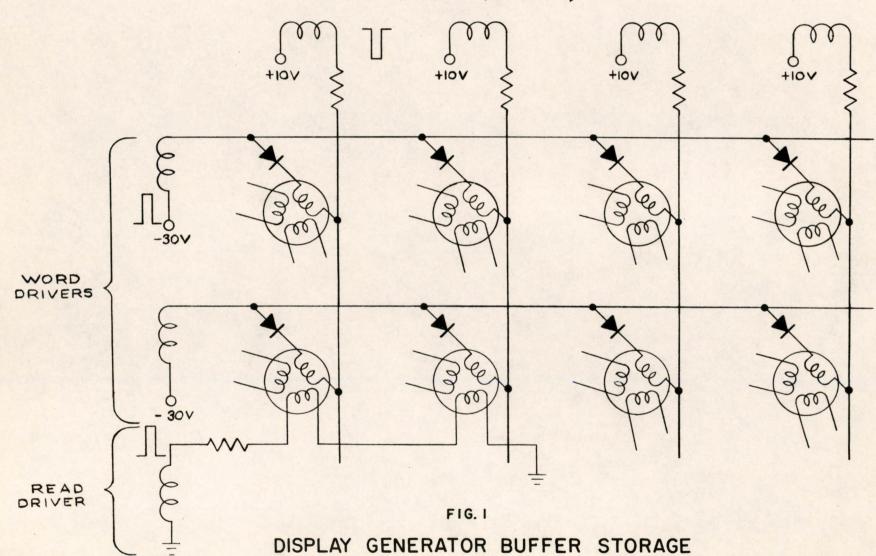

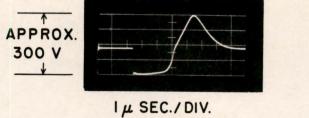

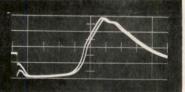

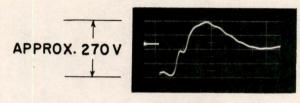

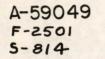

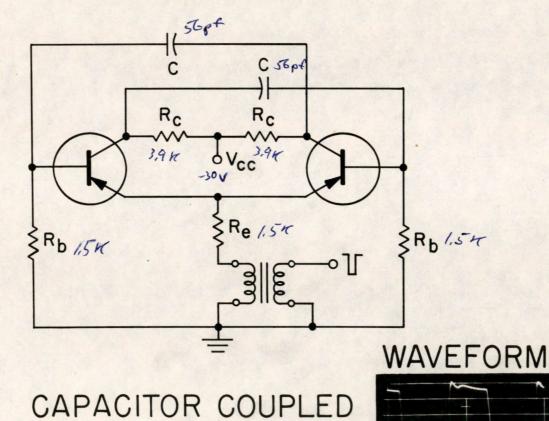

The bit driver circuit is shown in Fig. 2. It comsists of 1/2 5965 connected as a blocking oscillator. The pulse length is determined by a delay line in the grid circuit. The tube bottoms during the pulse. The 33 K resistor in the plate circuit reduces the overshoot and adds damping for stability. Delay of the Output pulse compared with the input pulse is about 0.2. The characteristic waveforms are shown in Fig. 3.

The input impedance to a pulse which will trigger the blocking oscillator is 400 ohms. The maximum cathode current is on the order of 80 ma. All possible voltage measurements were made directly on the plates of the scope. When the levels were too low to be read this way they were read through the amplifiers and calibration of the scope. In every case when direct and amplifier measurements were compared the amplifier measurements were about 30% higher than the direct measurements. Since all current measurements were made by measuring the drop in a small series resistor, it is assumed these readings are slightly high. Because of this observation those diagrams that have photographs show approximate voltages when the measurement could not be made directly on the scope plates. The maximum grid voltage during conduction of the tube is +7 volts.

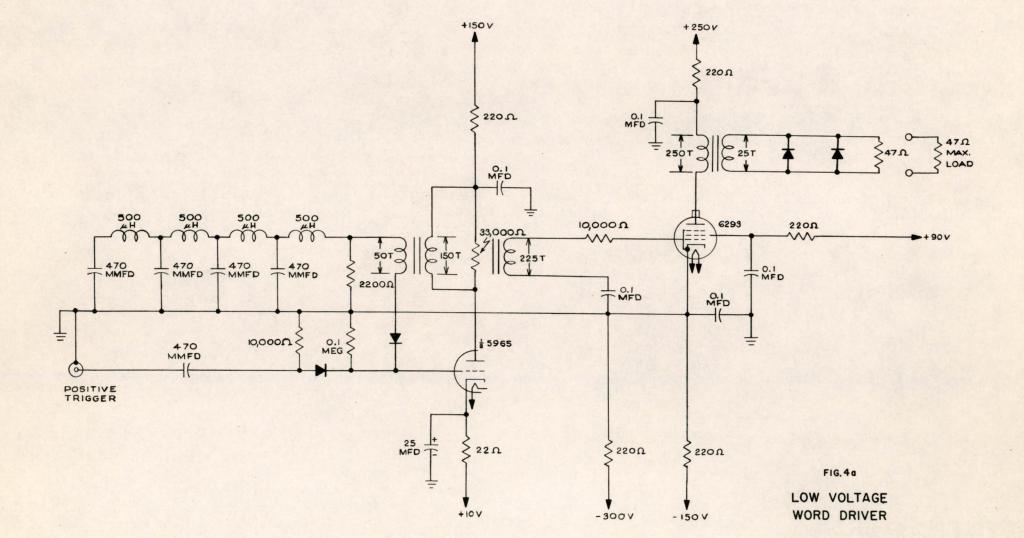

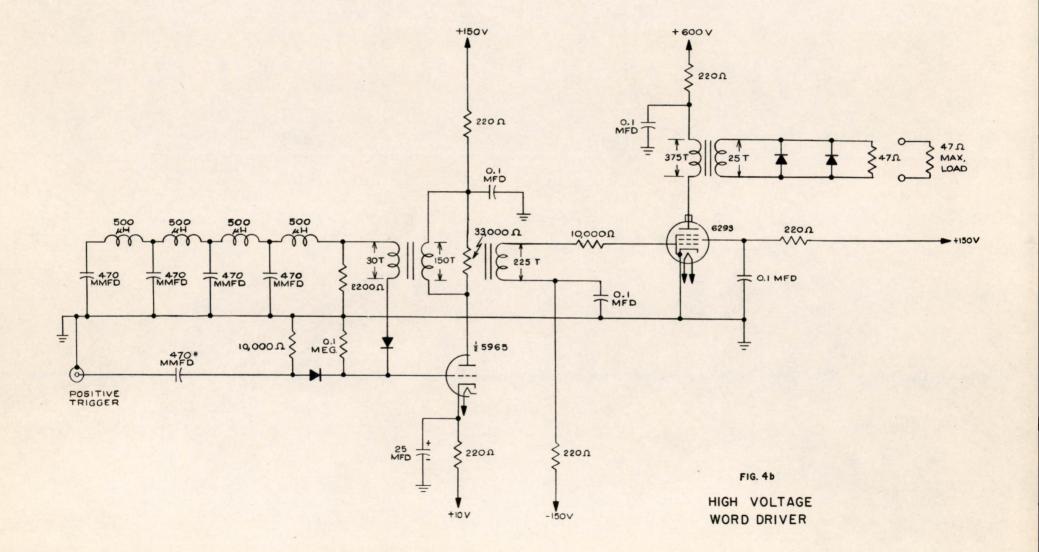

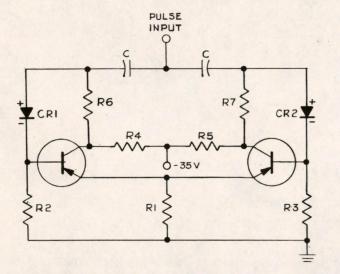

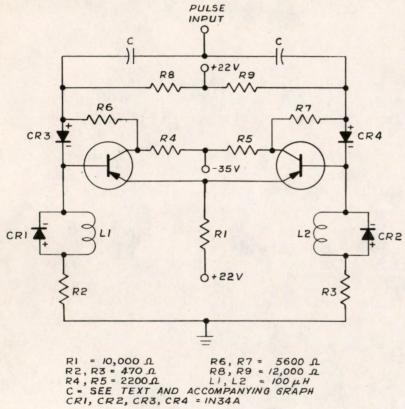

# 2) Word Driver

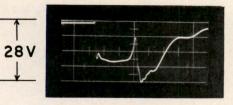

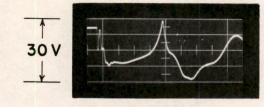

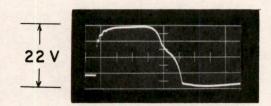

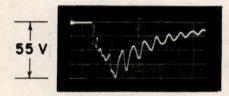

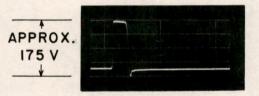

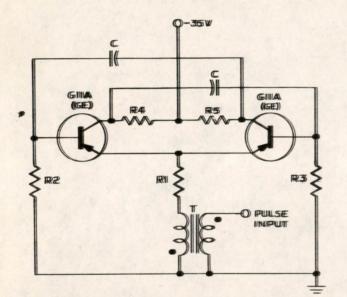

Two word driver circuits are shown in Figs. 4a and 4b. Each consists of a blocking oscillator (1/25965) driving a power amplifier (6293). The blocking oscillator bottoms. The output is stepped up to drive the power amplifier from cut-off to bottoming. The plate voltage of the power amplifier is transformed to the desired output level. Pulse length (4 µsec) is determined by the delay line in the grid of the blocking oscillator. Characteristic waveforms of Fig. 4b are shown in Fig. 5. The blocking oscillator peak grid voltage is +7 volts; the peak cathode current is about 60 ma. The peak current of the power amplifier cathode loaded (47 ohms) is 300 ma and the screen is 100 ma. Unloaded the peak current is 200 ma on the cathode and 100 ma on the screen.

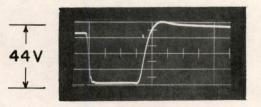

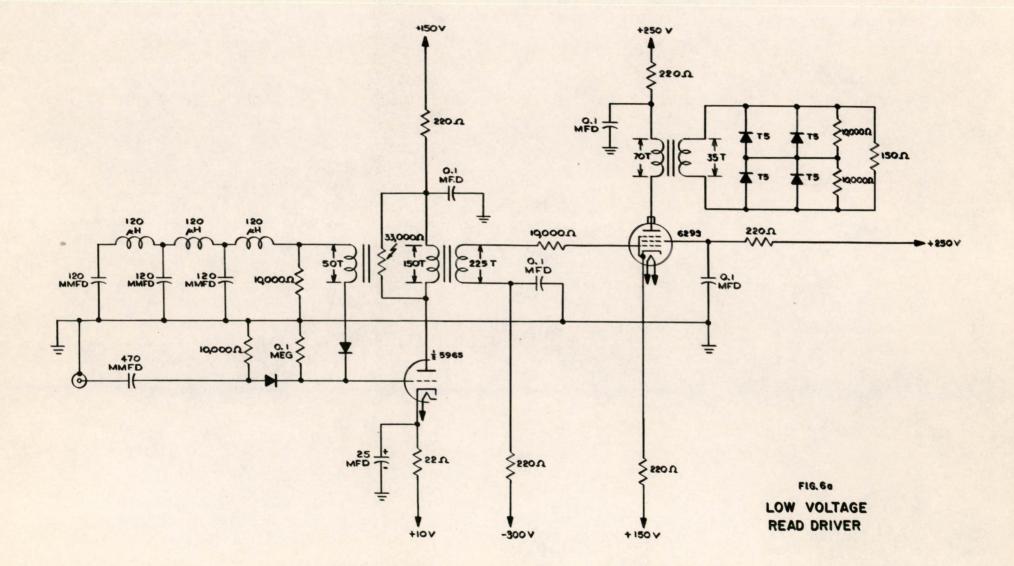

# 3) Read Driver

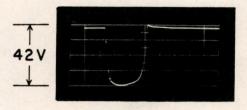

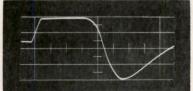

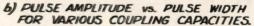

Two read driver circuits are shown in Figs. 6a and 6b. These are essentially the same as the word drivers with the exception of the delay line of the blocking oscillator. Here the pulse length is 1  $\mu$ sec. Characteristic waveforms of Fig. 6b are shown in Fig. 7. The peak cathode current of the blocking oscillator is about 60 ma; the peak grid voltage is +7. The peak cathode current of the power amplifiers is about 1 amp. and peak screen is about 0.5 amp.

The reason for two types is that at first the maximum B+ was 250 volts but later it was learned that 600 volts would be available.

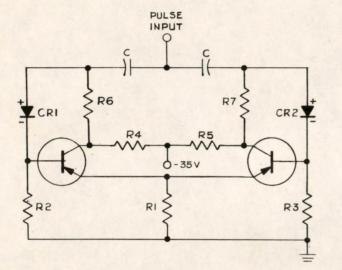

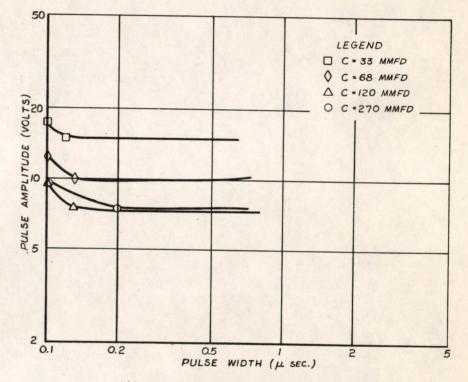

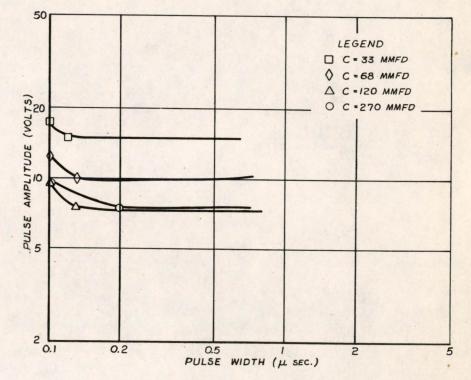

#### Circuit Margins

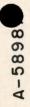

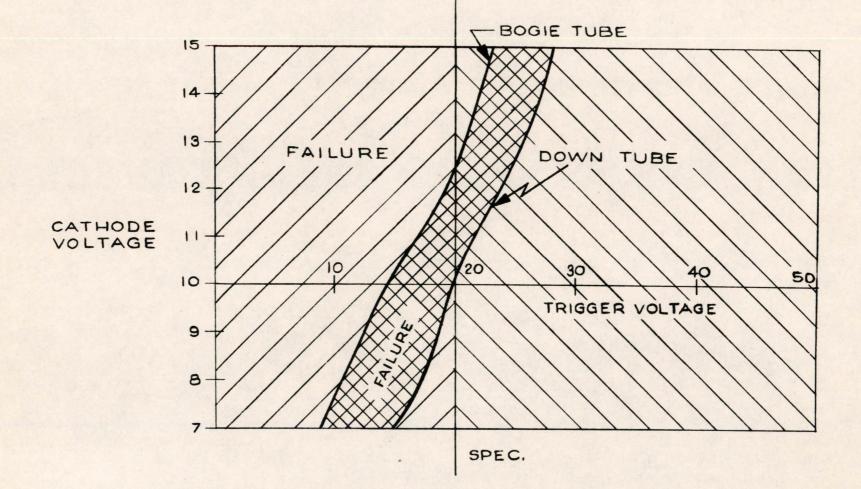

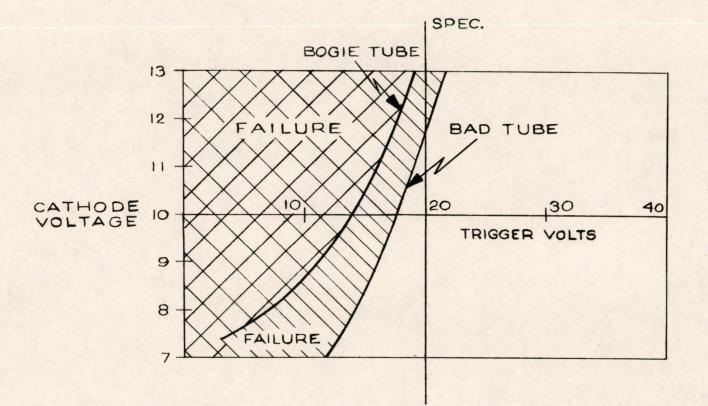

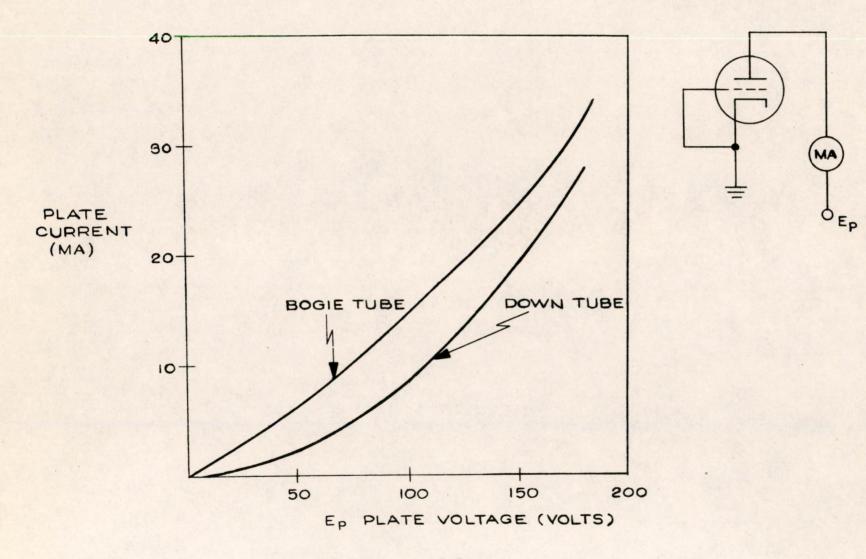

Curves of the input triggering voltage versus bias for the three types of drivers are shown in Figs. 8,9. and 10. These are shown for a bogie 5965 and a down 5965. The characteristic of the bogie and down 5965 are shown in Fig. 11.

It was found that the blocking oscillator worked well when the plate voltage was changed between  $\pm$  50 volts, however, the output is a function of the plate voltage. The blocking oscillator also works well when either a 12AY7 or 12AU7 are substituted for the 5965.

A table of screen margins of the 6293 for the various circuits is shown in the table below.

| Circuit | Min. Screen Voltage<br>for satisfactory Opr. | Max, Screen<br>Voltage tried | Nominal<br>Voltage |

|---------|----------------------------------------------|------------------------------|--------------------|

| Fig. 4a | 90                                           | 440                          | 240                |

| Fig. 4b | 60                                           | 440                          | 150                |

| Fig. 6a | 320                                          | 590                          | 400                |

| Fig. 6b | 210                                          | 440                          | 250                |

|         |                                              | States and States            |                    |

Shunting the diodes of the blocking oscillator grid circuits with lOK resistors had no effect on the output of the circuits. Raising the screen voltages on the power amplifiers lengthened the pulse on the order of 0.2 to 0.5  $\mu$ sec. at the extremes. The delay of the output pulses relative to the input pulses is a function of the triggering pulses. Over the required operating range of triggers the delay is 0.5  $\mu$ sec at most.

#### Suggested Improvements

It appears that the only handle for marginal checking the blocking oscillator is the triggering level. If a pentode is used such as a 7AK7 the screen could serve as a convenient handle.

While the maximum tube rating of the 5965 is not exceeded in the present application, an increase in the grid to plate winding ratio of the blocking oscillator transformer would reduce the maximum cathode current and the maximum positive grid voltage. A five to one ratio was tried and found to be marginal for triggering and bottoming. Perhaps a four to one ratio would be a good compromise.

To improve the screen margins of the read driver a circuit configuration as shown in Fig. 6b with the cathode of the 6293 returned to -150v and the blocking oscillator output winding returned to -300v is worth trying. The output transformer will have to be changed.

1) Blocking Oscillator Transformers

Wound on Ferramic H Core F109-3 die size Grid winding 50T #36 Formex Plate winding 150T #36 Formex Output winding 57T #36 Formex 2) Word Driver and Read Driver Blocking Oscillator Transformer

| Wound on Ferramic H Core | F109-3 | die size |

|--------------------------|--------|----------|

| Grid Winding 50 T        | #36    | Formex   |

| Plate Winding 150 T      | #36    | Formex   |

| Output Winding 225 T     | #36    | Formex   |

3) Word Driver Power Amplifier Transformer (Fig. 4a)

Wound on 2 mil Westinghouse L4 Hypersil Primary 250 T #36 Formex Secondary 25 T #36 Formex

- Word Driver Power Amplifier Transformer (Fig. 4b)

Wound on 2 mil Westinghouse L4 Hypersil

Primary 375 T #36 Formex

Secondary 25 T #36 Formex

- 5) <u>Read Driver Power Amplifier Transformer</u> (Fig. 6a) Wound on 2 mil Westinghouse Ll Hypersil Primary 70 T #36 Formex Secondary 35 T #36 Formex (Could just as well be 50 turns and 25 turns.)

- 6) <u>Read Driver Power Amplifier Transformer</u> (Fig. 6b) Wound on 2 mil Westinghouse Ll Hypersil Primary 100 T #36 Formex Secondary 25 T #36 Formex

Signed nfenge Approved

EA:cs

| Figure Number | Drawing Number |  |  |  |  |

|---------------|----------------|--|--|--|--|

| 1             | A-58979        |  |  |  |  |

| 2             | A-58980        |  |  |  |  |

| 3             | A-58981        |  |  |  |  |

| LA            | B-58982        |  |  |  |  |

| 4B            | B-58983        |  |  |  |  |

| 5             | A-58984        |  |  |  |  |

| 64            | B-58985        |  |  |  |  |

| 6B            | B-58986        |  |  |  |  |

| 7             | A-58987        |  |  |  |  |

| 8             | A-58988        |  |  |  |  |

| 9             | A-58989        |  |  |  |  |

| 10            | A-58990        |  |  |  |  |

| 11            | A-58991        |  |  |  |  |

BIT DRIVERS (16 TOTAL)

A-58980

PLATE VOLTAGE

I & SEC./DIV. DELAY LINE INPUT

I # SEC./DIV. OUTPUT VOLTAGE

I & SEC. / DIV. GRID VOLTAGE

IO μ SEC./DIV. BURST OF EIGHT OUTPUT PULSES

FIG. 3

# BIT DRIVER WAVEFORMS

A-58981

. ,

B-58983

.

I # SEC. / DIV. B.O. DELAY LINE INPUT

IμSEC./DIV. B.O. PLATE VOLTAGE (UPPER) (20 VOLT TRIGGER) (LOWER) (30 VOLT TRIGGER)

I # SEC./DIV. B.O. GRID VOLTAGE

I # SEC./DIV. P.A. GRID VOLTAGE

I μ SEC./DIV. OUTPUT PULSE (47 Ω LOAD)

I  $\mu$  SEC./DIV. OUTPUT PULSE (UNLOADED)

FIG. 5

WORD DRIVER WAVEFORMS

B-58985

98685-8

.

.

Iμ SEC. / DIV. B.O. PLATE VOLTAGE

20 V

1 μ SEC. / DIV. B. O. GRID VOLTAGE

I μ SEC. / DIV. B.O. DELAY LINE INPUT

APPROX. 350 V

Iμ SEC./DIV. P.A. GRID VOLTAGE

I # SEC. / DIV. OUTPUT PULSE

READ DRIVER WAVEFORMS

BLOCK OSCILLATOR, WORD DRIVER

FIG. 10 BLOCK OSCILLATOR, READ DRIVER

Memorandum M-2820 Supp. #1

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

SUBJECT: BLOCKING OSCILLATOR CORE DRIVERS FOR USE IN DISPLAY GENERATOR BUFFER STORAGE.

To: N.H. Taylor

From: E. Anfenger

Date: June 7, 1954

Abstract: This paper lists the corrections on M-2820

# Corrections

1. Page 2 under "word driver" item d, should read 20 to 40 volts instead of 10 to 40 volts.

2. Top of Fig. 1 should read 32 bit drivers instead of 16.

3. Fig. 4a return to  $-300^{V}$  should be from lower winding of 225T and condenser should go to ground as in Fig. 4b.

4. Fig. 6a cathode return 6293 should read -150V instead of +150V.

SIGNED E. Anfenger

APPROVED RLB

EA: jb

Distribution List for N. Taylor (When M-Notes are addressed to him)

# Internal Distribution

D. Arden The author R. Best D. Brown C. Corderman R. Callahan W. Thomas A. Heineck J. Jacobs W. Linvill R. Mayer P. Bagley R. Nelson K. Olsen W. Papian N. Taylor R. von Buelow H. Wainwright C. W. Watt J. W. Forrester

R. R. Everett S. H. Dodd A. F. Falcione Division 6-Library (15 to 20 Copies) M's by B.Paine--1 copy to V. Savio A's--1 copy to R. Nelson

#### External Distribution

A. P. Kromer (10 Copies of M-Notes for I.B.M.)

Bldg. 32 - Library

Air Force Gambridge Research Center Attention: Document. Room--CRQ-SL-1. 230 Albany Street

.

Page 1 of 1

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

# SUBJECT: ONE ONE OR THE OTHER

To: Group 62 and 63 Staff and Secretaries

From: R. P. Mayer and W. N. Papian

Date: May 28, 1954

# Discussion

When one writes a memo using binary numbers, such as one would use to describe one states or zero states in a binary device, he should not use one without at least one special symbol (e.g. ONE, or "one", or "l") otherwise the one is hard to interpret because one does not know whether one means one or one, that is, one one or the other one.

#### Conclusion:

There exist two small words we call "one," 'Which can cause great confusion, or fun. Use binary "ONE," To distinguish from "one" So we'll know you mean "ONE" and not "one."

Signed R.P. May R.P. Mayer Approved Papian

#### RPM:WNP:cs

N.H. Daggett John Bennett W. Wittenberg (IBM)

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

- SUBJECT: <u>TEST RESULTS ON THE DCL MEMORY PLANE</u>

- To: F. E. Vinal

- From: E. A. Guditz

Date: 28 May 1954

Abstract: The DCL plane (C25) is compared with a standard MTC plane which has General Ceramics cores. Except for requiring slightly higher driving currents for maximum output, the DCL plane compares favorably with the MTC planes and could, in fact, operate as a substitute MTC plane without seriously impairing the system's margins.

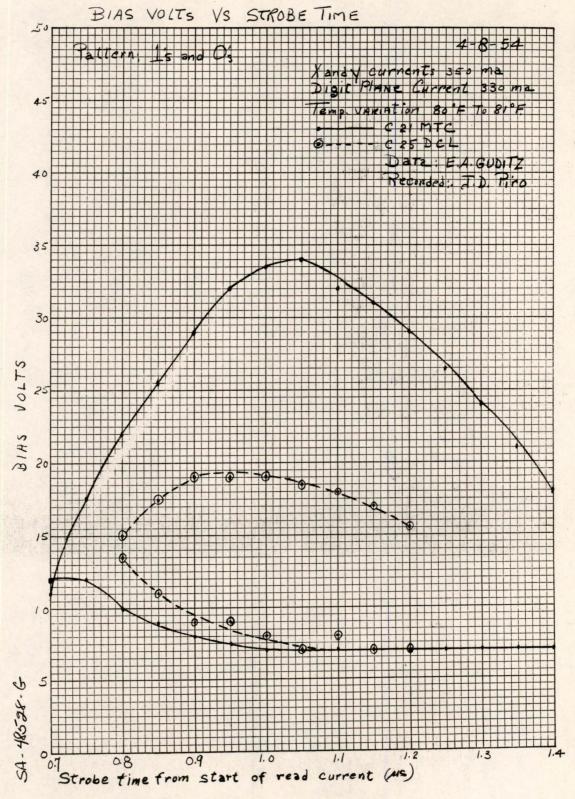

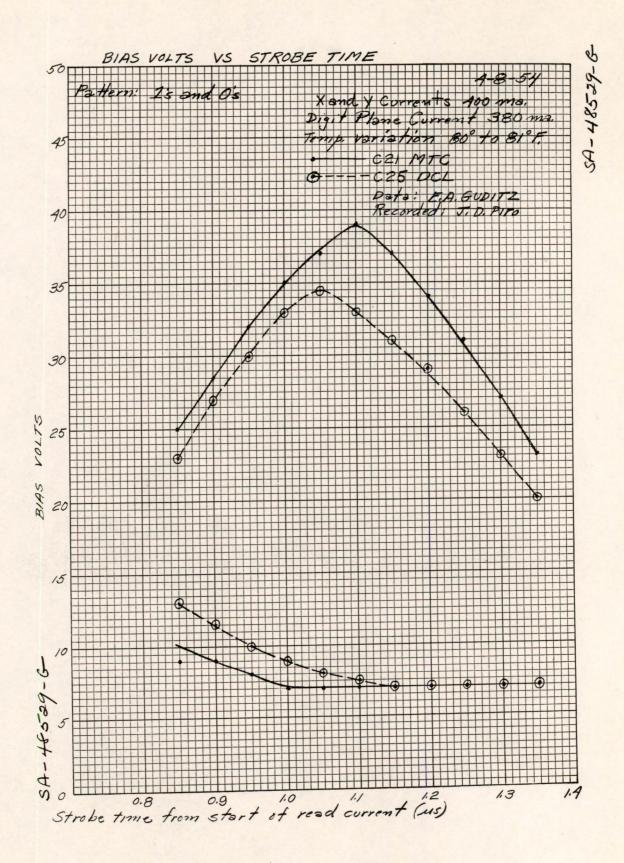

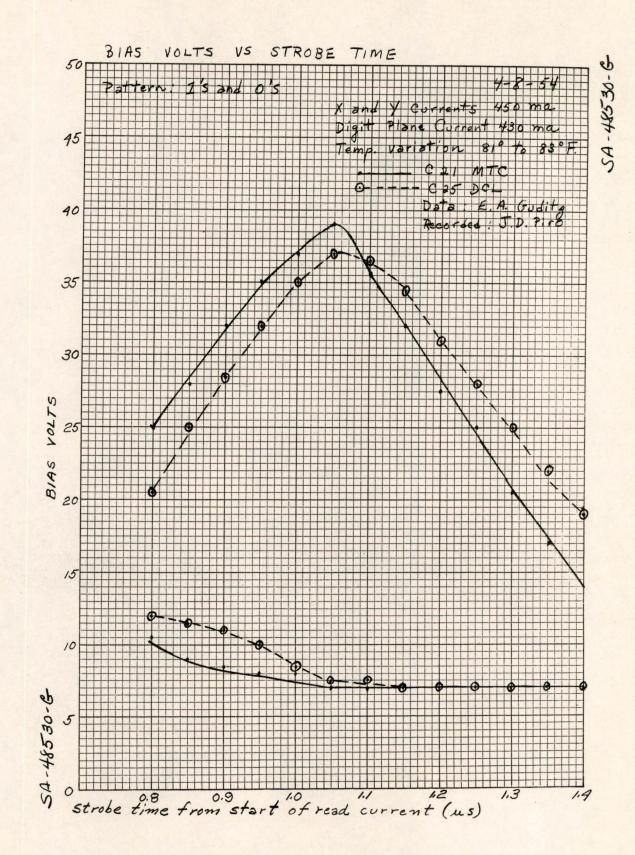

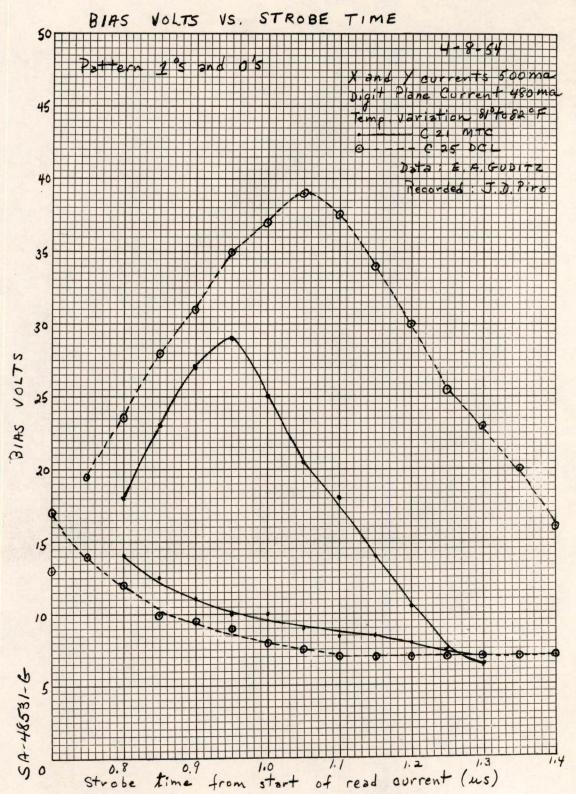

Plane C25, herin referred to as the DCL plane, contains cores made at this laboratory by Group 63. These cores are designated DCL-1-180. The object of this test was to find the optimum driving current for the plane and the worst ONE-ZERO ratio. Data was taken showing the relationship of Sensing Amplifier Gate Tube bias to Strobe Time for four values of driving current and four different patterns.

Patterns of all ONES and all ZEROS were used to find optimum driving current. Data was taken at 1.0a., 0.9a., 0.8a., and 0.7a. The attached graphs SA-48528-G through SA-48531-G show the comparison of the DCL plane (C25-dotted line) with the MTC plane (C21-solid line) under these conditions. Note that the MTC plane has its maximum ONE-ZERO ratio in the 0.8a. to 0.9a. region while the DCL plane has an increasing ONE-ZERO ratio right up to the maximum available driving current of 1.0a. Also, the ONE-ZERO ratio of the DCL plane at this maximum available current is approximately equal to the best ONE-ZERO ratio available from the MTC plane. It should be noted that at the best operating current for the MTC plane the DCL plane has a very good ONE-ZERO ratio and is quite capable of operating in conjunction with MTC planes.

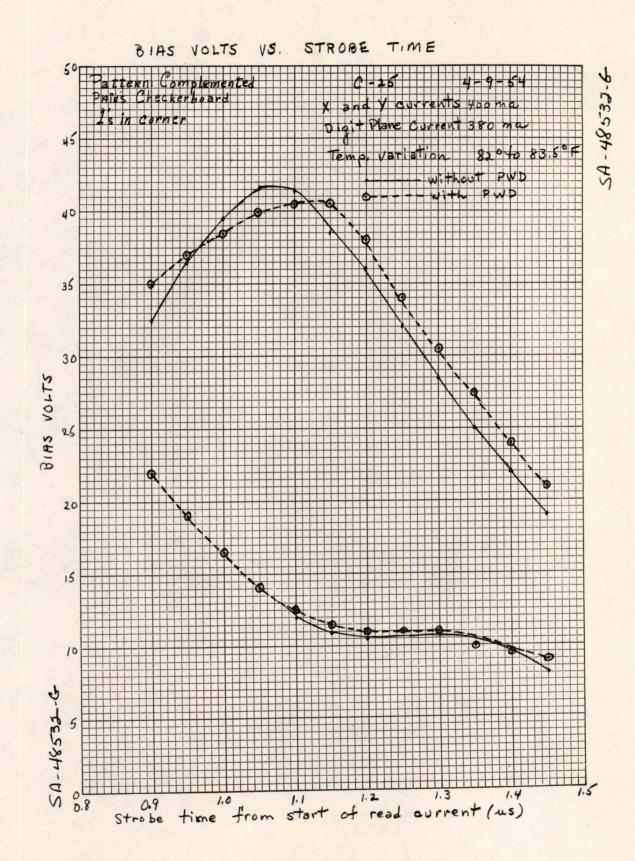

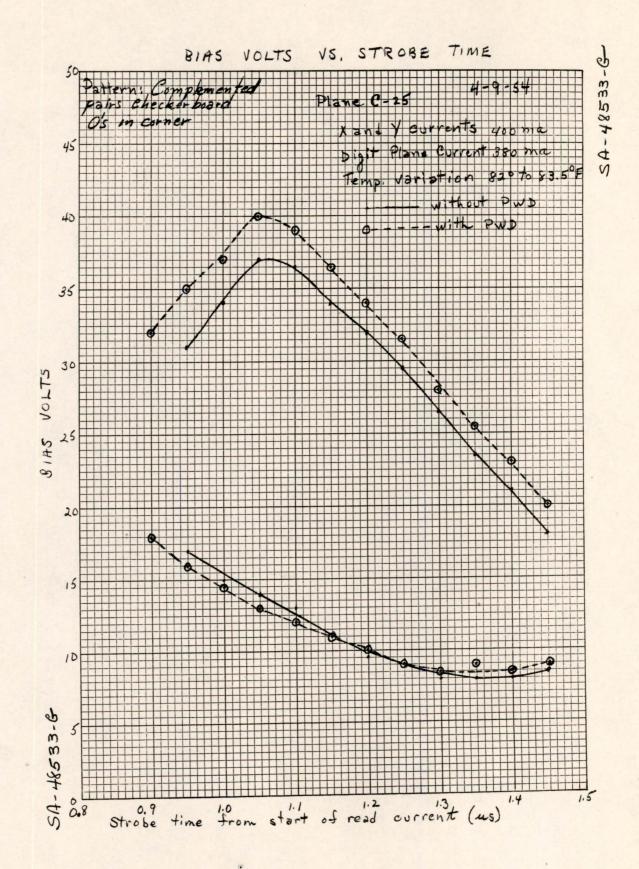

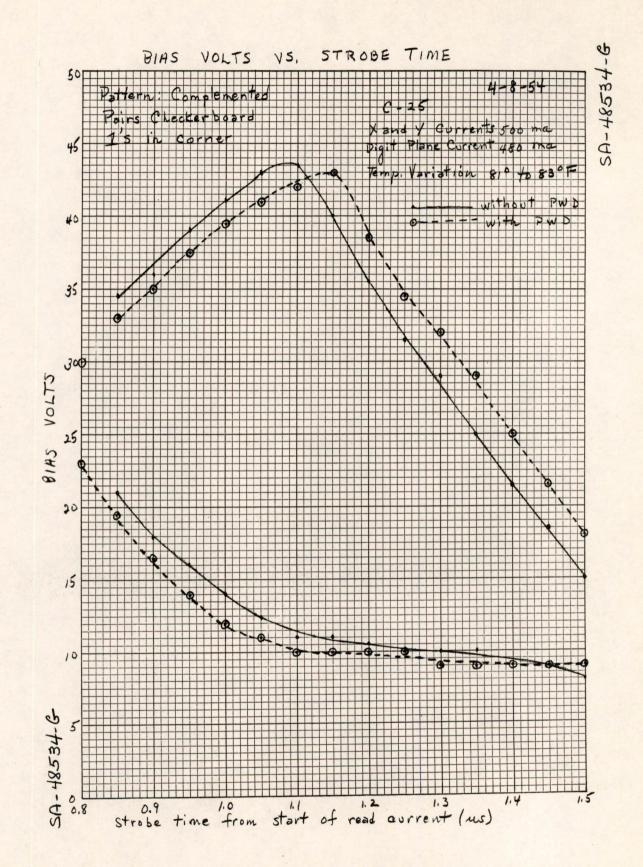

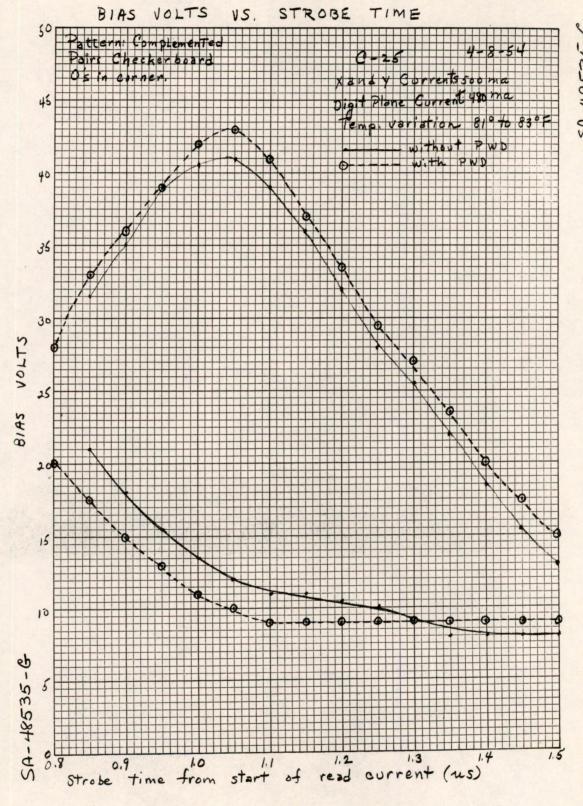

Graphs SA-48532-G through SA-48535-G show the operating margins for the two complementary patterns of complemented pairs-checkerboard for driving current values of 0.8a. and 1.0a. Again it can be seen that the margins are still increasing at the maximum available driving current of 1.0a. In these graphs a comparison is made not with the MTC plane but with and without the Post-Write Disturb current. It is interesting to note that the Post-Write Disturb current is most beneficial for the pattern with zeros in the corners (Graphs SA-48534-G and SA-48535-G). The reason for this is not understood. Observation of Sensing Winding output voltage showed that the spread in outputs is very small and is as good or better than that observed from the MTC planes.

It is felt that a memory made of planes using these cores and operated at its optimum currents would have operating margins at least equal to those of the present  $6\mu \ge 6\mu$  memory.

SIGNED E. Gudi APPROVE

EAG: jb

Group 63 Staff (Group 62) Magnetic Memory Section Staff (Group 62) W. Wittenberg (IEM)

Graphs

SA-48528-G SA-48529-G SA-48530-G SA-48531-G SA-48532-G SA-48533-G SA-48533-G SA-48534-G SA-48535-G

54-45534-6

SA-48531-6-

-

•

-

SA-48535-6-

Page 1 of

Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

#### SUBJECT: XD-I DIGIT-PLANE DRIVER

- To: N. Taylor

- From: D. Shansky

Date: 28 May 1954

Abstract: A self-balancing bridge is utilized in conjunction with an "and" and an "or" gate input to satisfy the wave form and gating specifications on the driver for a magnetic core memory digit plane winding.

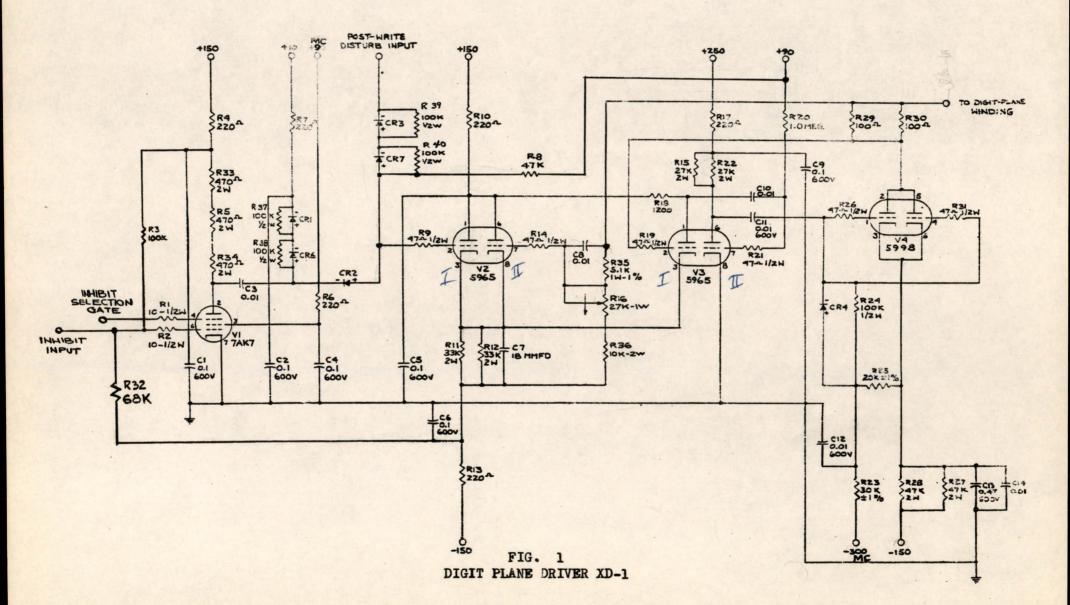

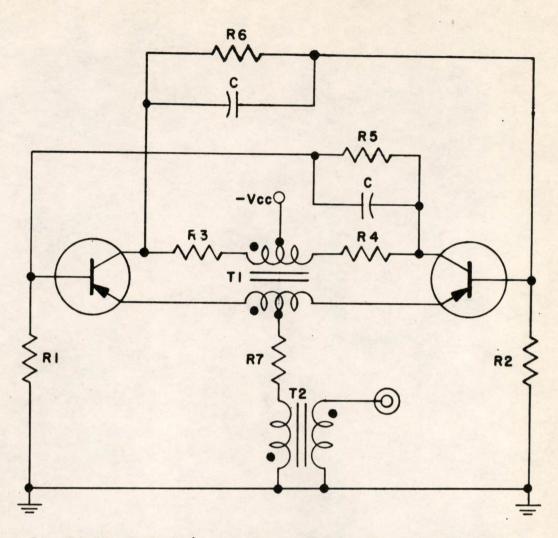

The digit plane driver is a circuit which combines the logical function of both an "and" and an "or" gate with a regulated pulse current source. For purposes of an explanation of circuit operation it is most convenient to simplify the discussion by describing the operation of the 2 logical blocks independently of one another. Regulated Pulse Current Source.

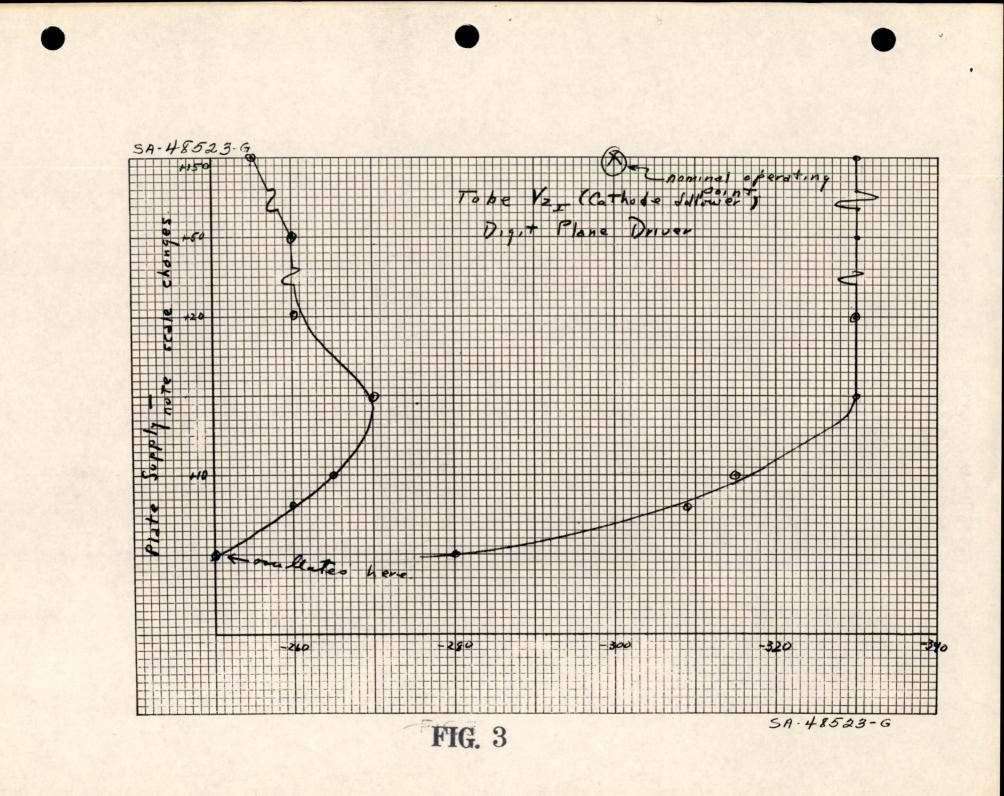

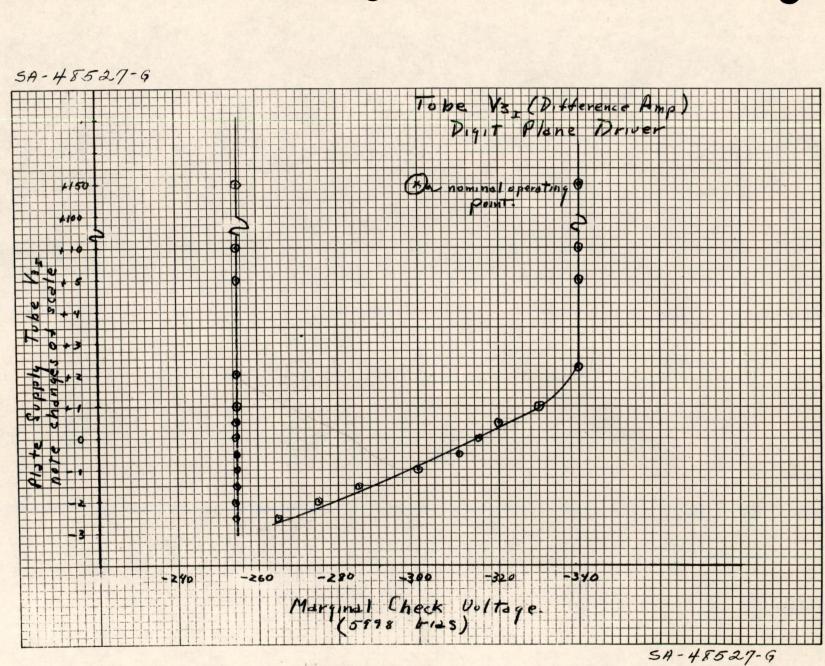

This portion of the circuit consists of 5 cathodes in a feedback loop. Two of these cathodes are in a difference amplifier ( $V_{2II}$ ,  $V_{3T}$ ), which serves to compare a signal voltage produced by current flow through a sampling resistor, to a constant voltage level established by a potentiometer connected across a power supply. A third cathode  $(V_{3_{11}})$  serves to amplify and invert the output voltage of the difference amplifier and drive the grids of the final tube  $(V_{\downarrow_{I},II})$ , which is a 5998. The cathodes of the difference amplifier are normally held up to 10 volts by a cathode follower  $(V_{2_{\rm I}})$ , so that these tubes are normally cut off. The inverter-amplifier tube  $(V_{3_{\rm II}})$  is normally conducting, while the driver tube  $(V_{4I,II})$  is normally cut off by the presence of a large negative bias. During the pulse, the cathodes of the difference amplifier  $(V_{2II}, V_{3I})$  are allowed to fall by applying a negative gate to the grid of the cathode follower  $(V_{2I})$  whose cathode is connected to the cathodes of the difference amplifier. Therefore, the plate of the difference amplifier will fall and the change in voltage will appear at the grid of the normally conducting inverter. The plate of the inverteramplifier  $(V_{3TT})$  will rise at a rate determined by the plate load resistor and stray, input and output capacities. This change in voltage will be coupled over to the grids of the normally off 5998 turning them on. The voltage developed across the sampling resistor  $(R_{29,30})$  by current flowing through the 5998 and the load is fed back to the difference amplifier where it is compared to a reference voltage applied to the other grid of the difference amplifier. During the pulse then, this regulated pulse current source becomes a self-balancing bridge. The back voltage produced by the load is fed back to the difference amplifier (via  $c_8$ ) as a common mode signal to insure an adequate current source regardless of load variation.

This particular geometry has resulted in a circuit which has extremely broad tolerances with respect to tubes, component values, and supply voltages, as the accompanying curves indicate, since the circuit inherently adjusts itself to compensate for these variations.

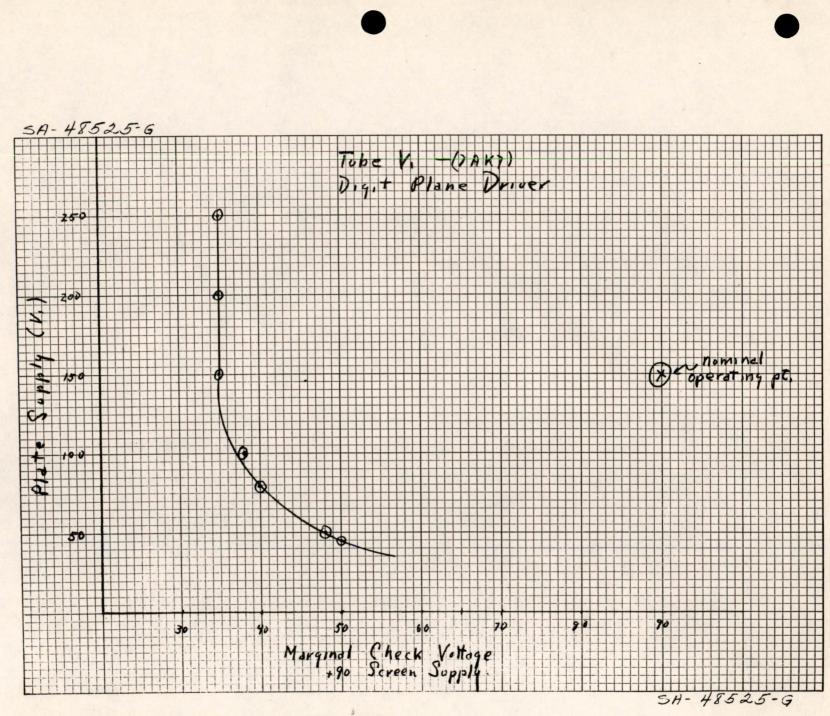

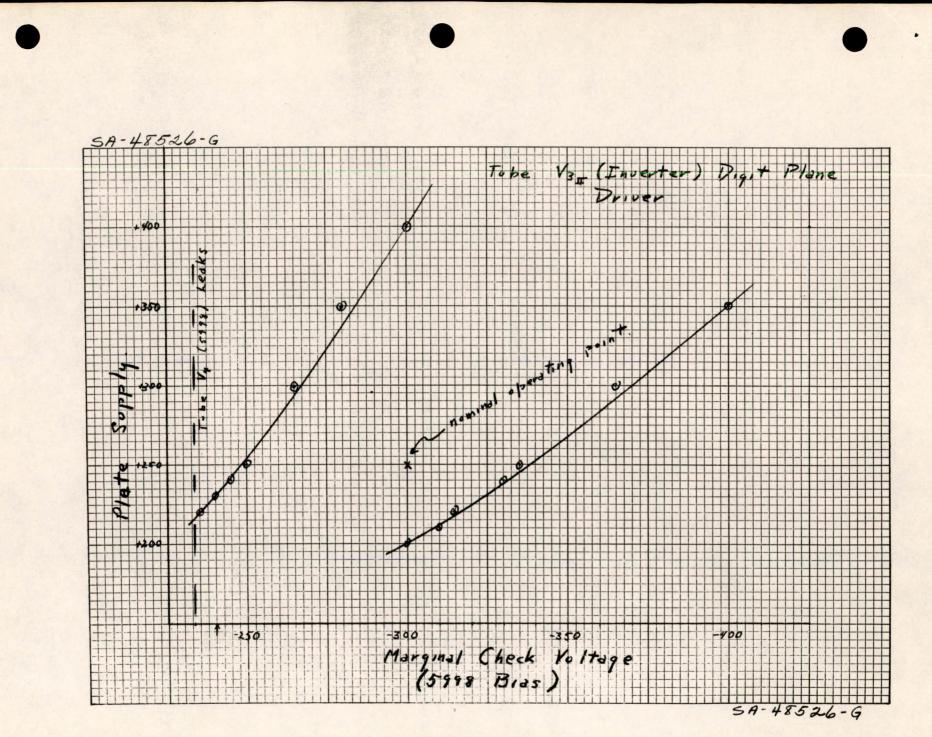

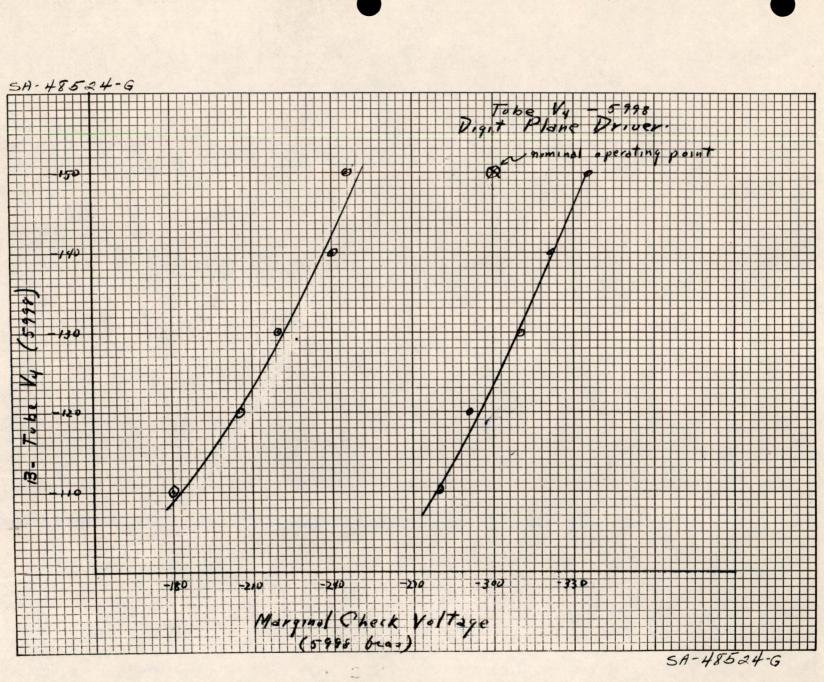

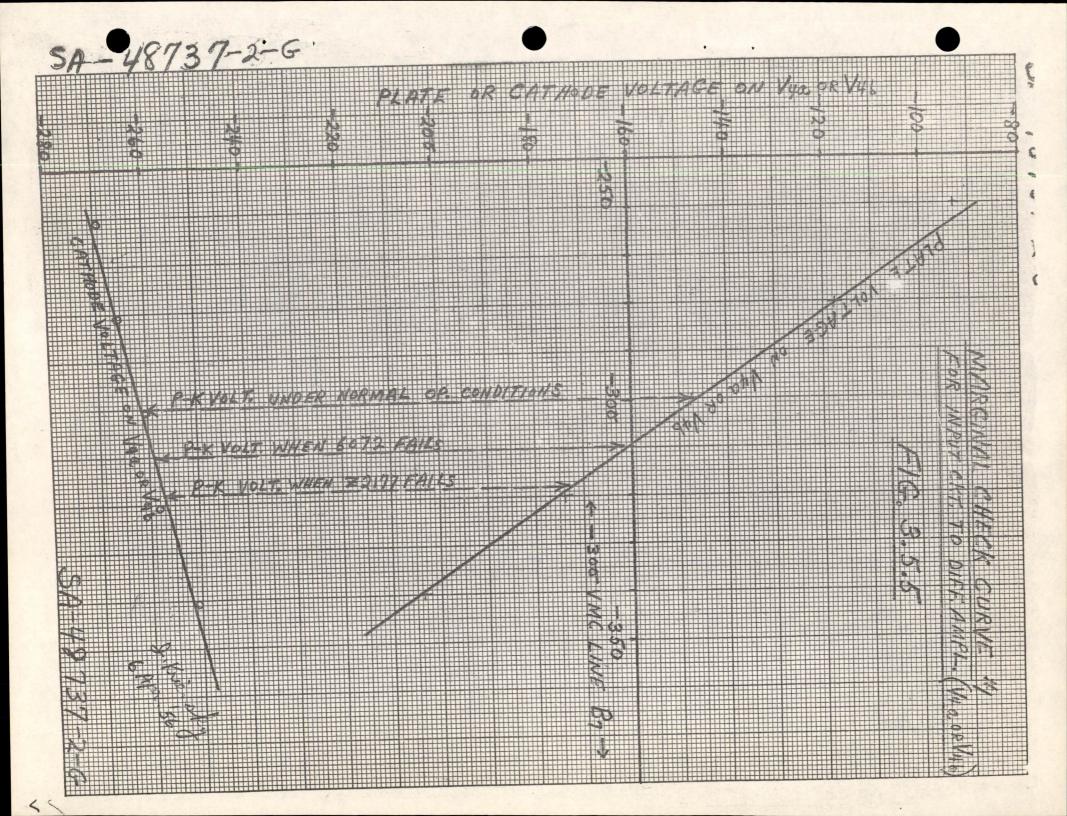

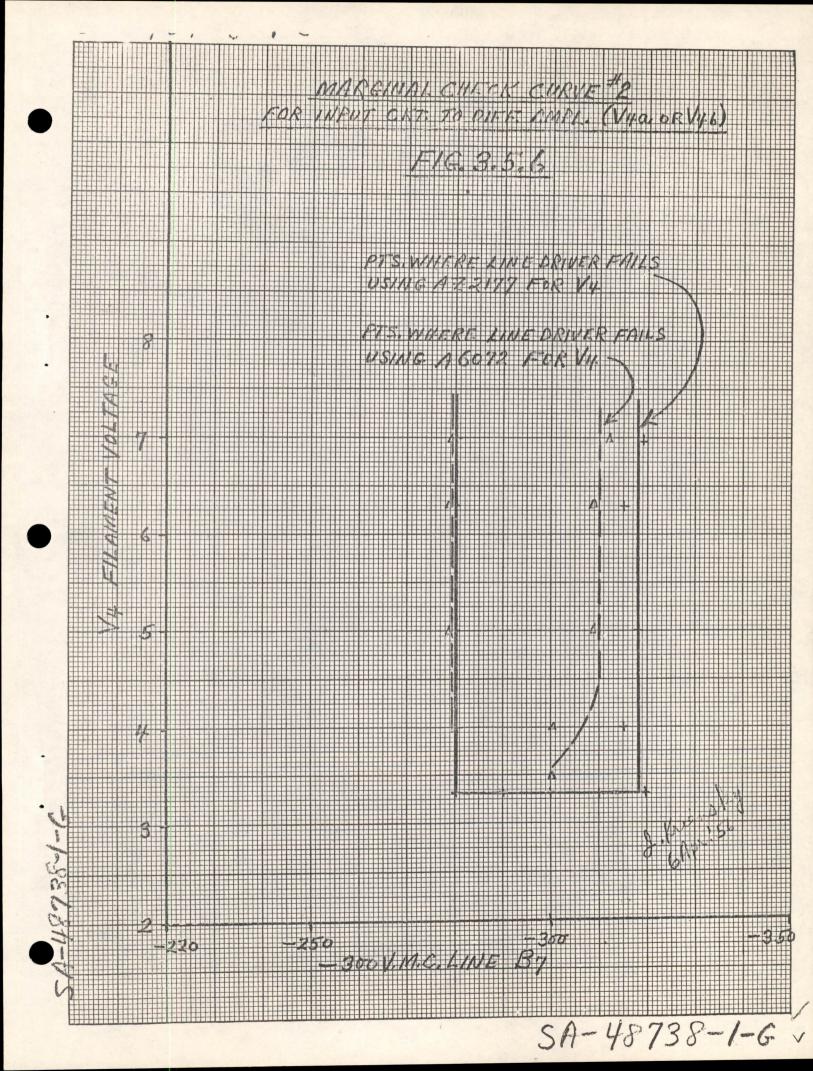

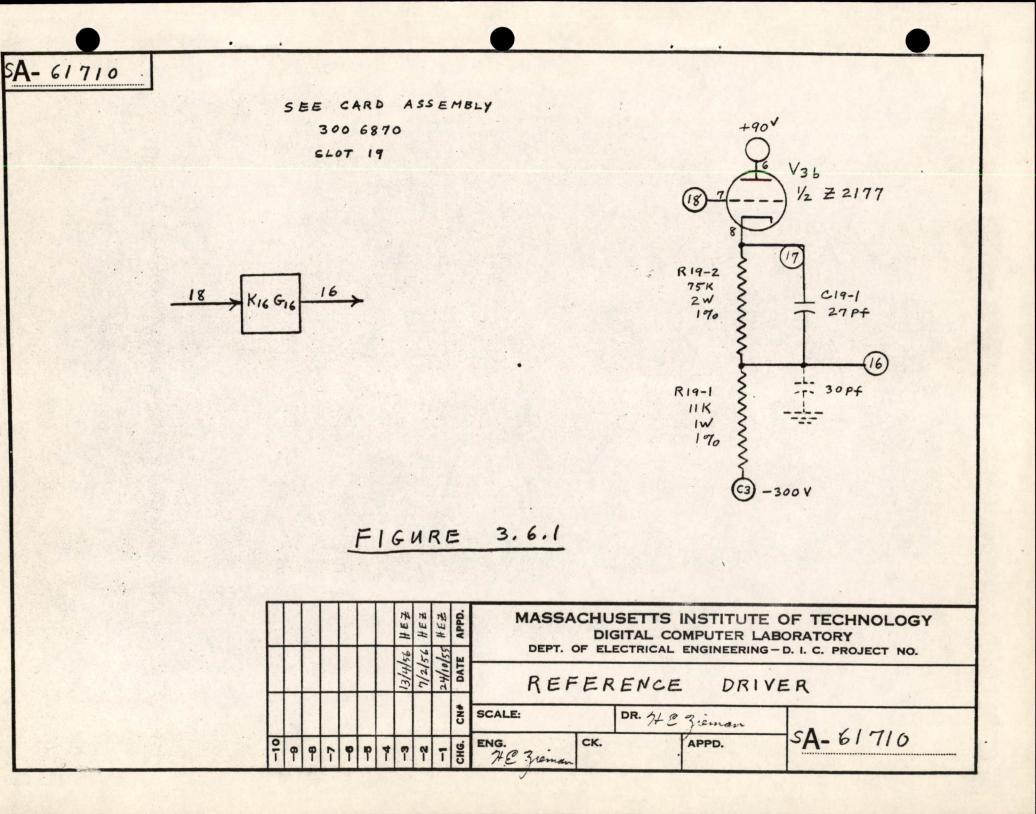

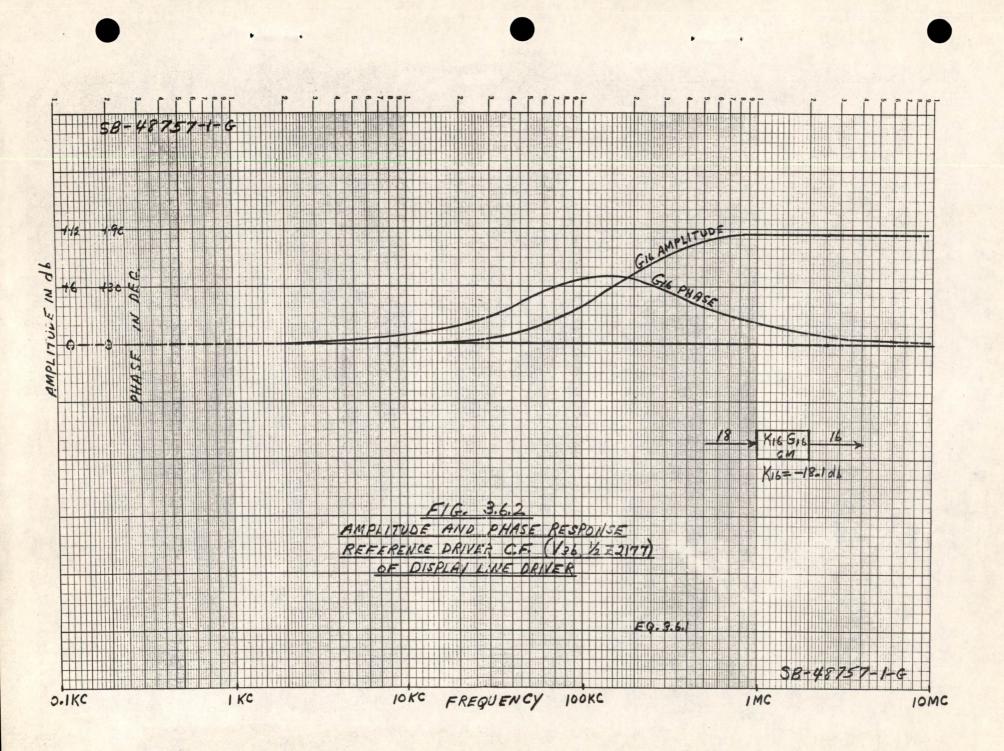

Figure #4, 5 and 6 portray the operating margins of the cathodes in the feed-back loop. The bias on the 5998 output tube was chosen as the marginal checking voltage in each case since the internal loop gain may most conveniently be changed by varying this voltage. A curve on V2II (the cathode follower portion of the difference amplifier) is not included because it was found that the plate supply of this tube could be made negative with respect to the cathode without causing failure. A diode is all that is apparently necessary here. (By way of explanation of this apparently superfluous cathede, I might point out that the specification on output current change was originally + 2%. This cathode was included to minimize the change in output current due to variations in contact potential of the difference amplifier. However, in view of the fact that unit failure had to be related to system failure, and in view of the experience gained in M.T.C., failure was defined as a 15% change in current.) In the case of tube V3 failure was defined as change in output pulse rise time of 1 0.2 µsec. This change in timing is compatible with system requirements. Failure was defined in similar manner for all the other cathodes in the circuit with the exception of  $V_{1,p}$  where the failure was evidenced by a 15% change in output current.

#### "And", "Or" Gate Circuitry.

Since it was necessary that the grid of  $V_2$  be allowed to fall more than forty volts because of the common mode signal on the difference amplifier ( $V_2$ ,  $V_3$ ) produced by the back voltage developed in the load, it was necessary to provide some amplification of the input signal (Flip-Flop output). A 7AK7 was used to provide the necessary amplification and perform the "and" gating function. The output of the "and" gate is fed to a diode negative "or" gate. The other input to the negative "or" gate is connected to the "Post-Write-Disturb" gate generator, which provides a negative going gate of the proper amplitude ( $\pm 10$  to  $\pm 40$ ).

The margins of operation of the 2 cathodes in this portion of the circuit are shown in figs 2 and 3. In the case of Tube V<sub>2</sub> failure was defined as a change in timing as previously mentioned, while failure of the 7AK7 manifested itself as a change in output current.

#### Conclusion

As a result of the experimental work which was done in garnering the information upon which the preceding report was based, it became apparent that a redesign of the unit could eliminate some cathodes and ease the input driving requirements. The Digit Plane Driver has therefore been redesigned so as to eliminate two cathodes and operate from standard voltage levels. This work was not completed in time to meet the XD-1 production schedules. A report on the improved version of this circuit is being prepared and will be forthcoming shortly.

SIGNED Haird Shansky D. Shansky

APPROVEL

DS: jb

Attached

Fig 1 B-59149

Fig 2 - SA48525-G

Fig 3 - SA48523-G

Fig 4 - SA48527-G

Fig 5 - SA48526-G

Fig 6 - SA48524-G

B-59149

1

.

.

Page 1 of 8

Best

Memorandum M-2919

Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Cambridge 39, Massachusetts

- SUBJECT: SENSING WINDING GEOMETRY AND INFORMATION PATTERNS

- To: N. H. Taylor

- From: J. I. Raffel

Date: July 22, 1954

Abstract: Two properties of the sensing winding used in the Whirlwind I and MTC core memories are common to a large class of winding configurations. These are: 1) maximum partial cancellation of core "noise" 2) no inductive coupling between drive and sense wires. A new winding is suggested to replace the present zig=zag geometry. This should prove easier to implement and preliminary tests on a plane containing both old and new sense windings indicate that the two are electrically equivalent. Since core "noise" is a function of information and sense winding geometry, a different checkerboard pattern exists for this new winding.

> In general, checkerboard patterns used for production testing should not be called "worst" patterns since no attempt is made to guarantee the disturbed states of the cores, and these have a considerable effect on sense winding outputs.

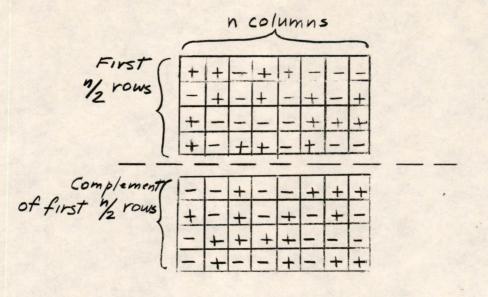

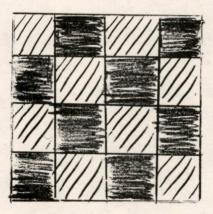

For a core memory using a two-dimensional read and consisting of n rows and n columns, all that is required in order to have a "cancelling" winding with respect to "noise" signals from half-selected cores is that the winding pass through half the cores of each row and of each column in one direction and through the remaining halves in the other direction. Consider a square array shown in Figure 1. Each of the first n/2 rows can be made of any of the nCn/2 combinations of n/2 pluses and n/2 minuses. (Plus and minus refer to core polarity with respect to sense winding.) If the next n/2 rows containe the complement configuration to that of the top half, the conditions for a cancelling winding as defined above are fulfilled. Figure 1 shows a typical example of a winding belonging to this class. The MTC-type sense winding has a distribution like that of Figure 2. It is seen to satisfy the necessary conditions also. Another possible geometry which suggests itself is shown in Figure 3. This appears to be the physically simplest configuration which satisfies the necessary conditions for partial concellation of core "noise".

Page 2 of 8

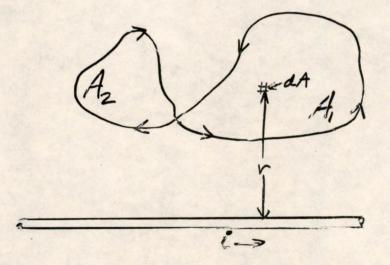

M-2919

It is now necessary to consider the problem of inductive pickup. For this the cores can be neglected entirely and only the large closed loops of wire comprising the sense winding need be considered. The requirement for a non-inductive winding, if we neglect end effects and consider the drive wires as infinitely long, is that the for the de zero where r is the perpendicular distance between a drive line and a differential area dA as shown in Figure 4. The integral over A in Figure 4 would be made up of the two components A1 and A2 of opposing sign following the usual polarity convention for evaluating surface integrals.\* The simplest way of guaranteeing this is that the net enclosed are (algebraic sum) at a given distance from any row or column wire is zero. The present sense winding uses two overlapping loops which have equal and opposite components of area with respect to any horizontal or vertical driving line. This has a map as shown in Figure 5 where solid areas and crosshatched areas refer to loop areas of opposing polarity. If we consider the map of Figure 6 any "checkerboard" pattern of the type shown having an even number of squares on a side will be non-inductive. Here, as with core-noise cancellation, all that is required is that n/2 rows be "half and half" and the other n/2 rows be the complement of the upper half. It is to be emphasized, however, that here we refer to areas comprised of closed loops of wire and not to cores. The winding of Figure 3 is therefore seen to be both cancelling and non-inductive. This winding may be thought of most simply as being composed of four digit-plane type windings, (a single section links all cores in the same direction) connected in series so that adjacent quadrants of the plane are of opposite polarity. In building larger arrays and/or utilizing printed wiring techniques, this type of winding may prove to be much simpler to install than the old zig-zag.

The problem of delta noise has been considered in E-488, M-2351 and M-2568. These analyses show that a so-called "worst" pattern (that is, a condition under which ONEs are smallest and ZEROs largest) results from having one type of information on the positive half of the sense winding and another on the negative half of the sense winding. Using Freeman's terminology \*\* half the cores should be in the "w" state and the other half in the "r\_" state on the selected row and column. That is, half the cores should be in the write-disturbed ONE state and half in the read-disturbed ZERO state. In the past no attempt has been made to guarantee that cores had been properly read-disturbed or write-disturbed, the emphasis being placed merely on inserting the proper pattern of ONE's and ZEROs in the array. For production testing of planes this type of test is probably sufficient for obtaining comparisons, but in no case should the results from such tests be used as any absolute indicator of margins and the term "worst" pattern should probably not be used where the disturb condition is not taken into account.

\*Osgood Advanced Calculus -

\*\*Pulse Response of Ferrite Memory Cores - M-2568

M-2919

A test plane containing the old zig-zag type of sense winding was wound with an additional winding of the type shown in Figure 3. The experimental results obtained with the new winding of Figure 3 indicated no inductive pick-up, as expected, but in rastering through the array extremely large ZEROs were encountered at certain places. These ZEROs were reduced to normal size by the addition of the post-write disturb pulse and were therefore seen to be attributable to the core output and not pickup.

It next became necessary to determine why this effect was only encountered when testing the new sense winding with its corresponding checkerboard pattern and not when testing the old with its pattern. In each case the memory is filled with a pattern which places ZEROs on one half (the half shown with minuses for instance) the sense winding and ONEs on the other (pluses). The only difference which arises for the two windings is that the halves are composed of different groupings of cores (see Figures 2 and 3). In each case the array is addressed cyclically, a row at a time, starting from the lower left-hand corner. The difference in outputs between the two windings is clearly the result of the difference in information sequencing which results in differences in the disturbed state of the cores in the array. In other words, in both cases we have half the cores in the ONE state and half in the ZERO but no consideration has been given to whether the ZEROs are read-disturbed and the ONEs write-disturbed. A glance at the old checkerboard pattern, Figure 2, indicates that since no more than two ONEs are written consecutively almost all of the cores in the array are, in fact, going to be in the readdisturbed state, having been placed there by the digit-plane driver used for writing ZEROs and therefore there is not even a remote possibility of having the ONEs write-disturbed by chance somewhere in the array.

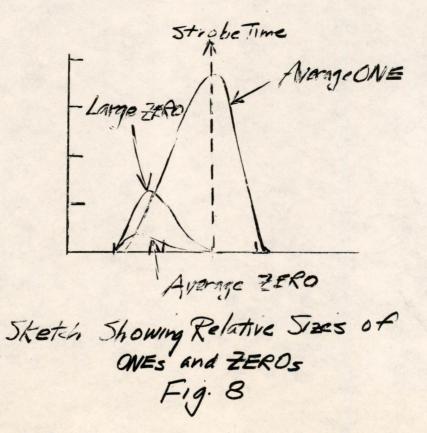

An examination of the sequence for the new checkerboard pattern, Figure 3, indicates two inherent characteristics which tend to guarantee the proper disturbed conditions for many more cores: 1)Long strings of consecutive ONEs and of consecutive ZEROs are placed in the array at a time. 2) Successive rows (except for the middle pair) have the same information. The results can be best demonstrated by considering two adjacent rows as shown in Figure 7. Writing the last ZERO of the bottom row read-disturbs all the cores in the array (digit-plane-driver pulse). Writing the series of ONEs to finish out the line write-disturbs columns directly above each ONE and hence leaves the ONEs in the second row writedisturbed. (Incidentally, the ZEROs of the bottom row are also writedisturbed.) The first ZERO of the second row is now about to be read out and the ZEROs in its row have been read-disturbed and the ONEs writedisturbed. It is therefore quite reasonable to expect an unusually large noise output. It should be pointed out that even now the disturb condition of all the cores has not been guaranteed. Only the row containing the selected core has been disturbed properly, no attention has been paid to the column, and indeed the cores here are all read-disturbed (except for the one core in the previous row) because the last excitation these cores saw was the digit-plane-driver pulse which occurred when writing ZEROs in the previous row. The ZERO output is therefore still far from the worst case. Figure 8 shows a sketch of the output from the array for this pattern.

Page 4 of 8

M-2919

Note that the peak value of the maximum ZERO has become alarmingly large, but at strobe-time discrimination is still excellent.

Another effect which has not been sufficiently evaluated is the size of the voltage induced in the sense winding by the digit-planedriver pulse. This is greatest when all the cores in the plane are in the proper w and r states, and under a true worst condition might very well be large enough to cause the sense-amplifier to block.

The new sense winding seems to work well and the experimental results obtains with it have served to emphasize the need for a thorough experimental investigation of theoretically predicted "noisy" pattersn. The term worst pattern which was previously used rather loosely to describe checkerboard patterns regardless of the disturbed condition of the cores should be avoided in the future. These patterns are worthwhile as standard tests but by no means represent the most adverse conditions which could be encountered in computer operation. It is hoped that this point has been made sufficiently clear to avoid the necessity of periodic re-discoveries that our test patterns do not give the worst signal-tonoise ratios.

Signed: Jack Raffel Jack I. Raffel

Approveds W. M. Papian 1d

JIRsjd

CC: Group 62 - Engineers Group 63 - Engineers W. Wittenberg N. Daggett A. Roberts

Page 5 of 8

M-2919

...

Typical Winding With Core-Noise Cancellation Fig. 1

| - | + | + | - | - | + | + | - |

|---|---|---|---|---|---|---|---|

| + | 1 | - | + | + | - | - | + |

| + | 1 | 1 | + | + | - | - | + |

| 1 | + | + | 1 | 1 | + | + | - |

| - | + | + | 1 | 1 | + | + | - |

| + | 1 | - | + | + | - | - | + |

| + | 1 | - | + | + | - | - | + |

| - | + | + | - | - | + | + | - |

MTC- type Core-Noise Cancellation

Fig. 2

Page 6 of 8

M-2919

| + | + | + | + | - | - | - | - |

|---|---|---|---|---|---|---|---|

| + | + | + | + | 1 | - | 1 | - |

| + | + | + | + | - | - | i | - |

| + | + |   |   |   |   |   |   |

| - | - | - | - | + | + | + | + |

| - | - | - |   | + | + | + | + |

| - | - | - | - | + | + | + | + |

| - |   | - |   |   | + |   | + |

Proposed Cancelling Winding

Fig. 3

Voltage Induction by Current-Carrying Conductor

Fig. 4

...

M-2919

Page 7 of 8

Loop-Area Map For MTC-type Winding Fig. 5

Loop-Area Map For Checkerboard Type

Fig. 6

Page 8 of 8

M-2919

Large Zero due to core noise ++-

Sequence For New Winding

Fig. 7

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

## SUBJECT: A CARRY SYSTEM EMPLOYING A MAGNETIC CORE AND TRANSISTORS

To: Transistor Distribution 2

From: S. Oken

Date: August 3, 1954

Abstract: This is a preliminary report on a carry system employing transistors, vacuum tubes and magnetic cores which has been developed as a possible substitute for the flip-flop and gate circuits presently used for the carry system in the arithmetic element. At present this system can be run at a maximum pulse repetition rate of about 350 kc. An output voltage in excess of 15 v can be obtained across a load resistance of 1 k A.

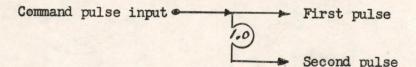

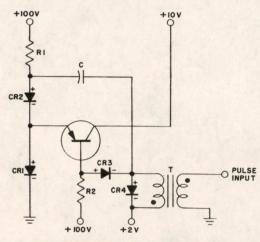

## 1.0 Introduction

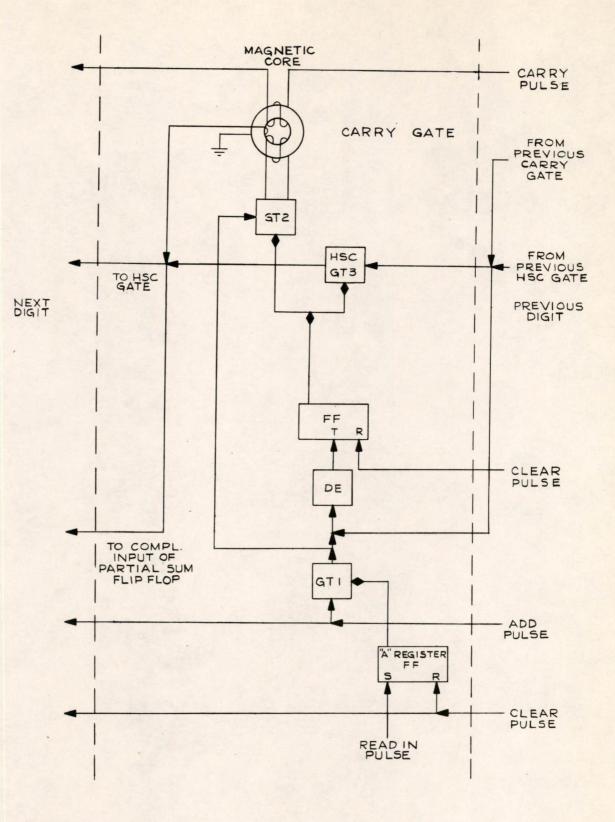

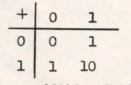

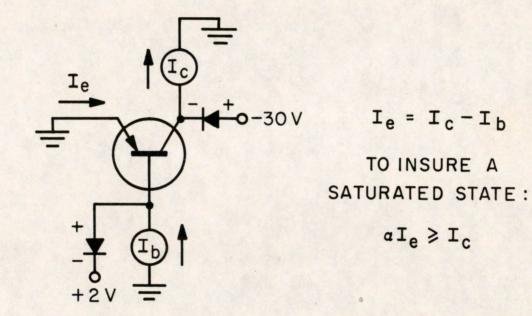

A block diagram of one digit of the proposed system is shown in Figure 1. When the partial sum flip=flop is in the "1" position, gate 2 will conduct a pulse to the core if the "A" register flip=flop is in the "1" position<sup>(1)</sup> and an add pulse is applied to the appropriate line. If the partial sum flip=flop is in the "0" position, the gate cannot be triggered by an add pulse. The carry pulse is assumed to come from a vacuum tube driver which drives the cores of the different digits in series. This is probably the best way to combine transistors, cores, and vacuum tubes. Local elements which drive only a gate and flip=flop, etc., can employ transistors, but a driver which must supply a current or voltage pulse to a whole line of elements should be a vacuum tube.

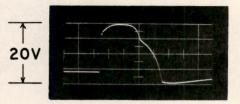

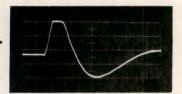

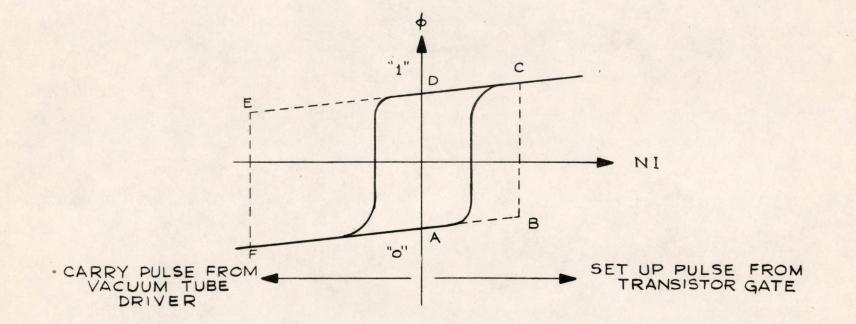

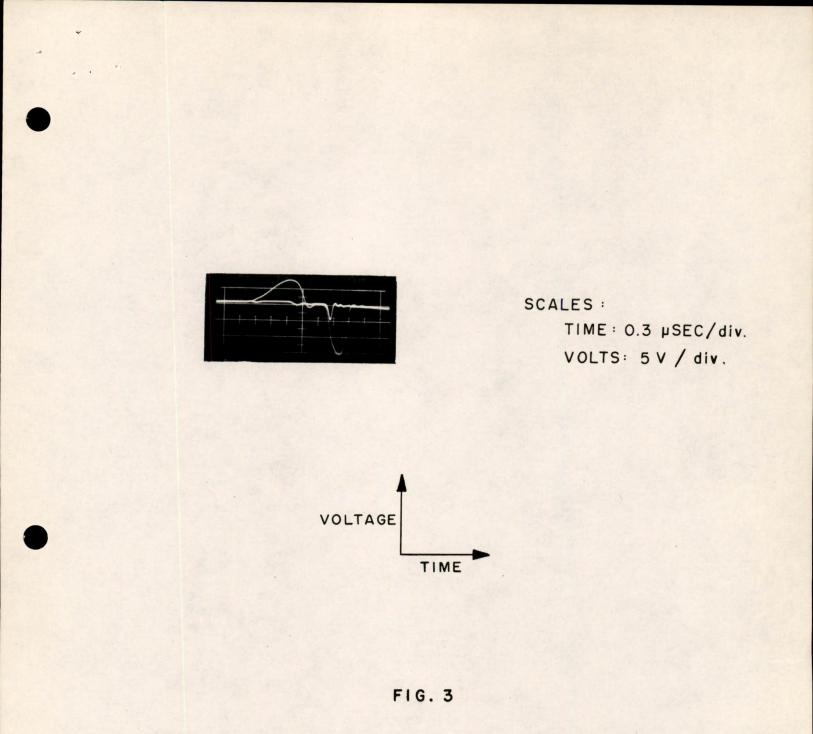

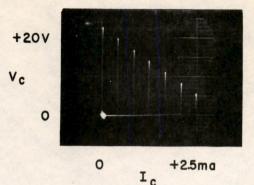

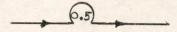

The transistor gate 2 in Figure 2A is required to set the core to the "1" position (see Figure 2B), if a carry is to be generated. The carry pulse then switches the core back to the "0" position. If the core held a "1", a large negative output voltage will be induced in the output winding by the carry pulse, whereas if it held a zero, a small output pulse will be obtained. The output from the core under these two conditions is pictured in Figure 3.

It should be noted here that the load on the gate is the complement input to a flip-flop and the sensing input to a "high-speed carry gate."

<sup>1.</sup> This is arbitrarily defined. When the flip-flop is in the "l" position, the voltage of the collector attached to the gate circuit is assumed at its most negative value.

The core replaces the carry flip-flop and gate circuit in the present system.

# 2.0 Details of the Carry System

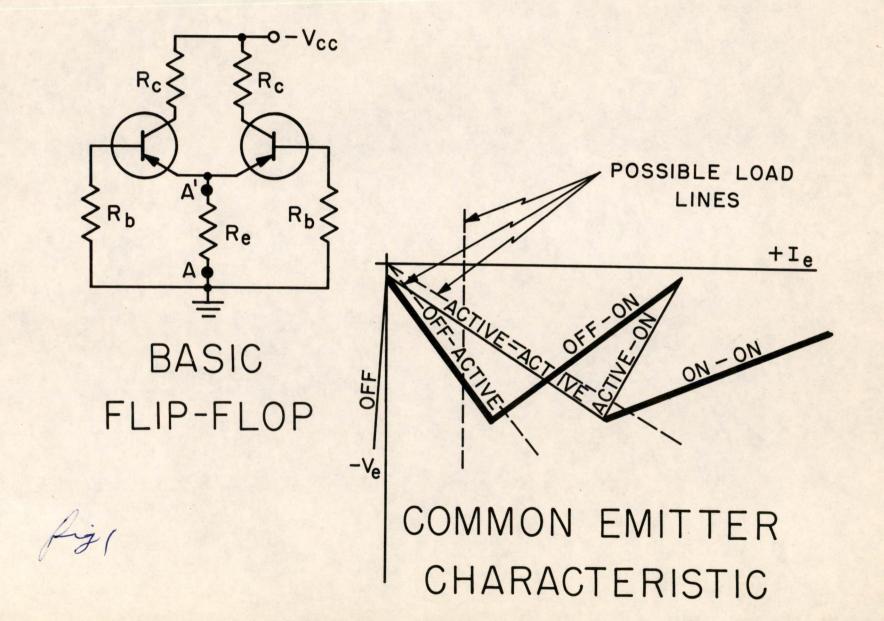

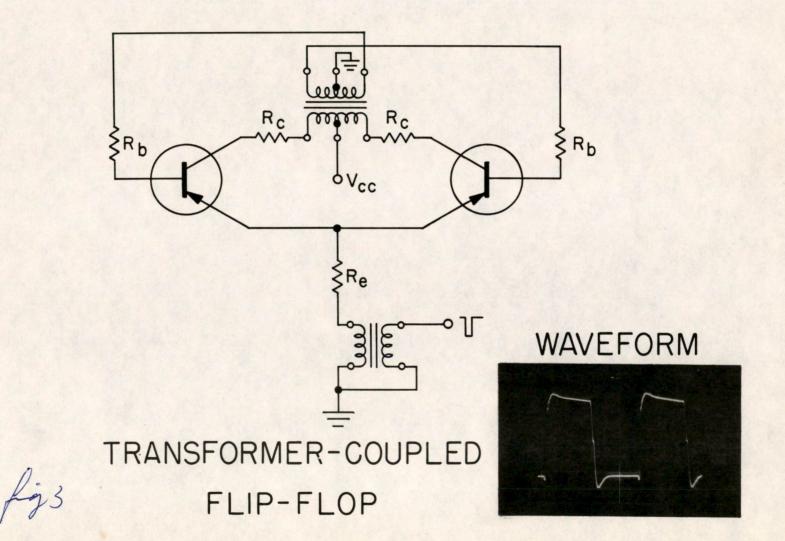

The schematic diagram of the complete system is given in Figure 2A. The partial sum flip-flop is a transistor flip-flop which is of the non-saturating type.(2) Thus the two stable states of the transistors are the "off" and the "active" states. Circuits of this type can be run at higher repetition rates and with smaller input trigger voltages because they are not plagued by "hole storage" problems.

The gate circuit is essentially one which was designed by C. T. Kirk<sup>(3)</sup> The collector voltage of the flip-flop usually swings from about =9 v to = 20 v. When the voltage at point A is =9 v the emitter diode of the gate circuit will be in the reverse direction due to  $V_{l_1}$ . When the flip-flop is complemented, the voltage  $V_{l_1}$  and diode  $d_{l_2}$  clamp the collector voltage to about =15 v. Now when a sensing pulse is applied at the emitter, the pulse will be conducted to the core and set it to the "1" position.

## 3.0 Design of Windings on the Magnetic Core

The design of the windings on the core was performed with the following points kept in mind:

- (1) A metallic core should be used because for a given (NI)<sub>net</sub> it will switch faster than a ferrite core.

- (2) In order to reduce both the back voltage on the transistor in the gate circuit and the switching time of the core, a core with the least number of wraps of material, the smallest diameter bobbin, and 1/8 mil tape should be chosen. (The core available was a mo-permalloy core 1/8 mil, 1/8 inch diameter, 1/8 inch depth and 5 wraps.)

- (3) The maximum number of turns which can be wound on this core is about 100 turns.

Using experimental data showing the switching time and maximum output voltage from different cores as a function of  $NI_{net}$ , an approximation to the switching times and output voltages to be expected may be obtained. In this design the  $(NI)_{net} = N_1 I_1 - (N_2 I_2)_{av}$ , where the values of N are those shown in Figure 2A. The output wave (Figure 3) can be

<sup>2.</sup> Carlson, W., "A High Speed Transistor Flip-Flop," Air Force Cambridge Research Center, Technical Report 53-16, June 1953.

<sup>3.</sup> Kirk, C. T., "A Transistor Grounded Base Amplifier as an AND Gate," M=2810, Lincoln Laboratory Division 6, May 7, 1954.

Page 3

approximated by a triangle; thus  $(N_2I_2)$  av =  $\frac{1}{2R_1}$ . Since the output voltage should have a peak amplitude of at least 15 volts,  $(N_2I_2)_{av} \approx 0.2$  ampere-turns. The  $N_1I_1$  used for the picture of Figure 3 was  $\sim 1.5$  ampere-turns. This can be increased with a corresponding decrease in switching time and increase in output amplitude since the area under the output voltage curve must be a constant as  $NI_{net}$  is varied.

#### 4.0 Selection of a Transistor for the Gate Circuit

The three design criteria for the gate circuit are:

- (1) The transistor should not go into the saturated region when driving the cores.

- (2) The transistor must be capable of dissipating the power encountered during the operation.

- (3) The frequency response of the transistor should be as high as possible in order to decrease the rise time of the output pulse.

When the carry pulse switches the core to the "O" position, a pulse of about 40 volts is induced across the winding in the gate circuit, opposing  $V_{CC}$ . If diode 2 were not included there would be a large hole storage effect since the collector diode would then be switched to the forward direction. Furthermore, a positive pulse would be fed back to the control flip-flop and trigger it. The diode d29 however, overcomes these difficulties since it reverses at this time. The forward current in the collector diode is thus limited to about 100 wa. Also, due to the voltage divider action the flip-flop receives very little feedback voltage.

Since  $I_e = 0$  and  $r_c = r_{cf}$ , the transistor actually goes into the passive region for a short time so there may be some hole storage effects. Because of the small forward current and short time in the forward condition, they should be negligible.

<sup>4.</sup> This set up pulse output will not be harmful since the following circuit can be designed to trigger on negative pulses only.

By increasing  $N_1I_1$  the output voltage can be increased to about 30 v peak amplitude with a 0.2 µsec width. The main limitation to the prf is the setup time of the core which is about 1 µsec. The maximum prf obtained was about 350 kc. The limitations are due to the frequency response of the transistor in the gate circuit and the maximum current obtainable from the gate circuit.

If vacuum tubes alone were used in this system it could, of course, be run at a much faster rate. The decision to use transistors or vacuum tubes, however, will be contingent upon many other factors as well as speed.

Stanley ( Stanley Oken Signed Approved

Donald

SO/jk

Drawings:

Figure 1 B-59506 Figure 2A B-59507 Figure 2B A-59508 Figure 3 A-59509

FIG. I

ONE DIGIT OF ACCUMULATOR USING THE NEW CARRY CIRCUIT

B-59506

FIG.2A SCHEMATIC DIAGRAM OF THE SYSTEM USED TO TEST THE NEW CARRY CIRCUIT

B-59507

A-59508

FIG. 2B

•.

THE OPERATING LOCUS ON THE HYSTERESIS LOOP OF THE MAGNETIC CORE

# OUTPUT VOLTAGE FROM THE CORE

## Distribution List for Transistor Section Distribution 2

# Internal Distribution

- I. Aronson R. Best

- H. Boyd

- D. Brown

- R. Burke

R. Callahan

- E. Cohler

- D. Eckl

- H. B. Frost

- R. Gerhardt

- A. Heineck

- J. Jacobs

- N. Jones

- C. Kirk

- W. Klein

- C. Laspina S. Oken H. Platt D. Smith L. Sutro

- D. Shansky C. Schultz N. Taylor J. Woolf C. Zraket

J. W. Forrester R. R. Everett S. H. Dodd A. M. Falcione Div. 6 - Library (15 to 20 Copies) M's by B. Paine--1 copy to V. Savio A's--1 copy to R. Nelson

#### External Distribution

Professor Adler - 22C-027C (4 Copies) I. Lebow - B-226 - Lexington R. Baker - B-226 - Lexington Professor Zimmerman (RLE) Professor Caldwell (EE Dept)

Professor D. P. Campbell (Servo Lab) Professor T. S. Gray (Servo Lab) Tom Gabor (Dyn. Anal. & Control Lab) S. Schwartz (Group 35) R. Bradbury - AFCRC

Dr. Johnson - AFCRC D. Esakov - AFCRC E. Rosenblum (Group 35)

A. P. Kromer (10 copies of M-Notes for I.B.M.)

Bldg. 32 - Library

Air Force Cambridge Research Center Attention: Document Room---CRQ-SL-1 230 Albany Street

Bert

Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SUBJECT: <u>GENERAL CHARACTERISTICS</u> OF <u>GERMANIUM</u> AND <u>SILICON</u> <u>DIODES</u> <u>AND</u> TRANSISTORS

To: Transistor Distribution 2

From: Nolan T. Jones

Date: July 1, 1954

Abstract: The construction and electrical characteristics of currently available germanium and silicon diodes and transistors are summarized. The general order of increasing diode forward resistance is alloy junction, grown junction, bonded, and point-contact. The general order of decreaseing back resistance is grown junction, bonded, alloy junction, and pointcontact. Transistors included are grown-junction n-p-n, alloy-junction p-n-p, and point-contact.

## 1.0 Introduction

A brief description of the physical and electrical characteristics of the common semi-conductor diodes and transistors is presented here as a foundation for later discussions of the minority carrier storage characteristics of these devices. This is Chapter II of the author's thesis, "Minority Carrier Storage in Diodes and Transistors." There are four types of construction: point-contact, bonded, grown junction, and alloy or diffused junction, and two materials used in commercial products: silicon and germanium.

#### 1.1 RTMA Type Numbers

The standard type numbers of the Radio-Television Manufacturer's Association are the familiar IN series for diodes, 2N for the three element transistors, and 3N for tetrode transistors. The diode type numbers such as 1N34, generally denote that the static characteristics will fall within certain specified limits. These are most often taken at three points: the forward current at +1 volt drop, and the currents at two values of back voltage. They are limits in the truest sense; the static characteristics may vary widely between units from the same manufacturer and between manufacturers, although all may fall within the specified limits for the given type number. A letter suffix on the type number may denote different static characteristics,<sup>\*</sup> construction, or manufacturer from that of the original application for the given type number to the RTMA.

\* Higher back resistance in the 1N34A, 1N38A, and 1N56A

The specification of transistors is in a state of flux at present. Several AIEE-IRE committees are studying the problems, and they will probably make specific recommednations for standardization when their work is completed. The electrical description of transistors is included in several articles in the literature<sup>\*</sup> to which the reader is referred.

# 2.0 Grown-Junction Diodes

The grown-junction diodes are constructed by the introduction of p-type impurities into the n-type melt as the germanium crystal is being grown, converting the remainder of the crystal to p-type with a higher impurity concentration. Then the ingot is cut into small rectangular prisms about 40 mils square and 120 mils long with the p-n junction normal to the length. Non-rectifying or "ohmic" contacts are soldered to each end and the diode has the cross section of Figure 2.1e. The junction is of high quality, i.e. the electrical characteristics are very similar to the ideal theoretical characteristics of a p-n junction.

The current-voltage relationship in an ideal p-n junction diode is the familiar expression:

$$I = I_{o} \left[ \exp(qV/kT) - 1 \right]$$

where V is the junction voltage, k is Boltzman's constant, T is absolute temperature, and q is the electronic charge. This assumes that ohmic drop is negligible.  $I_0$  is a function of the temperature and the impurity concentrations of the germanium. The term kT/q is about 0.026 volt at room temperature, so that for positive voltages large with respect to 0.026 the exponential term is much larger than 1, and for negative voltages of the same magnitude the exponential becomes small compared to 1. This means that the expressions for forward and reverse current become:

| If | - | $I_{o} \left[ \exp(V_{f}/0.026) \right]$ | $ V_{f}  > 0.026 \text{ volt}.$ |  |

|----|---|------------------------------------------|---------------------------------|--|

| Ir |   |                                          | $ V_r  > 0.026$ volt.           |  |

At very high reverse voltages, the junction should exhibit a zener breakdown and the dynamic resistance would drop to a very low value. Present day germanium junction devices do not show a true zener, but an ionization or avalanche breakdown<sup>13</sup> due to carriers crossing the junction under extremely high fields.

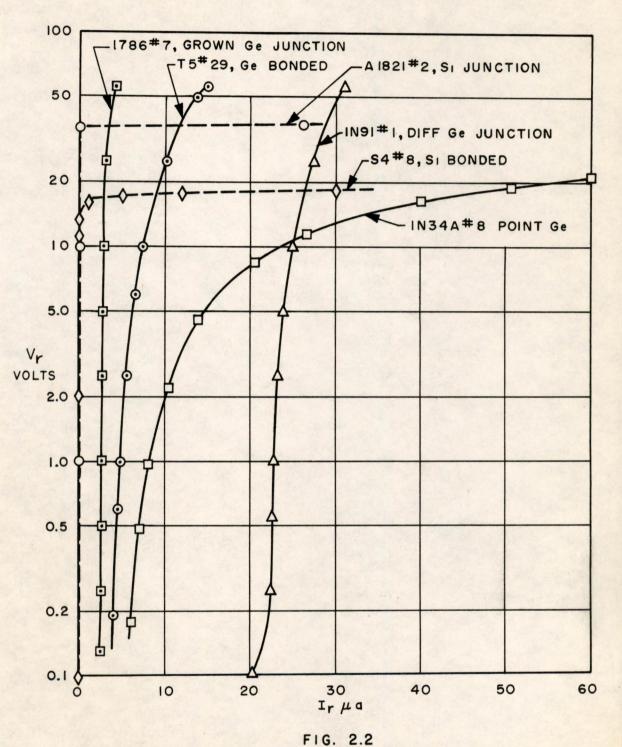

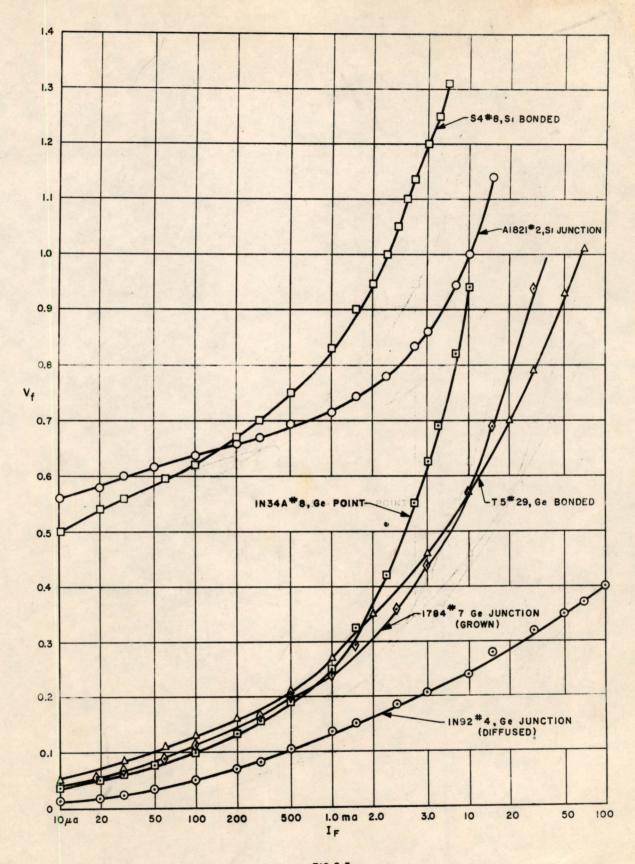

The static reverse and forward characteristics of all the diode types are illustrated in figures 2.2 and 2.3 respectively. The curvature of the forward characteristic of the grown junction diode, 1784 #7, indicates that ohmic drop is not negligible in this diode. Since the resistivity of the germanium used in these grown junction diodes is relatively high this ohmic drop could be anticipated. The reverse current for the 1786 grown germanium junction diode is quite constant over a wide range of reverse voltage.

\* References 1, 2, 3, 4, 5, and 6 present thorough coverage of the subject.

## 3.0 Alloy Junction Diodes

The first step in the construction of the alloy or diffused junction diodes is the placing of a pellet of p-type impurity on the surface of an n-type wafer, soft-soldered to a conventional ohmic contact base. Under heating the impurity dot melts and dissolves a small amount of germanium at the surface. The device is allowed to cool, and the solution re-crystallizes producing a highly doped p-region. The cross section is Figure 2.1d. The linear forward characteristic of the 1N92 plotted in Figure 2.3 fits the ideal case quite well. The reverse has noticeable curvature and the magnitude of the saturation (or constant) current is high. This is typical of this particular series of alloy diodes and not the construction method.

An alloy silicon diode, Type Al821 #2, is included in the electrical characteristics. The dynamic forward resistance at currents below 1 ma is the same order as the forward resistance of the germanium devices, but the static resistance, or  $V_f/I_f$ , is much larger. The reverse resistance is very high at low voltages; the reverse current is usually measured in millimicroamperes in silicon devices. This particular diode shows what is most likely an avalanche breakdown at 37 volts.

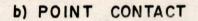

## 4.0 Point Diodes

The point diodes are made by a large number of manufacturers and in a wide variety of types. Many of these, such as 1N34 and 1N38, have been in general use for years, although much less is known of the physics of point devices even at the present. The construction of point diodes is illustrated in Figure 2.1b. An n-type germanium wafer about 40 mils square and 10 to 20 mils thick is soldered to a metal base to make the usual ohmic contact. Then a catswhisker 1 to 2 mils diameter with a pointed or chisel shaped tip is placed in contact with the wafer's surface. A small amount of mechanical stress is added to the whisker for mechanical stability after contact is made. Then the diode is electrically "formed" for mechanical and electrical stability and the desired electrical characteristics. This forming is basically a heating process and may be done by condenser discharge or by alternating or direct currents of the order of an ampere for a fraction of a second. The effect of this forming is to produce a p-type germanium layer under the point, either by diffusion of impurities from the whisker or by heat production of lattice imperfections. The size and quality of the peregion is apparently a function of the amount and length of time of forming, whisker shape, and least important, whisker material.

The principal physical difference between point and bonded diodes is the whisker material and the electrical prosessing. Point diode whisker materials used are hard, high-melting-point materials such as tungsten and molybdenum. In their commercially available forms, these materials often contain small amounts of p-type impurities. In addition at least one manufacturer actually plates the whisker with an impurity material before

construction. During forming the whisker tip retains its shape as the p-region forms, and the whisker apparently does not become physically attached to the germanium. Destruction of common diodes and examination of the surface of the germanium wafers has shown that it is extremely difficult, if not impossible, to determine where the contact had been. The p-n junction is ordinarily of low quality as shown in the electrical characteristics. The current increases directly (though not linearly) as back voltage increases, and the forward characteristic is curved throughout the range.

The electrical characteristics of point diodes are relatively complex functions of resistivity, surface states, and the size and character of the p=n junction. References 1, 2, 8, 9, 10, 11, and 12 furnish information on the subject although none presents a complete point diode theory.

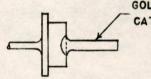

#### 5.0 Bonded Diodes

The whisker material of bonded germanium diodes is a low meltingpoint material, usually a gold alloy with a p-type impurity material. The electrical processing, or bonding, causes the whisker to melt under the localized heating, and dissolve a small amount of germanium. Cooling allows recrystallization and the result is a small-area, highly-doped p-region. The whisker tip may mushroom, and ordinarily forms a strong mechanical connection to the germanium. Cross section of the bonded diode is shown in Figure 2.1c. The electrical characteristics of the bonded diode illustrated in Figures 2.1 and 2.3, the T5 #29, indicate a high quality junction. Its reverse characteristic has low and fairly constant current. The forward resistance is quite low and the curvature of the forward characteristic is much less than for point devices.

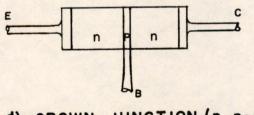

# 6.0 Grown Junction Transistors

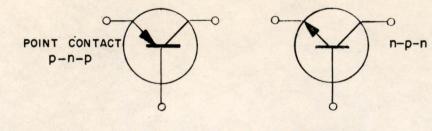

Transistors resemble two diodes on the same germanium wafer constructed so that the forward current in the emitter diode affects the reverse current in the collector diode. The various types of transistors are constructed in the same general way as the diodes of the same type.

Construction of the grown junction transistors is as follows: At a point in the drawing, or growing, of an n-type germanium crystal sufficient p-type impurities are introduced into the melt to cause the germanium to become p-type. The crystal is grown a very short distance and then an excess of n-type impurities is introduced to convert the crystal back to n-type, producing two p-n junctions with a common, thin layer of p-material between. Ohmic contacts are soldered to each end and to the p-region and the n-p-n transistor has the cross section of Figure 2.4d. All commercially available grown junction transistors are n-p-n. Electrical characteristics are illustrated in Figure 2.5a.

Current gain,  $\alpha_g$  is usually 0.90 to 0.999 and collector resistance,  $r_{cg}$ greater than a megohm.

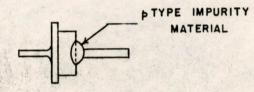

# 7.0 Alloy Junction Transistors

Two alloy junction diodes on opposite sides of a very thin wafer produce an alloy or diffused junction transistor. Cross section is shown in Figure 2.4c and electrical characteristics in Figure 2.5b. Both a and rc are slightly smaller than these parameters for the grown junction transistors; values of 0.85 to 0.99 and 0.3 to 1.0 megohm are typical. Most alloy junction transistors are p-n-p although one alloy n-p-n unit\* was marketed for several months.

In normal operation of transistors, the emitter diodes are biased in the forward direction and collectors in the reverse. Forward bias of a p-n junction is p-positive. This means that collector voltage for n-p-n units is positive and for p-n-p negative; hence the inversion of the collector characteristics of these types in Figure 2.5a and 2.5b. The schematic symbol has an arrow in the emitter denoting the direction of forward current flow as in Figure 2.4a.

### 8.0 Point-Contact Transistors

Construction is illustrated in Figure 2.4b and electrical characteristics in Figure 2.5c. Two contacts are located close together on the surface of an n-type wafer. Only the collector is electrically formed to produce the desired transistor characteristics. The result is that the collector contact area becomes relatively large and its back resistance low. re is about 20,000 ohms and a varies from 2 to 3 in most pointcontact transistors.

\* RCA 2N35

Signed Nolan T. Jones DJ.E. Nolan T. Jones Approved Donald J. Eckl

NTJ/jk

Drawings attached:

| Figure | 2.1 | 8 | A-58472 |

|--------|-----|---|---------|

| Figure | 2.2 | - | A-58439 |

| Figure | 2.3 | 0 | C-58442 |

| Figure | 2.4 | 8 | A=59105 |

| Figure | 2.5 |   | A-58856 |

Page 6

#### BIBLIOGRAPHY

- 1. Shockley, W., <u>Electrons</u> and <u>Holes</u> in <u>Semi-Conductors</u>, D. Van Nostrand Co., <u>New York</u> (1950).

- 2. Shea, R. F., Principles of Transistor Circuits, John Wiley and Sons, New York (1953).

- 3. Morrow, W. E., Jr., and Schwartz, S., "Some Measurements on Junction Transistors," M.I.T. Lincoln Laboratory Technical Memoranda TM=22 and TM=56 (10 December 1953).

- 4. Adler, R. B., and others, "Some Notes on Transistor Circuits," M.I.T. Lincoln Laboratory Technical Report No. 25 (6 January 1953).

5. "Transistors, Crystal Diodes, and Related Semi-Conductor Electronic Devices," Military Specifications MIL-T-12679A (Sig C) (23 September 1953).

- 6. Jones, N. T., "Standardized Transistor Parameter Measurements," M.I.T. Digital Computer Laboratory Engineering Note E-441-1 (January 3, 1952, revised June 10, 1952).

- 7. McMahon, M. E., Seminar on Properties and Applications of Hughes Diodes and Transistors, M.I.T., Cambridge, Mass. (7 May 1954).

8. Bardeen, J., and Brattain, W. H., "Physical Principles Involved in Transistor Action," <u>Physical Review</u>, Vol. 75, No. 8 (April 15, 1949).

- 9. Cutler, M., "The Forward Characteristics of Germanium Point Contact Rectifiers" Hughes Aircraft Co. (May 18, 1953).

- 10. Cutler, M., "Point Contact Rectifiers in Germanium: Flow of Electrons and Holes Through the Surface Barrier," Hughes Aircraft Co. Report (May 1, 1953).

- 11. Cutler, M., "The Flow of Electrons and Holes in Point Contact Rectifiers," Hughes Aircraft Co. Report (April 1, 1953).

- 12. Torrey, H. C., and Whitmer, C. A., Crystal Rectifiers, McGraw-Hill Book Co., New York (1948).

- 13. McKay, K. G., "Avalanche Breakdown in Silicon," Physical Review, Vol. 94, No. 4 (May 15, 1954).

# a) SCHEMATIC SYMBOL

GOLD OR GOLD ALLOY CATSWHISKER ANODE

c) GOLD BONDED

d) DIFFUSED JUNCTION

P n

e) GROWN JUNCTION

FIG. 2.1

DIODE CONSTRUCTION TYPES

TYPICAL STATIC REVERSE CHARACTERISTICS OF DIODES

FIG. 2.3 TYPICAL STATIC FORWARD CHARACTERISTICS OF DIODES

C-58442

all the second

# b) POINT CONTACT

c) DIFFUSED JUNCTION

d) GROWN JUNCTION (n-p-n)

TRANSISTOR CONSTRUCTION TYPES

-

•

(a) GROWN N-P-N JUNCTION RDR TYPE 2517 NO. 10

ΔIe = 0.5ma IN ALL CASES

(b) ALLOY OR DIFFUSED P-N-P JUNCTION CBS-HYTRON 2N36 NO.2

A-58856

(c) POINT CONTACT RCA TA 165 NO. R 386

FIG. 2.5 COLLECTOR CHARACTERISTICS OF THE THREE COMMON TYPES OF TRANSISTORS

& Salvato

Page 1 of 32

Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

Subject: MTC Technician Training Manual - Chapter I

To: N.H. Taylor and MTC Personnel

From: A. Vanderburgh, Jr.

Date: December 14, 1954

Approved: M. Oander C. W. Ogden, Jr.

Abstract:

A technician training course in the troubleshooting of Memory Test Computer was started late in September 1954. This memorandum is the first chapter of a text that will be prepared concurrently with the course.