R.L. Best DOG3

Sheet 1 of 5 Sheets

Division 6 — Lincoln Laboratory Massachusetts Institute of Technology Lexington 73. Massachusetts

SUBJECT: A LAPLACE TRANSFORM ANALYSIS OF PULSE BETA

| To: | Donald | J. | Eckl |  |

|-----|--------|----|------|--|

|     |        |    |      |  |

From:

Ralph C. Johnston Ralph C. Johnston Date: August 21, 1957 Approved:

Abstract: The current gain of a common-emitter pulse amplifier is obtained for a half sine wave input. An analytic expression for the output current is obtained as a function of d-c gain, cutoff frequency, and pulse width. For pulse gains appreciably less than the d-c gains. the former is shown to be almost independent of the latter but directly proportional to the cutoff frequency.

RCJ/md

Distribution:

Barck, P. Best, R.L. Bradspies, S. Cantella, M.J. Corderman, C.L. Davidson, G.A. Eckl, D. J. Fadiman, J. Goodenough, J.B. Gurley, B.M. Johnston, R.C. Kirk, C.T.

Kleinrock, L. Konkle, K. Langford, J. Mitchell, J. L. Neumann, L. Olsen, K.H. Papian, W.N. Pugsley, J. Raffel, J. Savell, R. Hughes, R.A.

Abstracts to the remainder of Group 63 Staff.

This document has been prepared for internal use only. It has not been reviewed by Office of Security Review, Department of Defense, and therefore, is not intended for public release. Further dissemination or reproduction in whole or in part of the material within this document shall not be made without the express written approval of Lincoln Laboratory (Publications Office).

2. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Depart-ment of the Air Force under Air Force Contract No. AF 19 (122)-458.

# A LAPLACE TRANSFORM ANALYSIS OF PULSE BETA

#### 1. Introduction

Pulse beta or the common-emitter current gain with a half sinewave input current pulse is of importance in pulse amplifier and gating circuits. It is not usually given in transistor specifications and so its relation to the common parameters of d-c gain and cutoff frequency is desirable.

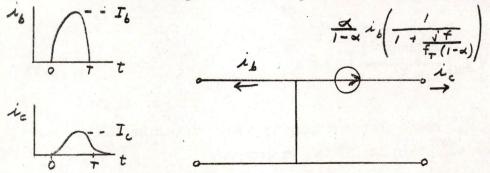

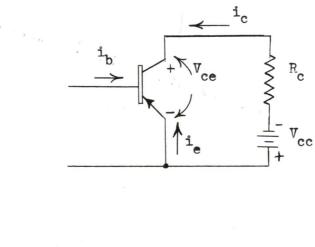

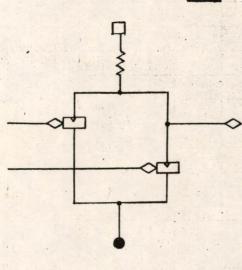

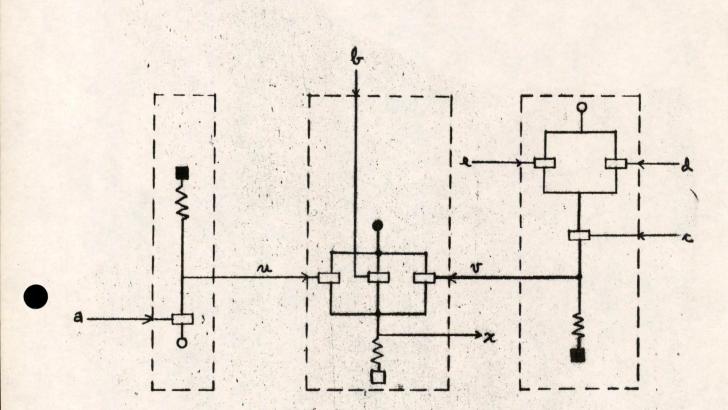

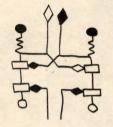

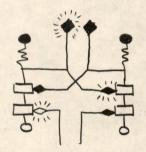

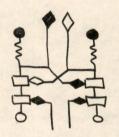

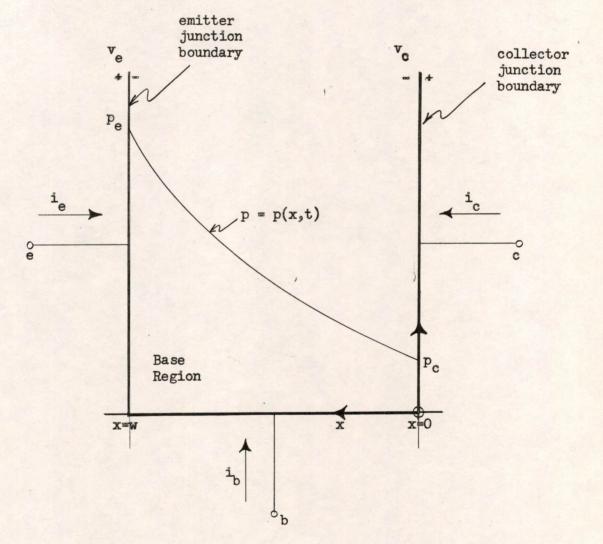

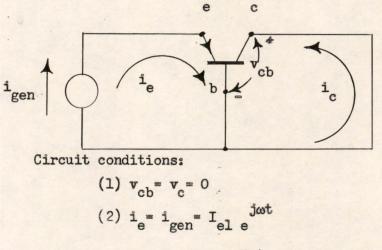

The following transistor equivalent circuit is assumed.

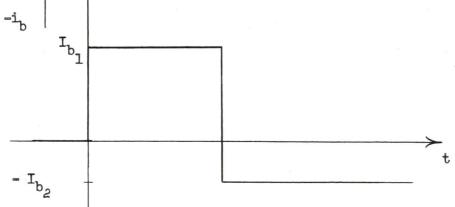

Pulse beta is defined as follows:

$$\beta_{\text{pulse}} = \frac{I_c}{I_b}$$

(1)

where  $I_b$  and  $I_c$  are peak values as shown above. The collector current generator is the product of the d-c beta, the base current, and a frequency response term which gives the magnitude and phase to a sinusoidal input.  $f_T$  is the cutoff frequency measured on the  $fh_fe$  test and equals  $\frac{2}{2.43}$   $f_{\alpha}$ . The common-emitter cutoff frequency is then  $f_T$  (1- $\alpha$ ).

# 2. Laplace Transform Analysis

The procedure for solution is to convert the transfer function from frequency to the s domain by replacing jw by s (this establishes

Johnston, R.C., "Transient Response of Junction Transistors -II" Lincoln Laboratory 6M-4913, S-1, June 19, 1957, eq (109)(110)(106).

1

(3)

2

zero initial conditions), transform the input current, and take the inverse transform of the product by expansion into partial fractions.

$$I_{c}(s) = \frac{\alpha}{1-\alpha} I_{b}(s) \frac{1}{1 + \frac{s}{2\pi f_{T}(1-\alpha)}}$$

(2)

$$I_{b}(s) = \int I_{b}(\sin \frac{\pi t}{T}) \left[ u(t) - u(t-T) \right]$$

$= \int \int_{D} \int_{D} e^{j\pi t/T} \left[ u(t) - u(t-T) \right]$  $= \int_{M} \left[ \frac{I_{b}(1 + e^{-sT})}{s-j^{\pi/T}} \right]$

The symbol,  $\int_{M}$ , means that the imaginary part should be taken. For 0 < t < T, the e<sup>-sT</sup> term in (3) can be dropped.

Next we substitute (3) in (2) and expand in partial fractions.

$$I_{c}(s) = \oint_{m} \left(\frac{\alpha}{1-\alpha}\right) I_{b} \left(\frac{1}{1+\frac{s}{2\pi f_{T}(1-\alpha)}}\right) \left(\frac{1}{s-j^{\pi/T}}\right) = \oint_{m} \left(\frac{K_{1}}{1+\frac{s}{2\pi f_{T}(1-\alpha)}} + \frac{K_{2}}{s-j^{\pi/T}}\right)$$

$$(h)$$

$$K_{l} = \frac{(-1)\left(\frac{\alpha}{1-\alpha}\right) I_{b}}{2\pi f_{T}(1-\alpha) + j^{T/T}}$$

$$K_{2} = \frac{\left(\frac{\alpha}{1-\alpha}\right)I_{b}}{1 + \frac{j}{2Tf_{T}(1-\alpha)}}$$

The inverse transform of (4) is

$$\mathbf{i}_{c}(t) = \int_{\mathcal{M}} \left[ 2\pi f_{T}(1-\alpha) \mathbf{K}_{1} e^{-2\pi f_{T}(1-\alpha)t} + \mathbf{K}_{2} e^{j\frac{\pi t}{T}} \right]$$

6M-4521

$$= \left(\frac{\alpha}{1-\alpha} I_{b}\right) \left[ \frac{\frac{1}{2Tf_{T}(1-\alpha)}}{1+\frac{1}{\left[2Tf_{T}(1-\alpha)\right]^{2}}} e^{-2Tf_{T}(1-\alpha)\frac{\pi t}{T}} e^{\frac{1}{\left[2Tf_{T}(1-\alpha)\right]^{2}}} \right]$$

$$+ \frac{1}{\sqrt{1+\frac{1}{\left[2Tf_{T}(1-\alpha)\right]^{2}}}} \sin\left(\frac{\pi t}{T} - \psi\right) \left[u(t) - u(t-T)\right] (5)$$

where

$$\Psi = \operatorname{Tan}^{-1} \frac{1}{2\mathrm{Tf}_{\mathrm{T}}(1-\alpha)}$$

For  $T \leq t \leq \infty$  the e<sup>-st</sup> term is retained

$$I_{c}(s) = \mathcal{D}_{m}\left(\frac{\alpha}{1-\alpha}I_{b}\right)\left(\frac{1}{1+\frac{s}{2\pi f_{T}(1-\alpha)}}\right)\left(\frac{1+e^{-st}}{s-j\pi/T}\right) = \mathcal{D}_{m}\left[\frac{K_{1}}{1+\frac{s}{2\pi f_{T}(1-\alpha)}} + \frac{K_{2}}{s-j^{\pi}/T}\right]$$

$$K_{1} = \frac{\alpha}{1-\alpha} I_{b} \left( \frac{(-1)(1 + e^{2\pi T f_{T}(1-\alpha)})}{2\pi f_{T}(1-\alpha) + j^{\pi/T}} \right) \qquad K_{2} = 0$$

$$i_{c}(t) = \left(\frac{\alpha}{1-\alpha} I_{b}\right) \left[\frac{\frac{1}{2Tf_{T}(1-\alpha)}}{1 + \frac{1}{\left[2Tf_{T}(1-\alpha)\right]^{2}}} \left(1 + e^{2\pi Tf_{T}(1-\alpha)}\right) e^{-2\pi Tf_{T}(1-\alpha)\frac{t}{T}}\right]$$

(6)

$$\left[u(t-T)\right]$$

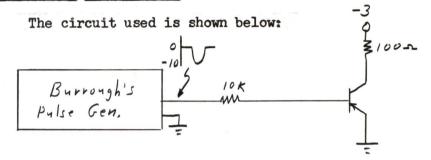

The result may be expressed in more compact form by letting

$$2Tf_{T}(1-\alpha) = \frac{1}{x}$$

and

$$\frac{t}{T} = \tau$$

3

6M-4521 4

$$i_{c}(T) = \begin{cases} \frac{\alpha}{1-\alpha} I_{b} \left[ \frac{x}{1+x^{2}} e^{\frac{-\pi \pi}{x}} + \frac{1}{\sqrt{1+x^{2}}} \operatorname{Sin}(\pi \tau - \psi) \right] & 0 < \tau < 1 \quad (7) \end{cases}$$

$$\left(\frac{\alpha}{1-\alpha}I_{b}\left[\frac{x}{1+x^{2}}\left(1+e^{-\pi/x}\right)e^{-\frac{\pi}{x}\left(\frac{\pi}{x}-1\right)}\right] \qquad \tau > 1$$

where  $\Psi = \operatorname{Tan}^{-1}x$

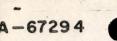

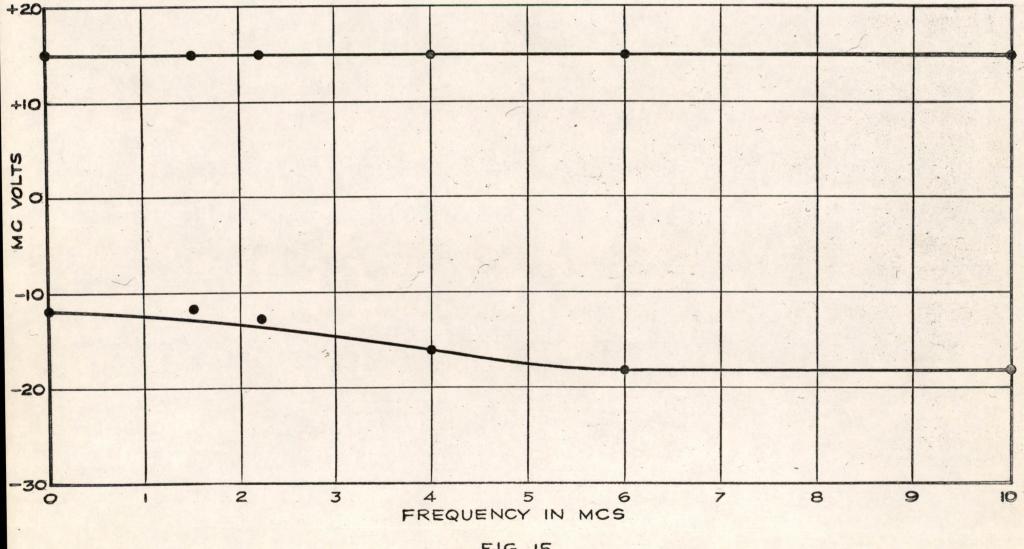

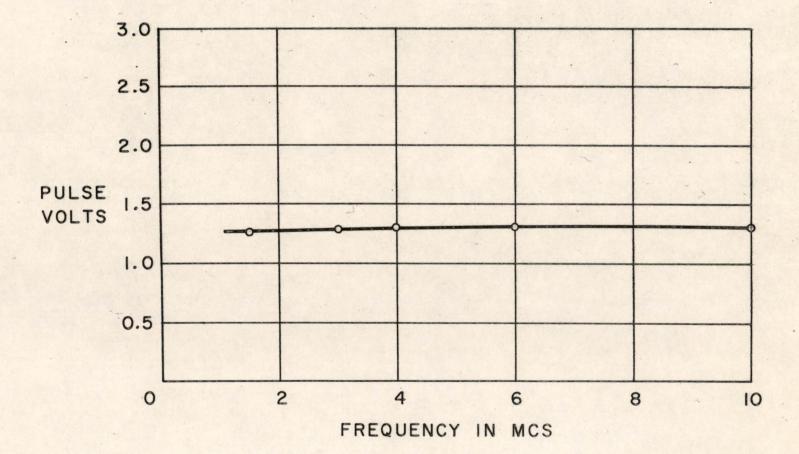

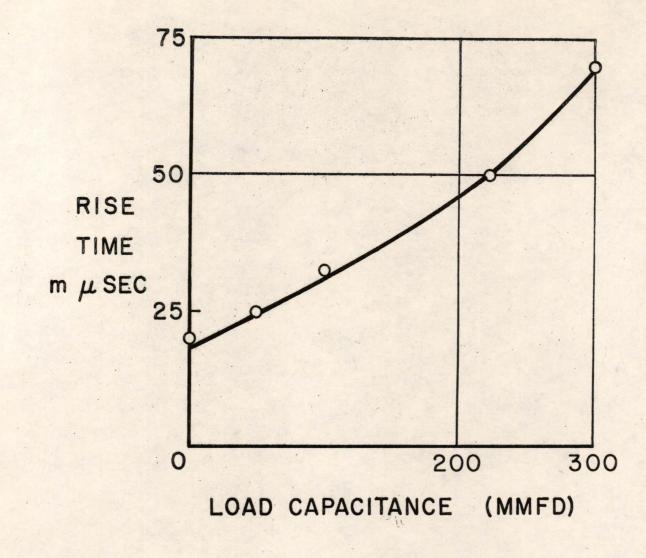

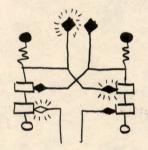

This function is plotted in Fig. 1 for x = 0,1, and 3. The sinusoidal and exponential components are shown dotted.

# 3. Pulse Beta Approximation

It is desirable to have a simple expression for pulse beta. By adding the peak value of the sine term to the value of the exponential term at  $\tau = 1$  an approximate formula is obtained which is 3 percent low at x = 1 and has less error for other values of  $x_{er}$

$$\beta_{\text{pulse}} = \frac{\alpha}{1-\alpha} \left( \frac{x}{1+x^2} e^{-\pi/x} + \frac{1}{\sqrt{1+x^2}} \right)$$

(8)

A useful form may be obtained for large x.

$$\beta_{\text{pulse}} = \frac{\alpha}{1-\alpha} \frac{2}{x} = \frac{\alpha}{1-\alpha} 4 \text{Tf}_{T}(1-\alpha)$$

$$\approx 4 \text{Tf}_{T}$$

(9)

For x between 3 and 12 the formula

$$\beta_{\text{pulse}} \cong 3 \text{Tf}_{\text{T}}$$

(10)

is about 10 percent accurate. Thus it is seen that when the pulse beta is less than say 1/3 the d-c beta, it is almost independent of d-c gain and directly proportional to the common-base cutoff frequency.

Attachment

1

Drawing No. B-82690

R. S. Best BOG3

Memorandum 6M-4521, S-1

Sheet 1 of 3 Sheets

Division 6 — Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SUBJECT: A LAPLACE TRANSFORM ANALYSIS OF PULSE BETA

| To:       | Donald J. Eckl                      |

|-----------|-------------------------------------|

| From:     | Ralph C. Johnston Ralph C. Johnston |

| Date:     | September 12, 1957                  |

| Approved: | 3 f C                               |

|           |                                     |

<u>Abstract</u>: Figure 1 is included, which was omitted by mistake from the main body of the note. The results of an experimental verification by K. Konkle are given and discussed.

### RJC/md

### Distribution:

Barck, P. Best, R.L. Bradspies, S. Cantella, M.J. Corderman, C.L. Davidson, G.A. Eckl, D.J. Fadiman, J. Goodenough, J.B. Gurley, B.M. Johnston, R.C. Kirk, C.T. Kleinrock, L. Konkle, K. Langford, J. Mitchell, J.L. Neumann, L. Olsen, K.H. Papian, W.N. Pugsley, J. Raffel, J. Savell, R. Hughes, R.A.

Abstracts to the remainder of Group 63 staff.

This document has been prepared for internal use only. It has not been reviewed by Office of Security Review, Department of Defense, and therefore, is not intended for public release. Further dissemination or reproduction in whole or in part of the material within this document shall not be made without the express written approval of Lincoln Laboratory (Publications Office). 2. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract Nc. AF 19 (122)-458.

# A LAPLACE TRANSFORM ANALYSIS OF PULSE BETA

# 4. Experimental Verification

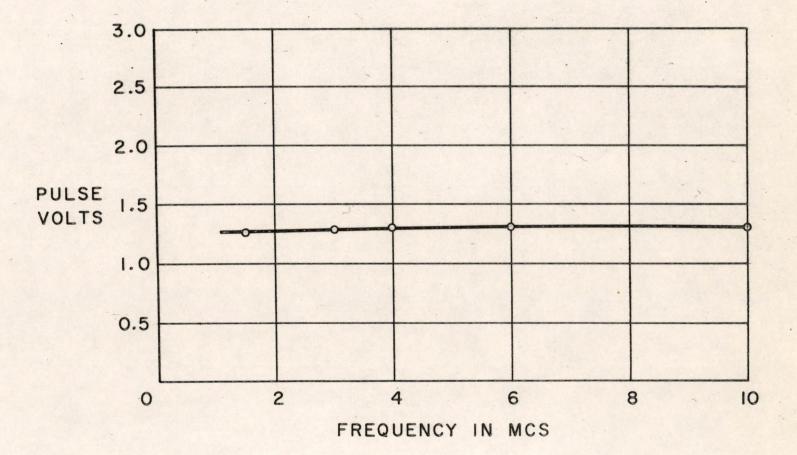

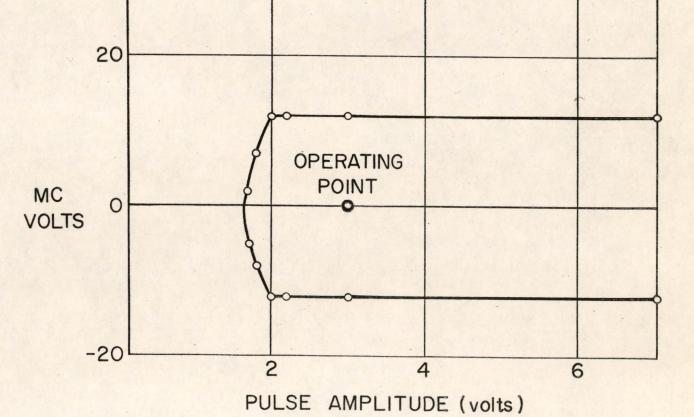

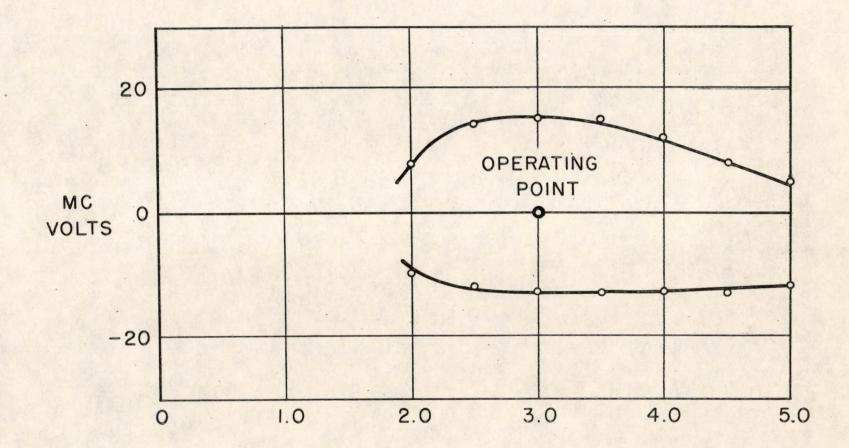

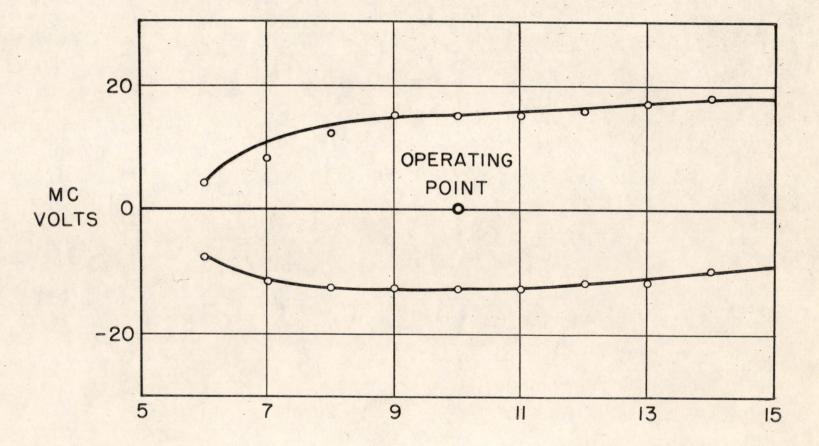

The peak base current is 1 ma. giving a maximum measurable value for pulse beta of 30.

The main difficulty in checking the theory is that the "constants"  $f_T$  and a are not. Actually  $f_T$  varies about as the fourth root of collector voltage and drops off for emitter currents below a few tenths of a ma. The value of a tends to decrease with collector current, especially on the surface barrier transistor.

|      |        | 1                  |     |      | β pulse |      |  |

|------|--------|--------------------|-----|------|---------|------|--|

| Туре | No.    | f <sub>T</sub> ,mc | βο  | x    | Calc.   | exp. |  |

| MAT  | ST276  | 42                 | 40  | 5.83 | 11.3    | 11.6 |  |

| MAT  | STIIII | 55                 | 207 | 11.2 | 17.7    | 17.3 |  |

| SBT  | 214    | 34                 | 11  | 1.72 | 6.65    | 6.0  |  |

Figure 2. Summary of Experimental Verification

Figure 2 gives the results of measurements on three transistors by K. Konkle. It is felt that the agreement between calculated and experimental values is quite good considering the measurement problems discussed previously.

Attachment Drawing No. B-82690

COMMON - EMITTER RESPONSE TO HALF SINE WAVE PULSE

B-82690

2

9

i

K& Olsen

179

Page 1 of 7

Division 6 — Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SUBJECT: Electronically Variable Power Supply

To: Donald J. Eckl

From: Edmund U. Cohler

Date: 30 November 1956 Approved: N.J.C.R.

Donald J. Eckl

<u>Abstract:</u> The design considerations for a supply capable of supplying from 50 millivolts to 40 volts to a 12 ohm load are presented. The supply is unique in being capable of excellent regulation, electronic control of output by means of a variable reference, and fast response to changes of electronic input. The supply is reversible with respect to ground (it may not be operated floating). The input requirement from the electronic standard is about 5 microamperes. The supply employs transistor regulators and semiconductor rectifiers for maximum efficiency at these low voltages and high currents. A supplement to this note will discuss the measured characteristics of this supply.

# Distribution List

Bradspies, S. Brown, D. R. Coffin, S. T. Davidson, G. A. Eckl, D. J. Fadiman, J. R. Fergus, P. A. Gurley, B. M. Hudson, R. W. Hughes, R. A. Jahn, R. C. Kirk, C. T. Olsen, K. H. Norman, C. A.

This document is issued for internal distribution and use only by and for Lincoln Laboratory personnel. It should not be given or shown to any other individuals or groups without express authorization. It may not be reproduced in whole or in part without permission in writing from Lincoln Laboratory. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No. AF 19(122)-458.

# I. INTRODUCTION

# Requirements

A supply was desired which would provide a means for automatic marginal checking of a computer. This application required the following features.

- a. Output voltage to be electronically variable from close to zero to +40 volts.

- b.. The response should be much less than 1 millisecond.

- c. A minimum load resistance of close to 10 ohms.

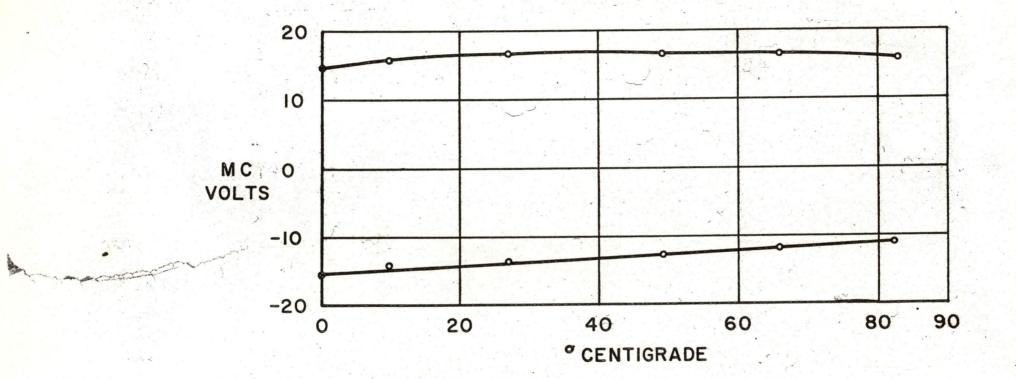

- d. Ambient conditions from 20°C to 55°C should not cause deterioration or failure.

- e. Regulation should be on the order of 0.2 volts.

- f. About 5 microamperes should be drawn from the electronic standard.

- g. Either end of the supply should be capable of being grounded. Basic Design

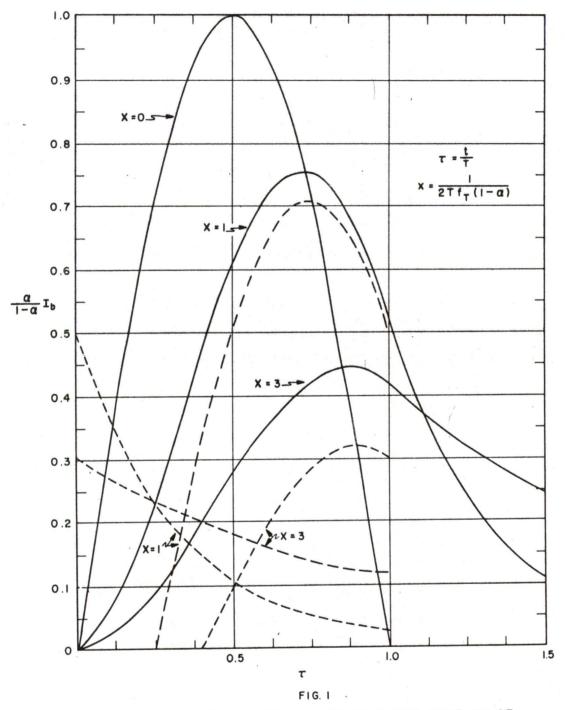

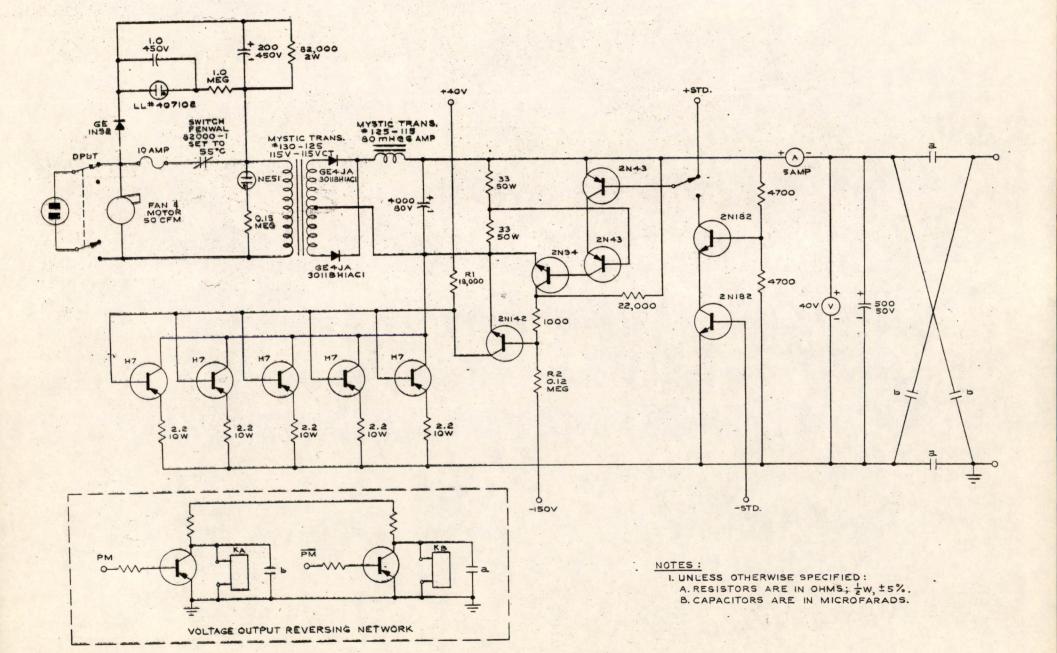

As a starting point a supply designed for TX-O by Robert Hughes was used. The circuit of this supply is shown in Fig. 1. Excellent as this supply was, it needed extensive modification to meet the above requirements. The dissipation in the series regulator transistors has been kept to a minimum in the TX-O supply by reducing the input voltage with tapped transformers and a range switch, (S2). This method could not be used in the new supply since electronic variation was desired. The maximum load current to be supplied is four times as great since the load resistance is the same but the maximum voltage is four times as great. Thus the power capabilities are multiplied 16 times. Voltages in the regulator are also higher which in some cases would overrun the transistor capabilities if the design were unchanged. Finally, the input circuit must be modified to permit a grounded reference with either end of the supply grounded.

II. DESIGN

Series Regulators

6M-4544

The series regulators were tackled first. They would be required to handle considerably more power than they had in the previous supply. The straightforward approach to solution of this problem was to provide enough series regulators of sufficient rating to pass the desired current at the required voltage. It can easily be shown that the dissipation required in such a regulator is:

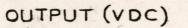

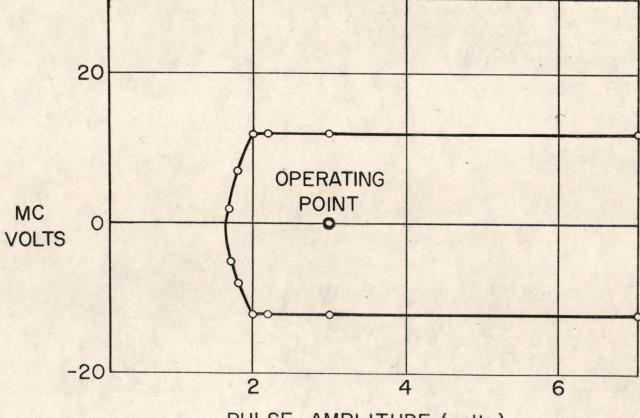

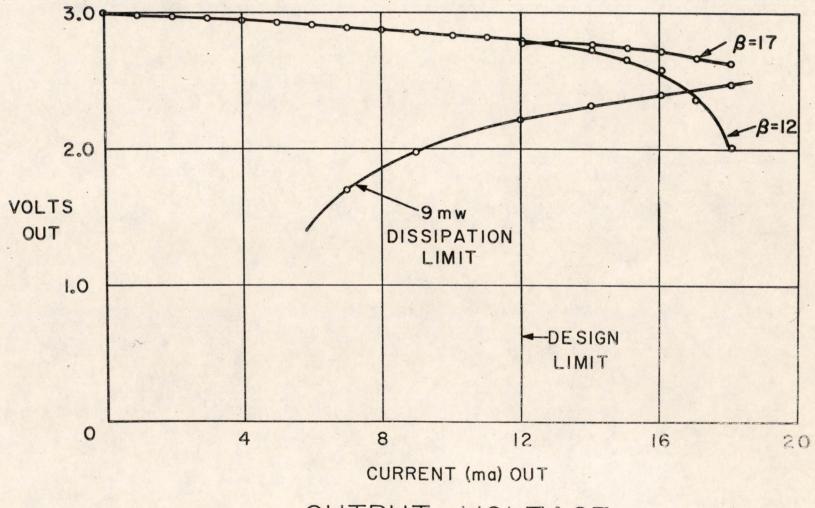

$$V_{s}^{2}/4R_{1s} = P_{max}$$

(1)

where  $V_s$  is the maximum voltage of the unregulated supply, and  $R_{1s}$  is the sum of the internal resistance of the unregulated supply and the load resistance. In the case of a negligible supply resistance and a total load of 10 ohms on a 56 volt supply, the dissipation,  $P_{max}$ , is 78.4W. As can be seen from Figure 3 the maximum voltage of unregulated supply for an input of 122.5 volts is 56 volts. It was felt that the AC input tolerance could be set at 115 volts + 7.5 - 10.0 volts because of the closer control on overvoltage inherent in the distribution system.

The transistors to be used in the series regulator position were to be Minneapolis-Honeywell's H-7's<sup>1</sup>. These transistors may be operated at a junction temperature of 95°C. Thus, at an ambient of 55°C we may allow a drop of  $40^{\circ}$ C in the thermal resistance from junction to ambient.

Assuming a total thermal resistance of  $2.55^{\circ}$ C/watt,  $2.2^{\circ}$ C/w for the H-7 and  $0.35^{\circ}$ C/w for the dissipator<sup>2</sup>, we then require 5 transistors in the series regulator.

CURRENT EQUALIZATION

In order to maintain equal currents in all five series regulator transistors, small resistors were inserted in series with each emitter. The collector current in the active region is given by

$$I_{c} = I_{B}\beta = \frac{V_{B}\beta}{R_{input} + R_{EX}}$$

(2)

where R<sub>EX</sub> is the extermal emitter resistance and R<sub>input</sub> is the grounded emitter input resistance of the transistor.

<sup>1.</sup> Minneapolis Honeywell 2N57 power transistor specifications sheet Form number TR17

Page 4

$$I_c \approx \frac{V_B}{\frac{R_{inp}}{\beta} + R_{EX}}$$

(3)

$$\frac{I_{c \min}}{I_{c \max}} \approx \frac{R_{EX} + \frac{R_{inp \min}}{\beta \max}}{R_{EX} + \frac{R_{inp \max}}{\beta \min}}$$

(4)

Actually Eq. 4 gives an extremely conservative estimate since the input resistance is very closely associated with beta. A more realistic estimate of the variation might be obtained from

$$\frac{I_{c \min}}{I_{c \max}} \stackrel{R_{EX}}{\longrightarrow} + \frac{R_{inp \min}}{\beta_{min}}$$

(5)

$$\frac{R_{EX}}{\beta_{max}} \stackrel{R_{EX}}{\longrightarrow} + \frac{R_{inp \max}}{\beta_{max}}$$

Let us then compute the ratio of the minimum to maximum current per transistor, in terms of Eq. 5.

$$r = \frac{I_{\min}}{I_{\max}}; \quad n = number of transistors in the series regulator.$$

$$A = Average current/transistor$$

$$I = Maximum current in any one transistor.$$

The worst case will occur where all of the transistors except one are carrying the minimum current and the other is carrying the maximum current. Then:

Total current =

$$nA = (n-1)r I + I$$

(6)

$I/A = \frac{1}{r + \frac{1-r}{n}}$

2. See 6M-4390, Heat Dissipator Characteristics, E. Cohler, 9 July 1956

If we now substitute in Eqs. 5 and 7 the value of  $R_{EX}$  shown in Fig. 2. and the known variation of  $R_{inp}$  for the H=7<sup>1</sup>° at 560 ma, we find: r = .84 and I/A = 1.15. The final rated load, may then be calculated to allow a 15 percent increase in transistor dissipation over the average dissipation.

# SERIES FEED TO SERIES REGULATORS

Series feed, rather than shunt feed, was used for the transistor supplying the series regulators. This allowed a decrease of beta in the power requirements from the series regulator stage to the feeding stage. Thus, beta being 80 minimum in the H-7, the requirement for this stage is 78.4/80 = 0.98 watts. Series feed meant using an n-p-n transistor in the feeding stage, and the best available in the desired dissipation range was the Sylvania 2N142<sup>3</sup>. In fact, this transistor attached to the chassis (for a heat sink) is rated at 4.0 watts at 25°C derated 0.1 watt/°C or 1.0 watt at 55°C. Moreover, the transistor will be forced-air cooled which will further increase its capacity.

## ZERO OUTPUT LEVEL

In order to get the output voltage down to low levels, it is necessary that the off current in the H=7's is a minimum. To accomplish this one must also reduce the off current in the 2N142 to a very low level. The positive and negative biasing arrangements involving external supplies and Rl and R2 achieve this result. By biasing the bases in the reverse direction for the off condition, one achieves leakage currents which are no more than a few times the grounded base  $I_{co}$  for the transistor. Measurements of the low value of output current run about 2.5 ma for a typical set of 2N57's (H=7's should be better since their 60 V. maximum  $I_{co}$  is one-half that for the 2N57). This will then give a 50 millivolt minimum output for a 20 ohm load.

# AMPLIFIER

The rest of the amplifier is designed with the object in mind of requiring about 5 microamperes from the standard to completely cut off the output transistors. The two input transistors are in series to provide

3. Sylvania Engineering Data Service. Advance Data on the 2N142 Feb. 8, 1956

double the voltage capability. The pair of 33 ohm bleeder resistors serve both to provide a bias for the voltage division in the input transistors and to keep the unregulated supply voltage down. Of course, with a negative standard (when the positive side of the supply is grounded) the two 4.7K resistors provide the voltage division for the input transistors (2N182's).

Page 6

#### PROTECTION

For economic reasons it is wise to protect this supply, in case of fan failure or excessive ambient temperature. If either of these conditions occurs the thermal switch will open and prevent operation of the H-7's above their rated junction temperature. In case of a current overload the fuse in the transformer primary will open. In either instance of failure, a neon light on the panel will flash, warning of the burn-out.

To provide the thermal protection, the thermal switch has been put at the warmest point of the chassis (under fan failure conditions) and set to switch off at  $55^{\circ}C$ .

## REVERSIBILITY

In order to reverse the polarity of the supply, relays are provided to change the location of the ground. This process runs into two problems: 1. The mercury relays, which are used for reliability, are of the make-before-break type, and sufficient interlocking must be provided to assure that the supply is not shorted while reversing. This is done by the circuit shown, provided the difference between the pull up or break time of two different contacts on the same relay is less than the pull up time of any contact on the relay. 2. The input for the standard must be such as to allow for either a positive or negative standard to be grounded. There was no simple way found for accomplishing this type of input, so two separate inputs were provided for the two standards. These inputs must then be switched when the supply is reversed.

# SYS TEMS

The control of the supply from the system point of view will be discussed more fully in the notes on the decoder and total system. How-

ever, it might be well to mention the speed of response here as a supply characteristic. The design set forth above has not yet been tested under various load conditions: however, the prototype supply was modified by reduction of capacities which brought the response to changes in the standard voltage to well below 1 millisecond. The only other important response time of the supply is the time required to switch polarities. In switching from plus to minus (and in returning to plus), at least two relay times will be used up. For the mercury relays used this will require 20 to 30 milliseconds. Fortunately, this switching is done much less often than the voltage switching.

# LIMITATIONS

As mentioned before, the supply load must be kept to 15 percent less than the load presented by 10 ohms. Thus, the rated load is 12 ohms. Moreover, a maximum load of 100 ohms is specified to allow the supply to go to 1/4 volt. Any higher resistance loads must be padded. In addition, no negative current can be supplied, that is, no current can be supplied in a direction opposite to the voltage. This is a basic characteristic of supplies using unilateral series regulators. The ambient temperature of the supply must be kept below  $55^{\circ}$ C. The resistance of the standard should be high enough to limit the surge currents resulting from sudden change of voltage. A resistance of 5K is sufficient for this purpose and will cause no appreciable error in the standard voltage under load.

# SUGGESTIONS FOR FURTHER WORK

Consideration might be given to the following as improvements or tests to be made on the above design: 1. Thorough tests of regulation under load, operation of the thermal switch, response under various conditions of load, and accuracy of output for given standard characteristics, 2. Replacement of the single 2N142 by a series pair of 2N142's to provide sufficient voltage rating. 3. Physical layout of the supply, including location of various associated devices such as the variable standard and the switching circuitry.

E.U. Cohler / RW Hidson

EUC:bac Attachments:

Fig. 1 - 15 volt 1 amp power supply Mod I TE Drawing #C63605

Fig. 2 - Electronically variable power supply Dwq. #C67152

Fig. 3 - Output vs. Input, electronically variable power supply. (Unregulated Supply) Dwg. #A67151

C-67152

ELECTRONICALLY VARIABLE POWER SUPPLY

FIG. 3 OUTPUT VS INPUT ELECTRONICALLY VARIABLE POWER SUPPLY (UNREGULATED SUPPLY)

A-67151

K. H. alsen

.

Page 1 of 4

# Division 6 – Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

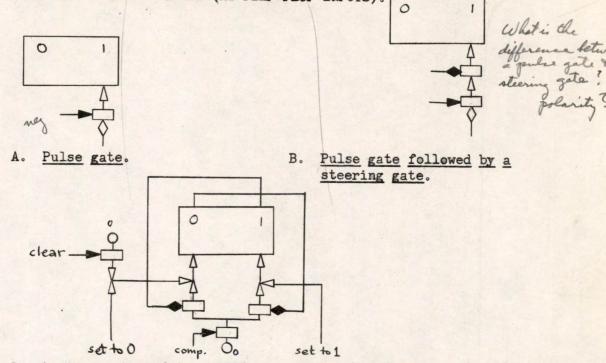

SUBJECT: A PRINTED WIRE MEMORY PLANE

| To:       | W. N. Papian       |

|-----------|--------------------|

| From:     | E. A. Guditz       |

| Date:     | September 10, 1956 |

| Approved: | J. E. Mitchell     |

|           | y L. Mitchell      |

Abstract: A  $\downarrow$  x  $\downarrow$  memory plane, made entirely with printed wiring, has been constructed and successfully operated. It demonstrates the techniques for making larger units which are the electrical equivalent of hand-sewn memory planes. The practical limit in size for planes made by this method is not yet known.

This document is issued for internal distribution and use only by and for Lincoln Laboratory personnel. It should not be given or shown to any other individuals or groups without express authorization. It may not be reproduced in whole or in part without permission in writing from Lincoln Laboratory. The research reported in this document was supported joinly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No. AF 19(122)-458.

# Introduction:

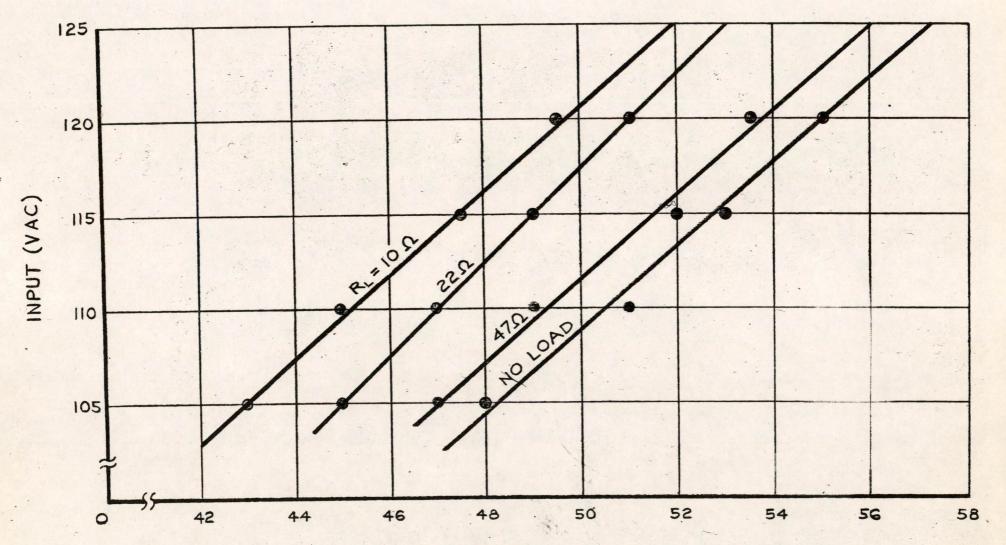

Memory planes constructed to date comprise cores and wires sewn in various configurations and strung in a suitable frame. Such planes are highly satisfactory from an operational point of view, but present some undesirable problems in fabrication. Not the least of these is the need for highly-skilled workers to sew the conductors through the cores. The object of the work reported here was to produce a plane which contained no hand-sewn wires. This was successfully accomplished in the form of a small  $\mu \ge \mu$  plane with 16 cores, four windings linking each core, and 128 dip-soldered connections. Two such planes have been made to date, and two more are being constructed. The nature of this experimental plane can best be understood by referring to the accompanying drawings and photographs while reading the text.

#### The Assembly:

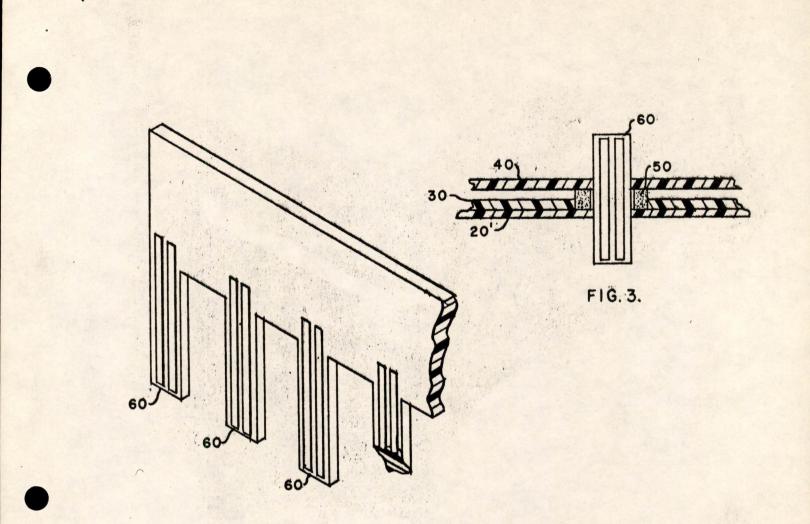

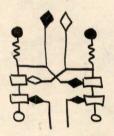

Figure 1 is an exploded view of a segment of a printed plane of this type. Sheets 20 and 40 formed of phenolic have printed wiring on their outer surfaces. Sheet 30 serves as a spacer layer for positioning the cores. Base 10 with posts 11 serves as a jig to properly orient the sheets during the assembly operations.

The steps in construction are as follows:

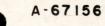

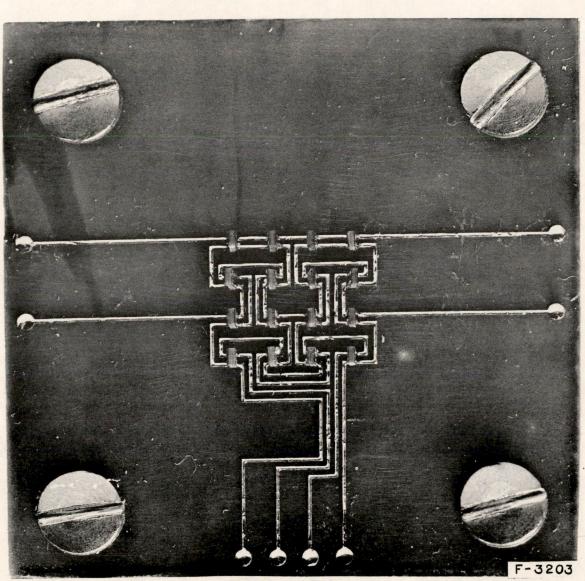

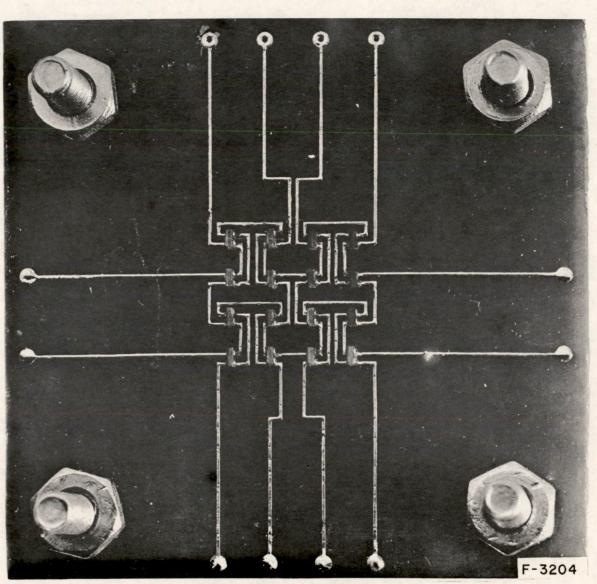

Sheet 20 with the printed wiring facing down is placed upon base 10. Then sheet 30 is placed over sheet 20. Next, cores 50 are positioned in the holes of sheet 30. This may be done by automatically vibrating the cores into position. A surplus of cores may be applied with the excess being brushed off after all of the holes have been automatically filled. Next, sheet 40 is applied with the printed wiring facing up. At this point, the cores are sandwiched between the two sheets containing printed wiring, and the pegs 60 forming the circuit connections between the two layers of printed planes are now inserted. If desired the pegs may be attached to a strip in comb-like fashion as shown in Figure 4 so that the pegs for an entire line of cores may be inserted at once. The completed assembly may now be removed from base 10 and dip soldered on both sides to make permanent connections. The solder forms fillets at the junctions between conducting lines on the pegs and printed wire lines. These are shown in the photograph, F-3248.

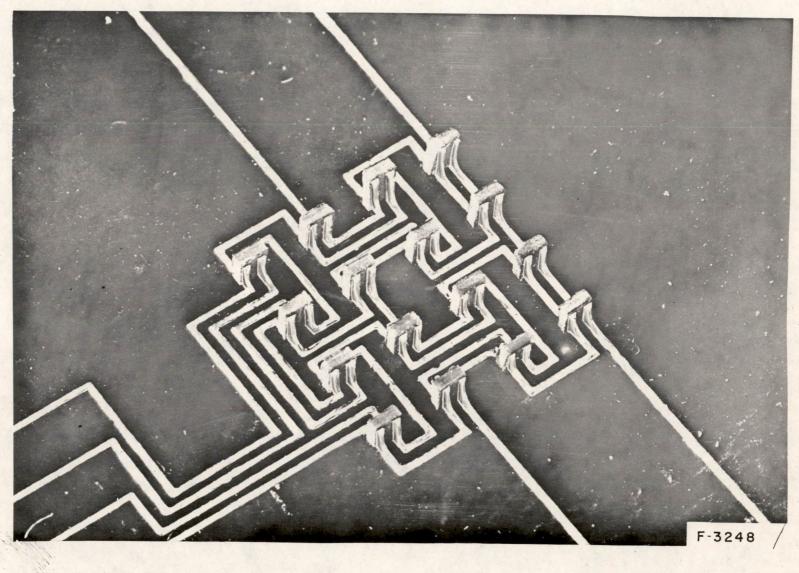

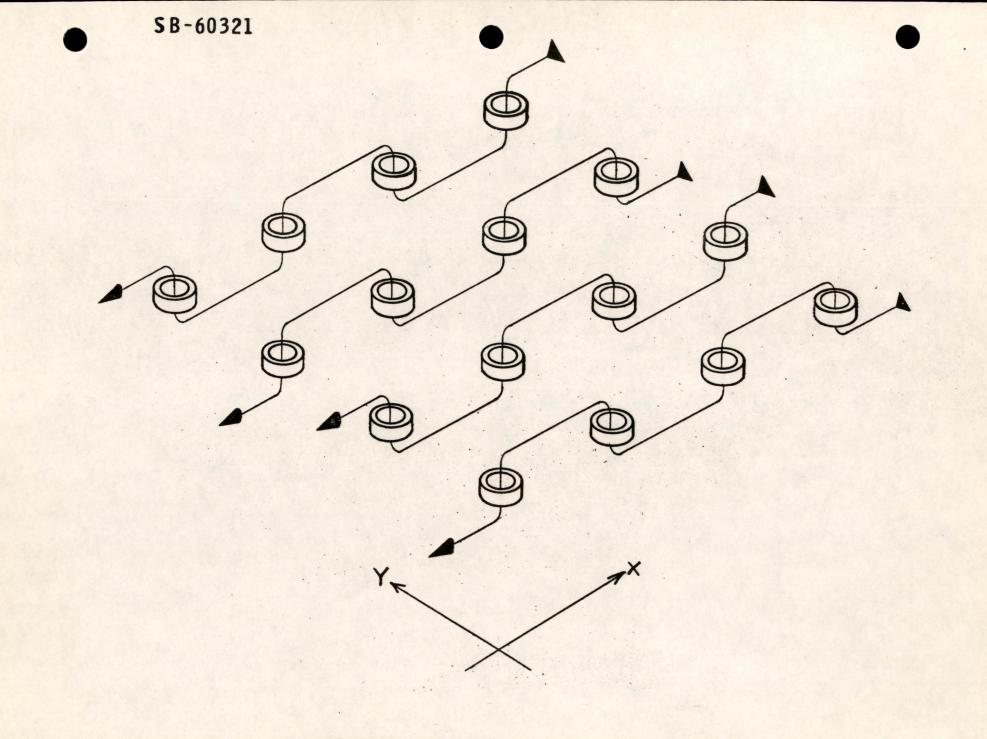

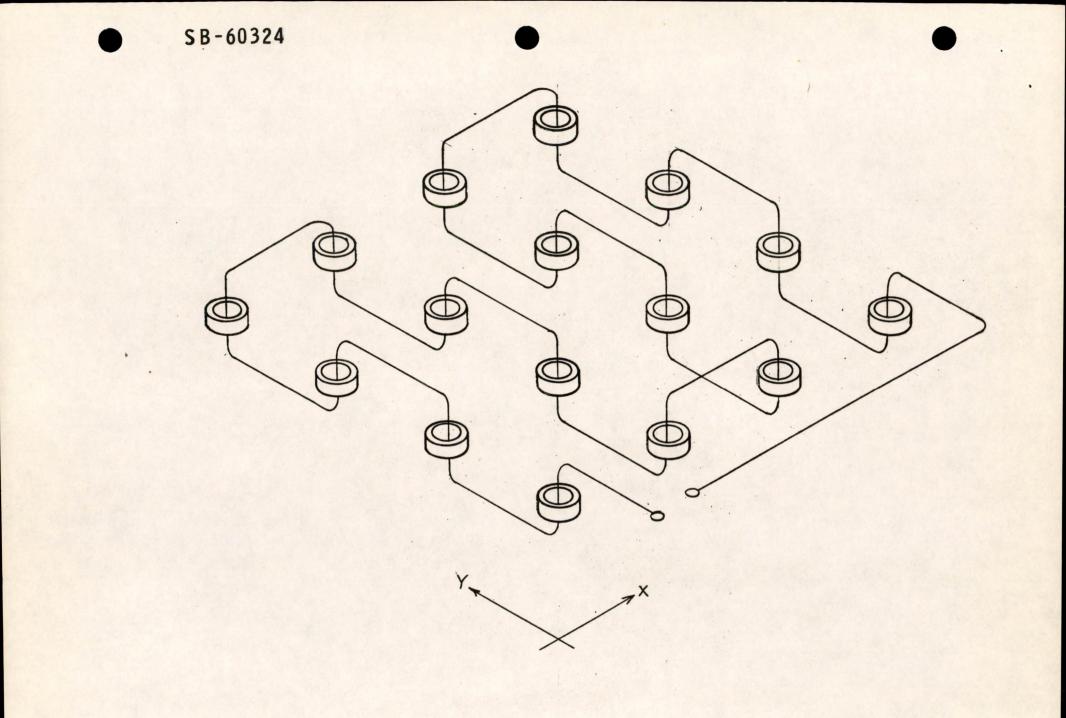

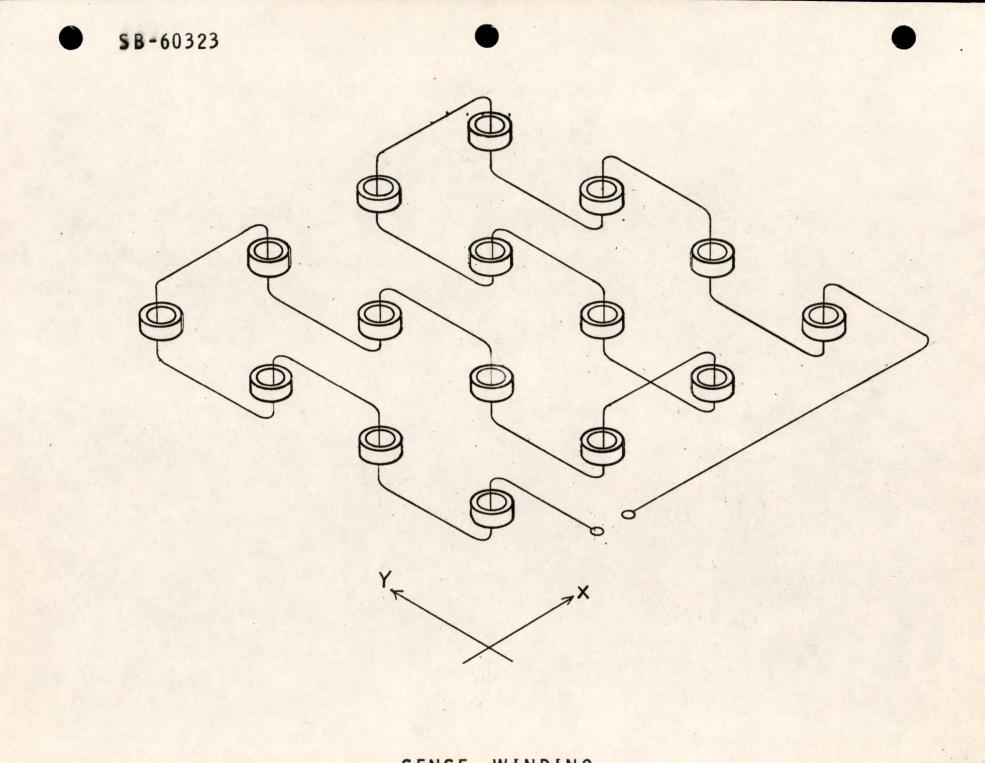

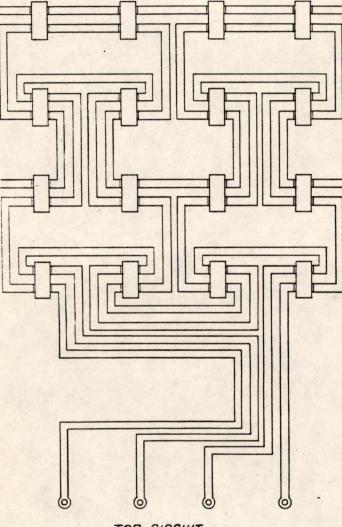

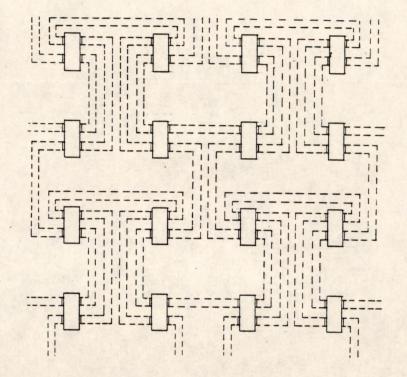

The detailed paths of the x, y digit and sense windings are shown in the accompanying drawings SB-60322, SB-60321, SB-60324, and SB-60323 respectively. Actual conducting paths for all windings are shown in SC-60365 and in photographs F-3203 and F-3204.

These conducting circuit paths may best be understood by continued reference to Figure 1. The wiring circuit for a row or "x" line will be considered first. Line 1 on sheet 20 connects with line 1B on peg 60. This conducting line goes through core 50 and connects with line 1C on sheet 40. Line 1C connects with line 1D on peg 60B. Line 1D goes through core 50B and connects with line 1E on

sheet 20. This conducting path continues on in a similar fashion for the rest of the row.

To illustrate a "Y" line, or a column circuit, line 2 on sheet 20 connects with line 2B on peg 60. Line 2B goes through core 50 and connects with line 2C on sheet 40. Line 2C connects with line 2D on peg 60C. Line 2D goes through core 50C and connects with line 2E on sheet 20. Line 2 continues on in a similar fashion for the rest of the column. It will be noted that while the initial appearance of the printed wire sandwich is different from that of the conventionally wired memory, the effective electrical paths for the rows and columns are identical with those obtained by threading wires through the rows and columns of a conventional memory. The remaining printed circuits may be traced out in a manner analogous to that used for the row and column circuits. These are the sense winding starting at line 3 and the inhibit winding starting at line 4, and are the overall electrical equivalent of those windings in a conventionally constructed memory.

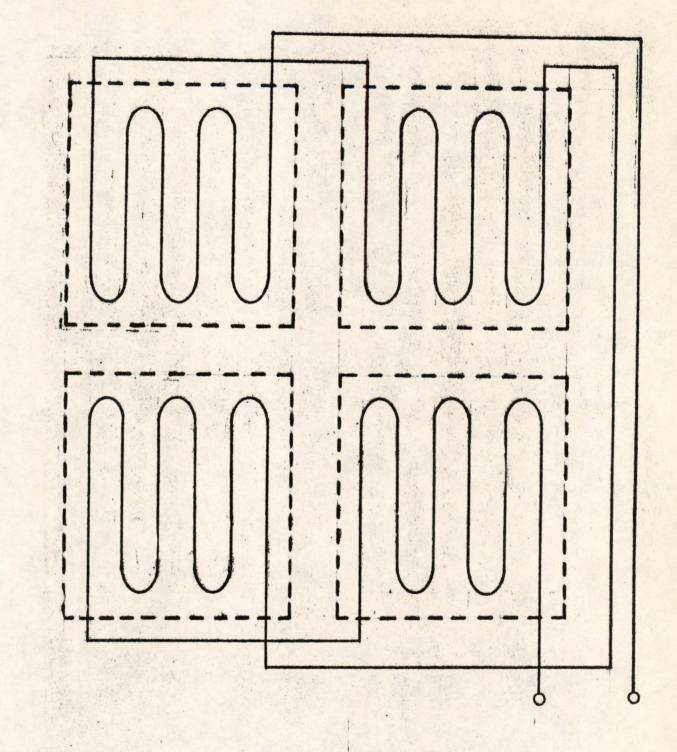

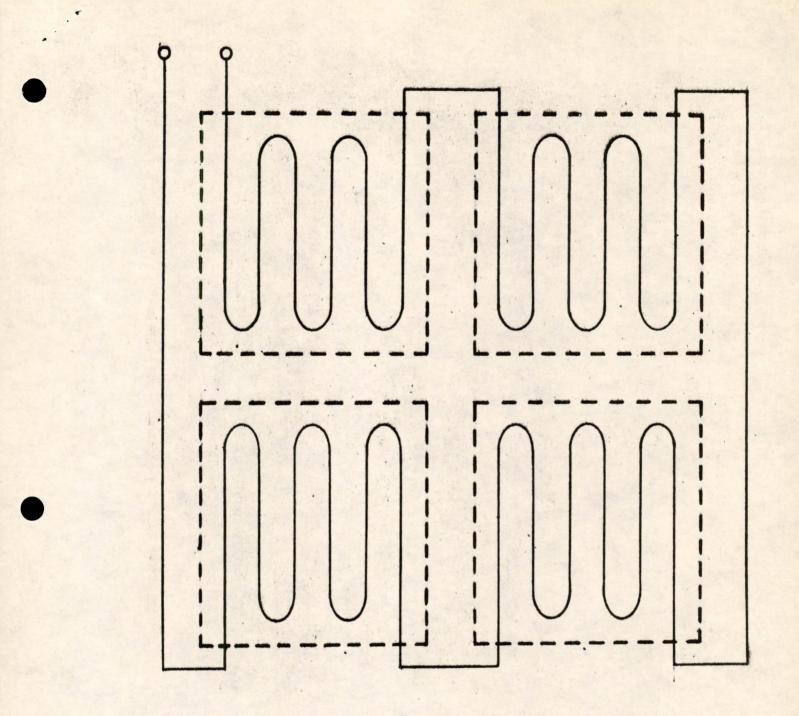

However, since it is difficult if not impossible to achieve a diagonally wired sense winding with this type of printed wire layout. the sense winding is rectangular in format. The cancellation of pulses from half-selected cores and air flux pickup normally accomplished by the diagonal format of the sense winding in conventionally wired memory planes is achieved by appropriate interconnection of rectangular subsections of the printed wire plane. Thus if two appropriately chosen quadrants are connected in one polarity and the other two quadrants in the opposite polarity, any row or column will have onehalf of its cores sensed in one polarity and one-half sensed in the opposite polarity, and also cancellation of air flux pickup will be effected. The interconnection of these quadrants is shown in Figure 5. For convenience in wiring layout, the digit winding is also printed in quadrants as is shown in Figure 6. Figure 3 shows how sheet 30 is made thinner than the memory cores to permit cooling the plane by passing air through it sideways.

The core density for this type of construction is the same as for planes in the MTC and TX-O memories. This design does, however, reduce the thickness of the memory plane. The major obstacle to be overcome in making larger planes of this type is control of the dipsoldering operation. Even in the 4 x 4 size the operator technique is very important. If larger numbers of junctions can be simultaneously soldered, then this could be a practical way to make a printed plane.

The first plane of this type to be completed has been operated in Memory Test Setup VI. It has output waveforms and operating margins comparable to conventional hand-wired memory planes.

E. A. Guestz

EAG:jd Attachments: B-67164 SB-60323

A-67156 A-66029 SC-60365 A-67077

SB-60322 SB-60321 A-67157 A-67074

SB-60324 A-67075

Page 4

# DISTRIBUTION LIST

Group 63 Staff

Division 2

F. L. McNamara

# Division 7

L. L. Grant M. M. Hannoosh E. B. Murphy H. C. Nichols K. L. Zapf

ALL PERSONS LISTED ABOVE ARE TO RECEIVE COMPLETE MEMO.

FIG. 4

PRINTED PLANE COMB CONNECTOR

Ser.

4 X 4 PRINTED MEMORY PLANE SHOWING SOLDER FILLETS

X COORDINATE DRIVING WIRES

Y COORDINATE DRIVING WIRES

DIGIT PLANE WINDING

SENSE WINDING

TOP CIRCUIT

BOTTOM CIRCUIT AS SEEN FROM TOP

TOP VIEW, 4 X 4 PEG-TYPE PRINTED MEMORY PLANE (FIRST WORKING MODEL)

A-67077

BOTTOM VIEW, 4 X 4 PEG-TYPE PRINTED MEMORY PLANE (FIRST WORKING MODEL)

A-67157

FIG. 5 QUADRANT SENSE WINDING FOR PRINTED MEMORY PLANE

FIG. 6 QUADRANT DIGIT WINDING FOR PRINTED MEMORY PLANE

R. Best Jup 63 B063

Memorandum 6M-4581-S-1

of 13 Sheets Sheet 1

Division 6 — Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SOME NOTES ON THE THEORY AND DESIGN OF ALLOY JUNCTION SUBJECT: TRANSISTORS FOR SWITCHING PURPOSES - PART IIIT

| 10:       | Donald J. Eckl   |                    |

|-----------|------------------|--------------------|

| From:     | Charles T. Kirk, | Jr. Chale J. Jurg. |

| Date:     | August 21, 1957  |                    |

| Approved: | D.J.E .          |                    |

Abstract: In Parts I and II of this paper, some equations relating to the design of switching transistors were obtained, based on Ebers' and Moll's approximate analysis of the transient behavior of a junction transistor, for the assumption that the effective minority carrier lifetime in the base region is independent of the mode of operation. In Part III, experimental evidence to the contrary is discussed and a more detailed analysis of the Ebers and Moll switching theory is made showing that indeed the effective base lifetime is a function of the mode of operation of the transistor. As a result of this, corrections are made in the set of transform equations originally obtained in Part I as equation set (29). The effects of these corrections on the design equations are discussed in Part IV of this paper.

CTK/md

Distribution List:

| Baker, R.      | Group | 24 |          |    |

|----------------|-------|----|----------|----|

| Barck, P.      | Group | 63 |          |    |

| Best, R.       | 88    | -  |          |    |

| Corderman, C.  | 99    | 99 |          |    |

| Davidson, G.   | 88    | 88 |          |    |

| Eckl, D. J.    | **    | 99 |          |    |

| Fergus, P.     | 99    | -  |          |    |

| Goodenough, J. | **    | =  |          |    |

| Johnston, R.   | 88    | 11 |          |    |

| Kirk, C.       | Ħ     | ** |          |    |

| Konkle, K.     | 11    | -  |          |    |

| Olsen, K.      | **    | -  |          |    |

| Papian, W.     | 81    | -  |          |    |

| Group 63       | Staff | in | Building | 10 |

Group 35 Rediker, R. 99 Sawyer, D.

& Parts I and II of this paper have been published as Division 6 Lincoln Laboratory Memorandum 6M-4581.

1. This document has been prepared for internal use only. It has not been reviewed by Office of Security Review, Department of Defense, and therefore, is not intended for public release. Further dissemination or reproduction in whole or in part of the material within this document shall not be made without the express written approval of Lincoln Laboratory (Publications Office).

2. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No., AF 19 (122)-458.

#### 6M-4581 S-1 1

#### PART III

A REVIEW OF FIRST-ORDER SWITCHING THEORY FOR P-N JUNCTION TRANSISTORS Introduction

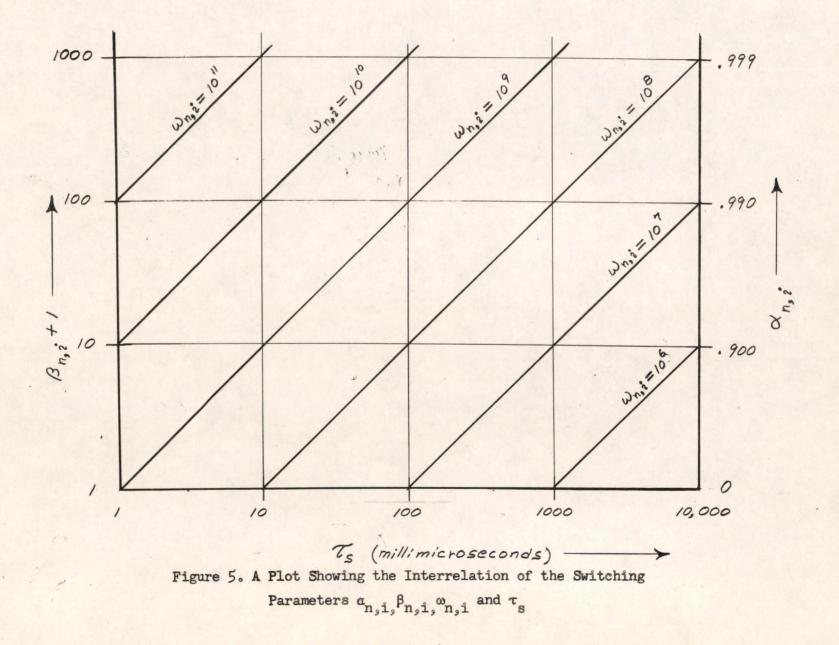

In Part II of this paper, we found that the principal switching parameters of a transistor,  $\beta_n$ ,  $\beta_1$ ,  $\omega_n$ ,  $\omega_1$ , and  $\tau_s$ , could be related by an equation of the form

$$(\beta_n + 1) = \omega_n \tau_s \tag{50}$$

$$(\beta_{i}^{*}) = \omega_{i}\tau_{s}$$

(51)

Konkle<sup> $\perp$ </sup> has shown that (51) agrees quite well with experimental data obtained from a group of L=5122 surface-barrier transistors with the exception that values of  $\tau_s$  calculated from (51) were 10 to 20 percent higher than the measured value. No such agreement, however, could be found for (50).

Now (50) and (51) are derived from the valid relationships

$$(\beta_{n_{j}i} + 1) = \omega_{n_{j}i} \tau_{n_{j}i}$$

(52)

and

$\tau_{\rm s} \approx \tau_{\rm b}$  (to a first-order approximation) (53)

where  $\tau_{n^9} \tau_{i^9}$  and  $\tau_{b}$  are various effective minority carrier lifetimes in the base region<sub>9</sub> such that, by identifying  $\tau_{n^9} \tau_{i}$  with  $\tau_{b^9}$  we arrive at (50) and (51) and the resultant dilemma between theory and experiment.

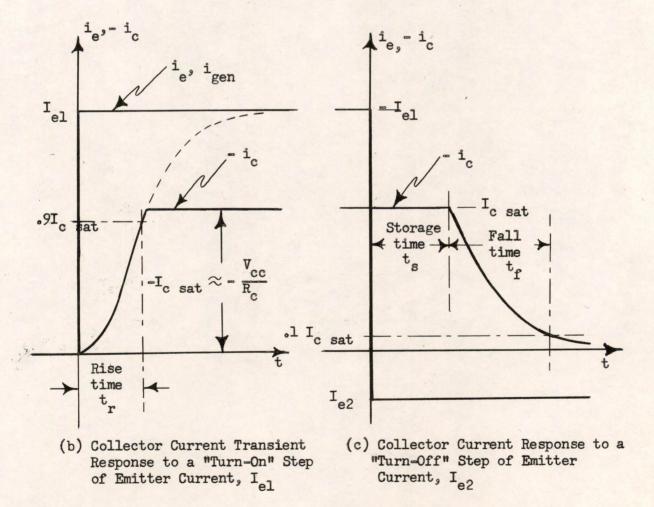

In assuming that  $\tau_n$  and  $\tau_i$  are identical to  $\tau_b$ , we have neglected to consider that these lifetimes are each defined under different transistor operating conditions. Consider the lifetimes  $\tau_n$  and  $\tau_i$ .  $\tau_n$  is the effective base lifetime defined for the normal mode of active region operation of the transistor. Under this operating condition, the minority carrier density in the base varies from a maximum at the emitter junction boundary to zero at the collector junction boundary. Similarly,  $\tau_i$  is the effective base lifetime defined for the inverted mode of active region transistor operation in which case the minority carrier density varies

<sup>1.</sup> K. Konkle, "Hole Storage in a Saturated Grounded-Emitter Transistor Circuit", M.I.T., Department of Electrical Engineering, Master's Thesis, Submitted in January, 1957.

1

1

from zero at the emitter junction boundary to a maximum at the collector junction boundary.  $\tau_{b}$ , on the other hand is the effective base lifetime defined for the saturation condition of the transistor in which the minority carrier density is more or less distributed uniformly through the base region.

In Part I of this paper, the effective base lifetime,  $\tau_b$ , was assumed to be approximately of the form

$\frac{1}{\tau_{b}} = \frac{1}{\tau_{p}} * \frac{2s}{w}$ (54) where  $\tau_{p}$  is the bulk lifetime s is the surface recombination velocity w is the width of the material.

This relation is derived for a uniform hole density distribution, and, consequently, neglects any effects on the effective base lifetime due to a non-uniform spacial distribution of the minority carrier density. Thus, the effective base lifetime as defined by this relation is seen to be symmetrical with respect to the mode of operation and independent of the region of operation. As a result of this interpretation of (54), we are led to assume that  $\tau_n$  and  $\tau_i$  must be identical with  $\tau_b$  and hence with  $\tau_s$ . If, however, a non-uniform spacial distribution of the minority carrier density does affect the value of the effective base lifetime (as is indeed indicated by the experimental evidence) then we must regard (54) as a zero-order approximation to the actual effective base lifetime for any given spacial distribution of the minority carriers. To a firstorder approximation, therefore, we require that in general

$\tau_{n} \neq \tau_{i} \neq \tau_{b} \approx \tau_{s} \tag{55}$

In this part of the paper, we shall show that (55), which is required to hold in view of the experimental evidence, is consistent with the first order switching theory of Ebers and Moll.<sup>4</sup> As we shall show in Part IV of this paper, the distinction we have made among the various minority carrier lifetimes in the base region of a transistor leads to a

\* Ebers, J.J. and Moll, J.L., Op. Cif.

set of design equations relating the electrical switching characteristics to the physical and geometrical design parameters of the transistor which are in agreement with the experimental evidence. In particular, we shall be able to show theoretically why (51) agrees so well with experimental data while (50) does not.

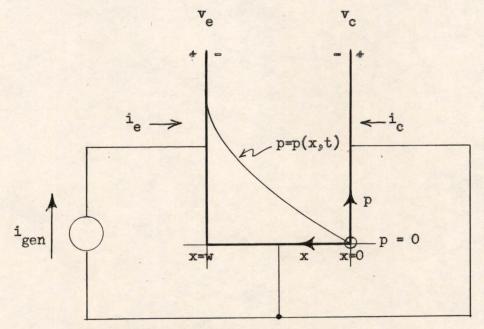

#### 2.0 Some Remarks Concerning the Solution to the Transient Response of an Alloy Junction Transistor

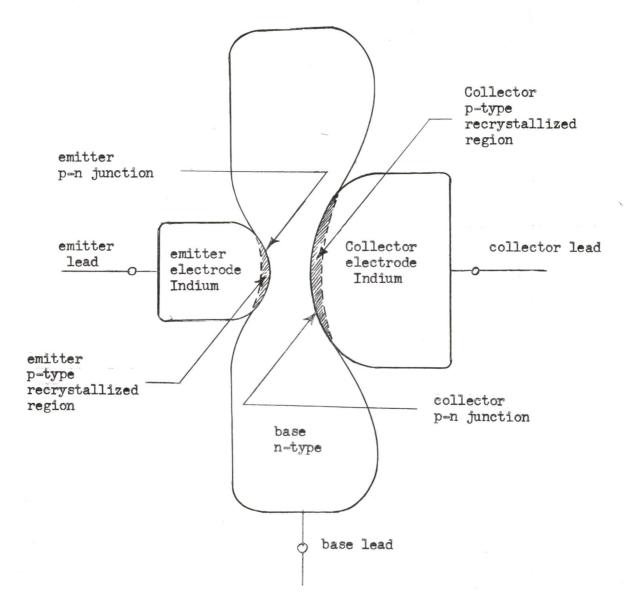

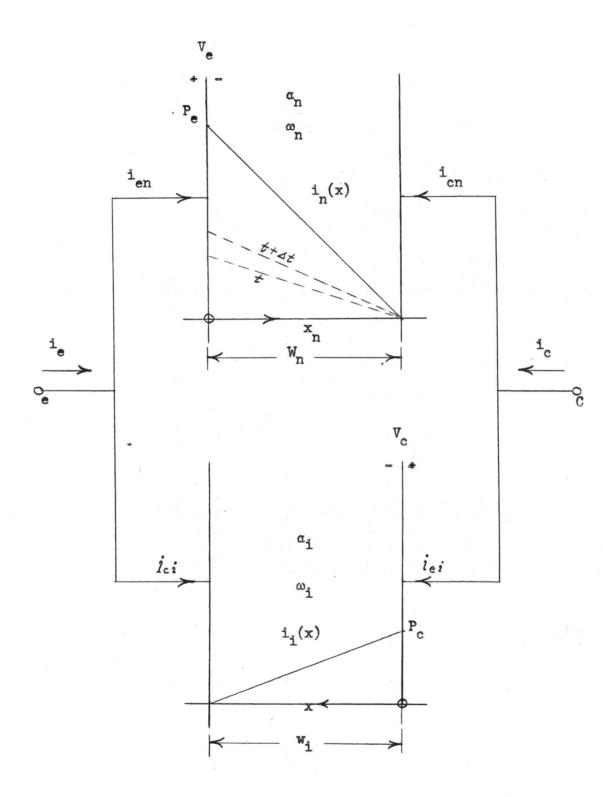

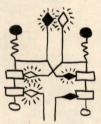

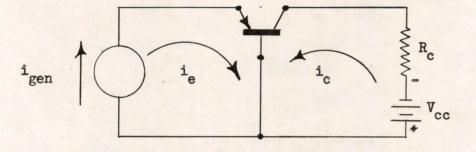

In order to see more clearly the material presented in the remaining parts of the paper, it is worthwhile to consider in some detail the general approach to the analytical solution for the transient response of an alloy junction transistor. Given an alloy junction transistor of arbitrary geometry, a typical case of which is shown in Figure 7, we desire the analytical solution to the transient response of the output current, usually the collector current,  $i_c$ , for a specified input driving current, which can either be the emitter current  $i_e$  or the base current  $i_b$ , depending on the configuration in which the transistor is operated.

The direct approach to this problem is to solve the timedependent diffusion equation of the form

$$D_{p} \nabla^{2} p - \frac{p}{\tau_{p}} = \frac{\partial p}{\partial \tau}$$

(56)

where  $p = p(x_yy_yz_yt)_y$  is the excess minority carrier density distribution in the base region

$\tau_{p}$  is the bulk lifetime of the minority carriers in the base region

D is the diffusion constant for the minority carriers.

for p as a function of position in the base region and time subject to the boundary conditions:

$= D_{p} \overrightarrow{\nabla p} \cdot \overrightarrow{dS} = s p ds \text{ (at the free base surfaces) (57)}$   $i_{p} = -q \int D_{p} \overrightarrow{\nabla p} \cdot \overrightarrow{dS} \text{ at the junction boundaries (58)}$ of the base region

6M-4581 S-1 4

¥

1

1

$p = p_{no} \left(e^{\frac{q}{kT}\phi} - 1\right)$  at the junction boundaries of (59) the base region

where s — is the surface recombination velocity of the minority carriers at the free base surfaces

S - refers to the base surface

ip is the total minority carrier current at a junction boundary

q - is the electronic charge

p\_is the equilibrium minority carrier density in the base region

d - is the voltage across a p-n junction and is

positive if the drop occurs in going from the

p-region to the n-region of the junction.

Once the solution for the excess minority carrier density in the base region is found, it is a simple matter to obtain the transient response of the collector current  $i_c(t)$  from the relation

$$\mathbf{i}_{c}(t) \approx \mathbf{i}_{p}(t) = -qD_{p} \int_{S_{c}} \nabla p \left| \begin{array}{c} \overline{\nabla p} \\ c \end{array} \right|_{collector} collector$$

(60)

where S is the surface of the base region at the collector junction boundary.

Except for special cases, however, involving simple geometric transistor structures, exact analytic solutions to the transient response of an alloy junction transistor are impossible or at least very difficult to obtain.

### 3.0 Ebers: and Moll's Approximate Solution for the Transient Response of an Alloy Junction Transistor

A good approximation to the solution for the transient response of an alloy junction transistor with an arbitrary geometry can be obtained by a method based on a linear separation of solutions developed by Ebers and Moll.

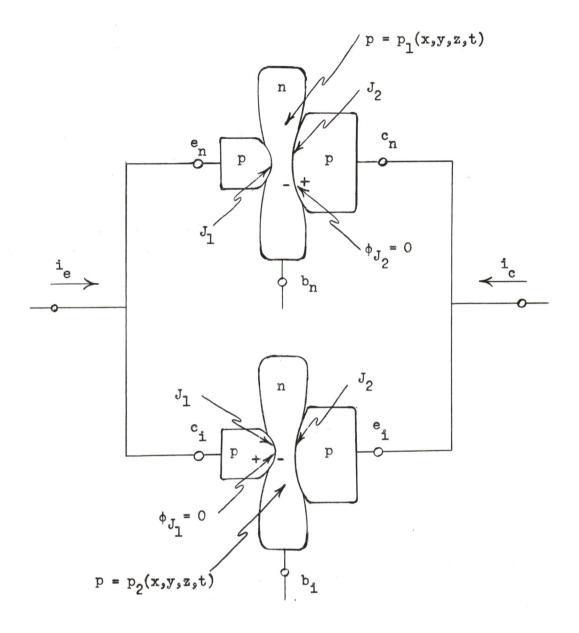

5

We notice that the diffusion equation (56) and the boundary conditions (57) and (58) are linear. Therefore, we can write the solution for  $p = p(x_yy_yz_t)$  as the sum of two independent excess minority carrier distributions,  $p_1 = p_1(x_yy_yz_t)$  and  $p_2 = p_2(x_yy_yz_t)$  provided that a linear combination of these two independent solutions also satisfies the boundary condition given by (59). In general (59) is nonlinear and any linear combination of two arbitrary independent solutions will not satisfy this boundary condition. However, if we choose the solutions to be of the form

$$p_{1} = p_{no} \begin{bmatrix} \frac{2}{kT} \phi_{e}(t) \\ e^{kT} \phi_{e}(t) \\ = 1 \end{bmatrix} f(x_{9}y_{9}z_{9}t)$$

(61)

where  $f(x_{9}y_{9}z_{9}t) = \begin{cases} 1 \text{ at the emitter junction} \\ \text{boundary} \\ 0 \text{ at the collector junction} \\ \text{boundary} \end{cases}$

and  $p_{2} = p_{no} \begin{bmatrix} \frac{2}{kT} \phi_{c}(t) \\ e^{kT} \phi_{c}(t) \\ = 1 \end{bmatrix} g(x_{9}y_{9}z_{9}t)$ (62)

where  $g(x_{9}y_{9}z_{9}t) = \begin{cases} 0 \text{ at the emitter junction} \\ \text{boundary} \\ 1 \text{ at the collector junction} \\ \text{boundary} \end{cases}$

and note that (59) is linear if and only if all the independent solutions except one are zero at a junction boundary, then the linear combination of  $p_1$  and  $p_2$  as given by (61) and (62), respectively, of the form

$p = p_1 * p_2$  (63)

is also a solution.

If we now define, p, in (63) to be the complete solution for the excess minority carrier density distribution, then we can represent the separation of p into the two independent solutions,  $p_1$  and  $p_2$ , as defined by (61), (62), and (63), schematically as shown in Figure 8. This schematic representation of an alloy junction transistor with an arbitrary geometry consists of two identical transistors of the same geometrical structure as the original transistor with their emitter, base, and collector leads each paired together to form single emitter, base,

.

.

.

.

Figure 8

and collector leads which are identical to the corresponding leads of the original transistor shown in Figure 7. Arbitrarily, the top transistor is designated to have an excess minority carrier distribution solution of the form,  $p_1$ , and the bottom transistor a solution of the form,  $p_2$ . Later on, we shall show that an alloy junction transistor having an excess minority carrier distribution of the form,  $p_1$  or  $p_2$ , can be transformed into an ideal one-dimensional junction transistor structure for which the transient response is known in analytical form. First, however, we shall indicate how the schematic representation of the alloy junction is derived by considering the physical significance of breaking down the complete solution for the excess minority carrier density into two independent solutions in the manner described above by  $(61)_9(62)$  and  $(63)_0$ .

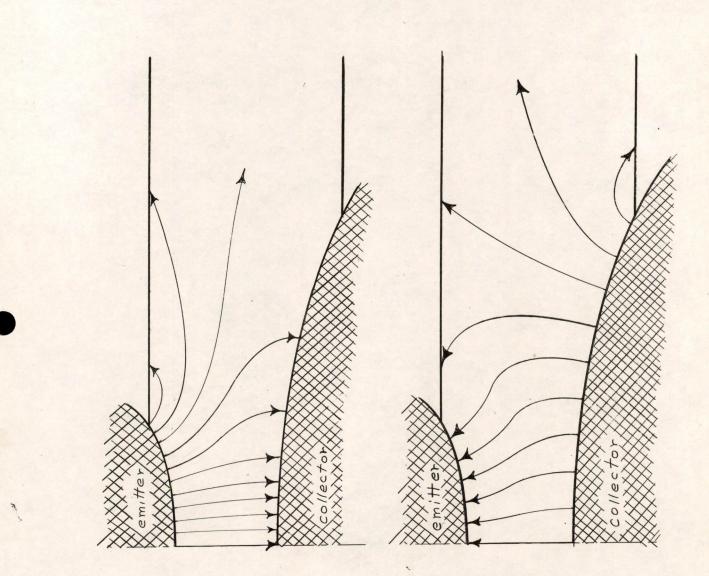

The derivation of the schematic representation of an alloy junction transistor shown in Figure 8 is analogous to the derivation of a similar schematic representation for the one dimensional form of a p=n junction transistor. Therefore, for simplicity and convenience, we shall consider this derivation in terms of the one-dimensional case.

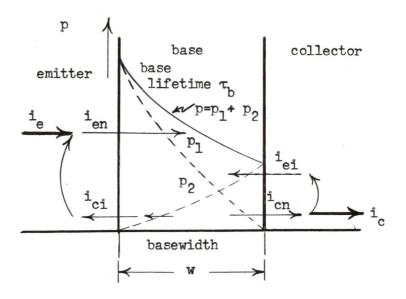

Figure 9(a) shows a one-dimensional step junction transistor in which p = p(x,t). The excess minority carrier density distribution in the base region for some time,t, (solid line) is separated into two independent solutions,  $p_1$  and  $p_2$ , (broken lines) as defined by (61) and (62). Now the gradient of pl is such that it represents a minority carrier diffusion current in the direction of the collector. Since  $p_1$  is by definition zero at the collector junction boundary of the base region at all times, the gradient of pl at the collector junction boundary represents a minority carrier current, i cn, into the collector that is independent of the collector voltage. In the collector region of the transistor this minority carrier current splits into two components. One component is the true collector current, ic. The second component, iei' which is equal to the difference between  $i_{cn}$  and  $i_{c}$  is reinjected into the base region through the collector junction giving rise to the excess minority carrier density distribution, p2. The gradient of p2 shows that the reinjected current is a diffusion current in the direction of the emitter. The resultant gradient of p2 at the emitter junction boundary of the base region represents a minority carrier current, i ci, into

ų,

.

.

-

Fig. 9 (a)

Figure 9(b)

the emitter. By definition,  $p_2$  is zero at the emitter junction boundary and therefore  $i_{ci}$  is independent of the emitter voltage. In the emitter region  $i_{ci}$  combines with the true emitter current  $i_e$  to yield a current  $i_{en}$  which is injected into the base region through the emitter junction. The injection of  $i_{en}$  gives rise to the excess minority carrier distribution,  $p_1$ , which we assumed to exist at the beginning of this discussion.

Now, since the two excess minority carrier density distributions,  $\mathbf{p}_{1}$  and  $\mathbf{p}_{2^{9}}$  are independent of each other, the only interaction that occurs as a result of separating, p, the complete solution for the excess hole density distribution, into  $p_1$  and  $p_2$  is a Kirchoff's summation of the various currents in the emitter and collector regions. Thus the problem can be treated in the completely equivalent form shown in Figure 9(b). This equivalent form of the problem is obtained by replacing the onedimensional transistor having an excess minority carrier density distribution of the form p = p (x,t) in Figure 9(a) by two, one-dimensional transistors both of which are identical to the original one-dimensional transistor. The pairs of emitters, bases and collectors are each connected together as shown in Figure 9(b). The leads common to the emitters, bases and collectors of the two transistors correspond to the actual emitter base and collector electrodes of the original transistor shown in Figure 9(a). In a similar manner, the schematic representation of an alloy junction transistor by two transistors with the same geometry as the original and excess minority carrier distributions of the form of (61) and (62) can be obtained.

A transistor having a minority carrier distribution of the form of (61) or (62) in which  $P_c = 0$  at all times in the case of (61) (or  $P_e = 0$ at all times in the case of (62)) is by definition operating in its active region. In order to distinguish as to whether  $p_e(\text{or } p_c)$  is zero in a particular case, we have designated the case in which  $P_c = 0$  as the "normal mode" of operation in the active region and the case in which  $p_e = 0$  as the "inverted mode" of operation in the active region. Thus, we see that by making a linear separation of the excess minority carrier density distribution into distributions of the forms (61) and (62) we now need only to obtain the transient solution for the transistor operating in the active region in order to determine the transient behavior of the transistor under any arbitrary operating conditions.

Having discussed the derivation and physical significance of the schematic representation of an alloy junction transistor shown in Figure 8, we shall next consider the problem of showing that an alloy junction transistor with an excess minority carrier density distribution of the form of (61) or (62), e.i., operating in the active region, can be transformed into an ideal, one-dimensional, junction transistor structure. Once this is done, we can transform the schematic representation of an alloy junction transistor into a one-dimensional form for which an analytical solution to the transient response can be obtained.

# 4.0 <u>Small-Signal Response of an Idealized One-Dimensional P-N</u> Junction <u>Transistor</u>

In order to obtain the equations for transforming an alloy junction transistor into an electrically equivalent, one-dimensional transistor, it is necessary to consider certain aspects of the active smallsignal behavior of an ideal one-dimensional transistor. The solution for the small-signal response of the one-dimensional idealized transistor was developed in Part I of this paper. In normalized form, we see from (12) (16) (18) and (19) that this response is given by the expression

$$\frac{\mathbf{i}_{\mathbf{c}}}{\mathbf{i}_{\mathbf{e}}} \stackrel{\Delta}{=} \alpha(\omega) \approx \frac{\alpha_{\mathbf{o}}}{\mathbf{i}_{\mathbf{f}} \mathbf{j} \frac{\omega}{\omega_{\mathbf{c}\alpha}}}$$

(64)

where

$$\alpha_{o} = \frac{1}{1 + \frac{w^{2}}{2D_{p}} \frac{1}{\tau_{p}}}$$

(65)

$\omega_{c\alpha} = \frac{2D_{p}}{w^{2}} + \frac{1}{\tau_{p}}$  (66)

The parameters  $\alpha_0$  and  $\omega_{c\alpha}$  appearing in (64) are defined as the common base d-c current-gain and cutoff-frequency, respectively, and are related to the base width, w, and the base bulk-lifetime,  $\tau_p$ , of the idealized one-dimensional transistor by (65) and (66).

<sup>&</sup>quot;Idealized" means here that the conductivity of the emitter and collector regions is extremely large compared to the base conductivity so that the emitter efficiency can be regarded as unity.

From linear circuit theory, we know that if the sinusoidal amplitude and phase characteristics of a device are known for all frequencies then the output response of the device can be determined for any arbitrary input function. This is the case for the idealized onedimensional transistor, since from (64) we can write

$$\left| \alpha \right| = \left| \frac{\mathbf{i}_{c}}{\mathbf{i}_{e}} \right| = \frac{\alpha_{o}}{\left[ 1 * \left( \frac{\omega}{\omega_{c\alpha}} \right)^{2} \right]^{1/2}}$$

(67)

$$\underline{/\hat{i}_{c}/\hat{i}_{e}} = \arctan\left(\frac{\omega}{\omega_{ca}}\right)$$

(68)

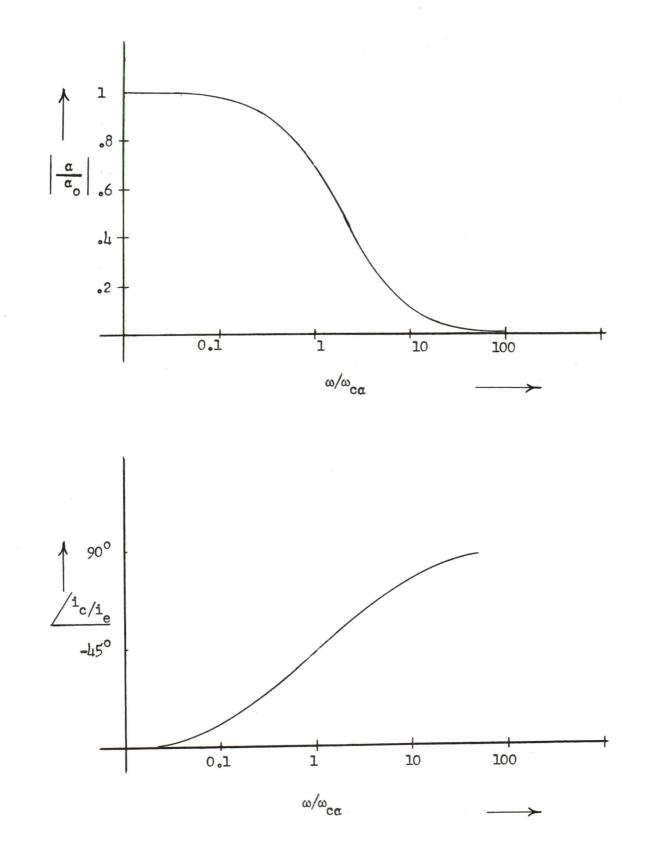

where (67) and (68) describe the amplitude response and phase characteristics, respectively of the idealized, one-dimensional transistor as a function of the drive frequency  $\omega$  and the parameters  $\alpha_0$  and  $\omega_{c\alpha}$ . Figure 10 shows a normalized plot of these amplitude and phase characteristics as a function of  $\omega/\omega_{c\alpha}$ .

From this brief discussion of the small-signal behavior of the idealized, one-dimensional transistor we see that when operating in the active region the output response of this device to any arbitrary input signal is completely characterized by the electrical parameters  $\omega_{ca}$  and  $a_{o}$  and, ultimately, through (65) and (66) by the base width w and the minority carrier lifetime,  $\tau_{p}$ .

## 5.0 Small-Signal Behavior of Alloy Junction Transistors

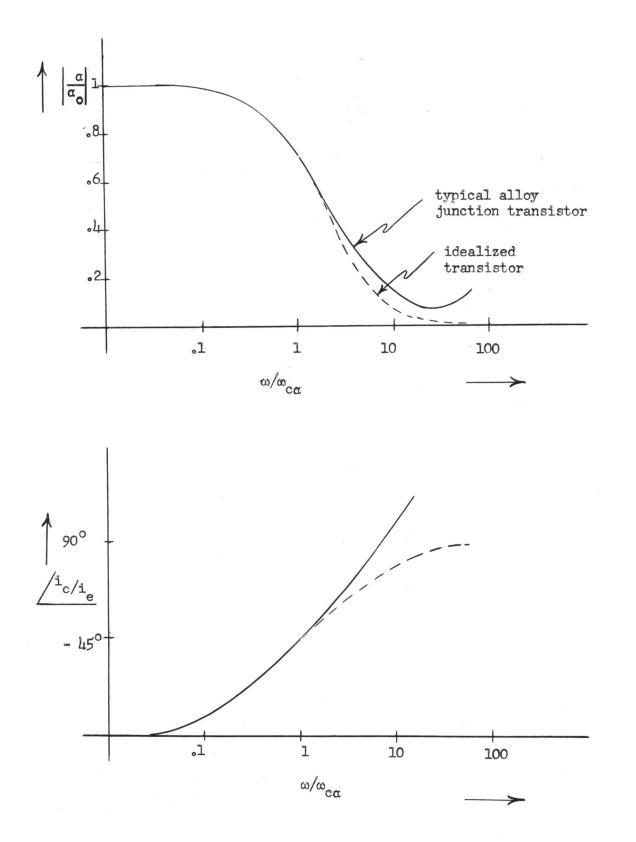

Figure 11 shows a typical normalized plot of the sinusoidal amplitude and phase characteristics of an alloy junction transistor (solid lines) in comparison with the normalized characteristics of the idealized one-dimensional transistor (dotted lines). We see from this Figure that the small-signal frequency characteristics of amplitude and phase approximates quite closely those of the idealized one-dimensional transistor from d-c out to three to five times  $\omega_{c\alpha}$ . It can be shown from linear circuit theory that the transient behavior of an alloy junction transistor with such small-signal characteristics is almost identical to the transient behavior of the idealized transistor except during the time

$$0 < t < \frac{1}{3\omega_{co}}$$

Figure 10

-

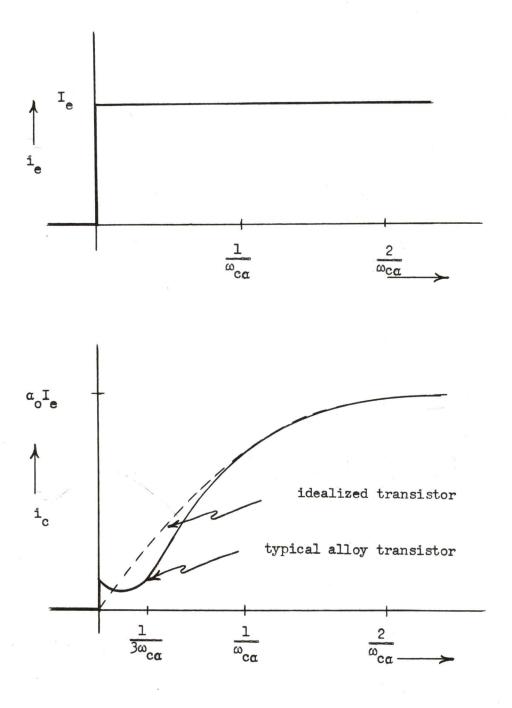

As an example of the veracity of this last statement we compare, in Figure 12, the collector current response of a typical, alloy junction transistor, and an equivalent, idealized, one-dimensional transistor for a step input of emitter current. We see from this Figure that for time  $t > 1/3\omega_{ca}$  the transient response for the alloy transistor is fairly well approximated by the response of the idealized transistor. While for  $t < 1/3\omega_{ca}$ , the transient response of the two devices differ considerably from one another owing to the differences in their high frequency (>3-5  $\omega_{ca}$ ) amplitude and phase characteristics.

Fortunately, in switching circuit applications, we are seldom if ever concerned with times much less than  $1/3\omega_{ca}$ . Consequently, it is possible, in the analysis of transistor switching circuits, to replace the alloy junction by an equivalent, idealized, one-dimensional transistor. The results obtained by this approximation are accurate to within  $1/3\omega_{ca}$ which turns out to be quite satisfactory in the analysis of a transistor's switching characteristic.

6.0 Continuation of Ebers' and Moll's Approximate Solution for the Transient Response of an Alloy Junction Transistor

Having shown that, to a good approximation, equivalence exists between the active region transient behavior of the alloy junction transistor and that of the idealized, one-dimensional transistor, we can now go on and complete our discussion of Ebers' and Moll's solution for the transient response of an alloy junction transistor.

Previously, we had found that the alloy junction transistor shown in Figure 7 could be replaced by the equivalent circuit shown in Figure 8 in which the alloy junction unit is replaced by two alloy junction transistors both identical to the original transistor but with each restricted to operating in the active-off regions only and interconnected as shown in Figure 8. As before, we shall arbitrarily consider the top transistor in this Figure to be operating in the normal-mode and the bottom transistor to be operating in the inverted-mode.

$<sup>\</sup>Psi$  By "equivalent", we mean that the dc current gain,  $\alpha_0$ , and the cutoff frequency  $\omega_{c\alpha}$  of the two devices are identical.

1

Figure 12

Now as we have just seen the transient behavior of each of these two transistors can be completely characterized by their dc current-gains and cutoff frequencies. These parameters can be obtained by direct measurement on the actual alloy junction transistor under consideration. The normal, common-base, dc, current-gain,  $a_n$ , and cutoff frequency,  $\omega_n$ , are obtained by making the appropriate measurements on the transistor while operating it in the active region under normal-mode conditions. The inverted, common-base, dc, current-gain,  $a_i$ , and cutoff frequency,  $\omega_i$ , are also obtained in a similar manner while operating the transistor in the active region under inverted-mode conditions. In general,

and

principly because of the differences in geometry and electrical characteristics of the two p-n junctions.

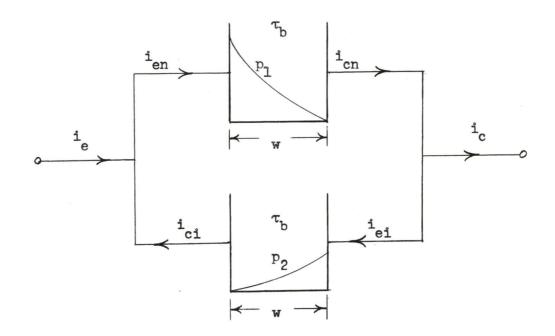

Having characterized the top transistor in Figure 8 by  $\alpha_n$  and  $\omega_n$ , and the bottom transistor by  $\alpha_1$  and  $\omega_1$ , we can replace each of these transistors by equivalent, idealized one-dimensional transistors, respectively. Thus, the equivalent circuit for an alloy junction transistor is now as shown in Figure 13. It is to be noted that the equivalent circuit of Figure 13 is only approximate and that the switching times to be derived from it shortly are accurate only to within  $1/3\omega_{ca}$  seconds.

A detailed analysis of the small-signal characteristics of the idealized one-dimensional transistor would show that the frequency response characteristics as given by (64) represent only a first order approximation to the actual expression<sup>4</sup>. Consequently, in order to obtain consistent results, the behavior of the minority carrier density distribution in the base region must be considered only to a first order approximation, e.i., the minority carrier density distribution is at all times a linear function of distance through the base region as shown in Figure 13 for times t and t  $* \Delta t$ .

Under these conditions, then, the current at the collector,  $i_c$ , and anywhere in the base region, i(x), of an idealized transistor is from (6) of the form

<sup>✤</sup> This is the principal reason why the transient response of an equivalent, idealized, one-dimensional transistor differs from the true response of an alloy junction transistor for t <1/30 ca°</p>

.

¥

6M-4581 S-1 19

$$i(x) = -i_c = -qD_p \frac{p}{w}$$

(69)

such that for the normal-mode case this equation becomes

$$i_{n}(x) = -i_{c_{n}} = -qD_{p} \frac{p_{e}}{w_{n}}$$

(70)

and for the inverted-mode case

$$i_{i}(x) = -i_{c_{i}} = -qD_{p} \frac{P_{c}}{W_{i}}$$

(71)

where the currents, minority carrier densities, and base widths are defined in Figure 13. Since,  $i_{(x)} = c$  everywhere in the base region, we can write that

$$\boldsymbol{a}_{n} \stackrel{\Delta}{=} \frac{\overset{-\mathbf{i}}{\mathbf{n}}_{n}}{\overset{\mathbf{i}}{\mathbf{n}}_{n}} = \frac{\overset{\mathbf{i}}{\mathbf{n}}(\mathbf{x})}{\overset{\mathbf{i}}{\mathbf{n}}_{n}} = \frac{\overset{\mathbf{i}}{\mathbf{n}}(\mathbf{w}_{n})}{\overset{\mathbf{i}}{\mathbf{n}}_{n}}$$

(72)

and

$$\alpha_{1} \stackrel{\Delta}{=} \frac{\stackrel{-i}{c_{1}} c_{1}}{\stackrel{i}{l}} = \frac{\stackrel{i}{l} (x)}{\stackrel{i}{l}} = \frac{\stackrel{i}{l} (w_{1})}{\stackrel{i}{l}}$$

(73)

and, thus,  $\alpha_n$  and  $\alpha_i$  are seen to behave as injection efficiencies in this analysis. Consequently, we can set the transport factor equal to unity and let

$\tau_p \longrightarrow \infty$  (74)

In the time domain, the behavior of the equivalent, idealized, one-dimensional transistors in Figure 13 is governed by the differential equations

$$qw_n \frac{dp_e}{dt} = \alpha_n i_{en} * i_{cn}$$

(75)

$$q w_{i} \frac{dp_{c}}{dt} = \alpha_{i} \dot{e}_{i} + \dot{e}_{ci}$$

(76)

where (75) refers to the one-dimensional equivalent of the alloy junction transistor operating in the normal mode and (76) refers to the onedimensional equivalent of the alloy junction transistor operating in the inverted mode. Eliminating  $p_e$  from (70) and (75) and  $p_c$  from (71) and (76) and noting that (66) and (74) allow us to write the cutoff frequencies  $\omega_n$  and  $\omega_i$  in the form

$$\omega_{n} = \frac{\frac{2D}{p}}{w_{n}^{2}}$$

(77)

and

$$\omega_{1} = \frac{2D_{p}}{w_{1}^{2}}$$

(78)

we can rewrite (75) and (76), the differential equations governing the behavior of the one-dimensional equivalent transistors, in the respective forms

$$= \frac{1}{\omega_n} \frac{di_{cn}}{dt} = \alpha_n i_{en} + i_{cn}$$

(79)

$$= \frac{1}{\omega_{i}} \frac{di_{ei}}{dt} = \alpha_{i} i_{ei} * i_{ci}$$

(80)

These two equations together with the node equations

$$i_{en} + i_{ci} = i_{e}$$

(81)

$$i_{ei} + i_{en} = i_c$$

(82)

and the appropriate boundary and initial conditions on  $i_e$  and  $i_c$  lead to the approximate expressions originally obtained by Ebers and Moll<sup>†</sup> for the switching times characterizing the transient response of a p-n junction transistor.

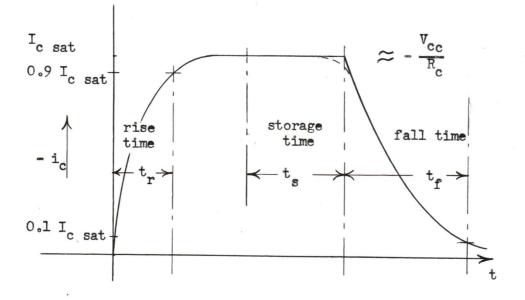

The most common and most useful configuration in which a transistor is utilized in a switching circuit is the common emitter configuration. In this case, the switching time expressions obtained in the manner just described are of the form

\* Ebers, J.J., and Moll, J.L., Op Cit.

6M-4581 S-1 21

$$\mathbf{t}_{\mathbf{r}} = \frac{1}{(1 - \alpha_{\mathbf{n}}) \, \omega_{\mathbf{n}}} \, \ln \left[ \frac{\mathbf{I}_{\mathbf{b}_{1}}}{\mathbf{I}_{\mathbf{b}_{1}} - 0.9 \, (1 - \alpha_{\mathbf{n}}) \, \mathbf{I}_{\mathbf{c}1}} \right] \tag{83}$$

$$\mathbf{t}_{s} = \frac{\boldsymbol{\omega}_{n}^{*} \boldsymbol{\omega}_{i}}{\boldsymbol{\omega}_{n} \boldsymbol{\omega}_{i} (1 - \boldsymbol{\alpha}_{n} \boldsymbol{\alpha}_{i})} \ln \left[ \frac{\mathbf{I}_{b_{2}} \mathbf{u}_{b_{1}}}{\mathbf{I}_{b_{2}} \mathbf{u}_{i}} \left[ \frac{\mathbf{I}_{b_{2}} \mathbf{u}_{b_{1}}}{\mathbf{I}_{b_{2}} \mathbf{u}_{i}} \mathbf{I}_{cl} \right]$$

(84)

$$\mathbf{t}_{t_{f}} = \frac{1}{(1-\alpha_{n})\omega_{n}} \ln \left[ \frac{\mathbf{I}_{c1} - \left(\frac{\alpha_{n}}{1-\alpha_{n}}\right)\mathbf{I}_{b_{2}}}{\frac{1}{10} \mathbf{I}_{c_{1}} - \left(\frac{\alpha_{n}}{1-\alpha_{n}}\right)\mathbf{I}_{b_{2}}} \right]$$

(85)

where the currents and switching times are as defined in Figure 14. In addition to the switching times, two steady-state parameters are of considerable interest in the design of a switching transistor namely: -the normal mode common-emitter current gain,  $\beta_n$ , the saturation region collector to emitter voltage,  $V_{ce \ sat}$ . The first of these parameters is related to  $\alpha_n$  by an equation of the form

$$\beta_n = \frac{\alpha_n}{1 - \alpha_n} \tag{86}$$

The second parameter is obtained by solving the equivalent circuit of Figure 13 subject to the boundary condition

$$p_e = p_{no} \left( e^{\frac{q}{kt} \nabla_e} - 1 \right)$$

(87)

$$p_{c} = p_{no} \left( e^{\frac{q}{kt} v_{c}} - 1 \right)$$

(88)

for

$$v_{ce} \triangleq v_c - v_e$$

(89)

In the saturation region, this solution, originally obtained by Ebers and Moll<sup>\*</sup> has the form

of Ebers, J.J., and Moll, J.L., Op. Cit.

.

•'

$$\nabla_{ce \text{ sat}} = \frac{kT}{q} \ln \left[ \frac{1 - \frac{I_{cl}}{I_{b_{1}}} \left( \frac{1 - \alpha_{n}}{\alpha_{n}} \right)}{\frac{1}{1 + \left( 1 + \frac{I_{cl}}{I_{b_{1}}} \right) \left( \frac{1 - \alpha_{1}}{\alpha_{1}} \right)}} \right]$$

(90)

From the point of view of switching circuit design, equations (83) to (86) and (90) present the transistor switching characteristics in a highly satisfactory form. Knowing the normal and inverted, commonbase, current gains,  $\alpha_n$ , and  $\alpha_i$ , and their respective cutoff frequencies,  $\omega_n$ , and  $\omega_i$ , of a transistor, one can relate the switching behavior of the transistor to its circuit environment in terms of the base current drives,  $I_{b_1}$ , and  $I_{b_2}$ , and the collector current,  $I_{c_1}$ . Thus, from a knowledge of the small-signal transistor parameters,  $\alpha_n$ ,  $\alpha_i$ ,  $\omega_n$ , and  $\omega_i$ , one can obtain a good idea of the over-all switching characteristics of a given switching circuit design for any particular type of transistor.

From the point of view of device design, on the other hand, the above-mentioned equations are not very useful. While these equations indicate the numerical values of  $\alpha_n$ ,  $\alpha_i$ ,  $\omega_n$  and  $\omega_i$  necessary to obtain a set of desired switching characteristics or, for a given transistor design, how and to what extent each of the electrical parameters should be varied to optimize its switching characteristics, the equations do not show how the electrical parameters are related to the physical design parameters of the transistor nor do they show how the electrical parameters are related, through the physical design parameters, among themselves. As we shall show, the electrical parameters are related in such a manner that in many cases the variation in a particular physical design parameter which results in a desired improvement in one electrical parameter produces undesirable changes (from the point of view of optimizing the switching characteristics of a transistor) in others. Consequently, in order to utilize equations (83) to (86) and (90) for the design of switching transistors, it is necessary first to establish the equations relating the electrical parameters  $a_n$ ,  $a_i$ ,  $\omega_n$  and  $\omega_i$  to the physical design parameters.

#### 7.0 The Transformation Equations

In the foregoing pages of Part III of this paper, we have seen that the transient behavior of a transistor of arbitrary geometry with normal and inverted small-signal characteristics  $\alpha_n$ ,  $\omega_n$  and  $\alpha_i$ ,  $\omega_i$ , respectively, can be approximated with reasonable accuracy by two, idealized, one-dimensional transistors, one of which has the smallsignal characteristics  $\alpha_n$ ,  $\omega_n$  and the other  $\alpha_i$ ,  $\omega_i$ , connected as shown in Figure 13. The analysis of the idealized, one-dimensional transistor which was discussed briefly above shows that the common-base, current gain,  $\alpha_o$ , and its cutoff frequency,  $\omega_{ca}$ , can be expressed in terms of the physical and geometrical parameters  $\tau_p$ , the minority carrier lifetime in the base region, and w, the width of the base region. The forms of the se equations are given by (65) and (66). By identifying  $\alpha_n$  with  $\alpha_o$ , and  $\omega_n$  with  $\omega_{ca}$ , we have from (65) and (66) that

$$\alpha_{n} = \frac{1}{\frac{W_{n}^{2}}{\frac{1}{2D_{p}} \frac{1}{\tau_{n}}}}$$

(91)

and

$$\omega_{n} = \frac{\frac{2D}{p}}{W_{n}^{2}} + \frac{1}{\tau_{n}}$$

(92)

where

$W_n$  is defined to be the base width of the equivalent, idealized, one-dimensional transistor for the normal-mode operation of the actual transistor.

$\tau_n$  is defined to be the minority carrier life-time in the base region of the equivalent, idealized, one-dimensional transistor for normal-mode operation of the actual transistor.

Similarly, by identifying  $\alpha_i$  with  $\alpha_o$ , and  $\omega_i$  with  $\omega_{c\alpha}$ , we also have from (65) and (66) that

$$\alpha_{i} = \frac{1}{1 + \frac{w_{i}^{2}}{2D_{p}} \frac{1}{\tau_{i}}}$$

(93)

and

$$\omega_{1} = \frac{2D_{p}}{\frac{p}{w_{1}}} + \frac{1}{\tau_{1}}$$

where

W<sub>i</sub> is defined to be the base width of the equivalent, idealized, one-dimensional transistor for the inverted-mode operation of the actual transistor.

$\tau_i$  is defined to be the minority carrier lifetime in the base region of the equivalent, idealized, one-dimensional transistor for the inverted-mode operation of the actual transistor.

From (91), (92), (93), and (94), we see that the four smallsignal parameters  $\alpha_n$ ,  $\alpha_i$ ,  $\omega_n$ , and  $\omega_i$  can be expressed completely in terms of  $w_n$ ,  $w_i$ ,  $\tau_n$  and  $\tau_i$ , the physical and geometric properties of the equivalent, idealized, one-dimensional transistors. As such, these relationships can be regarded as a set of transform equations since they essentially transform a realizable transistor into a pair of transistors of idealized one-dimensional form.

Comparing (91) (92) (93) and (94) with the set of equations given by (29) in Part I of this paper, we note that they are almost identical except for the fact that  $\tau_b$  in the normal-mode transform equation of (29) is replaced by  $\tau_n$  in (91) and (92) and, in the inverted-mode transform equations of (29),  $\tau_b$  is replaced by  $\tau_i$  in (93) and (94). The intended implication here, by making this symbolic distinction between the effective minority carrier lifetimes of the normal and inverted modes of operation, is that, in general,

$\tau_n \neq \tau_i$

The experimental evidence which substantiates this fact was pointed out and discussed in some detail in the introduction to this part (Part III) of the paper. Furthermore, in developing the first order switching theory which led to the transform equation (91) through (94), it was not necessary to impose nor did the switching theory imply any direct relationship between  $\tau_n$  and  $\tau_i$ . Consequently, in the rest of this paper we shall consider that, in general, no direct relationship exists between  $\tau_n$  and  $\tau_i$ .

(94)

As we shall see in Part IV of this paper, the rather subtle distinction that we have made between the minority carrier lifetimes in the base region of the normal- and inverted-mode, equivalent, one-dimensional transistor will enable us to express  $\alpha_n$ ,  $\alpha_i$ ,  $\omega_n$  and  $\omega_i$  more or less explicitly in terms of the actual physical and geometrical parameters of the realizable transistor and, ultimately, we shall be able to obtain expressions relating the switching characteristics,  $\beta_n$ ,  $\tau_s$ ,  $V_{ce sat}$  etc., to these same physical and geometrical parameters.

R. Bert

Page 1 of 8

Division 6 — Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

| SUBJECT:  | TX-0 Circuitry   |

|-----------|------------------|

| то:       | K. H. Olsen      |

| From:     | J. R. Fadiman    |

| Date:     | October 22, 1956 |

| Approved: | E. Ofsen         |

|           | K. H. Olsen      |

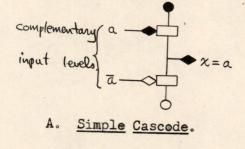

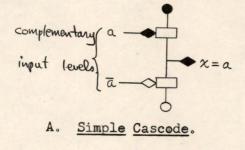

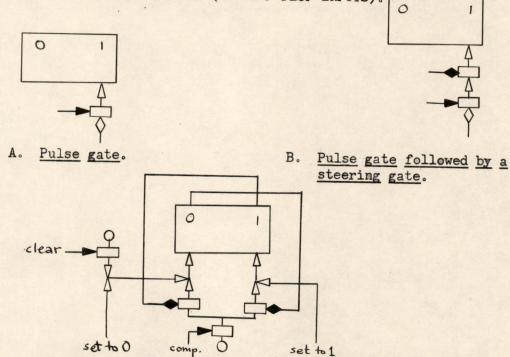

Abstract:

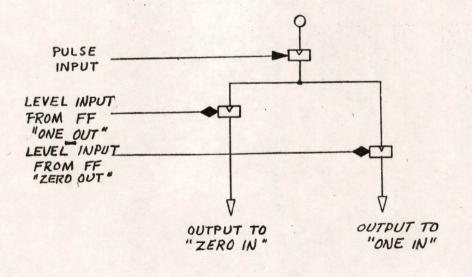

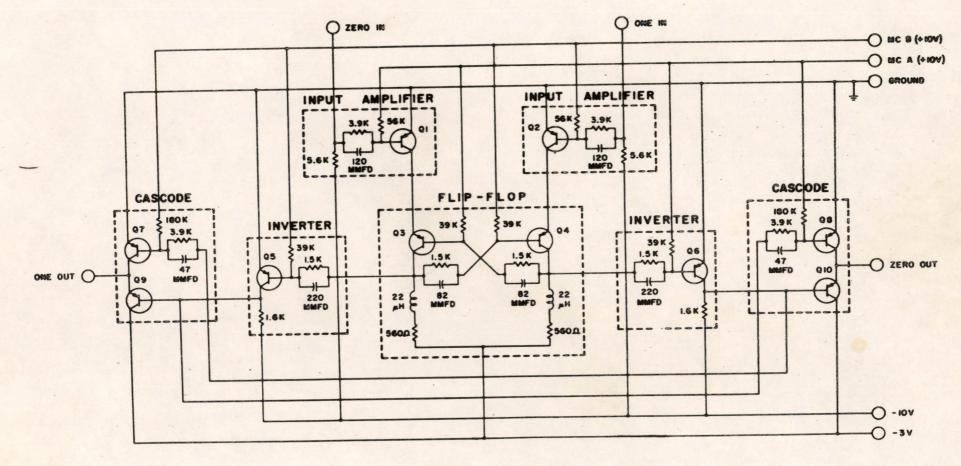

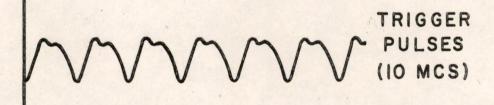

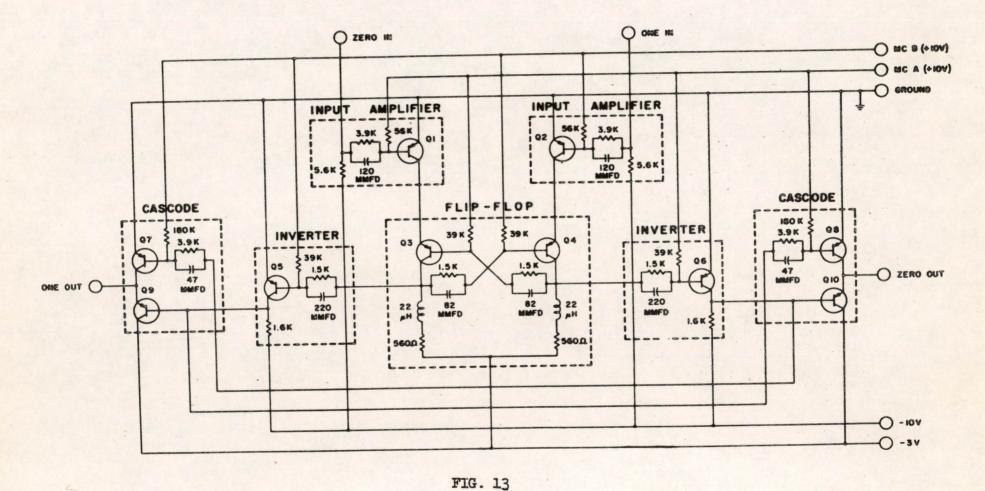

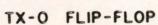

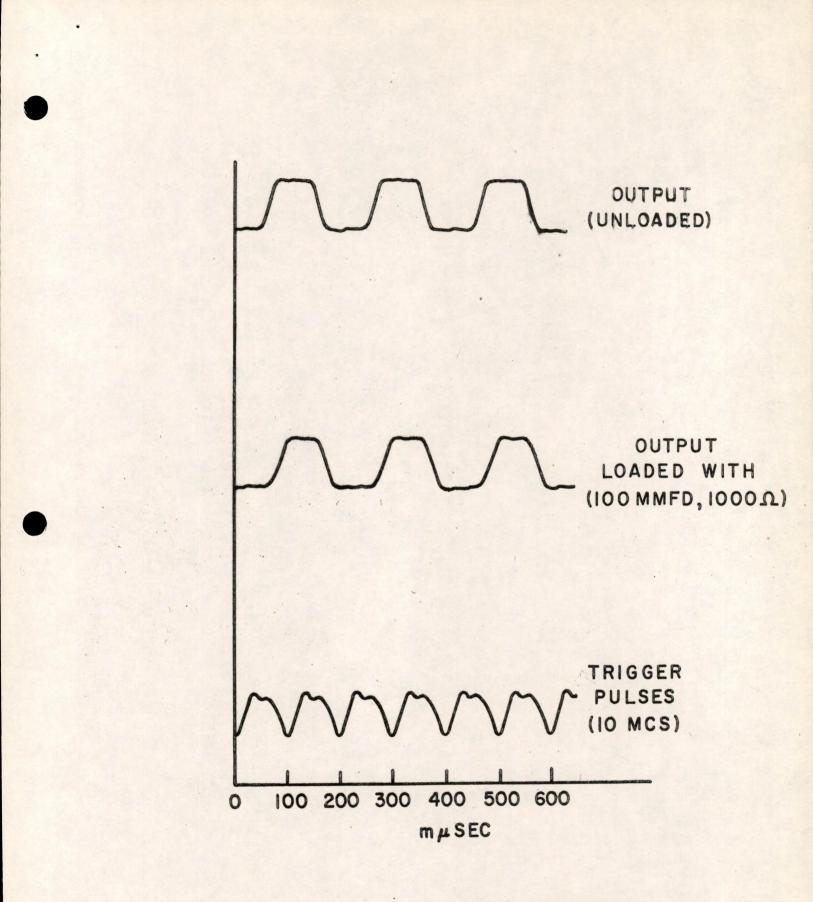

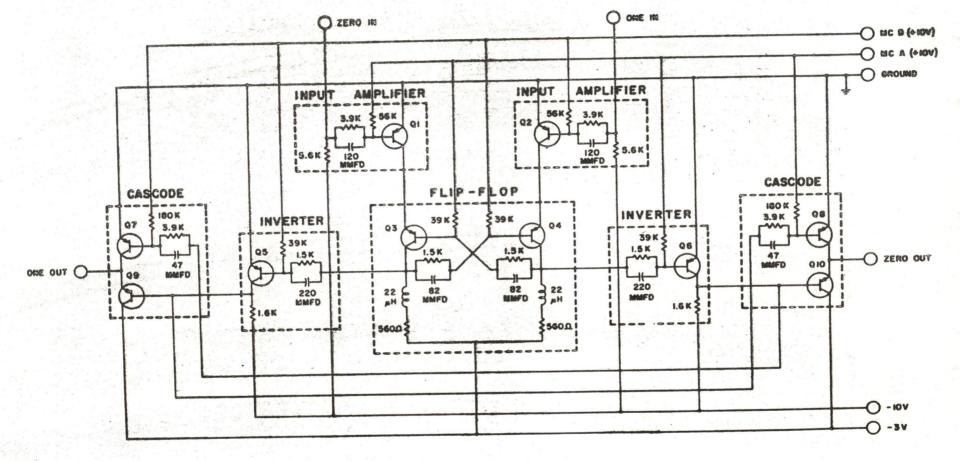

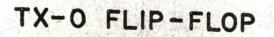

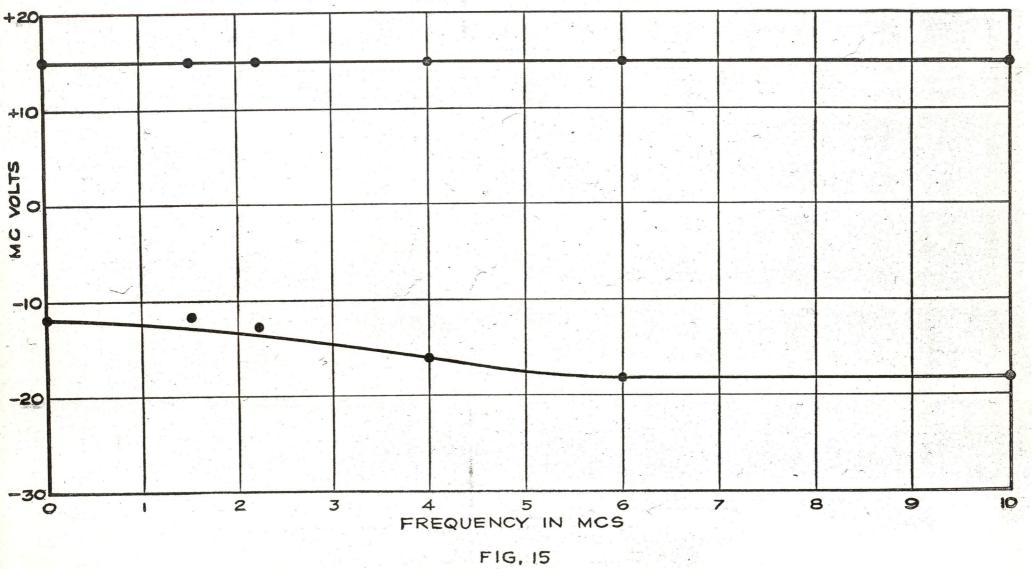

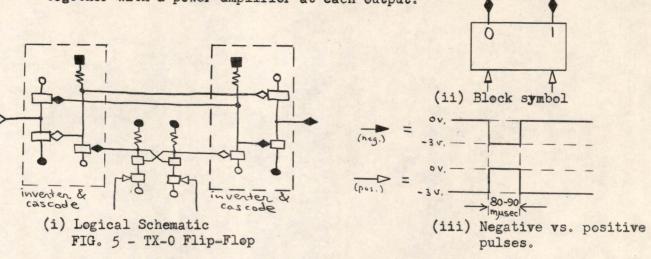

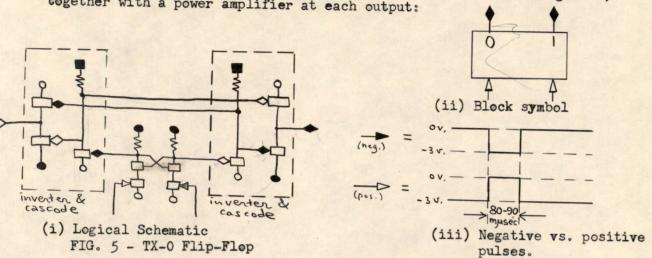

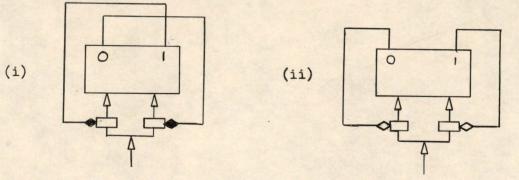

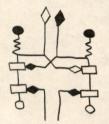

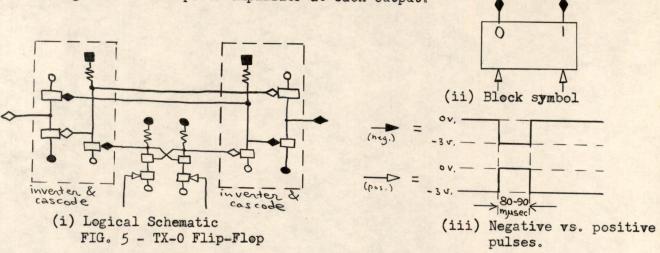

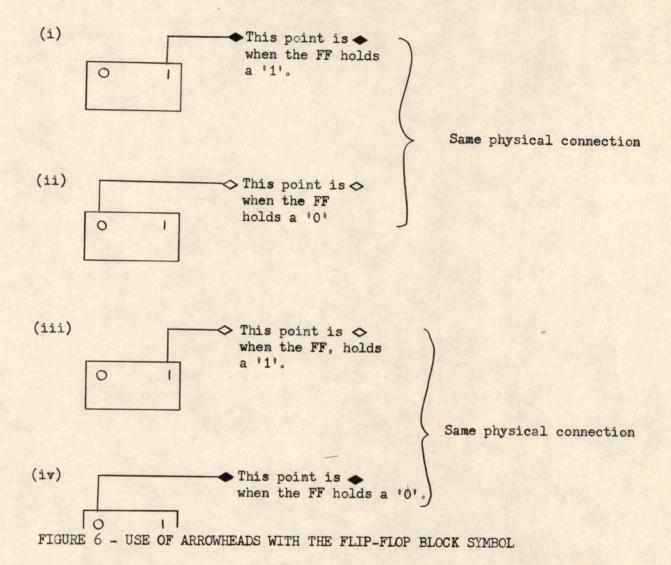

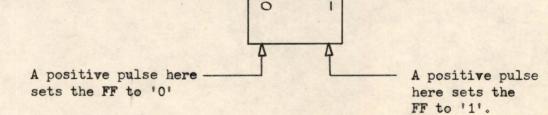

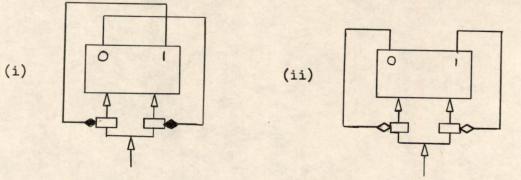

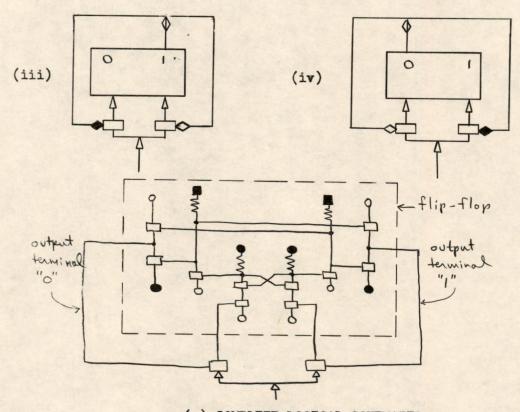

The high speed logical circuitry used in the TX-O transistor computer uses Philco 5122 Surface Barrier transistors. AND and OR gates are formed from inverter or emitter follower combinations. The cascode configuration is used as a power amplifier for fast rise and fall times. Timing pulses are generated by vacuum tubes, and gated on and off by a register driver circuit. Marginal checking is accomplished by varying a positive base bias voltage. The TX-O flip-flop is a high-speed flip-flop package using 10 SBTs and capable of 5 mcps operation.

This document is issued for internal distribution and use only by and for Lincoln Laboratory personnel. It should not be given or shown to any other individuals or groups without express authorization. It may not be reproduced in whole or in part without permission in writing from Lincoln Laboratory. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No. AF 19(122)-458.

Page 2 of 8

#### I. Introduction

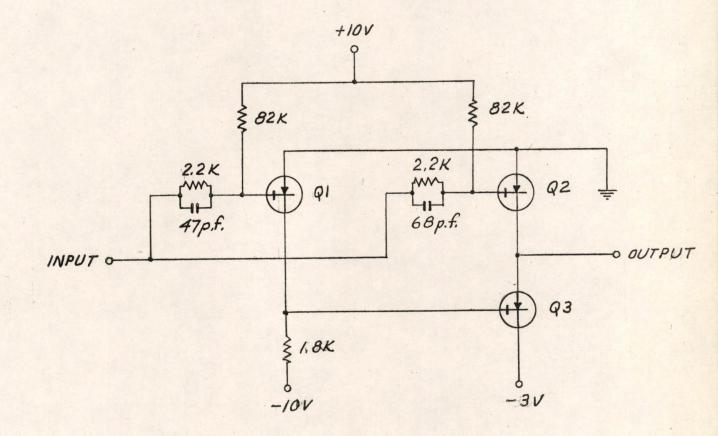

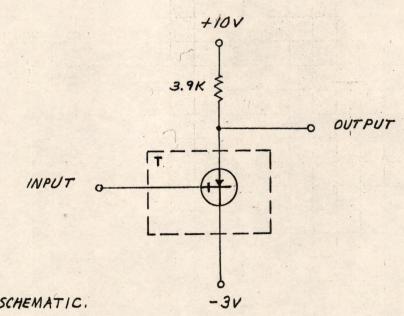

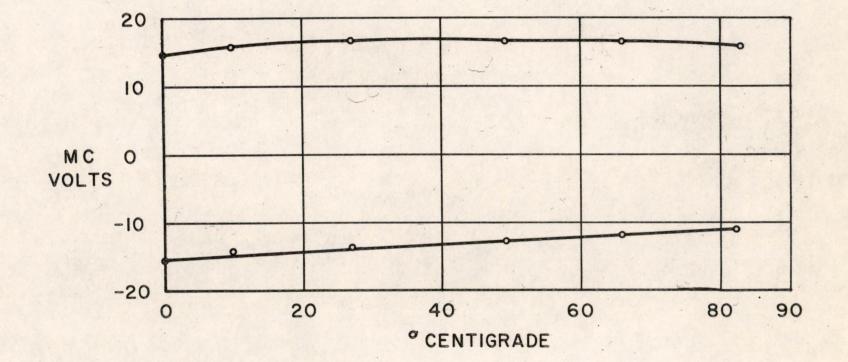

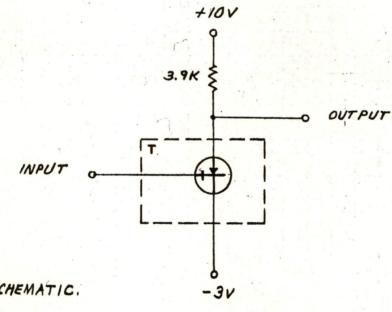

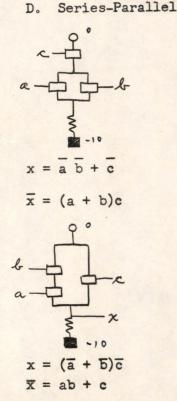

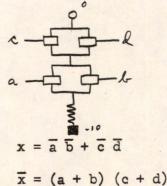

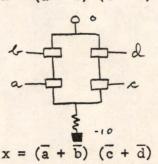

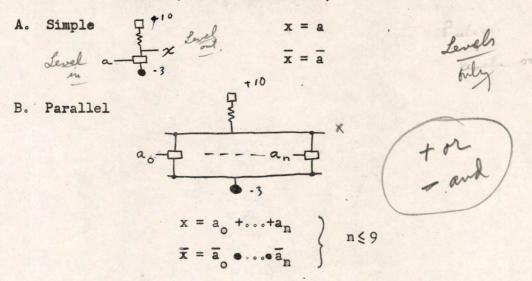

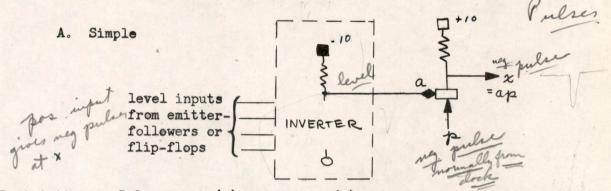

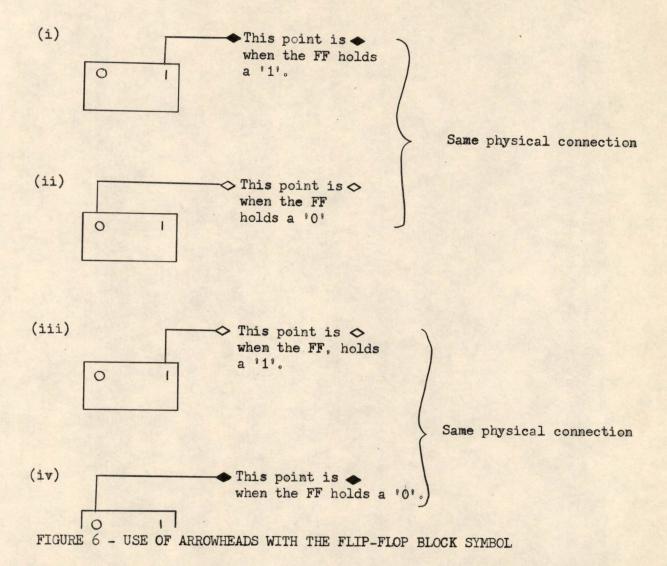

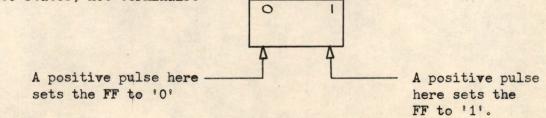

- A. The high speed circuitry for the TX-O computer uses the Philco 5122 Surface Barrier transistor. The two logical levels are ground and -3 volts. Pulses are negative, with an amplitude of -3 volts and a width of from 80 to 100 mu sec. The supply voltages used for the SBT circuitry are -3, -10 and +10 volts.

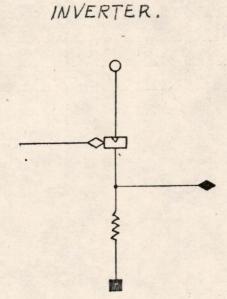

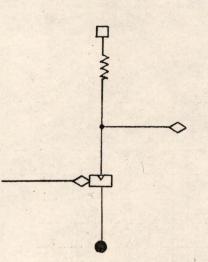

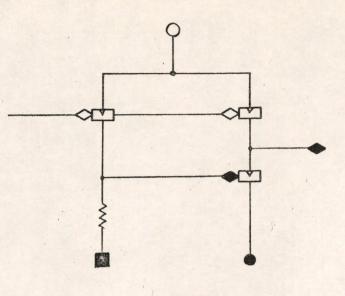

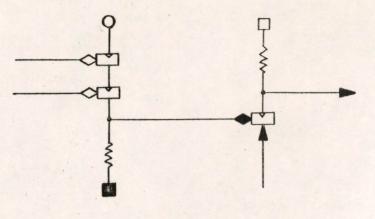

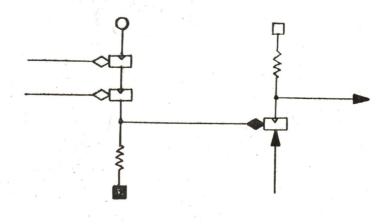

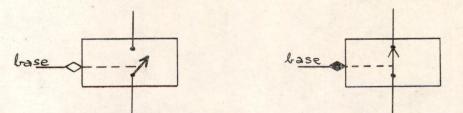

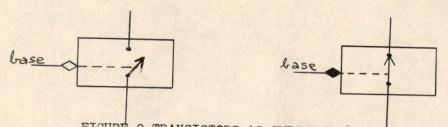

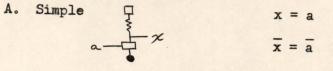

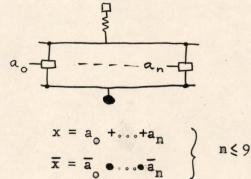

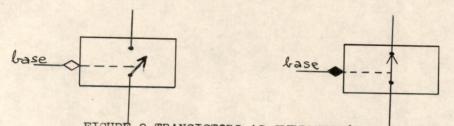

- B. Symbols (Note)

1

24

The following symbols are used.

Transistor (in circuit schematics)

emitter

Transistor (in block schematics)

| -3 volt level                         |

|---------------------------------------|

| Ground level                          |

| Negative pulse (ground to -3 volts) - |

| Positive pulse (-3 volts to ground) - |

| -3 volt supply                        |

| ground O                              |

| -10 volt supply                       |

| +10 volt supply                       |

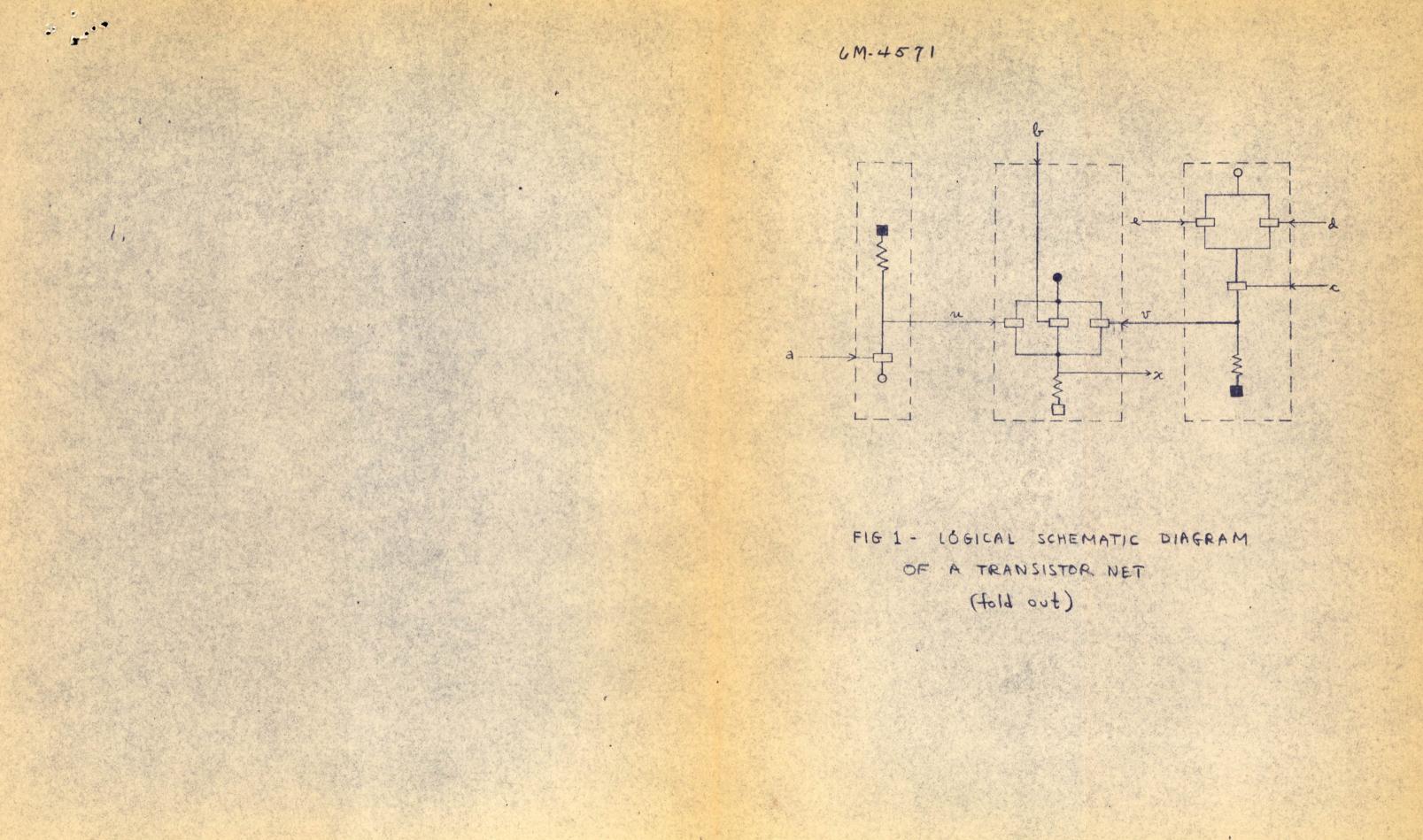

Note 1: For detailed considerations of transistor logic and symbology, refer to: 6M-4571, by R. C. Jeffrey.

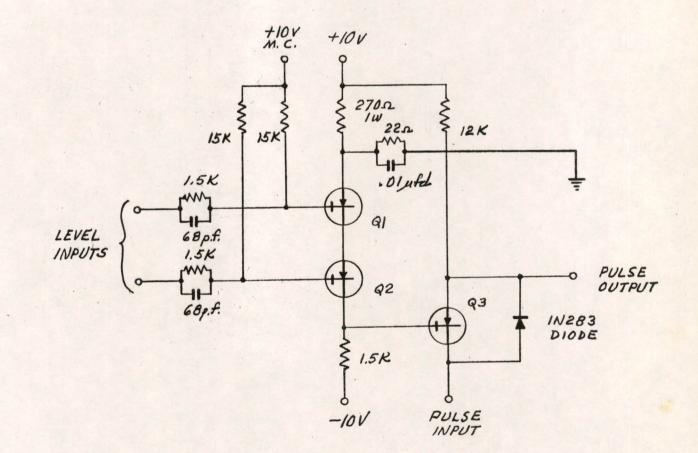

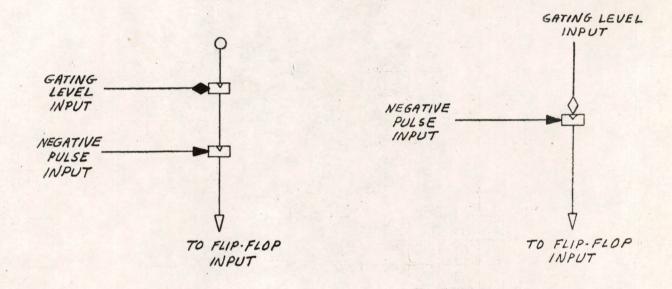

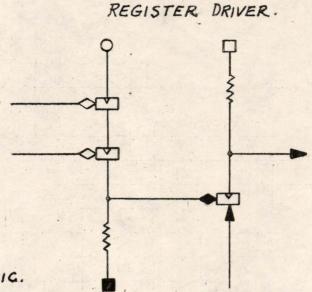

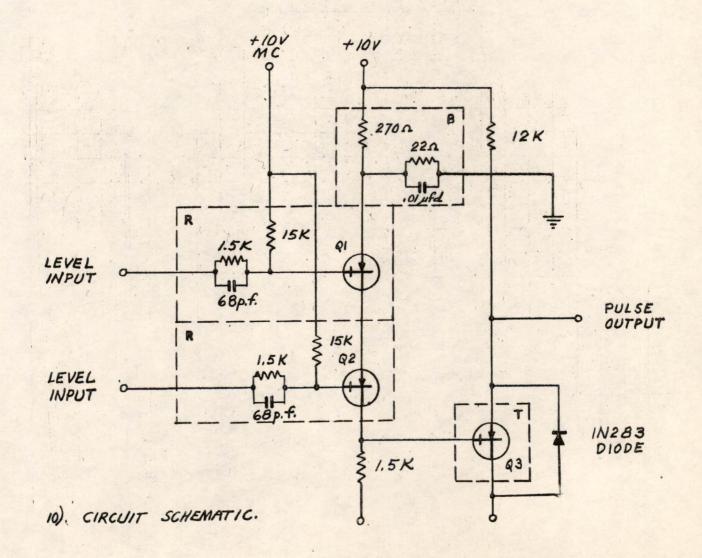

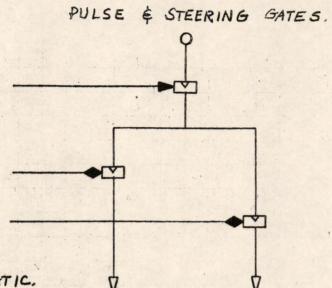

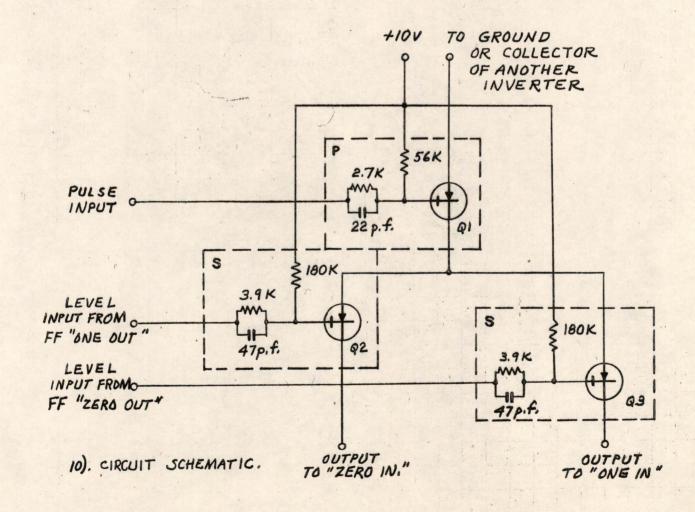

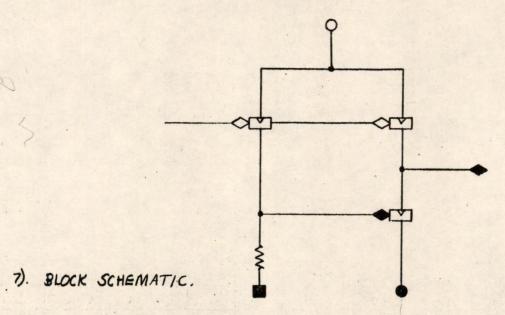

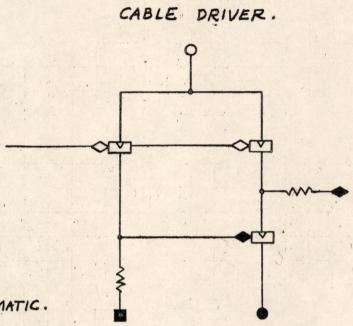

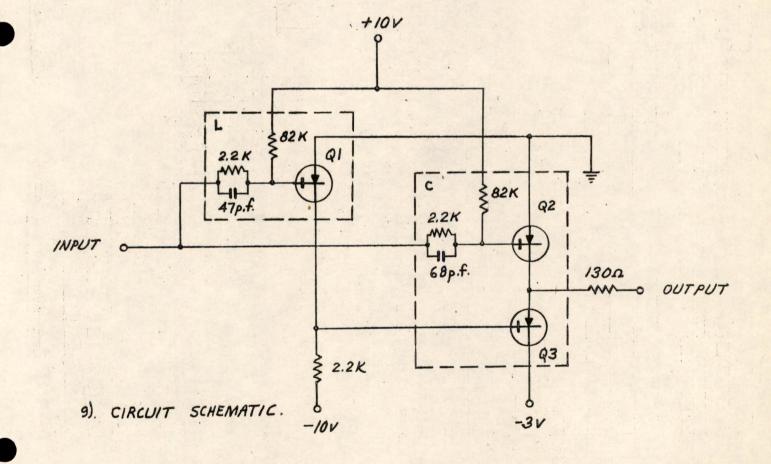

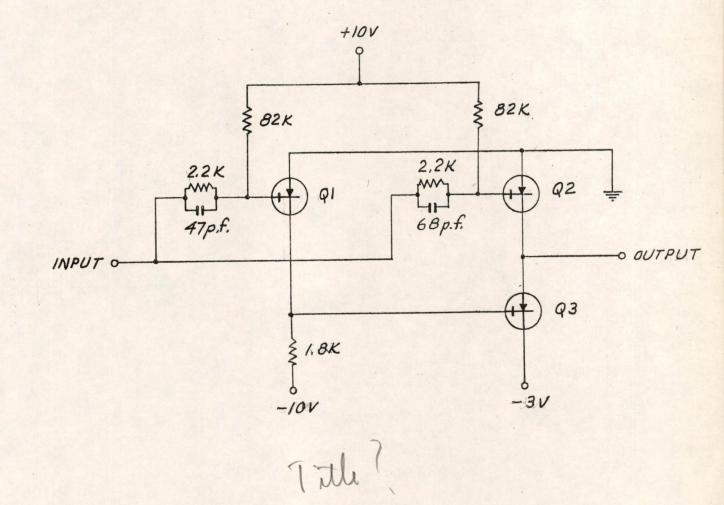

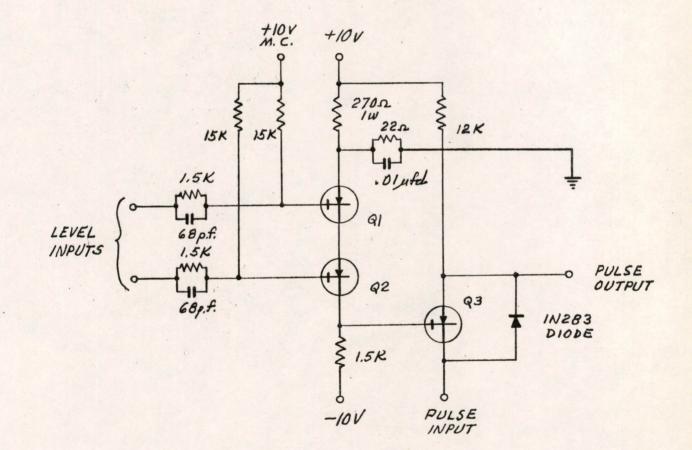

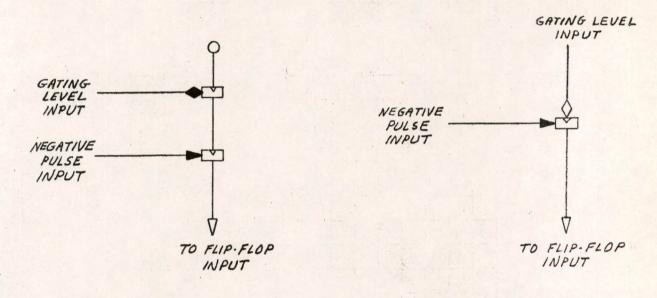

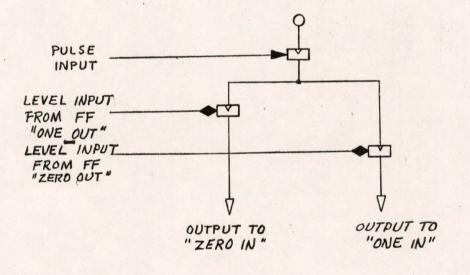

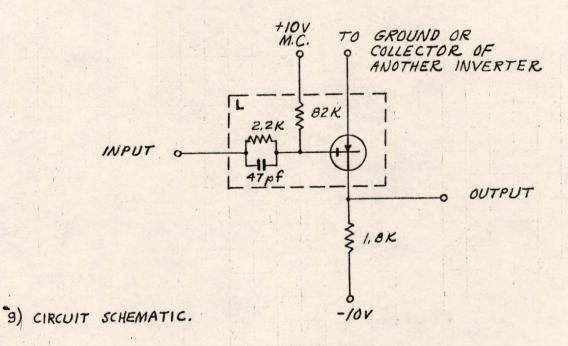

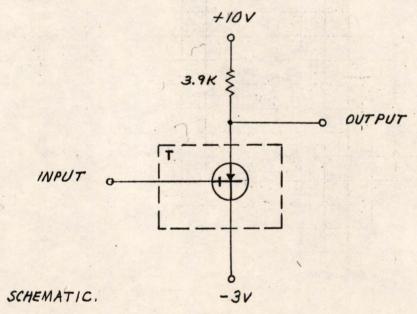

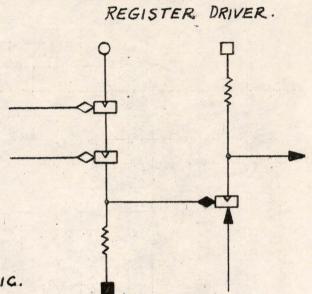

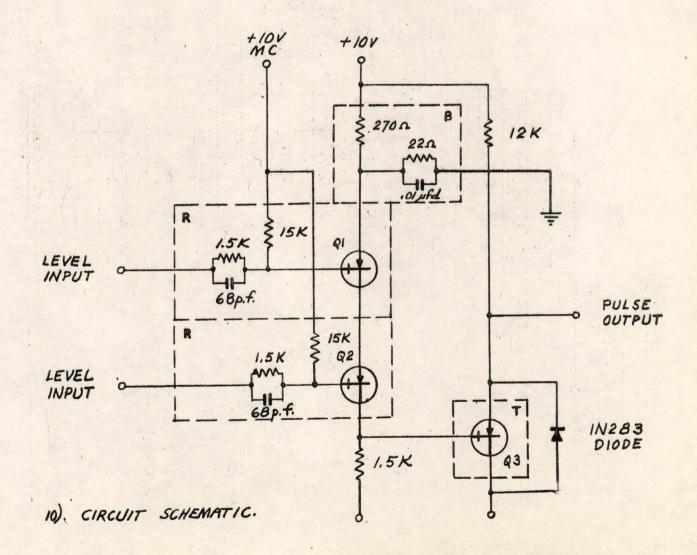

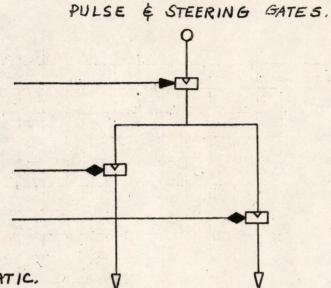

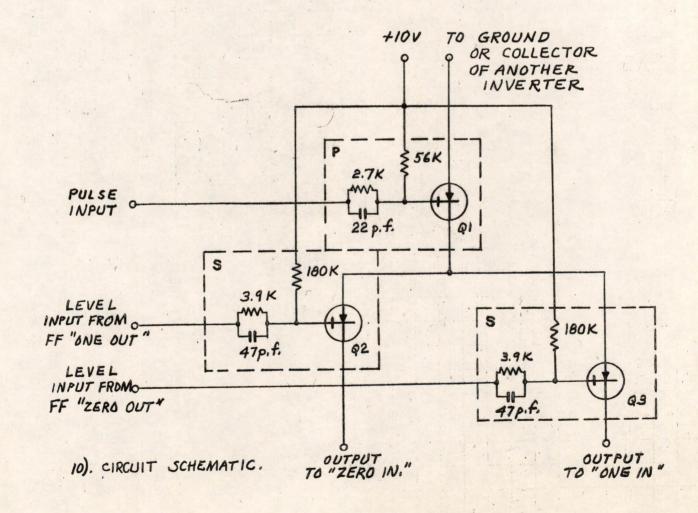

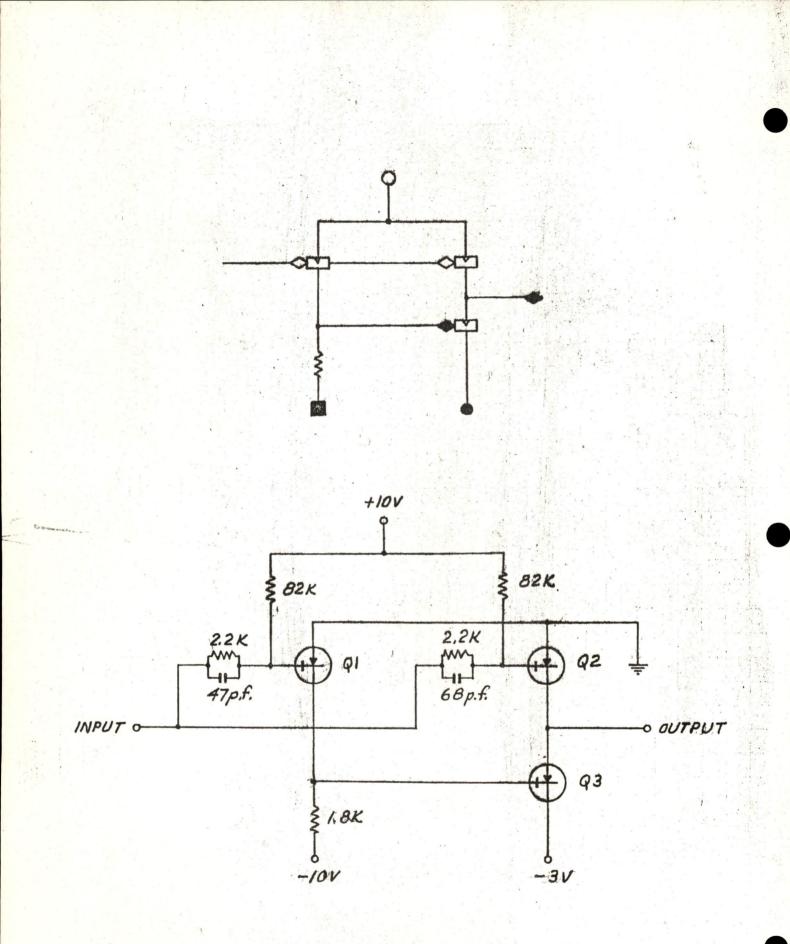

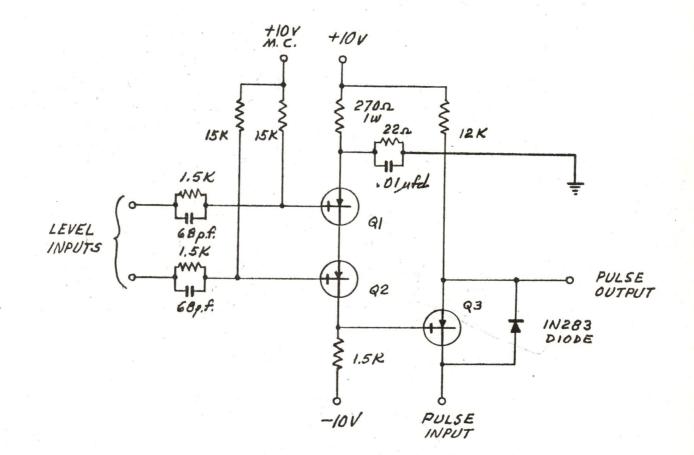

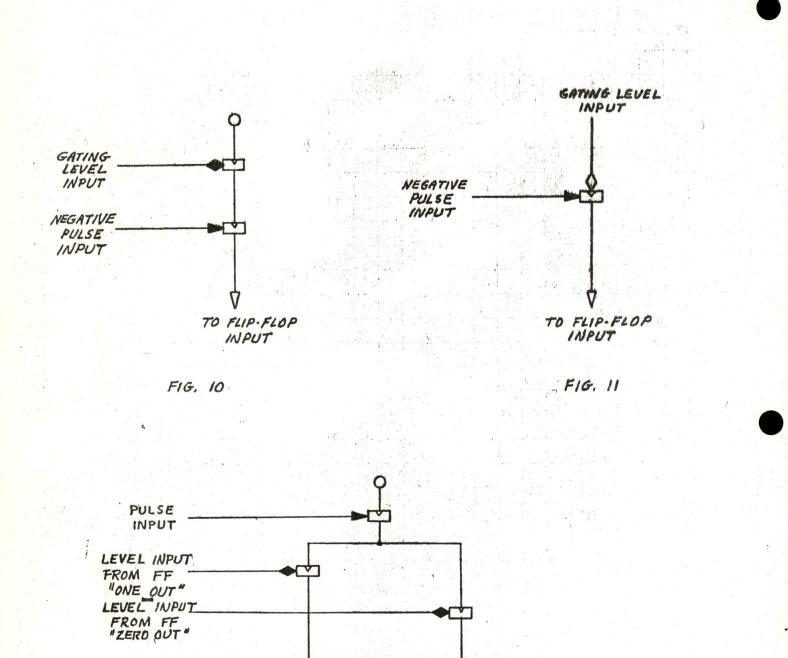

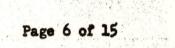

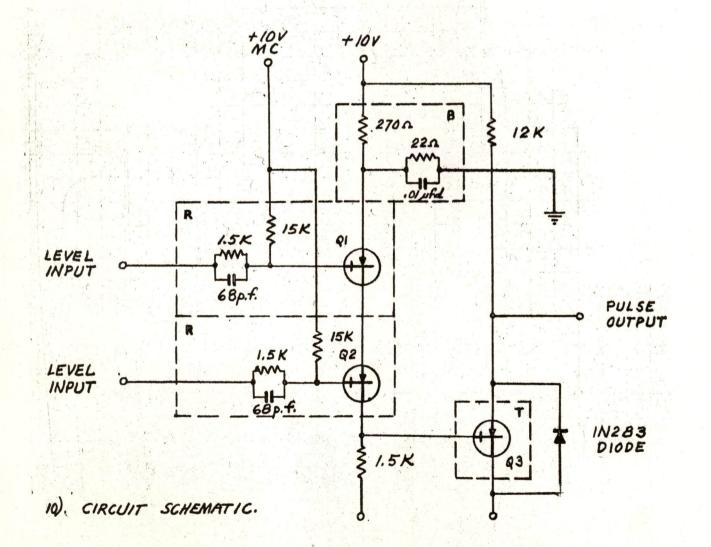

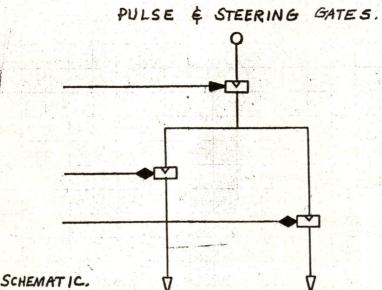

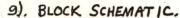

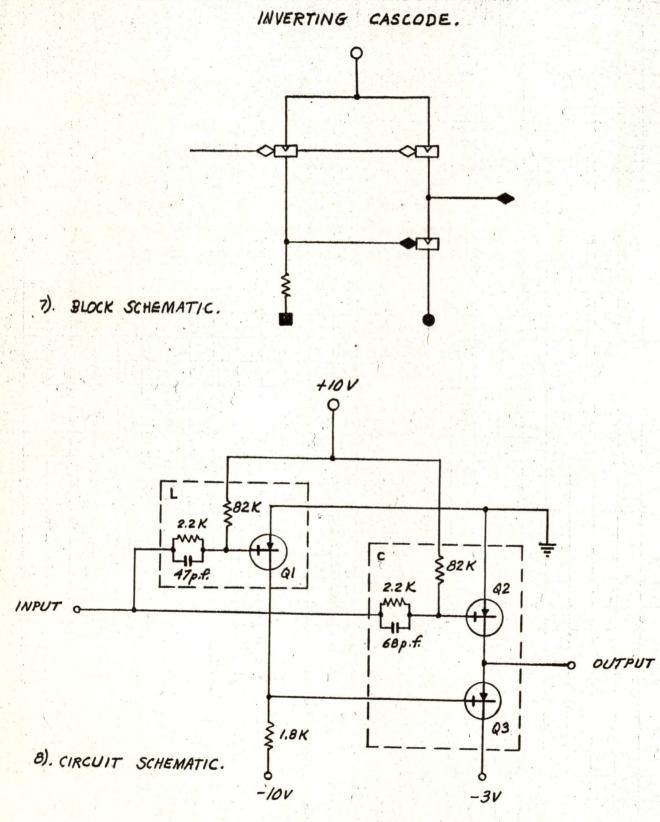

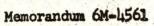

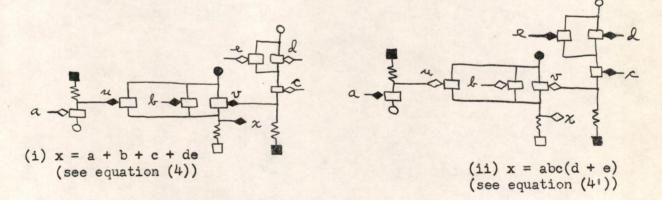

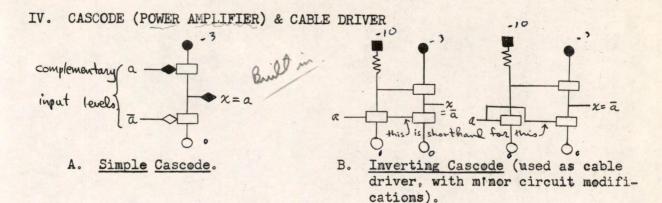

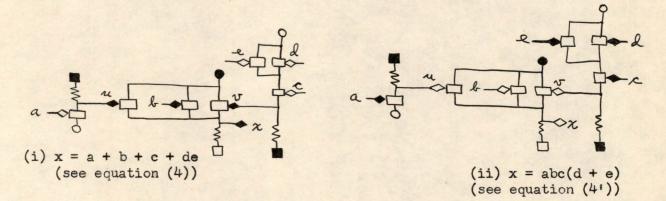

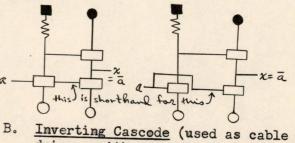

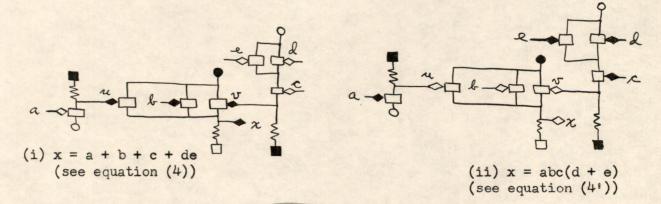

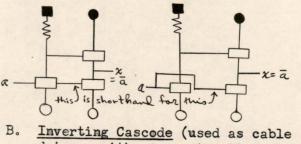

The logical circuitry for the central machine is constructed out of small plug-in units, each containing one, two, or three transistors and associated components. The types of units and their functions are listed below. The schematic circuit diagrams are in figure 1 and detailed descriptions are in the appendix.

| Unit       | Transistor         | Use                                              |

|------------|--------------------|--------------------------------------------------|

| Р          | l SBT              | Pulse input gate to flip-flop                    |

| L          | l SBT              | Level input gate and inverter                    |

| М          | 1 SBT              | Level input gate with high positive bias         |

| R          | l S <sup>B</sup> T | Register driver inverter                         |

| S          | l SBT              | Steering gate                                    |

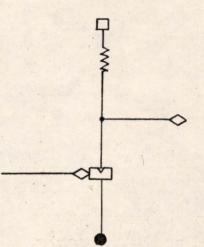

| Т          | l SBT              | Single transistor for single<br>emitter_follower |

| E          | 2 SBT              | Two emitter followers with separate outputs      |

| A          | 3 SBT              | Three emitter followers with a common output     |

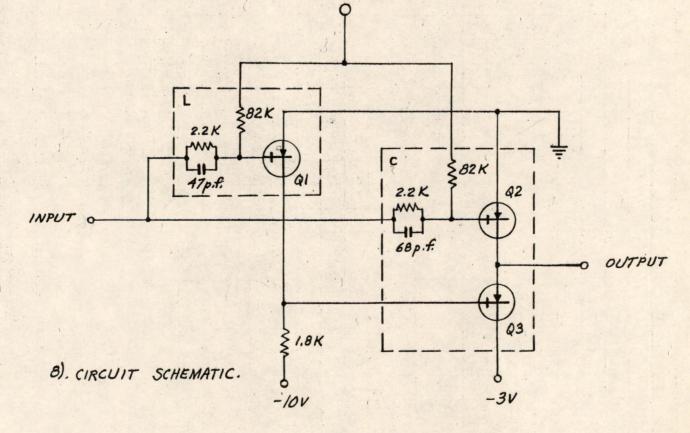

| С          | 2 SBT              | Cascode Circuit                                  |

| F          | 1 GE4JD1A17        | Ferranti Circuit                                 |

| F (Mod II) | 1 GE4JD1A17        | Ferranti Circuit                                 |

| В          | None               | Emitter bias for register driver                 |

| G          | 1 GE4JD1A17        | Indicator light circuit                          |

#### II Logic

----

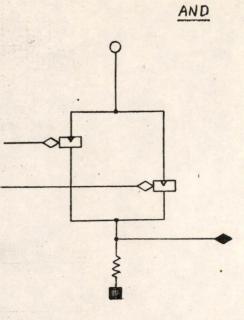

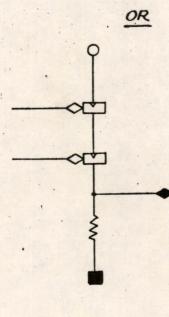

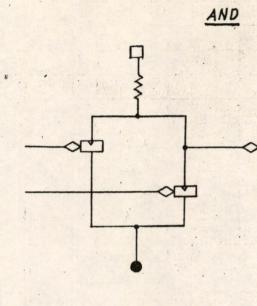

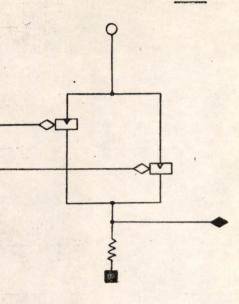

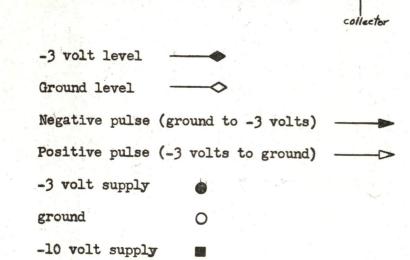

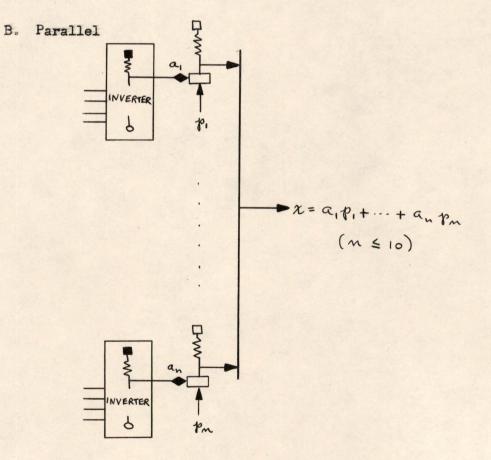

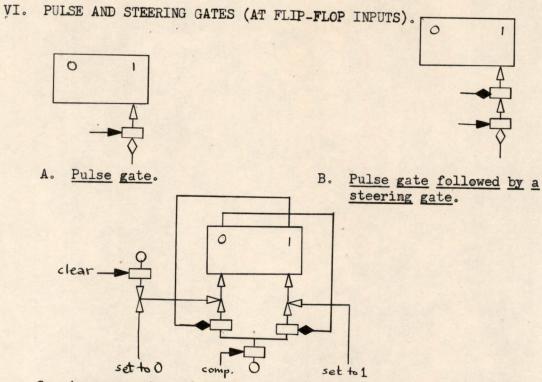

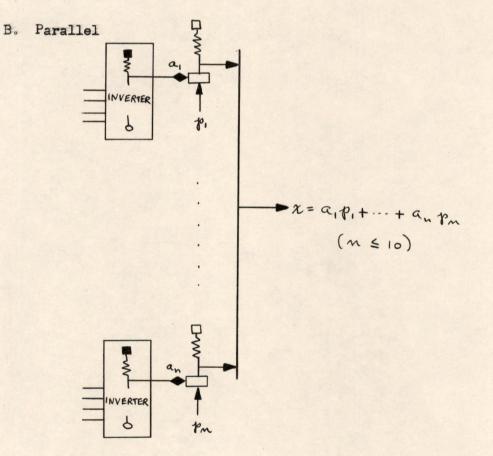

A. "AND" and "OR" Gates

The "AND" and "OR" gates for TX-O are either emitter followers in parallel or inverters in series or parallel. The AND gate for ground level in, ground level out is emitter followers in parallel as shown in Fig. 2. Because of the restrictions of speed for 5 mcps circuits, a maximum of 10 emitter followers may be placed in parallel in this fashion, providing up to a 10-way AND gate. An inverting AND gate for ground level in, -3 level out is shown in Fig. 3. Because of limitations of speed, only two inverters may be placed in parallel. The capacitance to ground goes up as  $\beta C_c$  where  $C_c$  is the collector capacitance of an off transistor and  $\beta$  is the current gain of the transistor, grounded emitter. The inverting OR gate for ground level in, -3 level out is shown in Fig. 4. Because there is a finite voltage drop across a saturated transistor, (about 0.1 volt), only two inverters may be placed in series in this manner.

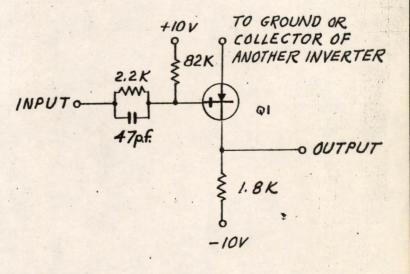

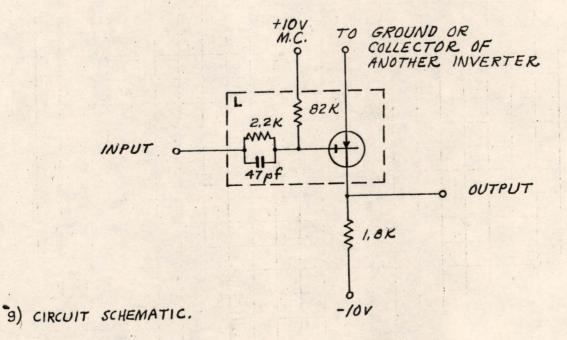

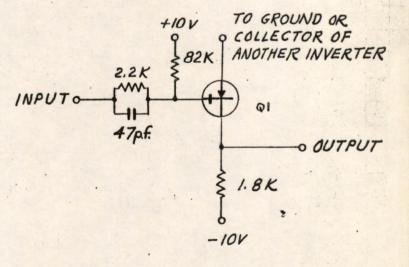

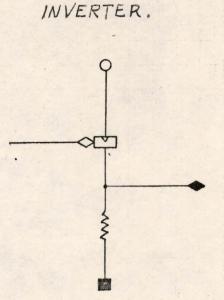

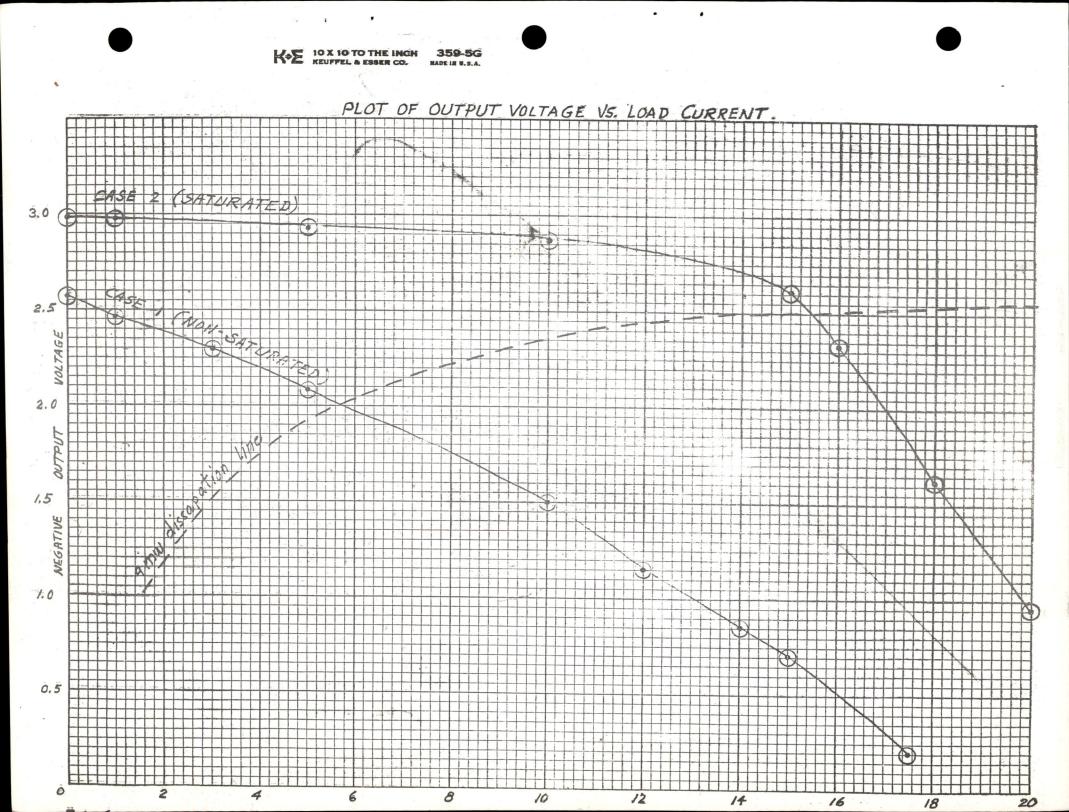

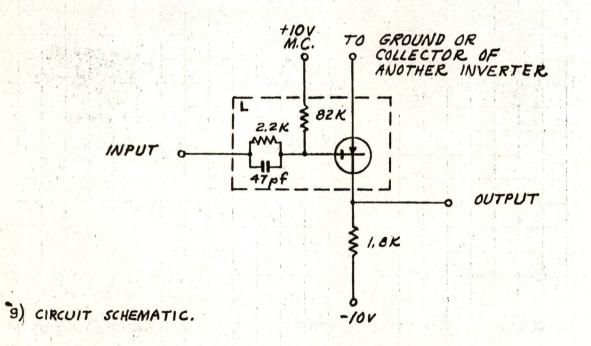

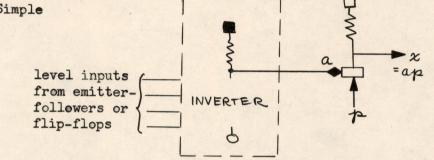

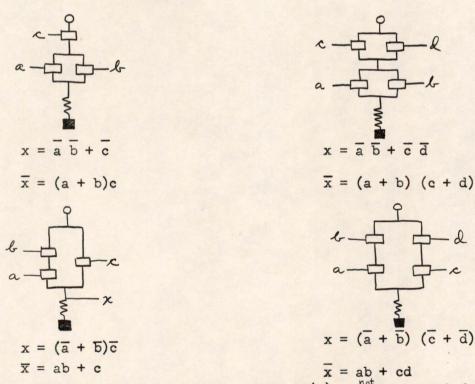

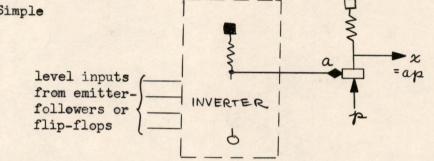

B. Inverter Circuit

For the inverter circuit (Fig. 5) the values of the input resistance and positive bias resistance are so calculated that there is safety margin when the transistor is saturated and when it is cut-off. This insures maximum noise rejection and tolerance to signal variation. It is assumed on the basis of several tests that no transistor will have a  $\beta$  of less than 5 at 5.5 ma. collector current. (Our minimum acceptance  $\beta$  at low current is 15, and ll at end of life). A larger amount of positive bias is used on inverter input gates to flip-flops when the input is from a distant frame, such as from core memory, toggle switch storage, or the photo-electric tape reader. In these cases the induced noise voltages are apt to be larger than usual, and the input impedance to the flip-flop is sufficiently high to allow the use of the larger positive bias current, and consequently smaller input base current.

This bias is also used in cases where the ground level for the emitter is supplied from an emitter follower gate. Such a level goes

4

0.3 volt positive and thus it is necessary for the base to be held at about #0.5 volts to provide adequate margins during cut-off.

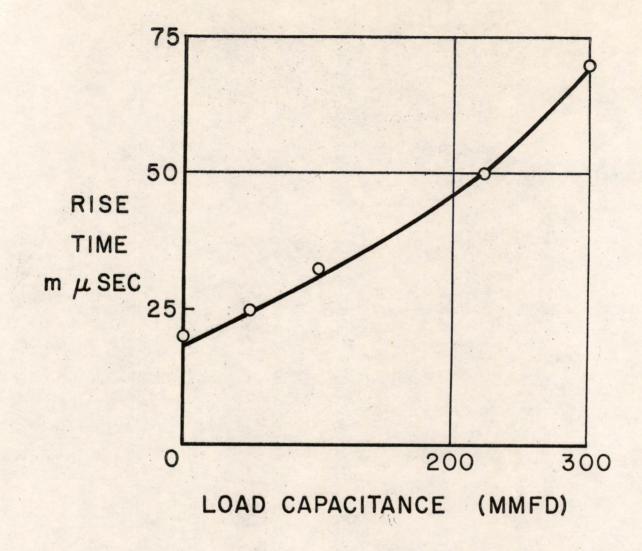

All of the inverters in TX-O use a supply voltage of -10 volts. However, the actual voltage at the collector never exceeds -4 volts, since it is clamped, either by an emitter follower following it, or by a voltage divider to ground. A single inverter provides current sufficient for driving three emitter followers or two inverters. It can drive a capacitance of 75 uuf, with a fall time of 0.1 µ sec.

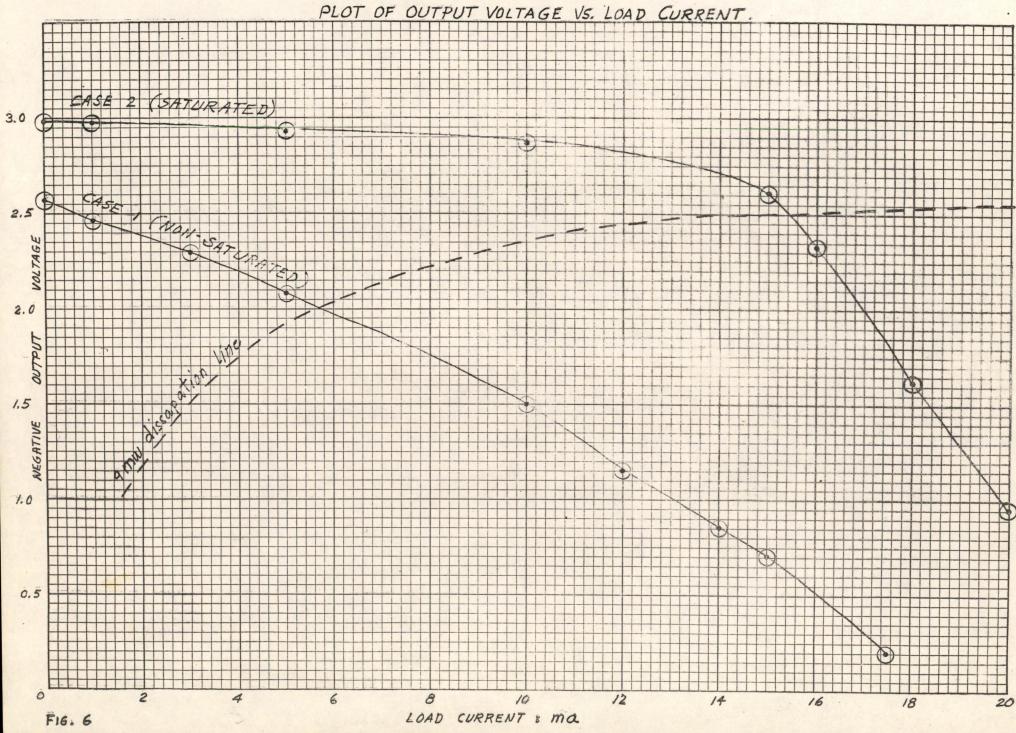

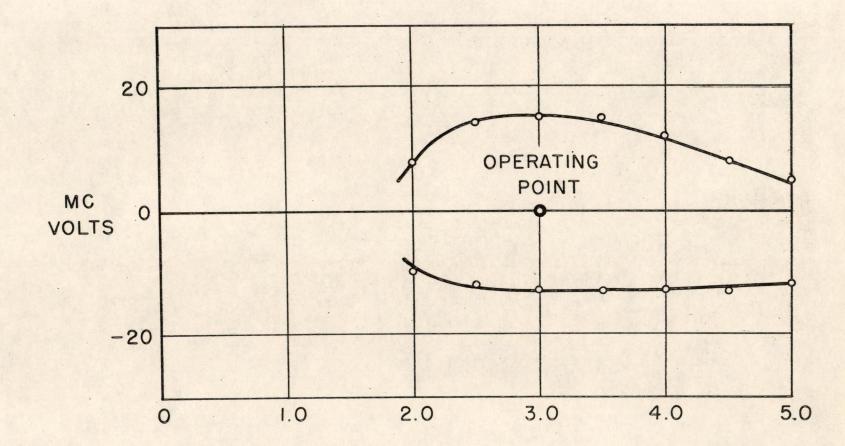

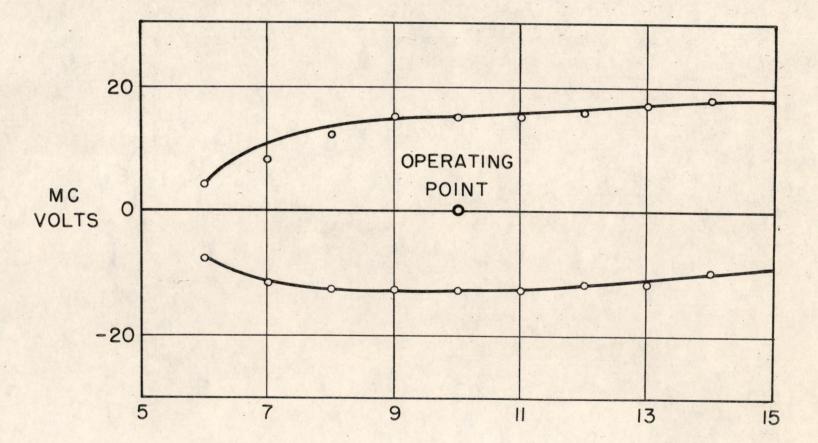

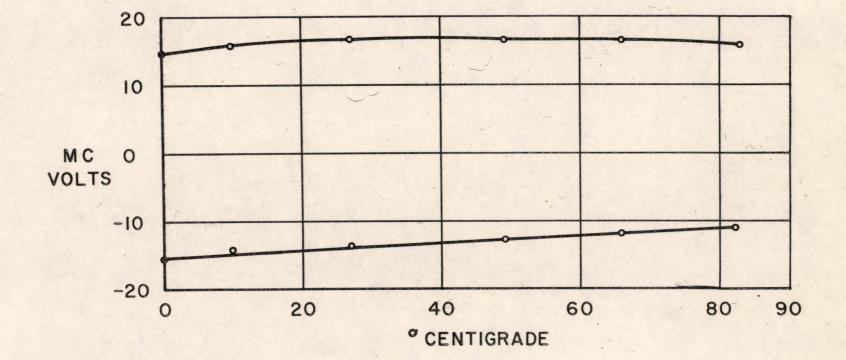

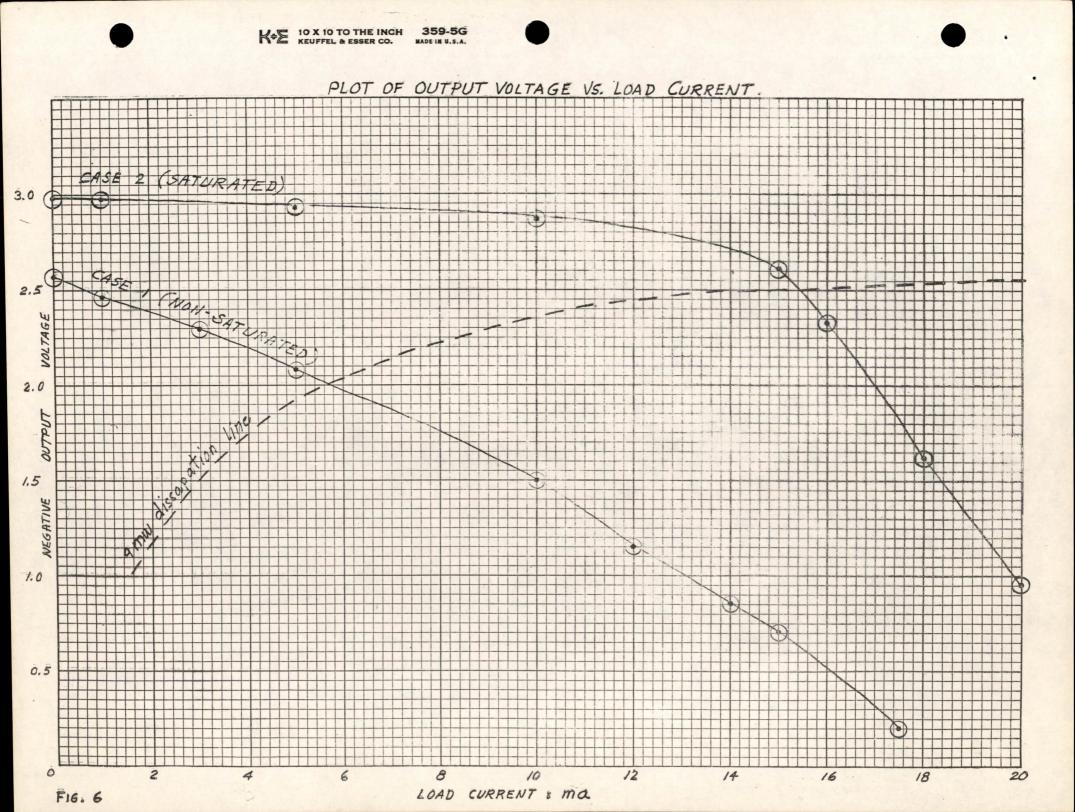

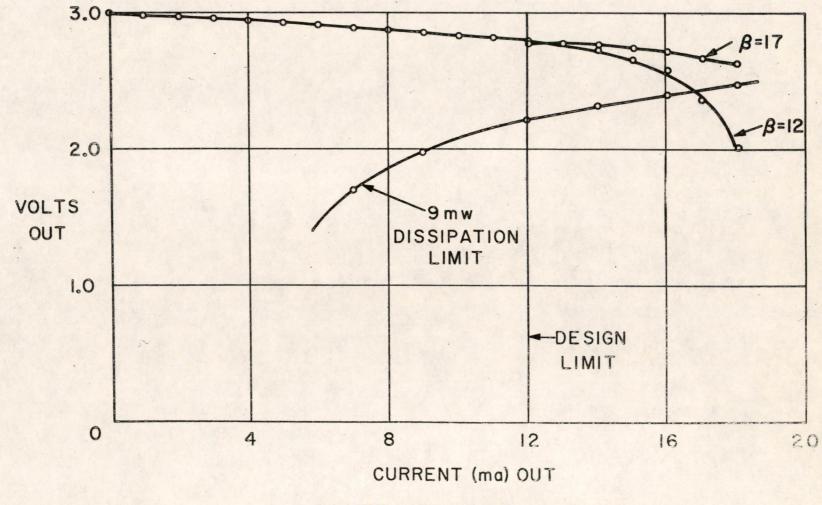

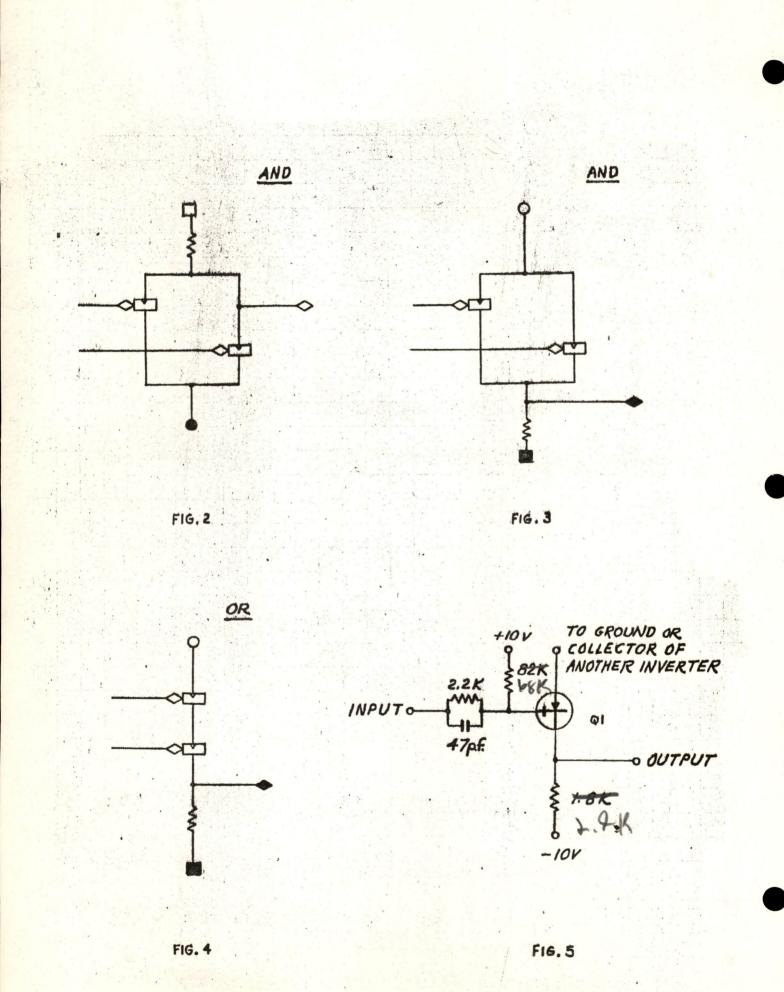

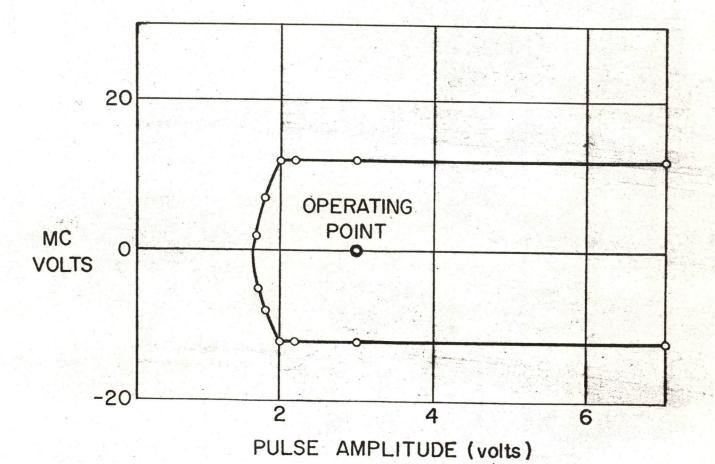

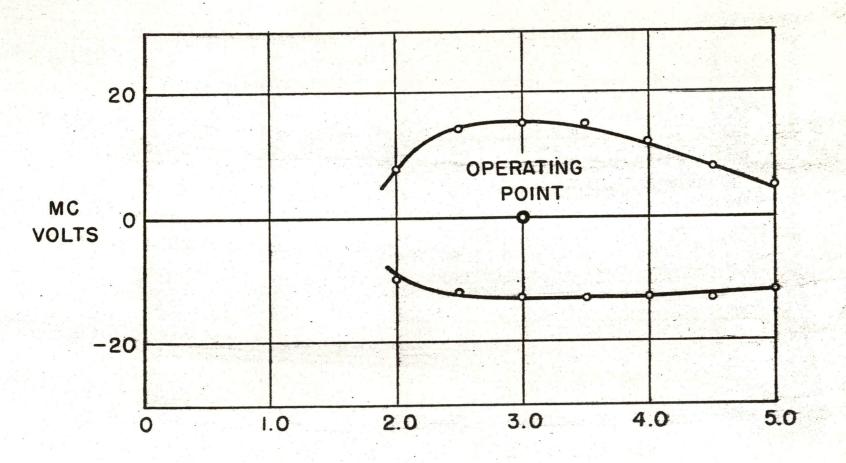

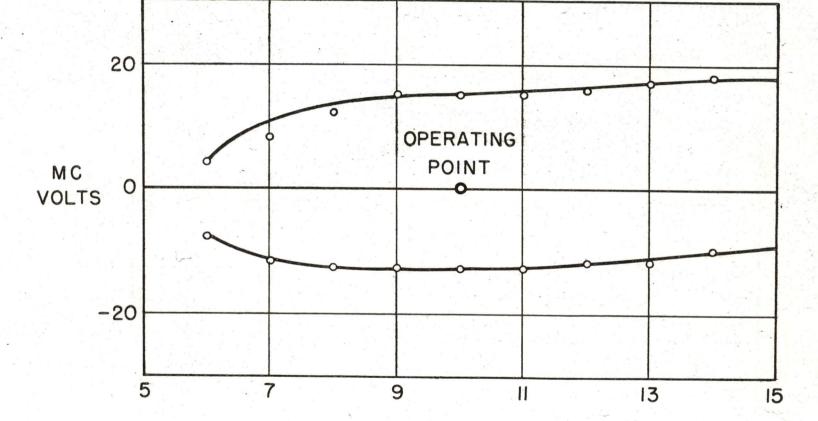

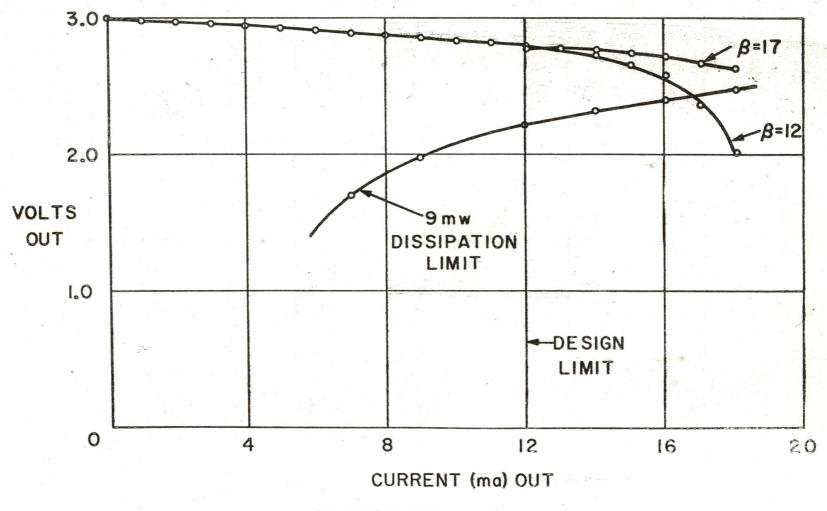

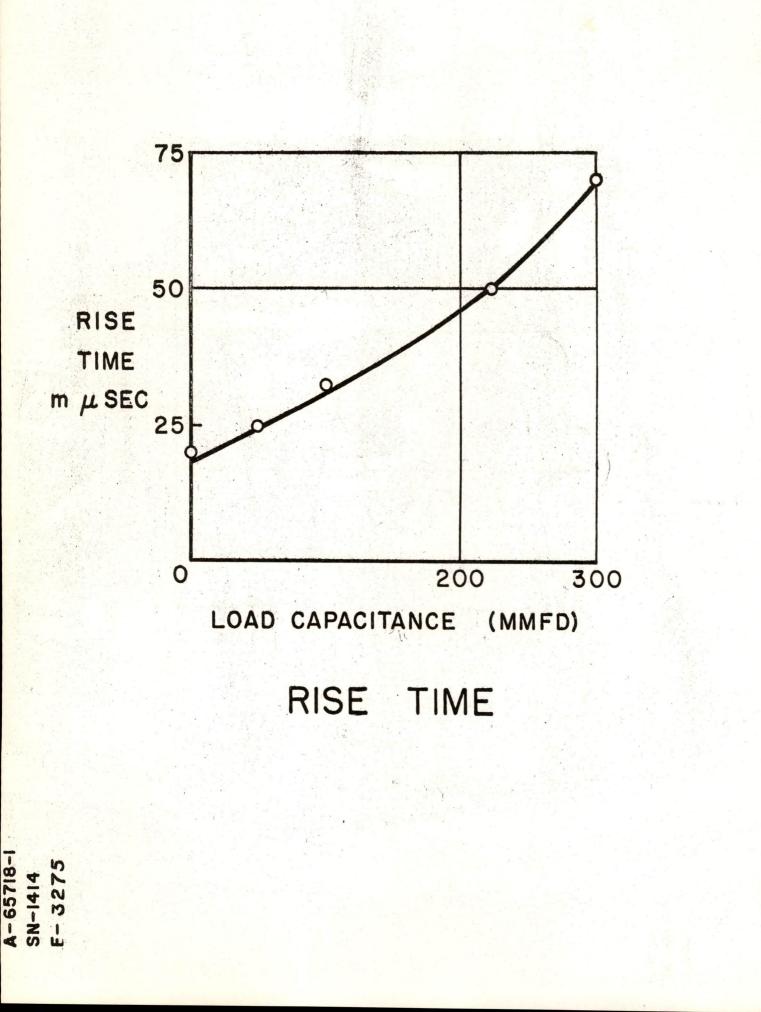

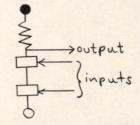

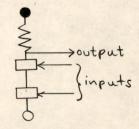

#### C. Emitter Follower Circuit

The logical circuitry utilizes a combination of inverters and emitter followers which in general are alternated. This ensures that when an emitter follower is turned on, it is always kept in saturation since its base is returned effectively to -10 volts through the load resistor of the previous inverter. The difference in driving capabilities of the saturated and non-saturated emitter follower is shown in the graph of Fig. 6. The load resistance of the emitter follower is returned to +10 volts instead of to ground to shorten the rise time of the emitter follower. This emitter follower will provide 8 ma. of output current at -3 volts and will drive a capacitive load of 120 uuf, with a rise time of 0.1  $\mu$  sec.

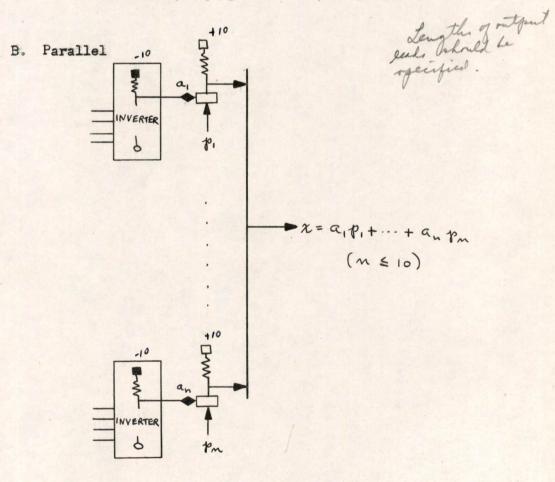

#### D. Cascode Circuit