Executive Records Record Control to 03-00006 Series 1955 - 58 Description MIT and Lincola Lab Moncos Label # A37396

FOLDER 1

11(

Memorandum 6M-3971 Division 6 - Lincoln Laboratory, MIT "Component Circuits for Digital - to - Analog Decoditions" author # H.E. Zieman 7/11/55

- Memonaudum 6M-3984 EE Dept. Master's Thesis Proposai 11/9/55 author. L. Jedynak "Circuit Application of the Avalanche Phenomenon in Inchom Transistons"

Memonaudum 6M-4035 "TRANSISTON GINCUITS COURSE. Number 5. Thermal Stability of TRANSISTORS' author D. ECK/ 12/2/55

Meno 6M-4062 "Design and Static Analysis of Emitter - Follower Inverter Combination" Andrew altrox T.H. Mersling 12/19/55

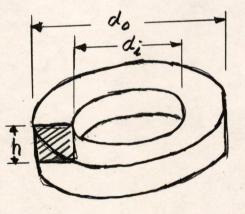

Memo 6M-4089 "Geometry of Magnetic Memory Elements" authon J. Childress 1/18/56

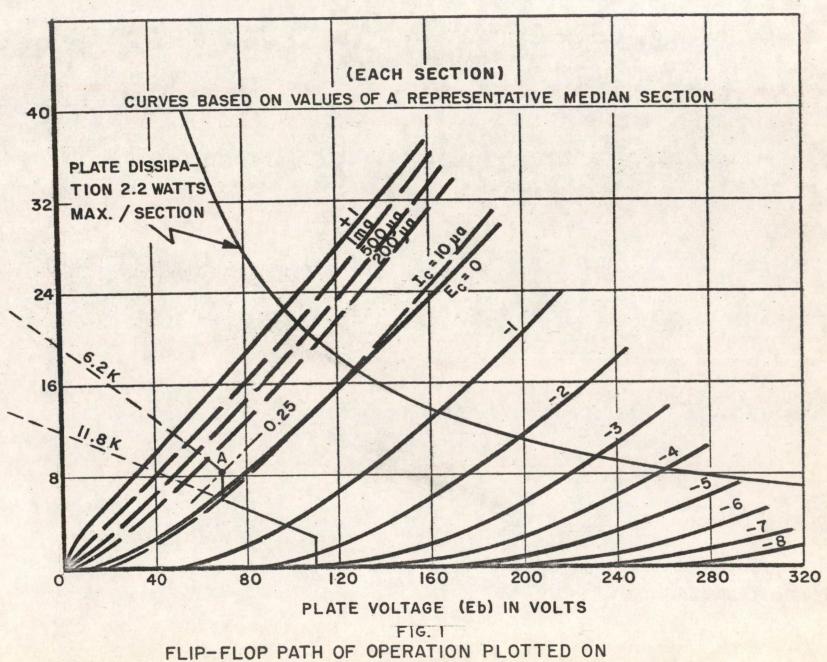

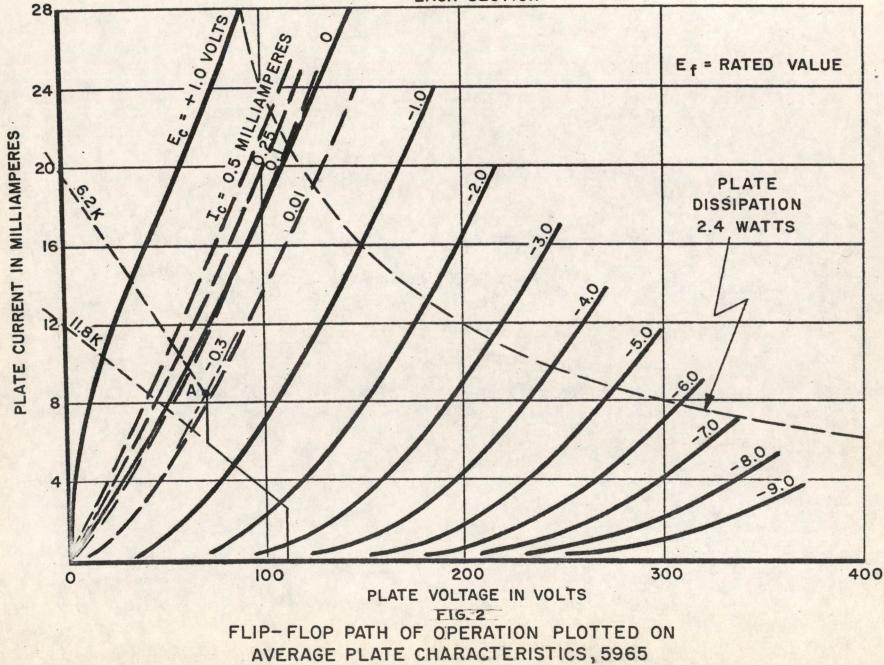

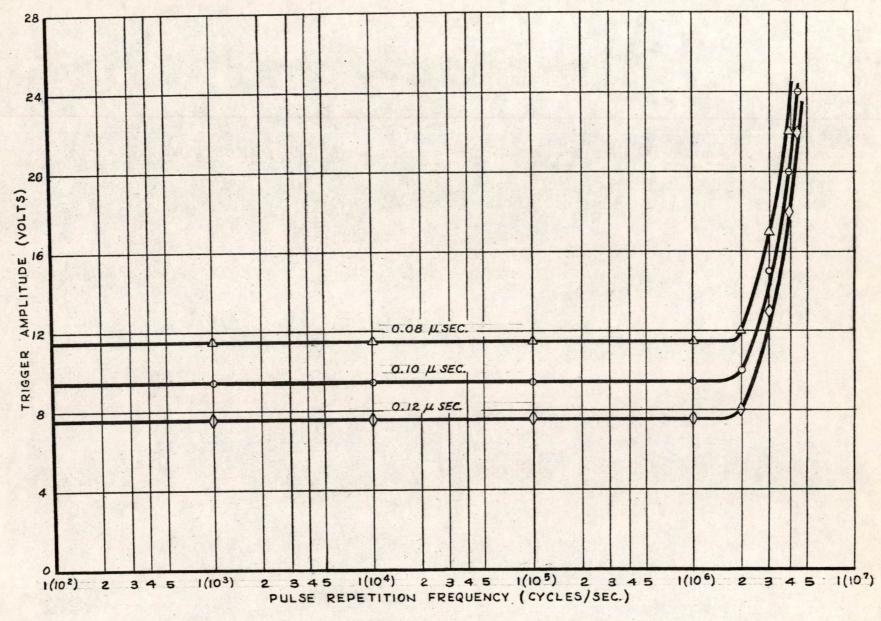

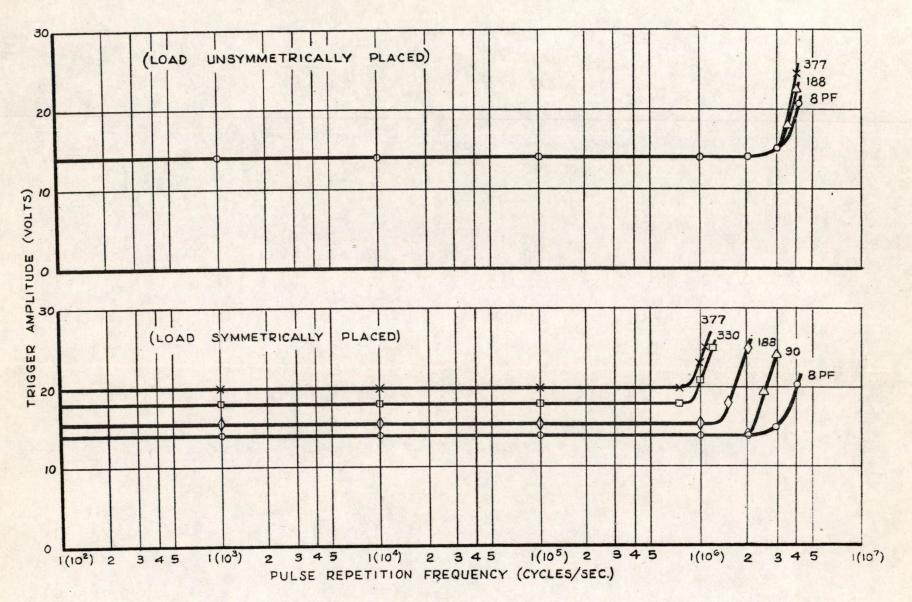

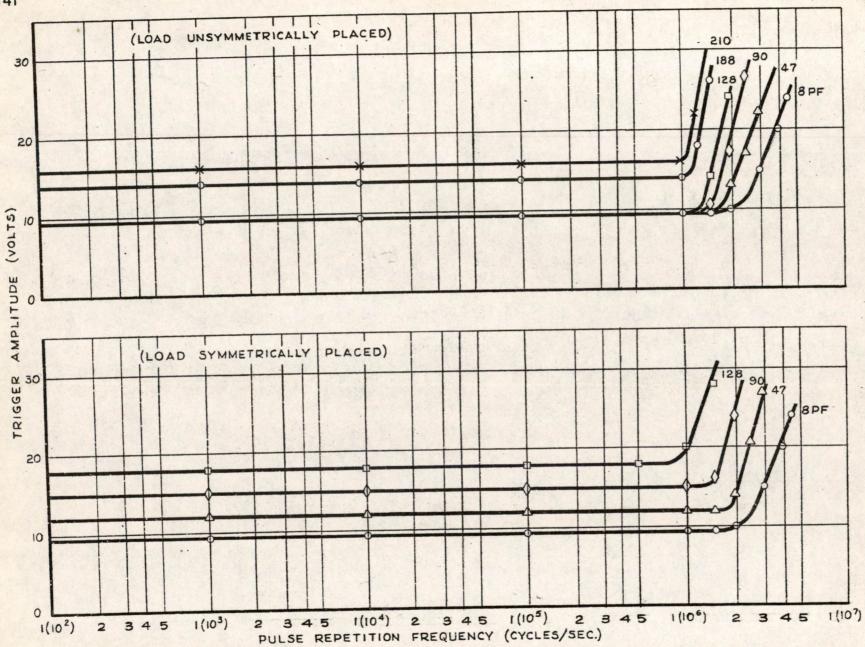

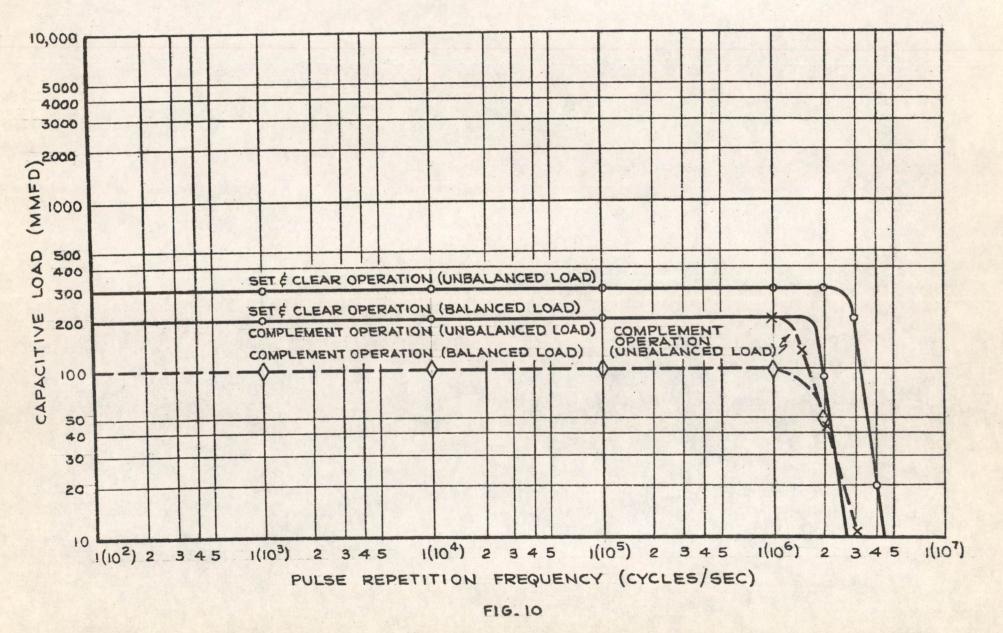

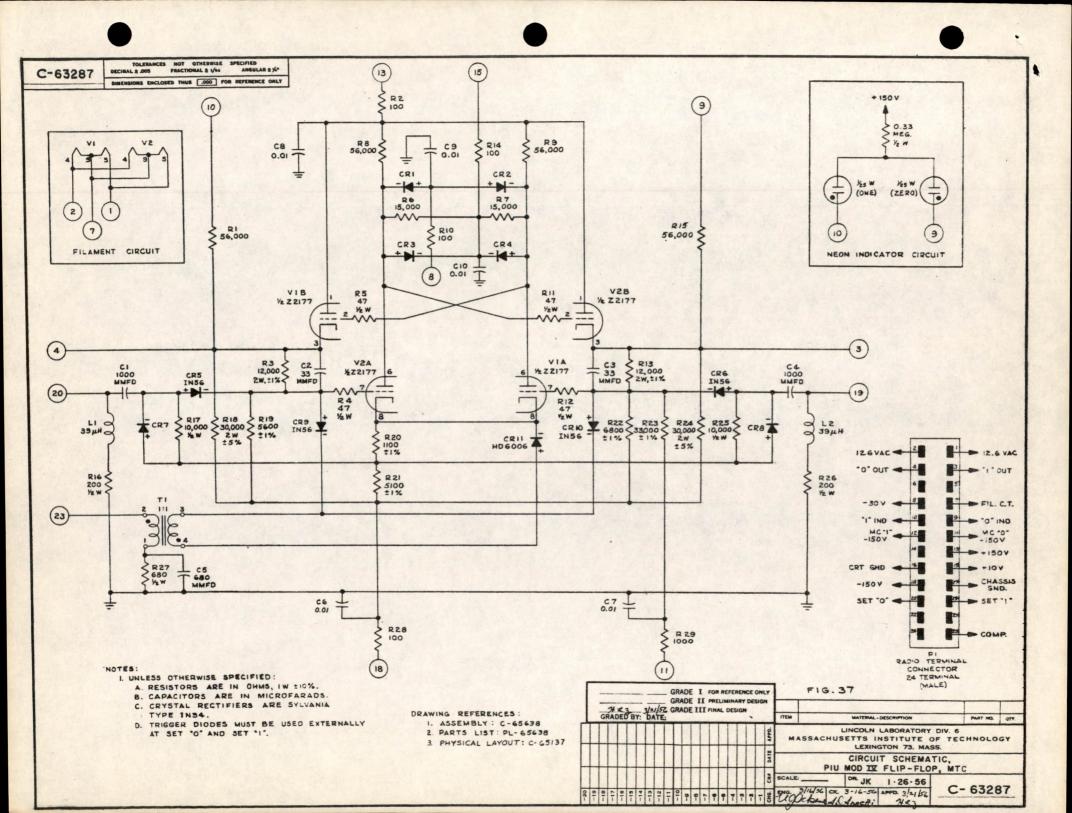

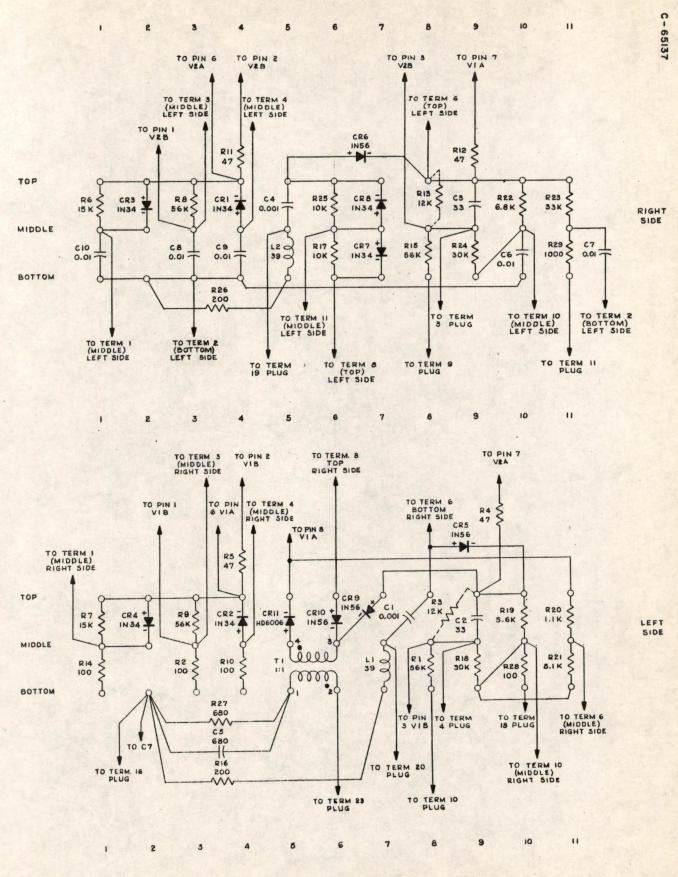

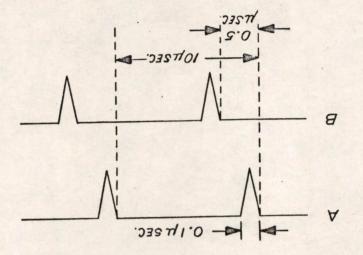

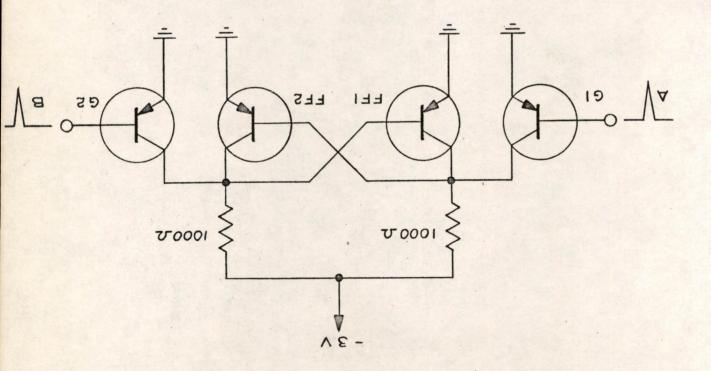

- Meno 6M-4109 "High Speed Frip Flop" (Mic Meder IV) author N. Ockene 310100

FOLDER 2 Box -# A37396

- Menio 6M-4110 "Surface Backier Transiston Life Tests" author D. Eckl + R. Bucke 12/14/55

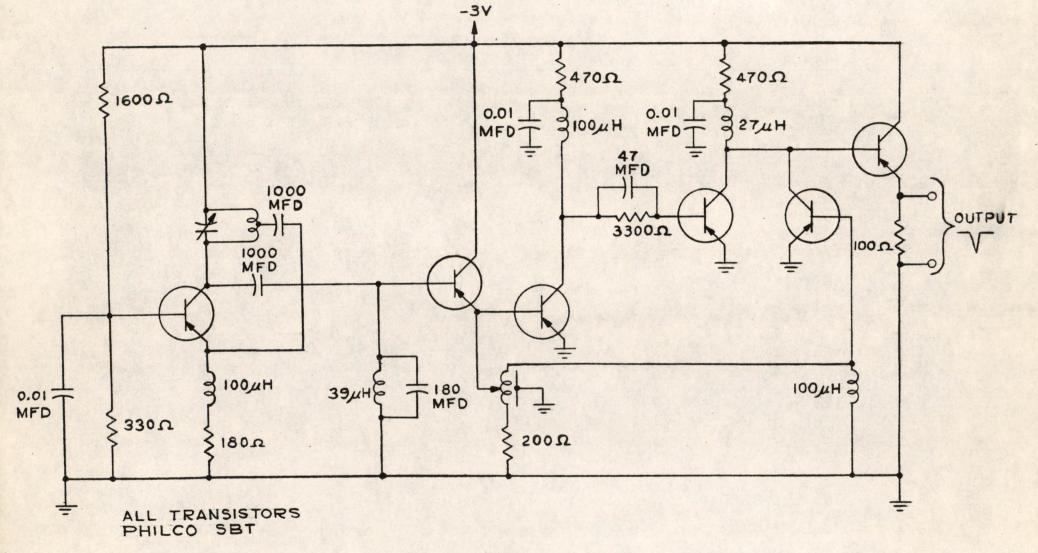

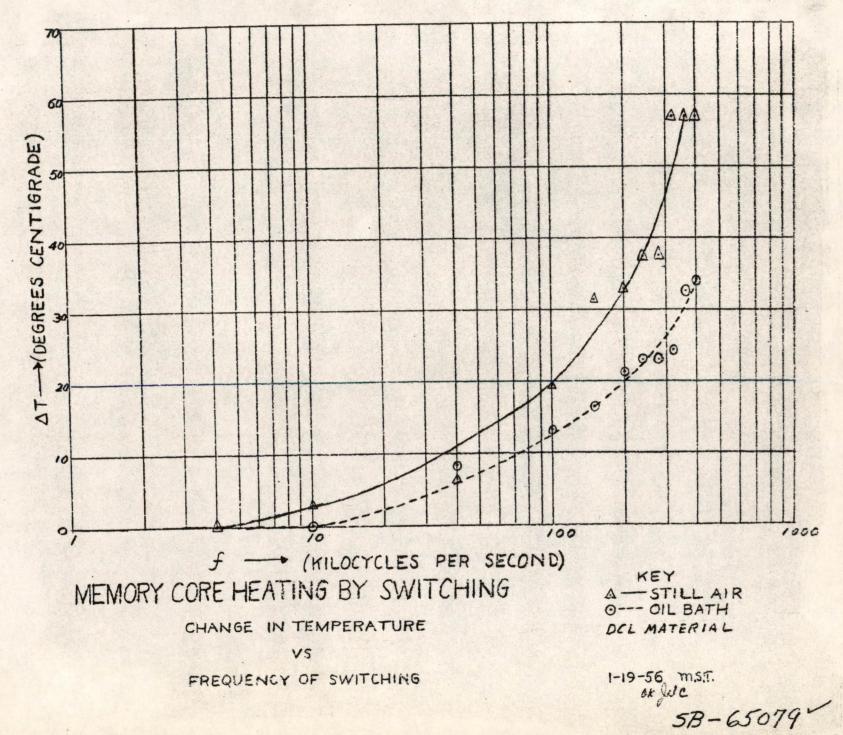

- Meno 6M-437 "Menory Obe Heating by Switching at High Frequencies" Outhor J. Childress 1/31/56

- Menno 6M-4155 Master's Thesis Proposal, K. Konkle 2/10/56 "Hole Storage us'a Satraated found-Emitter Transiston Grevit"

- Meno 641-4218 "A Sequential Access Three Microsecoud Coxe Memory" author R. Best and T. Meisling 3/8/56

- Merro 6M-4239 "Some Characteristics of the Western Flootnic GA 52830 (M-2012) Medium Power TRANSISTOR" author 6. Davidson 5/16/56

- Menio 6M-4283 "Centralized Probe System" author W. Santelmann Jr + A. Hingston 6/22/56

FOLDER 3

PPPP

4

77

T T

-

-

-0

-

T

1

- Memo 6M-4472 Repsonne l'List Div. 6 Lincoln Lab. 8/1/57

Memo 6M-4500 " A Project for The Strady of Seif Organizing Data Processing Systems" author B. Farley 5/1/56

Folder 3, Cont Box # A37396

- Menio 614-4303 "Parameters of The GE 2NI36 PNP Alloyed Junction Transiston " author D. Eakl 4/23/56 - Meno 6M-4324 "Syllabors for the SAGE Faun hauzahon Course 25-29 June 1956 " author A. Hill 5/21/50 - Meno 6M-4356 " An Agoroach to Reliabolity Analysis" arther M. Epstein 5/29/56 - Menio 6M - 4390 "Heat Dissipator Characteristics" arthon E. At Cohler 7/9/56 - Meno 6M-4394 ' Proposed Visual Unlity Equipment for Mile " authon R. Mayer 7/9/56 - Meno 6M-4409 Master's Them's Proposal by M. Cerier "Frequency Dependence of FERFILES at Malenate Field Intensities" 7/25/58 Folder 4 - Memo 6M-4521 "A La Place Transform Analysis of Polse Beta" R. Johnston 8/21/57 - Memo 6M-4544 "Electronically Variable Power Sypply" E. Cohler 4/30/56

- Folder 5

- Meno 6M-4583 " A Printed Wire Menory Plane E. Guditz Tholsto

Folder 5, cont

Box # A37396

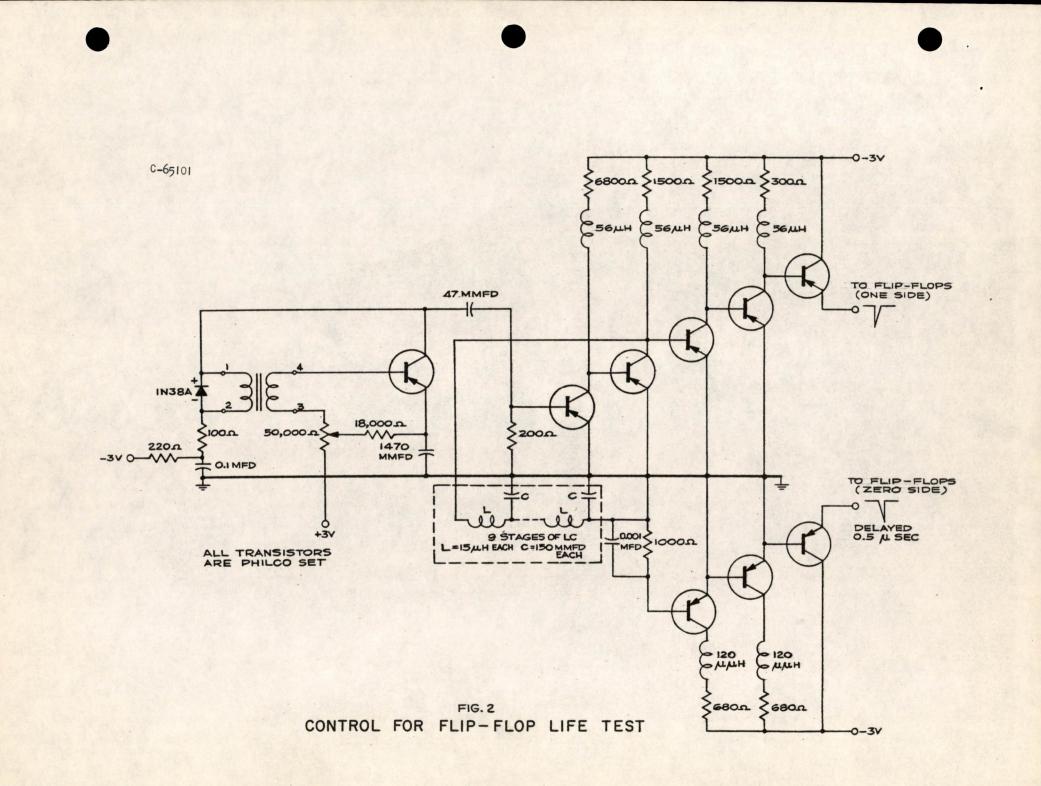

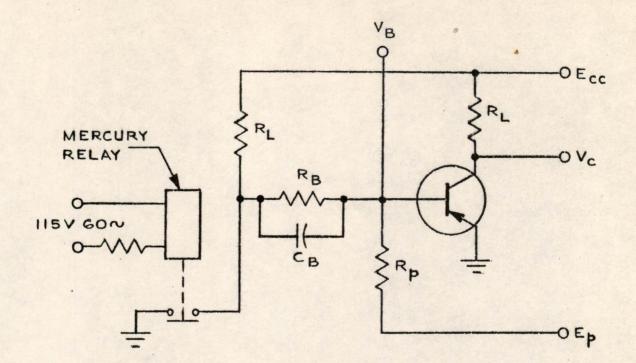

- Menno 6M-4561 "TX-0 Circuitry" J. Fadiman 10/22/56 (3 Copres)

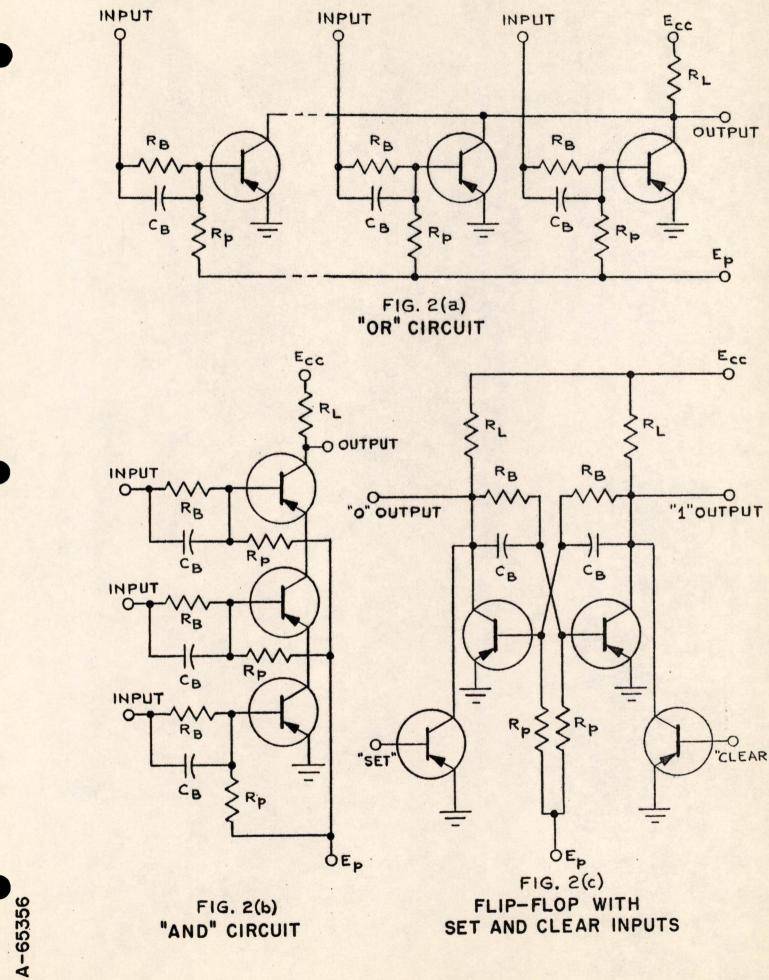

Menno 6M-4571 "Treasistory Logic in TX-0" R. Jeffrey 9/5/56 (3 copies (3 copies)

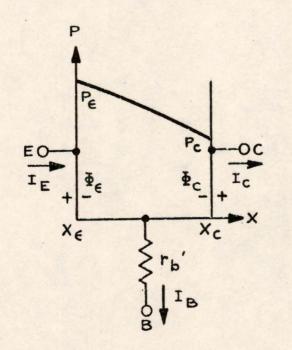

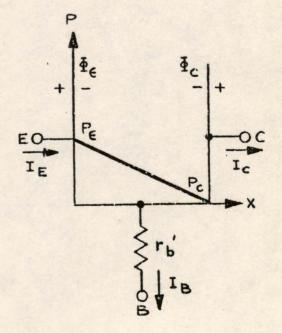

Menco 6M - 4581 "Some Notes on the Theory and Design of Alley Juncton Transiston's for Sunteling Purposes" C. KIRK \$1 9/28/56

FOIDER 6

- Menuo 6A1-4700 "A Proposal fon Training youngsters in Digital Comprising Techniques" R. Mayer 9/18/56

- Memo 6M-4713 "Lincohn TY-2 Compiter" K. Olsen + W. Clark 9/25/56

Meno 6M-4764 "Results of Investigations to Improve Reliability of the MIC Tape System" T. Stockebrand 11/5/56

- Menio 6M-4774 "Magnetic Auplifiers" S. Coffin 12/12/56

- Memo 6M-4774-SI "Magnetic Amphiers' S action (Syptement) 2/4/57

Folder 6, Cout. Box # \$ 37396 - Meno 6 M- 4774 - 52 "Magnetic Amplifiers" S. Coffin 4-3-57 (Sygptoment) - Momo 6M - 4785 "A Transistonized Sensing Amplifier for the 256 × 256 Core Memory " & S. Bradspies 11/14/56 (2 Copies) 5 Alexo 5644 54585 Folder 7 - Meno 6M-4789 "A Funchenal Description of the TX-0 Computer" J. Gimode + H. Peterson 11/20/56 (2 copies) - Memo GM-4837 " Tremsient Response of Brift Transistors ( Engineer's Thesis Proposal) R. Johnston, 12/26/56 - Memo 6M-4851 "Automatic Tracking System Transfer Finishon" R. Bleier, N. Vassalotti "19/57 - Meno 6M-4870 "On The Behavior of Junchon Transistons in Suntching Circuits" 1/17/57 C. Kirk Jr. FOLDER 8 - Memo 6M-4874 " Speed of Flux Reversal with Ston Rise-Time Drive " S. Bradspies 1/21/57 - Memo 6M-4878 "Survey of Photo Electric Elements" J. Downing 1/23/57 - Meno 6M-4913 "Transient Response of Juncher Transistons - [" R. Johnston atorts 2/21/57

TW

PPPPPPP

44

4

-

77

-0

-0

-

\_

7

Folder & Cont. Box # A 37396 Meno 614-4913, 5-1 "Transvent Response of Junchon Transistons - TT " R. Johnston 6/19/57 - Memo 64-4955 " Parameter Distributions for the Philco L-SIZZ Surface Barner Transiston " 3/19/57 D. Eekl Menue 6M-4956 "Selective Masking" G. Heidler 4/9/57 FOLDER 9 Meno 6M-4789 "A Finchonal Description of The TX-0 Computer" J. Gilmone, H. Breason 11/20/56 Meno 6M-4968 " The Lincoh TX-2 Compler" 4/1/57 W. Clark, J. Frankovich, H. Peterson, J. Fongie, R. Best, K. Olsen Memo 6M-5097 " TX-0 Derect Inport Utility Systen" J. Gilmore 4/10/57 Meneo 64 - 5780 " Some Examples of 7X-2 Programming" H. Peterson 7/23/58 FOLDER 10 Meno 6M-4963 "An Aspect - Coordination System for Subject Indexing Division 6 Decoments" M. Ferguson 3/25/57 614-4968 "The Lincoln TX-2 Compiter" Menco 41.150 62 010

T

\*\*

4

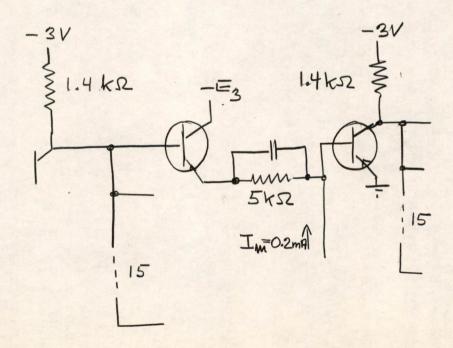

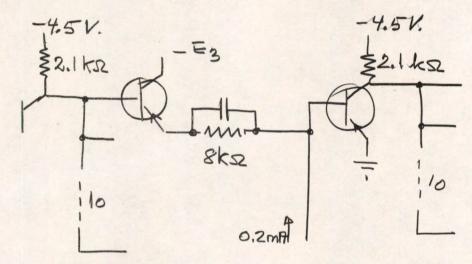

Bix # A 37 396 Folder 10, Cont. - Meno 6M-4983 ."Rake Earth Nichel Oxides" A. Wold 4/16/57 - Menio 6M-4987 " A Print - Wired Maquete Core Plane" E. Guditz 4/3/57 FOLDER 11 - Menio 6M-5090 "Test Equipment Committee Meeting 29 March 57" H. Hedgelon 3 4/22/57 - Mouro 6M-5097 "TX-O Direct light Uhility System" J. Silmore 4/10/57 - Meno 641-5151 "Three-Dimensional Etched Wiring" E. Guditz 5/29/57 - Memo 6M-SIII "Division 6 Accessions List - April 57" M. Fergeson 5/6/57 - Menio 611 - 5187 "Findamental Processes Soverning Stars Hole - Storage Phenomena ca Junction Transistoris" C. Kirk 8/26/57 Memo 6M-5191 "An Evolutionary Stidy of The Theory and Design of The L-5134 Switching Transistor - Past + Fitne" C. Kirk \$130/57 Mano 6M-5193 "Inverters and Flip-Flops Using L-5134 Transistons" 8/28/57 J. Langford

P D

Tolder 11, Conf Box # A37396 - Menio 6M-5199 " A Two Thansistor Flip Flop for The TX-2 Computer " R. Hughes 9/3/57 FOLDER 12 - Menus 611 - 5856 "Some Applications of 2N501 Transistors to Sustelling Circuits" J. Langford 8/29/58 - Mano 6M-5216 "A TRANSistorized Variable Delay Unit" L. Kleinkoch 9/12/57 - Menco 6M-5590 "TX-2 gared Rise Ampliper" L. Neumann 3/13/58 - Meno GM-5744 " Plated Electrical Connections" E. Giditz and S. Weiner 6/27/58 - Memo 611-5649 "Remote Display I" H. Zieman 6/2/58 Meno 611-5780 "Some Examples of TX-2 Programming" H. Peterson 7/23/58 FOLDER 13 Engreening Drawings - Assy, Composite, Schematic PIV, Decoder Power Unit, TX-2 " 8 Transistox Emitter Follower, TX-2 - Remote Display Fip Flop Plug In - Remote Display Blacking Oscillaton

Folder 13, Conf. # A37396 - Remote Display Inverter Picg - "" Sate Picg " Selector Driver - Circuit schenahe, power Room, power control purel TX-0 - Address Decide, 5 Memory, TX-2 - PiU Addien Decader, TX-2 Cascode and Cable Driver, TX-2 Series (8R) Inverter, TX-2 Series (8) Inverter, TX-2 Flexo Control Pauel, TX-O Block Schem. Schematic circuit, variable delay mit, TX-2 - Parity Gracuit, TX-2 - D.C. Power Supply TX-2 T (Man ) Memory, X+Y 2nd Level Deauders TX-2 - MTC Storage Control Bloch Schematic MTC A- Register AR - TMAR + TMAR X+Y 1st Level Decaders, 7X-2 - S (MAR) Register Digits 2.7-2.1 + 14-11 TX-2 S Memory Addien Decoder Digits 2.7-1.9 + 1.4-1.1, TX-2 S Memory " " 1.8-1.5 TX-2 S Memory - Position Decoder TX-2 FOLDER 14 Engineering Drawings - Pauallel (7) Inverter TX-2 - Memory Selector TX-2 - Memory Read Driver B 7X-2

# A37396 Folder 14, cont - Memory Read Ampl. and Digit Driver TX-2 Proposed power syzoly for marginal sheet MTC Black Schematic MTC Alarm System, K MTC Accumulaton, AC TX-2 D Register Digital 0,12 3,4,5 6,7,8 - B Register, TX-2 A+ C Register, TX-2 Lincoln Transistorized Multiple Sequence Computer (LITMUS) TK-2 Numbering System TX-2 V Register "F" "T" 5 " Program Counter, TX-2 MTC Control Cycle, Read and Test Control, TK-0 X Reg. Par Count, TX-2 Cincuit Schematic, Display Decader, WWT Power Wotector, TX-2 Circuit Schem, Display Decader, UNIT - Array Driver Decader Output Amp WWI Togle Suster Storage, TX-0 - De Poner Supply TX-2

Folder 14, Cont. # A 37396 IBM Card Machines, Write Operation 1BM Section and 1/0 Control, alement Diagian Folder 15 Eng. Drawings Console. Selector Unit 1BM "Proposal for Block Symbols + Dagrams" 1BM Left Areithmetic Flement " One Digit Column li h n Circuit Schematic Register Driver Ko drausing "Snigle Digst Adder" Ko drausing "& Position Magnetic Matrix Susteh" 2/26/52 "Broching Oscillator Stepping Register" "Flox Current Plotter" 4/19/52 4 4 "Core Driving Flip Flop" 6/23/50 4 n "Sensing Amp, Coramic Array IT" 5/19/52 "Comme Mensony Array IT" 4/4/52 "Magnetic Matrix Smitch II (Alternate) 4/4/52 4 5 4 4 5

FFFFF

\*\*

-

£ \$

-

6 B

t t t

-

-9

-9

8

1666666666666666

R. L. Best

Page 1 of 31

Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SUBJECT: Component Circuits For Digital-To-Analog Decoders.

To: N. H. Taylor and Group 62

From: Henry E. Zieman

Date: July 11, 1955

Approved:

C. L. Cordorna

Abstract:

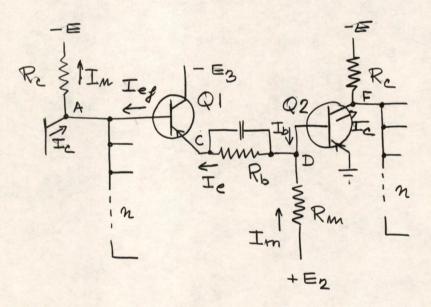

A digital-to-analog decoder is a circuit which converts digital information to a quantized voltage. The decoders discussed consist of four **basic** circuits: a voltage reference source, a constant current source, a current gate tube, and a decoder ladder. Each of these circuits is described in detail with typical operating values for the evaluation and maintenance of each circuit. Detailed analysis of a variably terminated push-pull decoder ladder is included showing the advantages of this ladder over the standard terminated single-sided ladder discussed by Walquist in R220. A second report (6M-3915) discusses three complete decoders in which these component circuits are used.

## 1.0 General

The

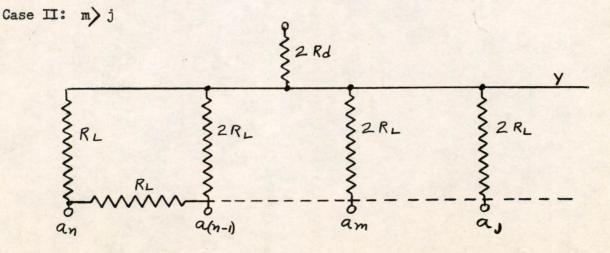

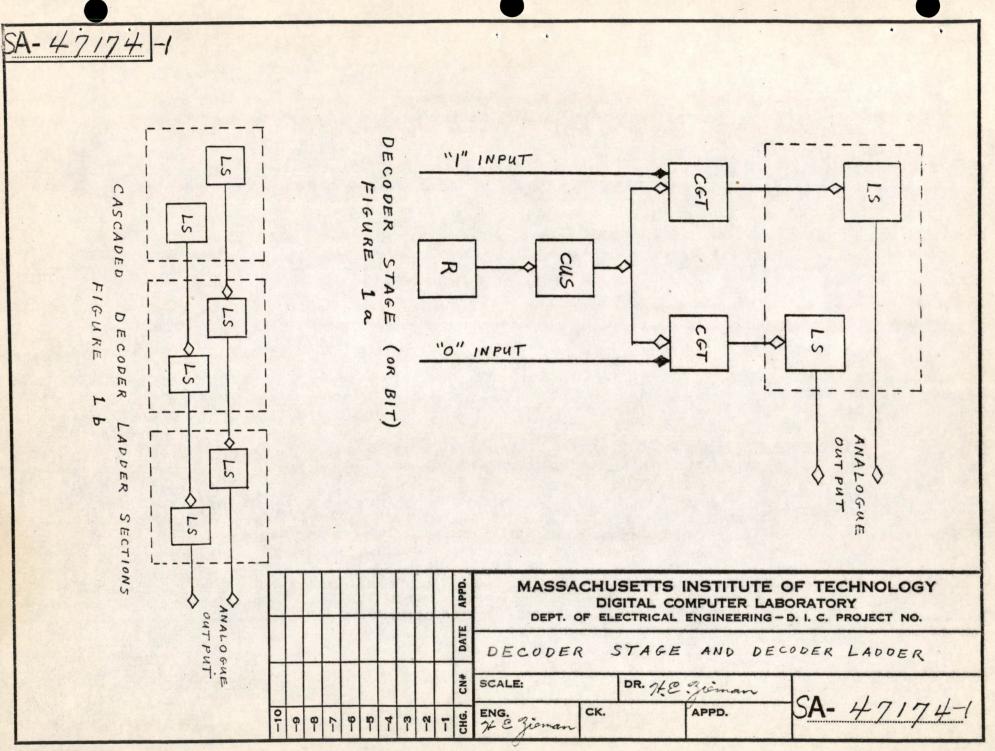

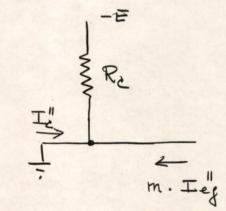

A Digital-To-Analog decoder is a circuit which transforms digital information in the form of flip-flop levels to a quantized analogue voltage which, through suitable amplification, can be used to deflect an electron beam in a cathode ray tube. Figure 1a (SA47174) shows a block diagram of a typical balanced decoder stage, or bit. Voltage reference source (R) acting on a current source ("CUs") produces a regulated source of current. This current can then be switched through either one of two current gate tubes ("CGT") into a ladder section ("IS") by an appropriate flip-flop level on the CGT input.

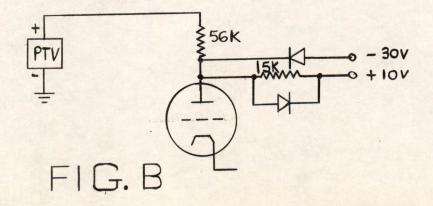

. The inputs to the two current gate tubes are connected to opposite sides of a single flip-flop. Thus one input will be at +10 volts while the other will be at -30 volts. The current gate tube whose input is at +10 volts will conduct current from the current source to the ladder section connected to it. The companion gate tube will be completely cut off.

This document is issued for internal distribution and use only by and for Lincoln Laboratory personnel. It should not be given or shown to any other individuals or groups without express authorization. It may not be reproduced in whole or in part without permission in writing from Lincoln Laboratory. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No. AF 19(122)-458.

#### Page 2 of 31

The ladder sections are resistive networks connected to a common supply voltage. As current passes through a ladder section, an output voltage is produced in this section in a negative direction from the supply voltage. Simultaneously the current in the companion ladder section is cut-off, and its output voltage approaches the supply voltage. If the output is taken across the output terminals of both ladder sections the output will be a push-pull signal whose amplitude is twice the swing of a single ladder section.

In a multi-stage decoder the various ladder sections are connected in series as shown in fig. 1b (SA47174). It will be shown that a property of this connection is to weigh the output of each individual section in a binary fashion. That is, for a given current flowing successively in sections 1, 2, and 3, section one will produce the greatest effect on the output, section two only one half the effect of section one, and section three only one quarter the effect of the first section.

#### 2.0 Specific Component Circuits

#### 2.1 Voltage Reference Source (R)

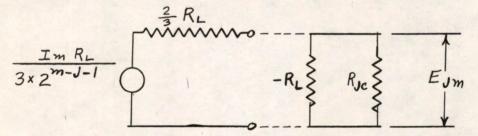

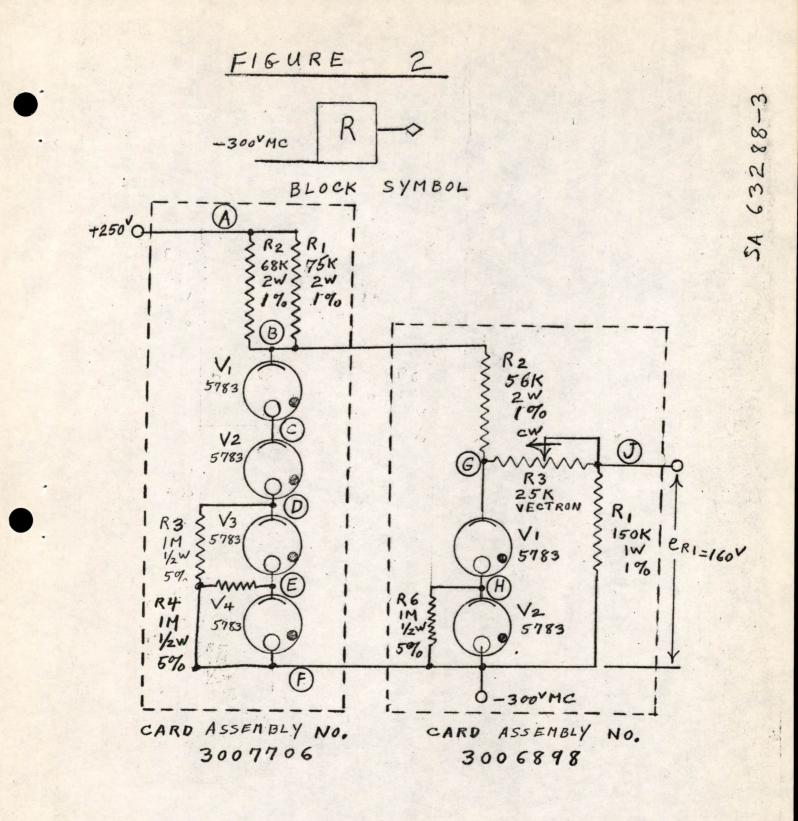

Figure 2 (SA63288) shows the block symbol and circuit diagram of the voltage reference source. Drawings 3006898, 3006899, 3007706, and 3007707 show the required card assemblies and details to make up the circuit.

The circuit on card assembly 3006898 functions as the primary voltage regulator and has a control pot (R3) which will permit setting the output of the circuit to 160 volts across R1, despite normal variations in the output voltage of the reference tubes  $V_1$  and  $V_2$  on this card. Because of manufacturing tolerances and aging the operating voltages at (H) will be  $86^{\circ} \pm 5^{\circ}$  referred to the -300v supply line, while point (G) will be  $172^{\circ} \pm 10^{\circ}$ . Thus for the extreme conditions on (G) the control pot can vary (R) between  $139^{\circ}$  to  $162^{\circ}$  and  $156^{\circ}$  to  $182^{\circ}$ . The  $160^{\circ}$  across R1 can therefore be realized at all times.

Card 3007706 functions as a secondary regulator to reduce variations in the supply voltages to card 3006898. In both circuits the IM 1/2W resistors are used to insure proper firing of the VR tubes. Table 2.1 gives pertinent data for the evaluation and maintenance of this circuit.

Page 3 of 31

Table 2.1a

Voltage Measurements (referred to ground)

| Point<br>A | <u>Voltage</u><br>+250 <sup>v</sup> ± 5 <sup>v</sup> | Point<br>F | <u>Voltage</u><br>-299 <sup>v</sup> ± 6 <sup>v</sup> |

|------------|------------------------------------------------------|------------|------------------------------------------------------|

| В          | $+45^{v} \pm 18^{v}$                                 | G          | -127 <sup>v</sup> ± 11 <sup>v</sup>                  |

| С          | -41 <sup>v</sup> ± 15 <sup>v</sup>                   | н          | -213 <sup>v</sup> ± 9 <sup>v</sup>                   |

| D          | -127 <sup>v</sup> ± 12 <sup>v</sup>                  | J          | -139 ± 6 <sup>v</sup>                                |

| E          | -213 <sup>v</sup> ± 9 <sup>v</sup>                   |            |                                                      |

## Table 2.1b

4

# Component Loading

| Component<br>card 3006898 | <u>Voltage</u><br>(in volts) | Current ( in ma.)  | Max. Power<br>(in watts) |

|---------------------------|------------------------------|--------------------|--------------------------|

| R 150K 1w 1%              | 160                          | 1.07 <u>+</u> .01  | 0.173                    |

| R2 56K 2w 1%              | 172 ± 17                     | 3.08 ± .34         | 0.646                    |

| R <sub>3</sub> 25K pot    | 11 ± 5                       | 1.07 <u>+</u> .01  | 0.42 rating<br>required  |

| R <sub>6</sub> IM 1/2w 5% | 86 ± 3                       | .086 ± .007        | 0.0081                   |

| V1 5783 WA                | 86 ± 2                       | 2.01 ± .35         | 0.208                    |

| V2 5783 WA                | 86 ± 3                       | 1.93 ± .36         | 0.204                    |

| card 3007706              |                              |                    |                          |

| R1 75K 2W 1%              | 205 ± 23                     | 2.73 ± .33         | 0.698                    |

| R2 68K 2W 1%              | 205 <u>+</u> 23              | 3.02 ± .37         | 0.773                    |

| R3 1 <sup>M</sup> 1/2W 5% | 172 ± 6                      | .172 ± .014        | 0.033                    |

| R4 1M 1/2W 5%             | 86 ± 3                       | .086 <u>+</u> .007 | 0.0081                   |

| V1 5783 WA                | 86 <u>+</u> 3                | 2.67 ± 1.04        | 0.330                    |

| V2 5783 WA                | 86 <u>+</u> 3                | 2.67 ± 1.04        | 0.330                    |

| V3 5783 WA                | 86 ± 3                       | 2.59 ± 1.05        | 0.324                    |

| V4 5783 WA                | 86 <u>+</u> 3                | 2.51 ± 1.06        | 0.325                    |

# Table 2.1c

| Power Supply Requirments |       |

|--------------------------|-------|

| Voltage Current          | Power |

| +250 5.75 ± .70ma        | 1.44w |

| -300 5.75 ± .70ma        | 1.73W |

### Page 4 of 31

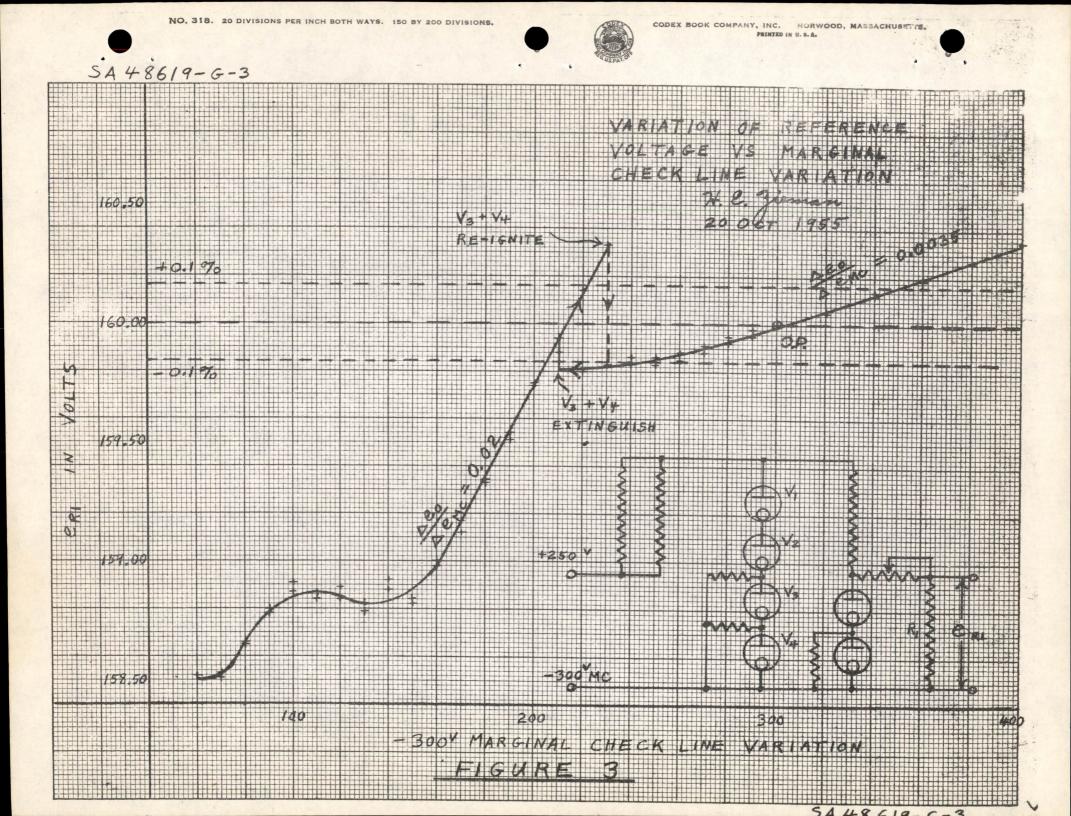

Figure 3 (SA 48619-G) shows the behaviour of this circuit as the -300 marginal check line is varied. It will be noticed that the output across R<sub>1</sub> remains within 0.1 % while the marginal check line is varied from  $-300^{\circ} \pm 31^{\circ}$ . In this region the output varies at a rate of  $.01^{\circ}/_{\circ}$  for every  $1^{\circ}/_{\circ}$  change of the marginal check voltage. This gives a transfer function Deo/Demc= 0.00355=K1. This value of K1 also holds for low frequency noise in either the -300V line or the +250V line. As the  $-300^{V}$  in the further reduced, the current through V3 and V4 on the card 3007706 is eventually reduced to a point where the tubes can no longer sustain conduction. This has occurred in the circuit under test at -197". Beyond this point the output varies at a rate of .05% of for each  $1^{\circ}/_{\circ}$  change in the -300<sup>v</sup> line, giving a transfer function  $\Delta e_{\circ}/\Delta e_{\rm emc} = 0.0265$ . Once Va has been extinguished, the marginal check line must be returned beyond the point at which V2 extinguished before sufficient voltage is available to re-ignite V3. In the circuit under test this occurred at -230V. It is to be understood that the variations on this MC line are not intended to marginal check this circuit. The variation will be used to marginal check the current source tubes. Hence, this study is intended to check whether the reference is sufficiently constant for the marginal check to be a valid indication of failure of the current source tubes. The only indication of failure of this circuit is the inability to adjust eRI to 160V. This voltage will have to be checked periodically and when the range of adjustment on R1 becomes critically small the circuit should be removed from service and repaired.

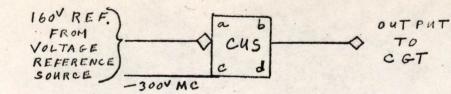

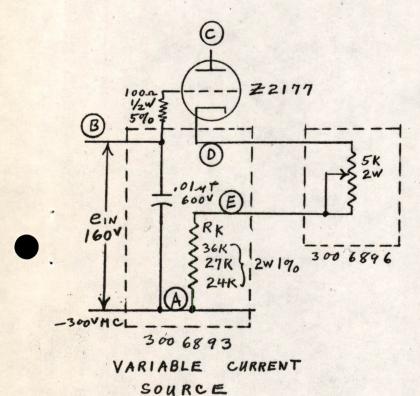

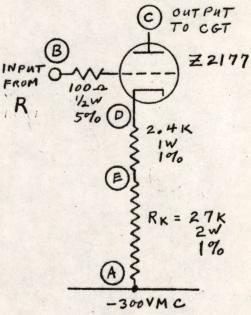

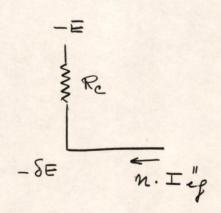

## 2.2 <u>Current Source Circuit</u> (CU<sub>S</sub>)

Figure 4 (SA 63702) shows the block symbol and circuit diagram of the current source circuit. Drawings 3006893, 3006894, 3006896, 3006897, 3006908, 3006913, 3006914 shows the necessary card details and assemblies to make up the circuit with its necessary variations.

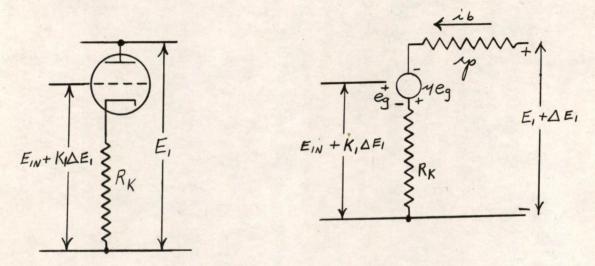

The constant current source is essentially a cathode follower with a fixed voltage applied to its grid. By definition a constant current source will supply a fixed current despite variations in load voltage. Therefore, a figure of merit for a constant current source is its dynamic output impedance (or equivalent resistance)  $\Delta eo/\Delta io$  (in conjuction with the voltage reference source). It can be shown for this circuit (see Appendix A) that

$$Req = \underline{Aeb} = \underline{rp} + (\underline{H+1}) \underline{Rk} \qquad eq 2.21$$

From this equation it can be seen that for a given change in output voltage, Req should be as high as possible to minimize the change in current.

$$\Delta ib = \underline{\Delta eb}_{Req} = \underline{\Delta eb} (1 + \underline{M}K1)_{rp} + (\mu+1) R_{k}$$

A quantity which is related to the circuit equivalent resistance is the circuit equivalent voltage. For this circuit

$$E eq = ib Req eq. 2.22$$

#### Page 5 of 31

Considering equations 2.21 and 2.22 it is found that the circuit is optimized by making  $R_k$  as large as possible. However, rise time considerations in the later circuits will limit the size of  $R_k$  if the available minus supply voltage is fixed. These considerations have dictated that the cathode resistance should be about 30K. Therefore, a current source with a 27K cathode resistor in series with a 5K variable resistor is considered a unity current source. In certain special decoders two additional values of current are required: one to give 1 1/8 unity current and a second to give 3/4 unity current. These are obtained by changing the fixed 27K cathode resistor to 24K and 36K respectively.

In each decoder one current source has a fixed 2.4K resistor in series with the 27K resistor (RK). This current source is then considered a reference current source and all other current sources can be adjusted with the 5K pot to give the same current as the reference current source, or the required proportionate amount. This adjustment is most easily carried out by connecting one side of a sensitive voltmeter to point E on the reference current source and the second side to point E on the variable current source under adjustment; then adjusting the pot until the voltage reads zero. This guarantees that the voltage across each Rk is equal, and since these are 1% resistors the current through the variable current source is within 20/o of that in the reference current source. To adjust these currents more accurately a special procedure will be needed to emphasize any inaccurracies in adjustment, and final trimming will have to be made by comparing the decoder output to a very accurate calibration signal. This procedure will be written up in more detail in an IBM Technical Report by J. Seeland.

From section 2.1 we have  $K_1 = 0.0035$  for variations in the  $-300^{V_1}$ line, and  $K_1 = 0$  for variations in the +10 volt level of the plate. Using these and the above values for  $R_k$  and the following values for tube parameters  $\mu=46$ , rp=10k, we get two sets of values for R eq and E eq. These values plus other pertinent data for the evaluation and maintenance of this circuit are presented in table 2.2.

#### Table 2.2a

| Voltage Me | asurements                 | (Fig 4) | and the second             |

|------------|----------------------------|---------|----------------------------|

| Points     | <u>Voltage</u><br>in volts | Point   | <u>Voltage</u><br>in volts |

| A          | -298 <u>+</u> 6            | D       | -138 ± 7 <sup>v</sup>      |

| в          | -139 <u>+</u> 6            | E       | -150 ± 7♥                  |

| С          | +10 +4                     |         |                            |

## Page 6 of 31

## Table 2.2b

Component Loading

| <u>Component</u><br>Unit current<br>source      | <u>Voltage</u><br>in volts      | <u>Current</u><br>in ma. | <u>Max Power</u><br>in watts |

|-------------------------------------------------|---------------------------------|--------------------------|------------------------------|

| $RK = 27K2W1^{\circ}/_{\circ}$                  | 148 <u>+</u> 1                  | 5.485 ± .095             | 0.83                         |

| R2 = 2.4K 1W1%                                  | 13.2 <u>+</u> .3                | 5.485 ± .095             | 0.074                        |

| $R_2 = 5K$ Pot                                  | 13.2 <u>+</u> 2.3               | 5.485 ± .095             | 0.16 (required)              |

| V <sub>7</sub> = <b>2</b> 2177                  | 148 <u>+</u> 9                  | 5.485 ± .095             | 0.88                         |

| eg = (bogey bias)                               | 1.8 <sup>V</sup> minimum gm = 2 | 28°/o of bogey           |                              |

| 3/4 current source                              |                                 |                          |                              |

| $R_{\rm k} = 36 \text{K2W } 1^{\circ}/_{\circ}$ | 148 <u>+</u> 1                  | 4.115 ± .065             | 0.63                         |

| $R_2 = 5K$ Pot                                  | 13.2 ± 2.3                      | 4.115 ± .065             | 0.09 (required)              |

| V <sub>1</sub> = Z2177                          | 148 ± 9                         | 4.115 ± .065             | 0.66                         |

| eg (bogey bias)                                 | 2.1 minimum gm = 2              | 21°/o of bogey           |                              |

| 1 1/8 current source                            | e                               |                          |                              |

| $R_{k} = 24k \ 2w \ 1^{\circ}/o$                | 148 <u>+</u> 1                  | 6.17 ± .11               | 0.94                         |

| $R_2 = 5k$ Pot                                  | 13.2 <u>+</u> 2.3               | 6.17 ± .11               | 0.2 (required)               |

| V <sub>1</sub> = Z2177                          | 148 <u>+</u> 9                  | 6.17 <u>+</u> .11        | 0.99                         |

| eg (bogey bias)                                 | 1.7 <sup>V</sup> minimum gm = 3 | 31º/o og bogey           |                              |

# Table 2.2c

Power Supply Requirements

+250<sup>V</sup> (indirectly)  $\alpha$  4.12 ±.06 ma, 5.48 ±.1 ma, 6.17 ±.11 ma -300<sup>V</sup>  $\alpha$  4.12 ± .06 ma, 5.48 ± .1 ma, 6.17 ± .11 ma 6.3<sup>V</sup> AC  $\alpha$  .45 amp/2 current sources biased at -150<sup>V</sup>

## Table 2.2d

Transfer Functions

| Current Source                     | -300 <sup>V</sup> line | 300 <sup>V</sup> line variations |                   | +10 <sup>v</sup> plate variations |  |

|------------------------------------|------------------------|----------------------------------|-------------------|-----------------------------------|--|

|                                    | Req<br>in megohms      | Eeq<br>in kilovolts              | Req<br>in megohms | Eeq<br>in kilovolts               |  |

| 3/4 = 4.115 ma                     | 1.44                   | 5.93                             | 1.80              | 7.50                              |  |

| 1 = 5.485  ma                      | 1.11                   | 6.00                             | 1.39              | 7.56                              |  |

| $1 \frac{1}{8} = 6.170 \text{ ma}$ | 1.00                   | 6.02                             | 1.25              | 7.58                              |  |

To insure proper operation of this current source it is important to insure that no grid current flows. Since the regulated current is actually the cathode current, any grid current which flows subtracts from the plate current. However, since the required regulated current is not the cathode current but the plate current, the grid current must be kept to a negligible quantity. In a Z2177 the grid current at zero bias is about 10  $\mu$ a. which is about 0.2  $^{O}/_{O}$  of the regulated plate current, but increases rapidly beyond this point. The zero bias point can therefore be used as a limit of operation. The other limit is determined by the maximum allowable plate voltage, which is 200 volts. Thus, the limits of operation on the plate with the marginal check at  $-300^{V}$  are  $+60^{V}$  to -95 volts for a bogey tube. The limits on the marginal check line, with the plate at  $+10^{V}$ , are  $-205^{V}$ to  $-360^{V}$ .

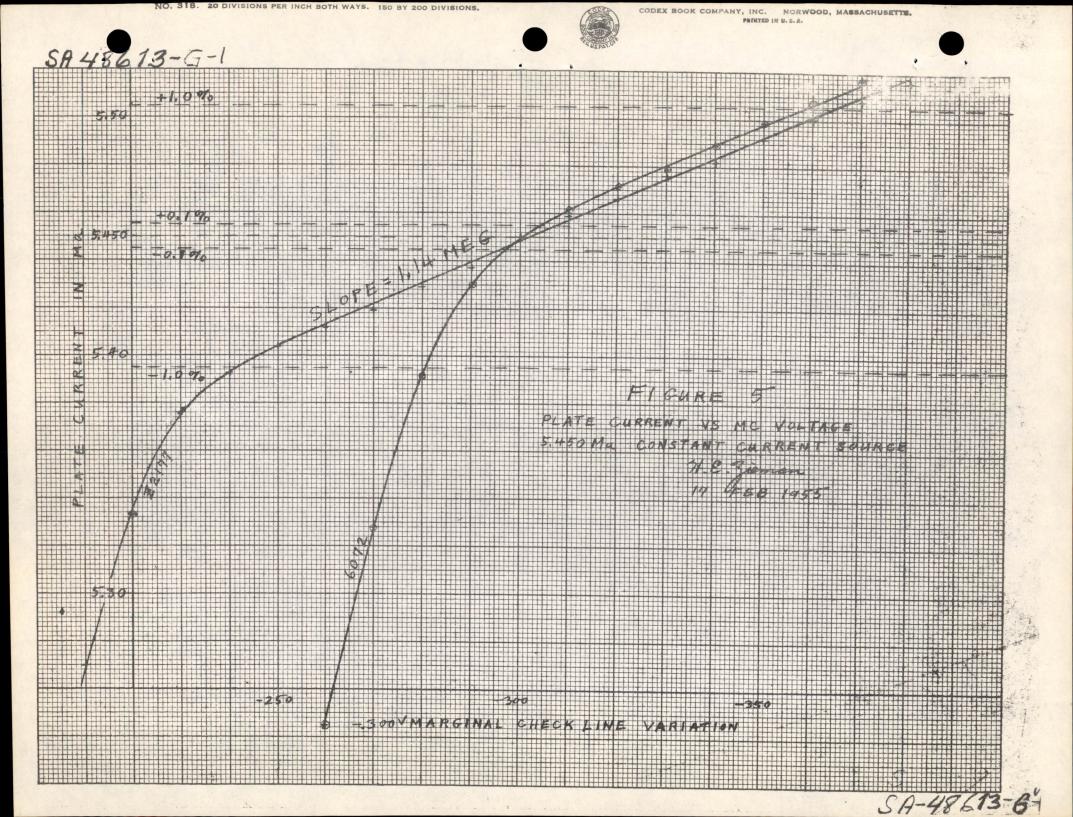

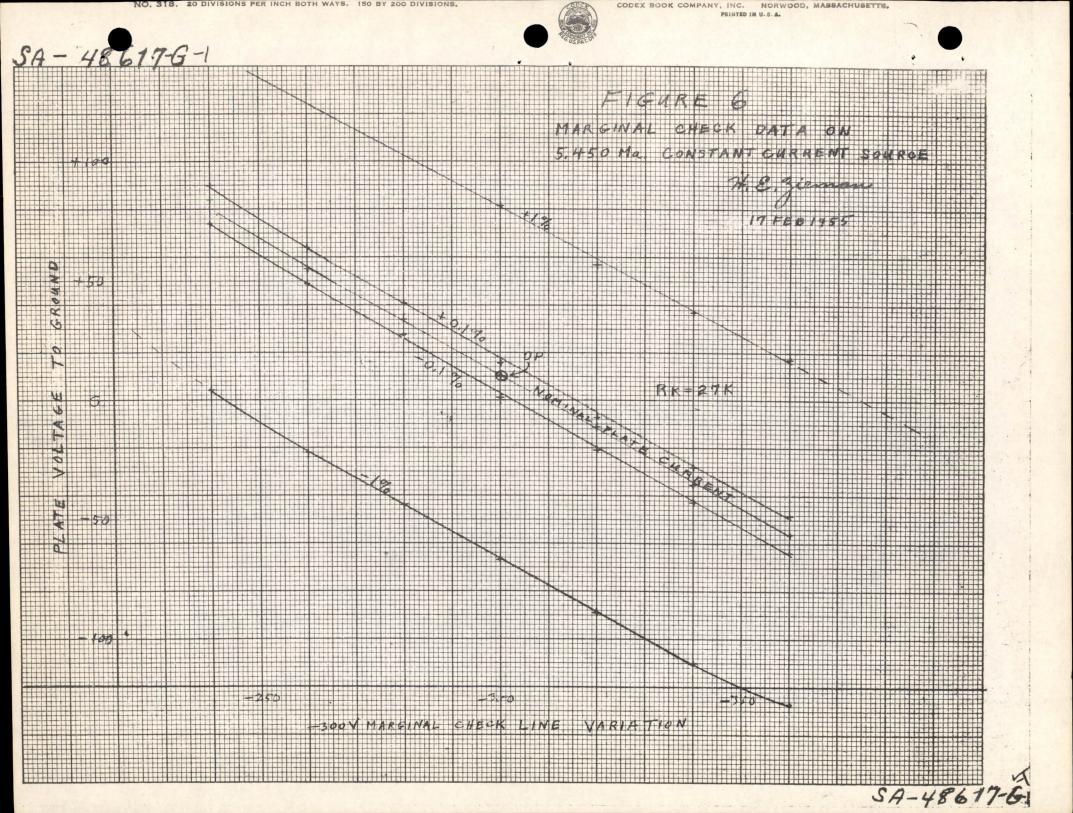

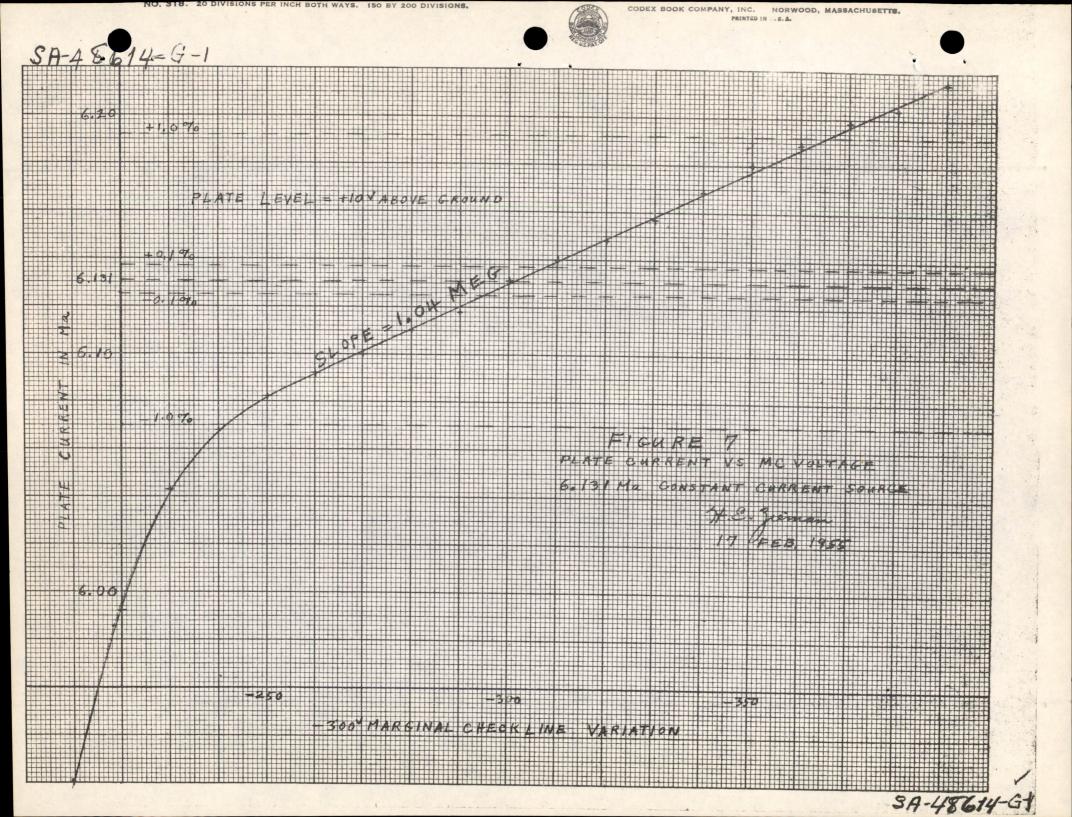

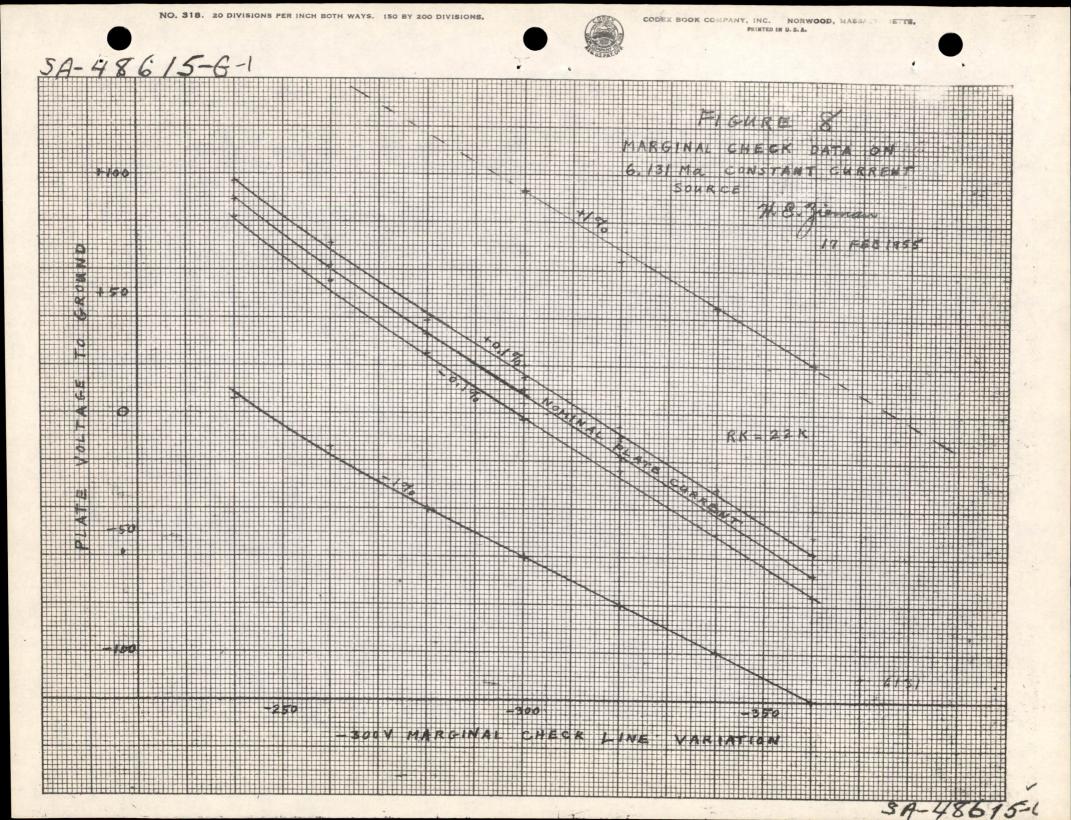

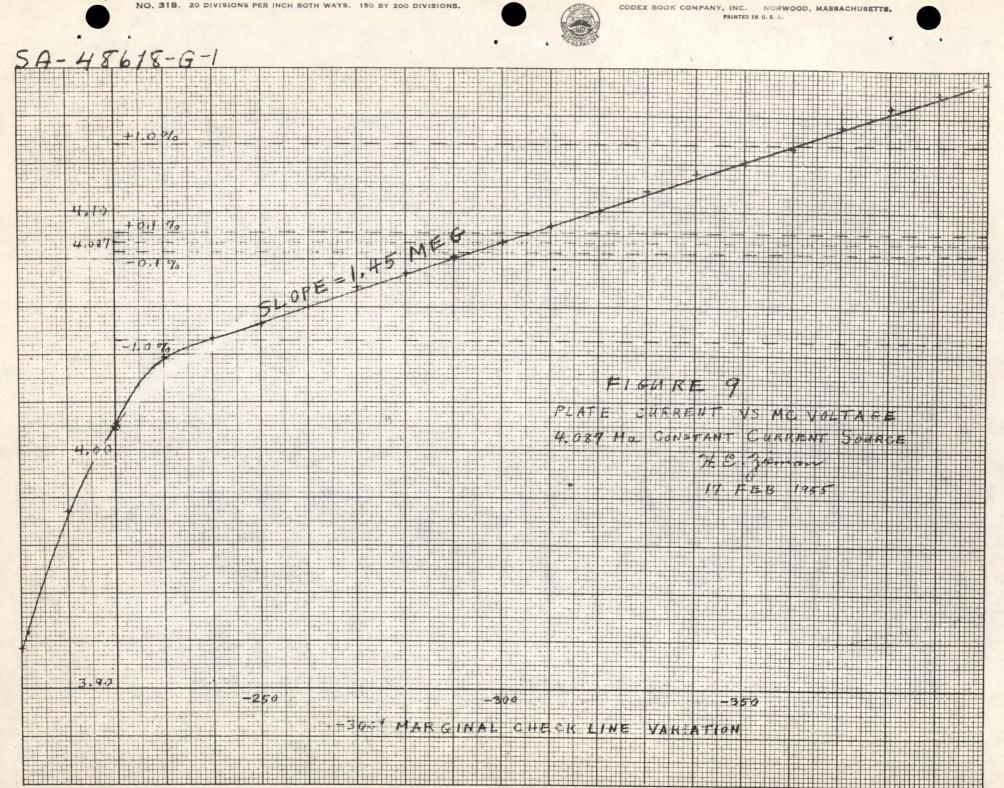

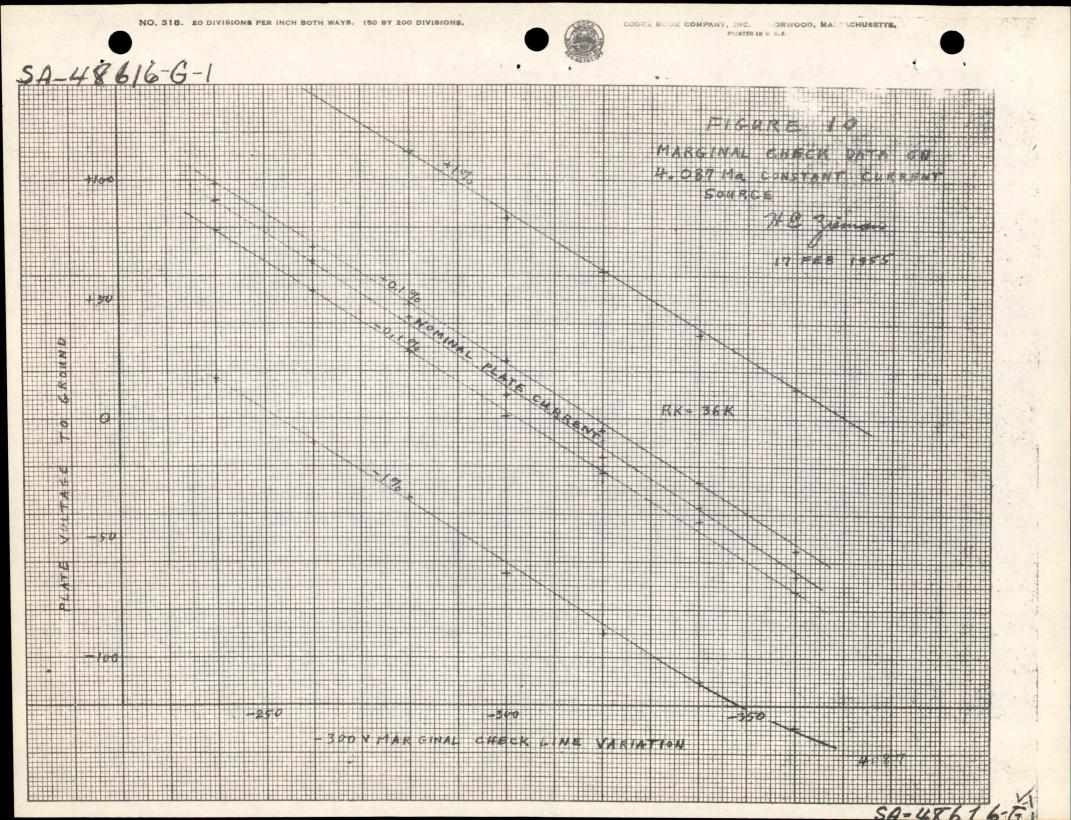

Figures 5, 6, 7, 8, 9, 10 (SA48613-G, SA48617-G, SA48614-G, SA48615-G. SA 48618-G, and SA 48616-G respectively) show the behavior of these various constant current sources as the -300<sup>v</sup> marginal check line is varied. Figures 5. 7. and 9 show the variation in the "constant" current of each source as the mc line is varied and the plate voltage is held constant at +10 volts. Figure 5 emphasizes the effect of a "down" tube by substituting for the Z2177 a 6072 which has approximately  $25^{\circ}/_{\circ}$  of the perveance of a Z2177. (25°/o of the plate current under same conditions of plate voltage and grid current.) Figures 6, 8 and 10 show the change in plate voltage necessary to maintain a constant current within given limits as the MC line is varied. It will be noticed in all of these cases that the current remains constant within  $0.1^{\circ}/_{\circ}$  for normal variations of the  $-300^{\vee}$  line (+6<sup> $\vee$ </sup>). Since variations of less than  $1^{\circ}/_{\circ}$  will not produce appreciably noticable effects in the display, the marginal check line will probably have to be raised 30 or 40 volts to pick out weak tubes. Assuming that the MC line is raised 30 volts the minimum perveance to cause failure would be  $27^{\circ}/_{\circ}$ , and  $36^{\circ}/_{\circ}$ , and  $40^{\circ}/_{\circ}$  respectively for the 3/4, 1, and 1 1/8 current sources. Thus, the 30 volt excursion would pick out tubes which are within 29% of failure under normal operating conditions.

Figures 5, 7, and 9 also show the effect of grid current. The increased slope in the plate current curve in the vicinity of -230 to -240 volts is caused by grid current replacing the plate current in the "constant" cathode current.

## 2.3 Current Gate Tube (CGT)

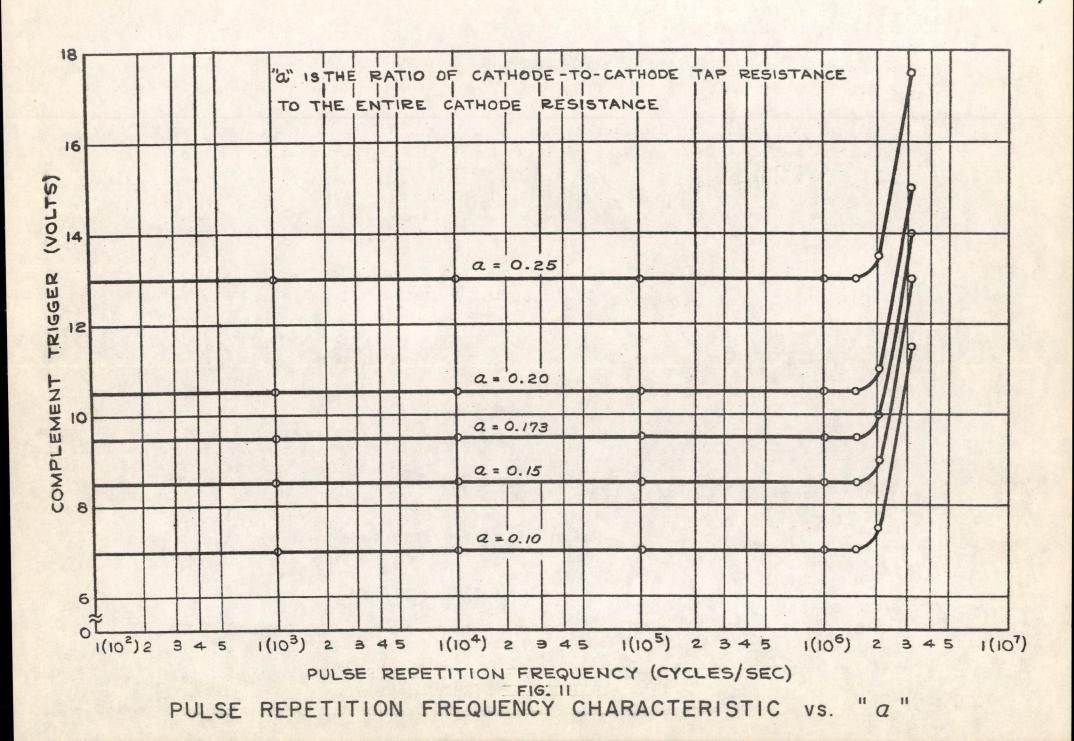

Figure 11 (SA 63717) shows the block symbol and circuit diagram of the current gate tube. Since the circuit contains only a tube and no other components, no special cards are needed for this circuit. However, the following card drawings show the necessary leads to make connections to this circuit: 3006893, 3006894, 3006908, 3006911.

#### Page 8 of 31

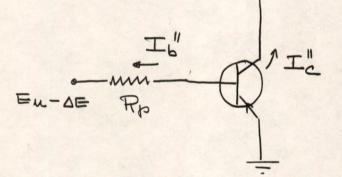

Two current gate tubes are always operated in parallel with their cathodes tied together to a constant current source. The constant surrent source requires that current must flow constantly from one CGT or the other, or both. If the grids were at exactly the same potential and if the tube characteristics were always identical then the current would split equally between these tubes. However, if these conditions cannot be guaranteed then the amount of current through each tube is indeterminate unless it can be guaranteed that no current flows through one tube. This is the case that is used by connecting the CGT's to opposite sides of a single flip-flop. In this case if we assume that point A (Fig. 11) is at +10 volts, then point D will be at  $-30^{\circ}$ . Under this condition Va will conduct and point B will be at +10V plus the necessary bias required by the voltage at point C and the current being conducted. In all cases point D will be at least 35 volts negative to B so that Vb will be completely cut off. The exact bias on Va cannot be specified because it depends on the voltage at C which, in turn, depends on the position of the CGT in a given ladder and on the number of bits which are simultaneously conducting. Curves are presented in section 2.4 which specify this voltage for several special cases. In general this variation will fall within the range of  $+150^{\circ} \pm 50^{\circ}$ .

The figure of merit for this circuit is similar to that of the constant current source: that is, a measure of the variation of "constant" current for various voltage inputs is required. Since the current source acts as buffer for variations in the  $-300^{V}$  line, and the current gate tube acts as a cathode-follower to the current source for flip-flop inputs, the equivalent resistance for this circuit to  $-300^{V}$  and  $+10^{V}$ variations is the same as for the current source, namely

$$R eq = (\mu+1) Rk + rp \qquad (eq 2.21)$$

$$1 + \mu K_1$$

where  $K_1 = 0.0035$  for  $+250^{v}$  and -300 variations and  $K_1 = 0$  for  $+10^{v}$  variations;  $\mu$ , rp, and  $R_k$  refer to the values of the current source feeding this current gate tube.

For variations in the plate voltage of the current gate tube we can use the above equation with  $R_k$  equal to the equivalent resistance of the current source to variations in the +10<sup>V</sup> level.

R eq =  $(\mu_1 \ \mu_2 + \mu_1 + \mu_2 + 1) \ R_k + (\mu_2 + 1) \ rp_1 + rp_2$  (eq 2.31) where  $\mu_1$ ,  $R_k$  refer to the values of the current source, and  $\mu_2$ ,  $rp_2$  refer to the values of the current gate tube. For  $\mu_1 = \mu_2$ ,  $rp_1 = rp_2$

$R eq = (\mu + 1)^2 R_{\mu} + (\mu + 2) rp$  (eq 2.32)

6M-3971

In Section 2.4 it is shown that noise on the  $+250^{\circ}$  line appears directly on the plates of the CGT. For these noise signals equation 2.32 must be modified to include the effect of this noise on the voltage reference source.

$$R eq = (\mu+1)^{2} Rk + (\mu+2) rp (eq 2.32a)$$

1 + \mu Kl

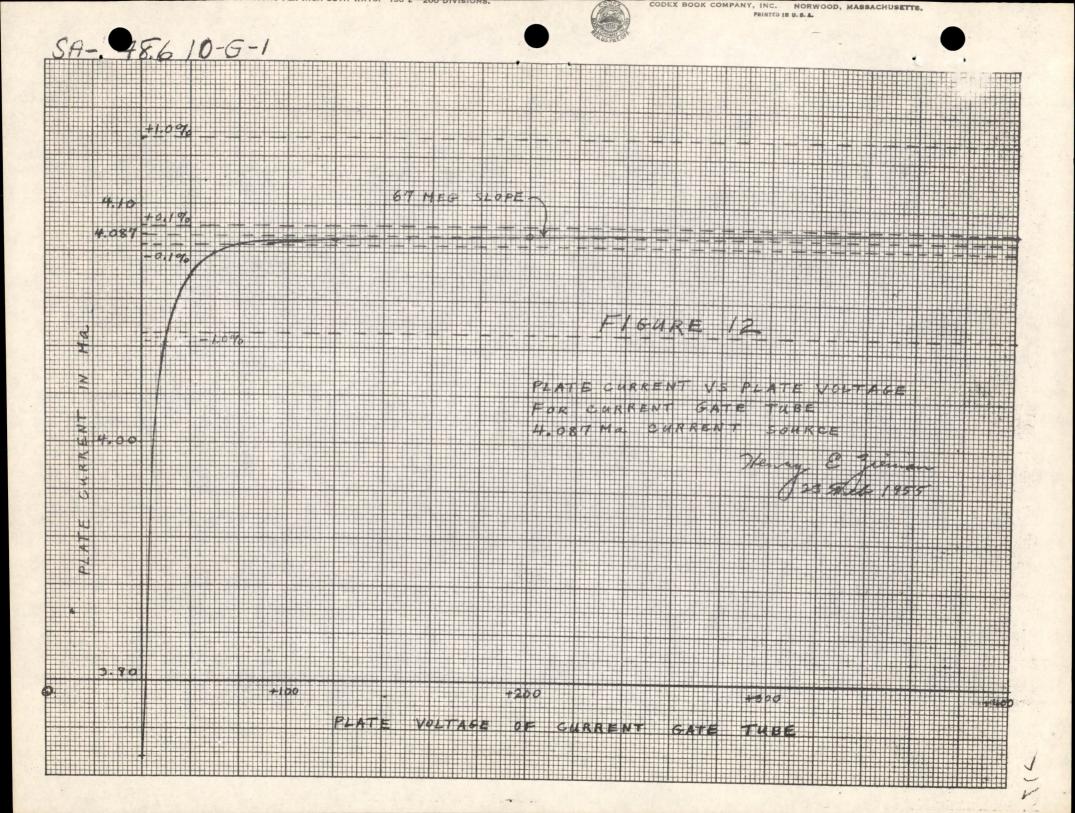

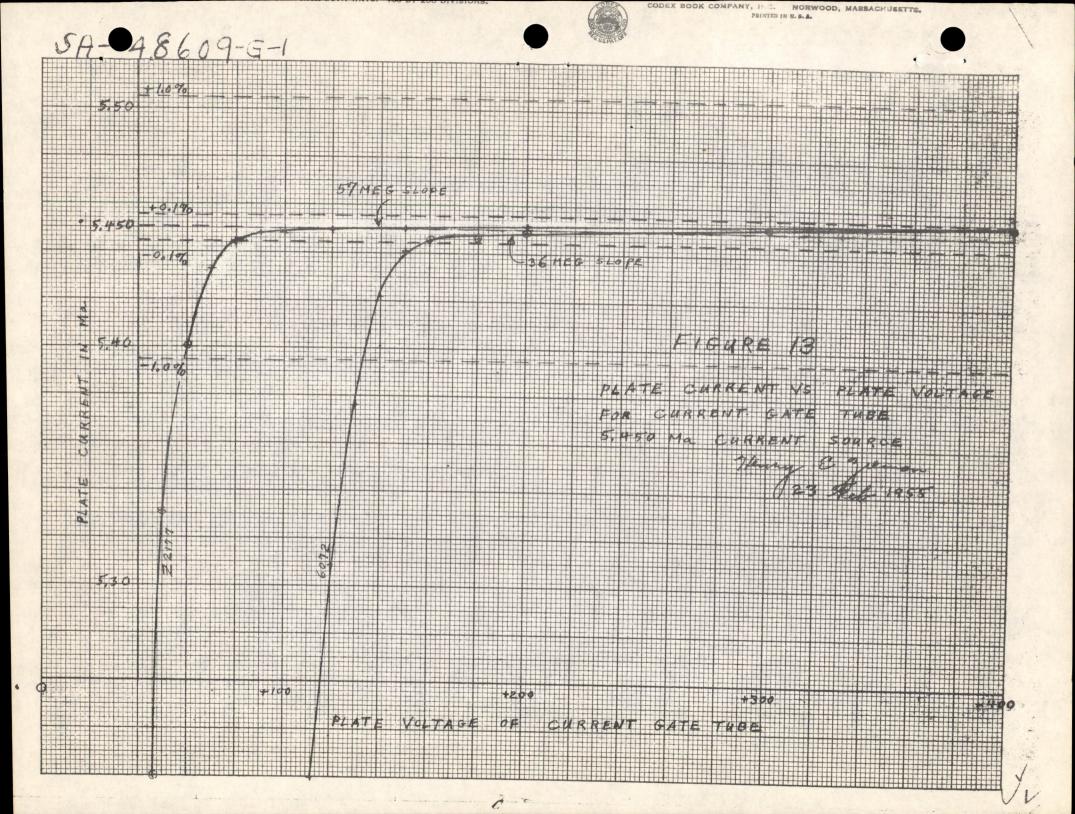

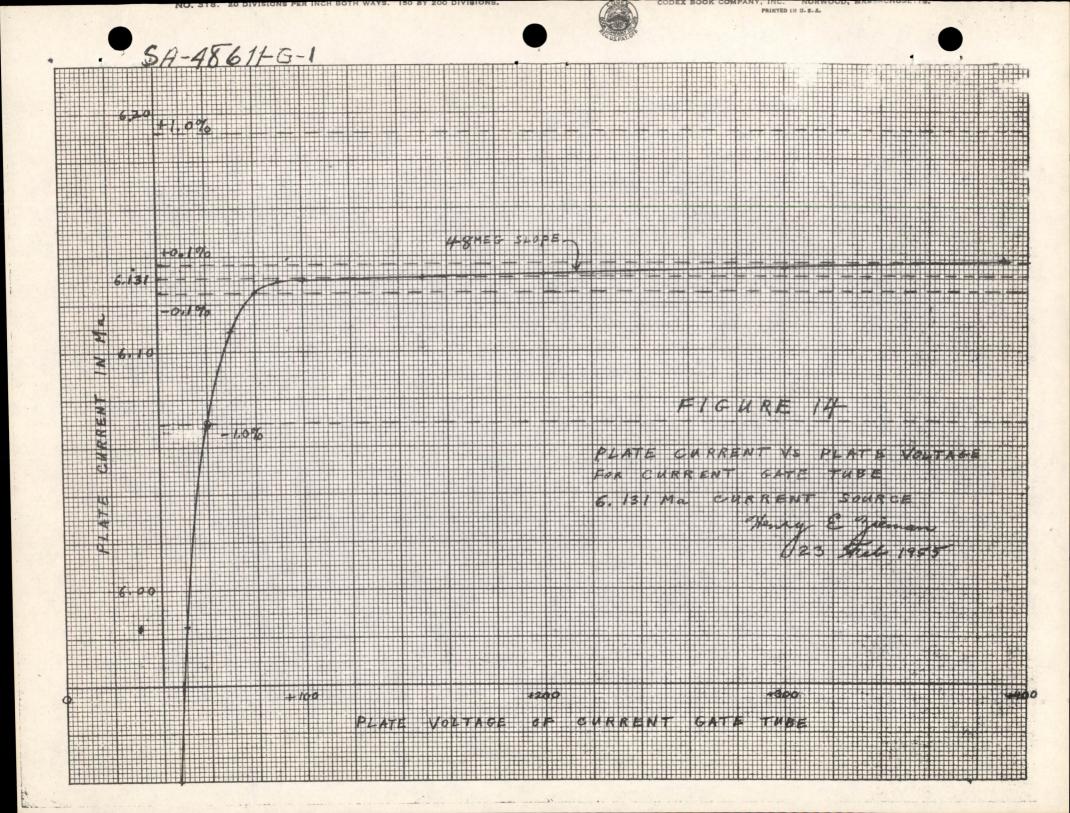

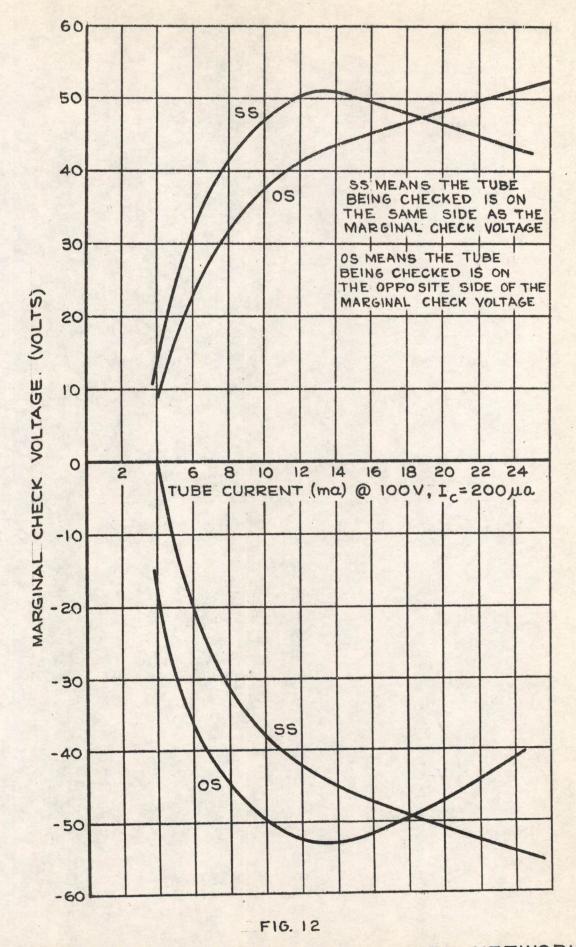

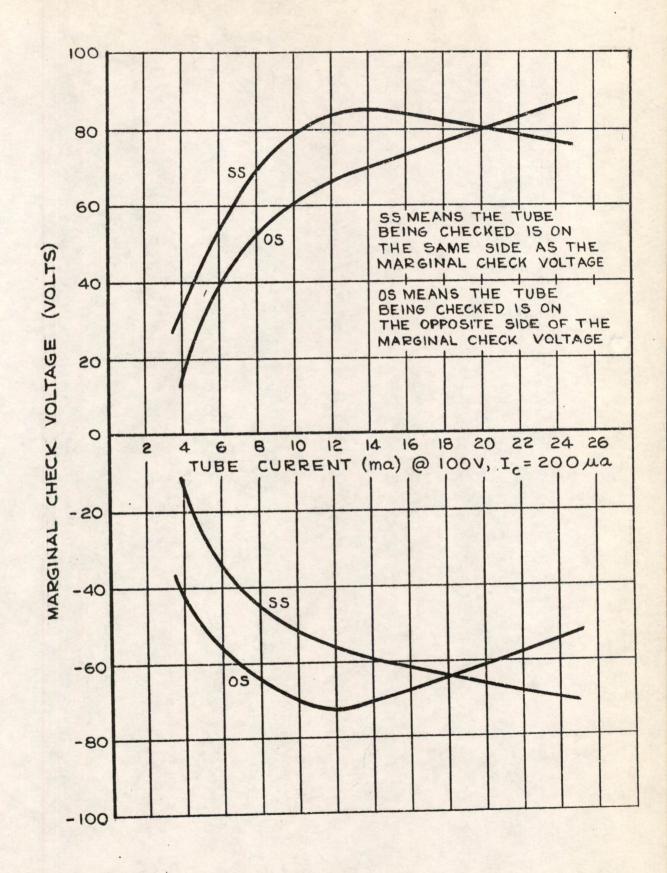

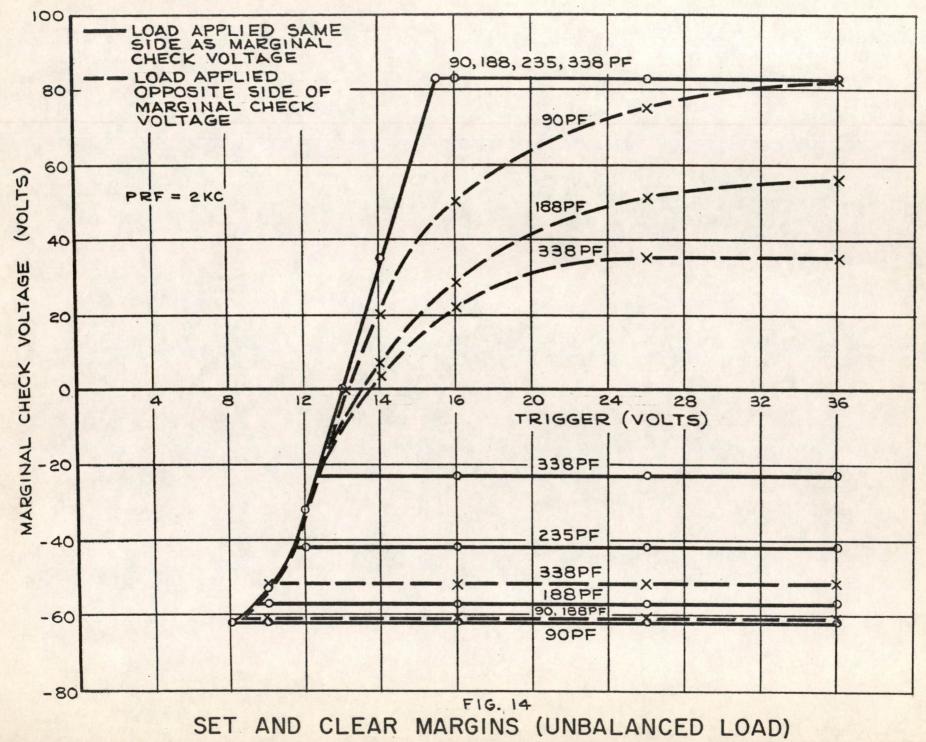

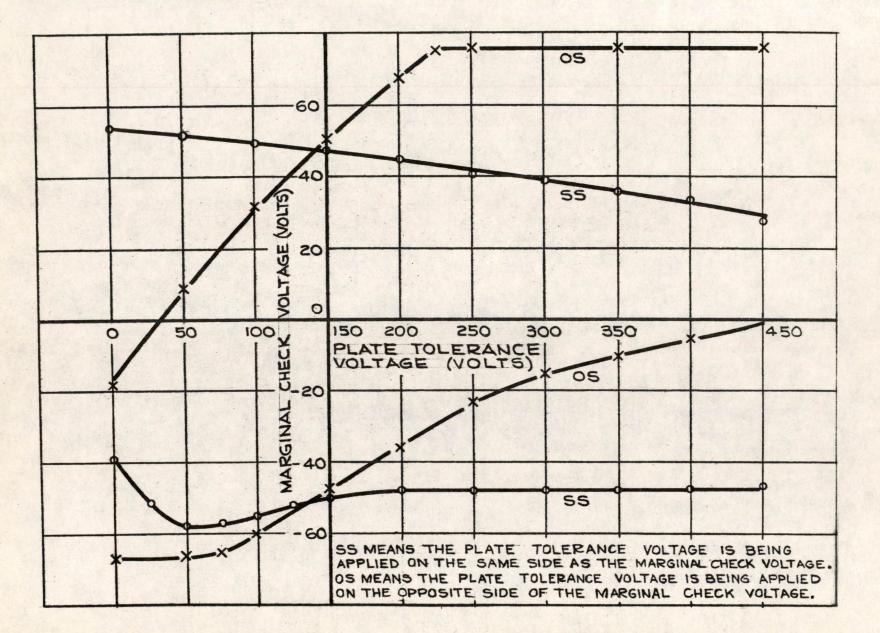

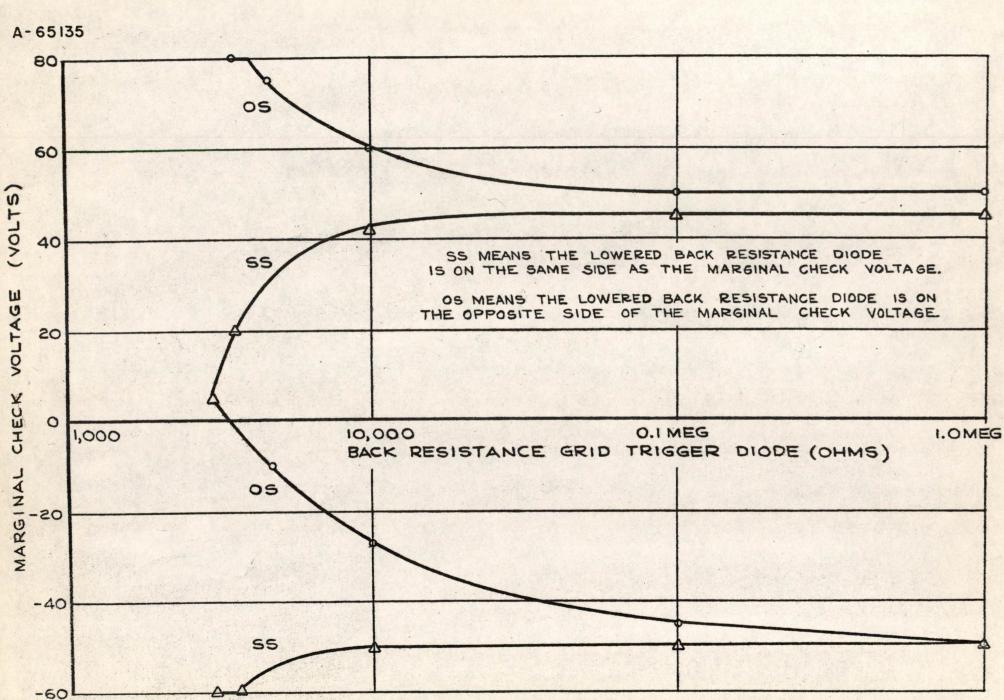

Table 2.3d shows the calculated values of Req for variations in  $-300^{\circ}$ ,  $+10^{\circ}$ , and  $+250^{\circ}$  lines using  $\mu_2 = 40$ ,  $rp_2 = 10K$ . These can then be compared to the measured values shown in figures 12, 13, and 14 (SA 48610-G, SA 48609-G, SA 48611-G respectively).

The importance of grid current is emphasized if figure 12, 13, and 14 in the vicinity of  $+80^{\circ}$ . The Req becomes considerably lower in this region so that the regulation deteriorates very rapidly. This reduction is the result of grid current which reduces the plate current by an equivalent amount. Figure 13 further emphasizes the effect by substituting a 6072 for a Z2177 to show the effect of a lower perveance, and consequently introducing grid current at a higher plate voltage.

This effect of grid current can conveniently be used to marginal check this circuit. If the 4250 volt line is lowered, the signal voltage on each tube plate will be lowered by an equivalent amount because of the constant current being drawn. If this voltage is lowered to a point where the operating voltage on all tubes is still slightly above the point of grid current, only a negligible effect on the plate current will be noticed. However, if a tube is below specs it will begin to draw grid current and the plate current will change by an equivalent amount. This eeffect is then reflected in a change in the output voltage of the decoder.

An effect similar to grid current is produced by plate current in the cut-off companion gate tube. It had been tacitly stated earlier that the cut-off bias on the circuit would be a minimum of 35 volts. However, if the input deteriorates from its  $\pm 10^{V}$  and  $-30^{V}$  levels it could happen that the cut-off tube might not have enough bias to completely cut off. With a weak-on tube the cathode of both tubes will be at the same potential as the input to the on-tube. Under this condition the cut-off bias on the companion tube is exactly equal to the difference in input levels. The exact minimum value of this difference can not be determined because the cut-off characteristics of the tube are not controlled to the degree required. However, a test of a representative group of tubes indicates that 13 volts bias will cut off 97% o of the tubes tested to within 10 µa. This indicates that with the inputs deteriorated to a difference of 13 volts, the "on" tube should still conduct 99.80/o of its nominal current. By limiting the minimum difference between inputs to 20 volts we should not expect any difficulty from this source.

The input impedance of this circuit is entirely capacitive but varies in magnitude depending on the state of the tube. Neglecting wiring capacity, there are three states during which the capacity differs. The first state occurs in the region between +10<sup>V</sup> input and the start of current transition between companion tubes, During this time the cathode essentially follows the grid but the plate remains constant because of the constant current source. At this time the only capacity of importance is the grid to plate capacity of the tube. The second state occurs during transition. At this time the cathode remains essentially fixed but the plate voltage varies depending on the gain of the tube. At this time the capacity is highest being equal to the grid to cathode capacity plus Miller capacity. The third state occurs between -30" and the start of current transition from a negative approach. At this time the plates are again constant but the cathode follows the grid of the companion tube. The capacity at this time is essentially the grid to plate capacity plus twice the grid to cathode capacity. The calculated values of capacity for states 1, 2, and 3 are respectively 3, 36, 11 µµf. Measured values of capacity necessarily include the wiring capacity in the plug-in-unit and the integrated effect of all three states. The measured value was 12 µµf + 20%/0.

Table 2.3 presents pertinent information for the evaluation and maintenance of this circuit.

#### Table 2.3a

Voltage Measurements (Fig. 11)

| Point<br>A | $\frac{\text{Voltage}}{\text{in volts}}$<br>+10 ± 2 $^{\nabla}$ (or -30 ± 2 $^{\nabla}$ ) | Point<br>D | <u>Voltage</u><br>in volts<br>-30 <u>+</u> 2 (or +10 <u>+</u> 2) |

|------------|-------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------|

| В          | +11.5 <u>+</u> 3.5                                                                        | E          | +150 ± 50                                                        |

C +150<sup>▼</sup> ± 50

## Table 2.3b

| Component             | <u>Voltage</u><br>in volts | <u>Current</u><br>in ma | <u>Max. Power</u><br>in watts |

|-----------------------|----------------------------|-------------------------|-------------------------------|

| Z2177<br>"on" section |                            |                         |                               |

|                       | 143 ± 43                   | 4.115 <u>+</u> .065     | 0.78                          |

| Plate to cathode      | <140 ± 40                  | 5.485 ± .095            | 1.0                           |

|                       | 139 ± 39                   | 6.17 <u>+</u> .11       | 1.1                           |

| Component        | <u>Voltage</u><br>in volts  | <u>Current</u><br>in ma | Max. Power<br>in watts |

|------------------|-----------------------------|-------------------------|------------------------|

| "ON" SECTION     |                             |                         |                        |

| grid to cathode  | -1.5 ± 1.5                  | 0                       | 0                      |

| "OFF" section    |                             |                         |                        |

| Plate to cathode | +150 ± 50                   | 0                       | 0                      |

| grid to cathode  | -40 <u>+</u> 5 <sup>♥</sup> | 0                       | 0                      |

Page 11 of 31

Table to 2.3c

#### Power Requirements

6.3" ac at .45 amp/2 CGT biased at ground

#### Table 2.3d

#### Transfer Functions

| Voltage Source<br>having noise | Req (in megohms)<br>3/4 current source | Unit<br>current source | 1 1/8<br>current source |

|--------------------------------|----------------------------------------|------------------------|-------------------------|

| +250                           | 71.0                                   | 54.4                   | 49.0                    |

| +10 (input signal)             | 1.80                                   | 1.39                   | 1.25                    |

| -300                           | 1.44                                   | 1.11                   | 1.00                    |

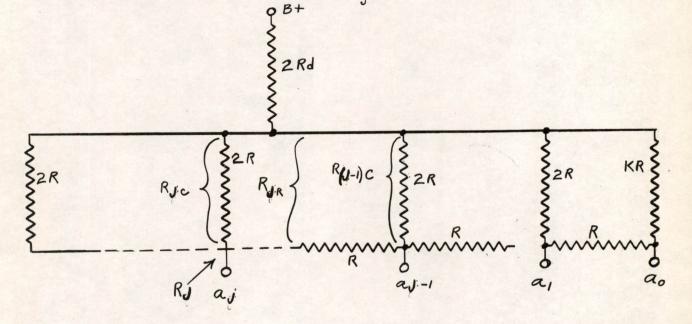

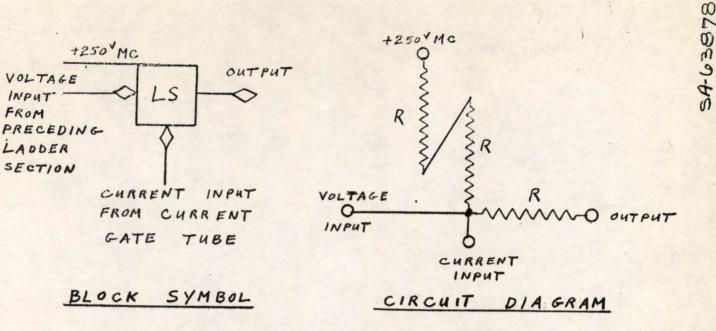

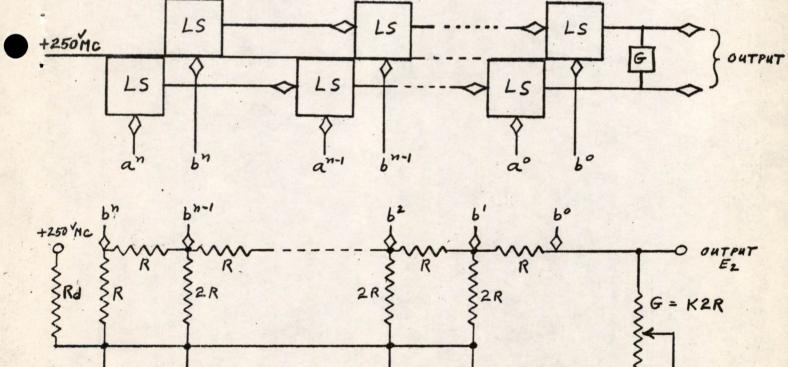

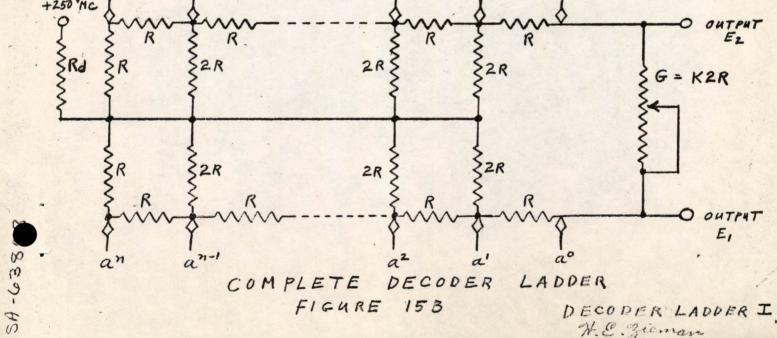

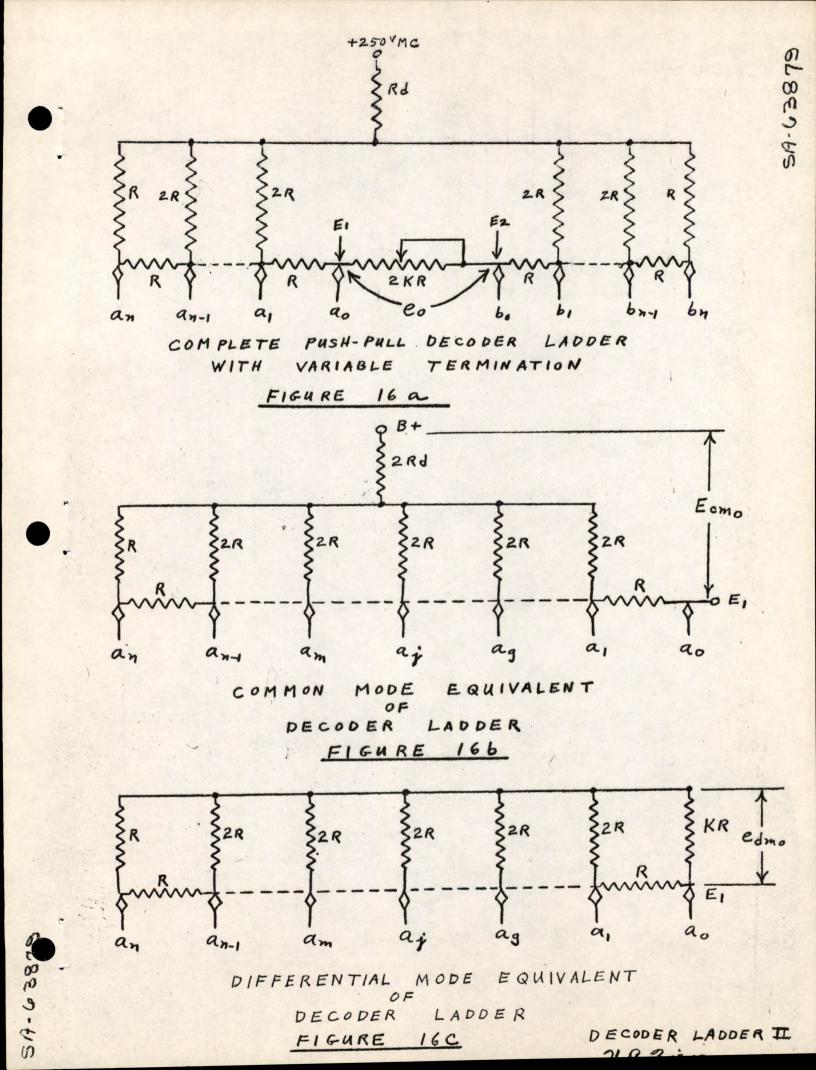

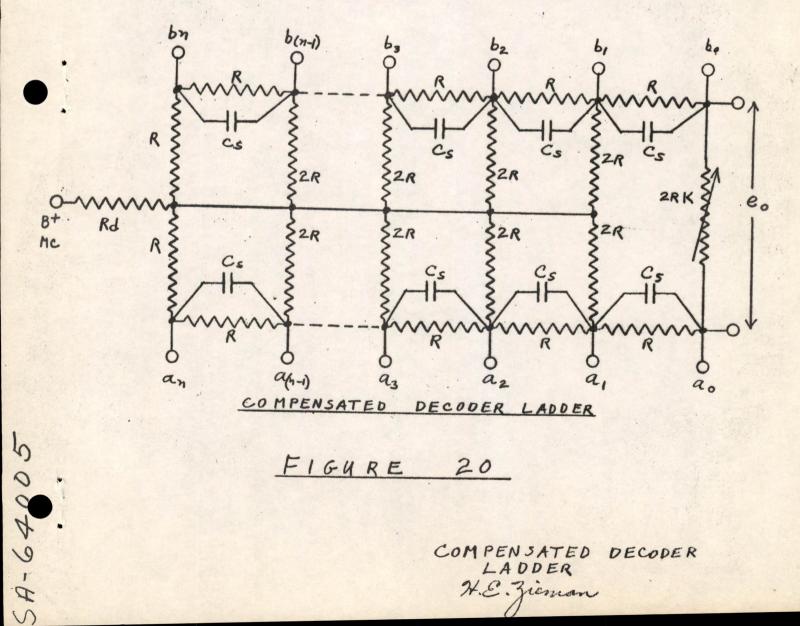

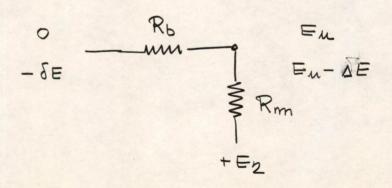

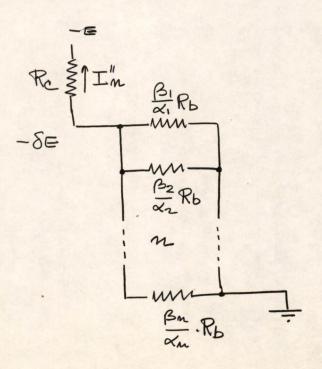

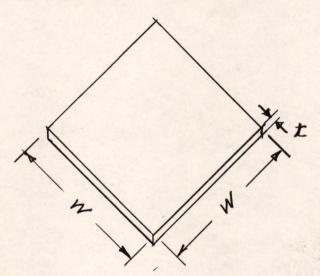

#### 2.4 Decoder Ladder

Figure 15a (SA 63878) shows the block symbol and circuit diagram of a single ladder section. Figure 15b shows how a number of these sections are tied together to make up a push-pull decoder ladder. Drawings 3006-895, 3006898, 3006899, 3006902, 3007694, show the necessary card details and assemblies to make up a decoder ladder and its gain control.

To study the steady state response of a general push-pull ladder it is convenient to analyze it by use of symmetrical components. It will be slightly easier to visualize the behavior of this circuit by redrawing it in the form shown in figure 16a (SA-63879). In this circuit current gate tube #0 (CGT-0) will switch a current I<sub>0</sub> between a<sub>0</sub> and b<sub>0</sub>. CGT-1 will switch I<sub>1</sub> between a<sub>1</sub> and b<sub>1</sub>, and CGT-j will switch I<sub>j</sub> between a<sub>j</sub> and b<sub>j</sub>. To consider this circuit symmetrically, we will have to break I<sub>j</sub> into two components, the common mode Id  $m = I_{j/2}$  going into both a<sub>j</sub> and b<sub>j</sub> continuously, and the differential mode I  $J_{j} = I_{j/2}$  going into a j and out of bj, or the reverse.

Considering only the common mode response of this circuit (figure 16a), it is easily seen that  $E_1 = E_2$  and E0 = 0. For this condition no

#### Page 12 of 31

current exists in KR and the circuit can be simplified to that shown in figure 16b. In this case the voltage at any terminal aj due to a current  $I_{cmj}$  alone is simply this current multiplied by the impedance presented by the ladder to this point. In appendix B it is shown that this impedance for terminal aj is

$$R_{jcm} = \frac{2RL}{3} \left( \frac{2^{2}j-1}{2^{2}j-1} + 2R_{d} \right) = eq 2.41$$

Thus the voltage at any terminal aj due to the current I is

$$E_{jj} = 2 I_{jcm} Rd + \frac{RL}{3} (\frac{2^{2j-1}+1}{2^{2j-1}})$$

Since Idem = Ij/2

$$E_{jj} = I_{j} \left[ Rd + \frac{RL}{3} \left( \frac{2^{2j-1} + 1}{2^{2j-1}} \right) \right]$$

eq. 2.42

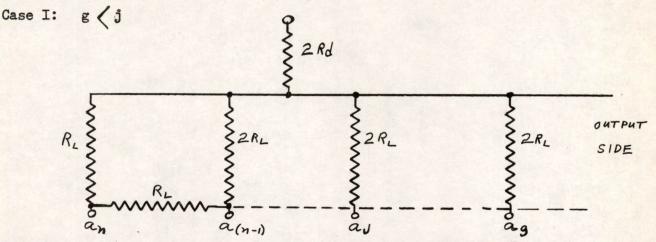

To consider the total common mode voltage at terminal aj we must also consider the effect on a, by currents in all other terminals ( $\sum IgRg + \sum ImRm$ ). Considering first the effect of currents  $I_g$  at terminal  $a_g$  where g < j, the voltage of  $a_g$  is

$$E_{gg} = I_{g} \left[ Rd + \frac{RL}{3} \left( \frac{2^{2}g-1}{2^{2}g-1} \right) \right]$$

eq 2.42a

Since only a fraction of this voltage will appear at  $a_j$ , it is shown in appendix C that the voltage at  $a_j$  due to a current at  $a_g$  is

$$E_{jg} = I_g \left[ Rd + \frac{RL}{3} \left( \frac{2^{2g-1} + 1}{2^{j+g-1}} \right) \right] \qquad eq 2.43$$

Similarly the voltage at  $a_j$  due to a current in  $a_m$  where m > j is shown to be

$$E_{jm} = Im \left[ Rd + \frac{RL}{3} \left( \frac{2^{2}j-1}{2^{j+m-1}} \right) \right] \qquad eq 2.44$$

The common mode voltage at aj due to currents in all terminals is, by superposition

$$E_{Jcin} = E_{jj} + \sum_{g=0}^{g=j-1} E_{jg} + \sum_{m=j+1}^{m=n} E_{jm}$$

Page 13 of 31

Memorandum 6M-3971

Substituting equation 2.42, 2.43, and 2.44 and simplifying gives

$$E_{JCm} = \sum_{g=0}^{g=n} I_g \left[ Rd + \frac{RL}{3} \left( \frac{1}{2^{j+g-1}} + \frac{1}{2^{j-g}} \right) \right] \qquad eq 2.45$$

Considering the differential mode, a similar line of reasoning can be followed.

The impedance presented by the ladder to any terminal a<sub>j</sub> is (See Appendix B)

$$R_{jdm} = \frac{2RL}{K+2} \left[ \frac{(2^{2j-1}+1)(K+2)-3}{3 \times 2^{2j-1}} \right] eq. 2.46$$

The voltage at terminal a; due to the current in this terminal is

$$E_{jj} = \frac{I_{jRL}}{K+2} \left[ \frac{(2^{2j-1}+1)(K+2)-3}{3 \times 2^{2j-1}} \right] eq 2.47$$

The voltage at terminal  $a_j$  due to a current terminal  $a_g$  where g < j is (See Appendix C)

$$E_{jg} = \frac{I_{gRL}}{K+2} \left[ \frac{2^{2g-1} + 1 (K+2) - 3}{3 \times 2^{j+g-1}} \right] eq 2.48$$

The voltage at  $a_j$  due to a current in  $a_m$  where M > j is (See Appendix C)

$$E_{jm} = \frac{ImRL}{K+2} \left[ \frac{(2^{2j-1}+1)(K+2)-3}{3 \times 2^{j+m-1}} \right] eq 2.49$$

The voltage at a; due to currents in all terminals is

$$E_{dmj} = E_{dmjj} + \sum_{g=0}^{g=g-1} E_{dmjg} + \sum_{m=j+1}^{m=n} E_{dmjm}$$

Substitutions equations 2.47, 2.48, and 2.49 in the above and simplfying gives

$$E_{Jdm} = \sum_{g=0}^{g=n} \frac{I_{gRL}}{3} \left[ \left( \frac{K-1}{K+2} \right) \frac{1}{2^{J+g-1}} + \frac{1}{2^{4}J-gI} \right] \qquad eq 2.410$$

The total voltage at any terminal is the sum of the common mode and difference mode signals subtracted from the positive supply voltage. Since the difference mode may be either positive or negative depending on the setting of the input signal, the differential mode current is either positive or negative. However, to simplify the resulting expression we can consider the current always positive and associate the reversal of sign with the impedance term.

Page 14 of 31

Substituting equations 2.45 and 2.410 we get

$$E_{j} = E_{bb} - \sum_{g=0}^{g=n} I_{g} \left\{ Rd + \frac{RL}{3} \left[ \frac{(K+2) \pm (K+1)}{(K+2) 2} + \frac{1+1}{2} \right] eq. 2.411 \right\}$$

The minimum voltage at any terminal aj will occur when all currents are flowing through one side of the decoder ladder. In this case we can use the plus signs in eq 2.411 to get,

$$E_{jmin} = E_{bb} - \left\{ \sum_{g=0}^{g=n} I_g \left\{ Rd + \frac{RL}{3} \left[ \frac{2K+1}{(K+2)} + \frac{2}{2^{j+g-1}} \right] + \frac{2}{2^{lj-gl}} \right\} eq.2.412$$

Similarly the maximum voltage will be of interest and can be derived by using the minus signs of eq. 2.411

Ejmax = Ebb -

$$\sum_{g=0}^{g=n} Ig \left\{ Rd + \frac{R_L}{(K+2) 2 j+g-1} \right\}$$

eq. 2.413

The binary weighting properties of this ladder can now be proven by determining the maximum push-pull differential output of the ladder. Setting j = 0 in equations 2.412 and 2.413 we have

Eod = 2 (Eomin - Eomax)

$$I_g$$

Eod =  $\frac{4 \text{ RLK}}{\text{K+2}}$   $2g$  eq. 2.414

The term <sup>1</sup>g emphasizes the binary weighting property of this ladder 2g

despite the variation of the terminating resistor.

For most decoder purposes the current to all bits is the same  $(I_g = I)$  with the exception of an additional commonVcurrent  $(I_L)$  drawn by the load attached to the decoder. Under this condition several of the preceding equations can be simplified. (See Appendix D)

In general use it is necessary to amplify the output of a decoder. (See 6M-3284 for a typical amplifier) To reduce the complexity of this amplifier it is desirable to produce as large an output from the decoder as possible. One of the governing factors in the allowable output swing is the bounded limit on the voltage across the current gate tube. The maximum voltage across the tube is dictated by the manufacturer, while the minimum voltage is restricted by the bias condition of the tube. The requirement that the grid current shall not be more than a given percentage of the plate current automatically limits the minimum plate voltage for any given current.

It has been shown in Walquist's Report (R220) that for an infinite decoder ladder terminated in its characteristic impedance and having all its current sources equal, the maximum voltage at the various bits varies, reading a maximum at the center of the ladder, where it is  $50^{\circ}/_{\circ}$  greater than at the output. Since this point then has the minimum voltage across the current gate tube, the output voltage is only  $67^{\circ}/_{\circ}$  of the maximum attainable if the full tube swing could be used at the output. By increasing the output termination it is possible to arrange the maximum voltage distribution along the ladder so that the maximum voltage will occur at the most significant bit. Since the output is taken from this bit, this will insure that the maximum possible output can be obtained. The necessary amount of increase in the termination can be calculated for the case of a decoder having equal currents going to all its bits by using equation 2.412a. (See Appendix D)

$K \ge -2^{-n}$  eq. 2.415

#### Page 16 of 31

Since this term is always negative, any terminating resistor used in figure 15b will insure that the minimum plate voltage will appear at the output tube. This in turn insures that the maximum possible output can be obtained from the decoder when this output is limited by the voltage swing on any plate.

These results apply to push-pull decoders directly. Equation 2.415 can be extended to include single **Side**d decoders by assuming a variable termination of MR (where R is nominal resistance of that decoder). Considering the similarity between a variably terminated single-sided decoder and the push-pull decoder shown in Figure 16A with all current sources conducting on only one side, the two resultant terminations can be equated.

$$MR = 2KR + 2R = 2(K+1)R$$

$$M = 2(K+1)$$

M = 2(K+1) $M \ge 2(1-2-1)$

eq. 2.415a

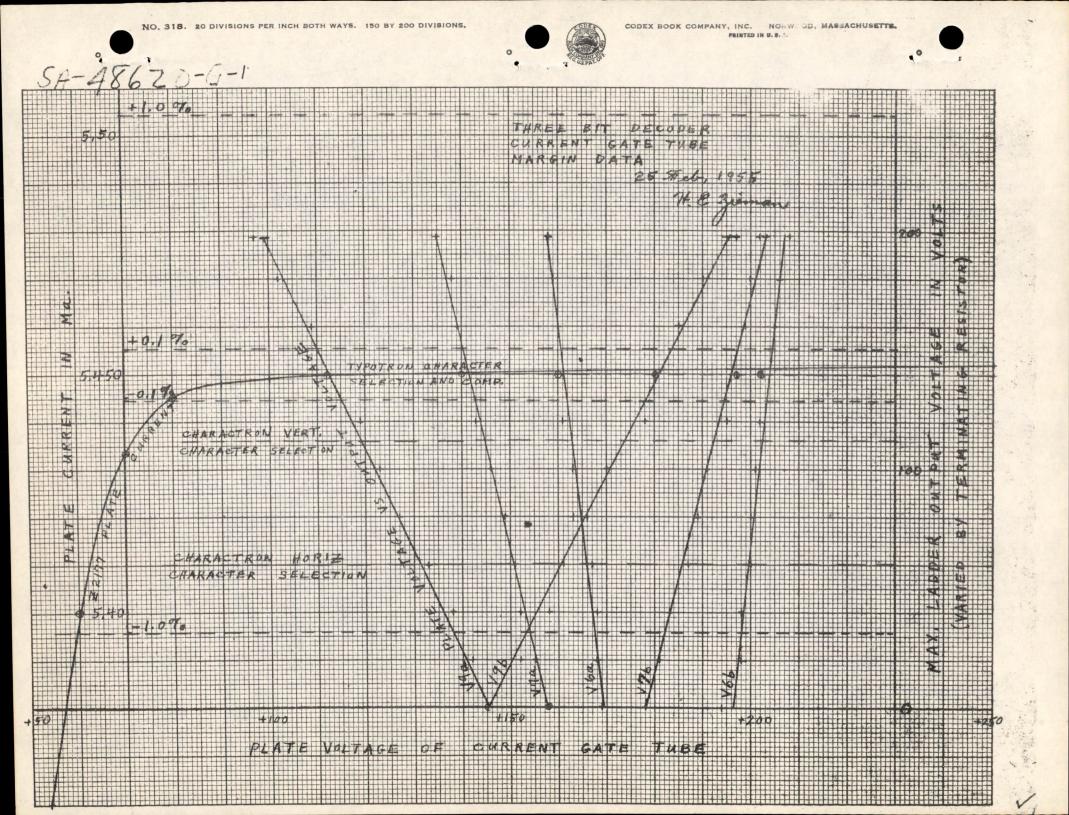

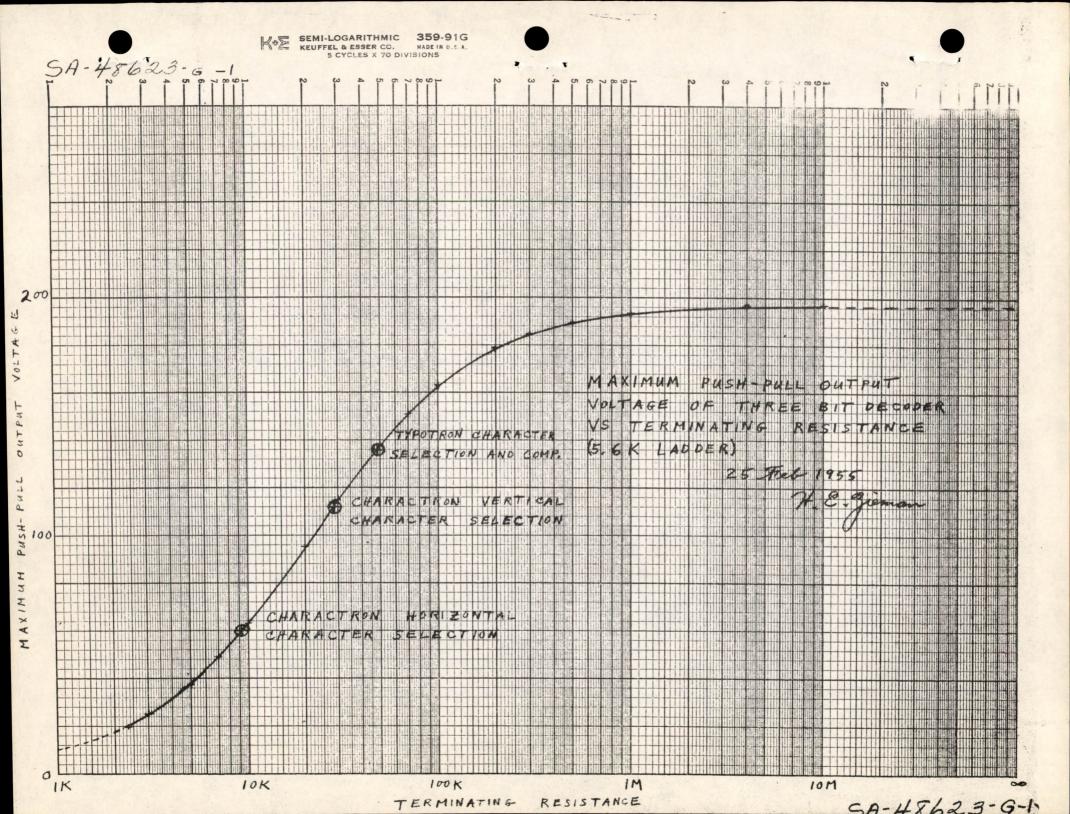

Several typical decoders are discussed in 6M-3915 (Push-pull Display Decoders in XD-1). Figures 17 and 18 (SA 48620-G and SA 48623-G) show the typical behavior of one of these. This is a three stage decoder using nominal currents of 5.45 ma. a nominal ladder resistance of 5600 ohms, a dropping resistor Rd of 1640 ohms, and a B supply of 244 volts. The output of the decoder is also loaded with an amplifier whose equivalent input circuit consists of a 235K resistor from each input terminal to a -150 volt supply.

Applying these values to equations 2.412a, 2.413a, and 2.414a gives:

$$E_{Jmin} = 152 + 5.08 \times 2^{J} - \left[14.06 + 5.08\left(\frac{10K-1}{K+2}\right)\right] 2^{-0}$$

$$E_{Jmax} = 213 - \frac{5.6}{2^{J}} \left(2.51 + \frac{19.1}{K+2}\right)$$

$$E_{od} = 214 \frac{K}{K+2}$$

Figure 17 shows how these voltages vary as a function of the terminating resistor and the position of the current gate tube in a ladder. For Ej min: j = 0 for V<sub>0</sub>a. j = 1 for V<sub>7</sub>a, and j = 2 for V<sub>6</sub>a. For E<sub>j</sub> max: j = 0 for V<sub>9</sub>b. j = 1 for V<sub>7</sub>b. and j = 2 for V<sub>6</sub>b. Figure 18 shows how the output voltage varies as a function of the terminating resistor.

#### Page 17 of 31

Equation 2.412 shows the feasibility of using the B+ supply as a means of marginal checking the current gate tube. Any variation on this line appears directly on the plates of all the current tubes so that the plate voltage can be reduced below its normal operating level whatever that may be, by lowering the B+ supply by an equivalent amount.

There is no direct method of marginal checking the ladder sections. It has been shown in Walquist's Report that variations in the ladder resistors affect the output linearly and can be compensated for by readjusting the current sources. This adjustment is therefore an indication of the state of the ladder resistors as well as the current source cathode resistors. If the range of adjustment on the current source tubes becomes critically small, the ladder resistors and current source cathode **resistors** must be checked.

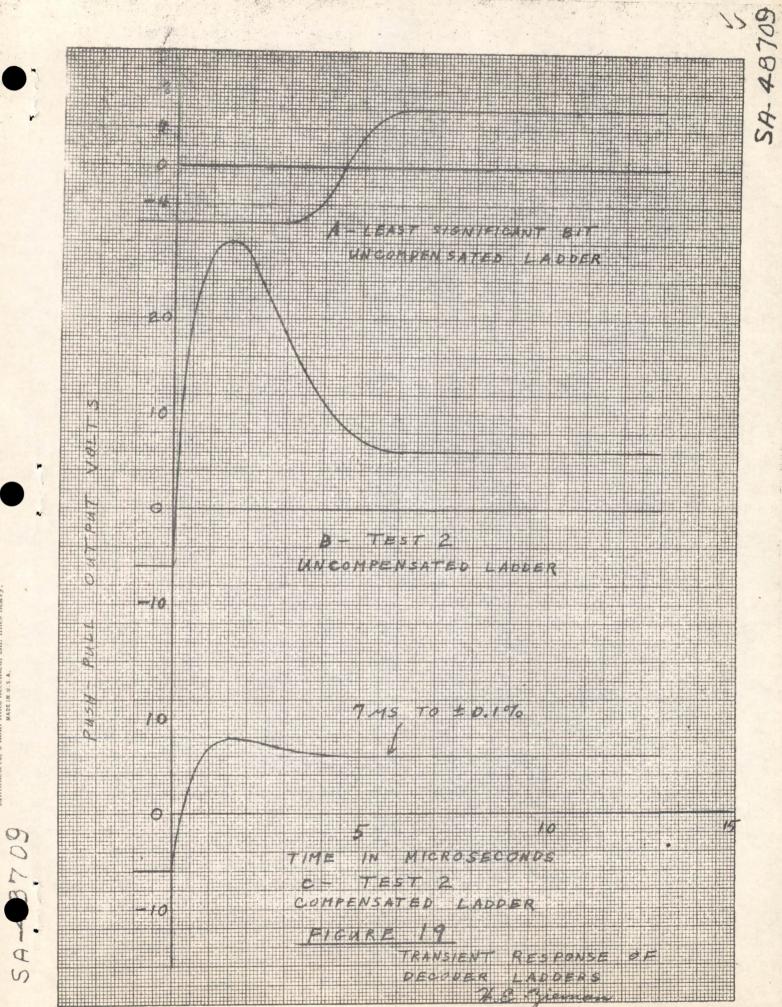

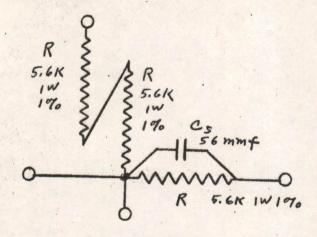

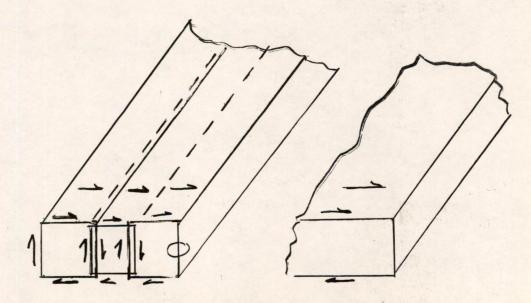

Experiments have shown that a delay line effect exists in the decoder ladder, apparently caused by the output capacity of the current gate tubes. This effect can be emphasized by operating the decoder in the following manner. First all bits are set in a fixed position except the least significant bit. This bit is then switched at a 100 KC rate by the output of a flip-flop and the rise time characteristic noted. Figure 19a (SA 48709) shows the result of this experiment on the above mentioned decoder showing especially the rise time and the exponential nature of this rise time. Secondly all bits are connected to the same flip-flop, with the most significant bit connected in the "1" position and all others connected in the "O" position. With no delays present, the output rise time characteristics and magnitude should appear exactly the same as in the first part of the experiment. Figure 19b (SA 48709) shows the result of this experiment. The large overshoot is caused by the signal of the most significant bit appearing at the output before the signal from any of the other bits. This effect has been compensated for experimentally by adding "speed-up" capacitors to the ladder sections as shown in Figure 20 (SA 64005). Figure 19c shows the result of the second part of the above experiment when the capacitors have been added to the ladder.

Page 18 of 31

# APPENDIX A:

Equivalent resistance and equivalent voltage of a constant current source:

$$\Delta E_{I} = \Delta i_{b} (n_{p} + R_{K}) - \eta \Delta e_{g}$$

$$\Delta e_{g} = K_{I} \Delta E_{I} - R_{K} \Delta i_{b}$$

$$\Delta E_{I} (I + \eta K_{I}) = \Delta i_{b} [f_{II} + I)R_{K} + n_{p}]$$

$$Re_{q} = \frac{\Delta E_{I}}{\Delta i_{b}} = \frac{(\eta + I)R_{K} + n_{p}}{I + \eta K_{I}} \qquad E_{q} 2.21$$

$$E_{eq} = i_{b} Re_{q} \qquad E_{q} 2.22$$

## Page 19 of 31

## Appendix B

Impedance  $R_j$  presented by a decoder ladder with variable termination to any terminal  $a_j$ .

Consider the impedance  $R_j$  to be composed of three parallel components, the left section of the ladder, the 2R resistor going directly to  $a_j$ , and the right section of the ladder. It is easily shown that the equivalent resistance of the left section of ladder is 2R since that end is terminated in the characteristic impedance of the ladder. The figure below shows the resultant simplification of the impedance  $R_j$ .

Thus

$$R_{JR} = 2R ||R_{JC} + 2Rd$$

$$R_{JC} = 2R ||R_{JR}$$

$$R_{JR} = R + R_{(J-1)C}$$

The first few terms for Rj can be calculated as in the table below.

Page 20 of 31

| J | Ryr                                                 | RJC                                         | Ry.                                                     | N   |

|---|-----------------------------------------------------|---------------------------------------------|---------------------------------------------------------|-----|

| 0 |                                                     | KRL                                         | $2R_{d} + \frac{2R_{L}}{K+2} (K)$                       | 1/2 |

| 1 | R <sub>L</sub> ( <i>K</i> +1)                       | $2R_{L}\left(\frac{K+1}{K+3}\right)$        | $2Rd + \frac{2RL}{K+2} \left(\frac{K+1}{2}\right)$      | 1   |

| 2 | $R_{L}\left(\frac{3\kappa+5}{\kappa+3}\right)$      | $2 R_{L} \left( \frac{3K+5}{5K+11} \right)$ | $2Rd + \frac{2RL}{K+2} \left(\frac{3K+5}{8}\right)$     | 3   |

| 3 | $R_{L}\left(\frac{11K+21}{5K+11}\right)$            | $2R_{L}\left(\frac{11K+21}{21K+43}\right)$  | $2RJ + \frac{2RL}{K+2} \left(\frac{11K+21}{32}\right)$  | 11  |

| 4 | $R_{L}\left(\frac{43\kappa+85}{21\kappa+43}\right)$ | $2R_{L}\left(\frac{43K+85}{85K+171}\right)$ | $2Rd + \frac{2RL}{K+2} \left(\frac{43K+85}{128}\right)$ | 43  |

From this table it will be noticed that the values of  $R_j$  are in the form.

$$R_{J} = 2RJ + \frac{2RL}{K+2} \left( \frac{NK+2N-1}{3N-1} \right) \quad \text{for } J \neq 0$$

The resultant values of N are calculated and are found to form a series having the ratio 4N-1. This series can be expressed more generally as

$$N = \frac{2^{2J-1}+1}{3}$$

Substituting this general expression of N into the above expression for R,

$$R_{J} = 2R_{J} + \frac{2R_{L}}{K+2} \left[ \frac{(2^{2J-1}+1)(K+2) - 3}{3 \times 2^{2J-1}} \right] \quad for \quad 0 \le J \le n$$

where n+l is the total number of bits in the ladder.

L.J. Manurge Tirt & Seite .

Page 21 of 31

For common mode analysis K = 00 so that

$$R_{J} = 2 R_{d} + \frac{2 R_{L}}{3} \left( \frac{2^{2J-1}}{2^{2J-1}} \right) for 0 \le J \le n$$

Eq. 2.41

For differential mode analysis Rd = 0 so that

$$R_{J} = \frac{2R_{L}}{K+2} \left[ \frac{(2^{2J-1}+1)(K+2) - 3}{3 \times 2^{2J-1}} \right] \text{ for oxJim Eq 2.46}$$

Similarly

$$R_{JC} = 2R_{L} \left[ \frac{NK + 2N - 1}{(2N - 1)K + 4N - 1} \right]$$

again

$$V = \frac{2^{2y-1} + 1}{3}$$

So that

$$R_{JC} = 2R_{L} \left[ \frac{(2^{2J-1}+1)K + 2^{2J-1}}{(2^{2J}-1)K + 2^{2J+1} + 1} \right] for \ 0 \le J \le n$$

For differential mode analysis Rd = 0. However, since it does not appear here, this expression is correct for differential mode analysis.

For common mode analysis K = 00 so that

$$R_{JC(cm)} = 2R_L\left(\frac{2^{2J-1}+1}{2^{2J}-1}\right)$$

Page 22 of 31

## Appendix C

Voltage at terminal  $a_j$  of a decoder ladder caused by a current  $I_g$  is some other terminal  $a_g$ .

The total ladder impedance to the left of a together with the 2R resistor at a forms a termination at a equal to R. Thus, of the entire voltage developed at a  $(I_{g}, R_{g})$ , the entire portion developed across  $2R_{d}$  will appear at a j, but only a portion of the remainder (See R-220

"Analysis and Design of a Digital-to-Analog Decoder" by Robert Louis Walquist Sect. 4.3 pp 31-64)

$$E_{Jg} = 2I_{g}Rd + \frac{I_{g}R_{g} - 2I_{g}Rd}{2^{J-g}}$$

$$E_{Jg} = I_g \left( 2Rd + \frac{R_g - 2Rd}{2^{J-g}} \right)$$

For common mode analysis we have R from Appendix B:

$$R_g = 2Rd + \frac{2R_L}{3} \left( \frac{2^{2g-1} + 1}{2^{2g-1}} \right)$$

Page 23 of 31

Thus

$$E_{Jg\ cm} = I_{gcm} \left[ 2Rd + \frac{2RL}{3} \left( \frac{2^{2g-1} + 1}{2^{J+g-1}} \right) \right]$$

But  $I_{gem} = \frac{I_{g}}{2}$

$$E_{Jg\,cm} = I_g \left[ R_d + \frac{R_L}{3} \left( \frac{2^{2g-1} + 1}{2^{J+g-1}} \right) \right] \qquad E_{Q, 2, 43}$$

For differential mode analysis

$$R_{g} = \frac{2R_{L}}{K+2} \frac{\left(2^{2g-1}+1\right)(K+2) - 3}{3 \times 2^{2g-1}}$$

and Rd = 0

$$E_{Jg\,dm} = I_{g\,dm} \frac{2RL}{K+2} \left[ \frac{(2^{2g-1}+1)(K+2) - 3}{3 \times 2^{J+g-1}} \right]$$

But  $I_{gdm} = I_{g/2}$  - therefore:

$$E_{Jg\,dm} = \frac{I_{g\,R_{L}}}{K+2} \left[ \frac{(2^{2g-1}+1)(K+2)-3}{3\times 2^{J+g-1}} \right] = E_{Q}, 2, 48$$

Consider terminal  $a_j$  terminated with the characteristic impedance of the ladder (R). Under this condition the voltage at  $a_m$  due to  $I_m$  is

$$E_{mm} = \frac{2}{3} I_m R_L + 2I_m R_d$$

Using the results of Walquist Report R220, the voltage at  $a_j$  due to the current at  $a_m$  is

$$E_{Jm} = I_m \left( 2Rd + \frac{R_L}{3x2^{m-J-1}} \right)$$

The output impedance between terminal  $a_j$  and line Y at this timelis 2/3R. This portion of the decoder can thus be replaced with its Thevenin equivalent circuit. If this Thevenin circuit is then shunted with an impedance equal to -R in parallel with  $R_j$  of Appendix B, the output voltage will be equal to the voltage at  $a_j$  due to  $I_m$  at  $a_m$  when the ladder is terminated in other than the characteristic impedance.

For common mode analysis Appendix B shows the value of R

$$R_{JC \ cm} = 2R_{L}\left(\frac{2^{2J-1}+1}{2^{2J}-1}\right)$$

$E_{jm}$  can be calculated from the Thevenin circuit and the above expression for  $R_{jc}$

$$E_{Jm \ cm} = I_{m \ cm} \left[ 2Rd + R_{L} \left( \frac{2^{2J-l}}{3 \times 2^{m+J}} \right) \right]$$

Page 25 of 31

However  $I_m cm = I_m/2$ . Therefore

$$E_{Jm} cm = I_m \left[ R_d + \frac{R_L}{3} \left( \frac{2^{2J-l}}{2^{J+m-l}} \right) \right]$$

Eq. 2.44

Similarily for differential mode analysis

$$R_{JC} = 2R_{L} \frac{\left(2^{2J+l}+1\right)K + 2^{2J}-1}{\left(2^{2J}-1\right)K + 2^{2J+l}+1}$$

$E_{jm}$  can again be calculated from the Thevenin circuit and the above expression for  $R_{jc}$ .

$$E_{Jm} d_{m} = \frac{I_{m} d_{m} R_{L}}{K+2} \left[ \frac{(2^{2J-1}+1)(K+2)-3}{3 \times 2^{m+J-2}} \right]$$

But  $I_m dm = I_m/2$ . Therefore

Page 26 of 31

Appendix D

Ej min., Eo min., Ej max., Eo max., and K for Eo min  $\leq$  Ej min when all Ig = I and load is a constant current IL from both output terminals.

$$E_{J cm} = \sum_{g=0}^{g=n} I_{g} \left[ R_{d} + \frac{R_{L}}{3} \left( \frac{1}{2^{J+g-1}} + \frac{1}{2^{J-g}} \right) \right] \qquad E_{Q} 2.45$$

$$E_{J cm} = \left[I_{L} + (n+1)I\right]R_{J} + \frac{I_{L}R_{L}}{2^{J}} + \frac{IR_{L}}{3} \left[\frac{2}{2^{J}}\sum_{g=0}^{g=n} \frac{1}{2^{3}} + \sum_{g=0}^{g=J} \frac{1}{2^{J-9}} + \sum_{g=J+1}^{g=n} \frac{1}{2^{g-J}}\right]$$

$$\sum_{g=0}^{g=n} \frac{1}{2^{g}} = 2 - 2^{-n}$$

$$\sum_{q=0}^{g=J} \frac{1}{2^{J-g}} = \sum_{q=0}^{g=J} \frac{1}{2^{g}} = 2 - 2^{-J}$$

$$\sum_{g=1}^{g=n} \frac{1}{2^{g-J}} = \sum_{g=1}^{g=n-J} \frac{1}{2^g} = 1-2^{J-n}$$

$$E_{J cm} = \left[I_{L} + (n+1)I\right]R_{d} + \frac{I_{L}R_{L}}{2^{J}} + \frac{IR_{L}}{3}\left[2^{J}(2-2^{-n}) + 2-2^{-J} + 1-2^{J-n}\right]$$

$$E_{J} c_{m} = \left[I_{L} + (n+1)I\right]R_{J} + \frac{I_{L}R_{L}}{2^{J}} + IR_{L}\left[1 + 2^{-J} - \frac{1}{3\times 2^{n}}\left(2^{J} + 2^{1-J}\right)\right]$$

Memorandum 6M-39715

$$E_{Jdm} = \int_{g=0}^{g=0} \frac{T_{q}R_{L}}{3} \left[ \frac{K-1}{K+2} + \frac{1}{2^{J+g-1}} + \frac{1}{2^{J-g}} \right] E_{q} 2,410$$

$$E_{Jdm} = \frac{T_{R_{L}}}{3} \left[ \frac{K-1}{K+2} + \frac{1}{2^{J+g-1}} + \frac{1}{2^{J-g}} \right] E_{q} 2,410$$

$$E_{Jdm} = \frac{T_{R_{L}}}{3} \left[ \frac{K-1}{K+2} + \frac{1}{2^{J-g}} + 2 - 2^{-J} + 1 - 2^{J-n} \right]$$

$$E_{Jdm} = T_{R_{L}} \left\{ 1 + \frac{K-2}{K+2} + 2^{-J} - \frac{1}{3^{3}2^{n}}} \left[ 2^{J} + \frac{K-1}{K+2} + 2^{J-J} \right] \right\}$$

$$E_{Jdm} = T_{R_{L}} \left\{ 1 + \frac{K-2}{K+2} + 2^{-J} - \frac{1}{3^{3}2^{n}}} \left[ 2^{J} + \frac{K-1}{K+2} + 2^{J-J} \right] \right\}$$

$$E_{Jmin} = E_{bb} - E_{Jcm} - E_{Jdm}$$

$$E_{Jmin} = E_{bb} - \left[ T_{L} + \frac{(n+1)T}{T} \right] R_{d} - \frac{T_{L}R_{L}}{2^{J}} - 2T_{L} \left\{ 1 + \frac{K^{2}}{K+2} - \frac{1}{3^{3}2^{n}} \left[ 2^{J} + \frac{2K+1}{K+2} + 2^{J} \right] \right\}$$

$$E_{Jmin} = E_{bb} - \left[ T_{L} + \frac{(n+1)T}{T} \right] R_{d} - \frac{T_{L}R_{L}}{2^{J}} - 2T_{L} \left\{ K^{2} - \frac{1}{3^{3}2^{n}} \left[ K^{2} + 2^{2} - \frac{1}{3^{3}2^{n}} \left[ K^{2} +$$

$$E_{0 \text{ MIN}} = E_{bb} - \left[I_{L} + (n+1)I\right]R_{d} - \left(I_{L} + 2I\right)R_{L} - \frac{2IR_{L}}{K+2}\left(K - \frac{K+1}{2^{n}}\right) \quad E_{a} 2.412b$$

$$E_{J \text{ MAX}} = E_{bb} - E_{J \text{ cm}} + E_{J \text{ dm}}$$

$$E_{J \text{ MAX}} = E_{bb} - \left[I_{L} + (n+1)I\right]R_{d} - \frac{I_{L}R_{L}}{2^{J}} - IR_{L}\left\{I + 2^{-J} - I - \frac{K-2}{K+2}2^{-J} - \frac{1}{3*2^{n}}\left[2^{J} - 2^{J} + 2^{I-J} - \frac{-K-1}{2^{J}}2^{I-J}\right]\right\}$$

$$E_{J \text{ MAX}} = E_{bb} - \left[I_{L} + (n+1)I\right]R_{d} - \frac{R_{L}}{2^{J}}\left[I_{L} + \frac{2I}{K+2}\left(2 - 2^{-n}\right)\right] \quad E_{Q}, 2.413a$$

$$E_{\sigma \text{ MAX}} = E_{bb} - \left[I_{L} + (n+1)I\right]R_{d} - R_{L}\left[I_{L} + \frac{2I}{K+2}\left(2 - 2^{-n}\right)\right] \quad E_{Q}, 2.413a$$

Page 28 of 31

FOR EOMIN & EJMIN OKJEN UNDER WORST CONDITION IL = 0  $K - \frac{K+1}{2^{n}} \rightarrow K 2^{-J} - \frac{1}{3 \times 2^{n}} \left[ (K+2) 2^{J} + (2K+1) 2^{-J} \right]$ 3×2" (K-K2"-K2-J-2-") > - [K2J+2J+1+K2"+2-J] K (3×2n-3-3×2n-J+2J+21-J) > 3-2J+1-2-J  $K > \frac{3-2^{n}-2}{3\times 2^{n}(1-2^{-1})+2^{1}-3+2^{1}}$  $K > \frac{1-2^{J+1}}{2+2^{N}+2^{J}-2}$  $K = \frac{-\frac{2}{3}}{\frac{2^{n}-\frac{1}{2}}{1}} + \frac{1}{3}$

FOR OXJEN K WILL HAVE ITS LEAST MERATIVE MALUE AS J->0. THEREFORE LET J=1

K) -2-"

Page 29 of 31

Appendix E: <u>Glossary of Symbols</u>

CGT Current Gate Tube (See section 2.3)

CU<sub>s</sub> Constant current source (See section 2.2)

Equivalent voltage source of a circuit - the voltage which would have to be applied to the equivalent resistance of a circuit to produce the same current which the actual circuit carries.

Egg cm The common mode voltage at terminal g of a decoder ladder measured with respect to the B + supply and caused by the common mode current through terminal g.

Egg dm Same as Egg cm except for differential mode voltage and differential mode current.

E. Total voltage at terminal j measured with respect to ground and caused by any currents through any terminals

E j cm Total common mode voltage at terminal j measured with respect to B + and caused by any common mode currents through any terminals.

Ej dm Same as Ej except differential mode voltage and differential mode currents.

E Maximum voltage at terminal j measured with respect to ground when all currents in the decoder are switched to the opposite side of the decoder ladder.

E j min Minimum voltage at the terminal j measured with respect to ground when all currents in the decoder are switched to the same side of the decoder ladder.

E jg cm The common mode voltage at terminal j measured with respect to B + caused by a common mode current in the terminal g when  $g < j_{\bullet}$

E jg dm Same as E jg cm except differential mode voltage and differential mode current.

Ejj cm Same as E gg cm except for terminal j.

E jj dm Same as E gg dm except for terminal j.

E jm cm Same as E jg cm except for terminal m instead of terminal g and m >j.

•

)

# Page 30 of 31

| E <sub>jm</sub> dm | Same as E <sub>jg dm</sub> except for terminal m instead of terminal g and m>j.                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eod                | Differential output voltage                                                                                                                                                  |

| E <sub>o max</sub> | Same as E, max except for output terminal.                                                                                                                                   |

| E <sub>o min</sub> | Same as E except for output terminal.                                                                                                                                        |

| Ig                 | Total current out of both g(a and b) terminals.                                                                                                                              |

| Ij                 | Same as I except for j terminals.                                                                                                                                            |

| I <sub>j cm</sub>  | Common mode current out of terminal j.                                                                                                                                       |

| I <sub>j dm</sub>  | Differential mode current out of terminal j.                                                                                                                                 |

| Im                 | Same as I except for terminal m.                                                                                                                                             |

| K                  | Proportionality factor relating value of terminating resistor of a push-pull decoder ladder to $2R_L$ where $R_L$ is the nominal resistance of the ladder.                   |

| ĸl                 | Transfer function for the output voltage variation of the voltage reference circuit vs supply voltage variations. For the circuit under consideration this value is 0.00355. |

| LS                 | Ladder section (See section 2.4)                                                                                                                                             |

| Μ                  | Proportionality factor relating the value of a terminating<br>resistor of a single-sided decoder ladder to the characteristic<br>impedance of the ladder.                    |

| n                  | One less than the total number of bits in a decoder ladder.                                                                                                                  |

| N                  | Total number of bits in a decoder ladder. $N = n + 1$ .                                                                                                                      |

| R                  | Voltage Reference Source (See section 2.1)                                                                                                                                   |

| RL                 | Characteristic resistance of a decoder ladder.                                                                                                                               |

| R <sub>d</sub> .   | Dropping resistor which lowers the B + supply voltage to a<br>level at which the decoder ladder is to operate.                                                               |

| Req                | Equivalent resistance of a circuit. It is the ratio of a change in the supply voltage of the circuit to the change in current caused by the change in voltage.               |

| Rje                | The resistance which a ladder presents to a current at<br>terminal j when all resistors from less significant bits<br>are removed. (See appendix B)                          |

R<sub>j</sub> r

Page 31 of 31

- R j cm The resistance which a ladder presents to a common mode current at terminal j.

- R<sub>j</sub> dm The resistance which a ladder presents to a differential mode current at terminal j.

- The resistance which a ladder presents to a current at terminal j when the 2R resistor at terminal j and all other resistors at less significant bits are removed.

$R_{jr} = R_{jc}$  in parallel with  $-2R_{c}$

Signed H. C. Jieman H. E. Zieman

distance inter

## Attached drawings:

| Figure | 1   | - | SA | 47174   |

|--------|-----|---|----|---------|

| Figure | 2   | - | SA | 63288   |

| Figure | 3   | - | SA | 48619-G |

| Figure | 4   | - | SA | 63702   |

| Figure | 5   | - | SA | 48613-G |

| Figure | 6   | - | SA | 48617-G |

| Figure | 7   | - | SA | 48614-G |

| Figure | 8   | - | SA | 48615-G |

| Figure | 9   | - | SA | 48618_G |

| Figure | 10- |   | SA | 48616-G |

Figure 11 - SA 63717 Figure 12 - SA 48610-G Figure 13 - SA 48609-G Figure 14 - SA 48611-G Figure 15 - SA 63878 Figure 16 - SA 63879 Figure 17 - SA 48620-G Figure 18 - SA 48623-G Figure 19 - SA 48709 Figure 20 - SA 64005

CC: Group 62 Staff I.B.M. Poughkeepsie Cecil Branson John Swatton

88-3

35

0

SA

VOLTAGE REFERENCE SOURCE FOR DECODERS

7 E greman

11 July 35

SA-63102

BLOCK SYMBOL

a = SLOT LOCATION OF CONTROL POT.

- PUT b= LOCATION OF CONTROL POT ON CARD.

- C = NOMINAL CURRENT OF CHS IN MR.

- d = LOCATION AND SECTION OF TUBE IN PLUGGABLE UNIT

CARD 300 6908 REFERENCE CURRENT SOURCE

CIRCUIT DIAGRAM

FIGURE 4

CURRENT SOURCE FOR DECODERS H.E. Zieman 1 aug 55

SA-63702

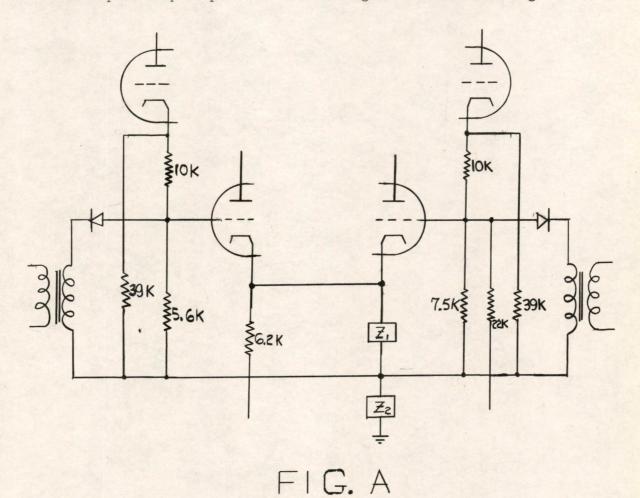

OUTPUT TO OUTPUT TO LADDER SECTION (LS) LADDER SECTION (LS) CGT CGT INPUT FROM INPUT FROM FLIP FLOP FLIP FLOP "O" SIDE "1" SIDE INPUT FROM CURRENT SOURCE (CUS) BLOCK SYMBOL OUTPUT OUTPUT TOLS TO LS E Vb Va 1/2 72177 1/2 Z2177 INPUTFROM INFUT FROM FLIP FLOP FLIP FLOP "O" SIDE "/" SIDE INPUT FROM CUS CIRCUIT DIA GRAM

FIGURE 11

CURRENT GATE TUBE FOR DECODERS H.C. Zieman 1,

LILEN-US

# SINGLE LADDER SECTION

FIGURE 15a

359-14 KEUFFEL & ESSER CO. Millimeters, 5 mm. lines accented, cm. lines heavy. MADE IN U.S.A.

SAL

#### COMPENSATED DECODER LADDER SECTION

FIGURE 20

COMPENSATED LADDER DECODER H.E. Zieman

54-64005

K. H. alsen 13-191

Page 1 of 7

Leo Jedynak November 9, 1955

#### ELECTRICAL ENGINEERING DEPARTMENT

## MASTER'S THESIS PROPOSAL

I. TITLE: CIRCUIT APPLICATION OF THE AVALANCHE PHENOMENON IN JUNCTION TRANSISTORS

## II. STATEMENT OF THE PROBLEM:

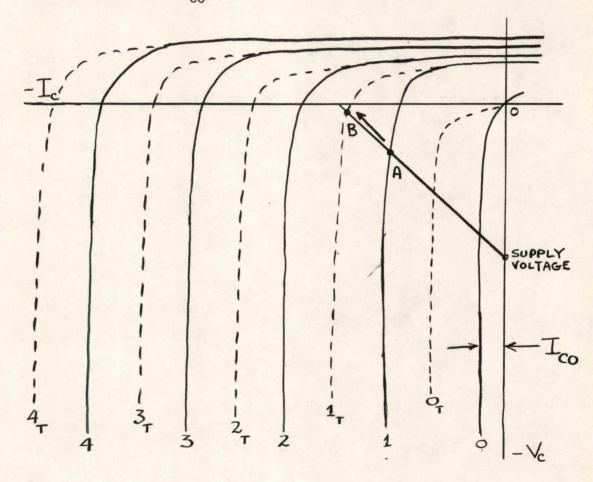

Recent research has indicated that the avalanche region of operation of junction transistors has outstanding possibilities in circuit application. Attention is to be given to the problem of application of this effect to practical circuitry. There are four distinct parts to this problem:

- 1. A survey of the variation in the static characteristics of regular low frequency junction transistors in the avalanche region of operation. At present there are no transistors whose avalanche region characteristics have been controlled in manufacture.

- Design, construction, and test of basic circuits employing the avalanche region of operation.

- Formulation of design principles for the design of circuits using the avalanche region of operation of junction transistors.

- 4. Specification of the most desirable set, or sets, of transistor static characteristics in the avalanche region.

#### III. HISTORY OF THE PROBLEM:

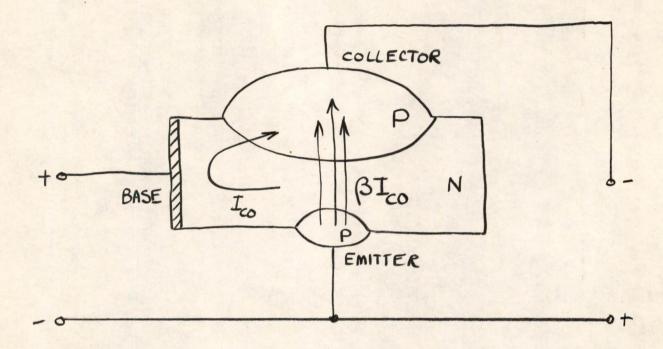

A new mode of operation of junction transistors has recently been developed. This new mode of operation employs the avalanche phenomenon which occurs in semiconductors under high electric field conditions.<sup>1,2</sup> In the region of the collector characteristics where avalanche breakdown occurs the emitter to collector current gain is equal to or greater than unity. In many ways avalanche breakdown in

transistors is similar to gaseous breakdown in cold-cathode gas tubes, with one notable exception; the control element of the transistor, the base, does not lose control after the breakdown is initiated, as is the case in gas tubes.

The sequence of events which occurs in a junction transistor as it approaches and reaches avalanche breakdown is well understood by the researchers in the semiconductor field.<sup>3</sup> The phenomenon is adequately described mathematically and thus the factors affecting the characteristics are known and can be controlled in the manufacturing process. However, there has been very little work done in actual application of the avalanche phenomenon to circuitry. Kidd, Hasenberg, and Webster of RCA have recorded the results of the application to several basic circuits and suggest that considerable attention is merited by these and other circuit applications.<sup>4</sup> They found that typical low frequency junction transistors could be made to operate at the speeds displayed by point-contact transistors. Switching times measured in millimicroseconds were found easily attainable. It was also found that for a given power dissipation the junction transistor could be operated at a higher voltage than could the point-contact transistor. In brief, the junction transistor was found to be more versatile since it has all the characteristics of both types of transistors, but not all the disadvantages.

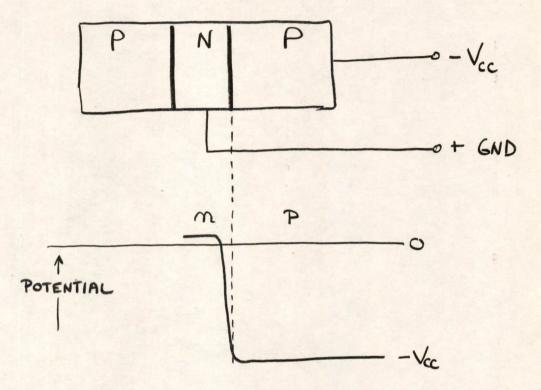

If the base electrode of a p-n-p junction transistor is positive with respect to the emitter electrode no emitter current flows and the transistor is said to be in "cutoff". If the collector voltage is now caused to become increasingly negative the depletion layer -- a region of existence of an electric field -- at the collector junction extends increasingly further into the base region and the electric field increases in strength. If surface breakdown due to contamination of the semiconductor surface, or punch-through due to the extension of the depletion layer to the emitter junction does not occur first, avalanche breakdown will eventually occur at some relatively large negative voltage -- from 50 volts to 100 volts for most types of junction transistors.

## Page 3 of 7

Avalanche breakdown occurs when a sufficient number of the holes in the depletion layer, which have been thermally generated in the base, attain sufficient energy from the electric field to produce one or more hole-electron pairs by impact ionization. The newly generated holes move rapidly to the collector and the corresponding electrons are swept back into the base region, and out the base electrode, where they forward bias the emitter into conduction. The holes injected at the emitter may now cause impact ionization and these resultant electrons bias the emitter even further into conduction. In fact, a high basecollector current gain is in operation and thus it is easily seen that the process can become highly regenerative with only a small percentage of the holes causing ionization.

The effect of the flow of electrons out of the base lead while the transistor is in the avalanche region of operation can be controlled by a resistance or a voltage. This results in a direct control of the collector current. If the base is caused to go sufficiently positive the emitter will again become back biased and the transistor will return to the cutoff state.

Operation in the avalanche region is characterized by emittercollector current gain greater than unity, by a reversal of base current from that encountered in normal operation, and by three possible output resistances. Typical collector V-I curves show a negative resistance for the highest voltages, a zero resistance for slightly lower voltages, and a positive resistance for even lower voltages.<sup>4</sup> Both p-n-p and n-p-n junction transistors display these characteristics, but investigations have indicated that the p-n-p is by far the most useable of the two.<sup>3</sup>

## IV. PROPOSED PROCEDURE:

Since no transistors are being made expressly for operation in the avalanche region it will be necessary to use regular low frequency junction transistors. The characteristics in the avalanche region will vary considerably from one unit to the next since there has been no

## Page 4 of 7

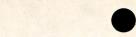

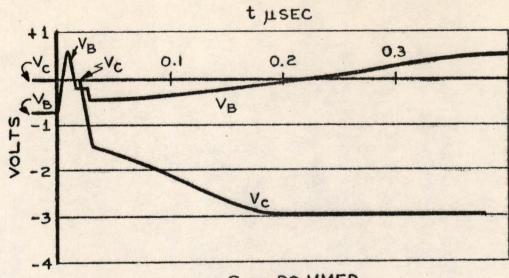

effort made to control them. A survey of the collector characteristics, in the avalanche region, of perhaps seventy-five junction transistors will be made. Both p-n-p and n-p-n transistors will be considered. From these transistors will be selected groups which display fundamental differences in characteristics. Special attention will be given to the useable range of collector voltage in the avalanche region, as well as to the magnitudes and voltage ranges of the negative and positive output resistances and the voltage range of the zero output resistance region. The linearity or nonlinearity of the characteristics will also be considered.