· ----

March 20, 1962

J. W. HAANSTRA ET AL

3,026,036

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

<sup>87</sup> Sheets-Sheet 3

Filed Jan. 24, 1956

<sup>87</sup> Sheets-Sheet 4

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

FIG. 3b

#### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

FIG. 4b

| March 20, 1962 | J. W. HAANSTRA ETAL     | 3,026,036 |

|----------------|-------------------------|-----------|

|                | DATA TRANSFER APPARATUS |           |

Filed Jan. 24, 1956

87 Sheets-Sheet 10

FIG. 6a

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

Filed Jan. 24, 1956

87 Sheets-Sheet 15

FIG. 10

# J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS 3,026,036

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS 3,026,036

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

87 Sheets-Sheet 22

FIG. IIg

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

87 Sheets-Sheet 23

F/G. // h

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

87 Sheets-Sheet 25

FIG. II j

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

### 87 Sheets-Sheet 26

FIG. 11 k

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

87 Sheets-Sheet 27

FIG. 111

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

J. W. HAANSTRA ET AL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

Filed Jan. 24, 1956

DATA TRANSFER APPARATUS

#### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

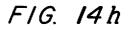

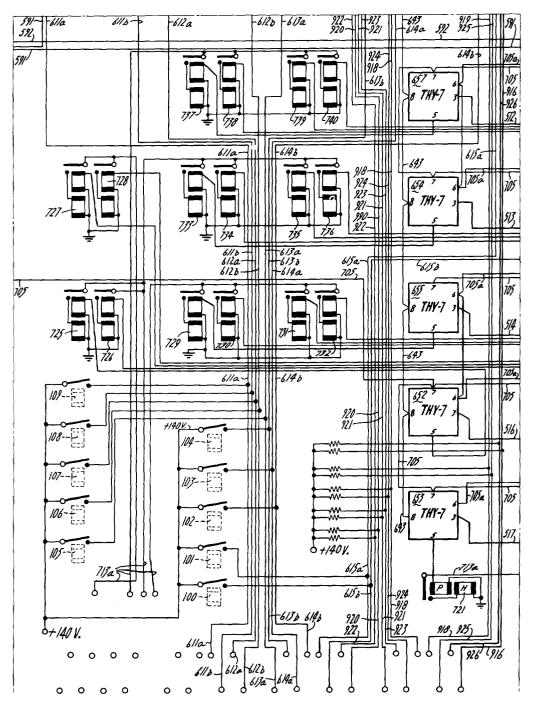

87 Sheets-Sheet 36

FIG. 14g

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS Filed Jan. 24, 1956

### J. W. HAANSTRA ET AL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

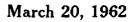

FIG. 14 i

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

87 Sheets-Sheet 39

FIG. 14j

Filed Jan. 24, 1956

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

FIG. 19

# FIG. 16

11

1

111

1

1

//

11

1 1

1 /

1

Γ,

1

17

11

11

17

Α

8 11 11

С 7

D ///

Ε

F 11

G 7 11

н

I

J

к

L

M

N

0 P Q

R

S Т

W

X 1

z 8

× 11

\$

\*

。

# 0

11 U v

7 Y

111

///

1/ 11

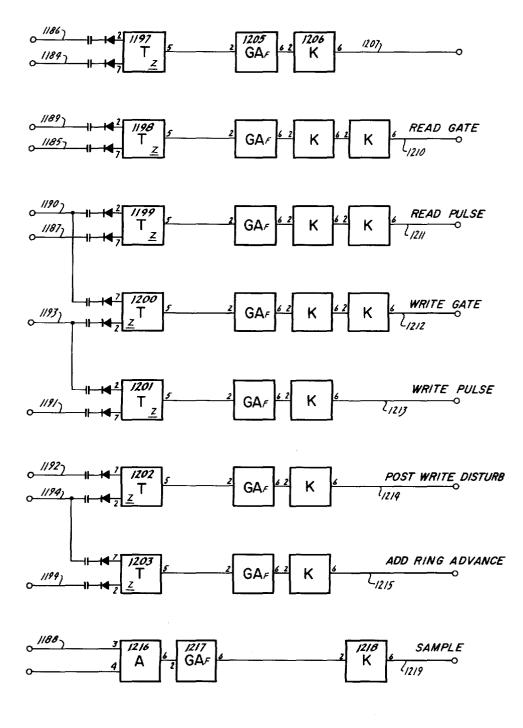

bs bx b b2 b4 b8 b<sub>R</sub> bs bo Bit Time A Clock E<sub>2</sub> Cycle Gate Char. Reg. Reset Buffer Operation --- Scan Char. Out of Char. Reg. -Buffer Cycle on E2 Cycle õ 2 6 8 9 ١Q 11 12 13 14 Char. Reg. Reset Read Gate Read Pulse Sample Write Gate Write Pulse Inhibit Post Write Disturb

#### Timing Diagram For E, Cycle

Address Ring Advance

Timing Diagram For E2 Cycle

| Bit Time                             | $b_{S}$ $b_{O}$ $b_{X}$ $b_{i}$ $b_{2}$ $b_{4}$ $b_{8}$ $b_{R}$ $b_{S}$ |

|--------------------------------------|-------------------------------------------------------------------------|

| A Clock                              |                                                                         |

| E, Cycle Gate                        |                                                                         |

| Char. Reg. Reset<br>Buffer Operation |                                                                         |

| ,                                    | - Scan Char. in Char. Reg.                                              |

#### Buffer Cycle on E, Cycle.

|                          | Ŷ  | ļ  | 2 | 3  |   | 4 | 5 | ę  | 7  | 8 | 9             | 10  | ļ | 12 | 13 | 14      |

|--------------------------|----|----|---|----|---|---|---|----|----|---|---------------|-----|---|----|----|---------|

| Read Gate                |    | r  |   | -+ |   | ┢ | ┶ |    |    |   | _             |     |   |    |    | $\perp$ |

| Read Pulse               | +  | -  | _ | _  | _ |   |   | 1_ |    | _ |               |     | _ | _  | _  | _       |

| Write Gate               | +- | ┿╌ | - | -  |   | - | + | -  |    | _ |               | 1   | _ |    |    | +       |

| Write Pulse .<br>Inhibit |    |    |   |    |   |   |   | F  | ‡- | + | $\rightarrow$ | -+- | ╉ | +  | -+ | +       |

| Post Write Disturb       |    |    | _ |    |   |   |   | 1  |    | _ | _             | _r  | Ŧ | T  |    |         |

| Address Ring Advance     |    |    |   |    |   |   |   |    |    |   |               |     |   |    | -  | L       |

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

FIG. 18

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS 3,026,036

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

# J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

Filed Jan. 24, 1956

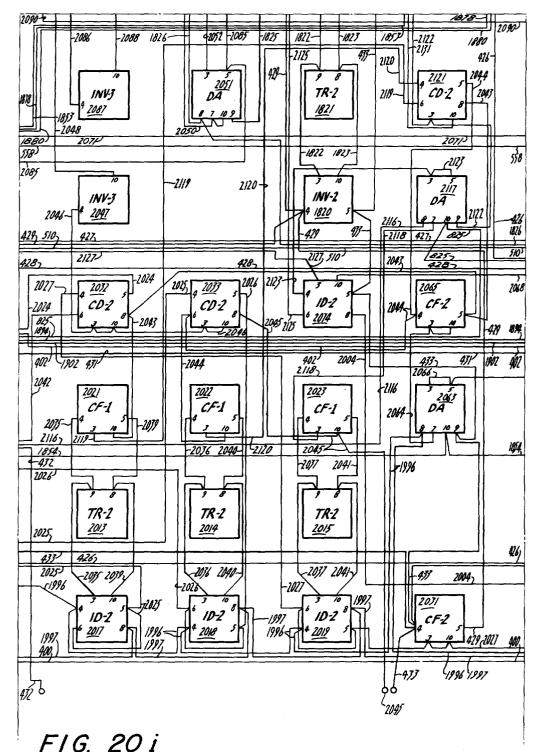

87 Sheets-Sheet 50

FIG. 20g

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS 3,026,036

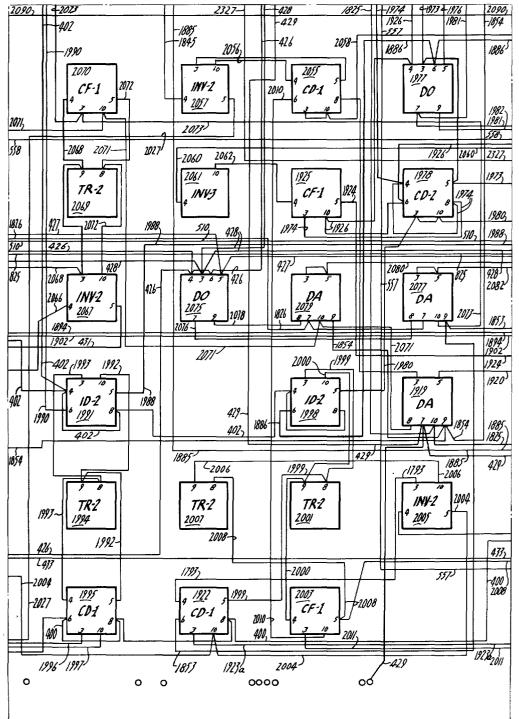

Filed Jan. 24, 1956

FIG. 20h

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS Filed Jan. 24, 1956

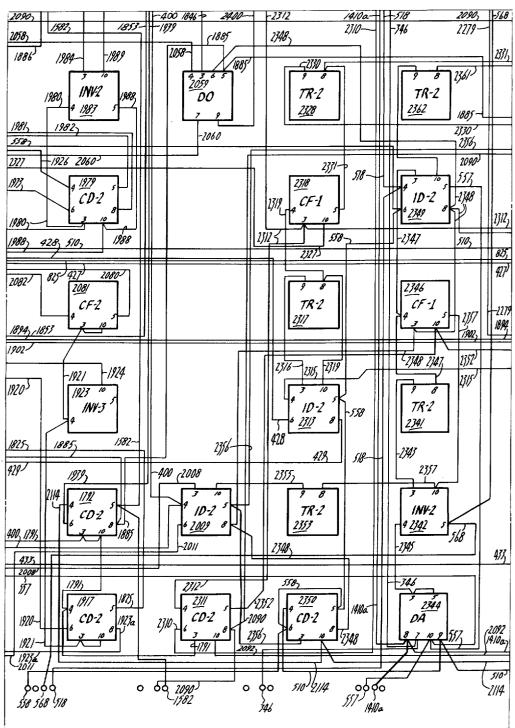

#### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS Filed Jan. 24, 1956

87 Sheets-Sheet 53

FIG. 20 j

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

FIG. 20 k

Filed Jan. 24, 1956

J. W. HAANSTRA ETAL

3,026,036

FIG. 201

### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

Filed Jan. 24, 1956

87 Sheets-Sheet 57

FIG. 22

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

87 Sheets-Sheet 59

FIG. 25

1 . 1 March 20, 1962

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

# J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

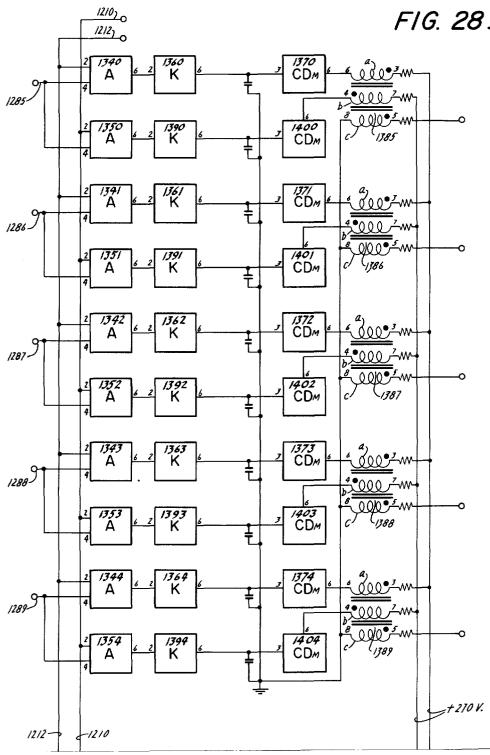

FIG. 28a

3,026,036

DATA TRANSFER APPARATUS

87 Sheets-Sheet 63

FIG. 28 b

Filed Jan. 24, 1956

3,026,036

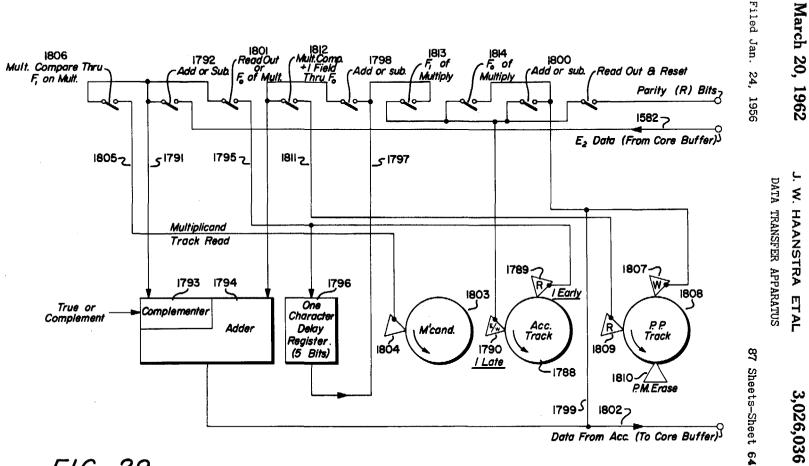

FIG. 29

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS 3,026,036

Filed Jan. 24, 1956

J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

### J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

87 Sheets-Sheet 67

•

### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

#### J. W. HAANSTRA ETAL

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

Filed Jan. 24, 1956

FIG. 34

FIG. 35

0

100

2239

0

225420 225022

2255

2249

bad

6-3

IN

ACC. O/FLO.

٦¦

ACC.O

22387

0-+

IN

č O NO O YES -@

2250 g

[=]

2248 Ø

F=3

6:23

ACC. 1

J. W. HAANSTRA ETAL

3,026,036

DATA TRANSFER APPARATUS

87 Sheets-Sheet 71

Filed

Jan.

24, 1956

₿₽

8 B I

Ē

**8** 6

**0**6

02 09

**o** 3

d

FIG. 37

### March 20, 1962

#### J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS

3,026,036

Filed Jan. 24, 1956

87 Sheets-Sheet 75

### FIG. 39a

|                                                                                        | F                                                                                                   |                                                                                                  | F        |                                           | F2                      | F3                                                 |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------|-------------------------------------------|-------------------------|----------------------------------------------------|

|                                                                                        | C <sub>O</sub> C <sub>I</sub> C <sub>C</sub> C <sub>3</sub> C <sub>4</sub> C<br>-1-1-1-1-1<br>00 0: | 5<br>5<br>5<br>5<br>5<br>5<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |          | 20<br>       ·                            | 25 30                   | <b>36</b>                                          |

| CUSTOMER ORDER<br>CARD INPUT<br>TRACK A                                                | NO.   1                                                                                             | C CUSTI<br>O ORDEI<br>D NO.                                                                      |          | ITEM 1<br>IUMBER QTY.                     | ITEM 2<br>NUMBER QTY    | ITEM 3                                             |

| CUSTOMER FILE RECORD<br>TRACK B                                                        | NO. 1                                                                                               | CA<br>OR<br>DEA                                                                                  |          | REDIT PRESE<br>MAX. DEB<br>BALAI          |                         | OMER NAME                                          |

| CUSTOMER PRINTING RECORD<br>(INVOICE HEADING)<br>TRACK C                               | I NO. II                                                                                            |                                                                                                  | S S OF   | USTR ORDER<br>DATE<br>NO. MOIDA           | CUST                    | OMER NAME                                          |

| ITEM OUTPUT RECORD<br>TRACK C                                                          | CUST'R                                                                                              |                                                                                                  | 2  &  ŌA | ISTR ORDER<br>IDER<br>NO.<br>MOIDA        | ITEM ITEM<br>CLASS CODE | DESCRIPTION                                        |

| BACK ORDERED ITEM<br>TRACK C                                                           | CUST'R                                                                                              | C A C R C A C A C A C A C A C A C A C A                                                          |          | IST'R ORDER<br>RDER DATE<br>NO.<br>MOI DA | ITEM ITEM<br>CLASS CODE | DESCRIPTION                                        |

| ACCOUNTS RECEIVABLE<br>INVOICE SUMMARY RECORD<br>INVOICE TOTAL FOR PRINTING<br>TRACK C | CUST'R                                                                                              |                                                                                                  |          | EDIT OLD<br>IAX. BALAN                    | CUST                    | 0MER NAME                                          |

| ITEM FILE RECORD<br>TRACK D                                                            | I NO. II                                                                                            |                                                                                                  |          |                                           | ITEM ITEM<br>CLASS CODE | DESCRIPTION                                        |

| SALES ANALYSIS<br>MINIMUM BALANCE<br>TRACK D                                           | ITEM C<br>NO. [                                                                                     |                                                                                                  |          |                                           | ITEM ITEM<br>CLASS CODE | DESCRIPTION                                        |

| ACCUMULATORS                                                                           |                                                                                                     | PRODI                                                                                            |          |                                           |                         | NEW ITEM<br>BAL.                                   |

|                                                                                        | ······<br>00 05                                                                                     |                                                                                                  |          | 20                                        | 25 30                   | <del>1                                      </del> |

March 20, 1962

J. W. HAANSTRA ETAL DATA TRANSFER APPARATUS 3,026,036

Filed Jan. 24, 1956

ł

87 Sheets-Sheet 76

## FIG. 39b

| F <sub>4</sub>                               |                             | F5            | Fe                                            |                      | F7                   | F <sub>8</sub>                                                                                             |                                       | F9                                                |

|----------------------------------------------|-----------------------------|---------------|-----------------------------------------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------|

| 40 45<br>-1 1 1 1 1 1                        | <b>50</b>                   | 55 6          | 0 <b>65</b>                                   | 70                   | 75                   | 80 85                                                                                                      | <b>90</b>                             | 96 99                                             |

| ITEM 4                                       | ITEM 5                      | ITEI          |                                               | M 7                  | ITEM 8               | ┲┲┲┲┲┲┲<br>┫                                                                                               | <del>, , , ,</del> , ,                | · <del>· · · · · · · · · · · · · · · · · · </del> |

|                                              | NUMBER QT                   | Y. NUMBER     |                                               | R GTY. NUI           | MBER QTY.            |                                                                                                            |                                       |                                                   |

|                                              |                             | * * * * * * * | <u>, , , , , , , , , , , , , , , , , , , </u> | ╶╾┰┰┎┊┑              |                      | <del>,,,,,,,,,</del> ,                                                                                     | 1 "1 1                                | <del>╶╷╷╷╷╷╷╷╷</del>                              |

|                                              |                             | STREET A      | DDRESS                                        |                      | СІТ                  | Y & STATE                                                                                                  |                                       |                                                   |

|                                              |                             |               | $\frac{1}{1}$                                 | ╶┬╶┱╻╸┱╶             | ╶┧╶┰╌╻┯╌┾╴           | ┑ <del>┍┍╛</del> ┶┊╛╧<br>╕ <del>┍</del> ╺┍╶╛╺                                                              | -1                                    | -+ <del> </del>                                   |

|                                              |                             | STREET A      | DDRESS                                        |                      | CIT                  | Y & STATE                                                                                                  |                                       | INVOICE<br>NUMBER                                 |

|                                              |                             |               |                                               |                      | 1111                 |                                                                                                            |                                       |                                                   |

| <u></u>                                      |                             |               | VI OTY                                        | TENSION              | NEW<br>BAL.          | <u>,,,,,,,,,</u>                                                                                           | ┼╶ <u>┲╶</u> ┰╶┇╶╿                    |                                                   |

|                                              |                             |               |                                               | ACK MIN.             |                      | Y<br>X<br>Z<br>D<br>D<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L<br>L | ┬┌┬┰╕<br><u>┺╘╘</u> ┟                 | <u>┈╷╷╷┍╷┍╷╷</u>                                  |

|                                              | CURRENT<br>DEBIT<br>BALANCE |               | Y'S AMOUN<br>CE THIS II                       |                      | CEEDS<br>REDIT<br>BY |                                                                                                            | ╶╷╌┰╷                                 | ╶┇╽╻┧╡╿┨                                          |

|                                              | y l                         |               |                                               | ACK MIN.<br>IDER BAL |                      | ┍┎ <u>╻╺</u> ╻┙┙┙                                                                                          | ╷╷╷╷╷╷                                | <del></del>                                       |

| <u>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,</u> | U U                         | PRICE QT      | OLD<br>TY ITEM EX<br>BAL.                     | TENSION              | NEW<br>ITEM<br>BAL.  | ┍┰┰╻┊╎╷                                                                                                    | , , , , , , , , , , , , , , , , , , , |                                                   |

| INVOICE TOTA<br>NEW DEBIT<br>BALANCE         |                             |               |                                               | ТОТА                 | AL BACK<br>RDER      |                                                                                                            |                                       |                                                   |

| • • • • • • • • • • • • • • • • • • •        |                             | 55 60         |                                               | 77777777<br>70       |                      | 80 85                                                                                                      | 90                                    | 95. 99                                            |

Filed Jan. 24, 1956

¢

### March 20, 1962

Filed Jan. 24, 1956

87 Sheets-Sheet 81

# F/G. 44

| FIG. | F1G. | F1G. | FIG. | FIG. | F/G. |

|------|------|------|------|------|------|

| II a | 11 b | 11 c | 11 d | II e | f    |

| FIG. | F1G  | F/G. | F1G. | F1G. | F1G. |

| IIg  | 11 h | i    | 11 j | 11 k | 11 1 |

| FIG.         | FIG.         | F1G.         | FIG.         | F1G. | FIG.  |

|--------------|--------------|--------------|--------------|------|-------|

| 14 a         | 14 b         | 14c          | 14d          | 14e  | 14 f  |

| FIG.<br>14 g | FIG.<br>14 h | F1G.<br>14 i | F1G.<br>14 j | FI   | G. 45 |

|   | FIG.<br>20 b | FIG.<br>20d  |             | FIG.<br>20 f |

|---|--------------|--------------|-------------|--------------|

| i | FIG.<br>20 h | FIG.<br>20 j | F/G.<br>20k | F1G.<br>201  |

F/G. 46

Filed Jan. 24, 1956

-130 V.

**ې**5

òв

<u>10-2</u> FIG. 59

87 Sheets-Sheet 83

#### March 20, 1962

•**6**

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

March 20, 1962

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

DATA TRANSFER APPARATUS

Filed Jan. 24, 1956

1

#### 3,026,036

DATA TRANSFER APPARATUS John W. Haanstra and Roy L. Huag, San Jose, Murray L. Lesser, Palo Alto, and Louis D. Stevens and William W. Woodbury, San Jose, Calif., assignors to International Business Machines Corporation, New York, N.Y., a corporation of New York Filed Jan. 24, 1956, Ser. No. 565,293 14 Claims. (Cl. 235–157)

This application is a continuation-in-part of the copending U.S. patent application Serial No. 525,446, now abandoned, filed August 1, 1955, and the invention disclosed herein relates generally to data processing machines. More particularly, this invention pertains to a <sup>15</sup> data processing device adapted to handle technical business transactions sequentially as they occur and to reflect each transaction concurrently into all accounts which it affects.

This processing technique, referred to herein as "in- 20 line" data processing, is made possible by the utilization of a high capacity random access memory device such as is disclosed in the copending U.S. patent application Serial No. 477,468, filed December 24, 1954, to any portion of which reference may be made in a short period 25of time, together with the novel data processing unit disclosed herein. The ability to obtain any record stored in the memory without appreciable loss of time makes possible the posting of transactions as they occur and 30 leads to the availability of more timely information. Consequently, a closer control over business transactions may be had. In the area of inventory control and billing, for example, the machine may, from a single order, determine availability, price each item, adjust stock balances, 35 invoice the customer, prepare accounts receivable records, accumulate data for sales analysis, and credit salesmen's commission accounts, etc. The procedures made possible by the ability to store a large quantity of data, any portion of which may be obtained at random in a short 40 period of time, eliminates the need for sorting, collating and successive runs, as is the practice in business installations utilizing present day machines. Current processing of data means dynamic accounting instead of a history for management to review. Closer control over inventory, for example, results in reduced inventory charges and increased service to customers by reducing back orders. Continuous processing made possible by the machine of the invention eliminates the need for data to accumulate before making a run, as is now customary. 50This makes possible the continuous flow of data through an office and results in a smoother, more efficient operation.

The present invention is additionally concerned with a unique magnetic data processing apparatus wherein data is transferred within the machine in fully variable word lengths, such transfer being accomplished under the control of both internal and external instructions, whereby such control is selectively exercised in response to logical decisions reached by the apparatus during processing.

It is one object of the present invention, therefore, to <sup>60</sup> provide an improved data processing machine.

Another object is to provide an in-line data processing machine wherein individual transactions are processed as they occur in a more useful and economical manner than is possible with machines presently in use.

A further object is to provide a data processing machine having an improved access time to a desired portion of a storage medium whereby data is processed in an in-line fashion with ready reference to master data recorded in the storage medium. 70

Another object is to provide an improved data process-

ing machine having a large capacity addressable memory, to any portion of which access may be had at random under control of both data being processed by the machine and programmed instructions.

Still a further object is to provide a data processing machine having a random access memory wherein the data entered in the machine is processed together with selected data stored in the momory under the control of the entered data and stored program.

Another object is to provide an apparatus wherein data of variable word lengths determined by stored programs is transferred from predetermined storage locations to other predetermined storage locations with unlimited flexibility.

A still further object of the invention is to provide a machine of the type described wherein data is processed under control of both internal and external instructions selectively employed according to a command of the apparatus based upon findings yielded by data in process.

Still another object is to provide a machine wherein data is entered for processing under control of programmed instructions, which machine is adapted to seek additional data from storage for processing together with entered data, the identity of the location of the additional data being under control of both the entered data and the programmed instructions.

A further object is to provide a data processing machine employing a high capacity magnetic storage medium wherein instructions programmed in the machine are arranged to cause a magnetic transducer associated with the storage medium to move to a location adjacent the recording surface controlled by the identity of data entered for processing, whereby entered data is processed together with selected data from storage determined by the entered data and in a manner controlled by the programmed instructions.

Another object is to provide a novel data processing apparatus operable under the control of sequences of simple and straight-forward instructions, each of which defines the source and destination of data to be transferred.

In general, machines of the type under consideration are based on one of two techniques: a fully stored program, or a fully wired (control panel) program, each of which has its advantages and disadvantages. It is another object of this invention, therefore, to provide a data processing machine utilizing an optimum combination of the stored program and control panel techniques.

Another object is to provide a data processing machine wherein data transfer is under the control of stored program and decisions are made by wired program.

A further object is to provide a data processing machine arranged to automatically check the accuracy of data recorded in selected portions of the storage of the machine upon the recordation thereof, without the provision of additional program steps, to thereby aid in the maintenance of accurate records with a minimum of programming.

Still another object is to provide a machine of the type described arranged to initiate operations such as read-in, read-out, etc., either directly in response to instructions taken from stored program or indirectly in response to the condition of decision elements examined as a result of an instruction taken from stored program.

A still further object is to provide such a machine adapted to compare selected fields of alphabetic and/or numeric data under the control of a single instruction.

Other objects of the invention will be pointed out in the following description and claims and illustrated in the accompanying drawings which disclose, by way of example, the principle of the invention and the best mode which has been contemplated of applying that principle. In the drawings:

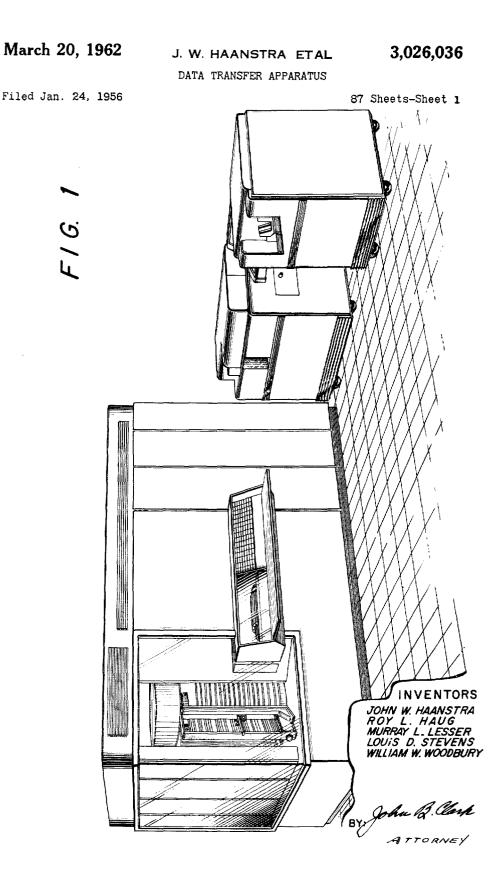

FIG. 1 is a perspective view of the machine of the invention.

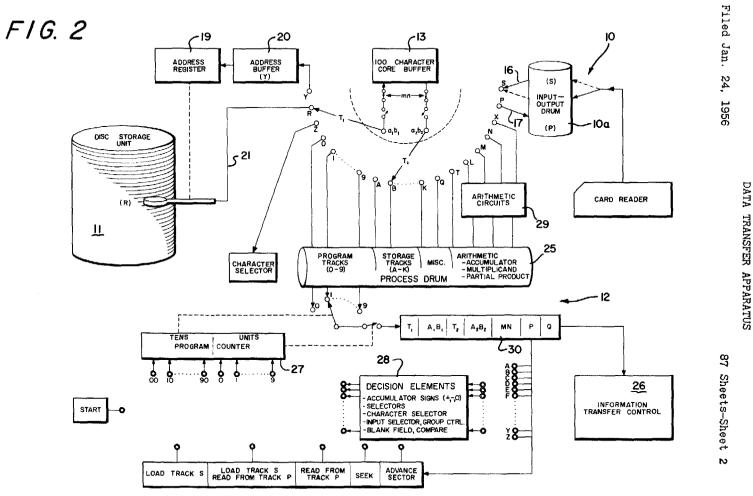

FIG. 2 discloses a block diagram of the machine dis- 5 closed in FIG. 1.

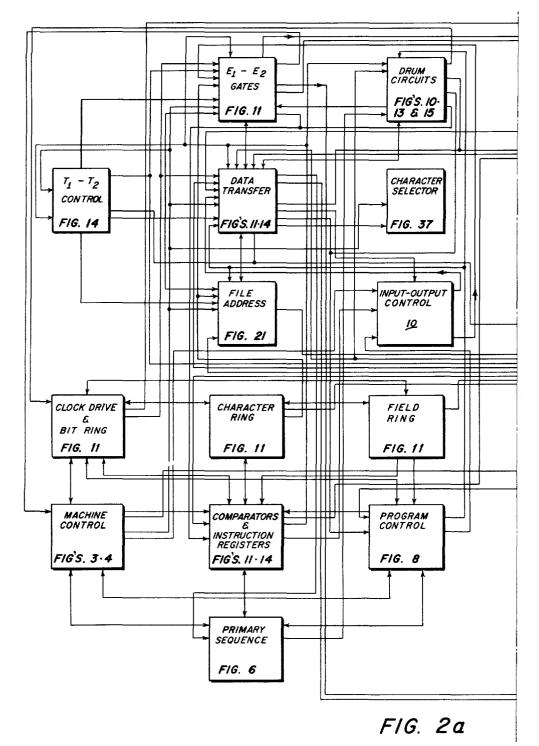

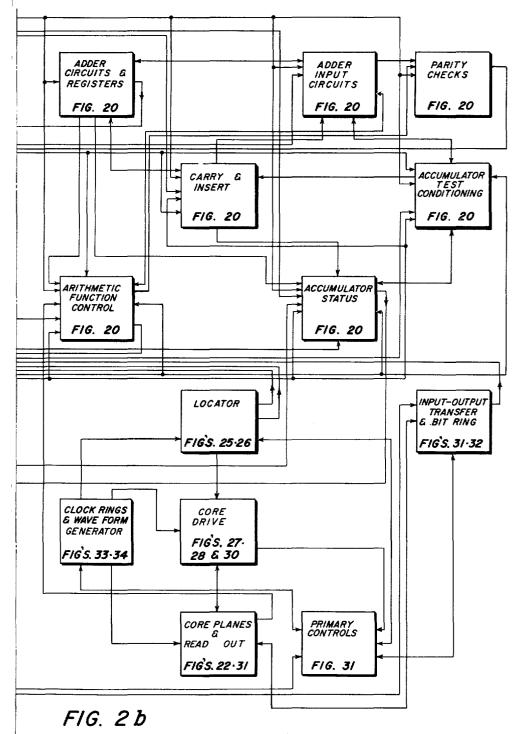

FIGS. 2a and 2b disclose a more detailed block diagram of the machine disclosed in FIG. 1.

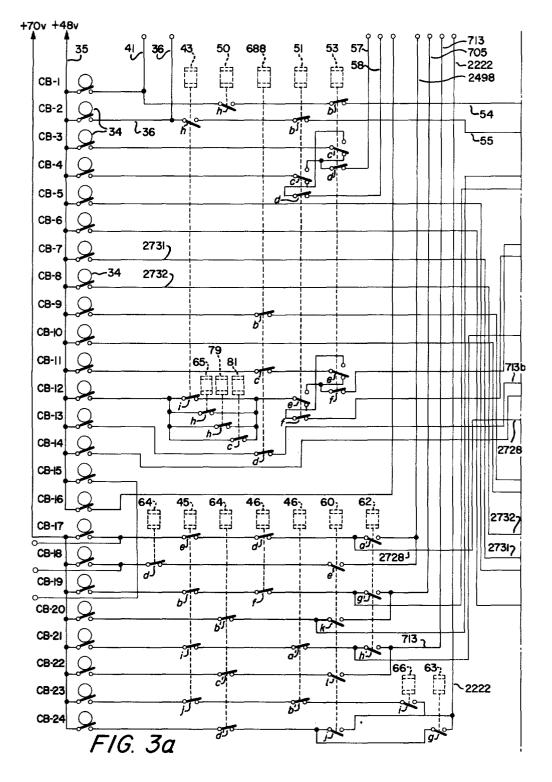

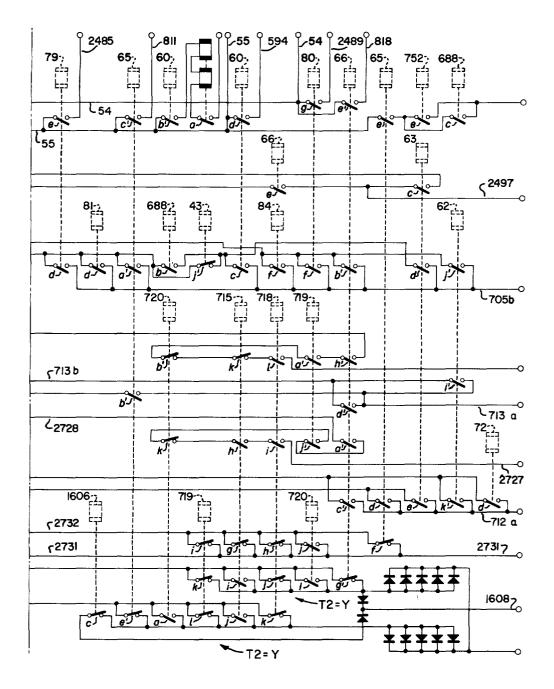

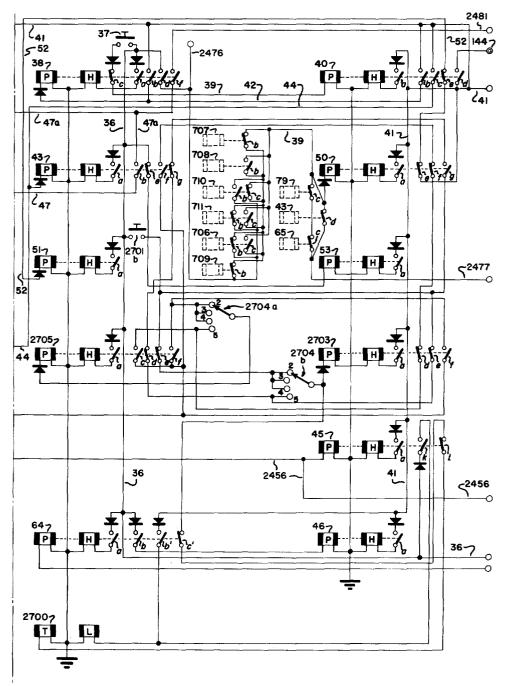

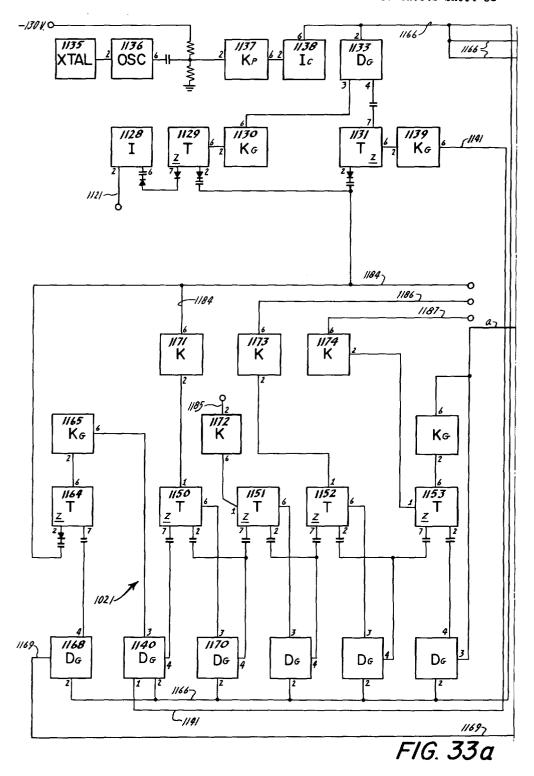

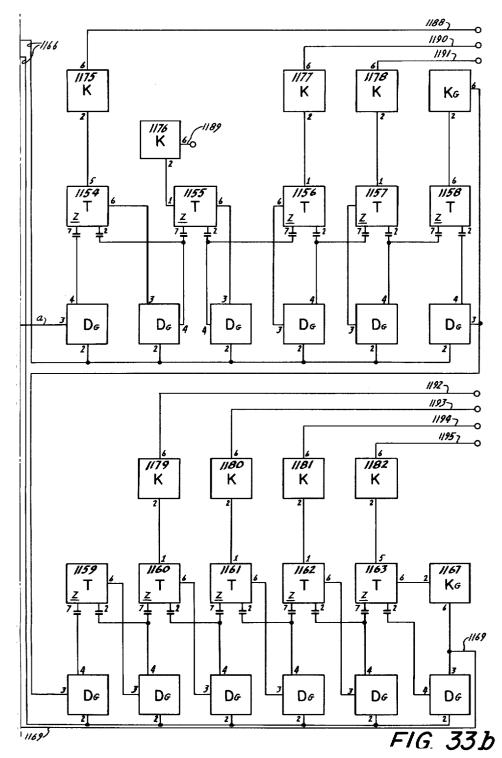

FIGS. 3a and 3b, when placed adjacent each other, disclose the circuitry for controlling the basic timing of 10the present machine.

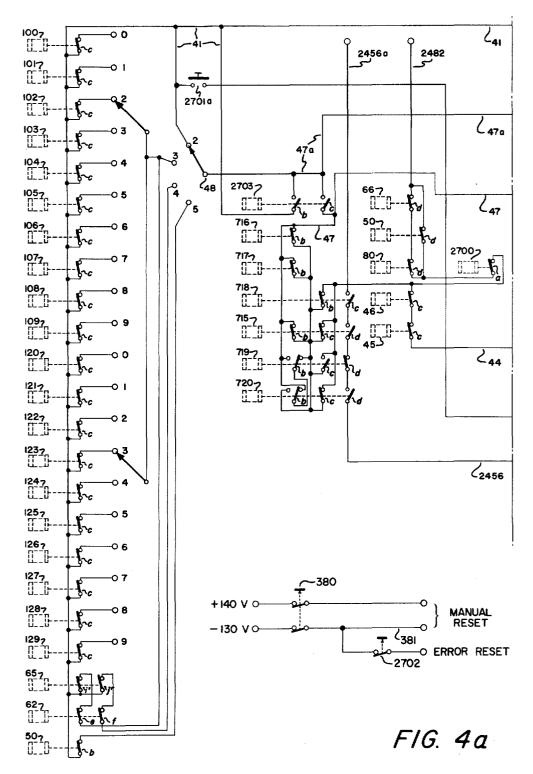

FIGS. 4a and 4b, when placed adjacent each other, disclose circuitry for providing various interlocks utilized in the operation of the machine.

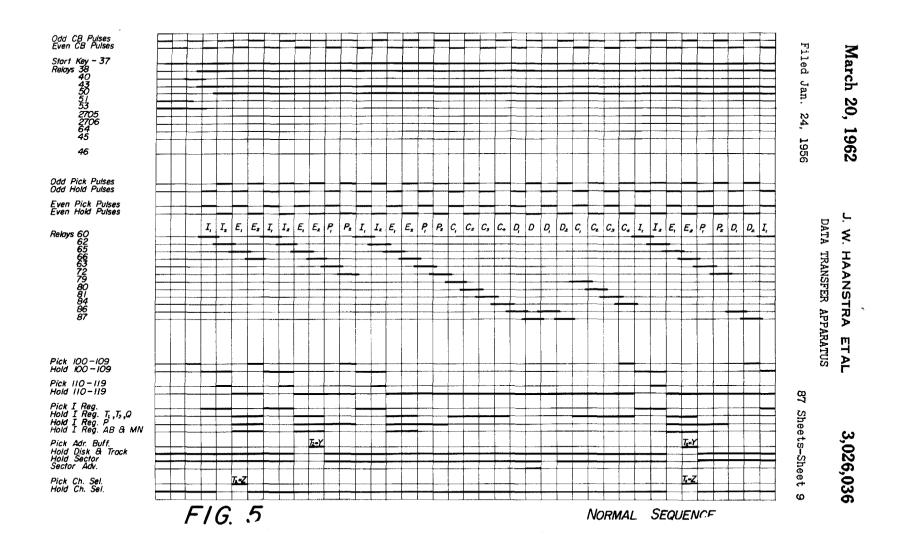

FIG. 5 is a timing chart which discloses the normal 15 with FIG. 20. sequence of operation of the various relays shown in FIGS, 3, 4 and 6.

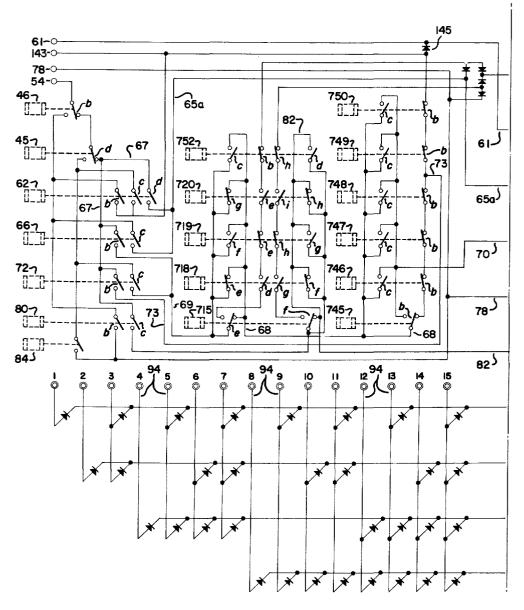

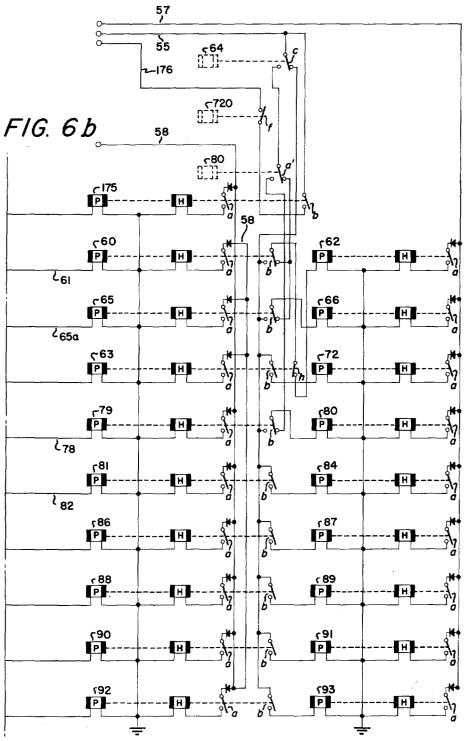

FIGS. 6a and 6b, when placed adjacent each other, disclose the primary sequence relays for defining the various operating cycles utilized herein.

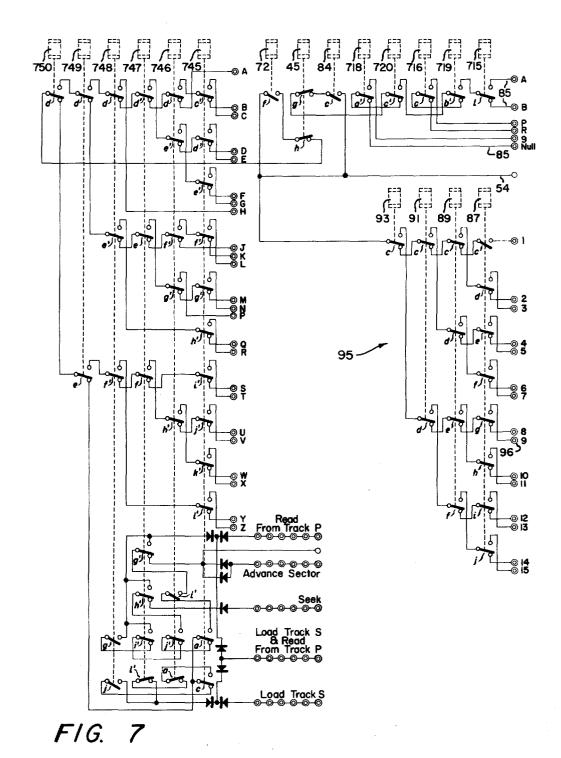

FIG. 7 discloses various hubs associated with the control panel, together with associated circuitry.

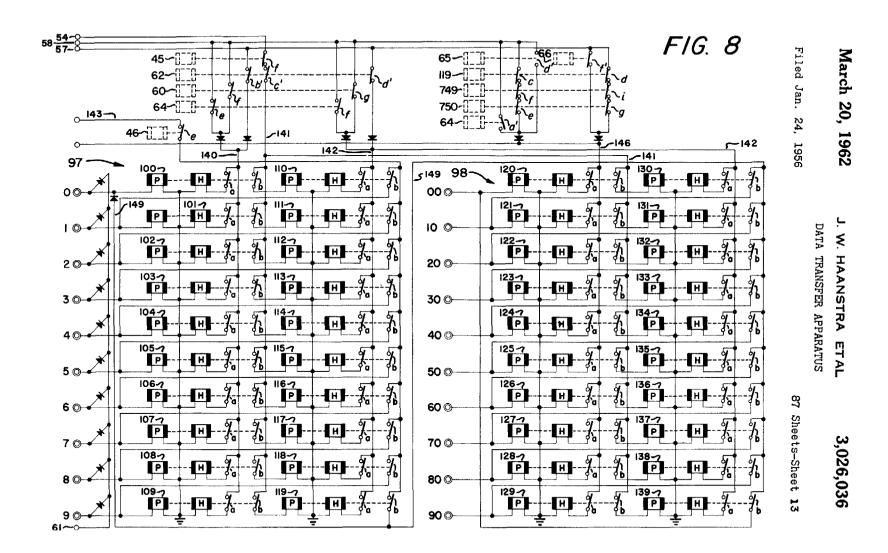

FIG. 8 is a schematic diagram of the program counter of the invention.

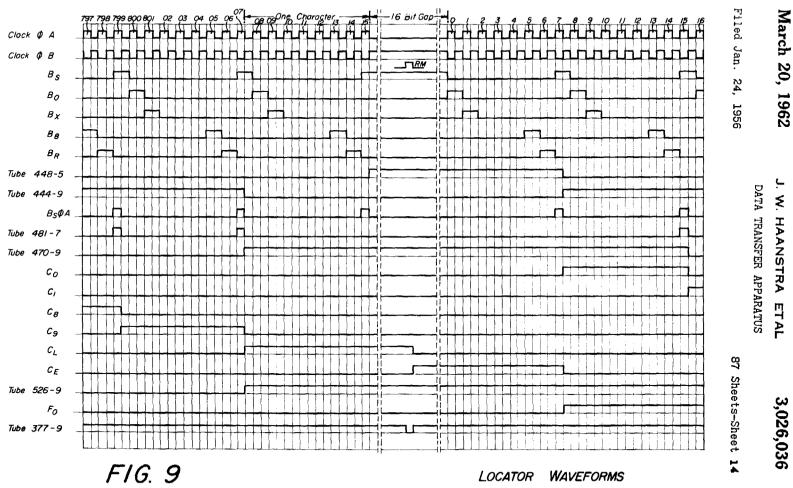

machine.

FIG. 10 discloses various read and write amplifier circuits utilized in connection with the various magnetic recording tracks.

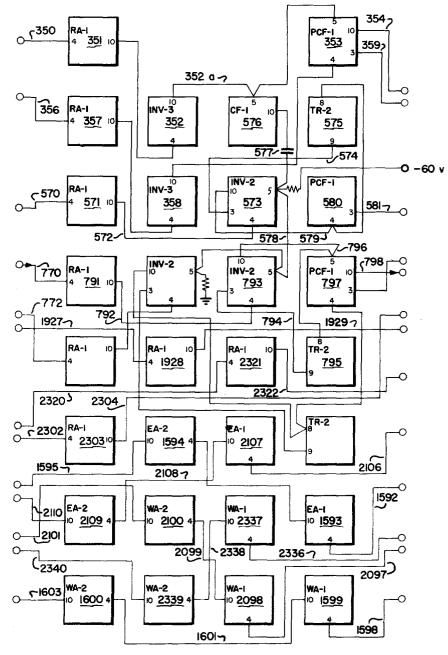

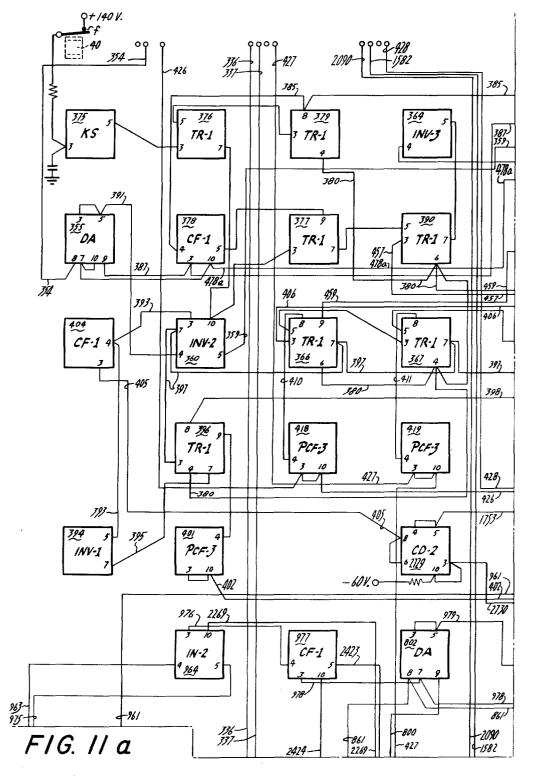

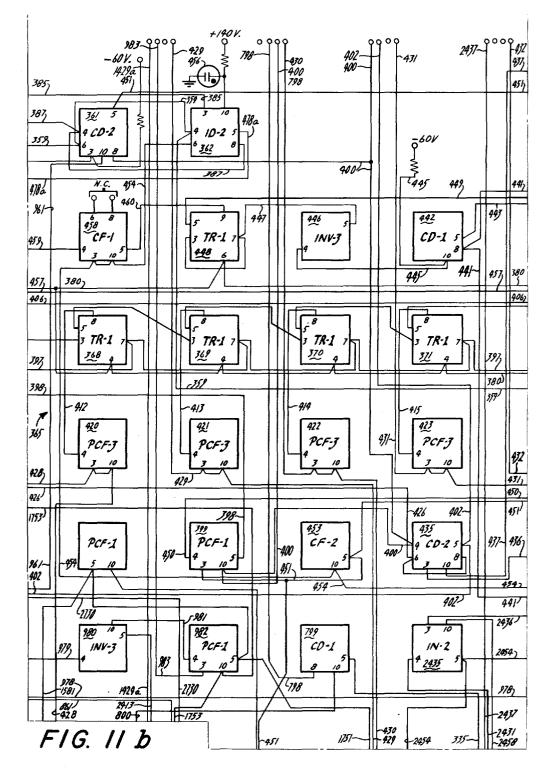

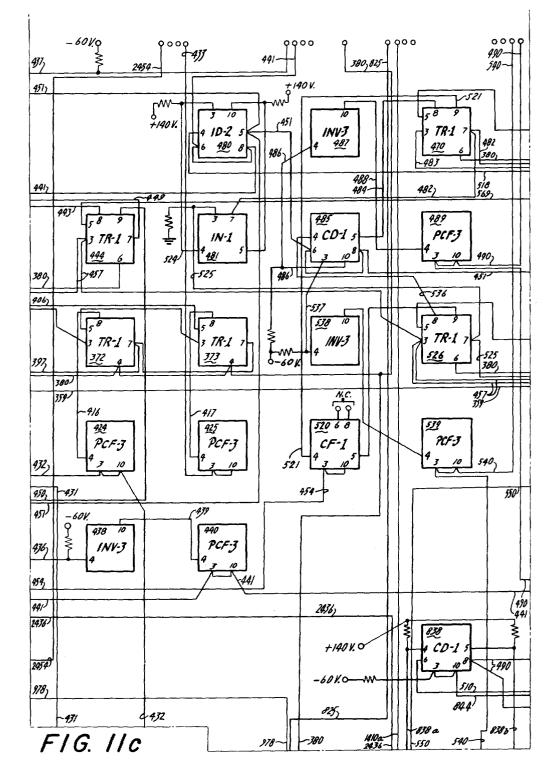

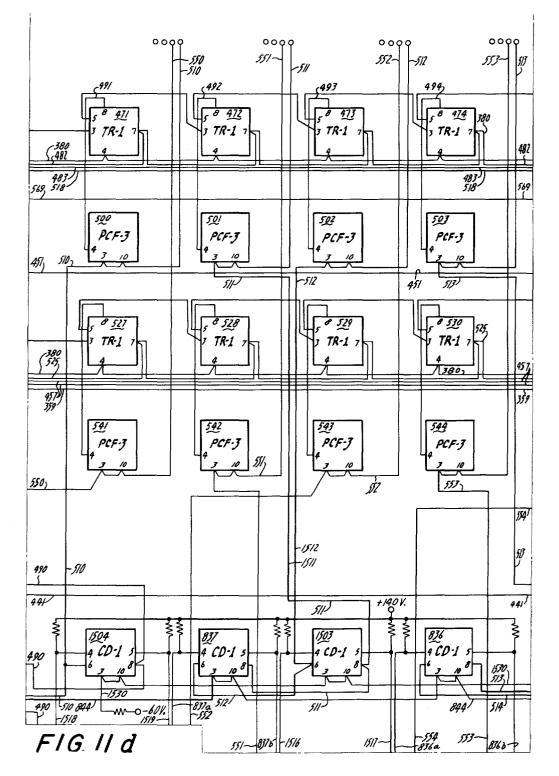

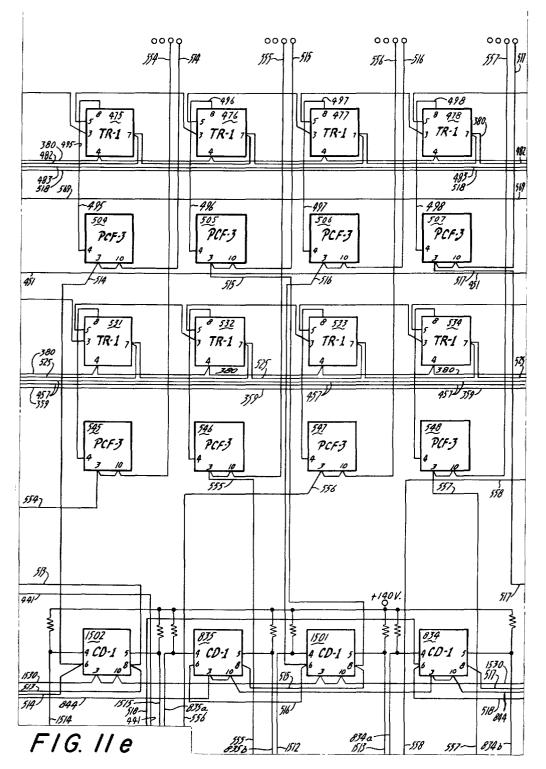

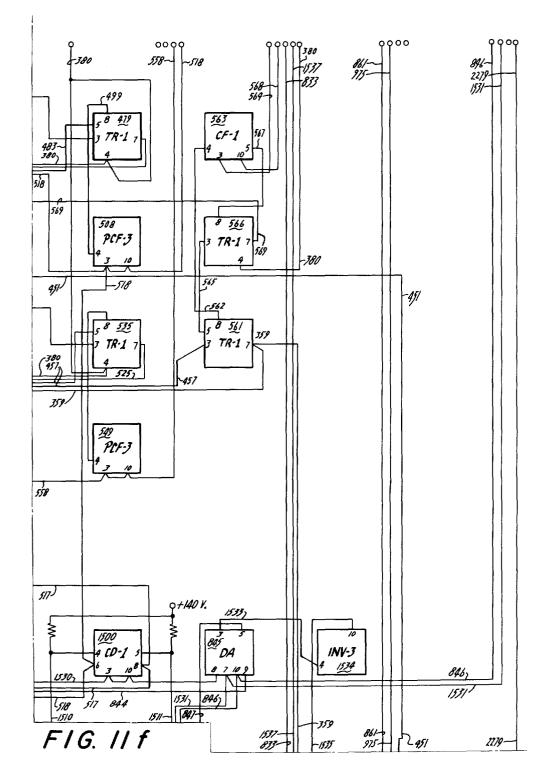

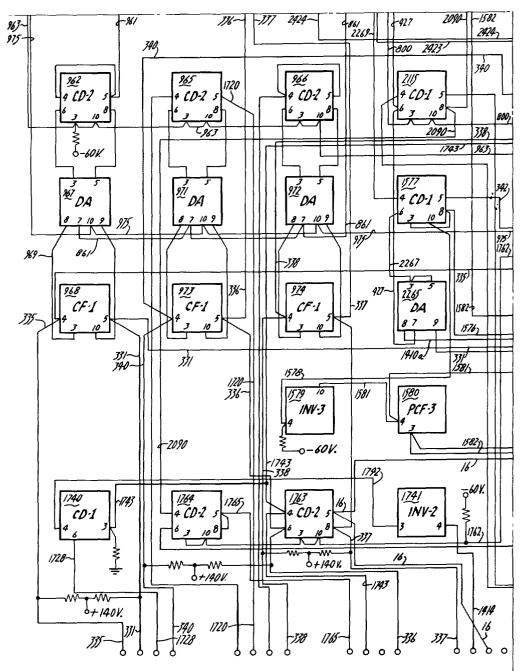

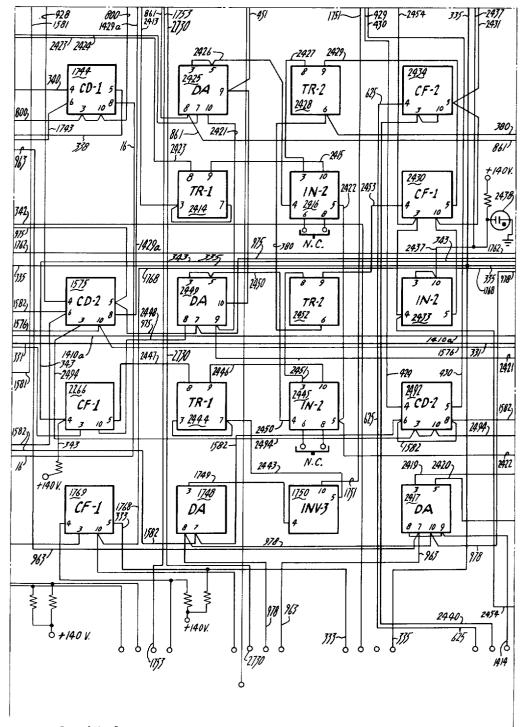

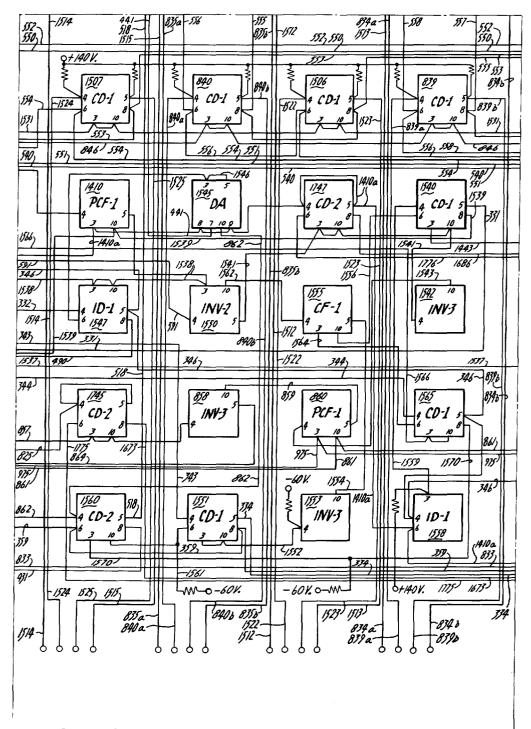

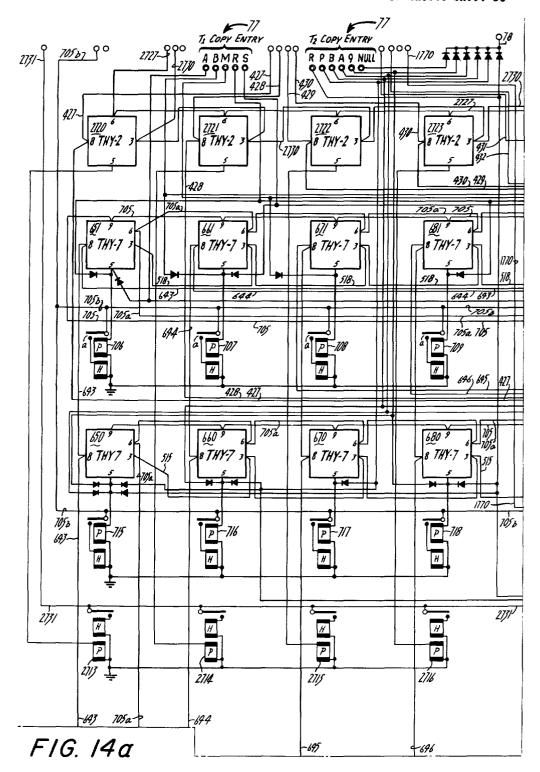

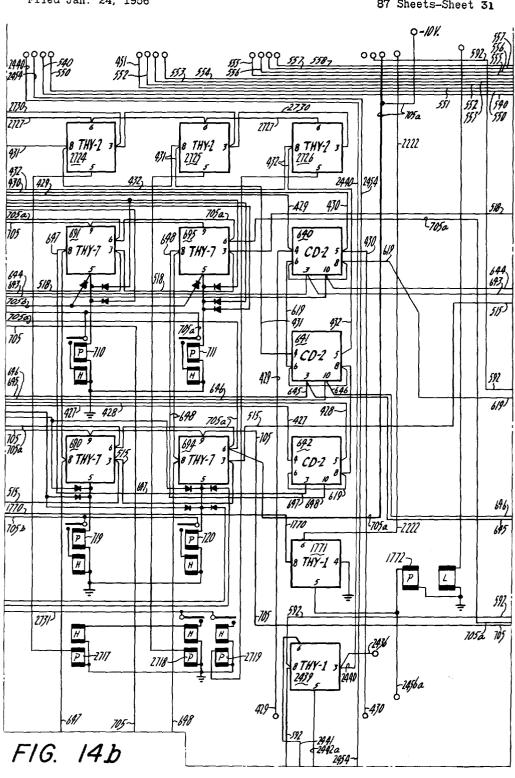

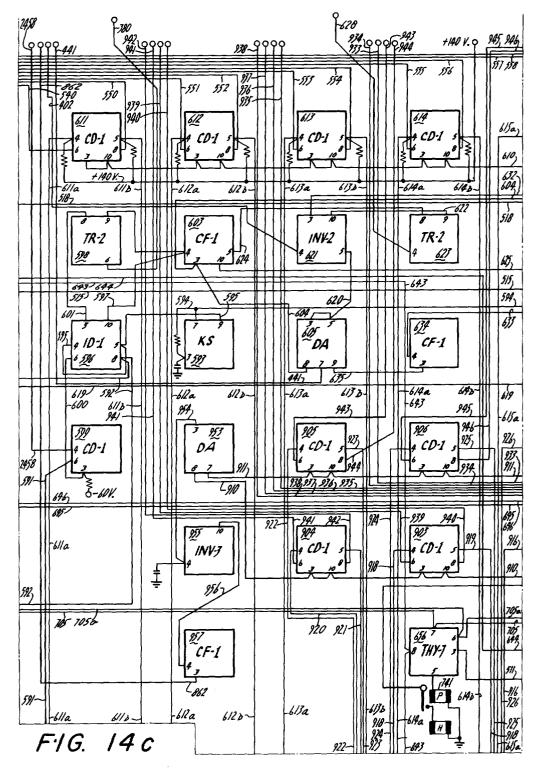

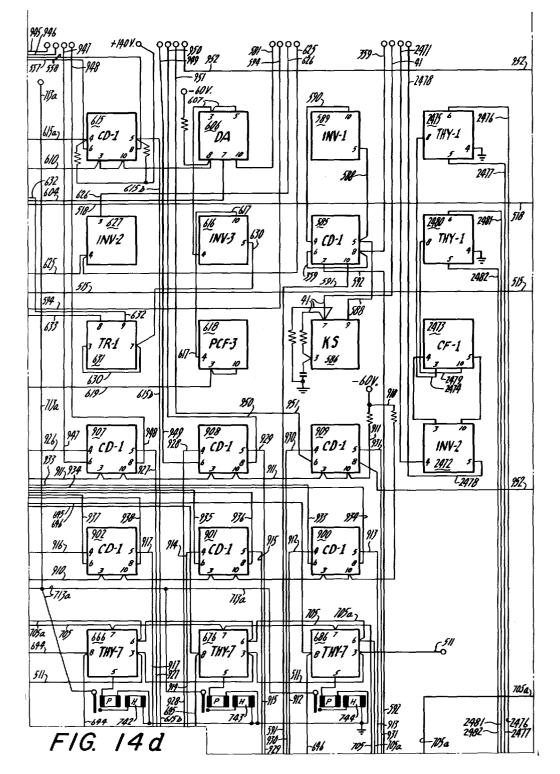

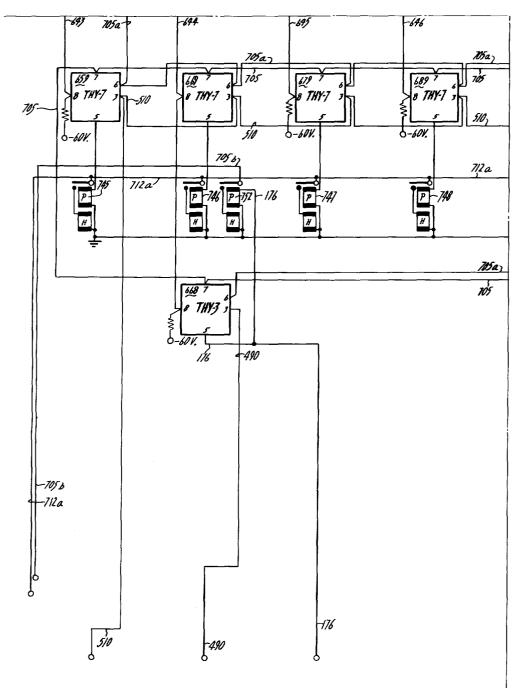

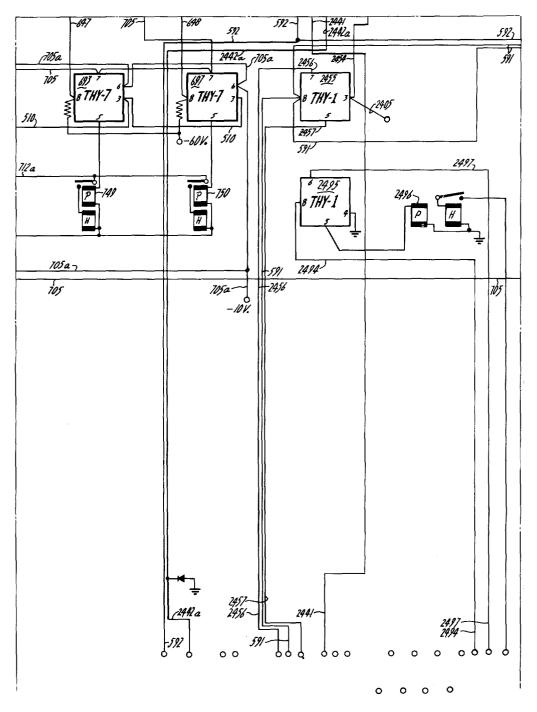

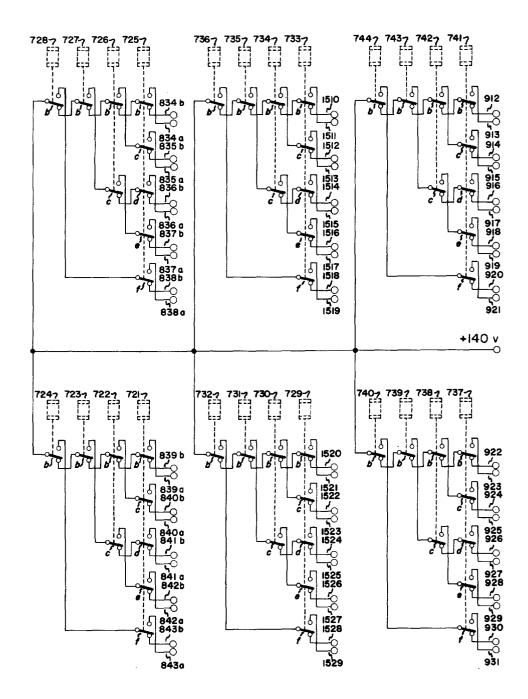

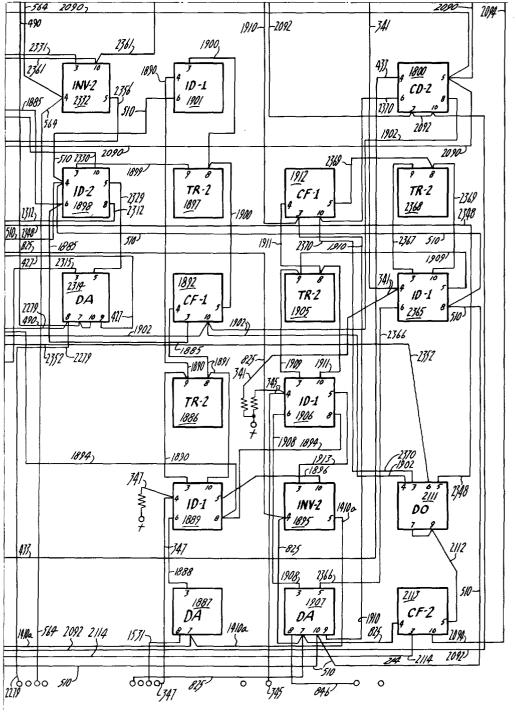

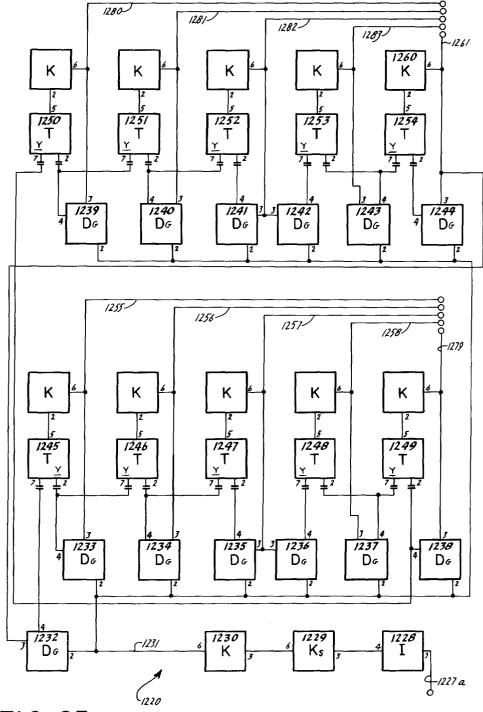

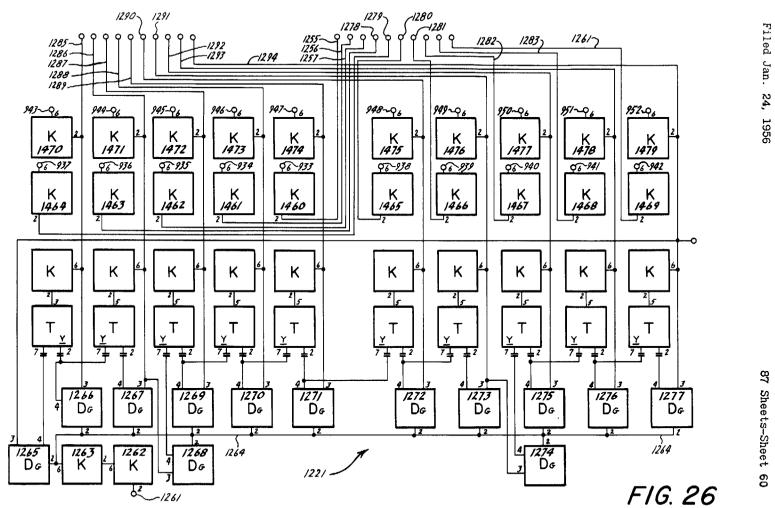

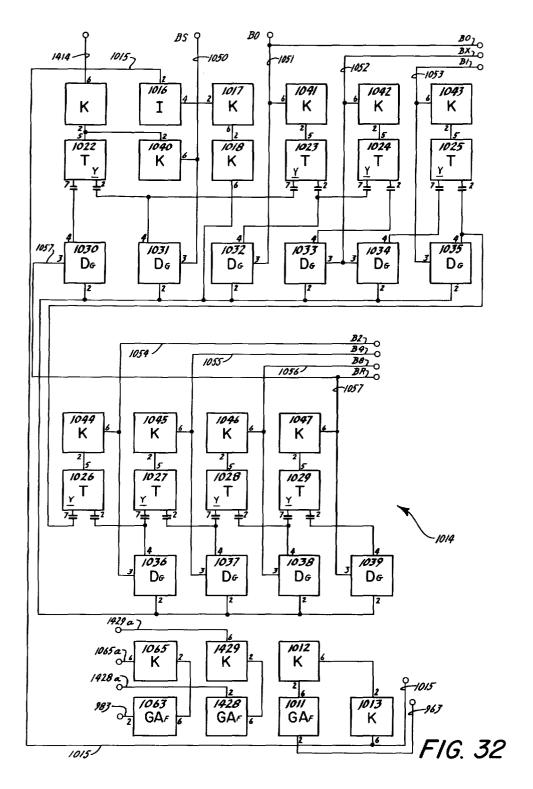

FIGS. 11a through 11-l, when arranged as shown in 30 FIG. 44, comprise a schematic diagram of a portion of the information transfer circuits of the invention.

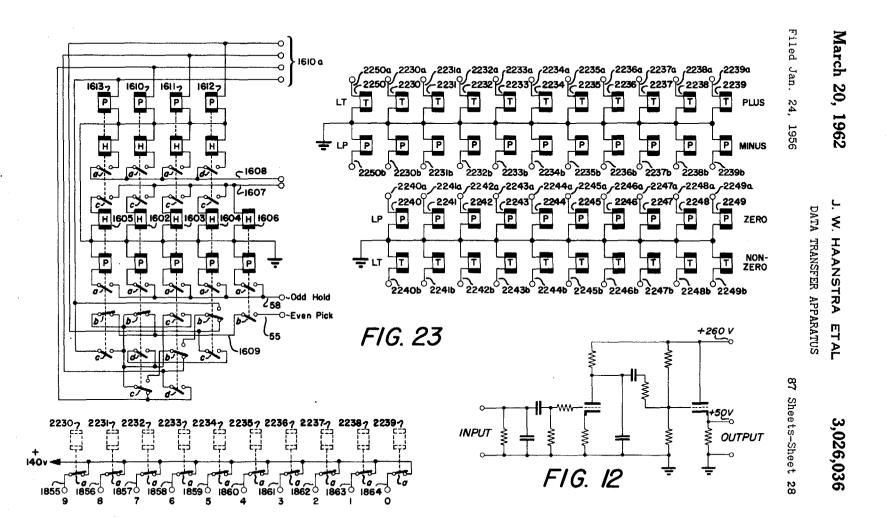

FIG. 12 is a schematic diagram of a preamplifier suitable for use in connection with each of the magnetic transducers associated with the process drum.

FIG. 13 is a schematic diagram of the  $T_1$  and  $T_2$  "read" relay trees.

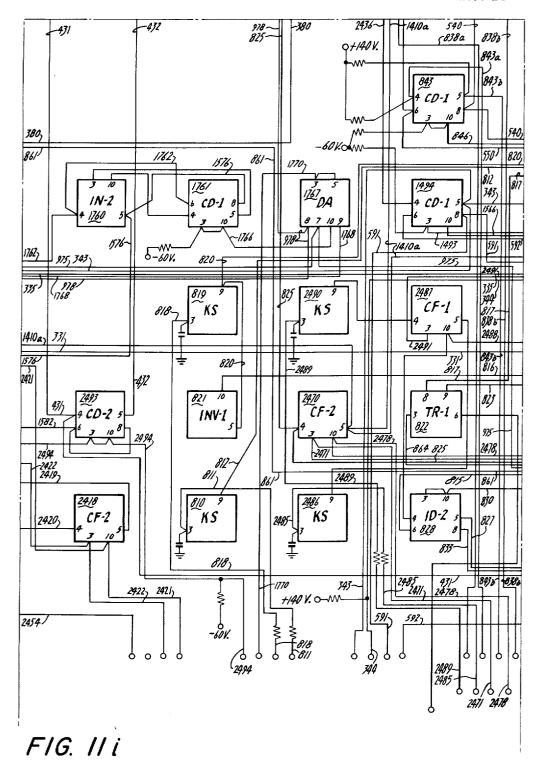

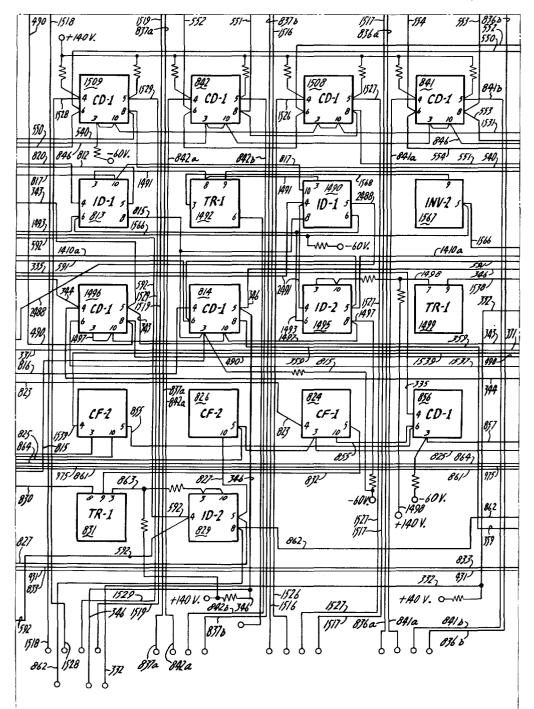

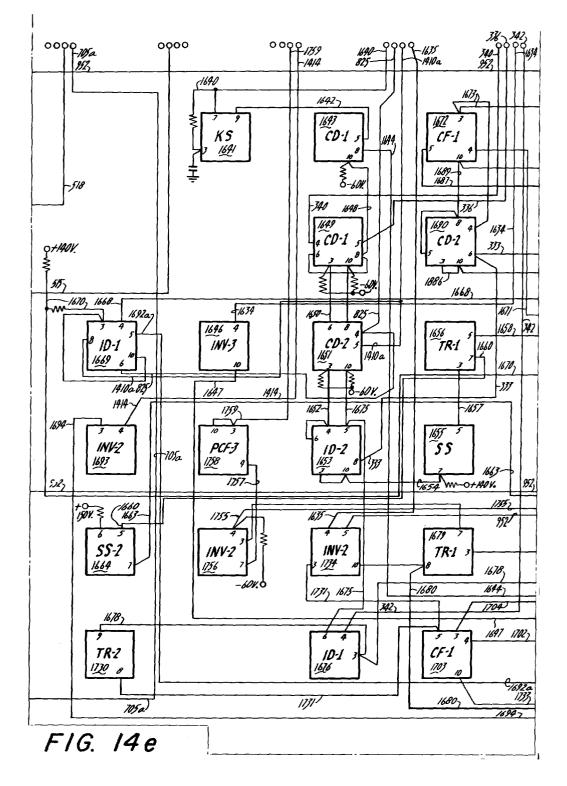

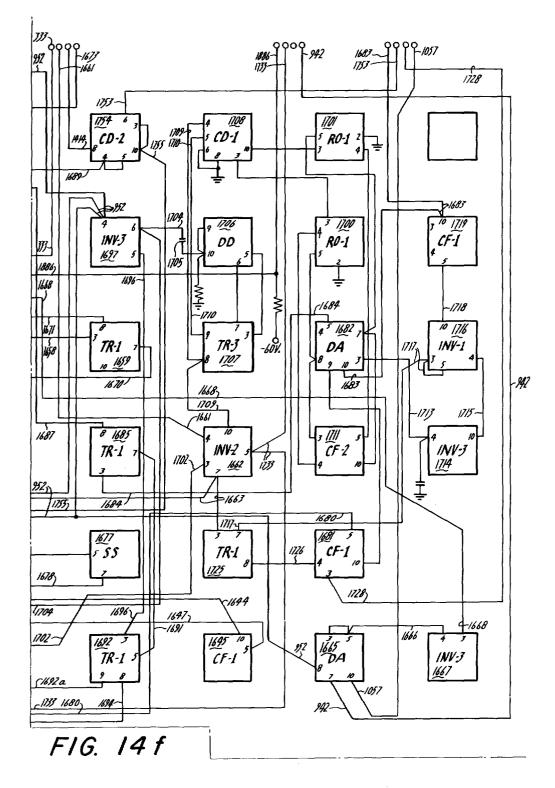

FIGS. 14a through 14j, when arranged as shown in FIG. 45, comprise a schematic diagram of a portion of the information transfer circuits.

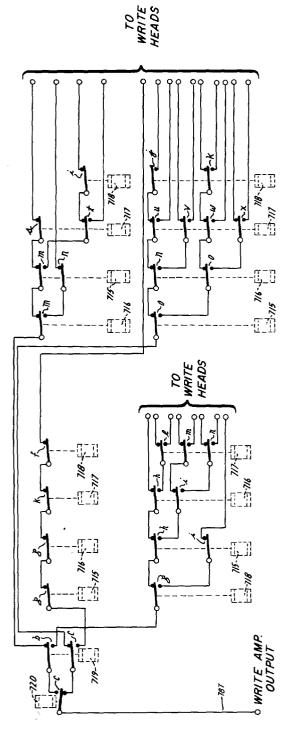

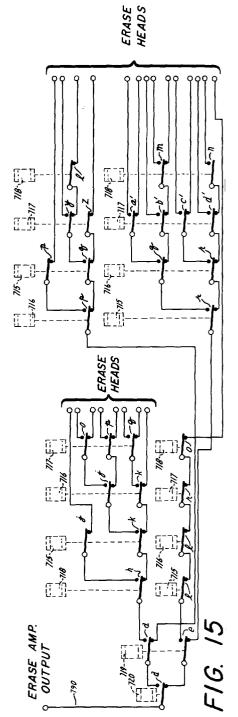

FIG. 15 is a schematic diagram of the "write" relay trees.

FIG. 16 discloses the code utilized in the machine of the invention.

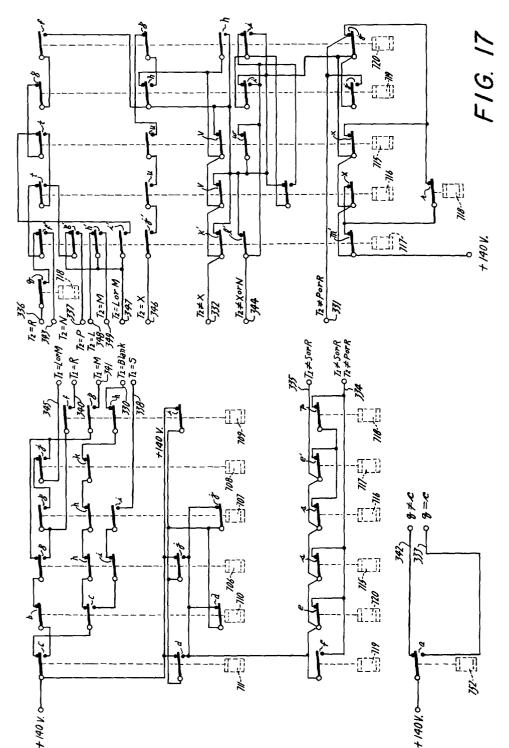

FIG. 17 is a schematic diagram of the control voltage 45 circuitry utilized herein.

FIG. 18 discloses the  $a_1b_1$ ,  $a_2b_2$  and mn relay trees.

FIG. 19 is a timing diagram of the  $E_1$  and  $E_2$  buffer cycles

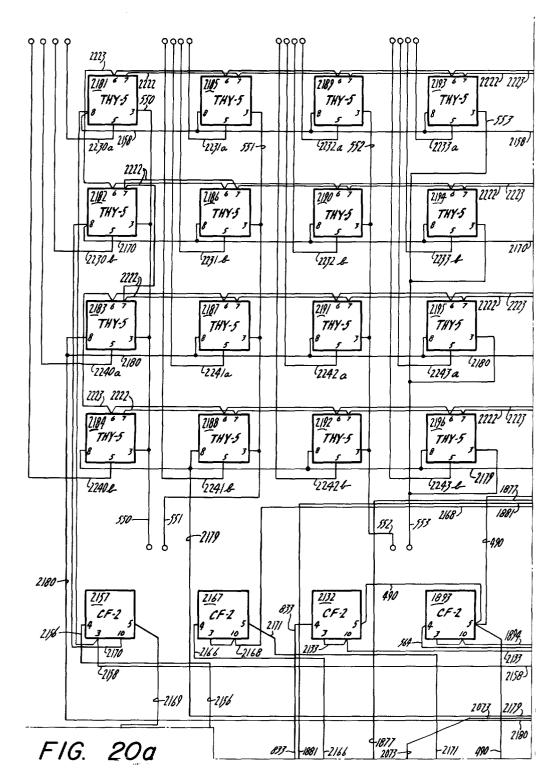

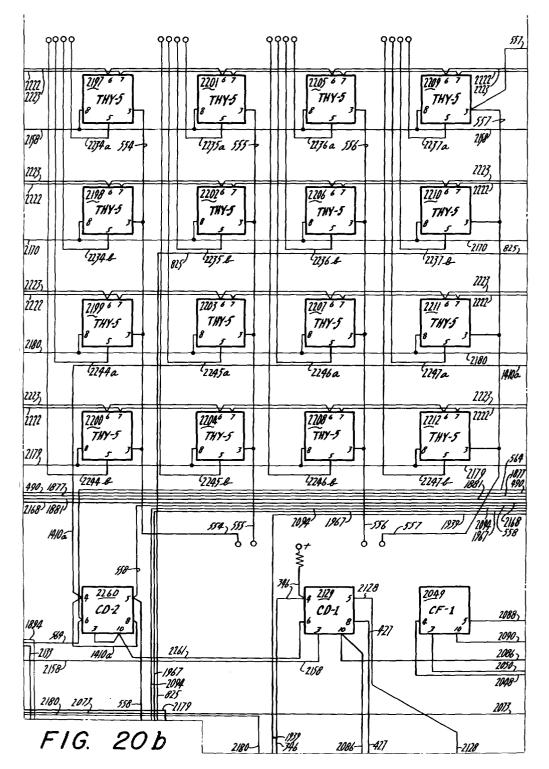

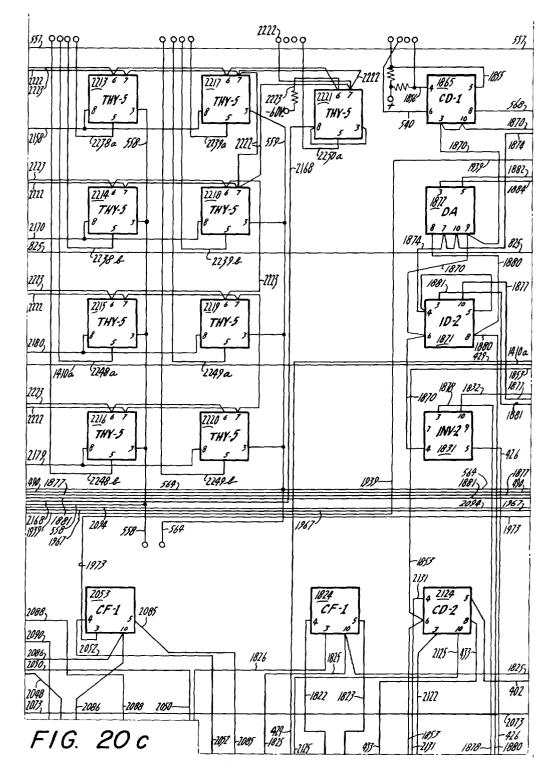

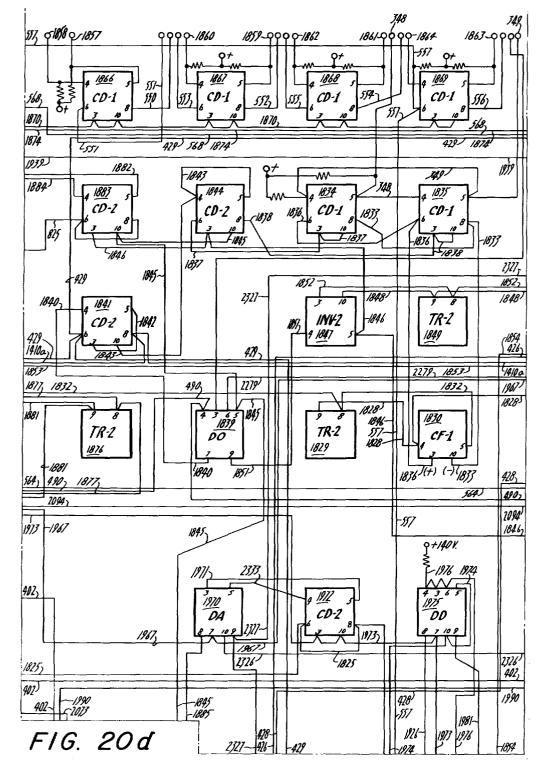

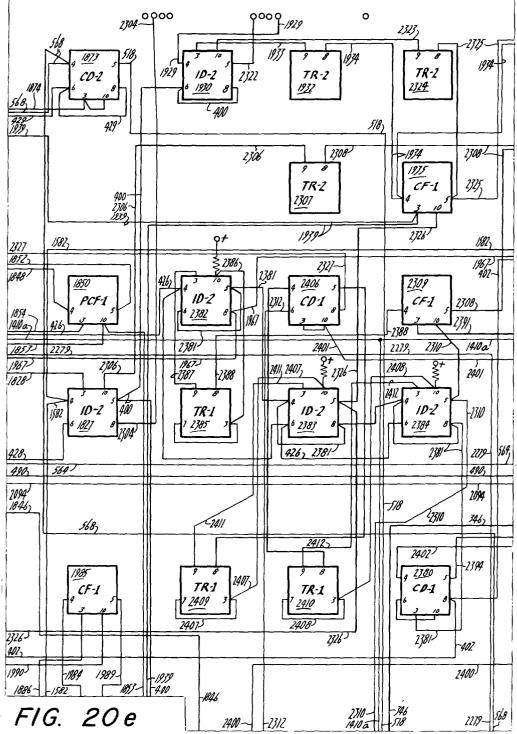

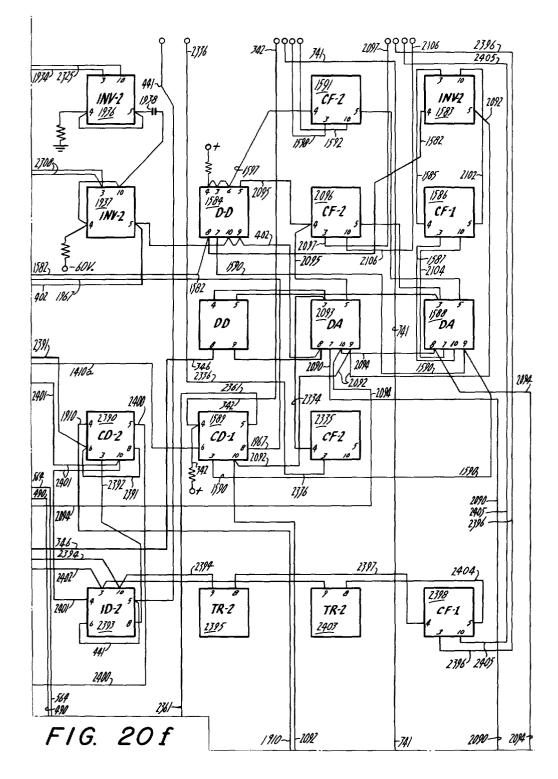

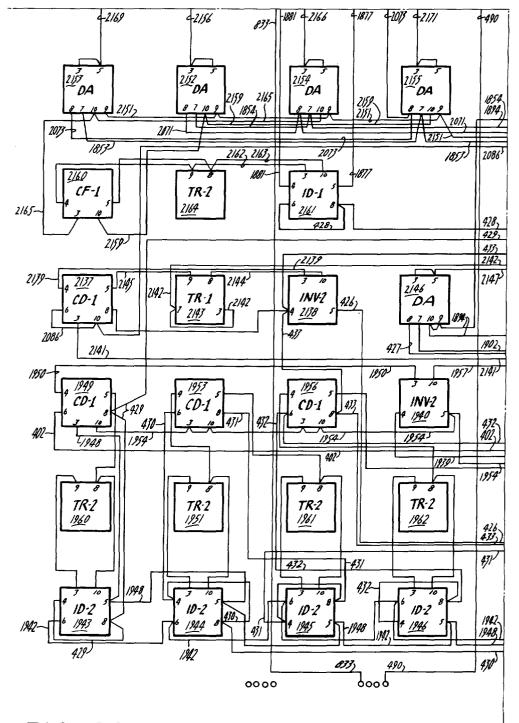

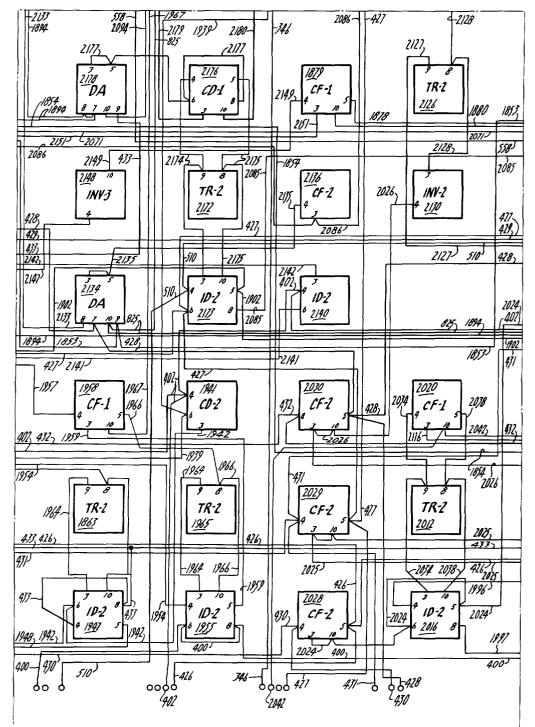

FIGS. 20a through 20-1, when arranged as shown in 50

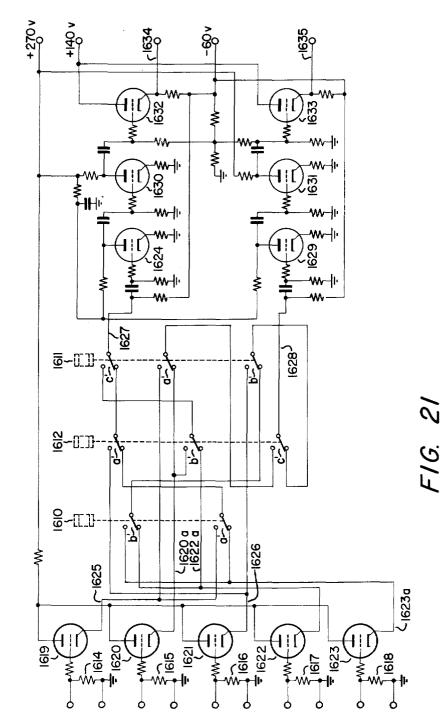

FIG. 46, disclose the arithmetic circuitry of the invention. FIG. 21 is a schematic diagram of the sector selection circuitry.

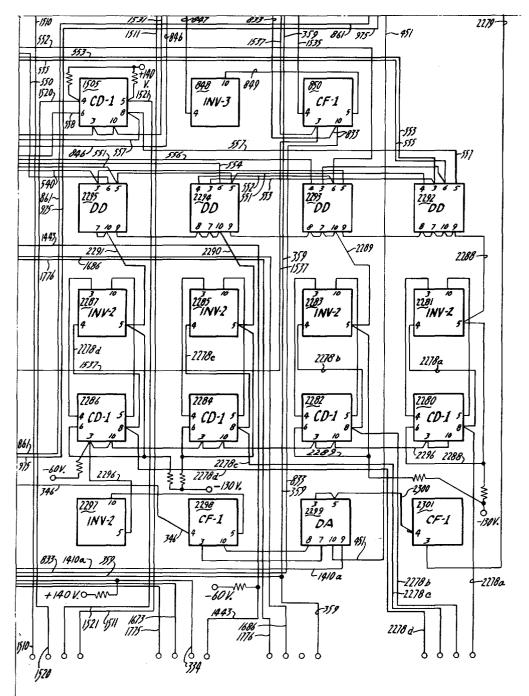

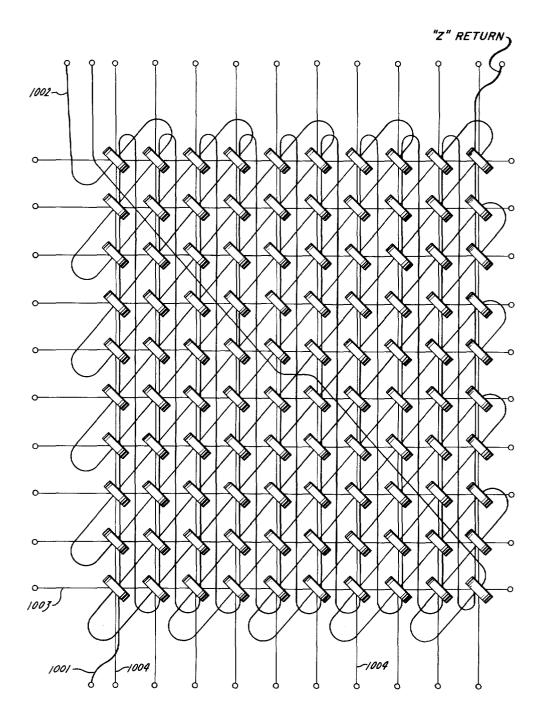

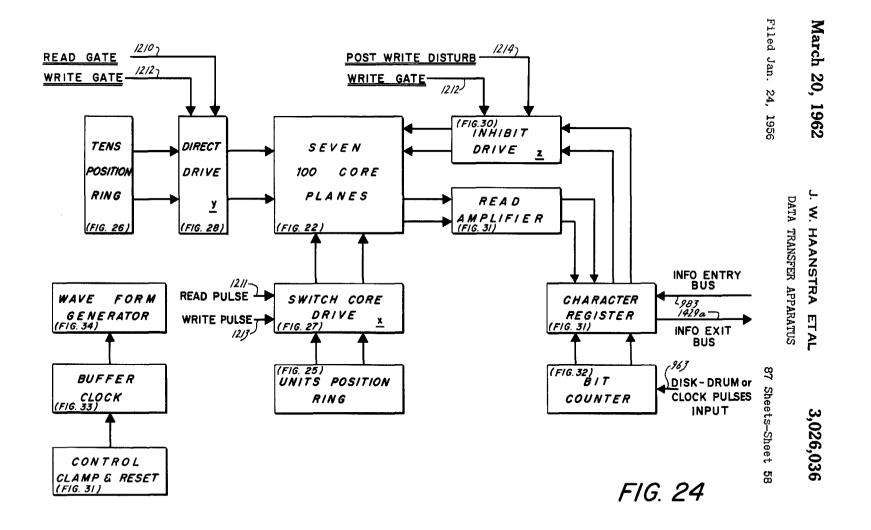

FIG. 22 is a schematic diagram of one of the seven planes of ferromagnetic cores utilized in the core buffer. 55

FIG. 23 is a schematic diagram of the sector relays together with various accumulator relays and circuitry associated therewith.

FIG. 24 is a block diagram of the core buffer.

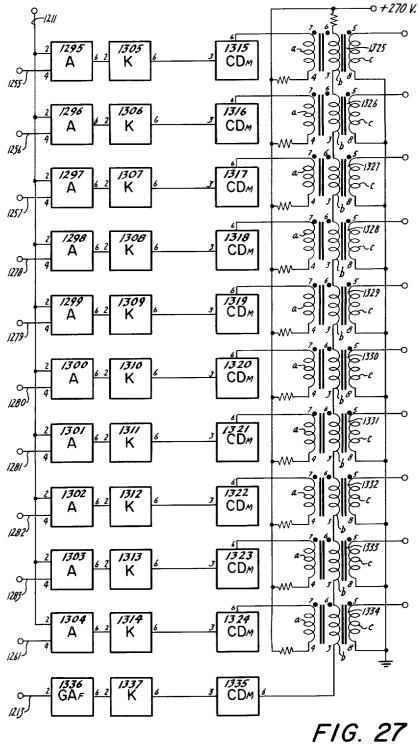

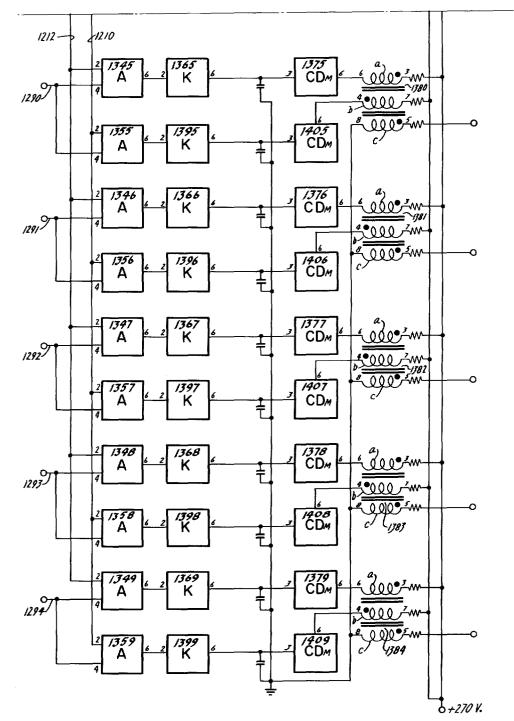

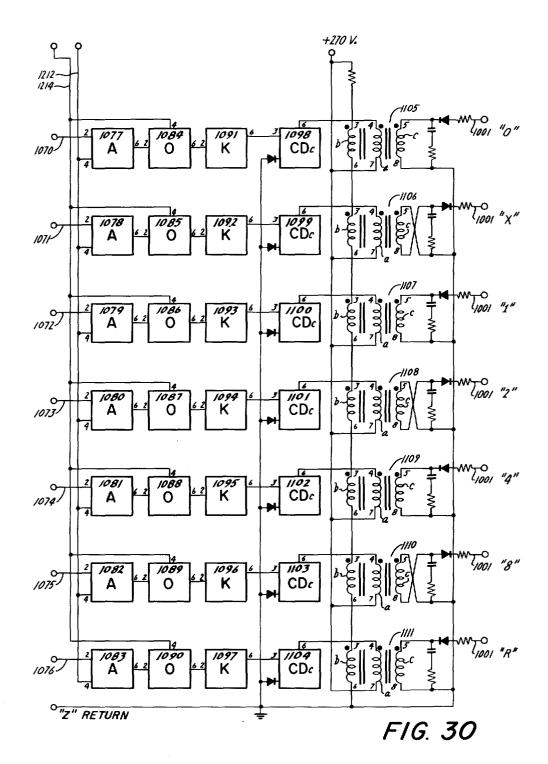

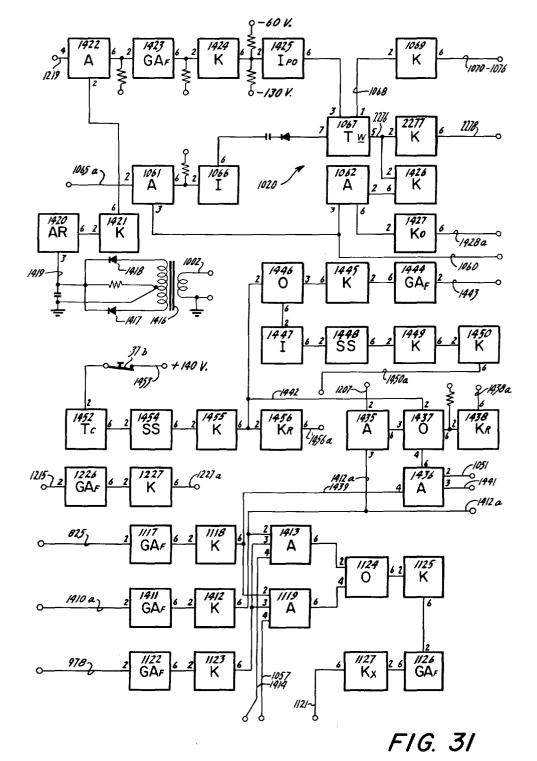

FIGS. 25 through 28 and 30 through 34 comprise a 60 schematic diagram of the core buffer circuitry.

FIG. 29 is a block diagram of the arithmetic circuitry of the invention.

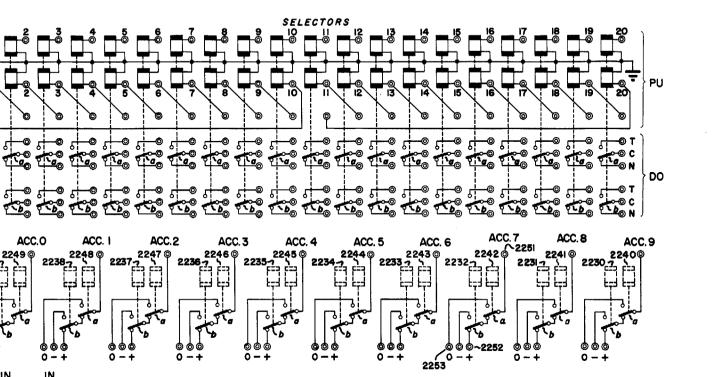

FIG. 35 discloses selector and accumulator hubs of the control panel, together with associated circuitry.

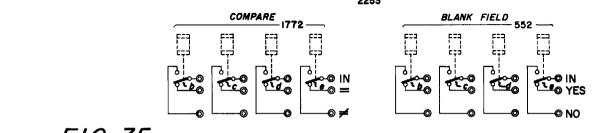

FIG. 36 is a timing chart disclosing relay sequences on an  $E_1$  and  $E_2$  interlock.

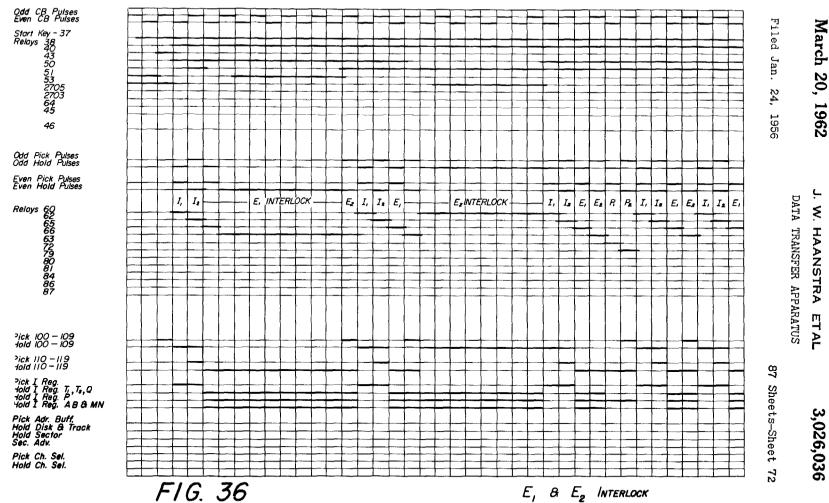

FIG. 37 is a schematic diagram of a portion of the character selector circuitry.

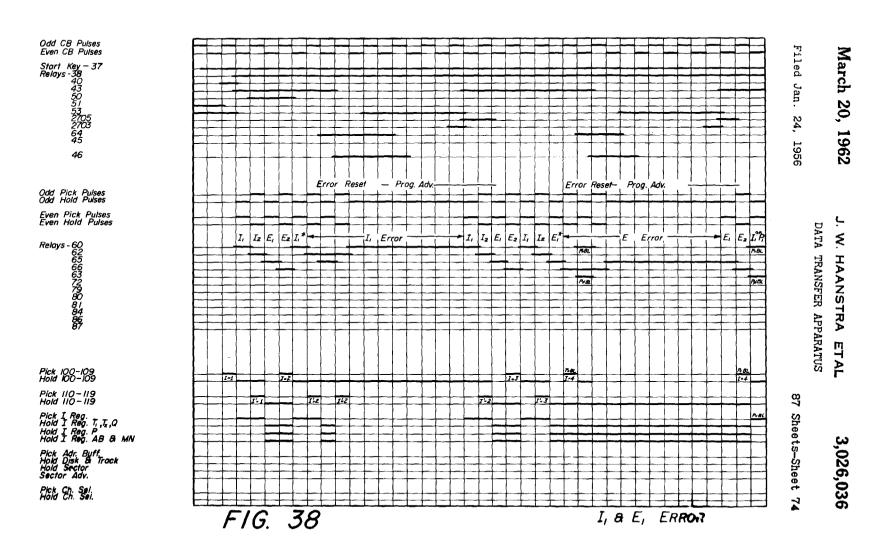

FIG. 38 is a timing chart disclosing relay sequences on 70 an  $I_1E_1$  error.

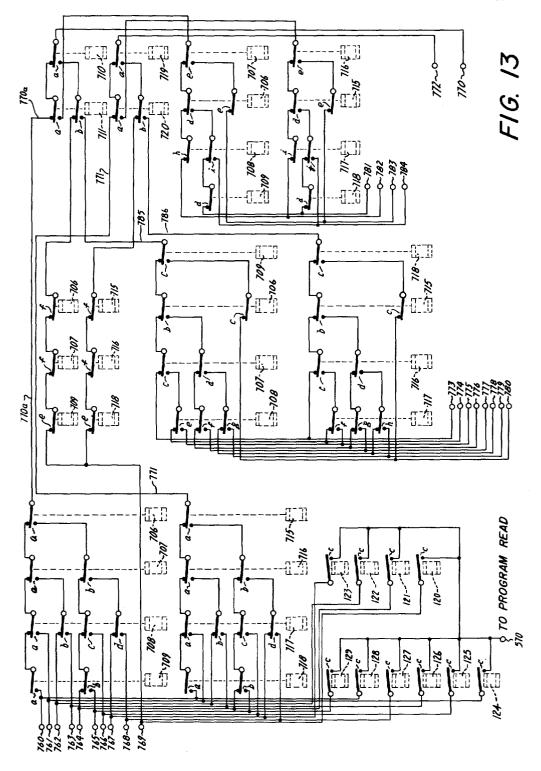

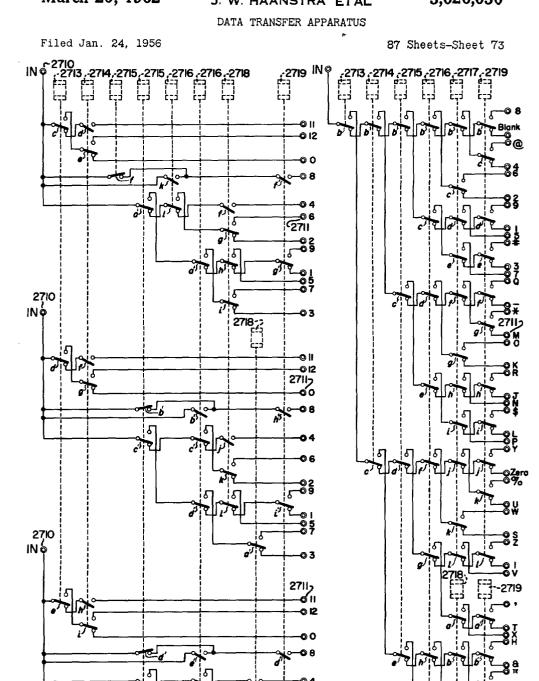

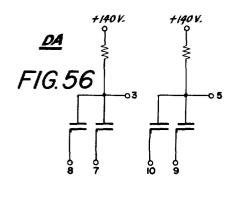

FIGS. 39a and 39b, when placed adjacent each other, are a pictorial sketch of various drum tracks and data recorded thereon during a typical application of the machine of the invention.

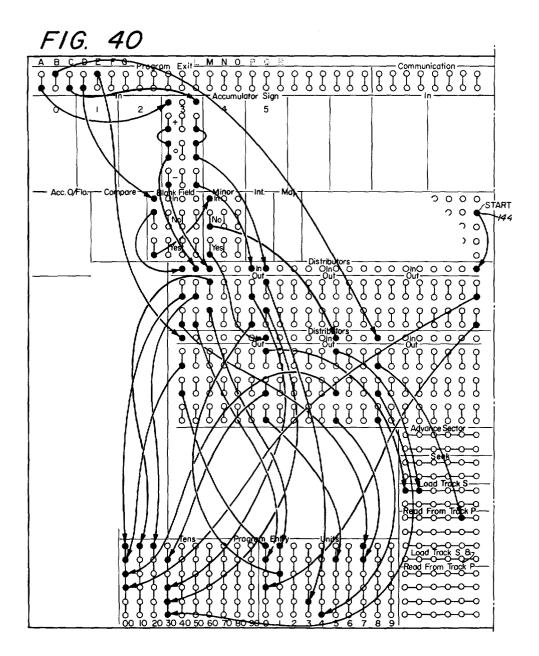

FIG. 40 discloses a portion of the control panel wired according to a typical application of the machine of the invention.

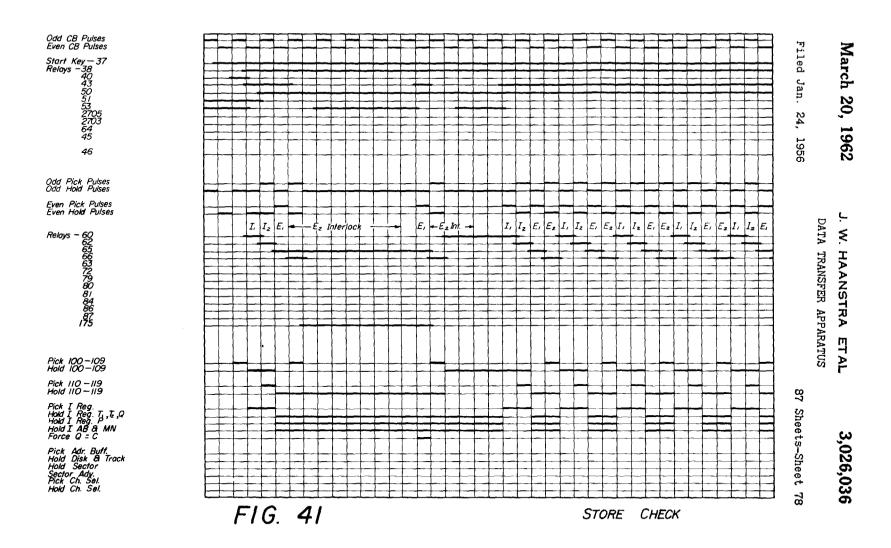

FIG. 41 is a timing chart disclosing relay sequences when q=c is forced, i.e., when  $T_2=R$ .

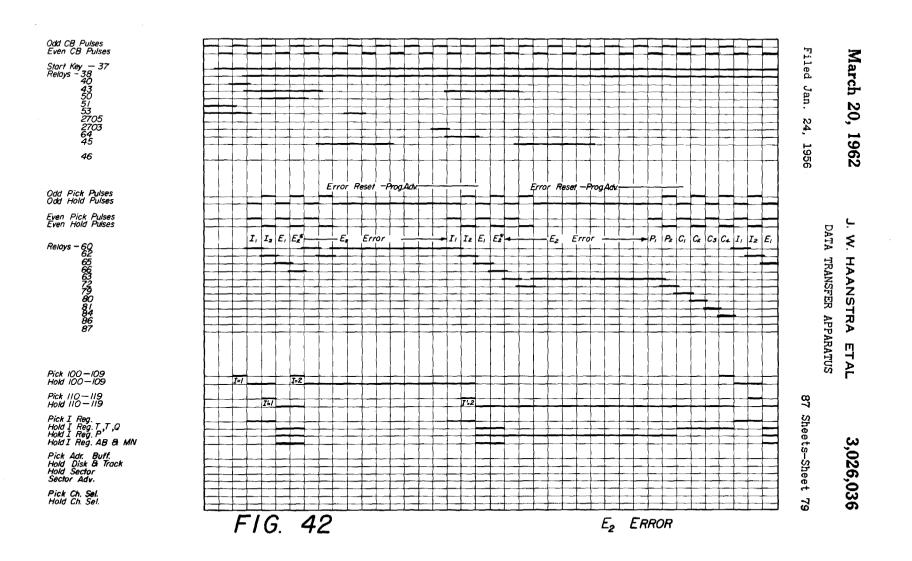

FIG. 42 is a timing chart disclosing relay sequences on an  $E_2$  error.

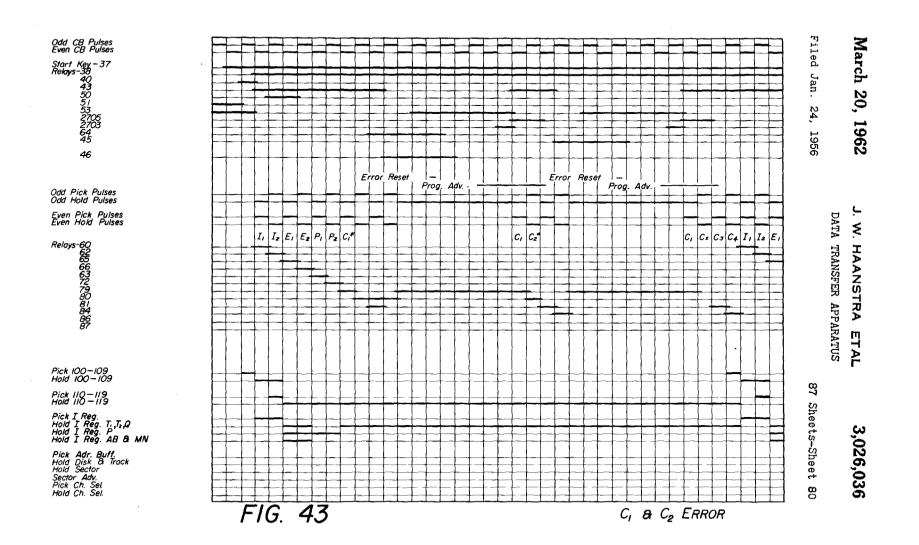

FIG. 43 is a timing chart disclosing relay sequences on C<sub>1</sub> and C<sub>2</sub> errors.

FIG. 44 discloses the layout of the drawings associated with FIG. 11.

FIG. 45 discloses the layout of the drawings associated with FIG. 14.

FIG. 46 discloses the layout of the drawings associated

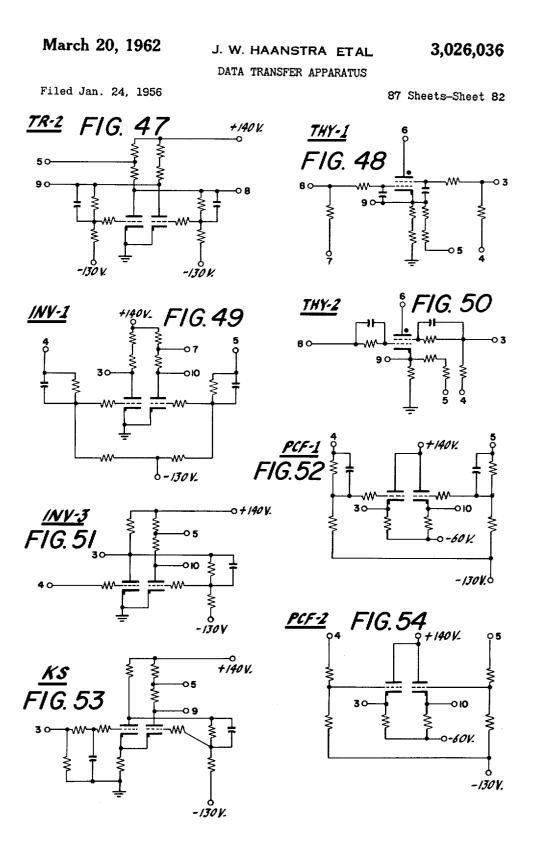

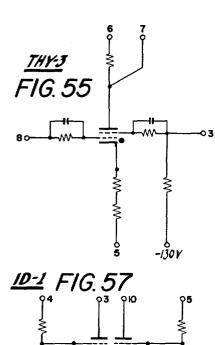

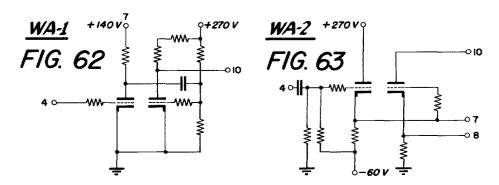

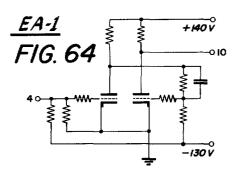

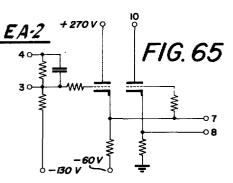

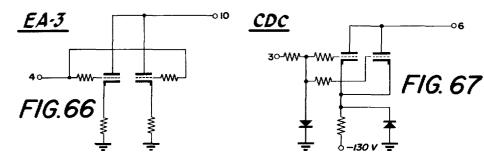

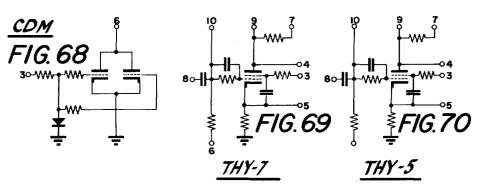

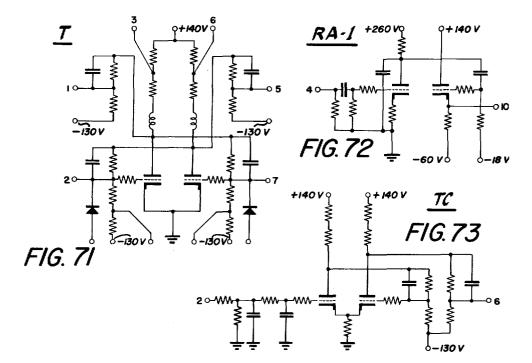

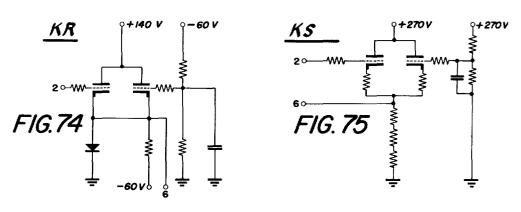

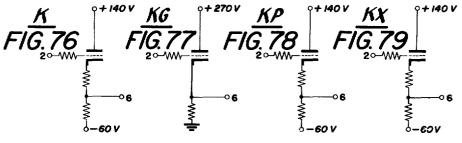

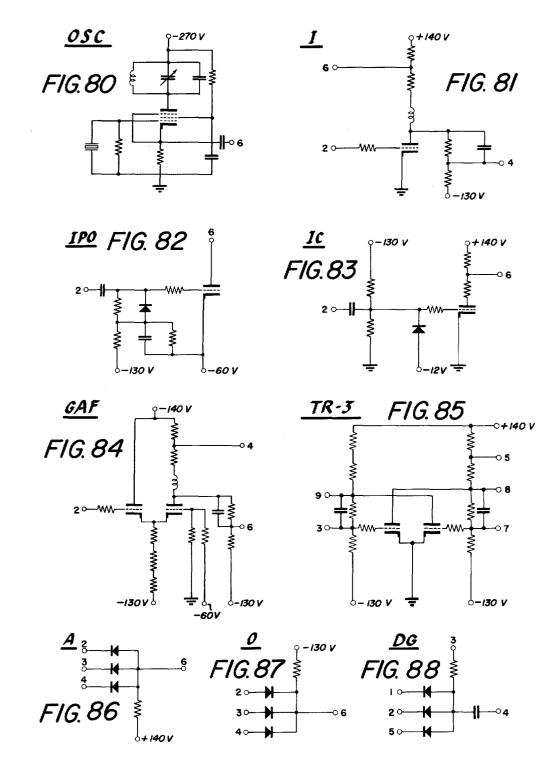

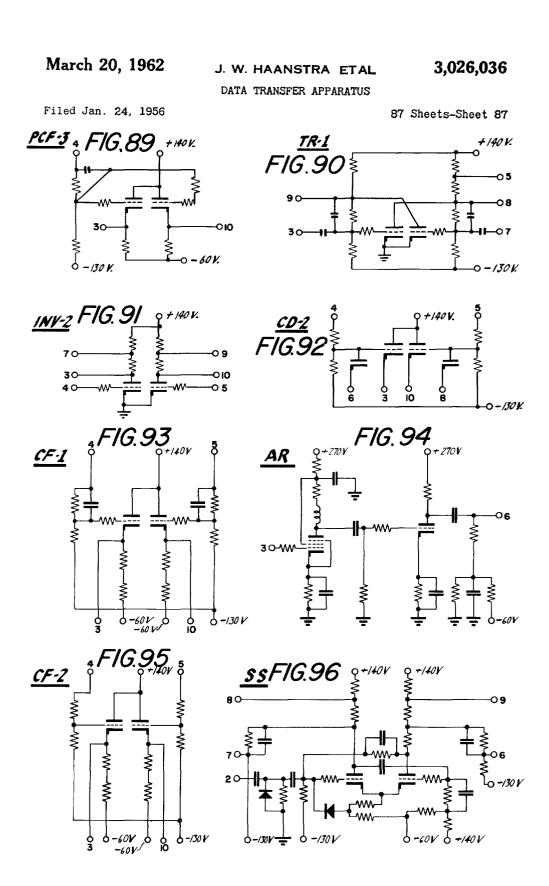

FIGS. 47 through 96 are schematic diagrams of various electronic components utilized herein.

Referring now to FIG. 2, the machine of the invention generally comprises an input-output unit 10, a large ca-

$_{20}$  pacity, random access, magnetic disc storage unit 11, a processing unit 12 for coordinating data transfer between the several units, and a 100-character magnetic core buffer storage unit 13 through which all data is moved when transferred from one unit to another or from one place FIG. 9 is an electronic timing diagram of the present 25 to another within the processing unit 12. The unit 13 provides the necessary synchronizing and realigning facilities and, in addition, performs certain arithmetical, logical and selection operations.

In the present embodiment the input-output unit 10 includes a drum 10a having three magnetic tracks for data storage, i.e., two input tracks S and an output track P, in addition to a timing or clock track  $CT_1$ . Data is entered on or taken from the drum tracks in any convenient manner. For example, the input may be made via punched record cards and a card feed, card reader and associated circuitry, such as that used in connection with the drum disclosed in the copending U.S. Patent No. 2,946,504, application Serial No. 555,026, filed December 23, 1955, may be utilized. Similarly, the output track P might be arranged to operate a printer in a manner taught in the above mentioned copending application or to control the operation of other apparatus, such as a punch, in a well known manner.

Each of the data tracks of the input-output drum 10a is adapted to store 100 eight-bit characters, each track being divided into 800 bit positions. By using two input tracks S which are alternately loaded with successive data sets to be processed, the next data set to be processed is always present on one or the other of these tracks. Thus, when data is being loaded on one track S, the read-out transducer associated with the second track S' is operative to read the data recorded thereon therefrom, the read-out transducer associated with the first track S being inoperative at this time. However, when the input-output unit 10 is instructed by the machine to load the next data set onto the drum, means are actuated to cause the next data set to be loaded onto the track S' and to render the readout transducer associated with the track S operative. The actual structure provided for accomplishing these operations is not disclosed herein, it being fully disclosed in the aforementioned copending U.S. Patent No. 2,946,504, application Serial No. 555,026, and it will be assumed herein that when the input-output unit is instructed to load data by means to be described, the next data set to be processed may be taken from a line 16 extending from the inputoutput unit 10 serially by bit and serially by character. Additionally, output data to be printed or punched is transferred serially from the machine by a line 17 to the output track P.

The disc storage unit 11, together with the access mechanism therefor, is similar to the structure disclosed in a copending U.S. Patent application Serial No. 477,468, filed December 24, 1954, and, since reference may be made to that case, only that information relative thereto 75 which is necessary to an understanding of the present in-

65

35

40

vention is given herein. The disc array comprises 50 metallic discs coated on each side with a ferrous oxide material well known in the magnetic recording art and provides storage for 5,000,000 eight-bit characters. Each side of each disc is arranged with 100 concentric magnetic recording tracks, there being 10,000 such tracks in all, and each track is divided into five sectors, each of which will accommodate a "record" of 100 eight-bit characters. Thus, storage is provided for 50,000 100-character record.

A five-digit address is utilized to select a given record to be read from or recorded upon, four of which are necessary to control the access mechanism (address register) 19 to position the transducers associated with the disc storage unit adjacent the desired track of the selected 15 disc, and one of which controls the selection of the proper record. The discs are numbered 00 through 49 and are addressed by similar numbers. The tracks are identified by numbers 00 through 99, each number referring to corresponding tracks on each side of a disc. Thus, each 20 track includes ten records, i.e., five on each side of the disc, which are referred to and are addressed by the numbers 0 through 9. The first two digits of a record address, therefore, control the access mechanism 19 to position the transducers adjacent the selected disc, the second pair of 25 digits control the mechanism 19 to dispose the transducers opposite the selected track of the selected disc, and the last digit of the record address controls which of the two transducers is selected for operation as well as the selection of one of the five sectors on the selected side of the 30 disc.

By entering the address of a particular record into an address buffer 20 which controls the operation of the access mechanism 19 and by giving the access mechanism an instruction to seek, the transducers are positioned adja-<sup>35</sup> cent the track within which the desired record is contained. The head defined by the last digit of the address is rendered operative and a gating mechanism, to be described, is controlled to gate the data recorded on the desired record onto a line 21 or to gate data coming in on <sup>40</sup> the line 21 onto the desired record.

The processing unit 12 is provided to process data and to coordinate and control the flow of data through the various portions of the machine, and includes a magnetic drum 25, information transfer circuits 26, a program 45 control unit 27, a control panel 28, and arithmetic circuits 29. The drum is provided with 25 tracks, each of which is arranged to store 100 eight-bit characters, in addition to a timing or clock track  $CT_2$ . Three of the drum tracks are associated with the arithmetic circuits 29, 50 eleven tracks are provided for general storage, one track serves as an emitter from which any selected character may be taken, and ten tracks are utilized for program storage.

FIG. 2 shows generally the paths over which data may 55 travel in the present machine. Input information taken from the input track S may be transferred through the magnetic core buffer 13 into either the processing unit 12 or the disc storage unit 11. Similarly, information from the disc storage unit may be entered through the buffer 60 to either the output track P of the unit 10 or the processing unit 12. In the processing unit, information is processed, modified, and rearranged as desired under the control of the internally stored programs, and the results of these operations may be transferred through the core buffer 65 either to the output track P or to the disc memory.

The flow of information through the machine is controlled, as mentioned above, by programming, the best features of internally stored programming and of wired control panels being combined herein to obtain maximum flexibility. The primary means of processing information herein is by transferring it from one location to another under the control of the internally stored program instructions. Ten tracks of the magnetic drum in the processing unit may be used to store a series of instruction for 75 ferred to J32, etc.

controlling the operation of the machine. Since tendigit instructions are utilized, each of the program tracks will store ten instructions, thereby providing storage for 100 ten-character instructions. These instructions are referred to herein as instructions 00 through 99. After executing a given instruction, the machine proceeds to the next higher numbered instruction unless it is transferred by the control panel to another instruction. For example, if the machine is started from instruction 24 and instruction 27 has a supplementary signal which is 10 wired to transfer the series to instruction 51, the machine obeys the sequence of instructions: 24, 25, 26, 27, 51, 52, etc. This transfer may be made dependent upon logical decisions made on the control panel of the process control unit. The drum tracks used to store programs are identified by the numbers 0 through 9 and are arranged to store instructions 00 through 09, 10 through 19, etc., as set forth below.

| ogram number |

|--------------|

| 00-09        |

| 10–19        |

| 20-29        |

| 30-39        |

| 40-49        |

| 50-59        |

| 60-69        |

| 70-79        |

| 80-89        |

| 90-99        |

|              |

(It should be noted that program tracks not used to store instructions may be used for the storage of information.)

The various storage tracks on the process drum are used for recording information being processed. As mentioned above, these tracks contain 100 character positions and are identified by the letters A through H, J, K and Q. Each character recorded on a track is identified by a position number, a two-digit address being used to define each of the 100 character positions on a track. Thus, the first character position on each track is defined by the address 00, the second position being defined by the address 01, etc., and the 100th position is defined by the address 99. The address B10, therefore, defines the position of the 11th character on general storage track B.

The ten-character instructions utilized herein are arranged as follows:  $T_1a_1b_1 T_2a_2b_2 mn pq$ . The first or  $T_1$ position identifies the track from which information to be processed or transferred is to be taken, and  $a_1b_1$  sets forth the address of the first character on that track to be transferred under the control of the instruction. In a similar manner,  $T_2a_2b_2$  specifies the track to which information is to be transferred as well as the position in which the first character transferred is to be recorded. The seventh and eighth character positions of each instruction, i.e., mn, define how many characters are to be transferred (it being understood that the instruction "00" in these positions specifies the transfer of 100 characters and that "01" calls for the transfer of but a single character). The remaining positions, pq, are provided to relate certain modifying and control instructions which will be explained later. Thus, the first three positions are referred to as the FROM portion of the instruction, the second three positions define the TO portion of the instruction. The seventh and eighth positions define the number of characters to be transferred. For example, to transfer data recorded in positions 05 through 09 of general storage track C into positions 29 through 33 of track J, the instruction would be as follows: C09 J33 05 --. This instruction controls the transfer of the character recorded in address 09 of storage track C into address 33 of storage track J. Similarly, the character recorded in C08 is trans-

50

Alphabetic code addresses are given to the other units through or to which there is data flow as follows:

|                                                       | From- | Т'о    | 5  |

|-------------------------------------------------------|-------|--------|----|

| Input storage track                                   | s     | P      |    |

| Output storage track<br>Disc memory<br>Address buffer | R     | R<br>R |    |

| Multiplicand                                          | N     | Ň      |    |

| Character emitter.<br>Accumulator add                 | T     | L      | 10 |

| Accumulator subtract<br>Accumulator read-out          |       | M      |    |

| Accumulator read-out and reset                        | M     | ]      |    |

As an example of the use of these codes, let us suppose that it is desired to read data into the machine and transfer it to track C of the processing unit. If it is assumed that an earlier instruction has caused the data to be entered onto one of the input storage tracks S, the machine is given an instruction such as S99 C99 00 - -. This controls the machine to take 100 characters, starting from position 99 and extending through position 00, from the input storage track and to transfer it to the corresponding positions on track C.

In a normal transfer operation, data from the T<sub>1</sub> address is transferred into the core buffer 13 during what is referred to herein as an E1 cycle and is transferred therefrom to the  $T_2$  address during an  $E_2$  cycle, and upon completion of this transfer, there being no modifying instruction in the pq portion thereof, the machine immediately prepares to execute the next successive instruction.

If a modifying instruction occurs in the pq portion of an instruction, selectors on the control panel 28 are tested to control the machine to proceed to one of a number of alternate programs. This operation, in which the machine selects the next sequence of programming, is called "branching," after which the machine proceeds immediately to the next instruction. Modifying instructions may 40be numerical or alphabetical. If a numerical code is placed in the ninth or p column of the instruction, the machine executes the instruction, performs the operation specified by the numerical code, and then proceeds to the next consecutive program step. The numerical control codes are as follows:

| 1 | Load track S            |

|---|-------------------------|

| 2 | Seek                    |

| 3 | Advance sector          |

| 4 | Read from track P       |

| 0 | Load track & and read t |

Load track S and read from track P

If no modifying control is desired, the p column of the instruction is left blank. As an example of the use of the modifying instruction, let us suppose that it is desired to transfer the data on track C of the drum 25 55 to the output track P and cause it to be read out for printing or punching as may be desired. In this case the machine is given the instruction: C99 P99 00 4-. This causes the 100-character record on track C to be transferred to the output track P from where it is taken to 60 control printing or punching.

When information is to be transferred from the disc memory to a storage track on the process drum, an entire 100-character record must be transferred. To cause the disc memory to locate the desired information, the ad-65 dress thereof is entered into the address buffer 20 and the seek control code is added to the instruction. Assuming that the address of the desired record in the disc file is presently located in positions 04 through 00 of general storage track A, such as instruction would appear 70 as follows: A04 Y99 05 2-. This instruction causes the address recorded in the last five positions of track A to be transferred to the address buffer 20. The control code 2 then causes the access mechanism to move the transducers associated with the file 11 adjacent the disc 75 the two hubs that correspond to the address of the desired

and track defined by the first four digits of the address and to locate the desired record, as discussed earlier. (It should be noted that the 99 recorded in the  $a_2b_2$  positions of the instruction is used only to fill these positions, there being no meaning therefor in this instance.) Since it takes time for the access mechanism to position the transducers according to an address, it is desired that the machine be given this instruction as soon as the address is known. In this way processing may continue until the 0 information is actually needed, thereby permitting utilization of the access time for other processing, which reduces the effective time required for a given operation. To transfer the disc record to the processing unit, an instruction such as R99 E99 00 - is utilized. This ininstruction such as R99 E99 00 -- is utilized. struction causes the entire 100-character record specified by the number in the address buffer to be transferred to the track E.

When successive records on the same disc storage track are to be read, it is not necessary to move the access arm 20physically and the number in the address buffer may be advanced one address at a time either by using the pcontrol code 3 or by control panel wiring, as will be explained. Thus, when the arm has been physically located. all ten records on the track being scanned may be read out on successive operating cycles. For example, if the record address is 12340, record 12340 is first read out. Simultaneously, if the 0 is changed to a 1, the record 12341 is read out on the next cycle. Subsequently, records 12342 through 12349 may be read out in a similar 30 manner. Note that the advance sector operation affects only the low order position of the address buffer and does not carry over into other positions, since, if it did carry over, a relocation of the access arm would be required and such relocation is accomplished only by a seek opera-35 tion.

A track T, referred to herein as the emitter track, on the processing drum is provided with various numerals, letters and special characters previously recorded thereon and is used as a source from which selected characters are taken for use when desired. The address of these characters is known and they are referred to by suitable instructions. If, for example, it is desired to record a "5" for record identification, etc., perhaps in character position 21 of track J, and assuming that a "5" is recorded in char- $_{45}$  acter position 43 of the emitter track T, the instruction would be T43 J21 01 ---

The numerical p codes discussed above control automatic operations such as loading the input track S and positioning the access arm. If an alphabetic p code is utilized, however, an impulse is emitted from a corresponding program exit hub on the control panel 28 of the processing unit 12 and the program sequence is cancelled. This impulse may be wired through various selectors to make logical decisions according to the results of previous operations and, as in other control panel operations known in the art, these selectors may be tested in combination and the impulse wired to cause different operations for different selector conditions. This allows branching to one of any number of possible alternate programs. The impulse from the program exit hub must be returned to a pair of program entry hubs, as will be described, to initiate the new sequence of programs. Thus, a program exit hub emits an impulse whenever the corresponding alphabetic p code is attached to an instruction. This impulse is used to make tests on the control panel, and when it is emitted, the program sequence is cancelled and is reestablished by wiring to the proper program entry hubs.

Program entry hubs are provided to accept the program exit impulse which sets up the first program step of a new sequence. When an alphabetic p code is attached to an instruction, the machine stops operation unless a new program is initiated by impulsing the program entry hubs. The new program step is set up by impulsing 5

instruction number. Thus, for example, if the impulse taken from program exhit hub B is to initiate a new sequence of program steps beginning with step 62, hub B is wired to the entry hubs which control the selection of program 62, as will be explained.

Latch type selectors are utilized herein to provide for storage and for analysis of control. Each selector has a common hub, a pick hub, a drop hub, a normal hub, and a transferred hub, the common hub being connected to the normal hub until the selector is picked up by impulsing 10 the pick hub. At this time the common hub is connected to the transferred hub where it remains until an impulse is sent to the drop hub. An impulse that is used to perform several functions on the plugboard is first wired through distributors which serve the same function as 15 parallel wires but prevent back circuits.

As an example of branching, let us suppose that the machine has proceeded through program steps 90 through 14 and the need for a logical decision arises. Under one condition a first selector is transferred, and in 20 this case the program is to be reinitiated at program step 19. Under another condition a second selector is transferred and the program is to be reinitiated at step 29. A third condition might be where neither selector is transferred, and in this case it will be assumed that the pro- 25gram should proceed to step 15. The instruction for step 14, therefore, is provided with an alphabetic p control code such as A. The control code A causes an impulse to be emitted from the A program exit hub after the in-30 struction has been carried out. Simultaneously, the program sequence is cancelled. If the first selector is transferred at this time, the impulse from program exit hub A emerges from the transferred side of this selector and is wired through a distributor to impulse the "1" hub in 35 the tens program entry and the "9" hub in the units program entry, and program 19 is set up to control the next program step. If the first selector is normal, the impulse emerges from the normal side thereof and is wired to the common hub of the second selector. Thus, if this selector is transferred, the impulse emerges from the trans- 40 ferred hub thereof to impulse program entry hubs "2" and "9" and initiate program step 29. If neither selector is transferred, the impulse from the program exit hub A emerges from the normal side of the second selector and 45 enters program entry hubs "1" and "5" to initiate program 15.

The q portion of the instruction is utilized to control special operations as may be desired. In the present embodiment only one such operation is disclosed, and when 50 q=c, data recorded at the T<sub>2</sub> address is compared with the data taken from the  $T_1$  address. Thus, when q=c, a comparison is made between the  $T_1$  data and the  $T_2$  data to determine, for example, whether or not a transfer was correctly made. When  $T_2=R$ , a comparison is forced 55automatically after the data is recorded on the disc. This operation requires a second  $E_1$  cycle, during which the  $T_1$  data is again read into the buffer, and a second  $E_2$ cycle during which the data is read from the  $T_2$  address and compared with the data in the buffer to determine if 60 they are identical.

The primary time base of the present machine is the rotating process drum 25, and all operations are timed to the process drum by cam operated circuit breakers 65 driven from the drum shaft. Most gross control paths are set up through relay points and, in general, these relays are picked during one drum revolution and the signal is sent through their points during the next following drum revolution. Thus, the basic operation is made up 70 of two drum revolutions. Successive revolutions or cycles are designated herein as "even" cycle, "odd" cycle, "even" cycle, etc., and since various segments of the control sequence are intimately associated with a given type

mal control sequence must exist until the correct phase reoccurs.

A normal transfer operation, i.e., a transfer operation solely within the processing unit, requires four cycles for completion. The first cycle, an even cycle, is the  $I_1$  cycle during which time an instruction is read from the appropriate ten-digit field of one of the program tracks under the control of the program counter 27 and into a static instruction register 30. The next cycle is referred to as the  $I_2$  cycle (odd) and is used to provide "wait" time required to allow relays associated with the instruction to be picked in the event that the instruction occurs late in the  $I_1$  cycle. The remaining two cycles of the trensfer operation include the  $E_1$  (even) and  $E_2$  (odd) cycles. During the  $E_1$  cycle, information from the sending track  $T_1$  is loaded into the magnetic core buffer, starting at the character address specified by  $a_1b_1$  and continuing until mn characters have been read into the buffer or until character position 00 has been passed, whichever occurs first. The unloading of the core buffer onto the receiving track T<sub>2</sub> occurs during the E2 cycle in an analogous manner. Thus, a normal transfer operation requires four cycles for completion. In terms of the usual stored program concepts, the  $I_1$  and  $I_2$  drum revolutions constitute the "fetch" cycle and the  $E_1$  and  $E_2$  periods are the "execute" cycle. Provided that the p column of the instruction is blank. the system proceeds to read the next instruction on the following cycle (even), and these four revolution sequences follow each other until interrupted by a p "flag" or by an operation that cannot be accomplished within the basic cycle.

If the p column of the instruction is not blank, i.e., if a relay in the p section of the instruction register has been picked, an additional pair of control cycles, i.e., the  $p_1$ and  $p_2$  cycles, are added to the basic cycle following  $E_2$ . the  $p_1$  cycle (even) is wait time provided primarily to allow any control panel relays of state that might have been affected during the E<sub>2</sub> cycle to reach their final condition. Also, if an alphabetic character is present in the p portion of the instruction, the program counter relays are dropped out during the  $p_1$  cycle. The actual control panel pulse is emitted during the  $p_2$  (odd) cycle and may be used to actuate various control panel functions as well as to pick up the program counter relays at a new starting point. Once the program relays are picked, the normal I<sub>1</sub> cycle starts on the following drum revolution. If a numerical code is located in the p column of the instruction, the program counter relays are not dropped out during the  $p_1$  cycle. The appropriate functions are actuated during p2 time and on the following drum revolution, an  $I_1$  cycle is initiated which controls the entry of the next consecutive instruction into the register 30.

Means are provided herein for transferring data under the control of the control panel and without the use of the internally stored programs. Such transfers are limited to full records, however, and are initiated by pulsing suitable hubs on the control panel, as will become clear. These operations are referred to as copy operations and an obvious necessity therefor is to initiate the operation of the machine by loading a few internal instructions on one of the instruction tracks. A copy operation requires four cycles which are identified as the C1, C2, C3 and C4 cycles. The buffer is loaded during the  $C_1$  cycle and is unloaded during the  $C_2$  cycle.  $C_3$  is provided as wait time and during  $C_4$  a new control panel pulse is emitted for initiating further operation as may be desired.

Two additional cycles,  $D_1$  and  $D_2$ , are provided for yielding a delay when necessary for some reason. When a control panel pulse is entered into a delay entry hub, it exits from an exit hub two cycles later and in this way a two-cycle delay is obtained. Where successive copy operations are to be taken, it is necessary to separate them by a delay to allow the various relays involved to be transof cycle, i.e., odd or even, any interruption in the nor- 75 ferred. This is but one reason for the provision of the

delay, others being obvious to those familiar with programming of such machines as the present one. Where more than a two-cycle delay is desired, the pulse taken from the delay exit hub may be utilized to initiate another two-cycle delay by entering it into a second delay -5 entry hub.

When  $T_1$  is either S or R, or when  $T_2$  is P or R, the basic timing cycle of the machine is altered since the drum 10a of the input-output unit 10 and the various discs of the disc storage unit 11 are not synchronized with the process 10 drum 25. The processing unit is arranged to proceed through the I<sub>1</sub> and I<sub>2</sub> cycles in the manner described above; however, when  $T_1 = S$  or R, the system is placed in an interlocked condition on the E1 cycle which extends the  $E_1$  cycle until a signal is obtained which indicates 15 of a switch 48 (FIG 4a) to the line 41. As will bethat the buffer has been loaded by the sending track. The next odd cycle after this signal is received is the normal  $E_2$  cycle unless  $T_2 = P$  or R. Additionally, when  $T_2$  is either P or R, the  $E_1$  cycle occurs in the normal fashion (unless  $T_1 = S$  or R) and the  $E_2$  cycle is extended. It will 20 an error has been made. Thus, assuming no error and now be understood that if in a given instruction  $T_1 = S$  or R and  $T_2 = P$  or R, both the  $E_1$  and  $E_2$  cycles are extended.

The basic timing of the present machine is under the control of 24 circuit breakers CB-1 through CB-24 (FIG. 3a) which are operated by corresponding cams 34  $^{25}$ mounted on a shaft driven by the shaft upon which the process drum 25 is mounted. The cam shaft however, is driven at one-half the speed of the process drum. The various CB's are closed by the corresponding cam for 30 slightly more than a full drum revolution, the odd-numbered CB's being closed from 350° to 190° of the cam shaft rotation and the even-numbered CB's being closed from 170° to 10° of the cam shaft rotation. The make and break of these CB's roughly defines the odd and 35 even cycles referred to hereinabove.

One side of CB-2 is connected to +48 volts by a line 35, the other side thereof being connected through a line 36 to one side of a n/o start key 37 (FIG. 4b) which, when actuated, initiates the operation of the machine. 40 The second side of the start key 37 is connected through the n/c c points of a relay 38 and through a line 39 to one side of the pick coil of a relay 40, the other side of which is connected to ground. Thus, when the start key is actuated, CB-2 makes and the pick coil of the relay 40 is energized. One side of the hold coil of the relay 40 is 45 grounded and the other side thereof is connected through its n/o a contacts, through a line 41 and through CB-1 (FIG. 3a) to +48 volts, and when CB-1 makes the hold coil of the relay 40 (FIG. 4b) is energized (see FIG. 5). Thus, the relay 40 (FIG. 4b) is picked by an even CB 50 pulse and is held by the following odd CB pulse.

When the relay 40 is picked, its b contacts are transferred and the same CB-1 pulse that holds relay 40 is connected from the line 41 through these contacts, through a line 42 and through the pick coil of the relay 38 to 55 ground, thereby picking the relay 38 at this time. One side of the hold coil of the relay 38 is grounded and the other side is connected through its a contacts to the line 36 from which CB-2 pulses are taken. Thus, relay 40 is picked by the first even CB pulse after the start 60 key is actuated and is held by the next following odd CB pulse. The relay 38 is picked by the first odd CB pulse after the relay 40 is picked and is held by the following even CB pulse, as described. It should also be noted that the pick coil of the relay 38 is connected 65 by the line 42 through its n/o b contacts to the line 41, and under normal conditions the relay 38 is continuously energized, through either its pick or hold windings, by odd and even CB pulses, respectively, after the relay 40 has been picked. Additionally, it should be 70 noted that the relay 40 drops out when the relay 38 picks since the c contacts of the relay 38 are opened at this time.

One side of the pick coil of a relay 43 is connected to ground, the other side thereof being connected through 75 key 37 is actuated, odd CB pulses pass through these

a line 44 and through the n/o c contacts of the relay 40 to the line 41, and the first odd CB pulse after the relay 40 is energized picks the relay 43. Since the hold coil of the relay 43 is connected between ground and through its n/o a contacts to the line 36, the relay 43 is held during the following even CB pulse since at this time its a contacts are transferred.

In addition to being connected to the line 44, the pick winding of the relay 43 is connected through the n/c ccontacts of a relay 45 (FIG. 4a) and through the n/cc contacts of a relay 46 to one side of a matrix of relay points, the other side of which is connected by a line 47 through the n/o b contacts of the relay 43 (FIG. 4b) and by a line 47a through the armature and #2 contact come clear later, the above mentioned matrix of relay points presents an open circuit when  $T_2 = P$ , X or R, it being closed under all other conditions. Additionally, the relays 45 and 46 are energized only in the event that assuming further that  $T_2 \neq P$ , X or R, the pick coil of the relay 43 (FIG. 4b) is connected through its b contacts to the CB-1 pulse line 41 when the switch 48 is in the condition shown. Under the conditions defined above, therefore, the relay 43 is continuously energized, from the time that the contacts of the relay 40 are transferred until one of these conditions is not met, at which time the machine is put in an interlocked condition as will be explained.

The line 36 (FIG. 4b) is connected through the n/o dcontacts of the relay 38 and through a matrix of relay points to a line 39 which is connected to one side of the pick coil of a relay 50, the other side of which is grounded, and when the relay 38 picks, as described above, its d contacts are transferred and the pick coil of the relay 50 is energized, provided there is a path through the last mentioned matrix of relay points to the line 39. As will be explained later, the only time this matrix presents an open circuit is when  $T_1$ =either R or S. Since the hold coil of the relay 50 is connected through its own n/o a contacts to the line 41, it should be clear that the relay 50 is picked by the first even CB pulse after the relay 38 is picked and that it is held during the following odd and even CB pulses as long as the relay 38 is energized, and as long as  $T_1 \neq S$  or R.

One side of the pick coil of a relay 51 is connected to ground, the other side being connected through a line 52, through the n/c e points of the relay 40, through the n/c e points of the relay 50 to the CB-1 pulse line 41. The hold coil of the relay 51 is connected between ground and one side of its n/o a contacts, the other side of these contacts being connected to the line 36. Thus, the relay 51 is picked by odd CB pulses and is held by even CB pulses until either relay 40 or relay 50 is energized, i.e., until the odd cycle following actuation of the start key 37 since at this time the contacts of the relay 40 transfer. After the relay 40 drops out, the relay 50 picks, thereby preventing further energization of the relay 51 as long as the relay 50 is energized.

The line 36 is connected through the n/c e contacts of the relay 43 to one side of the pick coil of a relay 53, the other side of which is grounded. Additionally, the line 41 is connected through the n/o a contacts of the relay 53 to one side of the hold coil of this relay, the other side thereof being grounded. Thus, the relay 53 is picked and held by even and odd CB pulses, respectively, until the e contacts of the relay 43 are transferred, at which time the relay 53 drops out.

Referring now to FIG. 3a, the line 41 connected to one side of CB-1 is also connected through the n/o hcontacts of the relay 50 and through the n/c b contacts of the relay 53 to a line 54, and as long as the relay 50 is energized and the relay 53 is not energized, as is the normal condition (see FIG. 5) soon after the start

contacts and appear on the line 54 (FIG. 3a). Similarly, the line 36 connected to one side of CB-2 is connected through the n/o h contacts of the relay 43 and through the n/c b contacts of the relay 51 to a line 55 from which even CB pulses are taken as long as the relay 43 is energized and the relay 51 is deenergized. This again is the normal condition after the start key is actuated. Odd CB pulses also appear on a line 57 connected through the n/c d and c points of the relay 53 to one side of CB-3 and even CB pulses also appear 10 on a line 58 connected through the n/c d and c points of the relay 51 to one side of CB-4 as long as the relays 53 and 51, respectively, are deenergized. It should be noted, however, that when the contacts of the relay 53 are transferred and when the relay 51 is deenergized, 15odd CB pulses appear on the line 58. Also, even CB pulses appear on the line 57 when the relay 53 is deenergized and when the contacts of the relay 51 are transferred.

The odd CB pulse taken from the line 54 is designated 20 herein as an "odd pick" pulse, the pulse taken from the line 55 being called an "even pick" pulse. Additionally, the pulses taken from the lines 57 and 58 are referred to as "even hold" and "odd hold" pulses, respectively, it being remembered that these pulses are 25normally odd and even CB pulses, respectively. The pulses taken from the line 54, 55, 57, 58 are utilized to control the operation of various relays to be described, which define the  $I_1$ ,  $I_2$ ,  $E_1$ , etc., cycles mentioned previously.

Referring now to FIG. 6b, if it is assumed that a 48volt pulse is initially applied to one side of the pick coil of a relay 60 through a line 61, the source of which pulse will be described later, it will be clear that the relay 60 is picked thereby since the other side thereof is grounded. The relay 60 defines the  $I_1$  cycle and, as will become clear, the pulse applied thereto is an odd CB pulse. When energized, the n/o a contacts of the relay 60 are transferred, and since the hold coil of this relay is connected between ground and the odd hold line 58 40 through these a contacts, the relay 60 is held by the odd hold pulse. The odd hold pulse is an even CB pulse, as described earlier, and the  $I_1$  relay 60 is thus held during an even cycle, at the end of which time it drops out.

The pick coil of the  $I_2$  relay, i.e., a relay 62, is con-45nected between ground and through the n/c h points of a relay 63, through the n/o b contacts of the  $I_1$  relay 60 and through the n/c c contacts of another error relay 64 to the line 55. Thus, the  $I_2$  relay is picked by an even pick pulse following the energization of the  $I_1$  relay 5060 provided the relays 63 and 64 are deenergized. When this occurs, the n/o a contacts of the relay 62 are transferred and the hold coil thereof is connected between the even hold line 57 and ground, thereby energizing the hold coil for the duration of the next even hold 55 pulse, i.e., odd cycle. The relay 62, like the relay 60, is therefore energized for only one cycle since as soon as the relay 60 drops out its b contacts open the circuit from the line 55 thereto, thereby causing the relay 62 to drop out at this time.

The  $E_1$  and  $E_2$  cycles are defined by two relays 65 and 66, respectively, in a similar manner. The pick coil of the relay 65 is connected between ground and by a line 65a through the n/o d contacts (FIG. 6a) of the relay 62 to a line 67, which line is connected through the n/c dcontacts of the error relay 45 and through the n/c b contacts of the error relay 46 to the odd pick line 54. Relays 45 and 46, it will be recalled, are picked only when an error has been indicated by the machine, and therefore under normal conditions these relays are deenergized and 70 their contacts are in the condition shown in the drawing. Thus, when the  $I_2$  relay 62 (FIG. 6b) is energized, its d contacts (FIG. 6a) are transferred and odd pick pulses are connected therethrough to the pick coil of the relay

3,026,036

5

nected between ground and through its n/o a contacts to the odd hold line 58. Thus, when the relay 62 picks, the next following odd pick pulse picks the relay 65 and the following odd hold pulse holds the relay 65 for the duration thereof. The relay 65, therefore, is energized for only one cycle, i.e., an even cycle, since prior to the next odd pick pulse the relay 62 drops out, thereby opening its d contacts (FIG. 6a) and opening the circuit to the pick coil thereof.

The pick coil of the  $E_2$  relay 66 (FIG. 6b) is connected between ground and through the n/o b contacts of the relay 65, through the n/c c contacts of the error relay 64 to the even pick line 55, the hold coil of the relay 66 being connected between ground and through its n/o acontacts to the even hold line 57. Thus, as long as there is no error, i.e., as long as the relay 64 is deenergized, and if the contacts of the  $E_1$  relay 65 are transferred, an even pick pulse energizes the pick winding of the E2 relay 66, the next following even hold pulse being arranged to hold this relay for the duration thereof. Thus, the relay 66 is energized for one cycle and defines the  $E_2$  cycle (odd).

In addition to being connected to a pulse source to be described, the line 61 (FIG. 6a) connected to one side of the pick coil of the  $I_1$  relay 60 is also connected through a diode 145 and through a series of n/c points of several relays 750 through 745, to be described later, to a line 68 which is in turn connected through a plurality of parallelly arranged points of several relays 715, 718, 719, 720 and 752, to be described, to a line 69. The line 69 is connected through the n/o b contacts of the relay 66 to the line 67. The various aforementioned series of contacts provide a closed circuit between the line 61 and the line 68 when the p portion of the instruction is blank, the parallelly arranged points providing a closed circuit when either  $T_2 \neq R$  or q = c. Thus, when the p portion of the instruction is blank and either  $T_2 \neq R$  or q=c, the line 61 is connected to the line 69 and the I<sub>1</sub> relay is picked by the odd pick pulse following energization of the  $E_2$  relay 66 since the *b* contacts of the relay

66 are transferred at this time. When p is not blank, one of a plurality of n/o, parallelly arranged points of the relays 746 through 750, one side of each of which is connected to a line 70, is closed. The other side of these relay points is connected to the line 68, and since the line 70 is connected to one side of the pick coil of the relay 63 (FIG. 6b), the other side of which is grounded, the relay 63 is picked by the next following odd pick pulse when p is not blank and when either  $T_2 \neq R$  or q=c, if the contacts of the E<sub>2</sub> relay **66** are transferred, there being no prior error. The relay 63 defines the  $p_1$  cycle and is energized on the cycle following the  $E_2$  cycle only if the p portion of an instruction is not blank. This relay is held by an odd hold pulse, the hold coil thereof being connected between ground and through its n/o a contacts to the odd hold line 58. Thus, the  $p_1$  relay 63 defines the  $p_1$  cycle (even) and when it is picked, its n/c h contacts are also opened, thereby preventing energization of the  $I_2$  relay 62.

60 Also, at this time the n/o b contacts of the relay 63 are closed, thereby connecting one side of the pick coil of a relay 72, the  $p_2$  relay, therethrough and through the n/c c contacts of the error relay 64 to the even pick line 55, and it will be clear that the next even pick pulse after the relay 63 is picked energizes the relay 72. The hold coil of the relay 72 is connected through its n/o a contacts to the even hold line 57, thereby holding this relay for the duration of the even hold pulse. Thus, neither relay 63 nor 72 is picked if p is blank, the relays 60, 62, 65 and 66 being arranged to repeat the above described sequence until p is not blank, at which time the relays 63 and 72 are sequentially energized as described, thereby defining the  $p_1$  and  $p_2$  cycles, respectively.

It will be recalled that when p is numeric it is desired 65 (FIG. 6b). The hold coil of the relay 65 is con-75 to resume the program from the point where it left off

3,026,036

5

and that when p is alphabetic a new program is initiated.