digital

#### FEATURES

- . Interfaces to most models of the IBM 360 or 370 on the selector, multiplexer or block multiplexer channels

- · Recognizes up to 128 IBM device addresses over the full range of 256 addresses.

- · Operates in the byte multiplexed or burst mode

- NPR (DMA) operations to present status to 360, store 360 commands in the PDP-11, and transfer data

- · Hardware recognition and presentation of the 360 device address plus hardware presentation of initial status

- Software interpretation and response to 360 commands

- · Can be programmed to emulate a 2848, 2703 or 3705 control unit

- In off-line or powered-down mode, the DX11B is transparent to the S/360 and presents no load to the channel data and tag lines

- Built-in maintenance and protection features

- 250,000 byte/second data transfer rate (depending upon IBM model)

#### DESCRIPTION

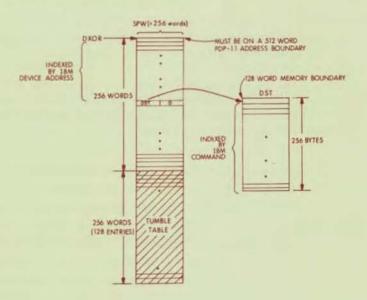

The DX11B is a programmable interface between a PDP-11 UNIBUS<sup>™</sup> and a S/360 or S/370 multiplexer or selector channel. The DX11B hardware handles the detection and response to all channel generated control signals. The DX11B hardware handles the Initial Selection Sequence operation without program intervention. It recognizes a wired (strapped) set of addresses, presents address, fetches a unique status (determined by the 360/370 command and device address) from a table in memory and stores an entry in a 128 entry tumble table. The status and tumble operations are by NPR (DMA). The tumble table entry contains status, IBM command and IBM address. Software interprets the command and responds to it. The commands recognized and the manner of response will depend upon the 360/370 control unit being emulated.

As soon as the hardware has stored the tumble table entry, it is ready to service another request from the 360/370. If both the PDP-11 and the 360/370 channel contend for the DX11B, the 360/370 channel wins and the PDP-11 is locked out. This protection feature makes sure the 360/370 channel is always master. It can cancel a previous request at any time.

The PDP-11 program loads DX11B registers to cause data transfers. Data transfer is by NPR. The length in bytes can be short (multiplex mode) or long (burst mode). Software determines which mode will be used. Burst mode is on selector channel or selector subchannel only.

The DX11B can be taken off-line or powered down. In either case, a relay closes to by-pass the SELECT-OUT line. The drivers and receivers on the 360/370 control and data lines present no bus loads when the DX11B is powered down. Thus, the DX11B is logically disengaged from the channel in the power-down or off-line mode. The DX11B contains power failure and timeout features. The power failure protection hardware interrupts the DX11 when an AC-low is detected. When in burst mode, timeout hardware interrupts the DX11 if the PDP-11 fails to respond in 5 seconds. In either case, the DX11B hardware stops all data transfers, presents UNIT CHECK status to the 360/370 and goes off-line. The programmer can disable the timeout feature during program debugging. The timeout will occur only while one of the DX11B-recognized devices is active (OPERATIONAL-IN is high).

The DX11B has a built-in channel simulator which is used by off-line diagnostics to verify the PDP-11 configuration up to and including the IBM cables. The latter can be checked by plugging one end into the DX11B and the other into the simulator.

Because NPR is used for data transfers, the DX11B is capable of data transfer rates in excess of 250,000 bytes/ second. It is limited by the PDP-11 configuration and the rated capacity of the 360/370 channel to which it is attached.

#### PROGRAMMING

#### **Programming Interfaces**

#### Registers

The DX11B has the following set of programmable registers:

| Address | Description                      |

|---------|----------------------------------|

| 176200  | Device Status (DXDS)             |

| 176202  | Command and Address (DXCA)       |

| 176204  | Control Unit Status (DXCS)       |

| 176206  | Offset and Status (DXOS)         |

| 176210  | Bus Address for NPR (DXBA)       |

| 176212  | Byte Count for NPR (DXBC)        |

| 176214  | Maintenance-Out (DXMO)           |

| 176216  | Maintenance-In (DXMI)            |

| 176220  | Control Bits (DXCB)              |

| 176222  | NPR Data (DXND)                  |

| 176224  | Extra Signals (DXES1)            |

| 176226  | Maintenance-Out Buffered (DXMOB) |

| 176230  | Extra Signals (DXES2)            |

#### REGISTERS

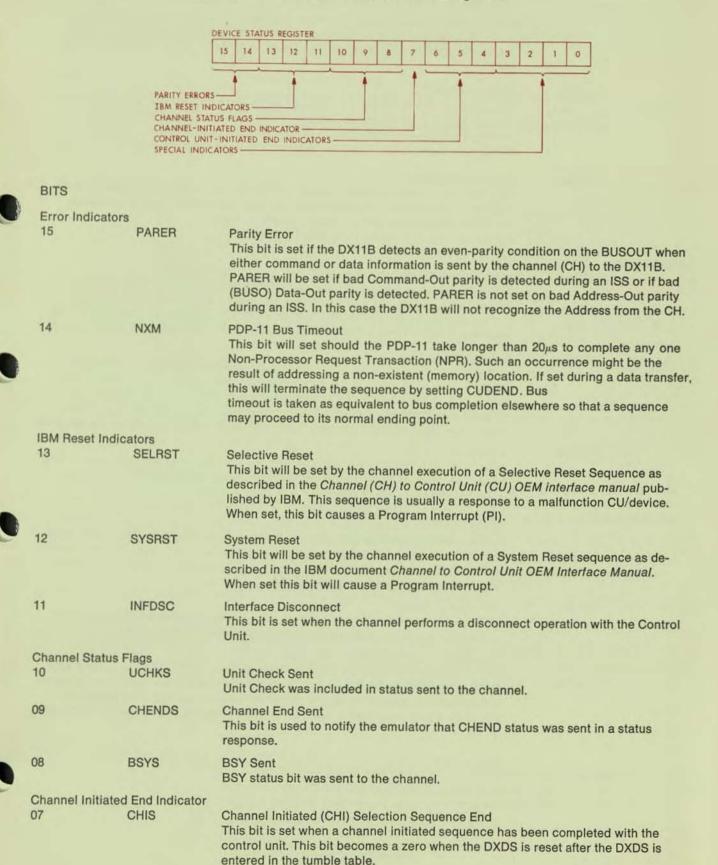

DXDS

#### DEVICE STATUS

This register contains all of the interrupt producing conditions along with various non-interrupt producing device status flags. This register is read only and is stored as the first tumble table entry before being reset.

| Control Unit In<br>06 | itiated (CUI) End<br>ESEND | Indicators (PDP-11/DX11B)<br>Ending Sequence End<br>This bit will set when a status byte is presented to the channel by a DX11 initial-<br>ized sequence and/or when a stacked status is finally accepted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                            | This bit is most commonly associated with the Ending Status presentation type of sequence which normally follows a Data Transfer Sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |                            | It may under some circumstances occur that the CHIS bit is set as a result of a CUI-ISS contention situation where the device address requested matched with the device address selected from the channel and the CU was requesting present status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 05                    | CHDEND                     | Channel Data End<br>This bit is set during a Data Transfer Sequence when the channel byte count over-<br>flows (Command-Out is sent in response to Service-In). This bit in its true state<br>causes the CU to terminate the Data Transfer Sequence. This bit is also set when<br>the CH terminates a Data Transfer Sequence by interface disconnect (INFDSC=1).                                                                                                                                                                                                                                                                                                                                                      |

| 04                    | CUDEND                     | Control Unit Data End<br>This bit is set during a Data Transfer Sequence when the DXBC (byte count)<br>register goes to its all zero state. When set, this bit causes a PI and also causes<br>the DONE bit to assert. When this bit asserts, it causes<br>the CU to terminate the Data Transfer Sequence.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Special Indicat       |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 03                    | ISSREJ                     | Initial Selection Sequence Rejected<br>This bit is set when a channel-initiated selection sequence addressed to the CU<br>was answered by the CU with a Control Unit Busy status indication and a short<br>Control Unit Busy sequence. This can only occur if the CUBSY bit in the DXCS<br>was set when the CH tried to initiate an ISS and the CU was in its idle phase.                                                                                                                                                                                                                                                                                                                                             |

| 02                    | CMDCHN                     | Command Chaining<br>This bit sets if the channel has indicated that another operation will probably<br>follow for the CU/Device currently connected when the DX11B presents Device<br>End status to the channel. Command chaining occurs when the current 360<br>Channel Command Word (CCW) has its command chaining bit set. The channel<br>informs the DX11 of this by raising Suppress-Out at the same time as Service-Out.                                                                                                                                                                                                                                                                                        |

| 01                    | STKSTB                     | Stack Status Copy<br>This bit is set when the Channel (CH) informs the DX11 that the status byte being<br>presented on the BUS-IN cannot currently be accepted by the CH. This occurs<br>when the CH responds to Status-In with Command-Out.<br>STKSTA may be set by the program if the DX11 is not active with the CH<br>(LOCK=0). This is useful when initiating a DX11 request for status presentation.<br>If Suppress-Out and STKSTA are both true, the DX11 drops its Request-In since<br>the status contained is suppressible (once status has been stacked the CH also<br>defines that status as suppressible). Since this bit is a copy of STKSTA, it is read<br>only and is not reset with the rest of DXDS. |

| 00                    | CMDREJ                     | Command Rejected<br>A Channel Initiated Selection Sequence command was ignored due to bad parity,<br>a busy device, a pending status, or an illegal command for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DXCA                  |                            | COMMAND AND ADDRESS<br>DXCA contains the control unit command register, CUCR, and the control unit<br>address register, CUAR. These two bytes are the address and command as trans-<br>mitted from the channel during an initial selection sequence. This register is<br>stored as the second tumble table entry upon completion of a CH-CU interaction.                                                                                                                                                                                                                                                                                                                                                              |

| COMMAND AND ADDRESS REGISTERS |    |    |       |    |    |   |   |   |   |   |   |               |   |   |   |

|-------------------------------|----|----|-------|----|----|---|---|---|---|---|---|---------------|---|---|---|

| 15                            | 14 | 13 | 12    | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3             | 2 | 1 | 0 |

|                               |    |    | ONTRO |    |    |   |   | - |   |   |   | OL UN<br>REGI |   |   |   |

| BITS  |      |                                                                                                                                                                                                                                                                                                                                                                |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-08 | CUCR | The odd byte of the DXCA register contains the Control Unit Command Register (CUCR). The CUCR cannot be loaded by the program. This byte contains the last command sent by the channel (even if it was rejected by the DX11).                                                                                                                                  |

| 07-00 | CUAR | The even byte contains the Control Unit Address Register (CUAR). The CUAR is loaded with the device address from Bus-Out during an initial selection sequence. The CUAR is also loaded and cleared via PDP program control if LOCKO is a (0). The CUAR need not be loaded with some device address that is to be supported by the DX11 prior to going ON-LINE. |

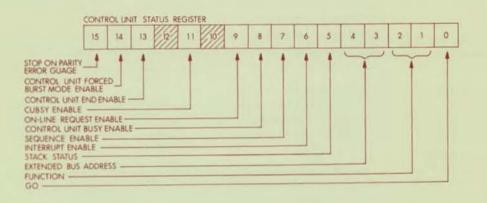

| DXCS  |      | CONTROL UNIT STATUS<br>This register contains the primary control command information bits and primary<br>status indications for the DX11. The DXCS may not be modified by the PDP<br>program when LOCKO equals one (except for DONE and INTEN).                                                                                                               |

| BITS |        |                                                                                                                                                                                                                                                                                                                        |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | PARSTP | Stop on Parity Error Enable<br>If this bit is set to a one and a parity error occurs on Bus-Out during a Data<br>Transfer Sequence, then the sequence is terminated and CUDEND will be set. If<br>this bit is not set, PARER may still become set but the sequence will end normally.                                  |

| 14   | CUFBM  | Control Unit Forced Burst Mode Enable<br>This bit can be set by the program when CU Forced Burst mode is desired. This<br>condition causes the CU to hold OPL-IN up from initial selection through the<br>presentation of Channel End (except for TIO and IIIO).                                                       |

| 13   | ENDEN  | Control Unit End Enable<br>This bit is set and cleared only by the PDP-11 program. The purpose of setting<br>this bit is to assert the control unit end bit (CUEND) in the device status presented<br>to the channel during a control unit busy sequence; i.e., where the CUBSY bit is<br>already set.                 |

| 12   |        | Reserved                                                                                                                                                                                                                                                                                                               |

| 11   | BSYEN  | CUBSY Enable<br>This bit enables the setting of CUBSY immediately upon responding to an ISS<br>(either CUI or CHI). This bit is set to a one by the program for emulating any single<br>thread (shared) control unit such as 2848, 2803 and 2821. It is set to zero for<br>multiple-thread control units such as 2703. |

| 10   |        | Reserved<br>This bit is reserved for future use.                                                                                                                                                                                                                                                                       |

|      |        |                                                                                                                                                                                                                                                                                                                        |

| 09     | ONLINA | On-Line Request Enable<br>This bit is writable (except when LOCKO is set) by the PDP program to either the<br>one or the zero state. ONLINA indicates that the control unit has made or is<br>making a request to go on-line to the 360 channel. It is a two-stage operation.<br>This is the lower stage of going on- or off-line operation and is the stage loaded<br>or cleared by program command (ONLINA: DXCS(09)). The upper stage is the<br>operating on-line bit ONLINB (DXCB(02)). ONLINB follows the changes of ONLINA<br>at a time when, as specified in the OEM channel manual (IBM), it is proper to<br>make changes from on-line to off-line or from off-line to on-line. (The CH is<br>considered on-line itself whenever Operational-Out is set.) |   |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 08     | CUBSY  | Control Unit Busy Enable<br>Setting this bit will cause a channel initiated sequence to be answered by the<br>DX11 with a Control Unit Busy Sequence. This bit causes the BSY bit to assert to<br>the BUS-IN during the subsequent status presentation from the DX11. This bit is<br>set and cleared by program and by the DX11 hardware if so enabled by BSYEN.                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| 07     | DONE   | Sequence Done<br>The DONE bit is the normal interrupt producing condition which the DX11 uses<br>for its primary interrupt control (c.f., INTEN). If both DONE and INTEN are set an<br>interrupt will be requested.<br>Clearing DONE is required (of the program) only before making an attempt to<br>change registers. With DONE reset, the DX11 will reset LOCKO if the DX11 is in<br>either phase 0 or phase 7. Loading DONE is allowed only in phases 0 or 7.                                                                                                                                                                                                                                                                                                 | - |

| 06     | INTEN  | Interrupt Enable<br>This bit is always writable. It is recommended that this bit always be set before<br>setting ONLINA and that ONLINB (via ONLINA) be cleared prior to clearing this<br>bit. This bit may be cleared or set by program control only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| 05     | STKSTA | Stack Status<br>If set, STKSTA indicates that status was stacked. When cleared, it indicates that<br>status was accepted. It may also be set voluntarily by a program that is presenting<br>a suppressible (or low priority) status. It is also set automatically by the<br>DX11 when the CH requires a status to be stacked and the DX11 will attempt to<br>present it again.                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 04, 03 | ХВА    | Extended Bus Address Bits<br>These bits are the two extended most significant bits of the memory address<br>register during data input/output. They are loaded and cleared under program<br>control and may be caused to complement should the DXBA overflow from a<br>DXBA increment of +2 during a data transfer. They are used only during a data<br>sequence.                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| 02, 01 | FCTN   | Function<br>These two bits make up the DX11 function register. It is used by the program to<br>select the CU operations desired:<br>FCTN=0—reset the DX<br>FCTN=1—input data transfer (from 360/370)<br>FCTN=2—output data transfer (to 360/370)<br>FCTN=3—present asynchronous status (to 360/370)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| 00     | GO     | When the GO bit is set, the function requested is performed. If FCTN=0 the reset operation is done on the DX11 and the DONE bit is left cleared.<br>If FCTN is not zero, then Request-In (REQI) will be raised as the start of a Control Unit Initiated (CUI) sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| DXOS   |        | OFFSET AND STATUS<br>This is a two-byte register. The odd byte (CUOR) contains the offset address of<br>the Status Pointer Word (SPW) table located in PDP-11 memory. The even byte<br>(CUSR) contains the status byte that will be presented to the 360/370.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| OFFSE | T ANI | D STAT | US RE | GISTE  | R  |   |   |   |   |   |   |   |   |   |   |

|-------|-------|--------|-------|--------|----|---|---|---|---|---|---|---|---|---|---|

| 15    | 14    | 13     | 12    | 11     | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| -     | -     |        |       | all in |    |   | - | - |   | - |   |   |   |   | _ |

OFFSET REGISTER

|                 | Sec. |    | (UL | 101.4 | 11 |

|-----------------|------|----|-----|-------|----|

| STATUS REGISTER | ATI  | JS | REC | GIST  | ER |

| 15-08 | CUOR   | Control Unit Offset Register<br>The CUOR contains the high order six bits of the SPW table and of the tumble<br>table. It is program-loaded while in the off-line mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07-00 | CUSR   | Control Unit Status Register<br>The CUSR contains the standard IBM status information bits which are transmitted<br>to the channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 07    | ATTEN  | Attention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 06    | STAMOD | Status Modifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 05    | CUEND  | Control Unit End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 04    | BSY    | Busy<br>The program should not directly set this bit. This bit is set only by a CU Busy<br>Sequence or by being loaded as the status portion of the Status Pointer Word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 03    | CHEND  | Channel End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 02    | DEVEND | Device End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 01    | UCHECK | Unit Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 00    | UEXCEP | Unit Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DXBA  |        | BUS ADDRESS REGISTER<br>The bus address register is a 16-bit register which can be cleared and loaded<br>under program control if LOCKO is not set (0). It is used during data transfers to<br>point to the PDP-11 core location to/from which data will be transferred 16-bit<br>words at a time. The DXBA register is also used during channel initiated sequences<br>to fetch both the Status Pointer Word and the device status byte from PDP-11<br>core. During a data transfer the DXBA is preset by program to point to the first<br>byte location where data is sent or stored. The DXBA register is incremented by<br>two each time a PDP data word is fetched or stored in core during the data<br>transfer process. Should the DXBA register overflow, the extended memory |

address bits (XBA) in the DXCS register will be caused to complement their states appropriately. The DXBA is also used to address the tumble table when information is to be stored there.

BUS ADDRESS REGISTER

**DXBA(00)**

BITS

DXBC

The low order bit of the DXBA is normally set to zero by program load. When this bit is placed on the UNIBUS address lines (ABUS), it is always represented as zero. This bit is also used to initiate the BALF flop when control is transferred to phases 5 or 6 to select the odd or even first byte of the first data word.

#### BYTE COUNT

This register is used only during data transfers. It is loaded and cleared under program control and is set up prior to the data transfer involved. The DXBC is set to the negative of the number of bytes to be transferred. As each byte is actually transferred to/from the DX11, the DXBC register is incremented by one until all bytes are transferred, whereupon the DXBC equals zero. When the DXBC contents go to zero during a Data Transfer Sequence, the CUDEND bit of the DXDS will set, thereby terminating the data transfer sequence with the channel.

| 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 15 14 13 12 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------------------------------|----------------|----|---|---|---|---|---|---|---|---|---|---|

|---------------------------------------|----------------|----|---|---|---|---|---|---|---|---|---|---|

BYTE COUNT REGISTER

DXMO

#### MAINTENANCE-OUT

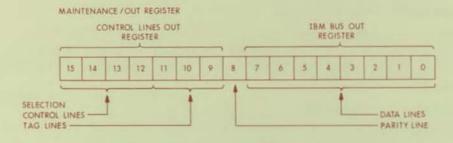

This register is used for holding the 360 Channel Bus-Out Data and Tags. This register is always directly readable by a PDP-11 program.

When the DX11 is On-line, the bits in this register are usually the same as what appears on the Bus-Out lines (hardwired cables to the Bus-Out Plug).

When the DX11 is Off-line, these bits may be written directly by a PDP programmed request. The programmed bits are held buffered in the DXMOB. When the DX11 is On-line but cabled to the Bus-Out Test Plug, these bits are also writable by PDP-11 programs. The on-line cabled mode is used to isolate the cables and Bus-Out receivers as an error source.

| BITS        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 15-08       | CONO          | Control Out-Lines Register<br>This byte contains the following signals as strobed from either the Bus-Out lines<br>or from CONOB:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • |

| Selection ( | Control Lines |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| 15          | OPLO          | Operational-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|             |               | This line indicates that the channel is in operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|             |               | Note: refer to IBM manual A22-6843 for detailed description of each line of the<br>360 bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 14          | HLDO          | Hold-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - |

| 13          | SELO          | Select-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|             |               | This bit is set only if both hold-out and select-out are set. When set or cleared by a PDP-11 program, only the simulated select-out signal is affected (see DXMOB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| 12          | SUPO          | Suppress-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| Tag Lines   |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| 11          | ADRO          | Address-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 10          | CMDO          | Command-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 09          | SRVO          | Service-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Parity Line |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| 08          | PARO          | Parity-Out<br>This bit does double duty when written by a PDP program while the DX11 is in<br>on-line cabled mode. At such times the state of the bit will be translated directly<br>into the state of the Simulated Clock-Out line (of the Bus-Out Test Plug) and into<br>the Parity-Out line. Clock-Out's primary purpose is to synchronize the control<br>units to make changes in their ON/OFF-LINE state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • |

|             |               | A construction of the later of the second se |   |

Another function of the bit is to allow the program generation of either normal (odd) Parity-Out or "bad" (even) Parity-Out. This feature is necessary in order to permit checking the parity generator within the main DX11 logic.

Data Lines 07-00

DXMI

BUSO

IBM Bus-Out Register

Bus-Out data bits 0 to 7, as seen either directly from the Bus-Out Cables or from BUSOB, if off-line.

When written by the PDP-11 program, this byte is buffered in BUSOB.

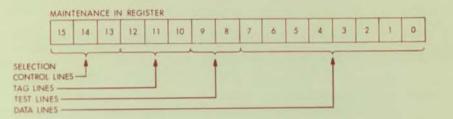

#### MAINTENANCE-IN

This register is used for reading the Bus-In Tags and data originating mainly from the main DX11 logic. In this way the register represents the channel's view of the Bus-In. The output of these flops is enabled to the Bus-In lines either whenever OPLI=1 or whenever a fast CU-Busy is in progress.

The register is normally read only, but for maintenance purposes programmed modification is permitted except for CLKO and PARI.

When the DX11 is off-line, the data read by PDP-11 programmed references come directly from DXMI. When the DX11 is on-line, the data read by the PDP-11 program comes from the Test-In plug. Correct data will be seen then only if the plugs are cabled together.

#### BITS

|   | 15-08              | CONI                | Buffered Control Lines in Register<br>This byte contains the following signals:                                                                                                                                                                        |

|---|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Selection Co<br>15 | ntrol Lines<br>OPLI | Operational-In                                                                                                                                                                                                                                         |

|   | 14                 | SELI                | Select-In (not direct cleared)                                                                                                                                                                                                                         |

|   | 13                 | REQI                | Request-In                                                                                                                                                                                                                                             |

|   | Tag Lines<br>12    | ADRI                | Address-In                                                                                                                                                                                                                                             |

|   | 11                 | STAI                | Status-In                                                                                                                                                                                                                                              |

| - | 10                 | SRVI                | Service-In                                                                                                                                                                                                                                             |

|   | Test Lines<br>09   | CLKO                | Clock-Out signal from Bus-Out<br>This line always comes from the cables, even when the DX is off-line.                                                                                                                                                 |

|   | 08                 | PARI                | Bus Parity-In (not a flip-flop—output of parity generation for BUSI)                                                                                                                                                                                   |