# TBM Field Engineering Manual of Instruction

### 2075 Processing Unit -- Volume 3

Fixed Point I Execute Branch Floating Point Variable Field Length

223-2874-1

#### PREFACE

This is one of six Field Engineering manuals for the 2075 Processing Unit. These six manuals contain the unit theory of operation, reference diagrams to be used when troubleshooting, and maintenance procedures.

A basic knowledge of the IBM System/360 as contained in the IBM System/360 Principles of Operation, Form A22-6821 is considered a prerequisite for studying the unit theory of operation. The theory of operation is contained in a four volume manual identified as a Field Engineering Manual of Instruction (FEMI). Volume 1 is a prerequisite for the detailed information contained in volumes 2, 3, and 4. Volume 1 contains the introduction to the system and the processing unit and a description of the functional units (registers, adders, and decoders) of the processing unit. Volumes 2 and 3 contain detailed information on special features and power supplies and control.

The four volumes of theory of operation contain many references to the diagrams packaged in the associated Field Engineering Diagrams Manual (FEDM). All diagrams in the FEDM are identified by a four digit figure number and unless otherwise specified, all four digit figure references in the FEMI indicate that the figure is contained in the associated FEDM.

The complete titles and form numbers of the six 2075 Field Engineering Manuals are:

- 2075 Processing Unit--Volume 1, Comprehensive Introduction, Functional Units, Field Engineering Manual of Instruction, Form 223-2872

- 2075 Processing Unit--Volume 2, Theory of Operation: Storage Bus Control; Instruction Preparation; FLT, Logout, MCW; Interrupts, Field Engineering Manual of Instruction, Form 223-2873

- 2075 Processing Unit--Volume 3, Theory of Operation: Fixed Point, I Execute, Branch, Floating Point, Variable Field Length, Field Engineering Manual of Instruction, Form 223-2874

- 2075 Processing Unit--Volume 4, Special Features, Power Supply and Control, Appendix, Field Engineering Manual of Instruction, Form 223-2875

- 2075 Processing Unit, Field Engineering Diagrams Manual, Form 223-2876

- 2075 Processing Unit, Field Engineering Maintenance Manual, Form 223-2880

#### MAJOR REVISION (January, 1966)

This edition, Form 223-2874-1 is a major revision of the previous edition, Form 223-2874-0. The major changes in this edition are the expansion of the introduction to the "Fixed-Point" section, and the complete revision of "Fixed-Point Divide." There are minor changes throughout.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Systems Development Division, Product Publications, Dept. 520, CPO Box 120, Kingston, N. Y., 12401

C 1965 by International Business Machines Corporation

#### CONTENTS

| T  | KED POINT                              |      | •    | ٠   | •   | •  | •   | •    |      | ٠  | • | • | • | 7    |

|----|----------------------------------------|------|------|-----|-----|----|-----|------|------|----|---|---|---|------|

| nt | roduction                              | ٠    | ٠    | ٠   | ٠   | ٠  | ž.  | •    |      |    | • | • |   | 7    |

|    | Operands                               | •    | ÷    | •   | ٠   | •  | •   |      | •    | •  | ٠ | • |   | 7    |

|    | Numeric Operands                       | 5    | •    | e   | •   | •  |     | ÷    |      |    | • | • |   | 7    |

|    | Overflow                               |      | •    | •   | •   |    |     | •    | •    |    | • |   | • | 7    |

|    | Condition Code .                       | •    | •    |     | •   | •  |     |      |      | •  |   |   |   | 8    |

|    | Instruction Format                     | •    | •    | •   | •   | •  |     |      |      |    |   |   |   | 8    |

|    | Program Interrupts                     |      | •    |     | •   | •  |     |      |      |    | • |   |   | 8    |

| Гł | eory of Operation                      |      | •    |     |     | •  |     |      |      |    |   |   |   | 9    |

|    | <b>Register</b> Operands               |      |      |     |     |    |     |      |      |    |   |   |   | 9    |

|    | Put-Away                               |      |      |     |     |    |     |      |      |    |   |   |   | 9    |

|    | Condition Registe                      | r Se | etti | ng  |     |    |     |      |      |    |   |   |   | 9    |

|    | Program Interrupts                     | 5    |      |     |     |    |     |      |      |    |   |   |   | 9    |

|    | MODAR Trigger                          |      |      |     |     | •  |     |      |      |    |   |   |   | 11   |

|    | Load (L, LR)                           |      |      |     |     |    |     |      |      |    |   |   |   | 12   |

|    | Load and Test (LTR)                    |      |      |     |     |    |     |      |      |    |   |   |   | 12   |

|    | Load Positive (LPR)                    |      |      |     |     |    |     |      |      |    |   |   |   | 12   |

|    | Load Negative (LNR)                    |      |      |     |     |    |     |      |      |    |   |   |   | 12   |

|    | Load Complement (L                     |      |      |     |     |    |     |      |      |    |   |   |   | 13   |

|    | Load Address (LA)                      |      | S    |     |     |    |     |      |      |    |   |   |   | 13   |

|    | Add (A, AR)                            |      |      |     |     |    |     |      |      |    |   |   |   | 13   |

|    | Subtract (S, SR) .                     |      |      |     |     |    |     |      |      |    |   |   |   | 14   |

|    | Condition Code Setti                   |      |      |     |     |    |     |      |      |    |   |   |   |      |

|    | Algebraic Add-Subtra                   |      |      |     |     |    |     |      |      |    |   |   |   | 14   |

|    | Condition Code 0                       |      |      |     |     |    |     |      |      |    |   |   |   | 15   |

|    | Condition Code 3                       |      |      |     |     |    |     |      |      |    |   |   |   | 15   |

|    | Add Logical (AL, AL                    |      |      |     |     |    |     |      | •    |    |   | • |   | 15   |

|    |                                        |      |      |     |     |    |     |      | •    |    |   | ٠ |   | 15   |

|    | Subtract Logical (SL,                  |      |      |     |     |    |     | •    | •    |    |   | ۲ |   | 15   |

|    | Compare (C, CR)                        |      |      |     |     |    | 1   | •    | •    |    |   | • |   | 24.2 |

|    | Compare Logical (CI                    |      |      |     |     |    | ٠   | •    | •    | •  |   | ٠ |   | 17   |

|    | Store (ST)                             |      |      |     |     |    | ٠   | ٠    | ٠    | ٠  |   |   | ٠ | 17   |

|    | Halfword Expansion                     |      | •    |     | •   | ٠  | •   | •    |      | •  | • | ٠ | ٠ | 17   |

|    | Load Halfword (LH)                     |      |      | •   | •   | ٠  | ٠   | ٠    | ٠    | ٠  | • | • | ٠ | 18   |

|    | Add Halfword (AH)                      |      |      |     | ٠   | ٠  | ٠   | ٠    | •    | ٠  | ٠ | • | ٠ | 18   |

|    | Subtract Halfword (S                   | 1    |      |     |     | ٠  | •   | •    | ٠    | •  | • | • | ٠ | 19   |

|    | Compare Halfword (                     |      | S    | ٠   | ٠   | •  | ٠   | •    | •    | ٠  | ٠ | ٠ | ٠ | 19   |

|    | Store Halfword (STH                    | )    | •    | ٠   | ٠   | ٠  | ٠   | ٠    | ٠    | •  | ٠ | ٠ | • | 20   |

|    | AND (N, NR)                            | ٠    | ٠    | ٠   | ٠   | •  | ٠   | •    | ٠    |    | ٠ | ٠ | • | 21   |

|    | OR (O, OR)                             | •    | •    | ٠   |     | •  | •   |      | ٠    |    | ٠ | • | • | 21   |

|    | Exclusive OR (X, XR                    | ()   | •    |     | •   | •  |     |      | •    |    | • |   | ٠ | 22   |

|    | Shift Right Single (S                  | RA   | )    |     | •   | •  |     | •    |      |    | • | • | • | 22   |

|    | Shift Right Double (S                  | SRI  | DA)  |     | •   | •  | •   | •    |      |    |   |   | • | 22   |

|    | Shift Left Single (SL                  | A)   |      |     | •   |    |     |      |      |    |   |   | • | 23   |

|    | Shift Left Double (SI                  | DA   | )    |     |     |    |     |      |      |    |   |   |   | 23   |

|    | Logical Shift Right S                  | Sing | le   | (SF | L)  |    |     |      |      |    |   |   |   | 23   |

|    | Logical Shift Right I                  | Dou  | ble  | (S  | RD  | L) |     |      |      |    |   |   |   | 23   |

|    | Logical Shift Left Sin                 | ngl  | e (S | LL  | )   |    |     |      |      |    |   |   |   | 23   |

|    | Logical Shift Left Do                  | oub  | le ( | SLI | DL) |    |     |      |      |    | ÷ |   |   | 23   |

|    | Circuit Descriptio                     |      |      |     |     |    | Ins | truc | ctic | ns | , |   |   | 23   |

|    | I Taken a strange and the state of the |      |      |     |     |    |     |      |      |    |   |   |   | 26   |

|    | Multiply Halfword (!                   |      |      |     |     |    |     |      |      |    |   |   |   | 26   |

|    | and Contract Instant                   |      |      |     |     |    |     |      |      |    |   |   |   | 26   |

|    |                                        |      |      |     |     |    |     |      |      |    |   |   |   | 29   |

|    |                                        |      |      |     |     |    |     |      |      |    |   |   |   | 30   |

|    | inter out a strong of the              |      | 1    |     | 1   |    |     |      |      |    |   |   | 1 |      |

| I  | EXECUTE                     |      |      |     |              | •    | •   |     |     |      |     | •  | •      |   | 34  |

|----|-----------------------------|------|------|-----|--------------|------|-----|-----|-----|------|-----|----|--------|---|-----|

| I  | ntroduction                 | •    |      |     |              | •    | 127 | •   |     | •    | •   | •  |        |   | 34  |

| ٦  | heory of Operation          |      |      |     |              |      | *   |     |     | •    | •   | •  | ٠      | • | 34  |

|    | Load PSW (LPSW)             |      |      |     |              |      |     |     |     | •    | •   | •  | •      |   | 34  |

|    | Set Program Mask            | : (S | PM   | )   |              |      | ٠   | •   |     | •    | •   |    | •      |   | 35  |

|    | Store Multiple (S'          | ГМ   | )    | •   |              |      |     |     |     |      |     |    | •      |   | 35  |

|    | Load Multiple (LN           | 1)   |      |     |              |      |     |     |     |      |     | •  |        |   | 38  |

|    | Start I/O (SIO)             |      |      |     |              |      |     |     |     |      |     |    |        |   | 40  |

|    | Test I/O (TIO)              |      |      |     |              |      |     |     |     |      |     |    |        |   | 40  |

|    | Test Channel (TC            |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Halt I/O (HIO)              |      |      |     |              |      |     |     |     |      |     |    |        |   | 41  |

|    | Set Storage Key (           |      |      |     |              |      |     |     |     |      |     |    |        |   | 41  |

|    | Data Flow                   |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Control                     |      |      | 4   |              |      |     |     | 4   |      |     |    |        |   | 42  |

|    | Insert Storage Key          |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Data Flow .                 |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Control .                   |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Diagnose                    |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    |                             |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    |                             |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

| -  | RANCH INSTRUCT              |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

| I  | ntroduction                 |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Units Other Than            | the  | e Br | anc | h U          | nit  | 2   | •   | •   | ٠    |     |    |        |   |     |

|    | Branch Unit .               |      |      |     |              |      |     |     |     |      |     |    |        | • |     |

| 1  | Theory of Operation         |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Branch Unit Opera           |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Preparation and E           | xec  | cuti | on  | of H         | Bran | hch | Ins | tru | ctio | ons | •  |        |   | 47  |

|    |                             |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

| F  | LOATING POINT               |      |      |     |              |      |     | e.  |     |      |     |    |        |   | 49  |

|    | ntroduction                 |      |      |     |              |      |     |     |     |      |     |    |        |   | 49  |

|    | Number Systems              |      |      |     |              |      |     |     |     |      |     |    |        |   | 49  |

|    | Instruction For             |      |      |     |              |      |     |     |     |      |     |    |        |   | 49  |

|    | Data Formats                |      |      |     |              |      |     |     |     |      |     |    |        |   | 51  |

|    | Normalization               |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Program Interr              |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Condition Cod               |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Floating-Point In           |      |      |     |              |      |     | ÷   |     |      |     |    |        |   | 53  |

|    | Add-Subtract                |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Compare .                   |      |      |     |              |      |     |     |     |      |     |    |        |   |     |

|    | Divide                      |      |      |     |              |      |     |     |     |      |     | ŝ. |        |   | 56  |

|    | Halve                       |      |      |     |              |      | 2   |     |     |      | 1   | 2  |        |   | 56  |

|    | Load                        |      |      |     |              |      |     |     |     |      |     | ċ  | Ċ      |   | 56  |

|    | Load Type .                 |      |      |     |              |      |     |     |     |      |     |    |        |   | 56  |

|    | Multiply .                  |      |      |     |              |      | •   | •   |     |      |     |    |        |   | 57  |

|    | Store                       | Ċ    |      |     |              | •    |     |     |     |      |     | Ċ  |        |   | 58  |

|    | Theory of Operation         |      |      |     |              |      |     | ÷   |     | •    |     |    | •      |   | 59  |

| 24 | Add-Subtract .              | •    |      |     |              |      |     |     | 1   |      |     |    |        |   | 61  |

|    | Compare                     | •    |      |     |              |      | •   |     |     |      |     |    |        |   | 65  |

|    | Divide                      | *    | •    | •   | •            | 1    | 2   |     |     |      |     |    |        |   | 68  |

|    |                             | •    | •    | •   | 3 <b>•</b> 0 | •    |     |     |     |      |     |    |        |   | 71  |

|    | Halve                       | •    | •    | •   | <b>.</b> •.) | •    | ٠   | •   | •   | •    |     | ٠  |        | • | 11  |

|    |                             |      |      |     |              |      |     |     |     |      |     |    |        |   | 72  |

| 2  | Load                        | •    | •    |     | *            |      |     | •   |     |      |     | •  | •      | • | 72  |

| 1  | Load · · ·<br>Load Type · · | •    | •    | •   |              |      |     |     |     | •    |     | •  | •      | • | 72A |

| I  | Load                        |      |      | •   |              |      | •   |     |     | •    |     |    | •••••• |   |     |

L

1

#### Form 223-2874-1 FES \$26-7035

| Introduction       78         Concepts of VFL       78         Instruction Format       78         Data Format       79         VFL Instructions       82         VFL Data Flow       82         AND-OR-Exclusive OR-Mask (AOE)       85         Digit Buffer       85         Digit Counter       85         S and T Pointers       85         Y and Z Counters       86         Multiplier Bus       86         VFL Execution and Control       88         VFL Control       90         Theory of Operation       96         VFL Instruction Execution       96         Set-Up Sequence Decimal Instructions       98         Set-Up Sequence TR and TRT       100         Interrupts Set-Up Sequence       100         Iteration Sequence Decimal Instructions       102         Prefetch Sequence       100         Iteration Sequence Decimal Instructions       102         Prefetch Sequence       107         Store-Fetch for AP, SP       111         Store-Fetch for ZAP, CP, MVO       113                                                                                                                                                                                  | VARIABLE FIELD LENGTH                     |   |   | • | 78  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---|---|---|-----|

| Instruction Format78Data Format79VFL Instructions82VFL Data Flow82AND-OR-Exclusive OR-Mask (AOE)85Digit Buffer85Digit Counter85S and T Pointers85Y and Z Counters86Direct Data Register86VFL Execution and Control86VFL Execution86VFL Execution90Theory of Operation96VFL Instruction Execution96Set-Up Sequence Decimal Instructions98Set-Up Sequence Logical Instructions100Iteration Sequence Decimal Instructions100Iteration Sequence Logical Instructions100Iteration Sequence Logical Instructions100Iteration Sequence Logical Instructions100Iteration Sequence Decimal Instructions100Iteration Sequence Logical Instructions100Iteration Sequence Decimal Instructions <td>Introduction</td> <td></td> <td></td> <td></td> <td>78</td> | Introduction                              |   |   |   | 78  |

| Data Format79VFL Instructions82VFL Data Flow82AND-OR-Exclusive OR-Mask (AOE)85Digit Buffer85Digit Counter85S and T Pointers85Y and Z Counters86Direct Data Register86VFL Execution and Control88VFL Control90Theory of Operation96VFL Instruction Execution96Set-Up Sequence Decimal Instructions98Set-Up Sequence Logical Instructions100Interrupts Set-Up Sequence100Iteration Sequence Decimal Instructions102Prefetch Sequence107Store-Fetch Sequence111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Concepts of VFL                           |   |   |   | 78  |

| VFL Instructions82VFL Data Flow82AND-OR-Exclusive OR-Mask (AOE)85Digit Buffer85Digit Counter85S and T Pointers85Y and Z Counters86Direct Data Register86VFL Execution and Control86VFL Execution90Theory of Operation96Set-Up Sequence Decimal Instructions98Set-Up Sequence Logical Instructions98Set-Up Sequence Logical Instructions100Interrupts Set-Up Sequence100Iteration Sequence Decimal Instructions102Prefetch Sequence107Store-Fetch Sequence111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Instruction Format                        |   |   |   | 78  |

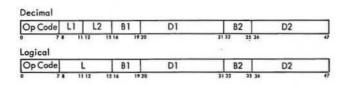

| VFL Data Flow82AND-OR-Exclusive OR-Mask (AOE)85Digit Buffer85Digit Counter85S and T Pointers85Y and Z Counters86Direct Data Register86Multiplier Bus86VFL Execution and Control88VFL Control90Theory of Operation96Set-Up Sequence Decimal Instructions98Set-Up Sequence Logical Instructions98Set-Up Sequence Logical Instructions100Interrupts Set-Up Sequence100Iteration Sequence Logical Instructions102Prefetch Sequence107Store-Fetch Sequence Decimal111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Data Format                               |   |   | • | 79  |

| AND-OR-Exclusive OR-Mask (AOE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VFL Instructions                          |   |   |   | 82  |

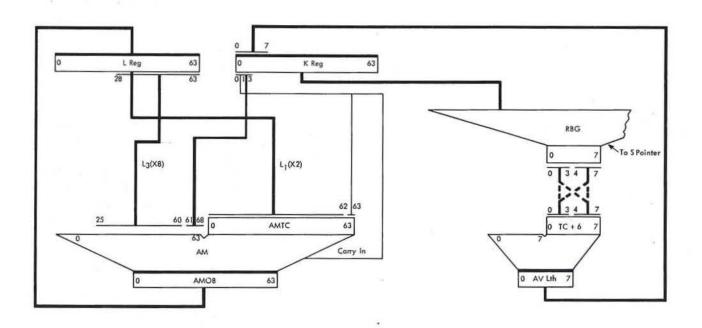

| Digit Buffer85Digit Counter85S and T Pointers85Y and Z Counters86Direct Data Register86Direct Data Register86Multiplier Bus86VFL Execution and Control86VFL Execution90Theory of Operation90VFL Instruction Execution96Set-Up Sequence Decimal Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequence Logical Instructions102Prefetch Sequence107Store-Fetch Sequence Decimal111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VFL Data Flow                             |   |   |   | 82  |

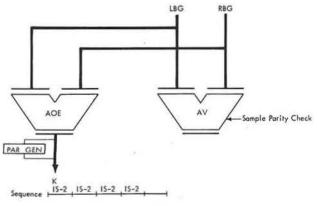

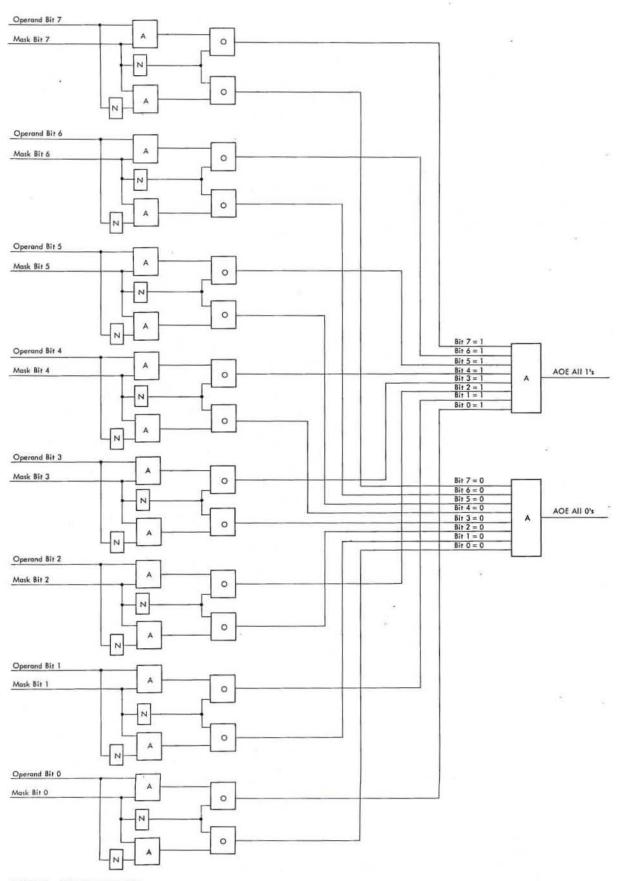

| Digit Counter85S and T Pointers85S and T Pointers86V and Z Counters86Direct Data Register86Multiplier Bus86VFL Execution and Control86VFL Execution86VFL Execution90Theory of Operation90Theory of Operation96Set-Up Sequence Decimal Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequence Logical Instructions102Prefetch Sequence107Store-Fetch Sequence111Store-Fetch for AP, SP111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AND-OR-Exclusive OR-Mask (AOE)            |   |   |   | 85  |

| S and T Pointers       85         Y and Z Counters       86         Direct Data Register       86         Multiplier Bus       86         VFL Execution and Control       86         VFL Execution       86         VFL Execution       86         VFL Execution       86         VFL Control       88         VFL Control       90         Theory of Operation       90         Theory of Operation       96         Set-Up Sequence Decimal Instructions       96         Set-Up Sequence Logical Instructions       98         Set-Up Sequence TR and TRT       100         Interrupts Set-Up Sequence       100         Iteration Sequences Decimal Instructions       102         Prefetch Sequence       107         Store-Fetch Sequence       111                                                                                                                                                                                                                                                                                                                                                                                                                              | Digit Buffer                              |   |   |   | 85  |

| Y and Z Counters86Direct Data Register86Multiplier Bus86VFL Execution and Control86VFL Execution88VFL Control90Theory of Operation90Theory of Operation96VFL Instruction Execution96Set-Up Sequence Decimal Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequence Logical Instructions102Prefetch Sequence107Store-Fetch Sequence111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digit Counter                             |   |   |   | 85  |

| Direct Data Register86Multiplier Bus86VFL Execution and Control86VFL Execution88VFL Control88VFL Control90Theory of Operation96VFL Instruction Execution96Set-Up Sequence Decimal Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequence Logical Instructions100Iteration Sequence Decimal Instructions100Store-Fetch Sequence107Store-Fetch for AP, SP111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S and T Pointers                          |   |   |   | 85  |

| Multiplier Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Y and Z Counters                          | 4 |   |   | 86  |

| VFL Execution and Control       86         VFL Execution       88         VFL Control       90         Theory of Operation       96         VFL Instruction Execution       96         Set-Up Sequence Decimal Instructions       96         Set-Up Sequence Logical Instructions       98         Set-Up Sequence TR and TRT       100         Interrupts Set-Up Sequence       100         Iteration Sequence Logical Instructions       100         Iteration Sequence Logical Instructions       102         Prefetch Sequence       107         Store-Fetch Sequence Decimal       110         Store-Fetch for AP, SP       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Direct Data Register                      |   |   |   | 86  |

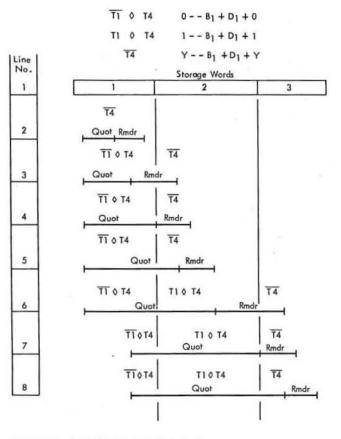

| VFL Execution88VFL Control90Theory of Operation96VFL Instruction Execution96Set-Up Sequence Decimal Instructions96Set-Up Sequence Logical Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequence Logical Instructions100Iteration Sequence Logical Instructions100Prefetch Sequence102Prefetch Sequence107Store-Fetch Sequence Decimal110Store-Fetch for AP, SP111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Multiplier Bus                            |   |   |   | 86  |

| VFL Control       90         Theory of Operation       96         VFL Instruction Execution       96         Set-Up Sequence Decimal Instructions       96         Set-Up Sequence Logical Instructions       98         Set-Up Sequence TR and TRT       100         Interrupts Set-Up Sequence       100         Iteration Sequences Decimal Instructions       100         Iteration Sequence Logical Instructions       102         Prefetch Sequence       107         Store-Fetch Sequence Decimal       110         Store-Fetch for AP, SP       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VFL Execution and Control                 |   | • |   | 86  |

| Theory of Operation96VFL Instruction Execution96Set-Up Sequence Decimal Instructions96Set-Up Sequence Logical Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequences Decimal Instructions100Iteration Sequence Logical Instructions100Iteration Sequence Logical Instructions100Iteration Sequence Logical Instructions102Prefetch Sequence107Store-Fetch Sequence Decimal110Store-Fetch for AP, SP111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VFL Execution                             |   | • | • | 88  |

| VFL Instruction Execution       96         Set-Up Sequence Decimal Instructions       96         Set-Up Sequence Logical Instructions       98         Set-Up Sequence TR and TRT       100         Interrupts Set-Up Sequence       100         Iteration Sequences Decimal Instructions       100         Iteration Sequence Logical Instructions       100         Prefetch Sequence       102         Prefetch Sequence       107         Store-Fetch Sequence Decimal       110         Store-Fetch for AP, SP       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VFL Control                               |   | • |   | 90  |

| Set-Up Sequence Decimal Instructions96Set-Up Sequence Logical Instructions98Set-Up Sequence TR and TRT100Interrupts Set-Up Sequence100Iteration Sequences Decimal Instructions100Iteration Sequence102Prefetch Sequence107Store-Fetch Sequence110Store-Fetch for AP, SP111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Theory of Operation                       |   |   | ٠ | 96  |

| Set-Up Sequence Logical Instructions       98         Set-Up Sequence TR and TRT       100         Interrupts Set-Up Sequence       100         Iteration Sequences Decimal Instructions       100         Iteration Sequence Logical Instructions       100         Prefetch Sequence       102         Prefetch Sequence       107         Store-Fetch Sequence Decimal       110         Store-Fetch for AP, SP       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VFL Instruction Execution                 | • |   | ٠ | 96  |

| Set-Up Sequence TR and TRT       .       .       100         Interrupts Set-Up Sequence       .       .       .       100         Iteration Sequences Decimal Instructions       .       .       100         Iteration Sequence Logical Instructions       .       .       .       100         Prefetch Sequence       .       .       .       .       .       .         Store-Fetch Sequence       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td>Set-Up Sequence Decimal Instructions .</td> <td></td> <td></td> <td>•</td> <td>96</td>                                                       | Set-Up Sequence Decimal Instructions .    |   |   | • | 96  |

| Interrupts Set-Up Sequence       100         Iteration Sequences Decimal Instructions       100         Iteration Sequence Logical Instructions       102         Prefetch Sequence       107         Store-Fetch Sequence Decimal       110         Store-Fetch for AP, SP       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Set-Up Sequence Logical Instructions .    |   |   |   | 98  |

| Iteration Sequences Decimal Instructions       .       .       100         Iteration Sequence Logical Instructions       .       .       .       102         Prefetch Sequence       .       .       .       .       .       107         Store-Fetch Sequence Decimal       .       .       .       .       .       .       .       .         Store-Fetch for AP, SP       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <t< td=""><td>Set-Up Sequence TR and TRT</td><td></td><td></td><td>•</td><td>100</td></t<>                                                                | Set-Up Sequence TR and TRT                |   |   | • | 100 |

| Iteration Sequence Logical Instructions       102         Prefetch Sequence       107         Store-Fetch Sequence Decimal       110         Store-Fetch for AP, SP       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interrupts Set-Up Sequence                |   |   |   | 100 |

| Prefetch Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Iteration Sequences Decimal Instructions  |   |   | • | 100 |

| Store-Fetch Sequence Decimal110Store-Fetch for AP, SP111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Iteration Sequence Logical Instructions . |   |   |   | 102 |

| Store-Fetch for AP, SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Prefetch Sequence                         |   |   |   | 107 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Store-Fetch Sequence Decimal              |   |   |   | 110 |

| Store-Fetch for ZAP, CP, MVO 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Store-Fetch for AP, SP                    |   |   |   | 111 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Store-Fetch for ZAP, CP, MVO              |   |   |   | 113 |

| Store-Fetch for PACK and U     | JN  | PK  | ٠   |      |      | ٠ |   | • | • | 114 |

|--------------------------------|-----|-----|-----|------|------|---|---|---|---|-----|

| Store-Fetch Sequence Lo        | ogi | cal |     | •    | •    | • | ٠ |   |   | 114 |

| Store-Fetch for ED, EDMK,      | Т   | R,  | an  | d T  | RT   |   | • | • | • | 115 |

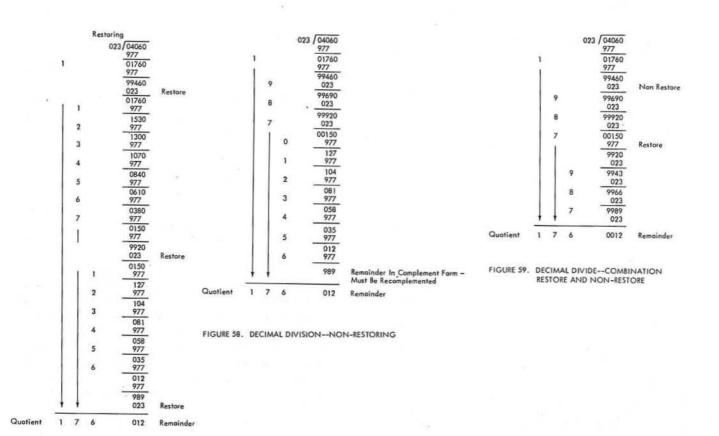

| Decimal Division               | •   |     |     |      |      |   |   |   |   | 115 |

| Method of Division             | •   |     |     | •    |      |   | • |   |   | 115 |

| Unit Functions                 |     |     |     |      |      |   | • |   | • | 116 |

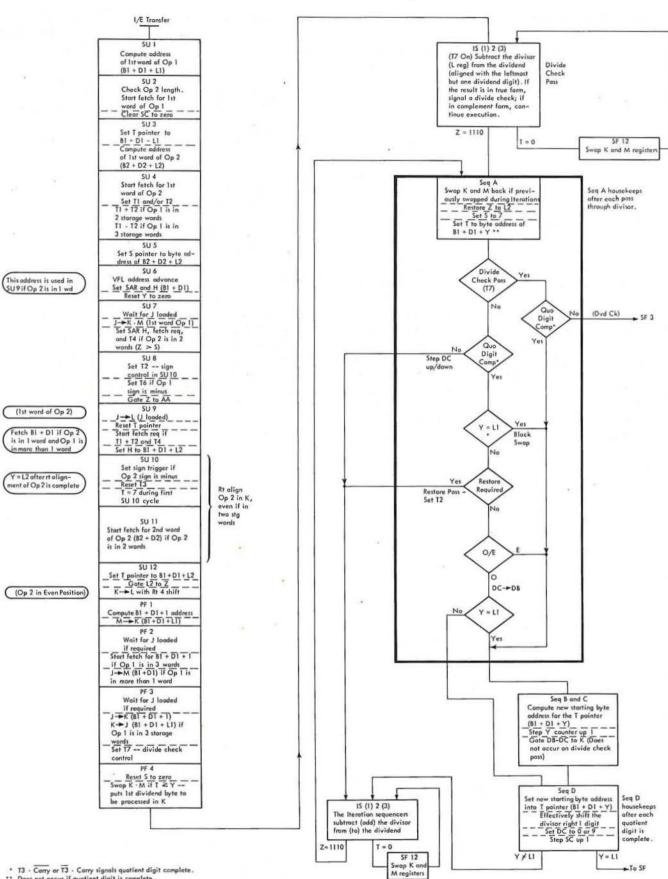

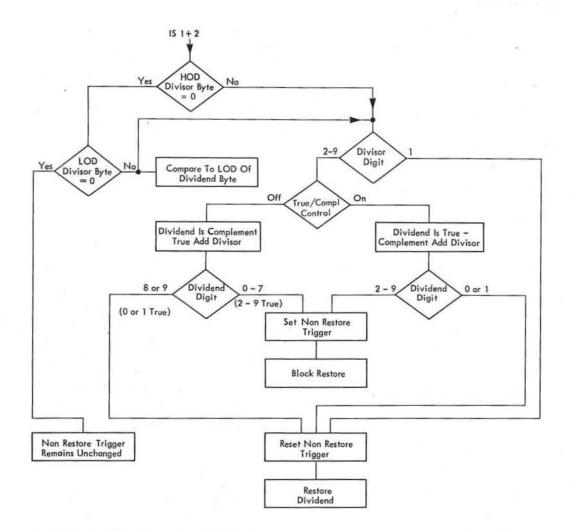

| Execution Decimal Divid        | de  |     |     |      |      |   |   | • |   | 123 |

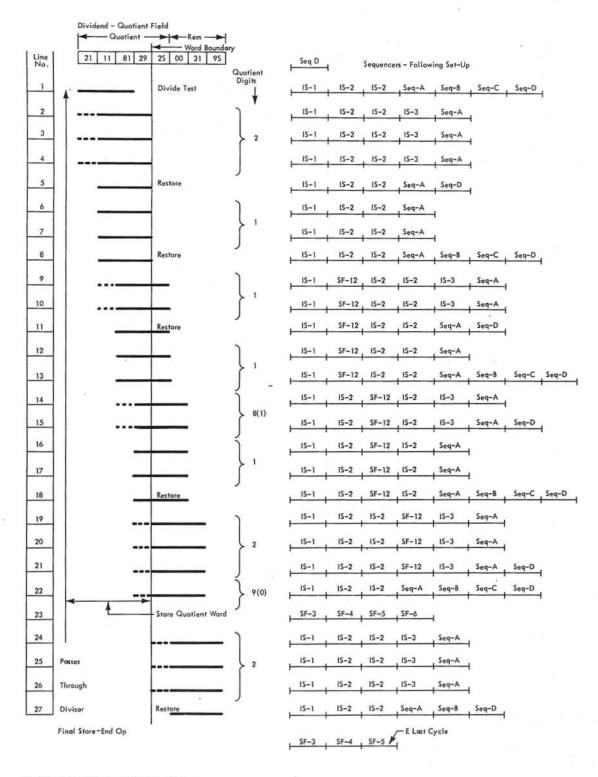

| Iteration Sequence Decin       | ma  | 1 D | ivi | de   |      |   | • |   |   | 127 |

| Store-Fetch Sequence De        | eci | ma  | 1 D | livi | de   |   |   |   |   | 128 |

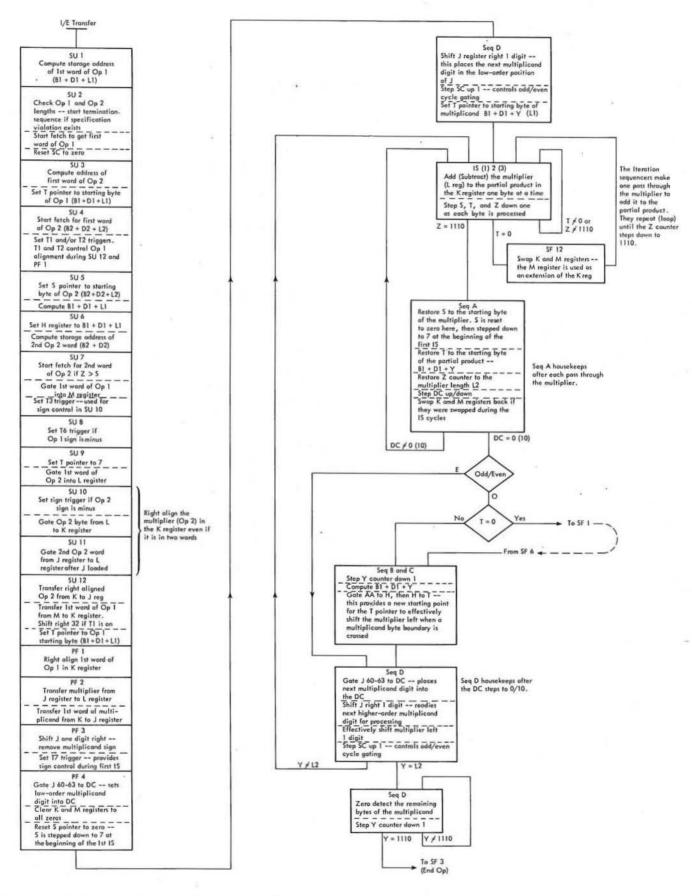

| Decimal Multiply               |     |     |     |      |      |   |   |   |   | 130 |

| Method of Multiplication       | •   |     |     | ÷    |      | • | • |   |   | 130 |

| Unit Functions                 |     |     |     |      |      |   |   |   |   | 131 |

| Set-Up Sequence                |     |     |     | ŝ    |      |   |   |   |   | 134 |

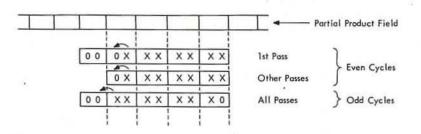

| Iteration Sequence             |     |     |     | ÷    |      |   |   |   |   | 138 |

| Store-Fetch Sequence De        | eci | ma  | 1 N | fult | iply | , |   |   |   | 142 |

| Fixed Sequence VFL Instruction | 15  |     |     |      |      |   |   |   |   | 142 |

| Insert Character (IC) .        |     |     |     |      | •    |   |   |   |   | 142 |

| Store Character (STC) .        |     |     |     |      |      |   |   |   |   | 143 |

| AND, OR, and Exclusive O       | R   |     |     |      |      |   |   |   |   | 143 |

| Compare Logical (CLI)          |     |     |     |      |      |   |   |   |   | 144 |

| Move (MVI)                     |     |     |     |      |      |   |   |   |   | 145 |

| Set System Mask (SSM)          |     |     |     |      |      |   |   |   |   | 145 |

| Test Under Mask (TM)           |     |     |     |      |      |   |   |   |   | 146 |

| Test and Set (TS)              | •   |     |     |      |      |   |   |   |   | 147 |

| Convert Instructions           |     | •   |     |      |      |   |   |   |   | 147 |

| Convert to Decimal (CVD)       |     |     |     |      |      |   |   |   |   | 147 |

| Convert to Binary (CVB)        |     |     |     |      |      |   |   |   |   | 152 |

| Direct Control (WRD and RDD    | )   |     |     |      |      |   |   |   |   | 155 |

| lex                            |     |     |     |      |      |   |   |   | ÷ | 156 |

#### ILLUSTRATIONS

|      | Figure      | Title                                        | Page | Figure   | Title                                        | Page  |

|------|-------------|----------------------------------------------|------|----------|----------------------------------------------|-------|

|      | Fixed Point | t                                            |      | 34       | SS Instruction Execution Example (Decimal    |       |

|      | 1           | I-E Transfer                                 | 10   |          | Add)                                         | . 88  |

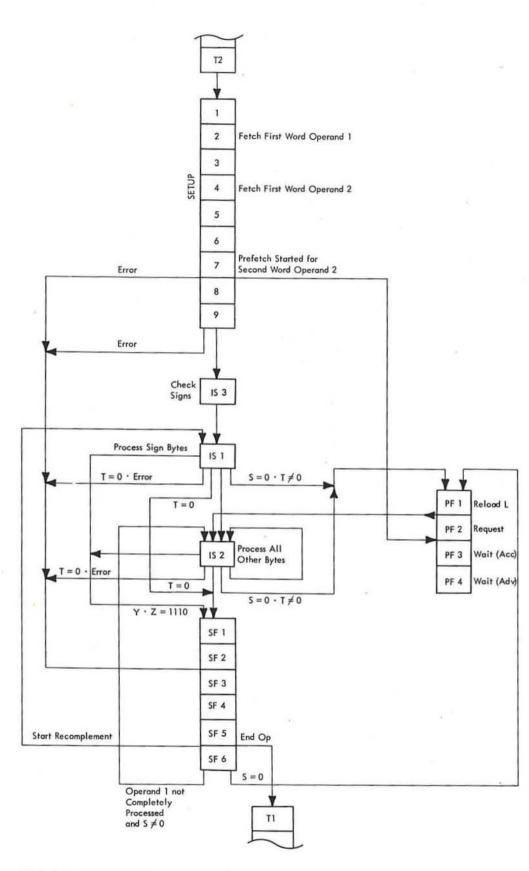

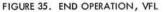

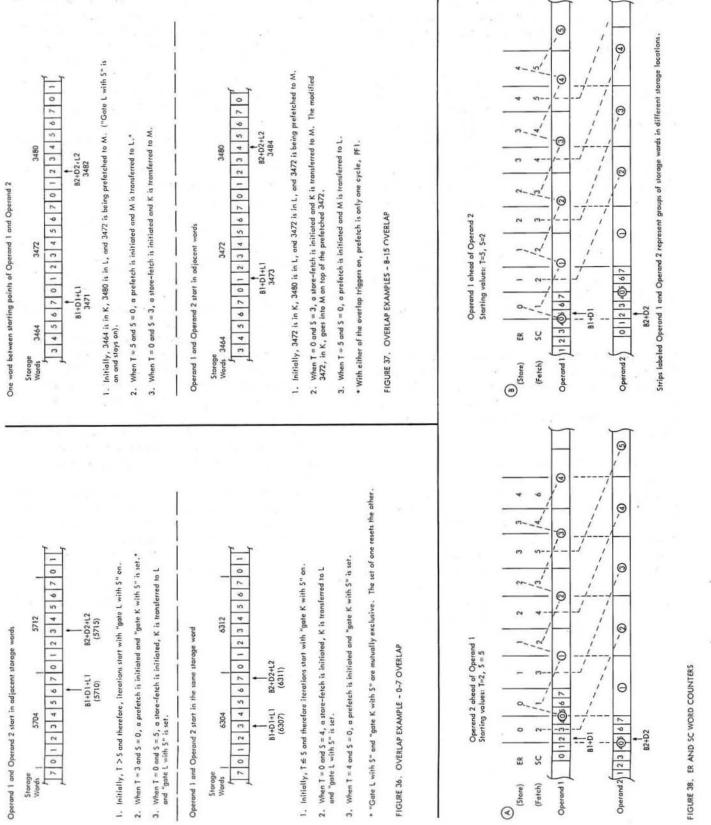

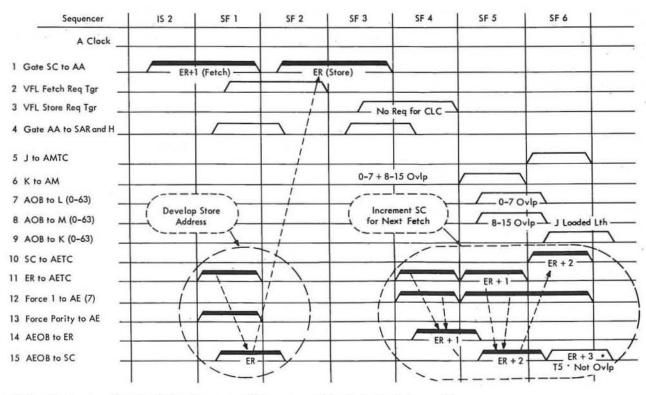

|      | 2           | Compare Examples                             | 16   | 35       | End Operation, VFL                           | . 91  |

|      |             |                                              |      | 36       | Overlap Example 0-7 Overlap                  | . 94  |

|      | Branch      |                                              |      | 37       | Overlap Examples 8-15 Overlap                | . 94  |

|      | 3           | Branch Instruction Differences               | 46   | 38       | ER and SC as Word Counters                   | . 94  |

|      | 4           | Branch Instructions, Major Control and Flow, |      | 39       | ER and SC Control During Prefetch Log        |       |

|      | · ·         | Units and Sequences                          | 46   |          | Instructions (not TR or TRT)                 | . 95  |

|      | 5           | Branch Unit                                  | 48   | 40       | ER and SC Control During Store-Fetch         |       |

|      |             |                                              |      |          | Logical Instructions (not TR or TRT)         | . 95  |

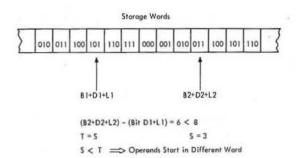

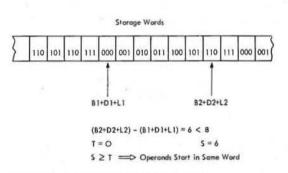

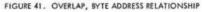

|      | Floating Po | oint                                         |      | 41       | Overlap, Byte Address Relationship           | . 98  |

|      | 6           | Hexadecimal, Decimal, and Binary Notation .  | 49   | 42       | Unpack Overlapping Fields                    |       |

|      | 7           | Hexadecimal Addition-Subtraction and         |      | 43       | Decimal Add or Subtract                      |       |

|      |             | Multiplication-Division Charts               | 50   | 44       | Basic Data Flow CP                           |       |

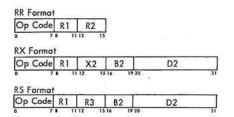

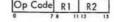

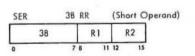

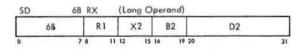

|      | 8           | RR Format                                    | 51   | 45       | Basic Data Flow MVO                          |       |

|      | 9           | RX Format                                    | 51   | 46       | Basic Data Flow PACK                         | . 103 |

|      | 10          | Double Word Format in Main Storage           | 51   | 47       | Basic Data Flow UNPACK                       |       |

|      | 11          | Single Word Format in Main Storage           | 51   | 48       |                                              |       |

|      | 12          | Double Word Format in FLP Register           | . 51 | 49       | Basic Data Flow NC, OC, XC                   |       |

|      | 13          | Single Word Format in FLP Register           | 51   | 50       | Basic Data Flow CLC                          |       |

|      | 14          | Floating-Point Exponent Values               | . 52 | 51<br>52 | Basic Data Flow MVC Basic Data Flow MCN, MVZ |       |

|      | 15          | Condition Code Setting                       | . 54 | 52       | First Prefetch                               |       |

|      | 16          | Floating-Point Arithmetic Codes              | . 55 | 54       | First Prefetch - Accept Delayed              |       |

|      | 17          | Divisor Multiple Selection True Dividend     | . 57 | 55       | Prefetch/Store-Fetch Interaction             |       |

|      | 18          | Divisor Multiple Selection Complement        |      | 56       |                                              |       |

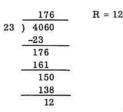

|      |             | Dividend                                     | . 57 | 57       | Decimal Division Restoring                   | . 117 |

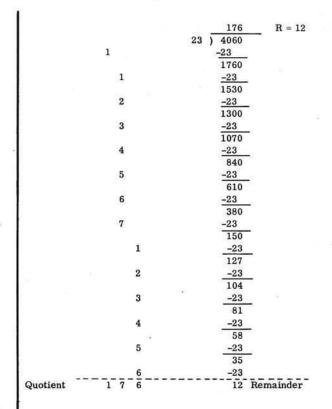

|      | 19          | Quotient Selection Decoding                  | . 57 | 58       | Decimal Division Non-restoring               |       |

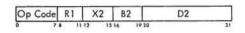

|      | 20          | Simple Floating-Point Multiply Problem       |      | 59       | Decimal Divide Combination Restore and       |       |

| ħi - |             | (Fraction)                                   |      |          | Non-Restore                                  | . 117 |

|      | 21          | FLP Operand Transfer to Working Registers .  |      | 60       | Addressing DP Store-Fetch                    |       |

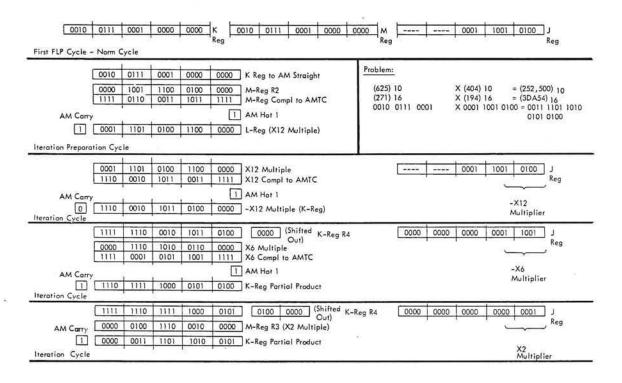

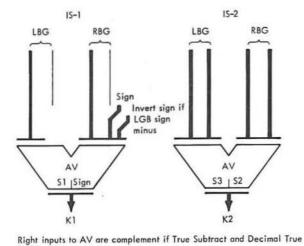

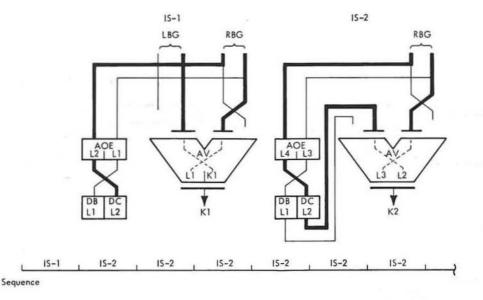

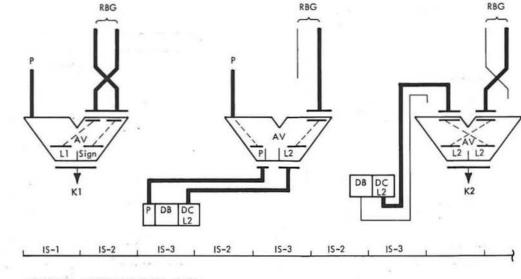

|      | 22          | Add/Subtract True/Complement Addition .      |      | 61       | Divide Iterations Example                    |       |

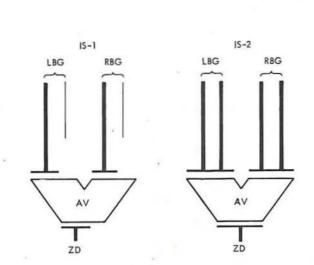

|      | 23          | Compare True/Complement Addition             | . 67 | 62       | Decimal Divide Simplified Execution          |       |

|      |             | 5 B                                          |      |          | Sequence                                     | . 121 |

|      | Variable F  | field Length                                 |      | 63       | Decimal Divide Decode Non-restore .          |       |

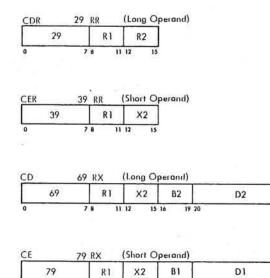

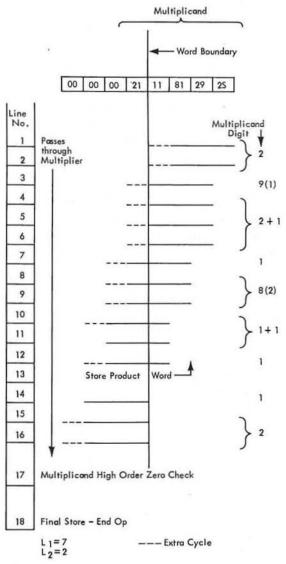

|      | 24          | SS Instruction Format                        | . 79 | 64       | Extra IS 3 Cycle Decimal Multiply            | . 133 |

| 20   | 25          | SS Instructions                              | . 80 | 65       | Extra Byte Processing Decimal Multiply .     | . 133 |

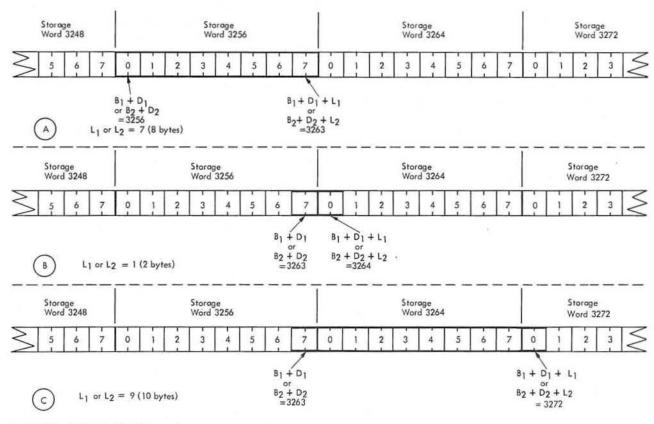

|      | 26          | Operand Length-Word Boundary Relationship    | . 80 | 66       | Multiply Iterations Example                  | . 140 |

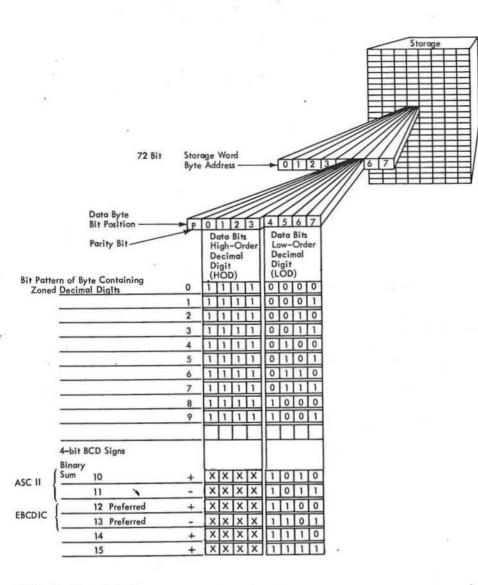

|      | 27          | Decimal Byte                                 | . 81 | 67       | Decimal Multiply, Simplified Execution       |       |

|      | 28          | BCD Coding                                   | . 83 |          | Sequence                                     | . 141 |

|      | 29          | Data Format Unpacked-Packed                  | . 83 | 68       | AOE Mask Function                            | . 148 |

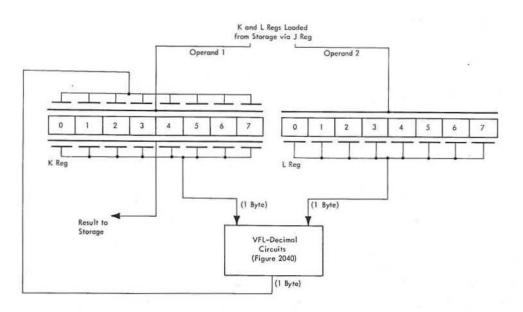

|      | 30          | General Data Flow Model 75 VFL               | . 84 | 69       | Convert Binary to Decimal                    | . 150 |

|      | 31          | TC + 6 Gate Combinations                     | . 85 | 70       | Convert Binary to BCD                        | . 151 |

|      | 32          | End Operation Conditions VFL                 | . 86 | 71       | Convert to Binary (Example)                  | . 154 |

|      | 33          | SS Execution Sequence AP/SP                  | . 87 | 72       | CVB Data Gating                              | . 154 |

|      |             |                                              |      |          |                                              |       |

|      |             |                                              |      |          |                                              |       |

|      |             |                                              |      |          |                                              |       |

|      |             |                                              |      |          |                                              |       |

|      |             |                                              |      |          |                                              |       |

|      |             |                                              |      |          |                                              |       |

|      |             | 4                                            |      |          |                                              |       |

|      |             | 8                                            |      |          |                                              |       |

|      |             |                                              |      |          | 1/68                                         |       |

-

#### ABBREVIATIONS

|                    |                                         | 10           |                                                  |

|--------------------|-----------------------------------------|--------------|--------------------------------------------------|

| AA                 | Addressing Adder                        | IC           | Instruction Counter                              |

| Adj                | Adjust                                  | ICR          | Instruction Counter Register                     |

| AD (or AV)         | Decimal Adder                           | IE           | I Unit Execution                                 |

| AE<br>AEOB         | Exponent Adder                          | IOP          | I Unit Operation Register                        |

| Contraction of the | Exponent Adder Output Bus               | IS           | Iteration Sequence                               |

| AM                 | Main Adder or Fixed Input of Main Adder |              |                                                  |

| AMOB               | Main Adder Output Bus                   | KBR          | Key Buffer Register                              |

| AMTC               | Main Adder True/Complement or True/     | 100          |                                                  |

|                    | Complement Input of Main Adder          | LBG          | Left Byte Gate                                   |

| AOB                | Adder Output Bus                        | LC           | Last Cycle                                       |

| AOE                | AND - OR - Exclusive OR                 | LCDR         | (Mnemonic) Load Complement Long FLP              |

| AP                 | (Mnemonic) Add Decimal (SS)             |              | (RR)                                             |

| ASC                | American Standard Interchange Code      | LCER         | (Mnemonic) Load Complement Short FLP             |

| ASCII              | American Standard Interchange Code      |              | (RR)                                             |

| AV (or AD)         | Decimal Adder                           | LNDR         | (Mnemonic) Load Negative Long FLP (RR)           |

|                    |                                         | LNER         | (Mnemonic) Load Negative Short FLP (RR)          |

| BALR               | (Mnemonic) Branch and Link (BR)         | LOD          | Low-Order Digit                                  |

| BCD                | Binary Coded Decimal                    | LPDR         | (Mnemonic) Load Positive Long FLP (RR)           |

| BCR                | (Mnemonic) Branch on Condition (RR)     | LPER         | (Mnemonic) Load Positive Short FLP (RR)          |

| BCTR               | (Mnemonic) Branch on Count (RR)         | LTDR         | (Mnemonic) Load and Test Long FLP (RR)           |

| BCU                | Bus Control Unit                        | LTER         | (Mnemonic) Load and Test Short FLP (RR)          |

| Bin                | Binary                                  | Lth          | Latch                                            |

| BOP                | Buffer Operation Register               | MDR          | (Mnemonic) Multiply Long FLP (RR)                |

|                    |                                         | ME           | (Mnemonic) Multiply Short FLP (RX)               |

| CLC                | (Mnemonic) Compare Logical (SS)         | MER          | (Mnemonic) Multiply Short FLP (RR)               |

| Comp               | Complement                              | MODAR        | Modified Addressable Register                    |

| CP                 | (Mnemonic) Compare Decimal (SS)         | MVC          | (Mnemonic) Move (SS)                             |

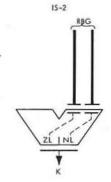

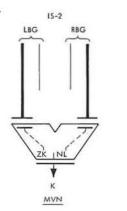

| CVD                | (Mnemonic) Convert to Decimal (RX)      | MVN          | (Mnemonic) Move Numerics (SS)                    |

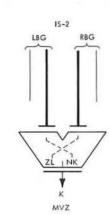

|                    |                                         | MVO          | (Mnemonic) Move With Offset (SS)                 |

| DB                 | Digit Buffer                            | MVZ          | (Mnemonic) Move Zone (SS)                        |

| DC                 | Digit Counter                           |              | , , , , , , , , , , , , , , , , , , , ,          |

| DCR                | Digit Counter Register                  | NC           | (Mnemonic) AND (SS)                              |

| Dec                | Decimal .                               |              |                                                  |

| DP                 | (Mnemonic) Divide Decimal (SS)          | oc           | (Mnemonic) OR (SS)                               |

|                    |                                         | OPF          | Operand Fetch                                    |

| ED                 | (Mnemonic) Edit (SS)                    |              |                                                  |

| EDMK               | (Mnemonic) Edit and Mark (SS)           | Par          | Parity                                           |

| ELC                | E (Unit) Last Cycle                     | PF           | Prefetch                                         |

| EOP                | E (Unit) Operation Register             | PH           | Parity Adjusted for Removal of HOD               |

| ER                 | Exponent Register                       | PK (or PACK) | (Mnemonic) Pack (SS)                             |

|                    |                                         | PL           | Parity Adjusted for Removal of LOD               |

| FLOUT              | Floating Point (Register) Out           | PSW          | Program Status Word                              |

| FLP                | Floating Point                          |              |                                                  |

|                    |                                         | RBG          | Right Byte Gate                                  |

| GPR                | General Purpose Register                | RDD          | (Mnemonic) Read Direct (SI)                      |

| GR                 | General (Purpose) Register              | RR           | (Instruction Format) Both Operands from GPR's    |

| GROUT              | General Register Out                    | RS           | (Instruction Format) One Operand from a GPR,     |

| GSR                | Gate Select Register                    |              | the other from storage                           |

| Gt                 | Gate                                    | RX           | (Instruction Format) One Operand from a GPR, the |

|                    |                                         |              | other from an indexed storage location           |

| HOD                | High-Order Digit                        |              | an a         |

| HS                 | Half-Sum                                | S            | S (Pointer or Register)                          |

| Hwd Add            | Halfword Add                            | SAR          | Storage Address Register                         |

| Hwd Log            | Halfword Logical                        | SBI          | Storage Bus In                                   |

|                    |                                         |              |                                                  |

1/68

| SBO         | Storage Bus Out                                                          | Term | Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC          | Shift Counter                                                            | TR   | (Mnemonic) Translate (SS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sel         | Select                                                                   | TRT  | (Mnemonic) Translate and Test (SS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Seq         | Sequence                                                                 |      | The second s |