## REPORT

Z50-1N

# MOBIDIC 7A

FINAL DESIGN PLAN

GAZZOCA

## MOBILE DIGITAL COMPUTER PROGRAM MOBIDIC 7A FINAL DESIGN PLAN

Signal Corps Technical Requirements SCL 1959A

Contract No. DA-36-039-SC-85117

Approved by:

N

I

I

I

I

G. M. Sokol, Manager MOBIDIC Program

26 August 1960

SYLVANIA ELECTRONIC SYSTEMS A Division of Sylvania Electric Products Inc. DATA SYSTEMS OPERATIONS 189 B Street - Needham 94, Massachusetts

### TABLE OF CONTENTS

| Section |      |        |                                                        | Page |

|---------|------|--------|--------------------------------------------------------|------|

| I       | INTI | RODUC  | FION                                                   | 1-1  |

| II      | OFF  | -LINE  | CONTROL SYSTEM                                         | 2-1  |

|         | 2.1  | Gener  | al                                                     | 2-1  |

|         | 2.2  | Purpo  | se and Use                                             | 2-1  |

|         | 2.3  | Opera  | tional Considerations                                  | 2-6  |

|         |      | 2.3.1  | Compatability with MOBIDIC In-Out Devices              | 2-6  |

|         |      | 2.3.2  | Format Control                                         | 2-7  |

|         |      | 2.3.3  | Padding                                                | 2-7  |

|         |      | 2.3.4  | Set-Up and Error Control                               | 2-8  |

|         |      | 2.3.5  | Blockette Mode                                         | 2-9  |

|         |      | 2.3.6  | On-Line and Off-Line Operation                         | 2-9  |

|         | 2.4  | Design | n Considerations                                       | 2-10 |

|         |      | 2.4.1  | System Compatibility                                   | 2-10 |

|         |      | 2.4.2  | Converter - OLCU Similarity                            | 2-10 |

|         |      | 2.4.3  | Design Approach                                        | 2-11 |

|         |      | 2.4.4  | Memory Capacity                                        | 2-11 |

|         |      | 2.4.5  | Device Switching Unit Interlocks                       | 2-12 |

|         |      | 2.4.6  | Verify Mode                                            | 2-12 |

|         | 2.5  | Design | Description                                            | 2-12 |

|         | 2.6  | System | n Design                                               | 2-13 |

|         |      | 2.6.1  | OLCU Block Diagram                                     | 2-13 |

|         |      | 2.6.2  | OLCU Control Center                                    | 2-15 |

|         |      |        | 2.6.2.1 Marginal Check Voltage System<br>Subassemblies | 2-15 |

|         |      |        | 2.6.2.2 Device and Mode Selection Section              | 2-15 |

|         |      |        | 2.6.2.3 Operating and Error Checking Section           | 2-23 |

|         |      | 2.6.3  | Memory                                                 | 2-23 |

|         |      | 2.6.4  | OLCU Registers                                         | 2-23 |

|         |      |        | 2.6.4.1 Input Buffer Register                          | 2-23 |

|         |      |        | 2.6.4.2 Memory Buffer Register                         | 2-28 |

1

1

1

I

| Section |       |         |              |                                         | Page |

|---------|-------|---------|--------------|-----------------------------------------|------|

|         |       | 2.6.4.3 | Output Buff  | er Register                             | 2-29 |

|         | 2.6.5 | Code Co | nverters     |                                         | 2-29 |

|         |       | 2.6.5.1 | Fieldata to  | Hollerith Code Converter                | 2-30 |

|         |       | 2.6.5.2 | Hollerith to | Fieldata Code Converter                 | 2-31 |

|         |       | 2.6.5.3 | Special Cha  | aracters Code                           | 2-32 |

|         | 2.6.6 | Row-Col | umn Conver   | sions                                   | 2-34 |

|         |       | 2.6.6.1 | Shifting Ope | erations                                | 2-34 |

|         |       | 2.6.6.2 | Operating S  | Sequence                                | 2-35 |

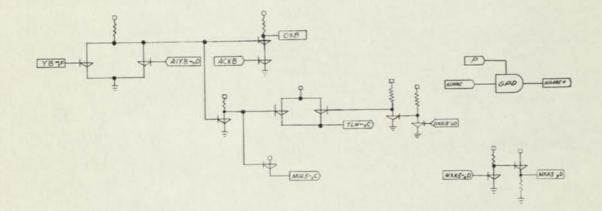

|         |       | 2.6.6.3 | Memory Ad    | ldress Counter                          | 2-44 |

|         | 2.6.7 | Control |              |                                         | 2-47 |

|         |       | 2.6.7.1 | External Co  | ontrol                                  | 2-47 |

|         |       |         | 2.6.7.1.1    | Standby                                 | 2-49 |

|         |       |         | 2.6.7.1.2    | Device Selection                        | 2-49 |

|         |       |         | 2.6.7.1.3    | Device Start                            | 2-49 |

|         |       |         | 2.6.7.1.4    | Read Operation                          | 2-49 |

|         |       |         | 2.6.7.1.5    | Write Operation                         | 2-50 |

|         |       |         | 2.6.7.1.6    | Device Stop                             | 2-50 |

|         |       |         | 2.6.7.1.7    | Read Synchronizer                       | 2-51 |

|         |       |         | 2.6.7.1.8    | Erase Operation                         | 2-53 |

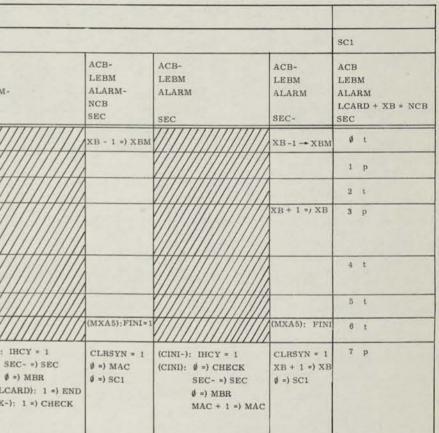

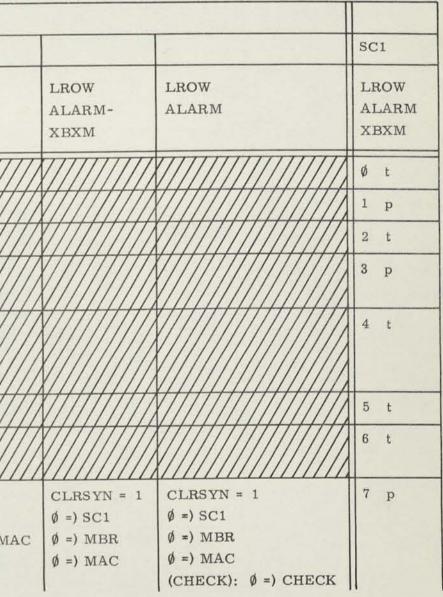

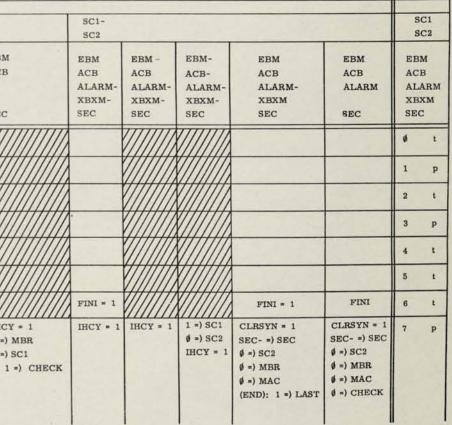

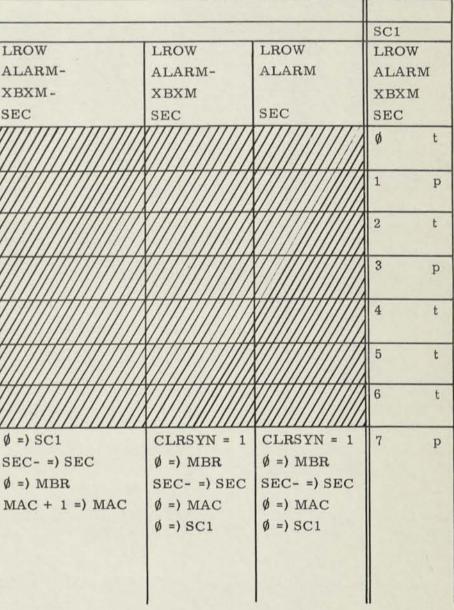

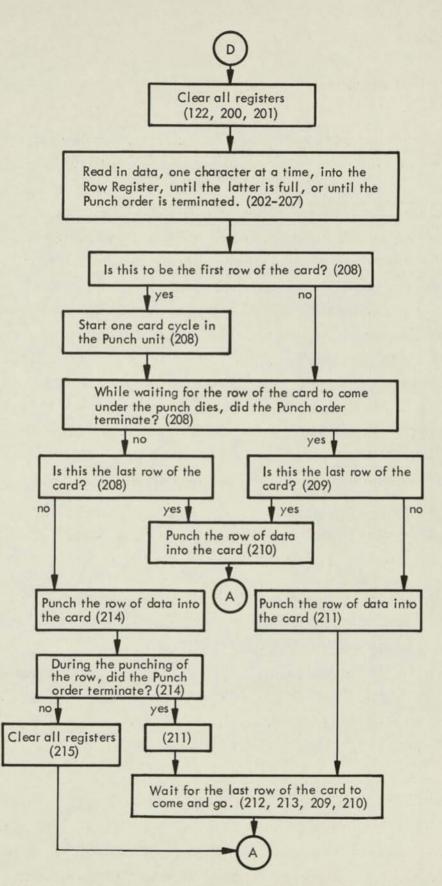

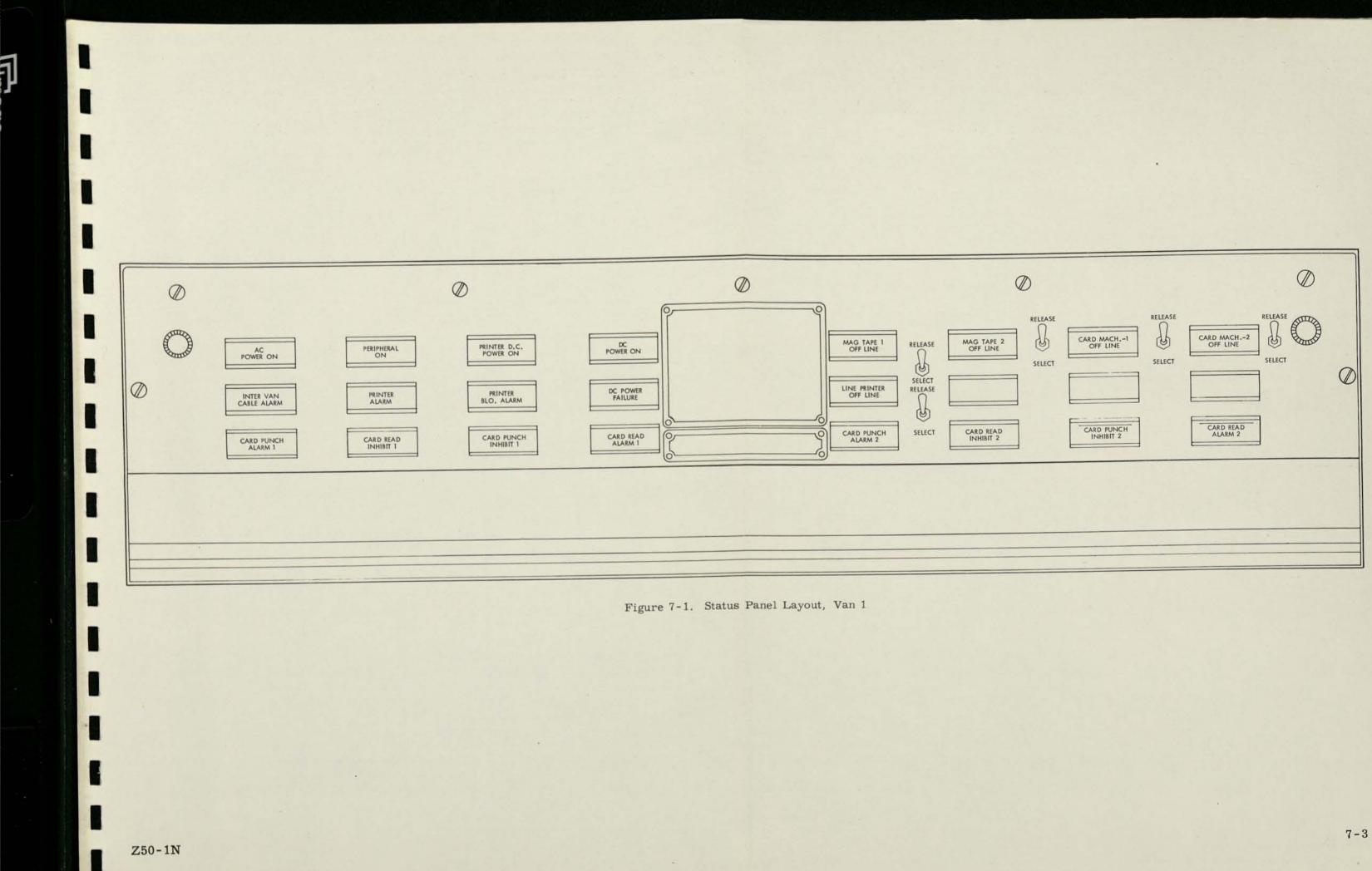

|         |       |         | 2.6.7.1.9    | External Control<br>Mechanization Lists | 2-53 |

|         |       | 2.6.7.2 | Internal Co  | ontrol                                  | 2-60 |

|         |       |         | 2.6.7.2.1    | Internal Control Equipment              | 2-60 |

|         |       |         | 2.6.7.2.2    | Internal Control<br>Mechanization       | 2-62 |

|         |       | 2.6.7.3 | Program C    | control                                 | 2-89 |

|         |       |         | 2.6.7.3.1    | Program Counter                         | 2-90 |

|         |       |         | 2.6.7.3.2    | Program Control<br>Mechanization        | 2-92 |

|         |       | 2.6.7.4 | Miscellane   | ous Mechanizations                      | 2-99 |

I

ľ

l

Section

Page

|     |        |            | 2.6.7.4.1               | Run and Single Cycle | 2-99  |

|-----|--------|------------|-------------------------|----------------------|-------|

|     |        |            | 2.6.7.4.2               | End-of-Tape Signal   | 2-100 |

|     |        |            | 2.6.7.4.3               | Device Alarms        | 2-100 |

|     | 2.6.8  | Timing P   | ulse Genera             | tor                  | 2-101 |

|     | 2.6.9  | Single Cy  | cle Control             | Flip-Flop            | 2-101 |

|     | 2.6.1  | 0 Alarm In | dications               |                      | 2-102 |

|     |        | 2.6.10.1   | Memory Pa               | arity Errors         | 2-102 |

|     |        | 2.6.10.2   | Data Error              | S                    | 2-102 |

|     |        |            | 2.6.10.2.1              | Input Data Errors    | 2-103 |

|     |        |            | 2.6.10.2.2              | Output Data Errors   | 2-104 |

|     |        | 2.6.10.3   | Device Err              | ors                  | 2-104 |

| 2.7 | Circui | it Design  |                         |                      | 2-106 |

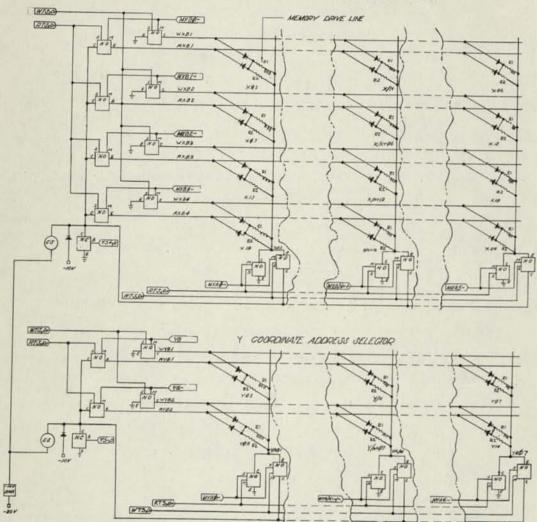

|     | 2.7.1  | Memory S   | System                  |                      | 2-106 |

|     |        | 2.7.1.1    | Direct Driv             | re System            | 2-108 |

|     |        | 2.7.1.2    | Drive Line              | Selection            | 2-110 |

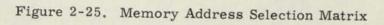

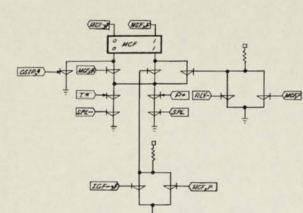

|     |        | 2.7.1.3    | Memory Ci               | rcuits               | 2-110 |

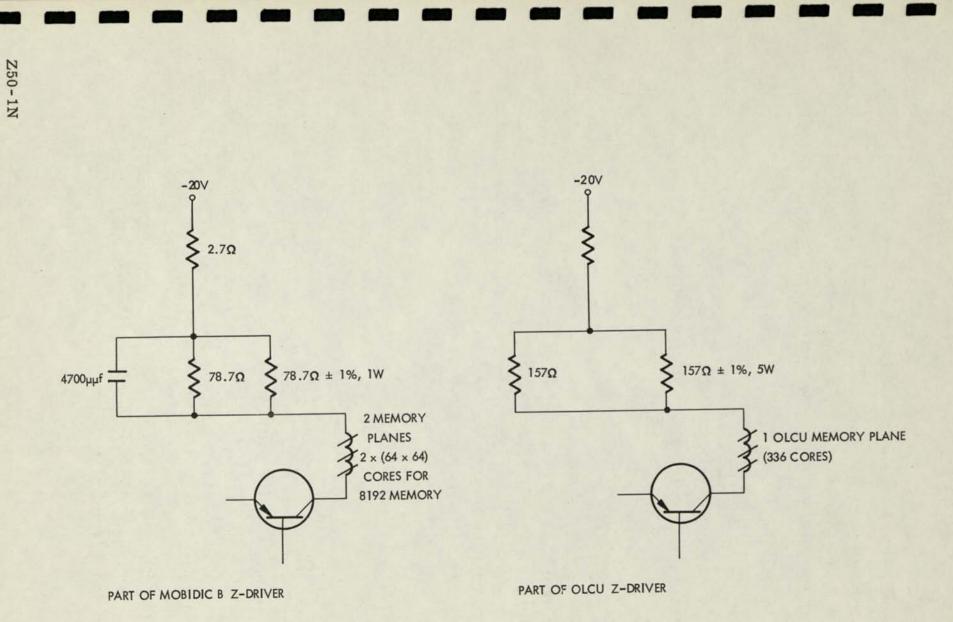

|     |        | 2.7.1.4    | Z-Drivers               |                      | 2-116 |

|     |        | 2.7.1.5    | -14 Volt Sin            | ık                   | 2-116 |

|     |        | 2.7.1.6    | Current Sou             | irces                | 2-116 |

|     |        | 2.7.1.7    | Sense Ampl<br>Reference | ifiers and Voltage   | 2-118 |

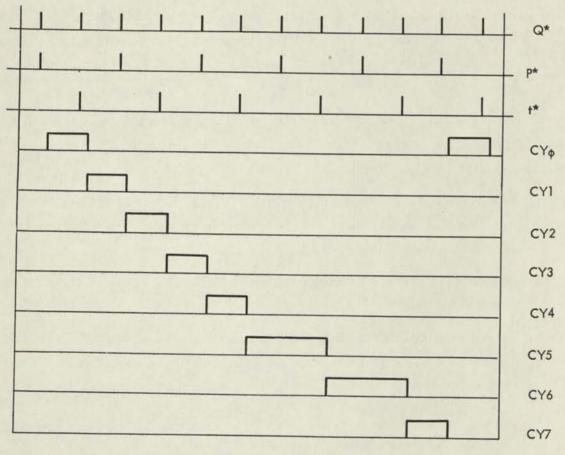

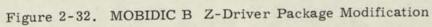

|     |        | 2.7.1.8    | System Tin              | ning                 | 2-118 |

|     |        | 2.7.1.9    | Single Puls             | e Operation          | 2-122 |

|     | 2.7.2  | Console S  | witch Interlo           | ocks                 | 2-125 |

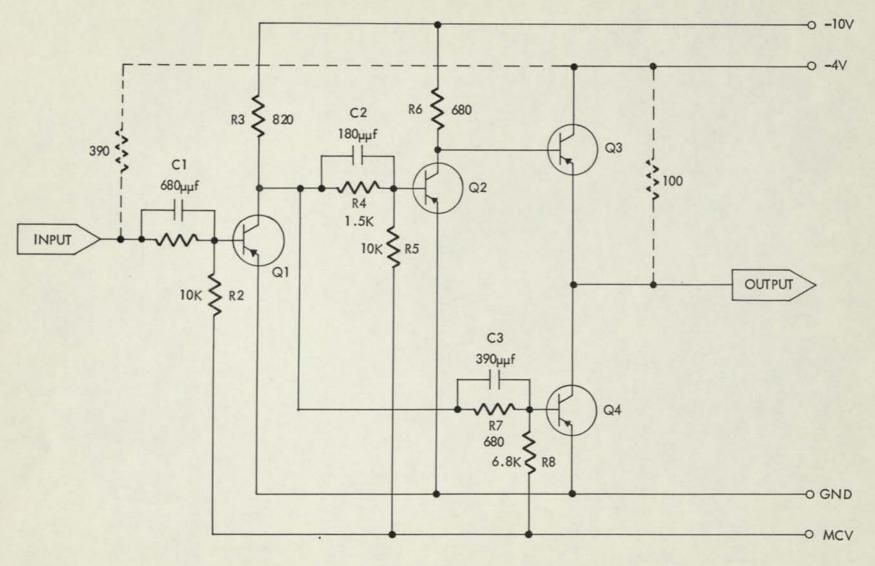

|     | 2.7.3  | Half Regis | ster Driver             |                      | 2-127 |

|     |        | 2.7.3.1    | General                 |                      | 2-127 |

|     |        | 2.7.3.2    | Theory of C             | peration             | 2-127 |

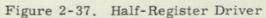

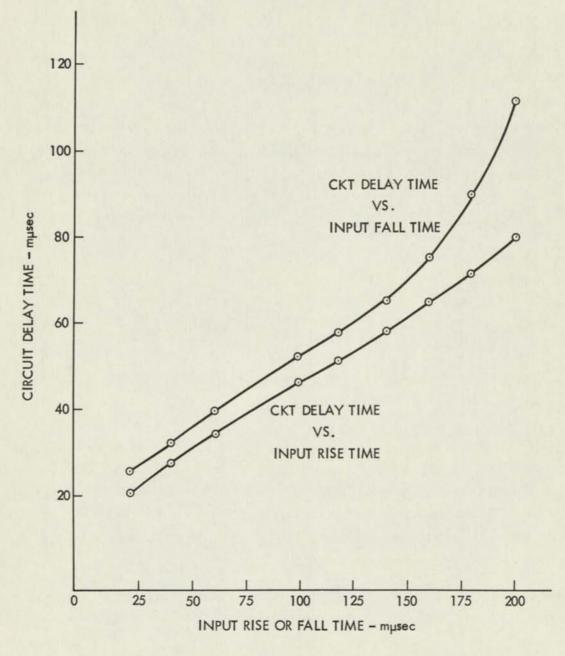

|     |        | 2.7.3.3    | Circuit Spee            | cifications          | 2-129 |

|     |        |            | 2.7.3.3.1               | Function             | 2-129 |

| Section | Se | C | ti | 0 | n |  |

|---------|----|---|----|---|---|--|

|---------|----|---|----|---|---|--|

|      |        |                     | 2.7.3.3.2    | Special Wiring Rules                | 2-129 |

|------|--------|---------------------|--------------|-------------------------------------|-------|

|      |        |                     | 2.7.3.3.3    | Operating Temperature<br>Range      | 2-129 |

|      |        |                     | 2.7.3.3.4    | Power Requirements                  | 2-129 |

|      |        |                     | 2.7.3.3.5    | Marginal Checking                   | 2-130 |

|      |        | 2.7.3.4             | Worst-Case   | e Considerations                    | 2-130 |

|      |        |                     | 2.7.3.4.1    | Cascode Output Power<br>Dissipation | 2-130 |

|      |        |                     | 2.7.3.4.2    | Output Inverter                     | 2-131 |

|      |        |                     | 2.7.3.4.3    | Emitter Follower                    | 2-137 |

|      |        |                     | 2.7.3.4.4    | Power Inverter                      | 2-139 |

|      |        |                     | 2.7.3.4.5    | Input Inverter                      | 2-141 |

|      | 2.7.4  | Off-Line            | Control Equ  | ipment Power Requirements           | 2-141 |

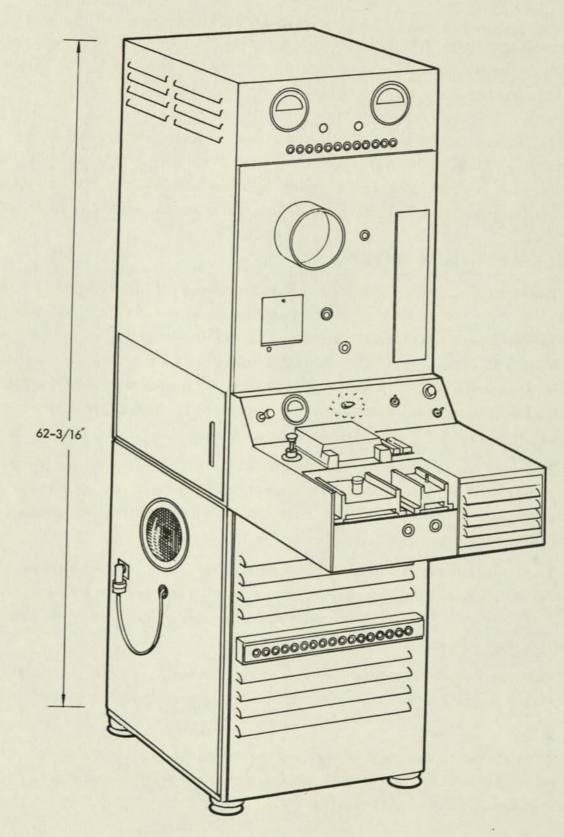

| 2.8  | Mechan | nical Desig         | gn           |                                     | 2-143 |

|      | 2.8.1  | Off-Line            | Control Unit | : (S6Ø2A)                           | 2-143 |

|      |        | 2.8.1.1             | Rack Layou   | at                                  | 2-143 |

|      |        | 2.8.1.2             | Memory A     | rray Assembly                       | 2-145 |

|      |        | 2.8.1.3             | Cooling      |                                     | 2-146 |

|      | 2.8.2  | Off-Line            | Control Unit | t (S6Ø2B)                           | 2-146 |

|      | 2.8.3  | Off-Line Unit (S72) |              | ching and Buffer                    | 2-147 |

| 2.9  | Equipn | nent Opera          | tion         |                                     | 2-148 |

|      | 2.9.1  | General             |              |                                     | 2-148 |

|      | 2.9.2  | Conversio           | on Summary   |                                     | 2-148 |

|      | 2.9.3  | Operation           | in the Bloc  | kette Mode                          | 2-153 |

|      | 2.9.4  | Error Co            | rrection Pr  | ocedures                            | 2-154 |

| 2.10 | System | Operation           | 1            |                                     | 2-157 |

|      | 2.10.1 | In-Out De           | vice Sharin  | g                                   | 2-157 |

|      | 2.10.2 | OLCU Ad             | dressing     |                                     | 2-158 |

÷.

| Section |              |         |                                                      | Page  |

|---------|--------------|---------|------------------------------------------------------|-------|

|         | 2.11         | Marg    | inal Check Voltage System                            | 2-160 |

|         |              | 2.11.   | 1 General                                            | 2-160 |

|         |              | 2.11.   | 2 Operational Control                                | 2-161 |

|         | 2.12         | OLCU    | Abbreviations                                        | 2-166 |

| III     | LINE         | PRIN    | TER AND LINE PRINTER BUFFER                          | 3-1   |

|         | 3.1          | Line 1  | Printer                                              | 3-1   |

|         | 3.2          | Line I  | Printer Buffer                                       | 3-3   |

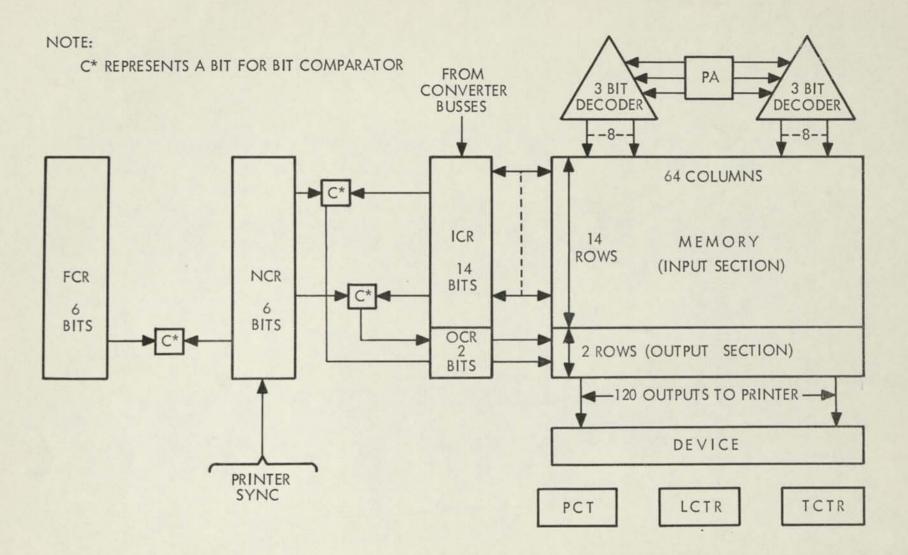

|         |              | 3.2.1   | Line-Printer Buffer Block Diagram                    | 3-5   |

|         |              |         | 3. 2. 1. 1 Memory Plane                              | 3-5   |

|         |              |         | 3. 2. 1. 2 In-Out Static Register (ICR)              | 3-5   |

|         |              |         | 3.2.1.3 Next Character Register (NCR)                | 3-7   |

|         |              |         | 3.2.1.4 Output Static Register (OCR)                 | 3-8   |

|         |              |         | 3.2.1.5 First Character Register (FCR)               | 3-8   |

|         |              |         | 3.2.1.6 Tab Counter (TCTR)                           | 3-8   |

|         |              |         | 3.2.1.7 Line Counter (LCTR)                          | 3-8   |

|         |              |         | 3.2.1.8 Main Sequence Counter (PCT)                  | 3-9   |

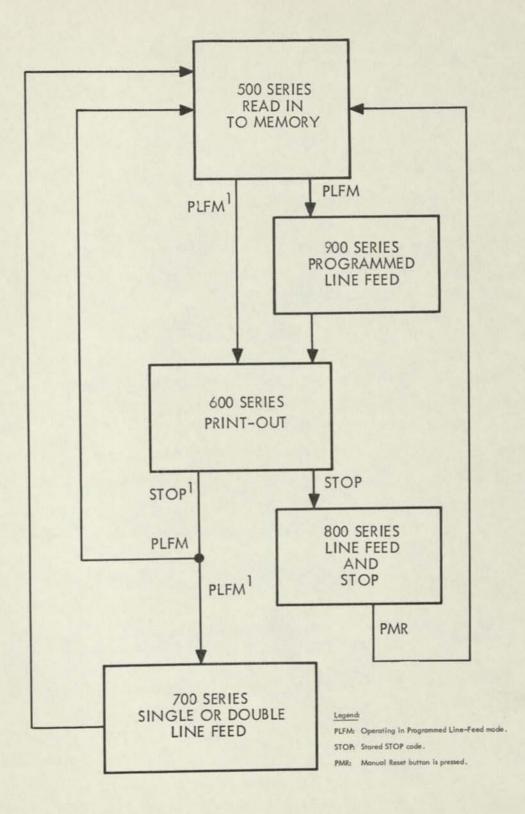

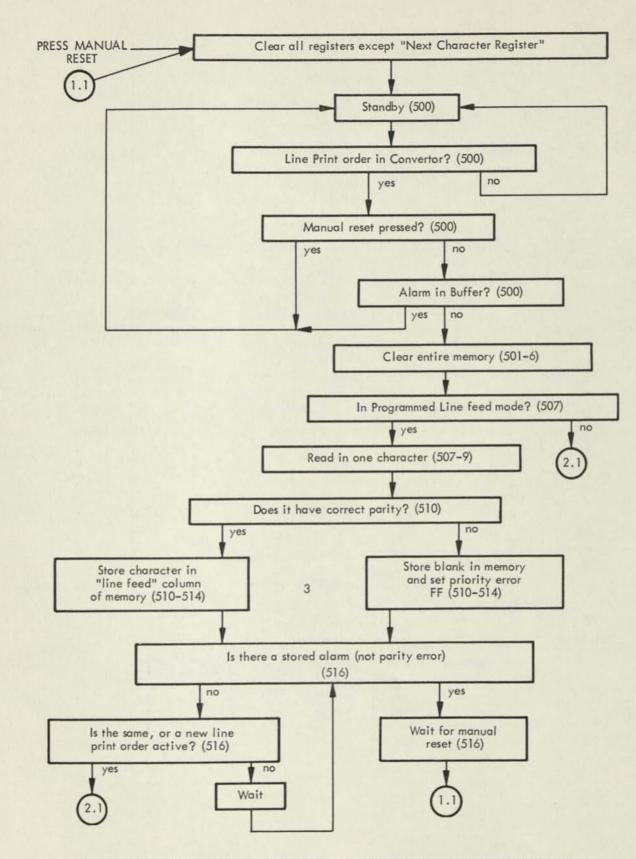

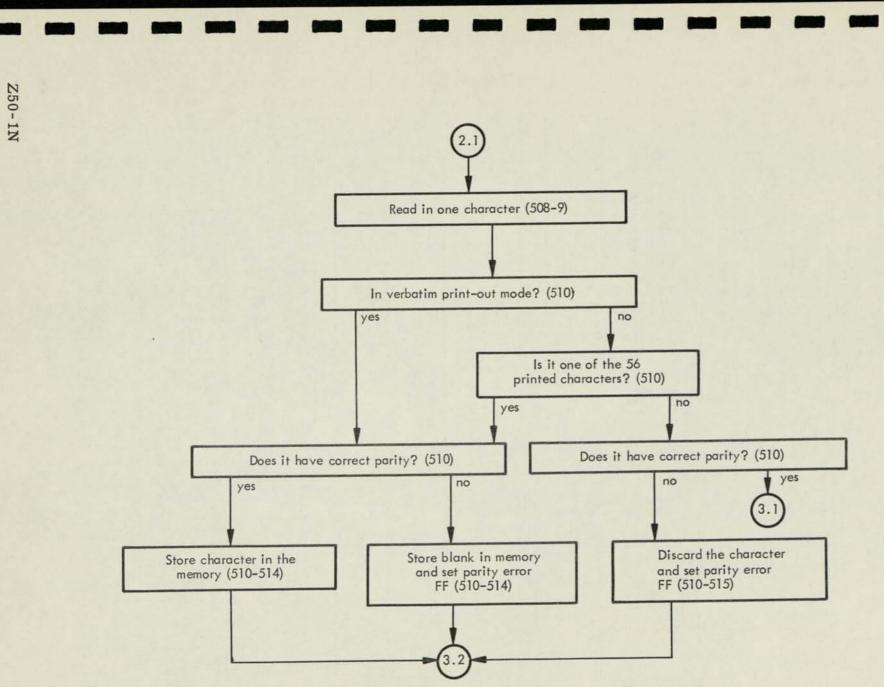

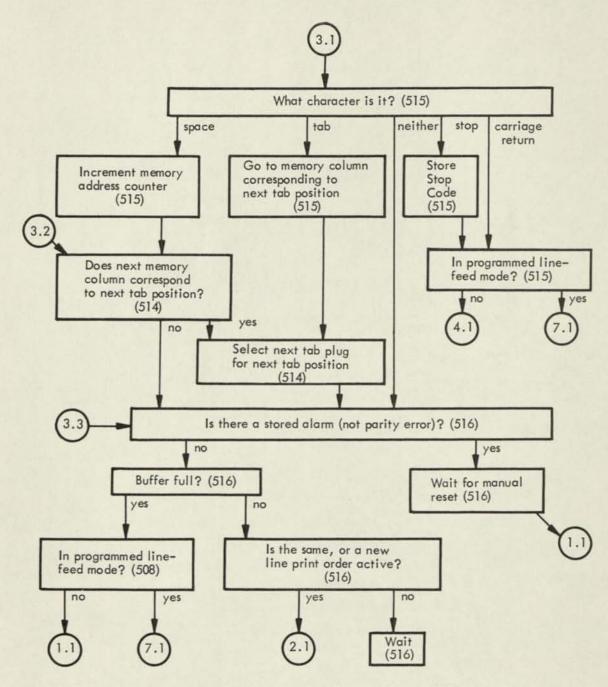

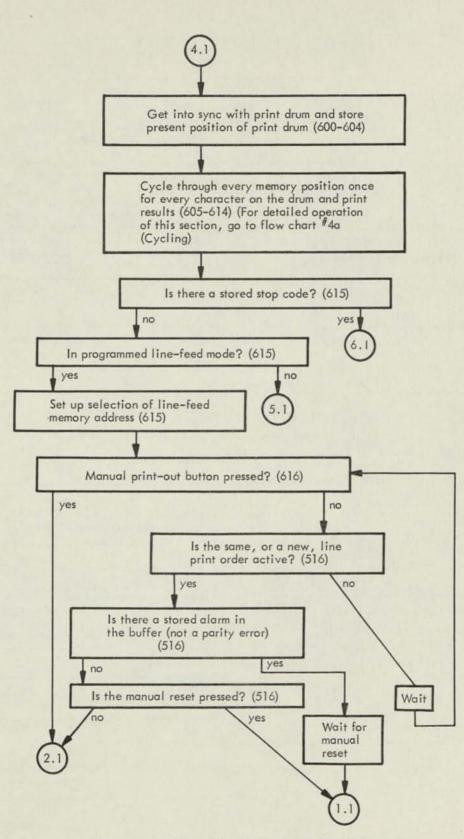

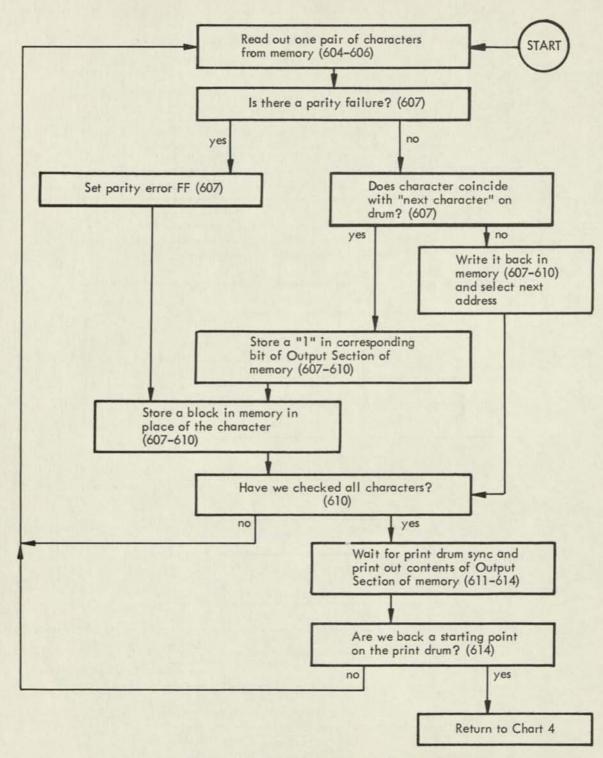

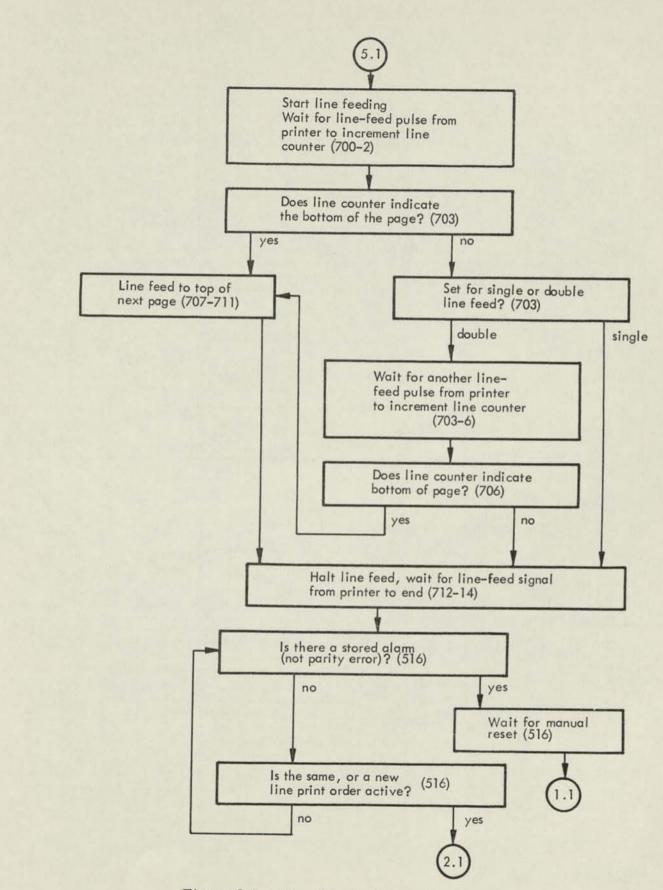

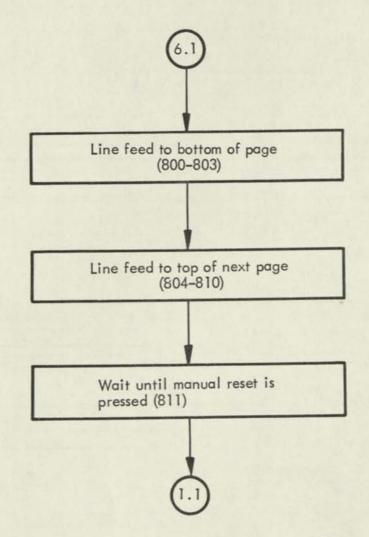

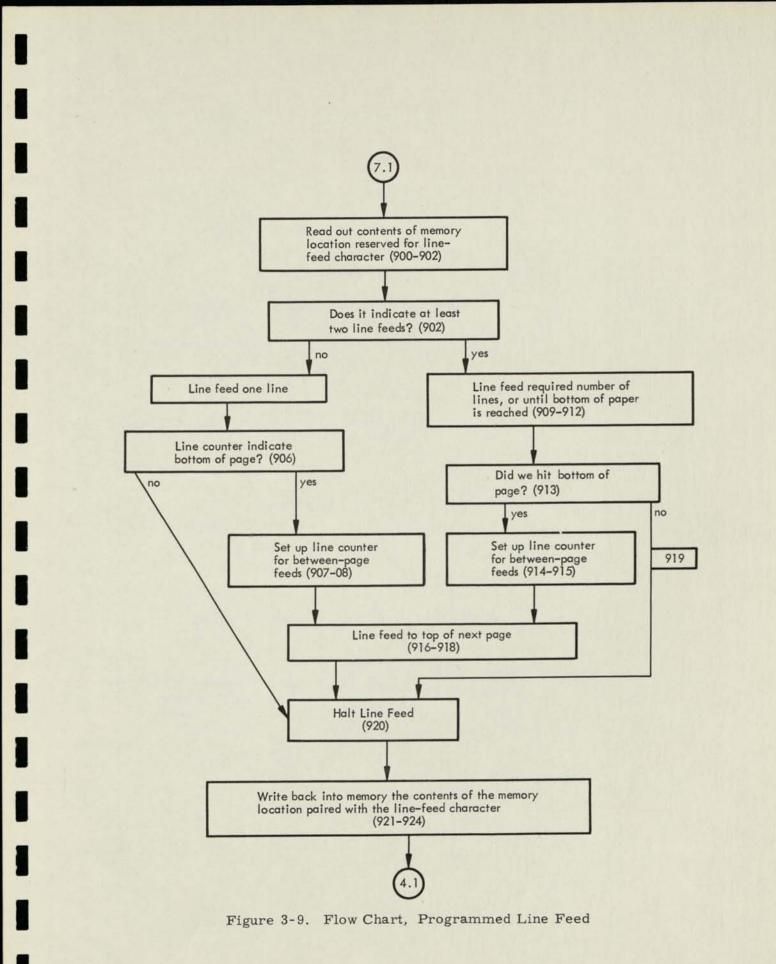

|         |              | 3.2.2   | General Flow Chart of the Line Printer Buffer        | 3-9   |

|         |              | 3.2.3   | Detailed Flow Charts of the Line Printer Buffer      | 3-11  |

| IV      | CARD<br>BUFF | READ    | ER-PUNCH AND CARD READER-PUNCH                       | 4-1   |

|         | 4.1          | Genera  |                                                      | 4-1   |

|         | 4.2          | Block ] | Diagram                                              | 4-3   |

|         |              | 4.2.1   | Row Register (R1 - R80)                              | 4-3   |

|         |              | 4.2.2   | Character Selection Counter and Decoder<br>(CSC, CS) | 4-3   |

|         |              | 4.2.3   | Parity Circuits                                      | 4-5   |

|         |              | 4.2.4   | Control Sequence Counter (CT)                        | 4-5   |

|         |              | Flow C  |                                                      | 4-5   |

|         |              | 4.3.1   | Standby Flow Chart                                   | 4-5   |

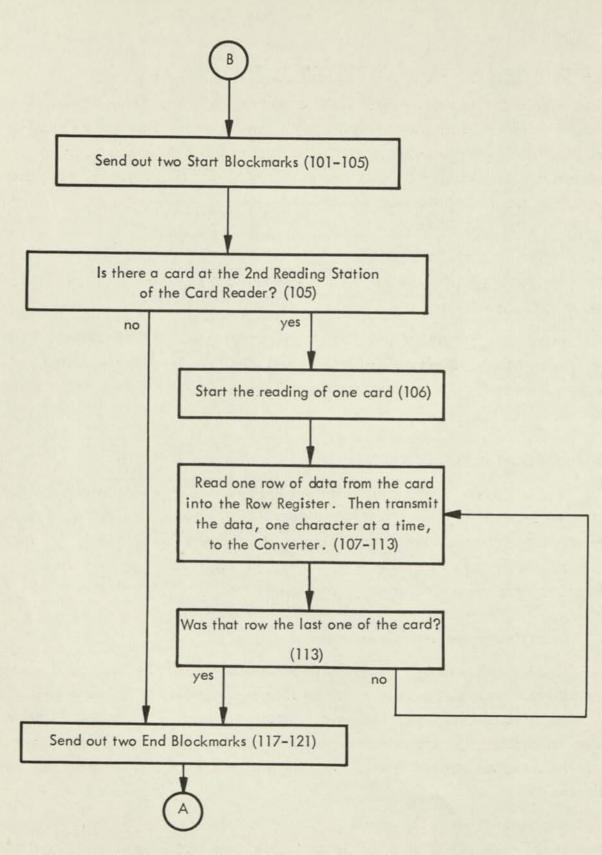

|         |              | 4.3.2   | Card Read Alphanumeric Flow Chart                    | 4-7   |

1

I

I

I

I

I

I

I

| Section | 1                                    |      |

|---------|--------------------------------------|------|

|         |                                      | Page |

|         | 4.3.3 Card Read Octal Flow Chart     | 4-7  |

|         | 4.4 Auxiliary Card Buffer            | 4-7  |

|         | 4.4.1 Read Operation (Off-Line)      | 4-7  |

|         | 4.4.2 Punch Operation (Off-Line)     | 4-10 |

|         | 4.4.3 On-Line Operation              | 4-12 |

| v       | LOGIC AND MECHANIZATION DESIGNATIONS | 5-1  |

| VI      | MECHANIZATION LISTS                  | 6-1  |

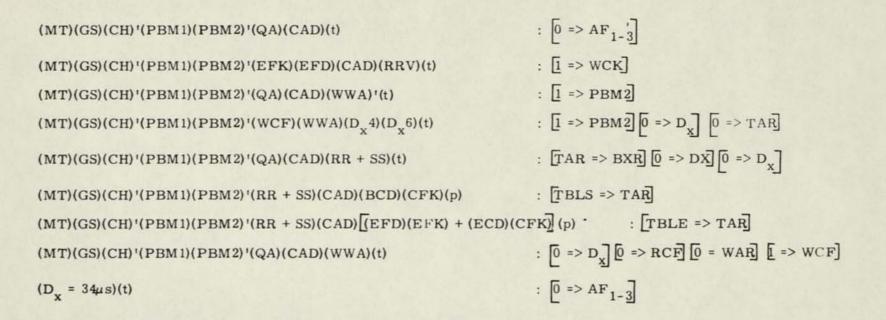

| VII     | VAN LAYOUT                           | 7-1  |

| VIII    | ELEMENT TESTER                       | 8-1  |

|         | 8.1 General                          | 8-1  |

|         | 8.2 Electrical Description           | 8-1  |

|         | 8.3 Mechanical Description           | 8-3  |

|         |                                      |      |

## LIST OF ILLUSTRATIONS

| Figure |                                                                  | Page  |

|--------|------------------------------------------------------------------|-------|

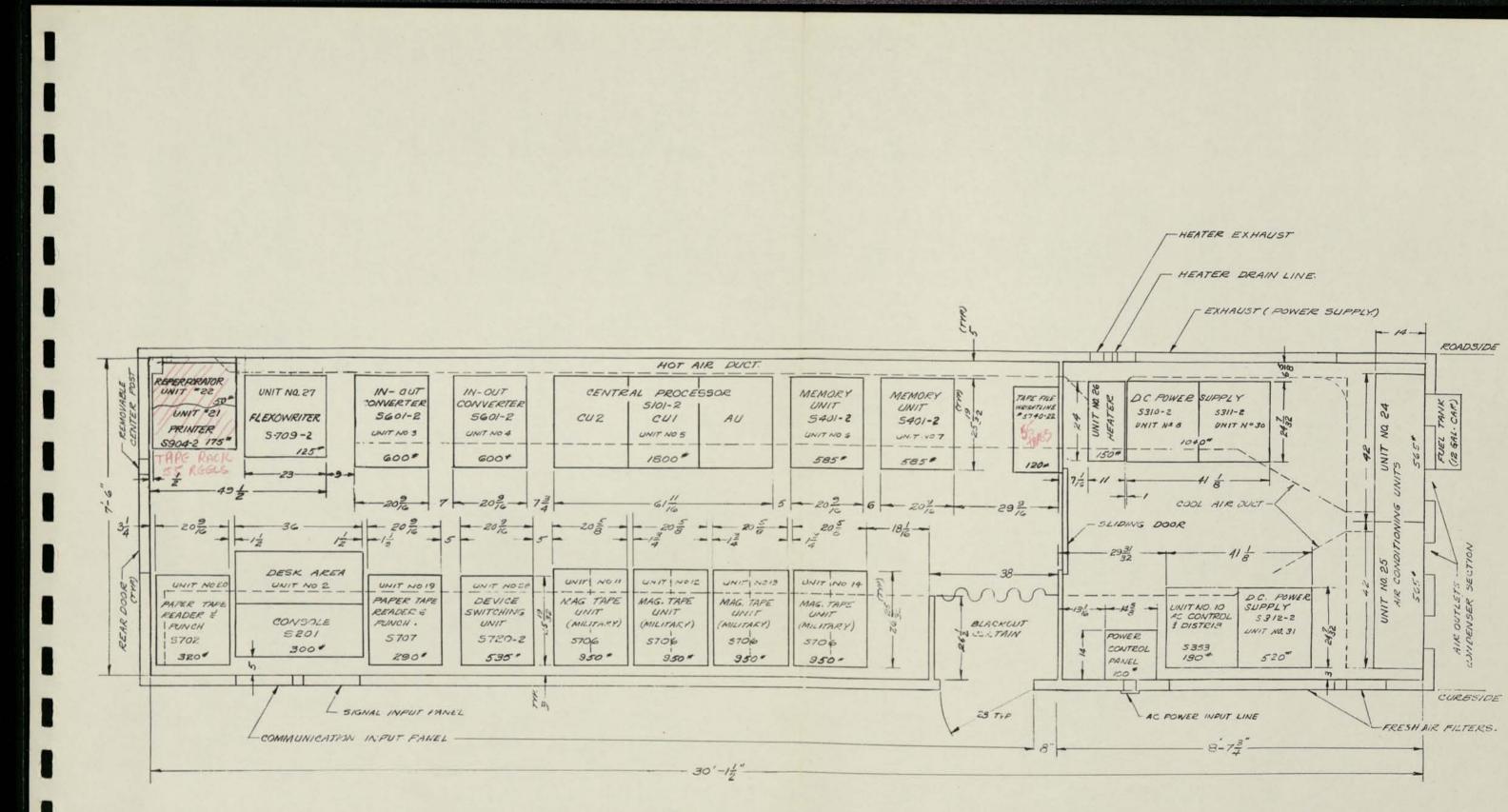

| 1-1    | MOBIDIC 7A Van 1 Layout                                          | 1-7   |

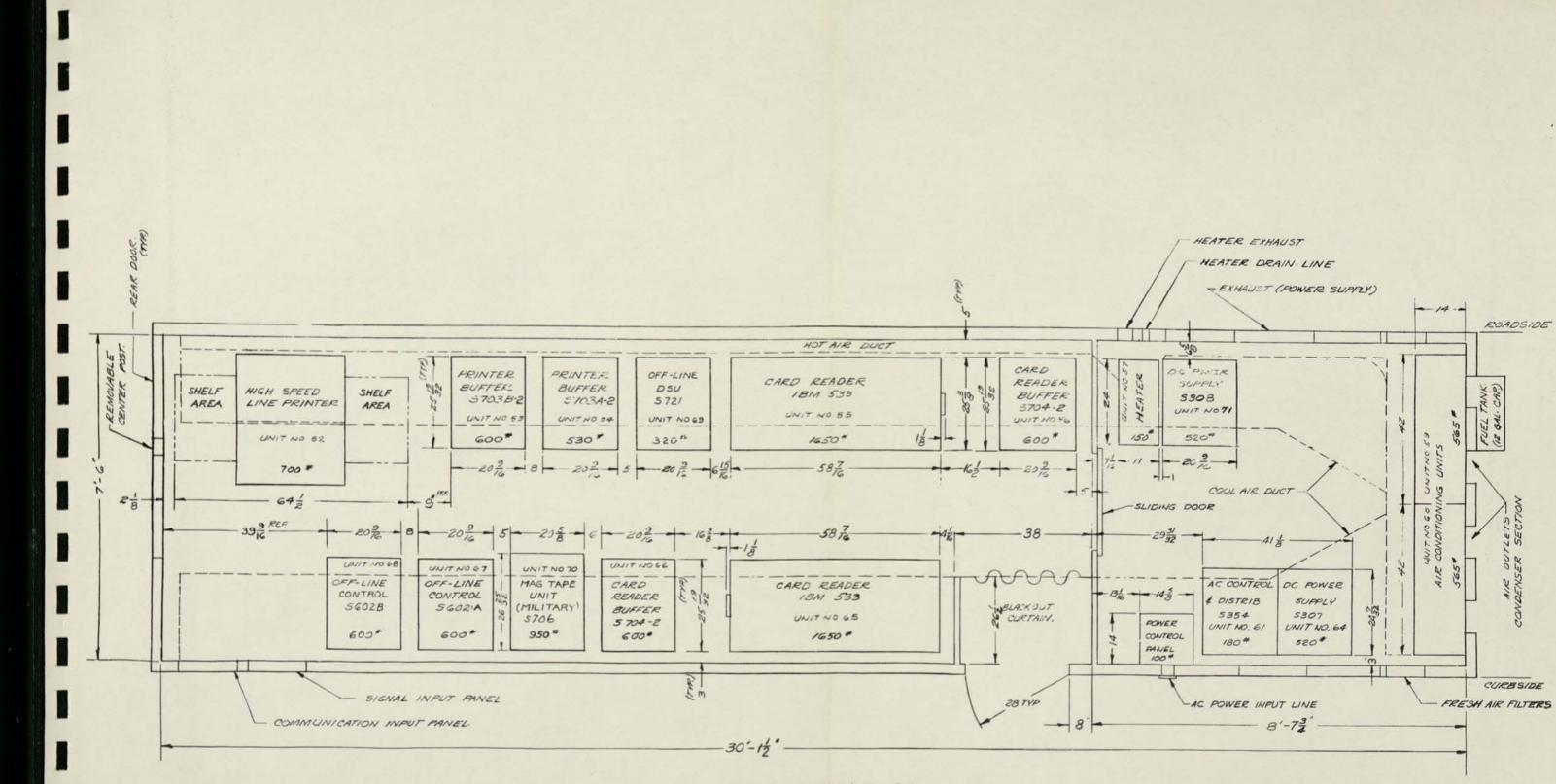

| 1-2    | MOBIDIC 7A Van 2 Layout                                          | 1-9   |

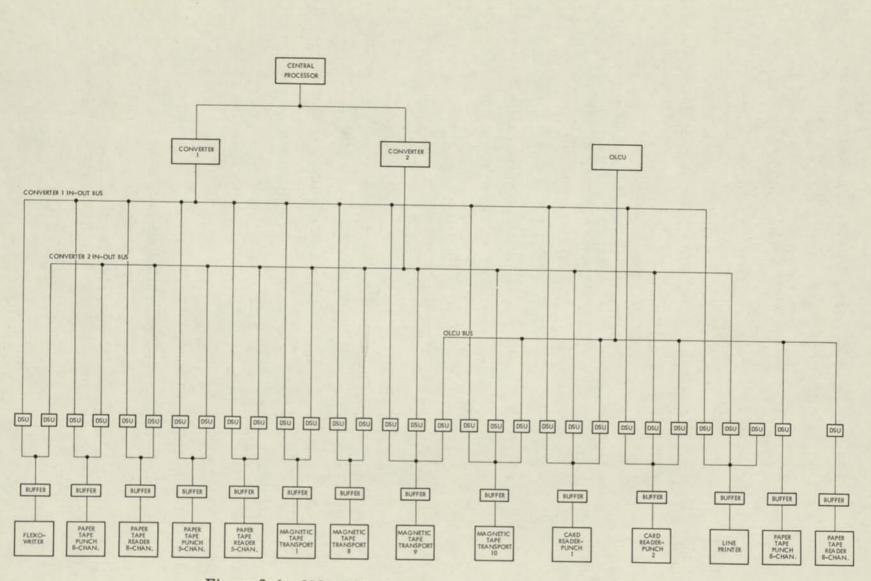

| 2-1    | MOBIDIC 7A In-Out and Off-Line Control Systems, Block<br>Diagram | 2-3   |

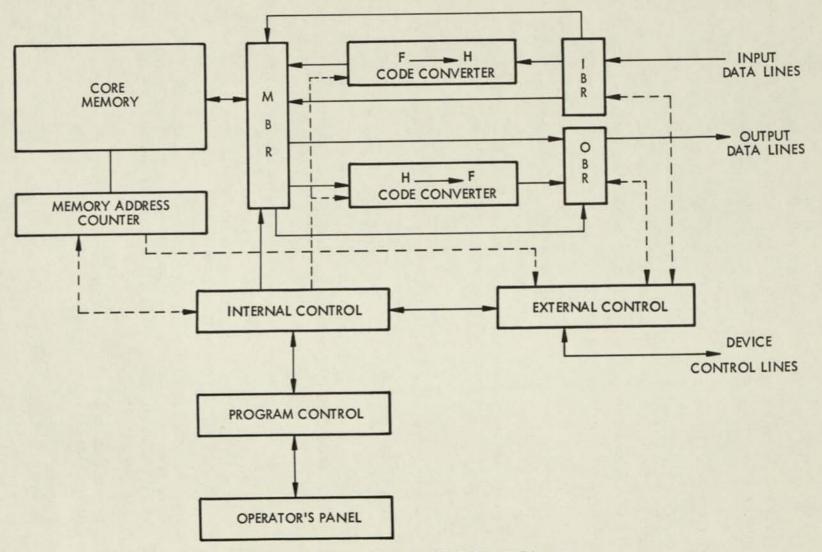

| 2-2    | Off-Line Control Unit Block Diagram                              | 2-14  |

| 2-3    | OLCU Marginal Check Voltage Subassemblies                        | 2-16  |

| 2-4    | OLCU Operator's Panel                                            | 2-19  |

| 2-5    | OLCU Buffer Register Interconnections, Block Diagram             | 2-26  |

| 2-6    | Memory Buffer Bit Position Contents, Before and After Shifting   | 2-36  |

| 2-7    | Flow Chart, Row to Column Conversion                             | 2-42  |

| 2-8    | Flow Chart, Column to Row Conversion                             | 2-43  |

| 2-9    | Timing Signals Generated by Cycle Counter (CY)                   | 2-61  |

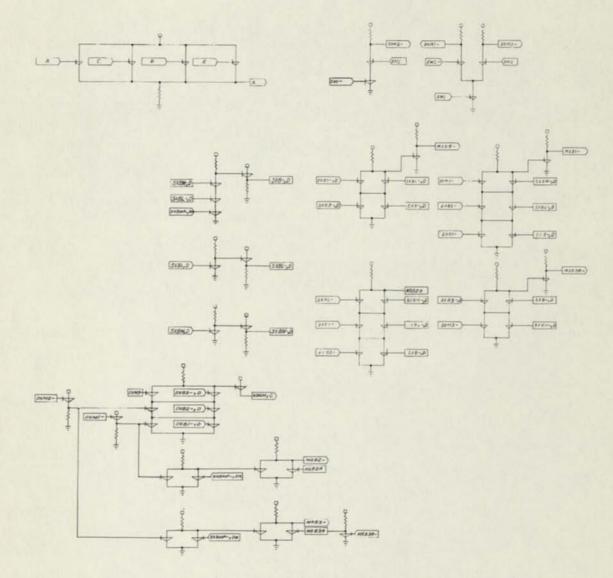

| 2-10   | Clear Mechanization                                              | 2-63  |

| 2-11   | Backspace Mechanization                                          | 2-64  |

| 2-12   | Magnetic Tape Input Mechanization                                | 2-65  |

| 2-13   | Paper Tape Input Mechanization                                   | 2-67  |

| 2-14   | Column Card Input (with Checking) Mechanization                  | 2-69  |

| 2-15   | Column Card Input (without Checking) Mechanization               | 2-71  |

| 2-16   | Row Card Input (with Checking) Mechanization                     | 2-73  |

| 2-17   | Row Card Input (without Checking) Mechanization                  | 2-75  |

| 2-18   | Magnetic Tape Output Mechanization                               | 2-77  |

| 2-19   | Line Printer, Paper Tape Output Mechanization                    | 2-79  |

| 2-20   | Column Card Output (with Checking) Mechanization                 | 2-81  |

| 2-21   | Column Card Output (without Checking) Mechanization              | 2-83  |

| 2-22   | Row Card Output (with Checking) Mechanization                    | 2-85  |

| 2-23   | Row Card Output (without Checking) Mechanization                 | 2-87  |

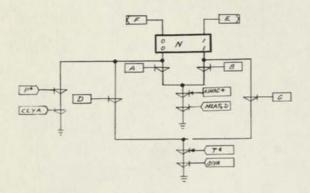

| 2-24   | Program Control State Diagram                                    | 2-91  |

| 2-25   | Memory Address Selection Matrix                                  | 2-107 |

| 2-26   | Typical X-Drive or Y-Drive Line Selection Configuration          | 2-109 |

1

I

### LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                        | Page  |

|--------|--------------------------------------------------------|-------|

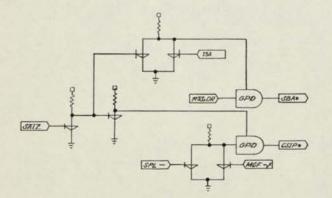

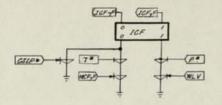

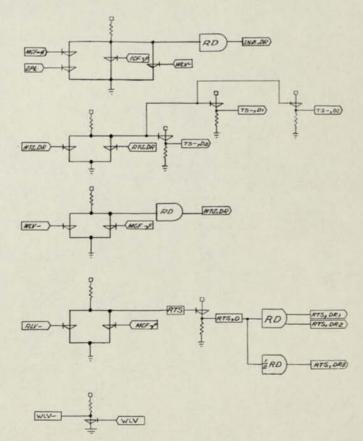

| 2-27   | Memory Control                                         | 2-111 |

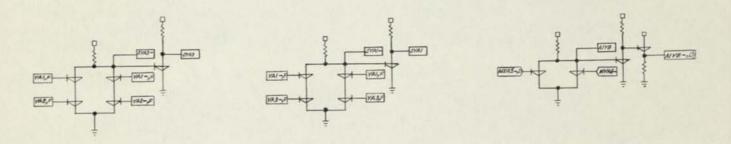

| 2-28   | Memory Address Decoders (MXB, DXM, TL)                 | 2-112 |

| 2-29   | Memory Address Decoders (XA, YA, Special)              | 2-113 |

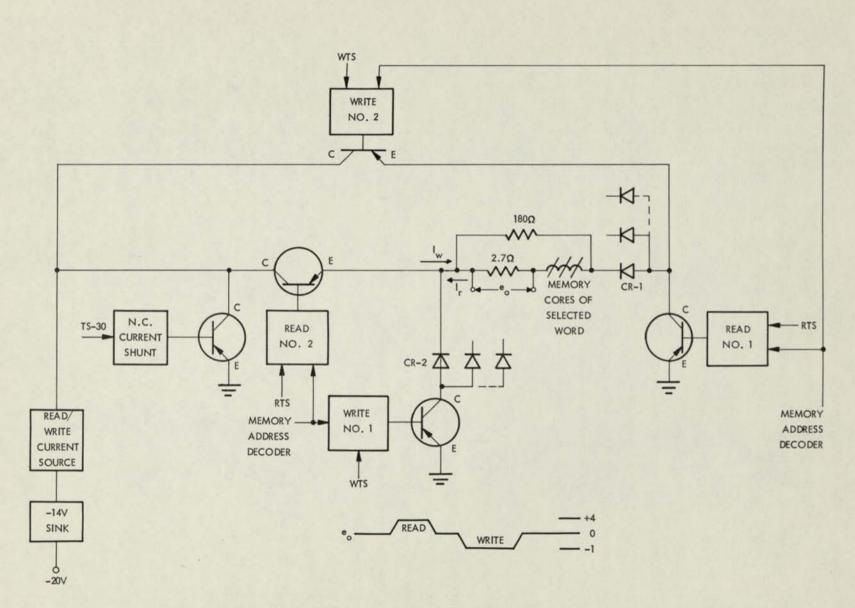

| 2-30   | Memory Address Counter                                 | 2-114 |

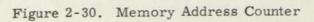

| 2-31   | Schematic Diagram, Element No. 92                      | 2-115 |

| 2-32   | MOBIDIC B Z-Driver Package Modification                | 2-117 |

| 2-33   | OLCU Memory Timing Diagram                             | 2-119 |

| 2-34   | Single Pulse Timing Cycle                              | 2-124 |

| 2-35   | Magnetic Switch Interlock Logic Diagram                | 2-126 |

| 2-36   | Register Selection Key Logic Diagram                   | 2-126 |

| 2-37   | Half-Register Driver                                   | 2-128 |

| 2-38   | Circuit Delay Time Vs Input Rise or Fall Time          | 2-132 |

| 2-39   | Input Amplitude Vs Input Rise and Fall Time            | 2-133 |

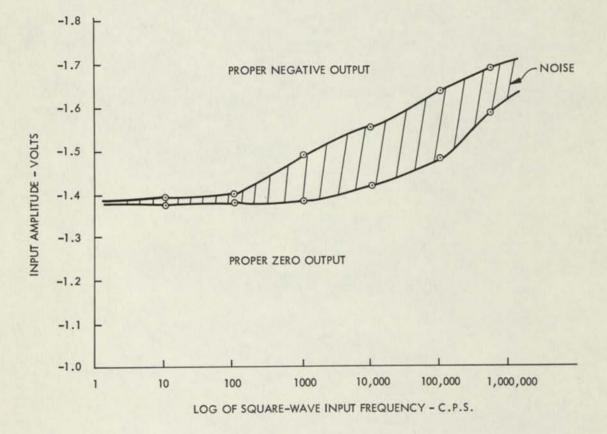

| 2-40   | Input Amplitude Vs Log of Input Frequency              | 2-134 |

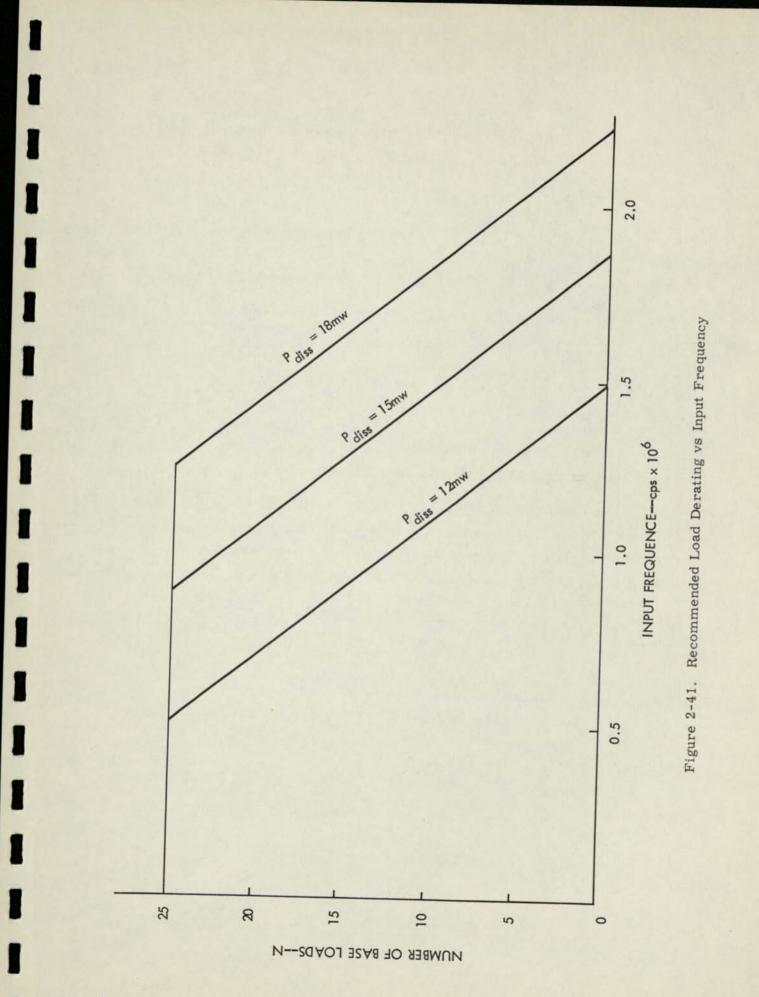

| 2-41   | Recommended Load Derating Vs Input Frequency           | 2-135 |

| 2-42   | Emitter Follower Worst-Case Loading                    | 2-138 |

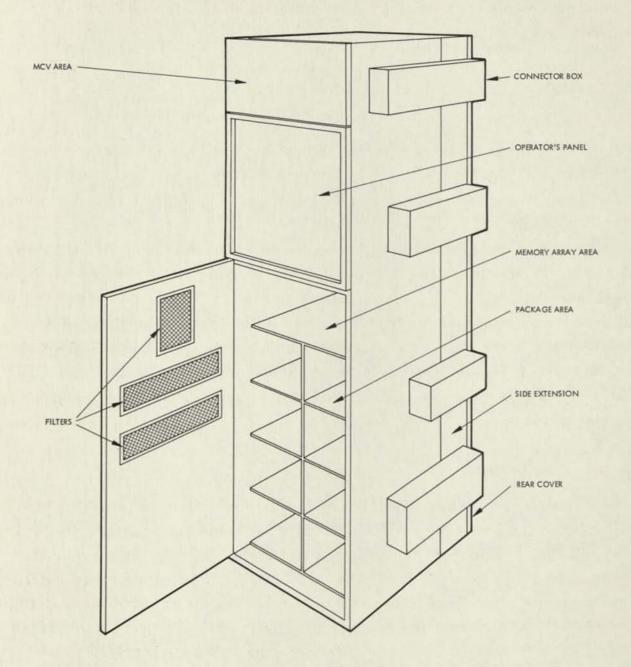

| 2-43   | Off-Line Control Unit, S602A                           | 2-144 |

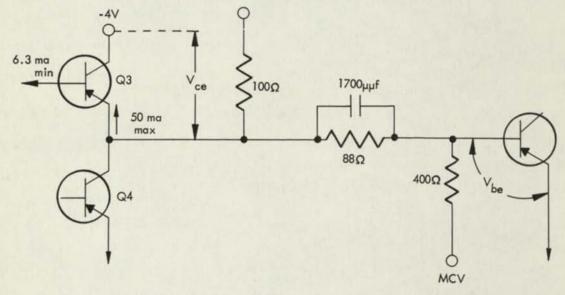

| 2-44   | MCV Control Circuits                                   | 2-163 |

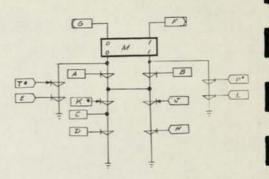

| 3-1    | Block Diagram of the Line Printer Buffer               | 3-6   |

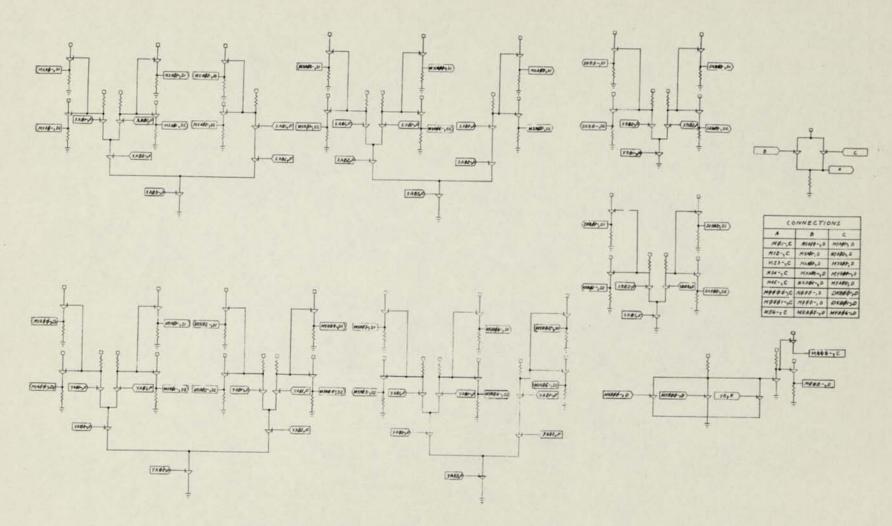

| 3-2    | General Flow Chart of the Line Printer Buffer          | 3-10  |

| 3-3    | Flow Chart, Standby and Reading In Line Feed Character | 3-12  |

| 3-4    | Flow Chart, Reading In Data                            | 3-13  |

| 3-5    | Flow Chart, Responding to Control Character            | 3-14  |

| 3-6A   | Flow Chart, Print Out                                  | 3-15  |

| 3-6B   | Flow Chart, Cycling                                    | 3-16  |

| 3-7    | Flow Chart, Automatic Line Feed                        | 3-17  |

| 3-8    | Flow Chart, Page Feed and Stop                         | 3-18  |

| 3-9    | Flow Chart, Programmed Line Feed                       | 3-19  |

| 4-1    | Block Diagram of the Card Reader and Punch Buffer      | 4-4   |

## LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------|------|

| 4-2    | Operational Flow Diagram, Standby Operation, Card Reader and Punch Buffer              | 4-6  |

| 4-3    | Operational Flow Diagram, Read Alphanumeric Operation,<br>Card Reader and Punch Buffer | 4-8  |

| 4-4    | Operational Flow Diagram, Punching Operation, Card Reader<br>and Punch Buffer          | 4-9  |

| 7-1    | Status Panel Layout, Van 1                                                             | 7-3  |

| 8-1    | Element Tester                                                                         | 8-4  |

|        |                                                                                        |      |

1

Ū

I

I

I

I

### LIST OF TABLES

| Table |                                                                | Page  |

|-------|----------------------------------------------------------------|-------|

| 1-1   | MOBIDIC 7A Equipment List, Sylvania-Manufactured Equipment     | 1-3   |

| 1-2   | MOBIDIC 7A Equipment List, Sylvania-Purchased Equipment        | 1-5   |

| 1-3   | MOBIDIC 7A Equipment List, Government-Furnished Equipment      | 1-6   |

| 2-1   | MOBIDIC 7A Off-Line Control System In-Out Devices              | 2-2   |

| 2-2   | OLCU Devices and Formats                                       | 2-5   |

| 2-3   | MCV Controls and Indicators                                    | 2-17  |

| 2-4   | Device and Mode Selection Controls and Indicators              | 2-20  |

| 2-5   | Operating and Error Checking Controls and Indicators           | 2-24  |

| 2-6   | Special Characters, Hollerith Code - Fieldata Code             | 2-33  |

| 2-7   | MOBIDIC Symbolic "Machine-Language" Conventions                | 2-37  |

| 2-8   | Read Counter Flip-Flops and ST States                          | 2-52  |

| 2-9   | Equations for Setting and Clearing the Read Counter Flip-Flops | 2-52  |

| 2-10  | Transient Dissipation in Q3 and Q4                             | 2-130 |

| 2-11  | Off-Line Equipment Power Requirements                          | 2-142 |

| 2-12  | OLCU Input-Output Summary                                      | 2-149 |

| 2-13  | OLCU Summary: Magnetic Tape Input                              | 2-150 |

| 2-14  | OLCU Summary: Paper Tape Input                                 | 2-151 |

| 2-15  | OLCU Summary: Card Reader Input                                | 2-152 |

| 3-1   | The 64 Six-Bit Fieldata Character Codes                        | 3-2   |

| 4-1   | Auxiliary Card Buffer                                          | 4-11  |

| 7-1   | Status Panel Indicators                                        | 7-5   |

1

I

I

1

I

### SECTION I

#### INTRODUCTION

MOBIDIC 7A is a general-purpose, high-speed, mobile computer intended for field use by the United States Army. It has been built by the Data Systems Operations of Sylvania Electronic Systems, a Division of Sylvania Electric Products, Inc., under the terms of contract number DA-36-039-SC-85117. MOBIDIC 7A conforms to Signal Corps Technical Requirements SCL 1959A, dated 14 October 1959. The computer provides a reliable mobile computing facility for use by military commanders in the field for combat support and combat control data processing and for combat computation. It can also serve as a vital element in MASS, the modern army supply system.

The computer is housed in two semi-trailer vans. A third semi-trailer van serves as a maintenance van. Tables 1-1, 1-2, and 1-3 list the Sylvania-manufactured, Sylvania-purchased, and government-furnished equipment included in the MOBIDIC 7A computer. The organization of the system is such that equipment in van 2 can be adapted for operation independent of equipment in van 1. The arrangement of the MOBIDIC 7A equipment in vans 1 and 2 is shown in Figures 1-1 and 1-2, respectively.

MOBIDIC 7A is essentially similar to other MOBIDIC computers. The principal difference is the addition of an off-line control system. MOBIDIC 7A includes both a real-time system and a program-interrupt feature.

This final design plan includes information additional to that included in the Final Design Plans of MOBIDICS A, B, C, and D and the Addendum to the Final Design Plan for MOBIDIC D. Reference should be made to those documents for a complete understanding of the MOBIDIC 7A design. This design plan includes the following sections:

- I Introduction

- II Off-Line Control System

- III Line Printer and Line Printer Buffer

I

I

- IV Card Reader-Punch and Card Reader-Punch Buffer

- V Logic and Mechanization Designations

- VI Mechanization Lists

- VII Van Layout

- VIII Element Tester

## TABLE 1-1. MOBIDIC 7A EQUIPMENT LIST SYLVANIA-MANUFACTURED EQUIPMENT

y J

| Unit    | Description                                                                                               | Quantity |

|---------|-----------------------------------------------------------------------------------------------------------|----------|

| S101-2  | Central Processor, with Program Interrupt                                                                 | 1        |

| S201    | Console, A                                                                                                | 1        |

| S307    | Power Supply Set (Van 2)                                                                                  | 1        |

| S308    | Power Supply Set (Van 2)                                                                                  | 1        |

| S310-2  | Power Supply Set (Van 1)                                                                                  | 1        |

| S311-2  | Power Supply Set (Van 1)                                                                                  | 1        |

| S312-2  | Power Supply Set (Van 1)                                                                                  | 1        |

| S353    | AC Control and Distribution (Van 1)                                                                       | 1        |

| S354    | AC Control and Distribution (Van 2)                                                                       | 1        |

| S401    | Core Memory (4,096 words)                                                                                 | 2        |

| S601-2  | Converter                                                                                                 | 2        |

| S602A   | Off-Line Control Unit                                                                                     | 1        |

| S602B   | Off-Line Control Unit                                                                                     | 1        |

| S702    | Paper Tape Reader and Punch (8-channel), Device Switching<br>Units (See Note 1), and Buffers (See Note 2) | 1        |

| S703A-2 | Line Printer Buffer                                                                                       | 1        |

| S703B-2 | Line Printer Control                                                                                      | 1        |

| S704-2  | Card Reader-Punch Buffer                                                                                  | 2        |

| S706    | Magnetic Tape Units (Militarized Magnetic Tape Transports)                                                | 6        |

| S707    | Paper Tape Reader and Punch (5-channel) and Buffer (See Note 3)                                           | 1        |

| S709    | Flexowriter Table                                                                                         | 1        |

1

6

1

1

F

F

ſ

I

1

- where

## TABLE 1-1. MOBIDIC 7A EQUIPMENT LIST SYLVANIA-MANUFACTURED EQUIPMENT (Cont.)

| Unit   | Description                                                                                                                                                                                                                                                                                                                          | Quantity |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| S720-2 | Magnetic Tape Unit Device Switching Units                                                                                                                                                                                                                                                                                            | 1        |

| S721   | Off-Line Control System Device Switching Units                                                                                                                                                                                                                                                                                       |          |

| S901   | Element Tester                                                                                                                                                                                                                                                                                                                       |          |

| S904   | Teletype Equipment Stand                                                                                                                                                                                                                                                                                                             | 1        |

|        | <ul> <li>Note 1: For the 8- and 5-channel paper tape readers and punches and for the Flexowriter.</li> <li>Note 2: For the 8- and 5-channel paper tape readers and punches (except for part of the 5-channel paper tape punch buffer) and the Flexowriter.</li> <li>Note 3: Balance of 5-channel paper tape punch buffer.</li> </ul> | ,        |

## TABLE 1-2. MOBIDIC 7A EQUIPMENT LIST, SYLVANIA-PURCHASED EQUIPMENT

| Description                         | Mounting          | Quantity |

|-------------------------------------|-------------------|----------|

| Line Printer                        | In Van 2          | 1        |

| Card Reader-Punch                   | In Van 2          | 2        |

| Militarized Magnetic Tape Transport | See Note 1        | 11       |

| Flexowriter                         | In Van 1, in S709 | 1        |

| Paper Tape Reader                   | See Note 2        | 3        |

| Paper Tape Punch                    |                   |          |

| 8-channel                           | See Note 3        | 2        |

| 5-channel                           | In Van 1, in S707 | 1        |

| Paper Tape Spooler                  | See Note 2        | 3        |

Note 1: 8 in Van 1, 2 in Van 2, 1 in Van 3.

Note 2: 2 in Van 1 (1 in S702, 1 in S707); 1 in Van 2, in S721.

Note 3: 1 in Van 1, in S702; 1 in Van 2, in S721.

1

1

1

### TABLE 1-3. MOBIDIC 7A EQUIPMENT LIST, GOVERNMENT-FURNISHED EQUIPMENT

| Description           | Mounting          | Quantity |

|-----------------------|-------------------|----------|

| Air Conditioner       | 2 in each Van     | 6        |

| Space Heater          | 1 in each Van     | 3        |

| Field Telephone       | See Note 1        | 2        |

| Teletype Printer      | In Van 1, on S904 | 1        |

| Teletype Reperforator | In Van 1, on S904 | 1        |

| Power Unit (100)KW)   |                   | 2        |

| M393A2 Van            |                   | 3        |

### Note 1: 1 in Van 1, 1 in Van 2

Figure 1-1. MOBIDIC 7A Van 1 Layout

Figure 1-2. MOBIDIC 7A Van 2 Layout

### SECTION II

E

### OFF-LINE CONTROL SYSTEM

#### 2.1 GENERAL

One of the features of MOBIDIC 7A is the off-line control system. This system permits off-line data processing without interference with computer data processing. The off-line control system is described in detail in this section.

#### 2.2 PURPOSE AND USE

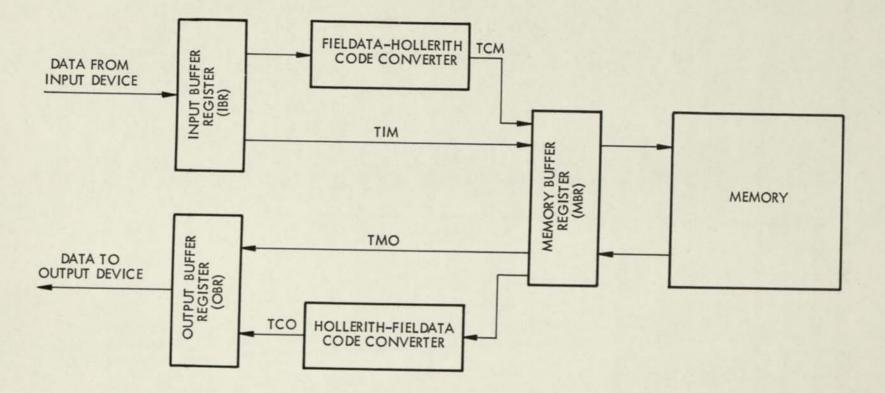

The MOBIDIC Off-Line Control Unit (OLCU) has been designed to increase the effectiveness of MOBIDIC data-processing systems. The OLCU enables transfer of data between MOBIDIC in-out devices, the transfer taking place independent of central computer control and despite differences in device operating rates. The OLCU makes it possible, for example, to transfer data between magnetic tape and in-out media having lower operating rates. This is often desirable since substantial savings in central computer operating time can be realized by taking advantage of the relatively high rate of data transfer which can be achieved by using magnetic tape as the in-out media during execution of in-out instructions. The OLCU enables the format of data to be changed. Data stored on paper tape, for example, can be punched on cards for further processing. The OLCU is highly useful in applications which require processing of a large volume of data which either has been prepared off-line or is to be used off-line. The in-out devices included in the MOBIDIC 7A off-line control system are listed in Table 2-1. The OLCU is useful in any Fieldata application that requires off-line transfer or conversion of data since the formats used by MOBIDIC computers are those used for Fieldata. In general, the term conversion will be used in this section to describe either transfer of data between in-out media or conversion of data from one format to another. Both transfer and conversion can be performed simultaneously by the OLCU. The relationship between the MOBIDIC 7A in-out and off-line control systems is shown, in block diagram form, on Figure 2-1.

## TABLE 2-1. MOBIDIC 7A OFF-LINE CONTROL SYSTEM IN-OUT DEVICES

| Unit | Device                                                                                                                             | Quantity |

|------|------------------------------------------------------------------------------------------------------------------------------------|----------|

| S706 | Militarized Magnetic Tape Transports                                                                                               | 2 *      |

| S721 | Paper Tape Punch, 8-channel                                                                                                        | 1        |

|      | Paper Tape Reader, 8-channel                                                                                                       | 1        |

|      | Card Reader-Punch                                                                                                                  | 2 *      |

|      | Line Printer                                                                                                                       | 1 *      |

|      | <pre>* = Capable of being used either on-line or off-<br/>For a description of the on-line, off-line in<br/>locks, see 2.10.</pre> |          |

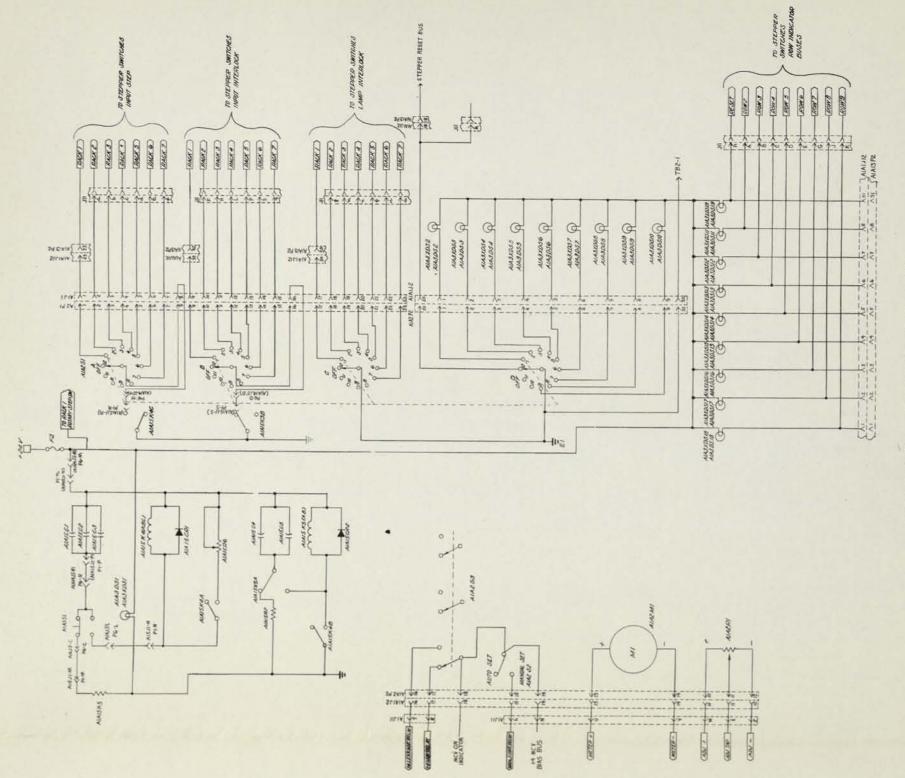

Figure 2-1. MOBIDIC 7A In-Out and Off-Line Control Systems, Block Diagram

2-3

Table 2-2 lists the devices, data rates, and formats used. The rates listed are those of the in-out devices presently used in MOBIDIC in-out systems. Conversion may be performed between any input and output device listed. Any necessary changes in format, including conversions between Hollerith and Fieldata code, are performed by the OLCU. The conversions actually carried out depend upon the control settings on the operator's panel.

The OLCU consists essentially of a memory, several high-speed buffer registers, controls for operating the in-out devices and OLCU, and associated circuits. The memory is of the magnetic-core type. It is capable of storing 672 Fieldata characters or 336 Hollerith characters. The memory and registers are described in 2.6 and 2.7. The controls are described in 2.6 and 2.9. The circuits are described in 2.7. OLCU equipment is housed in two MOBIDIC-type enclosures. These enclosures, the S602A and S602B units, are described in 2.8.

Transfer operations, also called conversion operations, are carried out one block of information at a time. A typical conversion cycle includes the following sequence of operations:

- 1. Clear the OLCU and check for operator errors.

- 2. Start the selected input device.

- 3. Transfer information from the selected input device to the OLCU memory. The transfer continues either until the OLCU memory is filled, or until an end-of-block or end-of-file mark is sensed, or until the specified number of cards (4 maximum) have been read. A stop code on paper tape input is considered to be equivalent to end-of-file mark. The card reader-punch generates an end-of-file signal if the last cards in the deck being run are fed through the reader with the card hopper empty.

- 4. Stop the selected input device.

- 5. Start the selected output device.

- 6. Transfer information from the OLCU memory to the selected output device.

- If end-of-file mark (or the equivalent) was not reached during step 3, repeat the entire sequence of operations starting at step 2.

|                                                              | Input Devices                                                     |                                                                                                                     |

|--------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Media                                                        | Rate *                                                            | Formats                                                                                                             |

| Magnetic Tape<br>Paper Tape<br>Punched Cards                 | 45,000 char/sec<br>270 char/sec<br>200 cards/min                  | Standard Fieldata<br>Standard Fieldata<br>Row Fieldata<br>Column Fieldata<br>Hollerith                              |

|                                                              | Output Devices                                                    |                                                                                                                     |

| Media                                                        | Rate                                                              | Formats                                                                                                             |

| Magnetic Tape<br>Paper Tape<br>Punched Cards<br>Line Printer | 45,000 char/sec<br>100 char/sec<br>100 cards/min<br>600 lines/min | Standard Fieldata<br>Standard Fieldata<br>Row Fieldata<br>Column Fieldata<br>Hollerith<br>Same as when used on-line |

## TABLE 2-2. OLCU DEVICE RATES AND FORMATS

I

ļ

-

8. If an end-of-file mark (or equivalent) was reached during step 3, stop the cycle of operations after step 6 and halt both the OLCU and the selected output device.

Since the OLCU completes a one-character cycle in ten microseconds, it can handle data more rapidly than can any presently-known and available MOBIDIC in-out device. It can, for example, operate with magnetic tapes having an operating rate of 90,000 characters per second. The off-line control system data handling rates are device-limited, rather than OLCU-limited.

The OLCU can be used in a blockette mode of operation when using either paper tape or magnetic tape input. When operating in this mode not all of the information contained in a block is converted. Instead, only that contained in part of the block is converted. Each selected portion within the block is called a blockette. Use of the blockette mode provides specialized searching capacity and permits on-line preparation of magnetic tapes on which are stored blocks of information longer than those capable of conversion during a single cycle of OLCU operation.

### 2.3 OPERATIONAL CONSIDERATIONS

### 2.3.1 Compatibility with MOBIDIC In-Out Devices

The design of the OLCU is such that it is operationally compatible with all in-out devices (and their associated buffers) previously incorporated in MOBIDIC systems. One of the primary design objectives was to make the transfer and conversion capabilities of the OLCU as universal as feasible. This requirement has been met. It is possible to convert or transfer data from any MOBIDIC input media to any MOBIDIC output media with but one exception. The only exception is that card to card transfers cannot be performed. The data formats used in off-line control operation are exactly the same as those of the various in-out media incorporated in MOBIDIC. Magnetic and paper tapes can be handled in either the interpret sign or the non-interpret sign mode. Punched cards of the type used in the MOBIDIC card reader-punch may also be handled in either of these modes. Because of the widespread use of Hollerith code in electronic data processing (EDP), provision has been made in the design of the OLCU for automatic conversion between

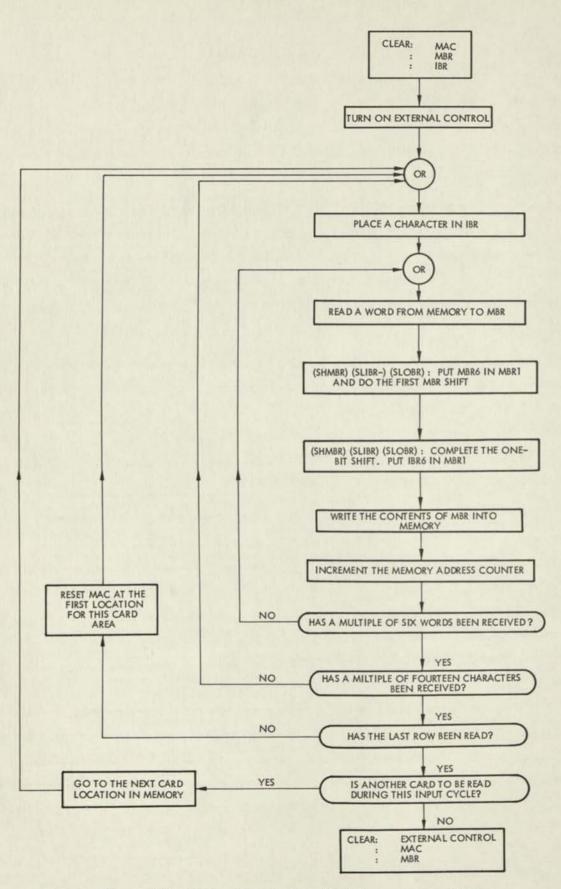

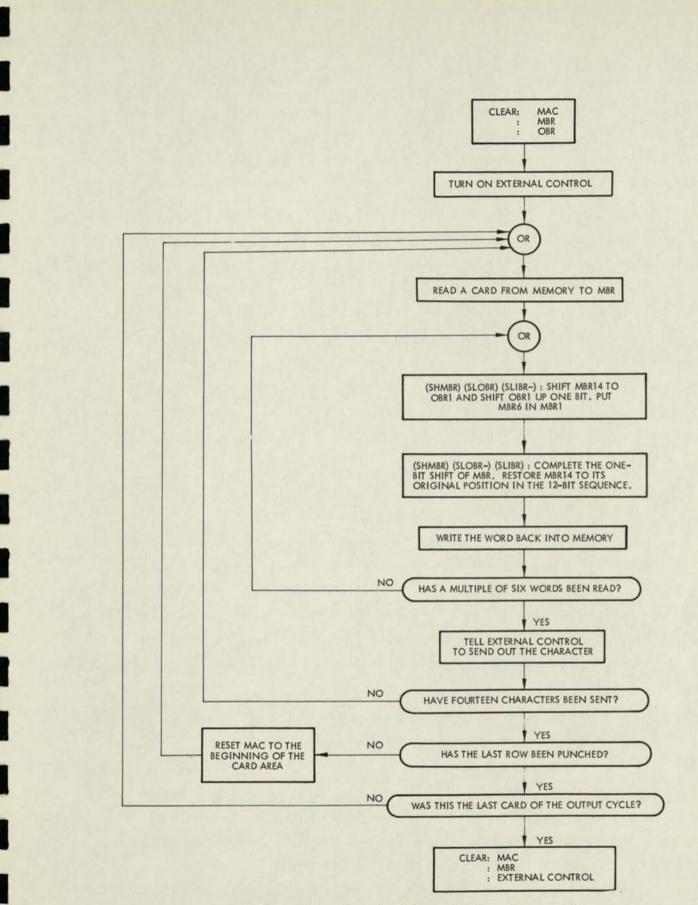

Hollerith and Fieldata codes when such is desirable. Because information in the OLCU memory is stored in column format, provision has been made for automatic row to column conversion during card input and for automatic column to row conversion during card output. When operating with punched cards, selection of the interpret sign mode, by operation of the BINARY mode switch, will cause the OLCU to read or punch the cards as row cards (information punched on the cards in horizontal rows, as distinct from column cards on which information is punched in vertical columns). The format of the row cards is the same as that of cards read or punched during normal MOBIDIC system on-line operation of the card readerpunch. Selection of the non-interpret sign mode, by operation of the ALPHANUM (alphanumeric) mode switch, will cause the OLCU to perform an automatic row to column or column to row conversion, as necessary. Every column on the card is then read or punched as if it consisted of two Fieldata characters (6 data bits each). The Hollerith mode may also be selected, by operation of the HOLL (Hollerith) mode switch, during OLCU operation when using punched cards. In that mode the OLCU automatically performs the required column to row or row to column conversion. Each column is treated as if it consisted of one Hollerith character. Conversions between the Hollerith and Fieldata codes is carried out automaticlly by the OLCU when operating in the Hollerith mode.

#### 2.3.2 Format Control

A minimum of format control has been included in the design of the OLCU. Such a design approach offers the following three advantages:

- 1. Simplicity.

- 2. Ready adaptability for future use with in-out devices or device formats not presently employed in MOBIDIC systems.

- 3. Compatibility and similarity of programming for on-line and off-line operation of the in-out equipment.

### 2.3.3 Padding

Provision has been made in the OLCU design for processing padding characters or bits in a manner appropriate to the in-out devices or formats used. The following examples indicate the use of padding characters by the OLCU. Cards handled by the card reader-punch during on-line operation are read or punched under computer control as if using an 84-column format. Such a format is compatible with the standard six or seven character MOBIDIC word length. During off-line operation cards are also handled as if they had a similar 84-column format. The four columns additional to the 80 columns on the standard card are always generated or deleted by equipment external to the OLCU. The extra, or padding, columns are carried through the conversion process in the OLCU although they are not actually punched or read. When converting information from magnetic tape to cards punched in the Hollerith code 84 characters must be physically present on the tape for each complete card punched. Four of these characters are the padding characters. The padding characters are not punched and, therefore, never appear on the punched card. They are, however, processed through the OLCU.

At times there may not be an integral number of six-character groups on paper tape. An integral number of such groups must, however, appear on any magnetic tapes to be read by the computer (if an integral number of such groups is not read a magnetic tape reading error signal is generated). The OLCU has been so designed that when converting information from paper tape to magnetic tape in the non-interpret sign mode sufficient padding characters are automatically generated by the OLCU to assure that the next larger integral number of six-character groups will be present on the magnetic tape.

### 2.3.4 Set-Up and Error Control

An optimum compromise between simplicity and flexibility, within the broad general requirement of over-all OLCU design simplicity, has been achieved in the design, arrangement, and function of the controls and indicators on the operator's panel. Except for actual loading of the in-out devices to be used during OLCU operation, any conversion can be completely set up and flexibly controlled by appropriate operation of the panel-mounted controls. OLCU operational and error control procedures are such that the operator is required to perform only simple actions. These actions are essentially similar for each of the in-out devices with which the OLCU is employed. A complete error-checking capability, extending to all in-out devices and formats used, has been incorporated in the OLCU design. This has been done to assure detection of all errors that might occur during conversion. It is imperative that such errors be detected at that time since in many cases the converted information is not used until some time later. Provision has been made not only for controlling the various error-checking and correcting features but also for ignoring errors when such is desirable. For example, error indications can be ignored when the urgent need for a particular conversion is more important than the general accuracy level of that conversion.

#### 2.3.5 Blockette Mode

Capability for operating in the blockette mode has been included in the design of the OLCU. This capability permits more efficient computer operation and increases OLCU flexibility. Computer operation is more efficient since long blocks of information can be written on magnetic tape at relatively high speed for subsequent off-line processing. The advantages of increased OLCU flexibility are particularly evident when magnetic or paper tape is used as the input media. When paper tape input is used blocks of information of variable length can be written on magnetic tape or cards can be punched with a variable number of characters per card. When magnetic tape input is used specific information within a block can be selected for conversion.

### 2.3.6 On-Line and Off-Line Operation

As noted previously, the OLCU has been designed to operate with the in-out devices and their buffers which are already in use in MOBIDIC systems. Certain of these devices can be used either on-line or off-line. The following example indicates the utility of this device sharing arrangement. Magnetic tapes can be prepared on-line for off-line processing and the off-line processing carried out without physical handling of the tape reel. Also, such tapes can be prepared offline and then used, without tape reel handling, for on-line input to the computer.

### 2.4 DESIGN CONSIDERATIONS

The MOBIDIC off-line control system was designed to meet several general requirements. It was necessary that the design:

- 1. Allow continuous operation of the complete MOBIDIC on-line system without interference by the off-line control system.

- 2. Prevent improper use of in-out devices. The design is such that attempts to do so can occur only as a result of an operator's error in using the off-line control equipment.

- 3. Indicate attempts to use an in-out device improperly.

More detailed design considerations are described in paragraphs 2.4.1 through 2.4.5.

### 2.4.1 System Compatibility

The off-line control system has been designed for compatibility with existing MOBIDIC in-out systems. Not only was it considered necessary that the OLCU be capable of operating with the same types of in-out devices and buffers as are used in such systems but it was furthermore considered desirable to so design the off-line control system that several such devices could be used either on-line or off-line. Accordingly, the OLCU bus and device switching units (DSUs) as well as the OLCU have been designed to meet these objectives. The same DSU can be used for either on-line or off-line operation in the case of devices capable of such operation. During on-line operation the DSU is used with the MOBIDIC converter; during off-line operation it is used with the OLCU. Such an arrangement is required, for example, when four converters and an OLCU are included in a particular MOBIDIC in-out system. In such a system three of the four DSUs associated with each shared (i.e., on-line, off-line) device are used during on-line operation. The fourth DSU can be connected, by appropriate manual procedures, for either on-line or off-line operation.

### 2.4.2 Converter - OLCU Similarity

The design of the OLCU has been based to a great extent upon the experienced gained on the standard MOBIDIC converter. This has been possible because of the

similarities between the two units. Control of in-out device operation by the OLCU is essentially similar to that exercised by the converter. Substantial savings in the number of transistors required have been realized by simplifying the converter design wherever feasible. The control area, for example, is one in which the simpler design has been employed to advantage. The OLCU does not need to modify orders and it is not required to regulate execution of rewrite instructions. Elimination of these functions has allowed use of a simpler design, resulting in a need for fewer transistors. Use of fewer transistors has also simplified trouble-shooting and maintenance procedures.

### 2.4.3 Design Approach

The OLCU design approach was determined after careful analysis of the operational requirements. Although the OLCU in general has been designed as a wired program machine, a variety of design techniques, each suited to the requirements of a particular area of the OLCU, have been employed. The desire for simplicity of design and ease of maintenance dictated division of operational control into three general sections. These are the internal, external, and master control sections. The external control section regulates in-out device operation. All of the various operations, or instructions, which must be performed within the OLCU to carry out a particular conversion are, in effect, mechanized within the internal control section. The master control section, at times referred to as the program control section, governs the sequence in which the OLCU performs the selected conversion.

### 2.4.4 Memory Capacity

112 writer

The capacity of the magnetic-core OLCU memory was chosen as a result of a design compromise. Use of a small capacity memory would contribute toward OLCU component cost reduction. Use of a larger capacity memory, however, would permit writing lengthy blocks of information on magnetic tape during a single conversion operation. This would have the effect of decreasing the operational cost of reading or writing information on magnetic tape. The size of the memory chosen, <u>672</u> Fieldata characters, is small enough to hold down component costs, yet it is sufficiently large to provide storage for relatively long blocks of information. It is large enough, for example, to store as much information as can be read from or written onto four punched cards. It should be noted, however, that memory storage capacity equal to that required to store information for one card is required for conversion checking purposes. Therefore, only as much information as can be stored on three cards can be converted during any single conversion when the card checking feature is being used.

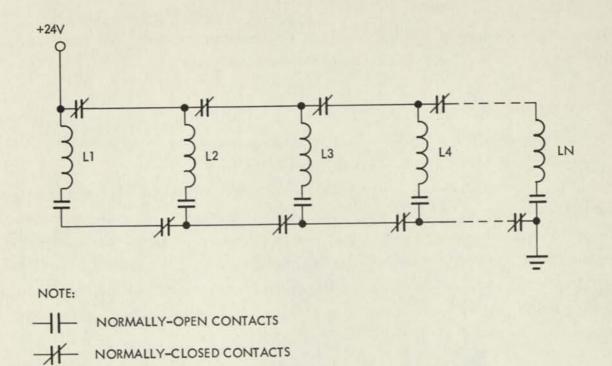

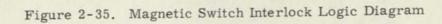

### 2.4.5 Device Switching Unit Interlocks

Interlocks have been provided in the design of those device switching units (DSUs) associated with in-out devices which are capable of either on-line or offline operation. The interlocks prevent improper use of such devices. The design is such that a device actually being used off-line cannot be used on-line by the MOBIDIC system and a device actually being used on-line cannot be used off-line.

### 2.4.6 Verify Mode

The OLCU design provides for operation of the equipment in a verify mode. This mode of operation permits off-line checking of paper tape punched under OLCU control. In the verify mode the output cycle is inhibited and input is checked for parity errors. The OLCU imposes no limit on block length when tape input is used during operation in the verify mode.

#### 2.5 DESIGN DESCRIPTION

The design of the off-line control system and its equipment is described in the three major paragraphs which follow. System design is detailed in paragraph 2.6, circuit design in paragraph 2.7, and mechanical design in paragraph 2.8.

### 2.6 SYSTEM DESIGN

The overall relationship between various items in the MOBIDIC computer and the off-line control system is shown in block diagram form on Figure 2-1.

### 2.6.1 OLCU Block Diagram

The OLCU is shown in block diagram form on Figure 2-2. A brief listing of the basic function of each portion of the OLCU represented by a block on the diagram follows. More complete descriptions of various aspects of the OLCU are given in paragraphs 2.6.2 through 2.6.7

- 1. Memory This is a magnetic-core type memory which provides storage capacity for up to 672 Fieldata characters (or 336 Hollerith characters).

- 2. MA Counter The MA (memory address) counter (MAC) used to address the memory location into which information is to be stored or from which information is to be extracted.

- 3. MBR The MBR (memory buffer register) is a 16-bit register used to store information being transferred to or from memory.

- 4. IBR The IBR (input buffer register) is an 8-bit register which accepts information entering the OLCU from the selected in-out device.

- 5. OBR The OBR (output buffer register) is an 8-bit register used to hold the information going from the OLCU to the selected in-out device.

- 6. FH Code Converter The FH (Fieldata to Hollerith) code converter is used when information is to be converted from Fieldata code form to Hollerith code form. Appropriate control and parity bits are generated in this converter. The FH code converter accepts information from the IBR and sends it to the MBR.

- 7. HF Code Converter The HF (Hollerith to Fieldata) code converter is used when information is to be converted from Hollerith code form to Fieldata code form. The HF code converter accepts information from the MBR and sends it to the OBR.

- 8. Internal Control The internal control section regulates transfers of information between the OBR, IBR, MBR, and memory.

- 9. External Control The external control section regulates transfers between the IBR, OBR, and in-out devices.

Figure 2-2. Off-Line Control Unit Block Diagram

- 10. Program Control The program control section provides all of the status and instruction signals necessary for OLCU operation and regulates the sequence of OLCU operations on the basis of the set-up on the operator's panel.

- 11. Operator's Panel The operator's panel contains the controls and indicators required for manual control of OLCU operation.

### 2.6.2 OLCU Control Center

The OLCU control center is located in the S602A enclosure. It occupies the upper four rows (A1, A2, A3, and A4) of that enclosure. The top row (row A1) houses the subassemblies associated with the marginal check voltage (MCV) system. The operator's panel, located in the area normally used for logic-package assemblies in standard MOBIDIC enclosures, is divided into two principal sections. These are the Device and Mode Selection and the Operating and Error Checking sections. The MCV row is provided with a door. This has been done because access to the controls on the MCV subassemblies is not usually required nor is it desirable that such access be easy during normal OLCU operation.

### 2.6.2.1 Marginal Check Voltage System Subassemblies

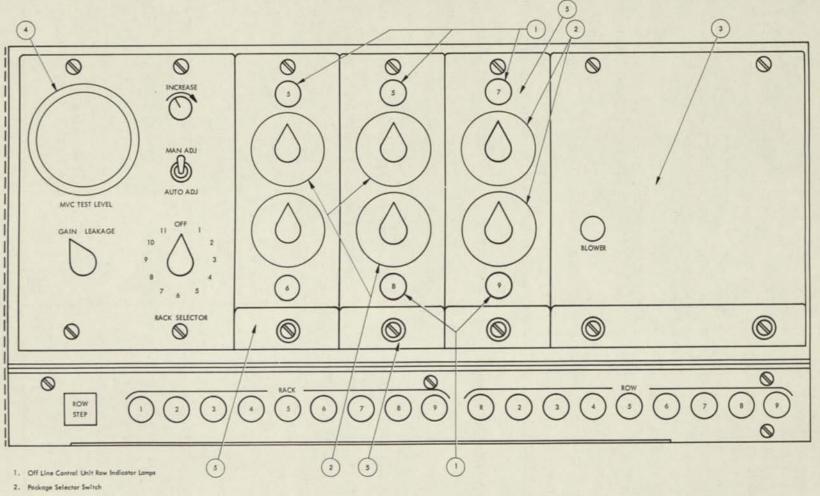

The marginal check voltage system subassemblies are similar to corresponding standard MOBIDIC MCV subassemblies. The arrangement of the six MCV subassemblies, in row A1 of the S602A enclosure is shown on Figure 2-3. The various controls, indicators, and associated items used in controlling MCV application are listed on Table 2-3 which also describes the principal function of each item.

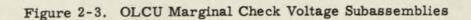

#### 2.6.2.2 Device and Mode Selection Section

The upper section of the operator's panel is the device and mode selection section. The arrangement of the controls and indicators are as shown on Figure 2-4. The controls and indicators on the device and mode selection section are listed on Table 2-4. This table also describes the principal function of each item.

- 3. Stepping Switch Sub-Assembly

- 4. MCV Control Subassembly

- 5. Selector Siwtch Subasembly

# TABLE 2-3, MCV CONTROLS AND INDICATORS

| Item                              | Function                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCV Control Subassembly           |                                                                                                                                                                                                                                                                                                                                                                                                 |

| MCV TEST LEVEL Meter              | Indicates the MCV level applied to circuits during MCV system operation.                                                                                                                                                                                                                                                                                                                        |

| GAIN-LEAKAGE Switch               | Used for MCV bias selection. Deterio-<br>ration in transistor beta is checked when<br>this switch is set at the GAIN position;<br>deterioration in transistor Ico is checked<br>when this switch is set at the LEAKAGE<br>position.                                                                                                                                                             |

| Manual Voltage Control            | Used to adjust the MCV level when the MAN<br>ADJ-AUTO ADJ switch is set at the MAN<br>ADJ position.                                                                                                                                                                                                                                                                                             |

| MAN ADJ-AUTO ADJ Switch           | Used to select the method of adjusting the<br>MCV level. When this switch is set at<br>the MAN ADJ (manual adjustment) posi-<br>tion the MCV level is determined by the<br>setting of the manual voltage control.<br>When this switch is set at the AUTO ADJ<br>(automatic adjustment) position the MCV<br>level is determined by the setting of the<br>level controls in the MCV power supply. |

| RACK SELECTOR Switch              | Use to select the rack to which the MCV is to be applied.                                                                                                                                                                                                                                                                                                                                       |

| MCV Selector Switch Subassemblies |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Row Indicators                    | Light to indicate the OLCU row to which the MCV is applied.                                                                                                                                                                                                                                                                                                                                     |

| Selector Switches                 | Used to select the logic-package assembly to which the MCV is to be applied.                                                                                                                                                                                                                                                                                                                    |

| Stepping Switch Subassembly       |                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                   | The stepping switch in this subassembly<br>is used to control automatically the se-<br>quential application of the MCV to the<br>logic-package assemblies in a selected<br>row in the OLCU.                                                                                                                                                                                                     |

I

l

1

1

1

I

I

1

1

1

1

I

1

## TABLE 2-3. MCV CONTROLS AND INDICATORS (Cont.)

| Item                        | Function                                                              |

|-----------------------------|-----------------------------------------------------------------------|

| BLOWER FAILURE Switch       | Lights if a blower failure occurs.                                    |

| Indicator Panel Subassembly |                                                                       |

| Rack and Row Indicators     | Light to indicate the rack and row to which the MCV is applied.       |

| ROW STEP Switch             | Used to apply the MCV to each row (one at a time) in a selected rack. |

1

Figure 2-4. OLCU Operator's Panel

## TABLE 2-4. DEVICE AND MODE SELECTION CONTROLS AND INDICATORS

| Item                          | Function                                                                                                                                                      |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Controls and Indicators |                                                                                                                                                               |

| Power ON Switch               | Used to energize the DC power supplies<br>and apply AC power to the peripheral<br>equipment.                                                                  |

| Power OFF Switch              | Used to shut off the DC power supplies.                                                                                                                       |

| AC POWER ON Indicator         | Lights to indicate that AC power is on.                                                                                                                       |

| DC POWER ON Indicator         | Lights to indicate that DC power is on.                                                                                                                       |

| PERIPH ON Indicator           | The PERIPH ON (peripheral on) indicator<br>lights to indicate that power has been ap-<br>plied to the peripheral equipment.                                   |

| MCV POWER ON Indicator        | Lights to indicate that MCV power is being applied.                                                                                                           |

| Operating Mode Controls       |                                                                                                                                                               |

| SINGLE PULSE Switch           | Used to provide the gating levels necessary<br>to gate off the normal pulse distribution<br>system and to provide a single pulse each<br>time it is operated. |

| RUN Switch                    | Used to provide the gating levels necessary for normal operation of the OLCU.                                                                                 |

| SINGLE CYCLE Switch           | Used to provide the gating levels necessary<br>for completion of a single input or output<br>cycle.                                                           |

| Input Media Controls          |                                                                                                                                                               |

| MAG TAPE Switch               | The MAG (magnetic) TAPE switch is used<br>when magnetic tape is to be used for input.                                                                         |

| PAPER TAPE Switch             | The PAPER TAPE switch is used when paper tape is to be used for input.                                                                                        |

| CARD READ Switch              | The CARD READ (card reader-punch)<br>switch is used when punched cards are to<br>be used for input.                                                           |

## TABLE 2-4. DEVICE AND MODE SELECTION CONTROLS AND INDICATORS (Cont.)

| Item                    | Function                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Media Controls   |                                                                                                                                                                                                                                                                                                                                                                            |

| MAG TAPE Switch         | The MAG (magnetic) TAPE switch is used<br>when magnetic tape is to be used for output.                                                                                                                                                                                                                                                                                     |

| PAPER TAPE Switch       | The PAPER TAPE switch is used when<br>paper tape is to be used for output.                                                                                                                                                                                                                                                                                                 |

| CARD PUNCH Switch       | The CARD PUNCH (card reader - punch)<br>switch is used when punched cards are to<br>be used for output.                                                                                                                                                                                                                                                                    |

| LINE PRINT Switch       | The LINE PRINT (line printer) switch is<br>used when the line printer is to be used for<br>output.                                                                                                                                                                                                                                                                         |

| Mode Selection Controls |                                                                                                                                                                                                                                                                                                                                                                            |

| BINARY Switch           | Usually used when input data has been pre-<br>pared in the interpret sign mode.                                                                                                                                                                                                                                                                                            |

| ALPHANUM Switch         | The ALPHANUM (alphanumeric) switch is<br>usually used when input data has been pre-<br>pared in the non-interpret sign mode.                                                                                                                                                                                                                                               |

| HOLL Switch             | The HOLL (Hollerith) switch is used with<br>magnetic or paper tape input when card out-<br>put in Hollerith code is desired. It is also<br>used when cards punched in Hollerith code<br>are to be used as input. In this case, how-<br>ever, the output will be in Fieldata code<br>regardless of whether line printer, magneti<br>tape, or paper tape output is selected. |

| BLKT Switch             | The BLKT (blockette) switch is used to<br>select the blockette mode of operation<br>when using input from either magnetic<br>tape or paper tape.                                                                                                                                                                                                                           |

| VERIFY Switch           | Used when it is desired to operate the OLCI<br>in the VERIFY mode. Use of this mode<br>enables checking of information on the in-<br>put media. No output device is selected<br>when operating in the VERIFY mode.                                                                                                                                                         |

1

1

1

1

### TABLE 2-4. DEVICE AND MODE SELECTION CONTROLS AND INDICATORS (Cont.)

| Item                    | Function                                                                                                                                                                                                                                                               |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blockette Mode Controls |                                                                                                                                                                                                                                                                        |

| MARK Switches (7)       | Used to set up the MARK character when<br>operating in the blockette mode. Only<br>the MARK character is used with paper<br>tape input. With magnetic tape input<br>both MARK and KEY characters are used.                                                             |

| MARK RESET Switch       | Used to reset the MARK switches to the OFF state.                                                                                                                                                                                                                      |

| KEY Switches (7)        | Used to set up the KEY character when<br>operating in the blockette mode with mag-<br>netic tape input.                                                                                                                                                                |

| KEY RESET Switch        | Used to reset the KEY switches to the OFF state.                                                                                                                                                                                                                       |

| Card Input Controls     |                                                                                                                                                                                                                                                                        |

| ONE CARD BLOCK Switch   | Used with punched card input when one card<br>is to be written per block of output.                                                                                                                                                                                    |

| TWO CARD BLOCK Switch   | Used with punched card input when two cards are to be written per block of output.                                                                                                                                                                                     |

| THREE CARD BLOCK Switch | Used with punched card input when three cards are to be written per block of output.                                                                                                                                                                                   |

| FOUR CARD BLOCK Switch  | Used with punched card input when four<br>cards are to be written per block of output.<br>Four-card output can be employed only in<br>off-line control systems which use a card<br>reader-punch which does not have capability<br>for performing a checking operation. |

I

ł

## 2.6.2.3 Operating and Error Checking Section