#### INTRODUCTION

This is a set of notes that is intended to introduce the reader to the H-800 and simultaneously to computer programming. It is intended that these notes will be used side-by-side with the book by McCracken "Digital Computer Programming". Since McCracken (hence forth abbreviated Mc) emphasizes scientific and arithmetic computations, and we are more interested in data processing and data manipulation programming, our examples will have a different emphasis from these in Mc. Likewise, the nature of the Honsywell 800 requires that we depart from Mc's organization in several places, particularly following his Chapter 4. In general, however, we will make the effort to parallel Mc's references to the fictitious computer "TYDAC" with references to the Honeywell 800.

## CHAPTER I.

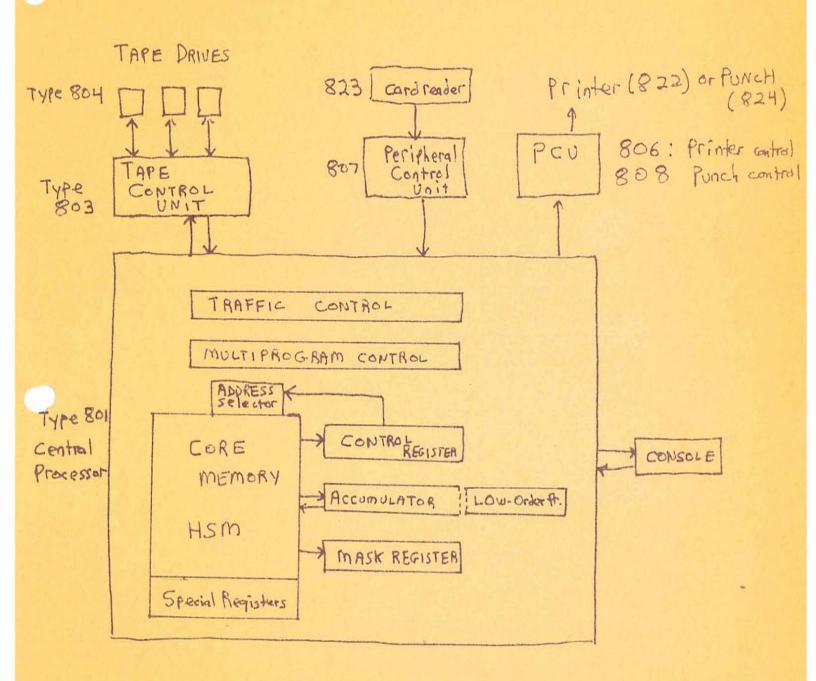

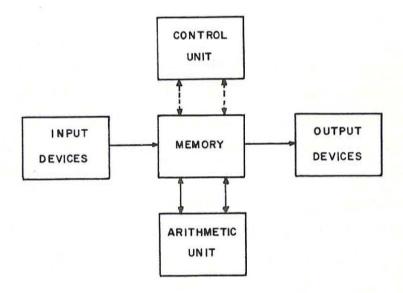

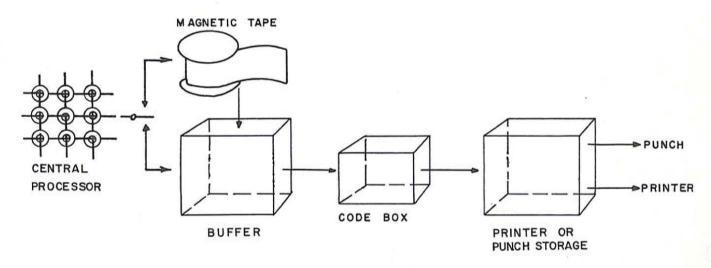

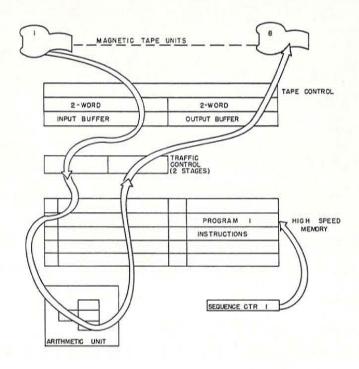

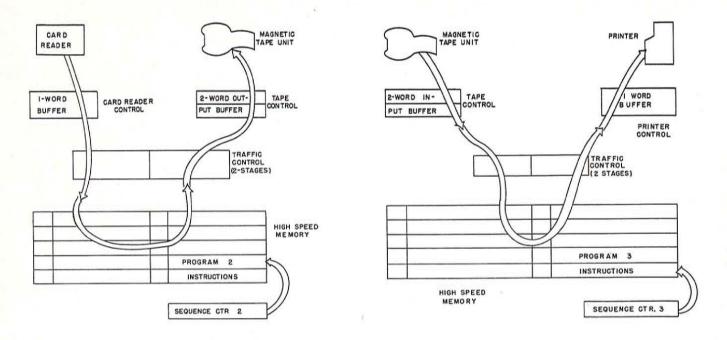

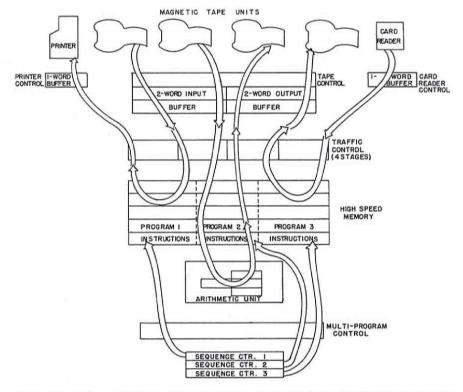

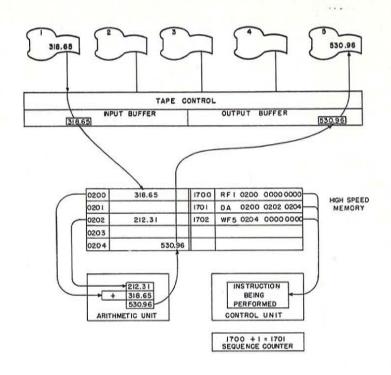

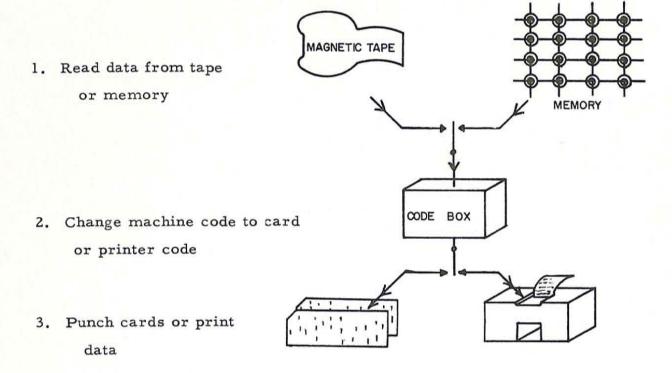

The attached figure is a general block diagram of the H-800 system.

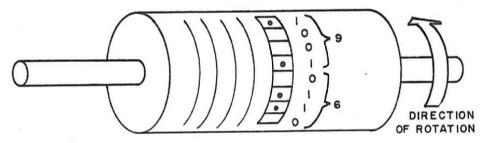

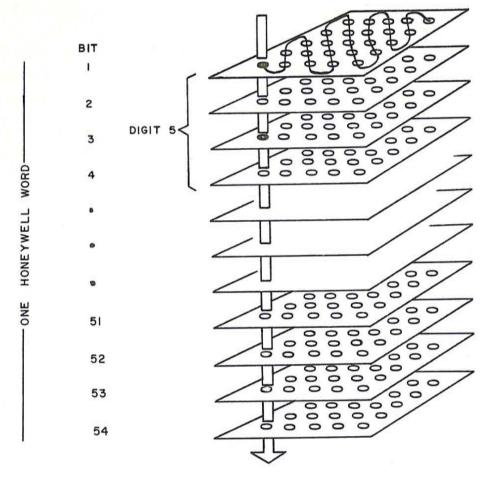

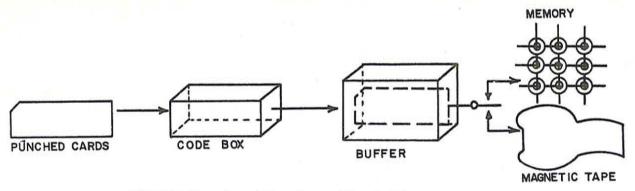

An H-800 system generally includes punched card input and output, console typewriter and line printer output, and magnetic tape units for input, output, and intermediate storage. The memory of the H-800 consists of several banks, a bank consisting of 20h8 words or memory locations. For the time being, we will not consider more than one bank of memory. A word may be made up of an 11 decimal digit number with a sign, 8 alphabetic (or numeric or punctuation symbol) characters, or h8 bits (binary digits) of binary coded information. A word may be either an instruction word or a data word. In addition to the above mentioned memory (frequently denoted by HSM, for High Speed Memory), the H-800 system includes 256 special registers which are used for control purposes. The special registers are divided into 8 groups, each containing 32 registers. We shall only consider one group of 32 special registers. These special registers perform such functions as sequencing counters, indexing and indirect addressing registers, and other specialized central functions.

In addition to these HSM and special register storage locations, the Arithmetic-Control Unit of the H-800 contains certain highly specialized registers that are capable of performing arithmetic and logical functions. These include an Accumulator, a Low-Order Product Register, and a Mask Register. Unlike the TYDAC or other one-address machines, the H-800 is a 3-address machine. For this reason, the arithmetic registers assume far less importance to a programmer than they do in a 1-address machine. (They operate in much the same fashion as they would in a 1-address machine, but their use is implicit rather than explicit).

#### Note to Section lak:

We will point out here that the present "state of the art" is such that "automatic programming" systems are an accepted fact. We will therefore in these notes use symbolic notation. In other words, our examples will be written not in terms of absolute machine language, but in terms of the more symbolic language which can be used by the programmer and which will automatically be translated to machine language by the machine itself. (This, incidentally, is the essence of "automatic", or machine-aided programming).

Similarly, the state of the art with respect to program checkout has advanced. There are presently available automatic aids to assist the programmer in "debugging", or detection of errors in programs which are in the process of being tested on a computer.

The ARGUS system for the H-800 incorporates all these features: automatic translation and memory assignment to allow the writing of programs in a convenient symbolic language, automatic program testing facilities, and automatic maintenance of files of programs, thus relieving the individual programmer of the responsibility of maintaining his own reel of tape or deck of cards; also increasing the efficiency of machine utilization by permitting automatic batch checkout of programs in a single program testing run.

#### CHAPTER 2. CODING FUNDAMENTALS AND INTRODUCTION TO H-SOO

14

It is suggested that the reader read Chapter 2 of Mc to become familiar with some of the basic ideas contained therein, remembering, however, that the structure of the M-800 differs considerably from the structure of the TKDAC, which is the specific machine to which Mc's examples refer.

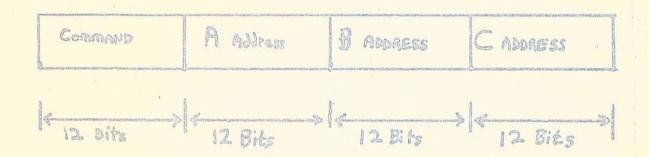

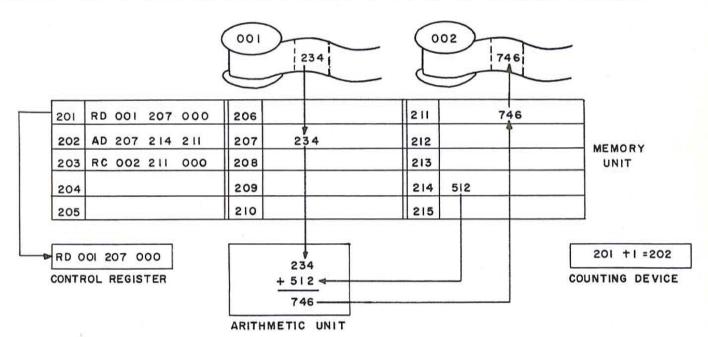

The most significant difference between the TYDAC computer and the H-800 is that TYDAC has a single-address command structure, while the H-800 is a 3-address machine. Consider the illustration near the top of p. 15 of Mc. A similar fillustration to describe the H-800 instruction word format is shown here:

Several points can be clarified in reference to this figure.

First of all, the term "bit" is a contraction of the words "binary digit".

Just as a decimal digit may assume one of the 10 values between 0 and 9,

a binary digit may assume one of the 2 values 0 or 1. This subject will be

covered in detail in Chapters 3. It is sufficient to note at this point that

a word is divided into h parts or fields of equal size. The fields each contain

12 bits, and are known as the Command field, the A Address Field, the B Address

field, and the C Address field. The Command portion of the instruction tells

the machine what to do when it operates this instruction. The address fields

are used to specify what memory locations are used as sources of operands or

destinations of results in the course of executing the instruction. In any

one address field, it is possible to refer to any one of the 2048 words in one bank of RSM. In addition, other techniques may be used to code the address fields. This will be covered in more detail later.

Example 1 (p. 15) illustrates the TYDAC coding to perform the operation of adding two numbers together and delivering the result to a 3rd memory location. The following example illustrates the same operation in

H-800 coding:

COMMAND AAOORESS BADDRESS CADDRESS ABC RES XYZ DA

Contents of XYZ: before - + 1

Operation:

ABC before - +92 These registers are left unchanged by this operation.

Contents of RES before - - 123456789 after + 93

Note that, as in Mc's example 1, the previous contents of the result location (identified here by the symbol RES) are destroyed by the operation. This order has been written in symbolic form. The first field (command field) contains DA, which is the memonic operation code for the order, "Decimal Add the contents of A to the contents of B and send the result to C". The subsequent 3 fields are the A, B, and C address fields of the order. The symbols, or tags. "XYZ" "ABC", and "RES" are symbolic names assigned to particular memory locations. The numeric identification of these memory locations need not be of concern to the programmer. The addition operation is algebraic. Thus, if XYZ had contained a -1. the result would have been the algebraic sum of -1 and +92 or +91, even though the operation code was "ADD".

Example 2 illustrates a more elaborate computation (this does not correspond to Mc's Example 2).

Assume that we are in the midst of calculating an employee's payroll, and it is necessary to evaluate the following quantity:

U · V - W - D - E.

Where: I is Normal Gross pay

V is Overtime pay

W is Federal Income Tax With-holding

D is FICA (Social Security)

E is State With-Holding Tax

We wish to deliver the result of this computation to a memory location to which we have assigned the symbol NETPAY.

The following & H-800 orders will perform this computation:

| COMMAND | Pi I | 8  | C      |

|---------|------|----|--------|

| DA      | Ū    | V  | TEMP   |

| DS      | TEMP | P9 | TEMP   |

| DS      | TEMP | D  | TEMP   |

| DS      | TEMP | E  | WETPAY |

Note that in addition to the symbols previously mentioned, a new symbol, TEMP, has been used. Following the first operation, the memory location TEMP contains the sum of U and V. Following the 2nd operation, a DECIMAL SUBTRACT order, the contents of TEMP have been diminished by the contents of W, and put back into TEMP. The 3rd takes away some more; the 4th operation does also, but delivers the result to NETPAY. In case anyone is interested, the location TEMP now contains the quantity U + V - W - D (which would be your net pay outside of Massachusetts). However, this location is now free and may be used as a temperary storage location for any other type of computation that it is desired to perform.

We shall, for the time being, emit discussion of multiplication and division and proceed to Example 6. (p. 25)

#### DETERMINING THE LARGER OF 2 NUMBERS.

The H-800 orders include h comparison orders. We shall consider here the 2 orders: NN (Inequality comparison, numeric) and LN (Less than or equal comparison, numeric). This example illustrates the use of the less-than or equal numeric comparison:

| COMMAND | phi-   | B | CI |

|---------|--------|---|----|

| INT     | HETPAY | X | Q  |

Where in memory location X we have the number O.

## This order operates as follows:

The contents of A (the word at the location specified in the A address field, also denoted by (A)) - in this case (NETPAY) - are compared with (X), or in this case, zero. If (A) is less than or equal to (B), a jump,

or sequence change will take place. If (A) is greater than (B), the next order will be taken in sequence. Thus, if we find ourselves executing the order at Q, we know that the poor fellow has managed to pile up more payroll deductions than he is able to handle. Likewise, the NW order will make a jump to the location specified in the C address field if and only if the 2 quantities (A) and (B) are not equal.

Section 2.5. It is appropriate to mention here the speed of the H-800 for comparison purposes.

To put our numbers on the same basis as those in Table 1, we must remember that the H-800 is a 3-address machine, and the machines tabulated are 1-address machines.

For instance, the "magnetic core, scientific, binary" machine of the right-hand column is capable of doing 40,000 single address orders per second. This corresponds to 16,667 3-address additions per second as illustrated in Mc's example 1. The H-800 is capable of doing 40,000 3-address additions per second. (Our example 1).

#### SUMMARY OF SELECTED E-800 OPERATION CODES:

| DA<br>DS<br>MH   | A<br>A<br>A | B<br>B | G<br>G | Decimal Add (A) to (B); send result to C.  Decimal Subtract " " " " "  Inequality Humeric comparison of (A) and (B).  Jump to C if Inequality condition is found.                             |

|------------------|-------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAV              | A           | B      | C      | Less than or equal comparison of (A) and (B).                                                                                                                                                 |

| TI<br>TIS<br>TIS | A<br>A<br>A | B      | 6      | Transfer (A) to C. (NOTE: B is ignored in this order) Transfer (A) to B and Jump (unconditionally) to C.  Move n words from memory locations starting at A to memory locations starting at C. |

#### EXAMPLES - CHAPTER 2.

1. It is desired to test the numbers at MA, MB, and MG. To the register denoted by ZCOUNT we want to deliver a count of the number of zero items. Assume that we have stored the following constants:

ZERO + O

ONE + 1

The following coding will accomplish the desired result:

| LOCATION | COMMUND        | A B                             | O                         | EXPLANATION                                                                      |

|----------|----------------|---------------------------------|---------------------------|----------------------------------------------------------------------------------|

| BEGIN    | TR<br>MW<br>DA | ZERO -<br>KA ZERO<br>ZGOUNT ONE | ZCOUNT<br>Q2<br>ZCOUNT    | Initial setup.  Te the first one pero? If not, yes - add 1 to ZCOUNT, jump to Q2 |

| Q2       | IN<br>DA       | XB ZERO<br>ZCOUNT ONE           | Q3<br>ZCOUNT              | Test 2nd number                                                                  |

| Q3       | NA<br>NA       | XC ZERO<br>ZCOUNT ONE           | Ql <sub>4</sub><br>ZCOUNT | Test 3rd number                                                                  |

| QL.      | ond.           |                                 |                           |                                                                                  |

Mote that we have written the orders in a format similar to that of the H-800 ARGUS coding form, and that we have in certain cases entered a symbol in the location field. It is not necessary to name or otherwise identify every order, so we have only named those orders which we refer to explicitly in our jump instructions, and the first order of the coding.

## Prample 2.

Evaluate the quantity 2x - y, where x is stored at 7FOD; y at 151MS. The result is to be delivered to 38IS.

One may to do this would be to multiply x by 2. However, a much faster may in this instance would be to add x to itself. Therefore, the following 2 orders will do the job:

| DA | 7500 | 7FOD  | TEMP |

|----|------|-------|------|

| DS | TRMP | 151NS | 38LS |

Again, we have used a register for intermediate storage of the quantity 2x. We can avoid this by using this alternative scheme:

| DA | 7FOD | 7FOD  | 38LS |

|----|------|-------|------|

| DS | 3818 | 151NS | 38LS |

#### Example 3.

We have stored in memory certain information relating to the time it takes to get from here to Florida on two different airlines. We wish to program a selection of that airline which will get us there first. At location TWA, we have the arrival time for the first airline; in the following 3 registers there is other information such as flight number, etc. In h memory locations, the first of which is UNITED, we have similar information for the other airline. It is desired to move these words for the selected airline to h memory locations starting at FASTEST.

The following coding will do the job. Assume that upon completion of this routine, an unconditional jump to the order at GETSEAT is to be made.

|        | TAT | TWATED | THA<br>Li | TPIRST<br>FASTEST |

|--------|-----|--------|-----------|-------------------|

|        | TS  | W      | 194       | GETSFAT           |

| UFIRST | TN  | UNITED | L,        | FASTEST           |

|        | TS  | **     |           | GETSEAT           |

Note that the TN order allows us to move the 4 words with just one order. (The order can be used to move from 1 to 63 words at a time).

Note also the hyphens in the A and B fields of the TS order. Since all we wish to do is make a jump, we are not interested in transferring one word. Therefore, the hyphen indicates that the address is an inactive address, and that we wish no processing to take place on its account. Certain H-800 orders take on special significance when some of their addresses are inactive; these examples will be covered later. This use of the TS order is a particularly simple one.

## CHAPTER 3 - Number Systems

The H-800 includes automatic coded decimal arithmetic operations. It can, however, also operate inthe binary number system, and can process individual bits of a machine word. It is therefore desirable that H-800 programmers become familiar with the fundamentals of the binary system.

Table 6, on Page 47, shows the Binary Goded Decimal system that is actually used in the H-600. Our figure, Table 6-a, illustrates the complete set of 4-bit codes known as hexadecimal notation. Notice that the first 10 entries here are identical with Table 6. The other 6 entries assign convenient (although somewhat arbitrary) names to the other 6 possible combinations of 4 bits. When it is desired to specify aribitrary binary quantities, but do not want to have to write out the individual 48 bits of a word. It is frequently convenient to use these hex codes for the 4 bit groupings. In the H-800, the programmer may use either hex or octal (3-bit groupings) notations.

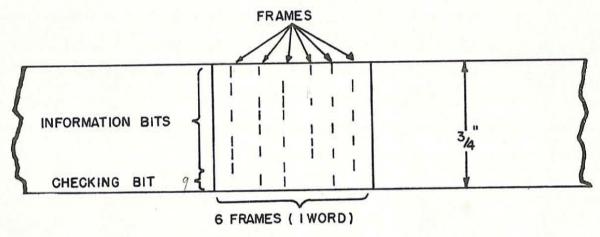

At this time, it is appropriate that we discuss in somewhat more detail the composition of an H-800 word. As mentioned before, an H-800 word can consist of il decimal digits and a sign, 8 alphabetic characters, or h8 bits of binary data. We use a code which requires h bits per decimal position. Il digits, therefore, require hh bits of the word. The remaining h bits are used to specify the sign of the word. If the sign position is 0 (all h bits are sero), the word is treated as a negative quantity in arithmetic operation. Otherwise, the word is treated as positive. The result of an arithmetic operation will have a sign which is either 0 or G (all ones). It appears as if this sign rule is more complex than actually necessary, but the reason will become more evident later.

Figure 3-b shows the binary and hexadecimal representations of the operands in our old example 1, adding 1 to 92.

| TABLE 6-a                              | HEXADECIMAL HOTATION                                                                                       |

|----------------------------------------|------------------------------------------------------------------------------------------------------------|

| 8 4 2 1                                |                                                                                                            |

| 00001010101010101010101010101010101010 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>8 (10)<br>0 (11)<br>0 (12)<br>E (14)<br>0 (14)<br>0 (15) |

## FIGURE 3-b

| (XYZ): | 3332<br>0 | 0000 | 0000 |  | 0000 | 0000 |  |      | 0001 |

|--------|-----------|------|------|--|------|------|--|------|------|

| (ABG)s | G<br>3111 | 0000 | 0000 |  | 0000 | 0000 |  | 1001 | 0010 |

The H-800, as mentioned above, is able to operate in either the binary or the decimal system. The following example illustrates a binary addition example, using the operation BA (Binary Add), and her notation for binary numbers.

BA

| Where:<br>(ALPHA):              | Q. | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prof. | G | (Binary representation of<br>the number 31) |

|---------------------------------|----|---|---|---|---|---|---|---|---|---|-------|---|---------------------------------------------|

| (BETA) :<br>The result will be: | G  | 0 | 0 | 0 | 0 | 0 | 0 | O | 0 | 0 | 0     | 7 | (Binary representation of 7)                |

|                                 | C  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 2     | 6 | (Binary representation of 38 - verify this) |

So far, we have seen examples illustrating numeric and binary H-800 words. It was mentioned above that a word can also be used to store 8 alphanumeric characters. This is done by using 6-bit groupings within the the word, each group or code representing one of the characters in the word. The following code is used:

|                              | T             | ABLE 6-C    |                       |                  |          |

|------------------------------|---------------|-------------|-----------------------|------------------|----------|

|                              | FIRST 2 BITS: | 00          | 01.                   | 10               | 2.1      |

| Next & bits                  |               |             |                       |                  |          |

| 0101<br>0100<br>0011<br>0010 |               | 12345       | A<br>B<br>C<br>D<br>E | J<br>K<br>L<br>M | /s T U V |

| 1000<br>0111<br>0110         |               | 6<br>7<br>8 | F<br>G<br>H           | 0<br>P<br>Q      | W<br>X   |

| 1001                         |               | 9           | I                     | R                | Z        |

In addition, other codes are used for punctuation marks, etc. For instance, the code for "space" is 00 1101.

As an example, consider the 8 letter word SUNSHINE.

It is represented in the binary code as follows:

DE 972 619 955

There is no distinction made inside the machine between any of the various types of words. Of course, when a decimal add order refers to a particular word, it assumes that it is working with a decimal number. When a word is to be printed in 6 bit alphabetic form, it is treated as 8 6-bit characters. If a mistake were

made, and a decimal number were used instead, 8 characters would still be printed, and would probably look like gibberleh. It is important to realize, therefore, that the distinction between the various types of words is a programmed distinction, and that the programmer or systems analyst would have control over this. Thus, an item may consist of mixed alphabetic, numeric, and binary coded information. An example would be a payroll record, where alphabetic words would be used for name, numeric words for pay rate and hours worked, and certain coded information stored in the individual bits of a control word. (For example, one bit might be 0 for male, and 1 for female).

## TYPICAL H 800 SYSTEM DIAGRAM

## NOTES:

- 1. CORE MEMORY IS EXPANDABLE (Type 802)

- Z. UP TO 8 TAPES MAY BE CONNECTED TO ONE TOU

UP TO 8 TOUS OF POUS MAY BE TIED IN.

- 3. OTHER TYPES OF PERIPHERAL DEVISES ARE ALSO AVAILABLE.

57-47

13

## CHAPTER L.

Me, Chapter h, is on decimal point positioning problems. It is suggested that this chapter be read; we will not, however, specifically cover the problem in these notes.

The H-800 includes several operations of the type commonly known as logical operations. These operations are not arithmetic or simple transfer orders, but rather operate on the individual characters (or bits, if desired) of an H-800 word.

The first of these orders is the extract order,

EX A B C

The effect of this order is to generate a word based on the contents of A and B, and deliver this word to C. The rule for forming the result is to make every bit zero except where both (A) - (a notation for "contents of A") and (B) have bits which are one.

EXAMPLE 1:

EX BB EC BD

Where:

Then BD will be:

The word at BC, in this case, is an extractor control word that allows everything to get through except the low order character. Note the application of this to rounding a number.

(AE) = \* 00 000 000 005

Then the following orders will round the word at QRT, discarding the low order digit - assume that (QRT) is always positive.

DA QRT AE TEMP EX TEMP BC RESULT

## (Chapter & continued)

The two comparison orders, NN and LN have already been covered.

The H-800 has 2 additional comparisons. NA (compare for inequality alphabetic) and LA (less than or equal compare, alphabetic). The term alphabetic is somewhat of a misnomer here, for, while these are the orders to be used when testing alphabetic data, it is more appropriate to describe them as word comparisons. The NA order will result in a jump if any of the 48 bits of the 2 operands are different. Note that, if this order is used, it is possible to distinguish between -0 and to. The LA order considers the 2 operands as 48 bit binary numbers. If (A) is less than or equal to (B), in this sense, the jump will take place.

Note the following example:

#### EXAMPLE 2:

(MINA): -00 000 000 000 008 (MIN8): -00 000 000 008

The comparison IN MINA MIN8 LESS

will fail (not jump) since -h is numerically greater than -8. However, if we remember that the h bit sign for a minus sign is 0000, and examine the two words, we see that the comparison

#### LA MINL MINS LESS

will succeed, since 600 000 000 000 is smaller than 000 000 000 008 (hexadecimal representation of the 2 binary numbers). Beware: it is generally a safe practice to use alphabetic comparisons unless it is known that signed numeric quantities are involved.

#### EXAMPLE 3:

It is desired to jump to JKL if the low order character of the word at GROAN is Z. The word at GROAN is an alphabetic word.

(TESTLO6) : 000 000 000 030 (her.)

Note that this word has ones in the low order 6 bits, and 00s elsewhere.

(LOZ): CO 00 CO OZ (alphabetic); zeros except for the Last character

EK GROAN TESTLO6 TEMP

HERE NA TEMP LOZ HERE\*2

The substitute order (SS A B C) is more complicated, in that it will deliver to C a word that may depend upon the previous contents of C.

The algorithm for this order can be stated as follows:

Wherever there is a 1-bit in (B) replace that bit position of C by the contents of the corresponding bit position of A.

Wherever there is a O bit in (B), do not disturb the bit of C.

EXAMPLE L: SS ASDFG HJKL CEE

perores

(CHE) : 0000 0000 1111 0000 0000 0000 1111 0000 0000 1111 0000 1111

Note that the contents of C are protected (i.e. left alone) where (B) has zero bits, while in the extract order, the write 1000 C is destructive; i.e. those bit positions are not protected.

Two more orders will/briefly mentioned:

Superimpose (SM A B C ).

Generate a word that consists of one-bits wherever either (A) or (B) or both has a 1 bit; where both (A) and (B) have zero bits, the generated word has a zero bit. Deliver this word to C.

Half-add ( HA A B C ).

Generate a word that has one-bitsin those positions where the bit of (A) differs from the bit of (B); zeros where (A) is the same as (B). Deliver this word to C.

One application of this order, which is also known as Add without Carry, or symmetric difference, is to change every bit of a word (this is known as complementing the word). This can be done by half-adding the word to a word of all ones. The verification of this is left as an exercise to the reader.

Note that all the above orders except SS are commutative with regard to A and B.

CHAPTER 5 SHIFT ORDERS:

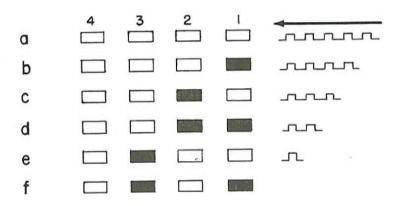

The H-800 has one type of shift order; shift one word right and around the end. There are h variants of this order. By end-around shift is meant the following:

Consider the following word -

012 345 678 9EC

If we shift this word right, end around by h bit positions, we get:

COL 234 567 89B

If we shift the original word right, end around, bl bit positions, we get:

123 456 789 BCO double 012 348 278 9 20

Note that this is identical to what we would get if we were able to shift the word left h bits.

In general, the information that comes around the end is of no great value to the programmer. In order to allow him to discard it easily, the shift orders incorporate "mask control". A mask address is specified as part of the shift order. The operation of the order is first to perform the indicated shifting, and then to deliver the shifted word to C under mask control. This may be of 2 varieties; protective masking, or extracting masking.

The other variants on the shift order are accounted for by the fact that it is possible to exclude the sign position of the word from shifting, if desired.

The 4 operation codes are:

SWS Shift Word and Substitute into C

SPS Shift, Preserving sign, and Substitute

SWE Shift Word, Extract to C

SPE Shift Preserving sign, Extracting to C

The format of the order as written by the programmer is:

SER, M A n G

## (Chapter 5 continued)

M is a symbol that refers to a mask. It is set off from the operation code by a comma, but written in the command field. This is one instance of the symbolic language varying slightly from the machine structure of the word, for the mask information is actually partially specified in the B field of the machine word. In indicates the number of bits of shifting that is desired. It may take on any value between zero and h8, inclusive. If preferred, it may be written as A, I (for alphabetic characters) or D, s (for decimal numbers). In this case, r is the number of 6-bit character positions, and s the number of h-bit characters to be shifted. The following 3 orders are identical in their operation and in their machine form:

| SWE, COH | X | 12  | Y |

|----------|---|-----|---|

| SWE, CGH | X | A,2 | Y |

| SWE, GOH | X | D,3 | X |

EXAMPLE 13

Evaluate O.1 SYA - SYB; deliver the result to SYN

SPE, XA SYA D,1 TEMP DS TEMP SYB SYN

Where the SHIFT MASK, XA is:

S, XA

GOG GGG GGG GGG

Note that this mask has a "hole" in the position where the digit we threw away in the shift comes up in the word as shifted end around.

EXAMPLE 2:

Evaluate 10 SYB - SYG; deliver result to SYP

SPE, XB SYB D, LO TEMP DS TEMP SYC SYP

SaxB

age age age age

· what happen to the high evelor spor.

Note that the numeric shift shifts hh bits of the word, leaving the h bits in the sign position undisturbed. Thus, a shift of 10 numeric places right brings everything around one digit position to the left of where it was originally.

The other 2 instructions, shift word, operate in the same fashion except that they treat all 48 bit positions of the word alike.

#### EXAMPLE 3.

At NUM is the word 000 Cd<sub>1</sub>d<sub>2</sub> d<sub>3</sub>d<sub>4</sub>d<sub>5</sub> d<sub>6</sub>d<sub>7</sub>d<sub>8</sub>. It is desired to convert this word to its alphanumeric equivalent for printing and deliver the result to ALPHA.

| EX<br>SWS,MI<br>SWS,M3<br>SWS,MI<br>SWS,MI<br>SWS,MI<br>SWS,MI | MUM<br>MUM<br>MUM<br>MUM<br>MUM<br>MUM<br>MUM | IOW4<br>46( -<br>44<br>40<br>38<br>36<br>34 | ALPHA ALPHA ALPHA ALPHA ALPHA ALPHA ALPHA ALPHA ALPHA | q <sup>5</sup><br>q <sup>1</sup> |

|----------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-------------------------------------------------------|----------------------------------|

| SWS,MJ<br>SWS,MS<br>SWS,M6                                     | NUM<br>NUM<br>NUM                             | 40<br>38                                    | ALPHA<br>ALPHA                                        |                                  |

#### Where

#### CHAPTER 6. INDIRECT ADDRESSING TECHNIQUES

Thus far we have seen the use of simple symbolic addresses to refer to specific fixed HSM locations. We have been able to handle simple examples, but we would not be able to add up 100 numbers without writing down 100 add orders, which rapidly leads to writer's cramp, and becomes impractical if the quota is 1500 numbers instead of 100. Actually, this process is one that is quite easily adapted to computation, by means of a loop.

Consider the following abstract statement of the job:

- 1. Set i to sero.

- 2. Set SIGMA to zero.

- 3. SIGMA + N into SIGMA 4. i+l into i.

- If i is less than or equal to 99, go back to 3.

Clearly, this procedure will suffice to add up the 100 numbers No. - Noo. All that remains is to indicate how we can actually do this on the H-800.

The block diagram of the H-800 with Chapter 1 indicated that the memory included both HSM and some "Special Registers". It is these special registers which can be used for indirect addressing, in addition to being used for certain control functions. (For instance, the sequence counter is actually nothing more than one of the special registers). These special registers may be addressed directly, just as HSM memory locations. In addition, they may be used for indirect addressing; meaning that the actual HSM location involved is specified by the contents of the designated special register. It is useful to define a special type of constant for this use; this is the SPEC constant. Only the A field of this is used; in it is written the symbolic address desired to be used.

To refer to a special register explicitly, the code "Z", is used, while the code "N", is used to perform indirect addressing. The comma is followed by the designation of the special register, which may either be absolute numeric or literal.

There are 32 special registers that are easily accessible at any one time; they constitute a group. At present, we shall not consider more than one group.

We shall use the "general purpose" special registers RO - R7 (16 - 24).

EXAMPLE 1. The 2 orders:

TX ADCON Z,RO N.RO TAX

Where

ADCON:

SPEC

POTS HORSE FICH INTO ADCOM

Have the same effect as the single order:

DA FICA TAX DEDNS

EXAMPLE 2. We will now take a crack at adding up the 100 numbers that are stored in consecutive memory locations starting with the location whose symbolic address is N.

| S | TEPL | TX · | KJ.    | 68.    | COMMER | ANTR OF D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|------|------|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | TEP2 | TX   | 767    |        | SIGMA  | 14 3735 AND 11 "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | TEP3 | WA   | BASEAD | COMMIR | Z,RO   | add good to all the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |      | DA   | SIGMA  | N,RO   | SÍGMA  | and you to contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | TEPL | WA   | CNTR   | KS     | CNTR   | Service and the service and th |

| S | TEP5 | LA   | CNTR   | K3     | STEP3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Where:

KI DEC K2 DEC 000 000 000 001 E3 0000 0000 0000 0113 OCT (binary 99) BASEAD SPEC N A DUCK ADDRESS OF N INTO BASEND

Note the use of the Word Add order on the unsigned quantities involved in the control computations.

This example can be improved upon; the location CNTR can be abolished by directly incrementing the contents of RO.

| STEP1 | TX  | BASEAD | ent.  | Z,RO  |

|-------|-----|--------|-------|-------|

| STEP2 | TX  | Kl     | ess   | SIGMA |

| STEP3 | DA  | SIGMA  | N,RO  | SIGMA |

| STEP4 | WA. | Z.RO   | K2    | Z,RO  |

| STEP5 | I.A | Z.RO   | ENDAD | STEP3 |

Where

ENDAD SPEC N+99

and we have gotten rid of K3.

We can still further improve on this example by taking advantage of another feature of special registers. This is the automatic incrementing feature. As a special register is used, it is possible to increment it for subsequent use. The size of the increment may be between zero and 31. Thus far, we have used zero increments, and have not needed to specify them. If an increment is desired, it is written, with a 2nd comma, following the special register address. Thus, N,RO,1 in an address field specifies indirect addressing with RO, incrementing it by 1. It is important to remember that the effective address (that is, the contents of the special register) is not incremented for the current reference. Instead, the incrementation takes place immediately after the use of the original contents of the special register.

Thus, the 2 orders

TX BASEAD - Z,RO EX N,RO,29 B C

will use the word at N as an operand in the extract order, and not the word at N+29. However, RO now contains:

SPEC N+29

We can apply this principle to our example, and eliminate STEPh.

STEPL TX BASEAD Z,RO TX STEP 2 KI SIGMA STEP3h DA SIGMA N.RO.l SIGMA STEP5 I.A Z,RO ENDAD STEP34 It would be equally satisfactory to increment RO in the reference STEP5.

The one case where incrementing never takes place is when a word is delivered to a special register. For instance,

TX WIGGLE - Z,RO,22 ??

puts the contents of

WHITE

WIGGLE SPEC GROSSPAY

and not GROSSPAY \* 22 in RO. This applies only to direct addressing of special registers, of course.

There is also available in the H-800 another variety of indirect addressing. The 32 special registers in one group include 8 registers known as index registers (denoted by KO - X7 or decimal addresses 8 - 15). These registers may, if desired, be used as indirect addressing registers (ex. N, X2, 1).

They may also be used in a somewhat different fashion. Generally that the index register is capable of storing an address. It is possible, in indexed addressing, to refer to the word at the address specified, or to the word at the address resulting from the addition of the address in the index register to an augmenter stored in the order.

Indexed addressing is denoted, in ARGUS language, by writing the number of the index register, followed by a comma. The comma may be followed by the augmenter.

Examples: 3, 5.2

The operation of the augmenter is different from the operation of incrementers in special register addressing. In the first place, the augmenter is used in calculating the effective address. Also, the augmenter does not affect the contents of the index register. The cappacity may be as large as 254.

We can illustrate the use of index registers by considering the example on page 8 of these notes. Assume that it is desired to indicate to the routine at GETSEAT which mirline we have selected, and that the routine at GETSEAT is going to add the 4th word of the item for the selected item to a word called COST.

Then we could do this:

|        |         | IN   | UNITED | TWA   | UFIRST  |

|--------|---------|------|--------|-------|---------|

|        |         | TS   | AWFA   | Z, X2 | CETSEAT |

|        | UFIRST  | TS   | AUNET  | Z, X2 | GETSEAT |

| stante | ATWA    | SPEC | TWA    |       | -3      |

|        | 2 AUNTT | SPHC | UNITED | 201   |         |

|        | GETSEAT | DA   | COST   | 2,3   | COST    |

| atanto | AUNTT   | SPEC | UNITED | 2,3   | COST    |

Note that, in order to put a word into an index register, we must address it by special register address, but to use it for indexed addressing, we use the 2, type notation. Note also that if we want to refer to the 4th word of the item, we must use an augmenter of 3, since it is the 3rd word following the first word of the item.

Unlike indirect addressing by special registers (N, type), indexed addressing may be used in any H-800 order. It is frequently a useful programming technique to use an index register for indexed addressing in part of a routine, and for special register indirect addressing elsewhere in the routine. Note the following scheme for processing 10 word items, where it is desired to go to NHWBATCH after every 12 items have been processed. The processing refers to the 2nd, buth and 5th word of the items. The 12 items are stored in consecutive memory locations starting with BASEAD.

| BEGIN   | TX  | KIL  | 40.0     | Z,X3     |

|---------|-----|------|----------|----------|

| PROCESS | 35  | 3,1  |          |          |

|         | 200 |      | 3,4      |          |

|         | K   | 3,3  |          |          |

|         | LA  | K2 - | Z, X3,10 | NEWRATCH |

|         | TS  |      | *        | PROCESS  |

Where:

K1 SPEC RASEAD K2 SPEC BASEAD \* 110

Note that, when we get to NEWEATCH, the number in X3 has overshot, since the incrementation by 10 takes place regardless of the output of the comparison. Note also that careful analysis is required in choosing a combination of comparison orders and comparison constants for termination of the loop. In this case, the following analysis applies:

The last item starts at HASEAD + 110. Therefore, when we have finished processing it, X3 will still contain its address. The use of the LA comparison will fail as long as HASEAD + 110 (K2) is greater than the base address of the item just processed. When it succeeds, we will break out of the loop.

Note an alternative solution for the last 2 orders:

NA KE Z,X3,10 PROCESS

TS - NEWBATCH

Company Trivata

# Inter-office Memo

DVATVALUNGGIGG

J. Thomas

Systems .nalysis Department

1123-658

| D5. |    | June | 8, | 1959 |  |

|-----|----|------|----|------|--|

| €.  | €. | TO:  |    |      |  |

SUBJECT:

TO\_

FROM.

Attached are rough notes intended to up-date the H-800 Introductory Lecture Notes.

ADDENDA, REVISIONS and RESTATEMENTS to an incomplete copy of the H-800 Introductory Lecture Notes. June 2, 1959

Multiply

DM & B & 8

High order product to 8 (and in acc.) UNROUNDED

LO product in LOP

to get it: The Can't be to be to be to get it: The Can't be

3-/-6

Shift Orders: Example 6

SWS, mask A M C

Mask Index Register: MASKBASE 61, 0 3

SWS, 20 1200 12 1438

p. 3-1-14

IXs

INDEXED INSTRUCTIONS

Example 17 (Bank 1)

Contents of: X1 SPEC, EL 0183

X2 SPEC, B1 0951

x3 SPEC, BL 1033

BM 1,0 2,5 3,11

OX

1,

Multiplies (183) (951 + 5)

= (956) (1033 ÷ 11)

= (lohl)

Contents of XL, X2, X3 do NOT change.

#### COMPARISONS

Numeric comparisons should not be used on SPEC constants. The sign bit in these constants has special significance only in the circuitry of the special registers. It does not constitute a numeric sign. All words from special registers will be treated as negative, since zeros are always present in the high order h bits.

S/C bit is the HIGH ORDER bit of the word. Blank or S for sequence

C for cosequence

The example on page 3-5-h (Figure 2) is WRONG. The instruction at location 190 will pick up the next order from CSC regardless of how the comparison comes out. Thus, the order at 583 (?) might be executed instead of 191 if  $A=B_0$

#### TRANSFER

3-46-2

TX

Transfer contents of A address to location specified by C address; ignore B.

TS

Transfer contents of A address to location specified by address.

The Caddress portion will replace the contents of the sequencing counter unless the Caddress is left blank, in which case the sequencing counter will not be changed.

#### Select Instruction

3-7-2

SSL, Mask A M. C

The mask must be of the form

OOOO ----OXXX XXXX XXXX

High order 37 Low order 11 bits = bits must = 0. desired mask

## Special Registers:

3-10-1

Example of coding indicating ARGUS Maskgroup process.

MASKGRP, 1

| Loco                | Command     | A            | В      | C   |  |

|---------------------|-------------|--------------|--------|-----|--|

| F <sub>5</sub> HALF | DEC         | GGG          | GGGOOO |     |  |

| Fo GEE              | DEC         | 0000         | 000000 | 000 |  |

| S, 3 NUMR           | DEG         | GOOOGGGGGGG  |        |     |  |

| So 3 NUML           | DEC         | aagaagaaaooo |        |     |  |

| S, SIX              | DEC         | 00000000030  |        |     |  |

| Z, MIR              | MASKBASE, 1 |              |        | ĕ   |  |

|                     | WAs GEE     | X            | Y      | Z   |  |

|                     | SSL, SIK    | Q            | 0      | R   |  |

The MASKBASE constant takes care of both base addresses for the MIR. The MASKS are automatically located in suitable memory spaces by virtue of the "F," or "S,", and the use of the mask tag in the command field quarantees that the proper subaddress will be provided.

## History Registers:

3-10-3

We have a subroutine starting at Y which is entered from several places in the program. The bisequence mode cannot be used in this case.

To get to the subroutine:

(三) (三) TS X Contains Sequence History SPEC X + 1 Y. TX. Z, SH - Temp Process sides and PRE-023 TX Temp - Z, SC 030 TS TETP Z, AUA N, AUA

3-10-7

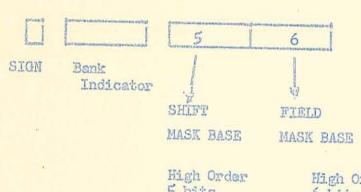

High Order High Order 5 bits 6 bits of an address of an address

This constant can be specified as follows:

X

MASKBASE

X is the base address of type S masks. Y is the base address of type F masks.

T

Use of Special Registers:

#### DIRECT ADDRESSING

3-10-13

Z, Tr. AA

rr may be decimal 0 = rr = 31

or literal (SC, X3, etc.)

ΔΔ may be decimal 0 4 ΔΔ 431.

Z, rr is sufficient.

Special register addresses are to be considered as follows:

ONE of 256 Special Registers.

256 = 8 x 32

8 groups; which one is determined by the Identification number of your Sequence Counter.

32 special registers in a group.

#### INDIRECT ADDRESSING:

3-10-17

Like direct, but No rr, AA

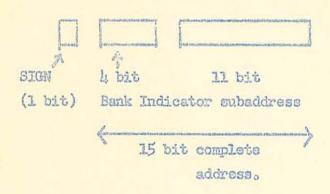

The effective address is the full address (including bank indicator) which is stored in the designated special register.

#### Examples:

(GO) = SPEC, BO 1000

(G1) = SPEC, BO 1500

(1000) = +00 111 222 333

(1500)= +00 111 111 111

DA No GO No G1 1200

puts in 1200 +00 222 333 bld

#### INDEXED ADDRESSING:

is re-

3-10-20

may be:

(a) numeric (0 ≤ - ≤255)

blank & 0

(b) symbolic - defined elsewhere by EQUALS.

Example:

GROSSPAY EQUALS 100

DA 3, GROSSPAY

is a DA 3,100

SPECIAL REGISTER INDEXED

MK is a special register address.

(numeric  $0 \le XX \le 31$ )

or literal.

Index register must contain a suitable constant,

Example A

Our program is in Group 1.

(Xl<sub>4</sub>) = SPEC, G2 0

order: TK 4, N, SC, 0 --- Q

Transfers the next order about to be executed under sequence counter control in program 2 to location Q.

Example B

(Xh) s SPEC, G2 N, SC

order: TX ha Za O

same effect.

The method of the first example is preferable, since it allows easy reference to any register in group 2, and the addressing scheme is more straightforward. However, since the effective address is computed, as for HSM indexed operations, by adding the complete address from the index register and the 8 bit augmenter from the order word, either method is acceptable.

Note that 4, N, SC, O is translated as follows:

Designator bit = 1 (because special register)

Indexed bit = 1 (because indexed)

1 designation = 100 (IR 4)

Augmenter = 00100010

This augmenter is identical to the low order 8 bits of an address we would get if we wrote No SC .

Note also the reason that  $\Delta^1 \leq 3$

This is because the 8 bits available in the order word correspond to the special register address (5 bits)

direct-indirect bit (1 bit)

incrementer (2 bits)

Thus the <u>augmenter</u> can only contribute to the 2 lowest bit positions of the incrementer portion of the effective address.

Defined, or SIMULATOR instructions.

ForM: Sp XXXX A B C

XXXX should previously have been defined by the Assembly Control code SIMULATE. It refers to an address which must end in octal 7.

or S, M, , when

n is an index register.

is an augmenter (symbolic or numeric)

It must end in octal 7.

The effective address need not end in octal 7.

#### ACTION:

- 1. The order itself is stored in the effective address of operation field.

- 2. The CSC is set to this address + 1.

- 3. The Address A is stored in AUA (Special register 0).

This address may be an effective address as a result of indexing.

- h. The effective C address is stored in AUC. (special register 1)

- 5. The GSC is used to select the next order.

AUA and AUC can be used immediately for indirect addressing of 2 locations of importance to the simulator routine.

#### TYPOGRAPHICAL ERRORS:

- P 3-1-15 Example 19

Shift order should be a 3 bit shift.

- P 3-1-3 Example 2

The product is wrong, and should be shifted right 1 digit.

- P 3-1-2 Figure 1.

The order should be DM, not BM

- P 2-1-12

The add order should be BA, not DA.

#### II. GENERAL TRANSFER INSTRUCTIONS

- A. One Word Transfers

- The H-800 has two one-word transfer instructions:

- (1) Transfer A to C, Ignore B (TX A B C)

This one-word transfer instruction causes the contents of the A

address to be transferred to the location specified by the C address.

The B address of the TX instruction is ignored and may be used to

store data.

- (2) Transfer A to B, go to C (TS A B C) This one-word transfer causes the contents of the A address to be transferred to the location specified by the B address. The C address portion of the TS instruction will replace the contents of the sequenci counter\*, unless the C address is left blank in which case the sequencing counter will not be changed.

(The A and B addresses can be left blank and the C address used to change the sequencing counter.)

"This means the sequencing counter specified for the next order. Thus, TS C A B Q will cause the cosequence counter to be set to Q, and the next order executed will be that at Q.

#### B. Multiple Word, Transfer Instructions

- (1) Transfer N words (TN A B C)

This instruction causes the number of words specified by the B address to be transferred from successive memory locations starting with the location specified by the A address to successive locations starting with the one specified by the C address. The number of words transferred may be any number from 0 to 63.

- (2) Item Transfer (IT A B C)

This instruction first substitutes the end of item symbol for the High Order 32 bits of B, protecting the Low-Order 16 bits of B. Secondly this instruction transfers from consecutive memory locations starting with A to consecutive locations starting with C until an end of item symbol has been transferred. The end of item symbol which terminates the operation need not be the one placed in B by the instruction. No address used in this instruction should be special register direct.

- (3) Record Transfer (RT A B C) This instruction is used to transfer an entire record within the memory The instruction is identical to the Field Transfer instruction, except that an end of record word is written at B instead of an end of item symbol and an end of record word terminates the transfer. No address used in this instruction should be special register direct.

- (b) Transfer A to C N times (MT A B C)

This causes the contents of the A address to be transferred to the location specified by the C address. This operation will be repeated as many times as specified by the contents in the B address, which must be less than 64.

The A and C addresses of the instruction are not modified during execution of the order, however, if special registers are specified, their contents may be incremented after each transfer.

## TABLE OF CONTENTS

| Chapter |                                                                                                                                                                                                                                                                                                   | Page                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| I.      | Introduction                                                                                                                                                                                                                                                                                      |                                                                                                  |

|         | Introduction to Electronic Data Processing                                                                                                                                                                                                                                                        | 1-1                                                                                              |

| II.     | Stored Programming                                                                                                                                                                                                                                                                                |                                                                                                  |

|         | Basic Properties and Operations                                                                                                                                                                                                                                                                   | 2-1                                                                                              |

| III.    | Central Processor                                                                                                                                                                                                                                                                                 |                                                                                                  |

|         | Multiply, Shift, Superimpose Instructions Decision Instructions Transfer Instructions The Bi-Sequence Mode of Operation Cyclic Counter Shift and Select Masking Special Registers Tabular Counter Distributed Read-Write Selective Control Referred Instructions Timing Addresses of Significance | 3-1<br>3-4a<br>3-4b<br>3-5<br>3-6<br>3-7<br>3-9<br>3-10<br>3-10a<br>3-12<br>3-13<br>3-14<br>3-15 |

| v.      | Peripheral Equipment                                                                                                                                                                                                                                                                              |                                                                                                  |

|         | Card Readers High-Speed Printer                                                                                                                                                                                                                                                                   | 5-1<br>5-2                                                                                       |

| VI.     | Optional Equipment                                                                                                                                                                                                                                                                                |                                                                                                  |

|         | Scientific Option                                                                                                                                                                                                                                                                                 | 6-1                                                                                              |

| VII.    | Appendix                                                                                                                                                                                                                                                                                          |                                                                                                  |

|         | Flow Charting for the Honeywell 800                                                                                                                                                                                                                                                               |                                                                                                  |

# LECTURE NOTES

# Introduction to Electronic Data Processing

## COMPANY HISTORY

Datamatic was originally formed as a corporation in April 1955 through the joint efforts of Minneapolis-Honeywell Regulator Company and Raytheon Manufacturing Company. Its nucleus was a group of scientists and engineers who had been active in electronic computer research and development since the pioneering days of World War II. Prominent members of this staff were key personnel in the work done at the Harvard Computation Laboratory, at the Aberdeen Proving Grounds, and at other such early developmental areas.

In addition to this personnel, Datamatic enjoys a well-trained and experienced staff which was developed at Raytheon over many years. The staff designed and built the RAYDAC, a giant scientific computer currently in use by the Department of the Navy, and performed basic research and design projects for various governmental agencies.

Next came the DATAmatic 1000 which begins its career as RAYCOM, the business data processing counterpart of RAYDAC. Initial work, including drawing up specifications and logical design, was begun in 1952. The next few years were spent in the development and construction of the machine with special emphasis on the requirements of todays business applications.

In June 1957, Honeywell acquired Raytheon's interest in the separate corporation and Datamatic subsequently became a division of Minneapolis-Honeywell Regulator Company.

#### LECTURE NOTES

# Introduction to Electronic Data Processing

# COMPANY HISTORY

Datamatic was originally formed as a corporation in April 1955 through the joint efforts of Minneapolis-Honeywell Regulator Company and Raytheon Manufacturing Company. Its nucleus was a group of scientists and engineers who had been active in electronic computer research and development since the pioneering days of World War II. Prominent members of this staff were key personnel in the work done at the Harvard Computation Laboratory, at the Aberdeen Proving Grounds, and at other such early developmental areas.

In addition to this personnel, Datamatic enjoys a well-trained and experienced staff which was developed at Raytheon over many years. The staff designed and built the RAYDAC, a giant scientific computer currently in use by the Department of the Navy, and performed basic research and design projects for various governmental agencies.

Next came the DATAmatic 1000 which begins its career as RAYCOM, the business data processing counterpart of RAYDAC. Initial work, including drawing up specifications and logical design, was begun in 1952. The next few years were spent in the development and construction of the machine with special emphasis on the requirements of todays business applications.

In June 1957, Honeywell acquired Raytheon's interest in the separate corporation and Datamatic subsequently became a division of Minneapolis-Honeywell Regulator Company.

were to be performed, and the disposal of the result. Control of the sequence of computing processes was to be carried out through a set of punched cards. These plans, over 100 years old, are amazingly modern in concept.

Babbage died in 1871. Although the analytical engine had been designed in great detail on paper and Babbage had spent a considerable sum of money on it, only a small portion of the machine had been constructed. After his death, part of the mill was built by his son, H. P. Babbage and may now be seen in the Science Museum at South Kensington.

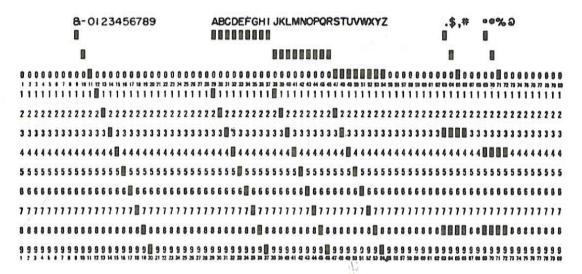

## THE PUNCHED CARD

In 1886, the census of the people of the United States, which had been taken in the year 1880, was still being sorted and counted. Among the men then studying census problems was a statistician and inventor, Dr. Herman Hollerith, the chief of the Census' tabulation section. He saw that existing methods were so slow that the next census (1890) would not be finished before the following census (1900) would have to be begun. Adapting the principle of the punched-paper control system, similar to that used by Babbage, he applied the method to the accumulation of statistical data. This was a most important stride in mechanical computation, for it introduced into a working system the concept of mechanically stored information. He employed this idea for many calculations or tabulations without the necessity for re-entering the data from a keyboard. He experimented with sorting the counting, using punched holes in cards, and with electrical devices to detect the holes and count them. The Hollerith equipment was one of the ancestors of familiar punch-card machines. He devised a coding system which bears his name, the Hollerith code.

A short time thereafter, another member of the Census Bureau staff,

James Powers developed another type of mechanical tabulator which also used

punched cards. Initially the holes in the card used by both Powers and Hollerith

were round but in subsequent years the holes in the Hollerith card were made rectangular in shape. Both types of equipment were used by the Census Bureau for many years and, in fact, are still in use.

Punched cards were used later in machines built for accounting and statistical purposes. The idea of an automatic calculating device in connection with punched-card machines led to the development of the first large automatic digital computer, the Mark I. It was built for the U. S. Navy in 1944 by the Computation Laboratory at Harvard University. Although not a punched-card machine its input and output mechanisms are controlled by punched-cards. This machine uses mechanical counters driven through electro-magnetic clutches controlled by relay circuits. In principle and in its function, it is somewhat similar to Babbage's conception of the Analytical Engine. Although in construction, in its free use of electrical components, it is very different from the engine; in principle, in what it does, it is rather similar. Other machines, developed later, use relays not only for control but for the storage and arithmetical units of the machine themselves. The first computer to make use of electronic circuits, with the speed of operation of which they are capable, was the ENIAC, installed at the Aberdeen Proving Grounds in 1948. It was one thousand times as fast as the Mark I.

# ORGANIZATION OF DATA PROCESSING SYSTEMS

Data Processing is the inevitable paper work involved in all phases of general business procedures. The basic elements which comprise record-keeping systems may be classified into several functions.

- Reading and recording of source data

- 2. Input; introduction and extraction of data from the system

- Processing data which includes sorting, classifying, computing and summarizing

- 4. Filing

- 5. Output

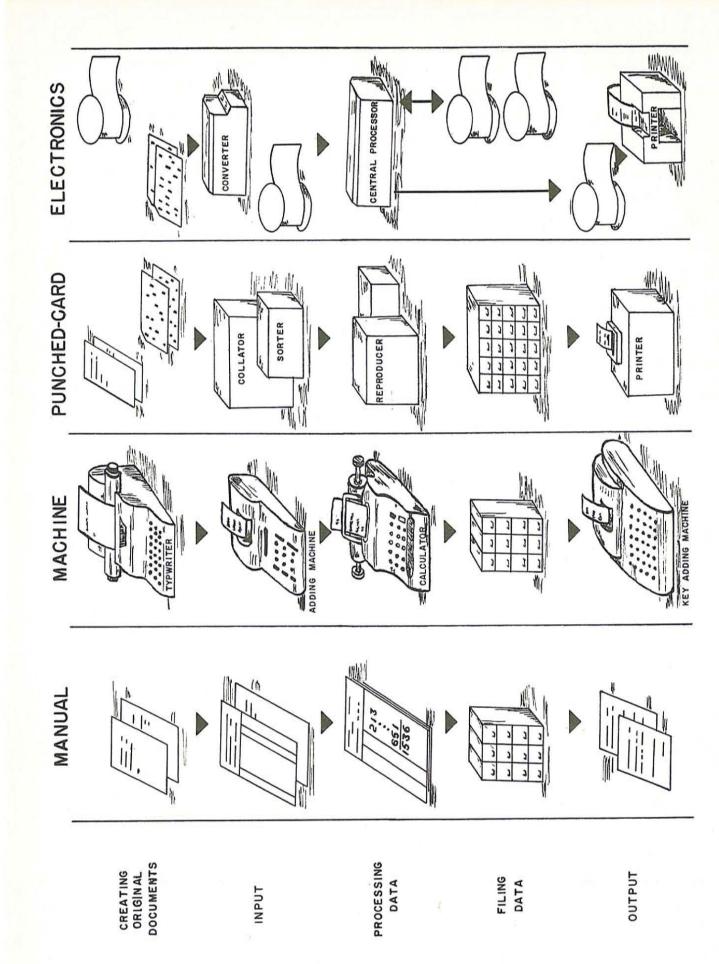

The four significant stages of advancement from the manual routines, through key-driven machine operation, to the punched card method and finally to electronic data-processing systems are illustrated in Figure 1. A purely manual system of data-processing would presumably use pencil and paper for transcribing and computing and a conventional file cabinet for filing. Manual methods are not only slow and costly, but are subject to errors especially if the work is routine or if the work load is heavy.

The second stage is one of mechanization where typewriters, desk calculators, accounting and bookkeeping machines are now standard office equipment. The unit cost of these devices is relatively low considering the accuracy and speed available over manual methods. The advent of the punched paper tape introduced compatibility to a wide range of equipment. Many of the standard office machines can now be used in combination with each other through the commonlanguage medium of the punched paper tape.

In the next stage, punched card machines were introduced wherein the punched card often serves as the source document and as a data storage and communication medium. These methods are rapid, accurate and relatively low-cost for the volume of work which they are capable of producing. Limitations, which have been overcome by electronic data processing, are evident in the punched card system. For example, the scope of operation performed is limited so that exceptions must be handled manually. Furthermore, the record or item size is restricted to the number of columns punched on a single card.

In the electronic data-processing system, many of the basic functions of record-keeping are accomplished at electronic speeds. Source data may be transcribed onto paper tape, magnetic tape or punched cards for conversion into binary code, a language which can be understood by the central processor. The use of magnetic tape as a storage medium for files permits the storage of tremendous volumes of data in a small space, with rapid access to the information in the files. Manipulation of data within the central processing unit, such as sorting, classification, computation, etc., is performed automatically as directed by a series of instructions called a program. The output from the

Figure 1. Organization of Data Processing Systems

central processor is written upon magnetic tape and may be transcribed to paper tape, punched cards, or fed into high-speed printers. In addition to the high degree of effectiveness in inventory and production control and sales analysis, more timely information for effective management control is attained through the increased speeds of which electronic computers are capable. Furthermore, the electronic processor introduces a major increase in reliability and freedom from error.

#### PRESENT DAY DATA PROCESSING METHODS

The standard punch card in use today consists of two main areas, the upper zone section and the lower numerical section (see Figure 2). This latter portion is subdivided into ten horizontal rows, one for each digit, zero through nine. The zone section is subdivided into three horizontal rows, the upper row being called the R or 12-zone, the second row the X or 11-zone and the 0-zone which is the zero row in the numerical section.

The card is composed of 80 vertical columns in which holes may be punched to represent all the digits (0-9), the alphabetic characters (A-Z) and several special symbols. The letters and symbols are characterized by a punch in each of the numerical and zone sections. These punch configurations are known as the Hollerith code.

Figure 2. Punched Card Showing Card Codes