### 1103 NORMALIZED

## FLOATING POINT ARITHMETIC ALGORITHMS

21 October 1955

H. Osofsky Prepared by:

G. Weeg

Issued by:

Systems Analysis Department Mathematics and Design Guidance Groups

Remington Rand

DIVISION OF SPERRY RAND CORPORATION

ENGINEERING RESEARCH ASSOCIATES DIVISION

# 1103 NORMALIZED FLOATING POINT ARITHMETIC ALGORITHMS

#### Introduction

This report presents a set of algorithms intended to accomplish the following four instructions:

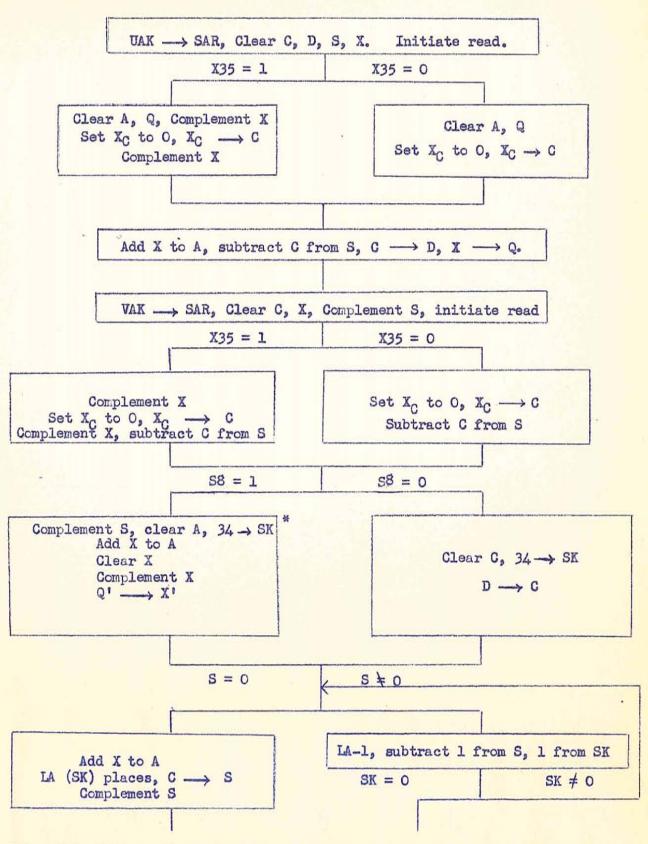

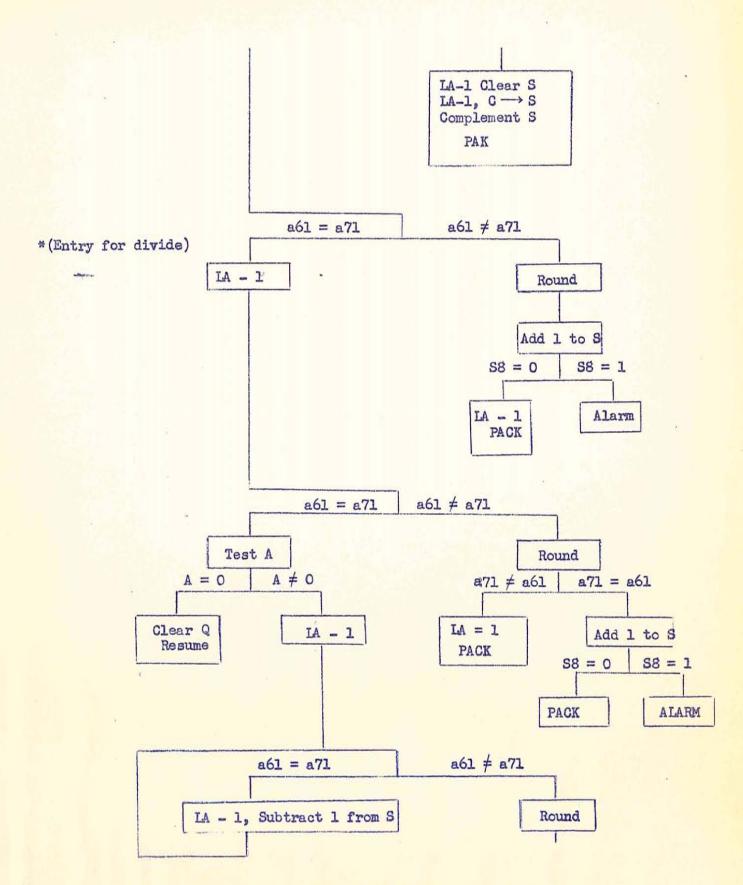

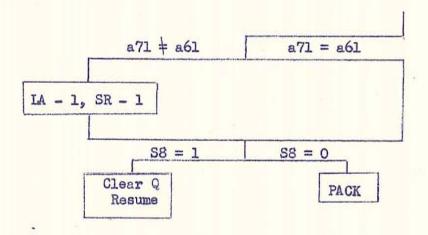

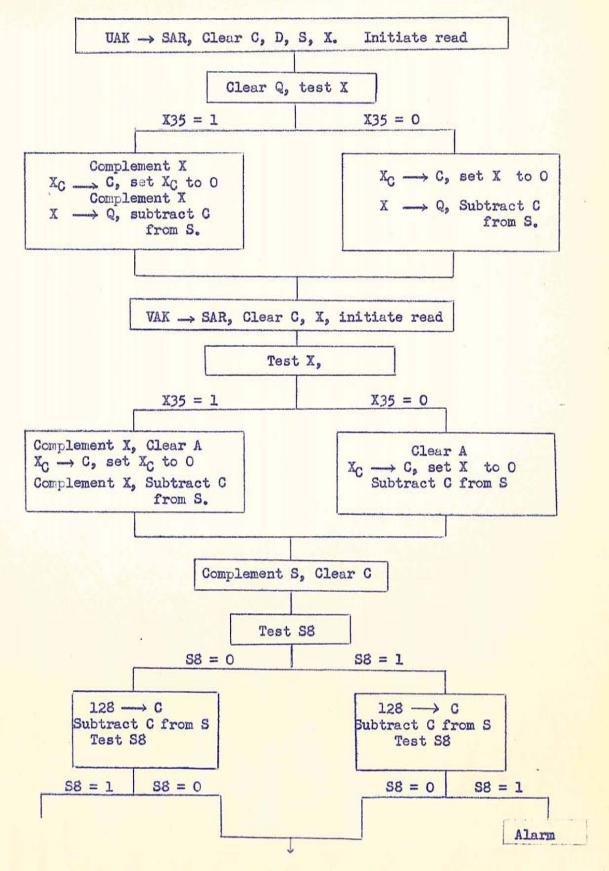

- 1. Floating Add (FAuv) Form in Q the normalized rounded packed floating point sum of the contents of u and the contents of v.

- Floating Subtract (FSuv) Form in Q the normalized rounded packed floating representation of the contents. of u minus the contents of v.

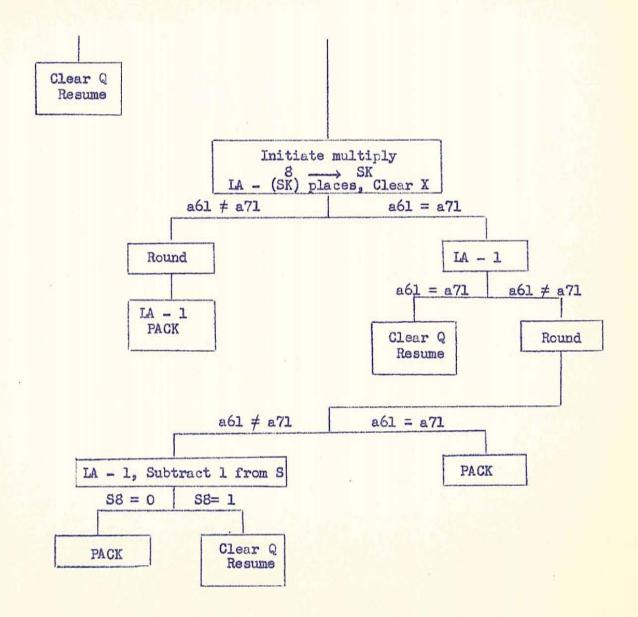

- 3. Floating Multiply (FMuv) Form in Q the normalized rounded packed floating point product of the contents of u by the contents of v.

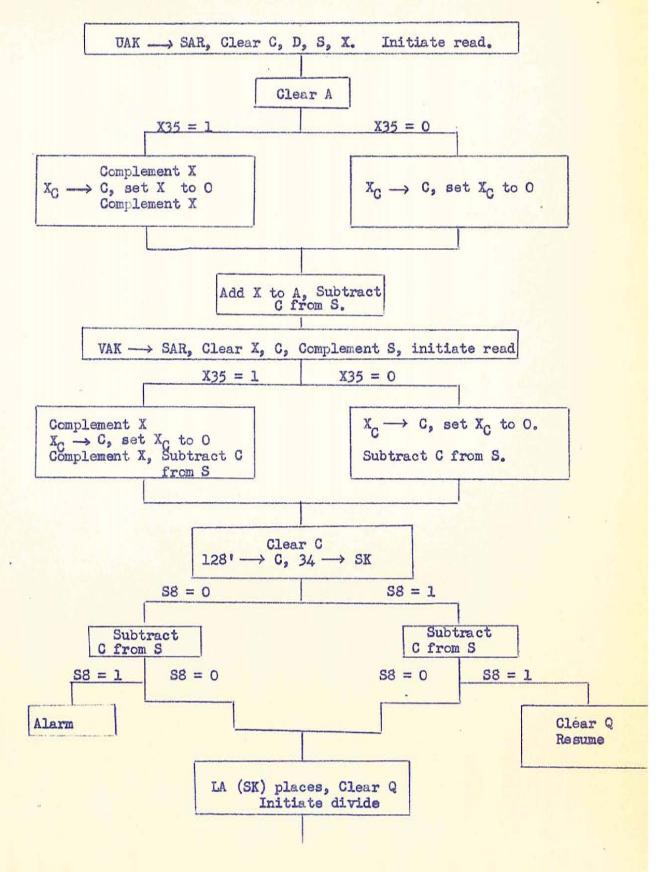

- 4. Floating Divide (FDuv) Form in Q the normalized rounded packed floating point quotient obtained by the division of the contents of u by the contents of v.

#### Conventions

Any real number can be represented, at least approximately, by  $(x \cdot 2^{27}) \cdot 2y$ , where x is a 27-bit real number such that  $\frac{1}{2} \le |x| < 1$ , and where y is an integer or zero. The 1103 packed normalized floating point representation selects that subset of the above approximations such that  $-128 \le y \le 127$ .

The floating point word structure is:

| 1 | 8 | 27 |

|---|---|----|

| S | С | М  |

where

S = 0 if

$$x \ge 0$$

, S = 1 if  $x < 0$ ;

$x = (-1)^{S} [(1 - 2^{-27}) S + (-1)^{S} M \cdot 2^{-27}]$  and

$y = [(2^{S} - 1) S + (-1)^{S} C] - 128$ ,

where if x = 0 then S = C = M = 0.

That is, S and M define the 1's complement representation of  $x \cdot 2^{27}$ , while C is the representation of y + 128, or, when S = 1, C is the 1's complement form of y + 128.

If the mantissa becomes zero, or if the characteristic became negative, as the result of one of the four floating point instructions, the result left in Q would be a positive zero.

If the characteristic exceeded 255, an alarm is initiated.

#### Registers

Besides the registers now found in the arithmetic section of the 1103, these algorithms require the following additional registers:

C register, an 8-bit register, the contents of which are always treated as non-negative. It carries no sign bit. The bit positions of the C register are designated

<u>D</u> register, an 8-bit register similar to C. Its bit positions are denoted

S register, a 9-bit subtractive accumulator. The bit positions of S are denoted

The arithmetic in the S register is assumed to be ones complement. Sg is used as both an overflow bit and a sign bit. This register must be able to be complemented.

#### Transmission Paths

The following transmission paths are also required:

From

$$(S_7 - S_0)$$

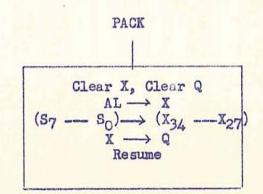

to  $(X_{34} - X_{27})$ . transfer input

From C to D.

From C subtractively to S.

. From D to C.

From AL to X.

\*When the number n is put into SK, this means a left shift of n places is to be called for.

next page

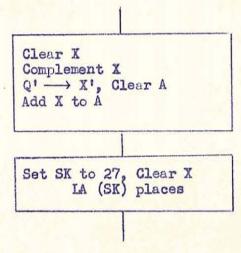

Floating subtract is the same as floating add, except that where (v) is entered into X in add, (v) is entered in subtract.

To addition end. \*