OUR BUSINESS AT KENDALL SQUARE RESEARCH IS TOTALLY FOCUSED

ON THE OPERATIONAL, FUNCTIONAL, AND ECONOMIC REQUIREMENTS

OF OUR CUSTOMERS WHO USE COMPUTING AS A STRATEGIC TOOL. TO

THAT END WE HAVE DEVELOPED A NEW FAMILY OF PRODUCTION

ORIENTED, HIGHLY PARALLEL, SHARED MEMORY COMPUTERS, UNIQUE

IN THEIR ABILITY TO MEET BOTH THE NUMERICALLY-INTENSIVE

COMPUTING NEEDS OF TECHNICAL USERS AND THE TRANSACTION

AND DATABASE-INTENSIVE REQUIREMENTS OF BUSINESS. THE KSRI

FAMILY OFFERS NEW LEVELS OF PERFORMANCE AT DRAMATICALLY

LOWER COST, AND FOR THE FIRST TIME, COMBINES THE SCALABILITY

OF A DISTRIBUTED-MEMORY (PARALLEL) ARCHITECTURE, WITH THE

PROGRAMMING EASE OF A CLASSIC SHARED-MEMORY COMPUTER.

TECHNICAL SUMMARY

FRONT COVER: FROM THE BEGINNING, MAN'S ART AND CRAFT HAVE BEEN INSEPARABLE AND CONTAINED A BEAUTY BORN OF SIMPLICITY. THE HAND PRINT FOUND IN CAVES AND ON CANYON WALLS ON FIVE CONTINENTS FUNCTIONED AS A SIGNATURE, PASSPORT, AND TERRITORIAL MARKER. THE GEAR, WHICH WAS THE CENTRAL TECHNOLOGY OF THE FIRST WORKING COMPUTER, HAS ULTIMATELY BECOME A UNIVERSAL SYMBOL FOR TECHNOLOGY AND PRODUCTIVITY. NOWHERE IS THE FUSION OF ART AND SCIENCE MORE EVIDENT THAN IN TODAY'S COMPUTERS WHERE THE BEST TECHNICAL SOLUTIONS ARE TERMED "ELEGANT" AND THE MOST RECENT ADVANCE IS CALLED "STATE OF THE ART."

> 8 0

-

OR BUSINESS AT RENDALL SQUARE RESEARCH IS TOTALLY. COLU

部隊の

調査

記載

変配

**就** 就 就

聖聖

.

-

ON THE OPERATIONAL, FUNCTIONAL, AND ECONOMIC READER

OF OUR CUSTOMERS WHO USE COMPUTING AS A STRATEGIC TO

| M. A LOPER N. H. W "DE PRODUCTION    |

|--------------------------------------|

| WORKING ON                           |

| A PROBLEM I NEVER                    |

| T.U.O.B.A.B.N.M.L.H.J.PUTERS, UNIQUE |

| BEAUTY. JONLY                        |

| THINK HOW TO                         |

# ERRATA

There are several corrections to be made to the Technical Summary.

- On page 28, the first two instances of "GNUMAKE" should change to read "GNU EMACS."

- Page 67 includes a discussion of "quashing." In this discussion, there are two references to "quash\_never." The second instance should be "quash\_false."

Sorry for any inconvenience this may have caused.

## KENDALL SQUARE RESEARCH

SIMPLICITY THE HAND PRINT FOUND IN CAVES AND CRAFT HAVE BEEN INSEPARABLE AND CONTAINED A BEAUTY BORN OF SIMPLICITY. THE HAND PRINT FOUND IN CAVES AND ON CANYON WALLS ON FIVE CONTINENTS FUNCTIONED AS A SIGNATURE, PASSPORT, AND TERRITORIAL MARKER. THE GEAR, WHICH WAS THE CENTRAL TECHNOLOGY OF THE FIRST WORKING COMPUTER, HAS ULTIMATELY BECOME A UNIVERSAL SYMBOL FOR TECHNOLOGY AND PRODUCTIVITY. NOWHERE IS THE FUSION OF ART AND SCIENCE MORE EVIDENT THAN IN TODAY'S COMPUTERS WHERE THE BEST TECHNICAL SOLUTIONS ARE TERMED, "ELEGANT" AND THE MOST RECENT ADVANCE IS CALLED, "STATE OF THE ARD."

TECHNICAL SUMMARY

## PARTONE INTRODUCTION TO THE KSR1

| NTRODUCTION I                                 |  |

|-----------------------------------------------|--|

| HE NEED FOR HIGHER PERFORMANCE COMPUTING 1    |  |

| RADITIONAL MAINFRAMES AND SUPERCOMPUTERS 2    |  |

| HE MASSIVELY PARALLEL PROCESSORS (MPPs) 3     |  |

| OMPUTING IN THE CONTEMPORARY WORLD 4          |  |

| NTRODUCING THE KSR1 HIGHLY PARALLEL PROCESSOR |  |

| NTRODUCING ALLCACHE™                          |  |

## PART TWO DEPLOYING THE KSR1

| INTRODUCTION                    | 9  |

|---------------------------------|----|

| KSR1 AS A COMPUTE SERVER 1      |    |

| KSR1 AS A COMMUNICATIONS SERVER | 12 |

| KSR1 AS A STORAGE SERVER 1      |    |

| KSR1 FOR VISUALIZATION          | 16 |

## PART THREE SUPPORT FOR TECHNICAL APPLICATIONS

| IDEAL FOR NUMERICALLY INTENSIVE PROCESSING      | 19 |

|-------------------------------------------------|----|

| BENEFITS OF THE SHARED MEMORY PROGRAMMING MODEL | 19 |

| BENEFITS OF INCREMENTAL OPTIMIZATION            | 20 |

| IMPLEMENTING NEW ALGORITHMS                     |    |

| PARALLEL PROGRAMMING ENVIRONMENT                |    |

| COMPILERS AND LANGUAGES                         |    |

| PARALLELIZATION CONSTRUCTS                      |    |

| KSR OS                                          |    |

| RUN-TIME ENVIRONMENT                            |    |

| PORTING CODES TO THE KSR1                       |    |

## PART FOUR SUPPORT FOR COMMERCIAL APPLICATIONS

| IDEAL FOR DATABASE PROCESSING                     | 37 |

|---------------------------------------------------|----|

| CRITICAL ISSUES FOR COMMERCIAL USERS              |    |

| BROAD COMMERCIAL SOFTWARE OFFERING                | 38 |

| THE ORACLE DBMS                                   | 39 |

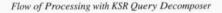

| DECISION SUPPORT - KSR QUERY DECOMPOSER           | 40 |

| HOW THE KSR QUERY DECOMPOSER WORKS                | 41 |

| APPLICATION DEVELOPMENT WITH THE QUERY DECOMPOSER | 43 |

| ON-LINE TRANSACTION PROCESSING                    | 44 |

| TUXEDO TRANSACTION MONITOR                        |    |

| COBOL                                             | 46 |

化化化化化化化

22

## PART FIVE ARCHITECTURE AND THEORY OF OPERATION

| OVERVIEW                                         | . 47 |

|--------------------------------------------------|------|

| THE KSR1 MEMORY SYSTEM                           | . 48 |

| THE ALLCACHE SOLUTION                            | . 49 |

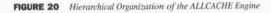

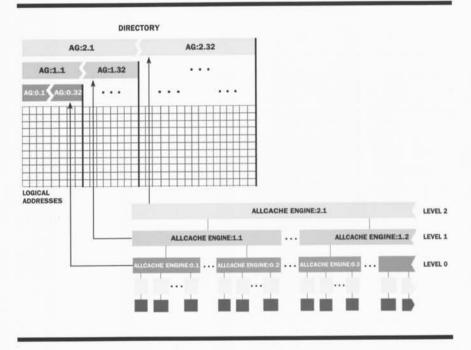

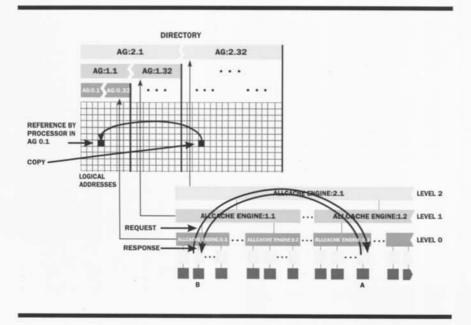

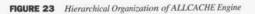

| HIERARCHICAL ORGANIZATION OF THE ALLCACHE ENGINE | . 55 |

| OPTIMIZING LOCALITY OF REFERENCE                 | . 59 |

| SYNCHRONIZATION PRIMITIVES                       | . 61 |

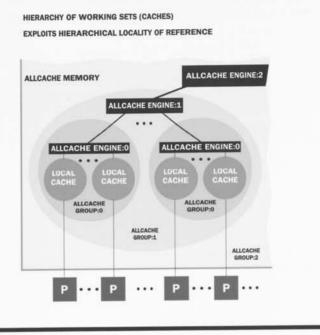

| INSIDE THE ALLCACHE ENGINE                       | . 62 |

| THE KSR1 PROCESSOR                               | 64   |

| AVAILABILITY AND RELIABILITY                     | . 68 |

#### PART SIX

## A BRIEF HISTORY OF MULTIPROCESSOR RESEARCH

| VIRTUAL MEMORY                                            | 3 |

|-----------------------------------------------------------|---|

| NON-SCALABLE SHARED MEMORY ARCHITECTURES                  |   |

| SCALABILITY                                               | 4 |

| LOCALITY OF REFERENCE                                     | 6 |

| DISTRIBUTED ARCHITECTURES WITH SOFTWARE IMPLEMENTATIONS   |   |

| OF SHARED MEMORY 7                                        | 7 |

| SHARED MEMORY DISTRIBUTED ARCHITECTURES                   |   |

| WITHOUT COHERENCY                                         | 7 |

| SHARED MEMORY AS A NETWORK ABSTRACTION                    | 8 |

| OTHER CACHE-ORIENTED, SHARED MEMORY, SCALABLE COMPUTERS 8 | 0 |

| THE DE-SCALING TEST 8                                     | 1 |

### INTRODUCTION

The high performance KSR1 family of general purpose, highly parallel, standards based computer systems runs a broad range of mainstream applications, ranging from numerically intensive computation, to on-line transaction processing (OLTP) and database management and inquiry. The KSR1 differs from conventional mainframes and supercomputers in that it incorporates the scalability and power of highly parallel processing. The KSR1 can be differentiated from the class of massively parallel processors (MPPs) because it uniquely provides the superior performance and ease of use of the shared memory programming model in a scalable, highly parallel computer. In essence, the KSR1 combines the scalability and lower cost of highly parallel processing — across an entire spectrum of computing power, mass storage, and I/O bandwidth — with the higher performance, ease of use and familiarity of the shared memory programming model that has been an industry standard for three decades. The use of shared memory enables a standards based open environment.

## THE NEED FOR HIGHER PERFORMANCE COMPUTING

Since the 1970s, the demand for more computer power has increased significantly among large users of numerically intensive, OLTP and database applications. To date, this need has typically been met by mainframes for OLTP and database applications and by vector supercomputers for numerically intensive tasks.

The proliferation and complexity of the data generated by personal computers, workstations, electronic cash registers, and other high speed electronic devices has significantly exceeded the capabilities of the enterprise-wide computing resources of many organizations. For these companies to provide competitive products and services they must find new ways of keeping up with the increasing volume and use of data. The immediate processing of available and requested data requires organizations to move from historical batch processing environments to on-line computing. Current mainframe systems of most corporations have limited power and capability to support this substantial change in requirements and data usage.

In the fields of science and engineering, the demand for more computing power is driven by a greatly increased emphasis on computational modeling to develop and verify engineering solutions and by an increased focus on highly challenging basic and applied scientific problems requiring a seemingly unlimited amount of numerically intensive computation. The basic extension of human knowledge in many scientific areas can only be addressed by the application of high performance computing resources. Examples abound in both basic and applied sciences: innovations in material science (including semiconductor and superconductor design); the mapping of the human genome; pharmaceutical design; speech recognition; and advanced oil and gas recovery.

Visualization is applicable to both commercial and technical applications. The capacity of modern high performance computers to help people "see" or visualize things provides vivid and compelling examples of the increasing need for more computing power, whether the purpose involves intellectual investigation or entertainment. A single earth satellite can produce the requirement to organize, store, and analyze a Terabyte (1 billion bytes) of data each day. The spectacular special effects produced by contemporary movie-makers require computer systems to handle up to 1.8 Gigabytes (1,800,000,000) of visual data per second of finished film footage. The theme parks

of the future will require high performance computers to conjure up virtual reality for their audiences.

In all these seemingly disparate applications, the common thread is the growing need for everhigher levels of computer performance. Progress in the computational science laboratories has been rapid in recent years, but extensions of that progress from the lab to the real world of applications have not yet achieved success on a widespread basis. Several different computer architectures have demonstrated the ability to achieve very high speed and power, but only in narrow and specialized areas.

F

E

1

1

1

K-

10

1

1

Large users, ironically, are most often limited in their options. An example may be seen in the area of fourth generation languages (4GL) software development tools. A small firm, whose business makes only limited demands on computer power and speed, can effectively select a 4GL and build a satisfactory application in weeks or months, at a relatively low cost of development and with a high expectation of good results. This option is not open, however, to the very largest companies, whose demands already tax the speed and power of their computer systems. Fourth generation languages are relatively inefficient and become an issue for large users whose systems are already at capacity. The ideal computer system for such large users is one that can provide so much power that the user is no longer constrained by the relative inefficiency of the 4GL and can thus benefit from the reduced costs of application software development and maintenance.

Over the past two decades, system designers have approached the development of high-powered computers in two basic ways.

#### TRADITIONAL MAINFRAMES AND SUPERCOMPUTERS

Mainframes have typically been the workhorses of the data processing departments of major corporations worldwide. They are primarily used for database intensive and on-line transaction processing applications during business hours and for batch processing large updates to the corporation's database at night. At the high end of the performance spectrum a number of mainframes working concurrently are required to meet the ever expanding needs of the world's largest users (airlines, banks, brokerage, insurance). Before the development of "vectors" in the 1970s, mainframes were also used for scientific computing.

The first supercomputers involved the use of one (or, at most, a few) of the fastest processors that could be obtained by increasing the packing density, minimizing switching times, heavily pipelining the system, and employing vector processing techniques, which apply a small set of program instructions repeatedly to multiple data elements. Vector processing has proven to be highly effective for certain numerically intensive applications, but much less so for more commercial uses such as OLTP or database. With the introduction of vector supercomputers began the somewhat artificial distinction between the uses of supercomputers and mainframes. The vector supercomputers were seen as useful primarily for numerically intensive applications, such as those found in the technical areas of science and engineering. Non-vectorized mainframes were seen as better for commercial applications.

This partly arbitrary distinction, which became conventional wisdom, was further bolstered by the comparative difficulty of programming supercomputers, whose sheer computational speed was achieved at substantial cost. By contrast, sequentially-processing mainframes traded off a portion of their own theoretically maximum computational speed through the adoption of virtual memory techniques to facilitate their programmability.

The development of the concept of virtual memory,<sup>1</sup> a landmark achievement in computer science, provided a way to free programmers from the unnecessary burdens of memory storage and allocation by separating the notion of address from *physical location in the memory*. Its incorporation into the design of mainframes in the early 1970s, can arguably be said to have helped create the computer revolution.

The sheer computational speed of sequential-processing vector supercomputers has led to the development of a considerable body of specialized program code, much of it written in Fortran, but virtually all of it confined to applications in the scientific and engineering communities. To date, traditional supercomputers have found no place in the compute intensive applications of the commercial arenas of OLTP, database management and decision support.

Moreover, even within the confines of science and engineering, incremental improvements in hardware speed and power have proven ever more costly. This class of machine is now widely recognized to be approaching fundamental limits, such as the speed of light, the laws of thermodynamics and architectural constraints on the number of processors.

## THE MASSIVELY PARALLEL PROCESSORS (MPPs)

In the 1980s, the first massively parallel processors (MPPs) began to appear, with the single goal of achieving far greater computational power at greatly improved price/performance ratios. The concept behind massively parallel processing is to employ large numbers of low cost processors to provide performance far beyond that of mainframes and supercomputers.

However, in actual practice, MPPs have experienced limited market acceptance. The chief reason for the rapidly diminishing expectations has been that the distributed memory architecture of the MPPs, while very scalable, does not support conventional shared memory programming.

Because of the high cost of developing software for MPPs, most such systems have typically been used for only one or a few applications. Although some large-scale users have developed technical and engineering software for certain applications, the majority of third-party software companies have not found it practical to port applications to these computers.

In addition, MPPs have been basically designed to operate in batch processing mode. The use of such systems to support large networks of interactive terminals, workstations, or single-user desktop computers operating in OLTP or interactive mode has proven to be inefficient and expensive. Even at sites where MPPs have met with some computational success, it is common to find other conventional systems functioning as servers to handle I/O or communications.

The difficulty of porting existing programs; the absence of a conventional, standards based and familiar software development environment; the lack of widely available third-party application programs; and the restriction in operating modalities — all these factors have combined to restrict acceptance of MPPs. Although a number of approaches have been tried by the various suppliers of MPPs, simple solutions to the seemingly intractable difficulties encountered with MPPs have eluded all but the most dedicated (primarily government) segment of the market.

Kilburn, T., Edwards, D.B.G., Lanigan, M.J., and Sumner, F.H. "One-level Storage System;" IRE Transactions, EC-11, Vol. 2, pps. 223-235, April, 1962.

## COMPUTING IN THE CONTEMPORARY WORLD

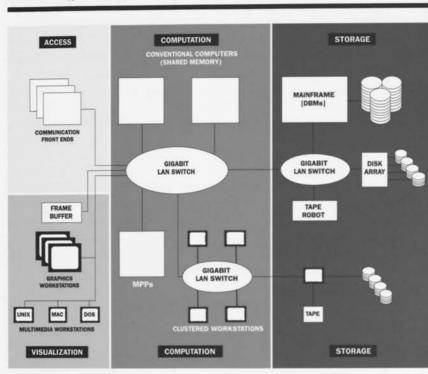

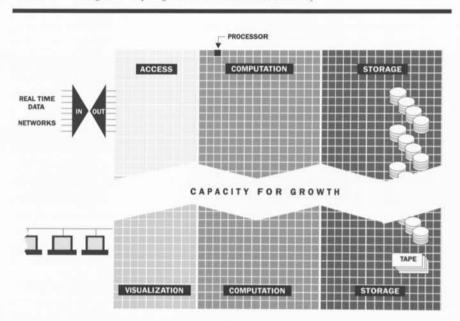

Whether employed for science, engineering, or commercial purposes, most contemporary computer centers resemble, in basic ways, the hypothetical site described in Figure 1. Large computer centers today are characterized by their use of various systems functioning as servers to accomplish some specific purpose within the overall hardware/software assemblage. -

-

c

Contemporary servers fall into four basic types, depending on the functionality assigned to them within the overall site architecture:

- The compute server The compute server is the core of the overall system, and it is

responsible for the actual computational task. This is the sole function to which traditional supercomputers and traditional MPPs can be assigned.

- The data/storage server Another computer in the overall system, the data/storage server, is assigned to manage the movement and storage of large volumes of data across and through a multiplicity of disks and storage devices. Mainframes and dedicated servers are used for this purpose.

- 3. The access/communications server Still another system, the access/communications server, is responsible for all user access and communications into and out of the overall configuration. At complicated, modern sites, the demands upon this server may range from handling the I/O of a variety of devices, each with its own specifications and requirements, to the management of sophisticated networks. Specialized access servers and sometimes minicomputers are used to manage user access.

4

4. The visualization server — A relatively new development, but increasingly common at contemporary computer centers is the visualization server. This server is tasked to allow the users to envision the data or computations in ways that allow the human eye and mind to perceive their significance. Clusters of workstations are most often used for this purpose.

#### INTRODUCING THE KSR1 HIGHLY PARALLEL PROCESSOR

The KSR1 is a highly parallel open standards based system specifically designed to function as any one of the servers described above, as any combination of them, or as all of them simultaneously, while providing a system-wide parallel processing capability. The KSR1 performs the multiplicity of jobs ordinarily assigned to the various servers, simultaneously and in the face of the vastly differing circumstances and requirements that the tasks themselves may exhibit from moment to moment in real time. The KSR1 provides production-level parallel computing power, all of it scalable, with the familiar shared-memory programming model that is the contemporary industry standard. The use of shared memory enables a standards based, open environment [O/S, communications, languages and applications].

See Part Five, Architecture and Theory of Operation, for full details of the architecture of the KSR1 and its capabilities.

### INTRODUCING ALLCACHETM

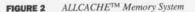

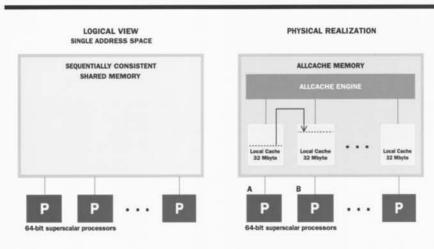

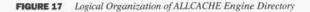

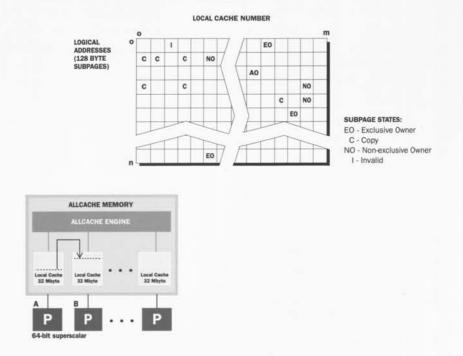

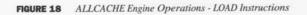

The patented ALLCACHE memory system is the enabling technology at the heart of the KSR1, a major innovation that allows the system to provide scalable, highly parallel processing power on a system-wide basis, whether the standard of measurement is sheer computational speed, I/O bandwidth, data throughput, or visualization. ALLCACHE merges the concept of virtual memory with the modern power of highly parallel processing to give the KSR1 unprecedented applicability.

ALLCACHE is precisely that — all cache memory that re-creates the time-honored standard of virtual memory for the contemporary parallel programmer. ALLCACHE returns the tasks of dynamic storage allocation and management to the hardware, relieving programmers of tasks they have not been compelled to do since the mid-1960s.

Figure 2 on the following page illustrates the ALLCACHE concept. When processor A first references the address X, hardware in the ALLCACHE memory system examines that processor's local cache to see if the requested address is already stored there. If processor B's local cache contains address X, the processor request is satisfied without any request to the ALLCACHE Engine. If not, the ALLCACHE Engine hardware locates another local cache (for example, local cache A) where the address and data exist. The ALLCACHE Engine moves addresses and their associated data to the point of reference on demand. There is no fixed physical location for an "address" within the ALLCACHE memory system, and this physically eliminates main memory.

ALLCACHE is the first memory architecture to deliver the conventional, sequentially consistent shared memory programming model in a highly parallel computer. Thus it combines the memory model used by traditional mainframes and supercomputers with the scalability of highly parallel systems. Scalability allows users to add computer resources in incremental and cost-effective steps, without changes in software and without performance degradation. The entire KSR1 system implements sequential consistency to guarantee that a program will behave in a manner most intuitive to its programmer. The result of a program executed on the KSR1 is significantly faster but otherwise equivalent to the execution of the program on a conventional, multi-tasking single processor, which carries out its tasks in sequential fashion.

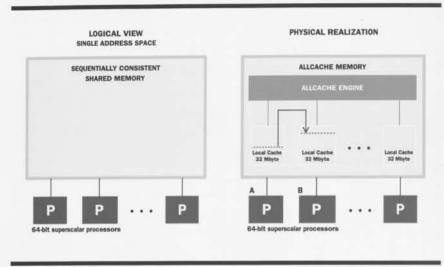

This fundamental improvement in the way that highly parallel processors can be programmed will serve as the basis for the next major wave in hardware architecture. Just as appearance of minicomputers in the late 1960s and supercomputers in the 1970s affected the history of mainframes, highly parallel processors that may be programmed as conventional systems will give rise to the computer industry depicted in Figure 3.

The combination of the KSR1 highly parallel processor, its ALLCACHE memory system and a number of innovative features that take maximum advantage of the best qualities of both traditional programming methodologies and the cost-effective speed and power of highly parallel processing technology advances is described in detail in the following pages.

### Patent 5,055,999

The following quotations are extracted from U.S. Patent No. 5,055,999, assigned to Kendall Square Research, 8 October 1991, for "MULTIPROCESSOR DIGITAL DATA PROCESSING SYSTEM." This patent, which describes the heart of the idea to cast the solution to the memory management problem of highly parallel processors in silicon for the first time, is the foundation concept underlying the architecture of the KSR1 system.

.... A system of the type provided by the invention does not require a main memory element, i.e., a memory element coupled to and shared by the system's many processors. Rather, data maintained by the system is distributed, both on exclusive and shared basis, among the memory elements associated with those processors.

.... the processing cells include central processing units coupled with memory elements, each including a physical data and control signal store, a directory, and a control element.

.... a controller coupled with each memory monitors the cell's internal bus and responds to local processor requests by comparing the request with descriptors listed in the corresponding directory.

.... a memory management unit facilitates... transfer of information. .... Data movement between processing cells is governed by a protocol involving comparative evaluation of each access request with the access state associated with the requested item.

.... The caches of a KSR system can be used by system software as part of a multilevel storage system. In such a system, physical memory is multiplexed over a large address space via demand paging.

.... A system of the type described...

.... provides improved multiprocessing capability with reduced bus and memory contention.

.... The dynamic allocation of exclusive data copies to processors requiring exclusive access, as well as the sharing of data copies required concurrently by multiple processors reduces bus traffic and data access delays.

.... Utilization of a hardware-enforced access protocol further reduces bus and memory contention, while simultaneously decreasing software overhead required to maintain data coherency.

.... The interconnection of information transfer domain segments permits localization of data access, transfer and update requests.

.... These and other aspects of the invention are evident.

## INTRODUCTION

Access, computation, data storage, visualization — these are the four functions performed by modern computer centers. Yet, at most modern centers, the four tasks are often assigned to different types of systems, creating the heterogeneous computer environments so common today.

By contrast, the KSR1, with its high performance capabilities and its patented ALLCACHE memory system, can serve in any of the four roles, in any combination of them, or in all of them at the same time. The KSR1 is truly general purpose in nature, and it provides a homogeneous computing environment with unlimited scalability.

### KSR1 AS A COMPUTE SERVER

In the specific arena of computational speed and power, the KSR1 provides users of high performance systems with an escape from the dilemma posed by the limited choice of architectures previously available. Prior to the introduction of the KSR1, users requiring high performance computing were restricted to the choice of supercomputers or mainframes on the one hand or massively parallel processors (MPPs) on the other. Mainframes and supercomputers permit a conventional programming environment, but are intrinsically limited in performance and bear a very high cost of computation. The MPP architectures, by comparison, offer high performance at a lower cost of computation, but have proven to be very difficult or impractical to program for most applications and have not been generally effective in multi-user, multi-application environments.

| PROCESSOR<br>CONFIGURATIONS | PEAK<br>MIPS | PEAK<br>MFLOPS | MEMORY<br>(MBYTES) | MAX. DISK<br>CAPACITY<br>(GBYTES) | MAX. I/O<br>CAPACITY<br>MBYTES/SEC |

|-----------------------------|--------------|----------------|--------------------|-----------------------------------|------------------------------------|

| KSR1-8                      | 320          | 320            | 256                | 210                               | 210                                |

| KSR1-16                     | 640          | 640            | 512                | 450                               | 450                                |

| KSR1-32                     | 1,280        | 1,280          | 1,024              | 450                               | 450                                |

| KSR1-64                     | 2,560        | 2,560          | 2,048              | 900                               | 900                                |

| KSR1-128                    | 5,120        | 5,120          | 4,096              | 1,800                             | 1,800                              |

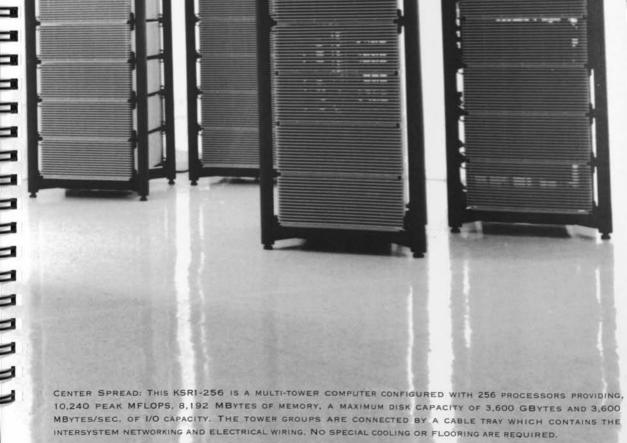

| KSR1-256                    | 10,240       | 10,240         | 8,192              | 3,600                             | 3,600                              |

| KSR1-512                    | 20,480       | 20,480         | 16,384             | 7,200                             | 7,200                              |

| KSR1-1088                   | 43,520       | 43,520         | 34,816             | 15,300                            | 15,300                             |

#### TABLE 1

The KSR1 offers an alternative to this dilemma by presenting a clear third path to high performance computing. The KSR1 provides users with a scalable family of computer systems (see Table 1 for configuration examples) which combine: the very high levels of performance and lower costs of computation inherent in parallel processing, with the high performance and ease-of-use of conventional shared memory programming, and the benefits of industry standards. These standards include OS, databases, communications, languages and applications.

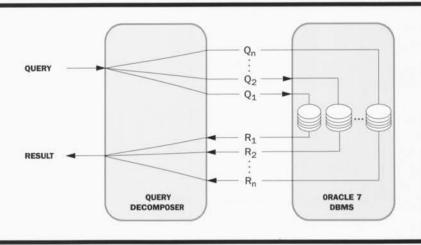

On conventional MPPs the program must explicitly manage memory allocation and memory movement. On a KSR1, the ALLCACHE Engine embedded in hardware automatically manages memory allocation and movement relieving the program of these chores, delivering higher performance and ease of programming. Therefore programs explicitly written for message passing massively parallel computers will run faster on a KSR1 due to the higher efficiency of shared memory.

The ALLCACHE memory system architecture implements a sequentially consistent shared address space programming model, masking the physical distribution of local caches of memory. ALLCACHE automates the addressing and location of memory, so that programmers may be less concerned with the location of data while developing or porting programs to the KSR1.

ALLCACHE automatically moves an address requested by a processor to the 32 MByte local cache memory associated with that particular processor. Thus it exploits the "locality of reference" property of address reference sequences. (Programs and data, once referenced, are likely to be referenced again.) ALLCACHE keeps memory traffic close to the processor that is using the data, which is the key to the scalability of current and future products of Kendall Square Research. -

1

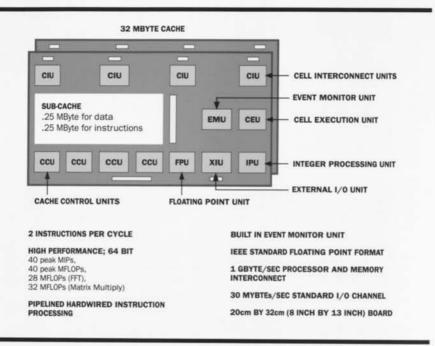

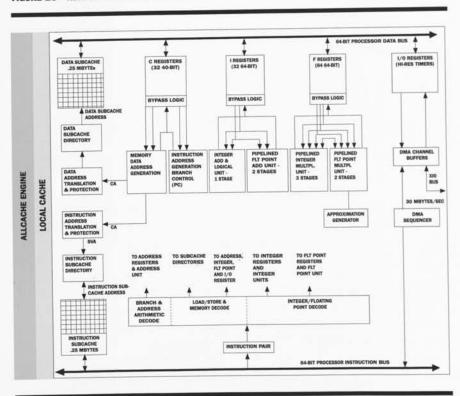

Each KSR1 ALLCACHE Processor, Router and Directory cell (APRD) consists of a 64-bit superscalar processor, a 32 MByte local cache memory and a portion of the ALLCACHE Engine responsible for finding addresses and their contents and relocating them to the local cache of the processor requiring them, while maintaining sequential consistency among all the local caches within the system. (See Part Five, Architecture and Theory of Operation, for detailed information.) When taken as a whole, the collection of local caches behaves as a single shared address space.

The KSR1 processor employs 64-bit address, 64-bit integer, and 64-bit floating point data types, and it can perform arithmetic operations on IEEE standard 64-bit floating point numbers at a peak rate of 40 MFLOPS. To reduce memory traffic, each APRD has large register sets: 64 floating point registers, 32 integer registers and 32 address registers.

The KSR1 architecture allows it to perform work on a variety of jobs simultaneously, unlike traditional supercomputers and MPPs. Large scale users at a number of supercomputer centers have recently observed surprising patterns of workloads and user behavior/requests that indicate that a majority of user programs may require only a relatively short compile and execution runtime on the supercomputer, yet may be compelled to wait in queue for extended periods of time while larger programs are executed.

In these analyses of typical patterns of user demands upon CPU usage and performance, most requests are of a relatively low order of complexity or CPU time consumption. This has led to the use of clustered workstations to accommodate user demands. However, this approach has all the limitations of multicomputers, namely programming complexity, enormous operations complexity, poor load balancing and lack of scalability.

The KSR1 provides a far more expeditious and efficient solution, because it handles multiple jobs of widely varying sizes and requirements simultaneously ranging from uni-processing to massively parallel processing.

## KSR1 AS A COMMUNICATIONS SERVER

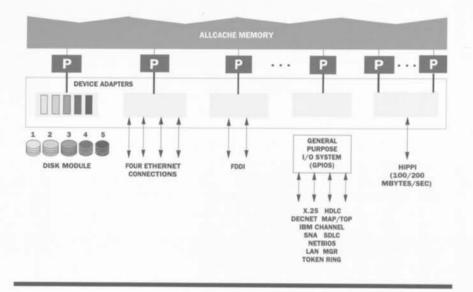

The KSR1 is ideally suited to the communications management task. The high performance network, graphics and I/O connections of the KSR1 are both scalable and flexible. Peripheral capacity and effective bandwidth increase in step with the addition of central processing power to achieve a constantly balanced system.

The KSR1 permits interactive, batch, database and realtime applications to be run simultaneously, because the system is designed to support multiple user interaction models. All users are allowed transparent access to networks and devices, regardless of different network topologies and the varying levels of intelligence that may exist on the user interface devices (e.g., terminals and workstations). The KSR1 can simultaneously support the entire classical spectrum of user interactions:

- Distributed file allows sharing of files between KSR1 systems, user interface devices and other computers

- · Interactive interface allows real-time access to information

- · Batch processing allows submission of jobs to be run without user interaction

- Client/server model allows processing of a transaction on a single machine or split across multiple machines

Different users on the KSR1 interact with the system in ways that are already familiar and comfortable, including graphic and window-based interfaces.

Physical I/O connections to the KSR1 are of two basic types, depending on the performance level requirements:

- Direct adapter connections. The processor uses special adapters to connect with high performance and frequently used I/O interfaces such as the multiple channel disk, Fiber Distributed Data Interface (FDDI), Ethernet and the High Performance Parallel Interface (HiPPI);

- General Purpose I/O System (GPIOS) connections. The GPIOS provides convenient

access to other networks and devices. The I/O subsystem provides industry-standard

hardware (initially VME IEEE 1014 through the special VCC adapter) and the UNIX

System V software environment to allow straightforward customization of applications.

This cost-effective approach allows access to a wide variety of third-party hardware and

software interfaces.

In a KSR1 system, software applications' access to the hardware can be device-independent and, if necessary, network-independent. This approach serves to protect user development investment as new networks and devices become available. Figure 5 on the following page shows connections between KSR1 systems and external devices.

APRD cells in the KSR1 system support 30 MBytes/sec transfers to external sources and users of data. Each 32-cell Processor Module can accommodate up to 15 I/O adapters. A KSR1-32 configured with 32 APRD cells thus achieves an aggregate I/O rate of 450 MBytes/sec (30 MBytes/sec x 15 adapters) and very high throughput with parallel I/O. A KSR1-1088 has an aggregate I/O capacity of 15,300 MBytes/sec.

| UP TO 510 I/O CHANNELS PER KSR1-1088     | CONFIGURATION | I/O<br>CHANNELS | BANDWIDTH<br>(MBYTE/SEC) |

|------------------------------------------|---------------|-----------------|--------------------------|

| ANY COMBINATION OF DEVICE ADAPTERS       | KSR1-32       | 15              | 450                      |

| EACH I/O CHANNEL 30 MBYTES/SEC BANDWIDTH | KSR1-128      | 60              | 1,800                    |

|                                          | KSR1-512      | 240             | 7,200                    |

KSR1-1088

510

15.300

Adapters connect the APRD cell to specific I/O adapters:

- Multiple Channel Disk (MCD) adapter supports disk arrays (RAID) that use five differential SCSI channels for connection to the mass storage subsystem;

- Multiple Channel Ethernet (MCE) adapter with four Ethernet controllers for terminal and workstation servers;

- Multiple Channel FDDI (MCF) adapter with two FDDI X3T9.5 controllers for connection to processors, terminal servers and workstations;

- VME Channel Controller (VCC) adapter with an interface to the VME backplane. This

gives users an open interface for insertion of the many peripheral and I/O boards which

comply with IEEE 1014. The VCC adapter supports networking and an easy pathway for

the customization of specific user requirements;

- Single Channel HiPPI (SCH) adapter for HiPPI X3T9.3 connections supports both 100 and 200 MBytes/sec transfer rates.

Application access to either direct adapters or GPIOS is entirely transparent. For example, access to NFS files is independent of the physical connection type chosen. Transparency of access, which is network-independent, allows for future changes in network media or even protocol stacks.

The network connections supported on KSR1 high performance systems include:

- SNA 3270, 3770/RJE and LU6.2 over serial lines and X.25

- X.25

- X.29, X.28 and X.3

- FDDI

- Ethernet

- TCP/IP and NFS over Ethernet FDDI and X.25

- Serial lines

### KSR1 AS A STORAGE SERVER

The KSR1 is an ideal system for the management of mass storage for groups, departments or an entire enterprise. Mass storage tasks include on-line updates via transaction processing (OLTP), file and archival storage and the maintenance and querying of complex databases. The KSR1 architecture achieves scalable performance as a storage, transaction and database server through a combination of two methods: reduction of disk I/O requirements by use of caching and scalable disk I/O.

An important principle in increasing I/O performance is to complete the operation using primary (main) memory. Main memory is 10,000 times faster (microseconds vs. 10s of milliseconds) than the time to access secondary (disk or tape) storage. The ALLCACHE memory system and 64 bit addressing of the KSR1 processor are fundamental to enabling operations which require physical disk I/O. On most systems physical disk I/O can be satisfied within ALLCACHE through a technique called single level store or mapped files.<sup>1</sup>

The second principle in increasing I/O performance is scalability in random access rates (typically required for OLTP and paging) and high bandwidths (typically required for complex database queries and file transfers). Although steadily improving access latency and transfer rates of mass storage devices have not kept pace with processing speeds, the size, power requirements and costs of mass storage devices are improving dramatically, allowing the deployment of redundant arrays of inexpensive disks (RAID).

Three distinct forces drive the trend toward the concept of multiple smaller disks under intelligent control as the optimum means of mass storage:

- Economic: The use of PC and workstation technologies provide improved price/performance.

- Reliability: The approach provides tolerance for individual disk failure. Expedients as simple as parity, ECC<sup>2</sup> and mirroring suggest seamless data integrity in an environment (e.g., OLTP) in which seconds of downtime may be unacceptable.

- 3. Performance: The use of many small disks allows parallel operations. The basic approach allows different mapping schemes and arrays to take full advantage of classical trade-offs: increase the number of actuators to increase the number of random seeks per second (e.g., OLTP); or spread the file across multiple disks to increase the I/O bandwidth (e.g., large-scale simulations in technical applications or complex database queries).

The KSR1 system combining a large shared memory, scalable I/O access rates and bandwidth, modular packaging of disk arrays, battery backup power system and a UNIX based operating system, incorporating RAID software, is capable of managing a broad spectrum of storage requirements.

Duby, R.C., J.B. Dennis, "Virtual Memory, Processes, and Sharing in Multics," Communications of the ACM, 11, 5, May 1968, pp. 306-312.

<sup>2.</sup> Error Correction Code

## KSR1 FOR VISUALIZATION

Visualization is a new and fast growing area of computing. Its application is far reaching and spans areas as diverse as oil exploration, consumer purchasing patterns, and weather forecasting. Evolving from the simple graphs and charts of the past, true visualization gives the user tools to map any aspect of the data such as color, shape, density, motion and even sound in an exploratory environment.

As visualization needs grow beyond the capacity of the workstation, the same crippling architectural bottlenecks of mainframes and workstation clusters limit expansion of visualization capacity as they limit computation, communications and storage. Visualization is a demanding server application since it combines the need for large databases of 3D structures or scanned images, very high bandwidth communication to send many multi-megabyte pictures to a remote display device and very high computation rates to compute the motion of the millions of objects that make up a complex scene.

ALLCACHE provides a significant performance improvement for high end visualization, graphics rendering and image processing. With conventional multi-computers, whether a distributed cluster of workstations or message passing MPPs, it is necessary to rewrite the graphics or image processing programs, often from scratch, as a set of independent communicating tasks.

With ALLCACHE, existing visualization applications can be ported intact with only minor modifications. In graphics rendering and image processing in particular, a small portion of the code does most of the computational work, only this part needs to be tuned for parallel execution. Another important benefit derived from ALLCACHE is the improvement in performance that comes with memory allocation and memory movement being handled by the hardware rather than by message passing software.

#### **Graphics Rendering**

The KSR1 supports a native port of the OpenGL Graphics Library, an industry standard, threedimensional graphics Application Programming Interface (API). This library includes facilities for drawing geometric objects, text, pixel operations, curves and surfaces, object hierarchies and objects for picking and selecting.

Direct display of rendered graphics from the KSR1 to a color monitor is accomplished via a HiPPI framestore at full resolution and at animation rates up to 170 MBytes per second. Lower resolution views or animations at non-realtime frame rates may be sent to a workstation over Ethernet, using KSR1 graphics compression architecture. (See the section below on "Networked Graphics" for more information.)

### Scientific and Commercial Visualization

The KSR1 will support the Iris Explorer Visual Application Environment. Iris Explorer is a visualization product whose architecture has been designed specifically for maximum efficiency in a client-server environment. The user interface at the front end of Explorer, which resides on many popular graphics workstations, will communicate with the KSR1 parent over the network. Unlike earlier visualization applications, control of the modules' execution is distributed, rather than centralized at the level of the workstation. This design will leverage the full power of the KSR1 highly parallel processor in building very large visualization models.

Explorer is an application-building software system that provides tools to introduce and integrate visualization capabilities with an existing application. The package includes execution modules for numerical analysis, feature analysis, image processing, geometric representation and rendering. A visual programming model is used to interconnect the various modules. The system provides tools which create data filters but require no programming to add user-supplied modules.

Explorer is designed to support the following types of users: application developers who wish to add visualization capabilities to their applications; programmers whose function is to support groups of researchers; computational scientists whose primary task is to develop large-scale algorithms for high-order simulations; scientists who wish to simulate complex phenomena and explore the resulting parameter space visually; and business strategists who wish to analyze more completely complex sets of data.

#### **Networked Graphics**

The extremely high computational performance of the KSR1, combined with its massive I/O capacity and throughput, make possible a new computing paradigm for visualization. The KSR1 provides the means by which the power of the world's fastest computers can be brought down to the user's networked PC or X-terminal. The KSR1 is designed to stimulate progress toward the next evolutionary step in the development of the basic graphics model, from the current stage where polygons are drawn at a high performance graphics workstation, to a model that more closely resembles teleconferencing.

While the KSR1 can inherently provide solutions such as HiPPI framestores for high-end animation requirements, Kendall Square Research has continued to focus attention on the problems involved in providing graphics over conventional LANs to PCs and workstations. To this end, the KSR1 graphics architecture is organized to render animation sequences interactively to a software framestore in the KSR1, then to use advanced image compression to forward the images across the current-era network. While implementing JPEG (and, in the future, MPEG) for compatibility with emerging compression standards, Kendall Square has also adopted newer video compression schemes based on wavelet transforms and vector quantification. This provides both high quality displayed images for sharp edged computer graphics as well as faster decompression by software in workstations, PCs and X-terminals. The graphics capabilities of the KSR1 conform to the de facto industry standards of the present day, and work continues to exploit the unique advantages of the KSR1 architecture while maintaining conformity. For example, Kendall Square's implementation of OpenGL will provide for parallel execution of entire frames in an animation, as well as fast-rendering of a single frame with parallel processing. The OpenGL implementation on the KSR1 will be optimized to leverage the advantage of high performance floating point capabilities for optimum image quality. For instance, rasterizing is accomplished by stochastic point sampling, rather than the conventional method of integer rasterization.

The KSR1 will meet the demanding needs of the visualization server for both technical and commercial applications.

## PART THREE SUPPORT FOR TECHNICAL APPLICATIONS

### **IDEAL FOR NUMERICALLY INTENSIVE PROCESSING**

The KSR1 provides a completely integrated programming and development environment for applications, including all the software engineering features inherent in the UNIX operating system, along with an extensive set of programming languages and compilers, including Fortran, C, C++, Cobol, and assembly language. Numerous enhancements by Kendall Square, such as the addition of full screen debugging facilities, profiling tools, and utilities such as GNUMAKE, assures a productive environment for software development. For applications that require database management capabilities, the KSR1 supports the industry-leading DBMS software, ORACLE7. (See Part Four for details on database software.)

The software environment addresses the special requirements of multiprocessor parallel programming and makes the KSR1 an ideal platform for numerically intensive processing. It provides tools for examining the state of all the processors involved in an application simultaneously, and for analyzing the complex dynamical interaction of multiple processes. The Fortran compilation system incorporates advanced application parallelization technology. For database applications, the implementation of query decomposition in the relational database enables seamless parallel speedup on transaction-intensive applications.

### BENEFITS OF THE SHARED MEMORY PROGRAMMING MODEL

The benefits of shared memory multiprocessors<sup>1</sup> are high performance and a conventional programming model (including virtual memory). When compared to multicomputers, the higher performance of shared memory has two benefits, efficiency and flexibility. Processor communication is more efficient because with shared memory, **hardware** automatically manages memory allocation, coherency and data movement transparently. In contrast, communication between processors within a multicomputer requires **software** to explicitly manage memory allocation, coherency and data movement.

The implicit nature of sharing an address space on a shared memory multiprocessor results in a flexible environment which dynamically moves only those addresses required by program execution between processors. In contrast, on a multicomputer, the exact details of all data movement must be specified statically at compile time. Attempts to build a more flexible environment on a multicomputer by emulating a shared address space in software<sup>2</sup> have resulted in lower performance on shared memory applications, since the shared memory primitives are in software. Thus, the most computationally efficient algorithms can be chosen to execute on a shared memory architecture such as the KSR1, while only explicit algorithms with rigid, static behavior execute efficiently on a multicomputer.

The shared memory programming model represents huge investments in existing programs and programmer training. Whether it is the development of new applications or the migration of existing codes from other shared memory systems, the KSR1 is the first large scale parallel system that

Bell, C. Gordon. "Multis: A New Class of Multiprocessor Computers;" Science, Vol. 228, pps. 462-467, 26 April 1985.

Li, Kai and Hudak, Paul. "Memory Coherence in Shared Virtual Memory Systems;" Proceedings of the 5th Annual ACM Symposium on Principles of Distributed Computing, pps. 229-239, August, 1986.

preserves these investments while providing scalable performance for a broad range of applications. Existing codes can be migrated with minimal code changes. Starting with a port to a single processor, the application can be incrementally optimized and parallelized with data allocation and data sharing, transparently handled by the ALLCACHE memory system. A single, uniform address space of 1 Terabyte (1TB) is accessible to all processors. The system hardware handles data sharing among the processors, without resorting to the complexity of message-passing protocols. (See Part Four for further details.)

Thus users are not forced to rewrite their applications in data-parallel syntax or insert message passing calls to achieve parallel speedups. The parallel speedup is often achieved automatically (see section on Compilers and Languages below), or requires minimal modifications of the code. Not only can applications be ported easily to the KSR1, but because the KSR1 is programmed as a shared memory system, the resulting code remains portable from the KSR1 to other systems. Portability from the KSR1 greatly reduces the cost of maintaining applications across a number of platforms.<sup>1</sup>

### **BENEFITS OF INCREMENTAL OPTIMIZATION**

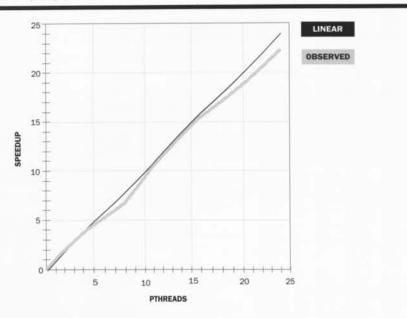

During the migration process, a programmer is concerned with the following issues:

- · Does the application port with minimal source code modifications?

- Does the performance of the application scale with the number of pthreads that participate in its execution?

On a KSR1, applications (whether previously parallelized or not) will run with no modification and depending on the previous level of parallelization some degree of parallelization will automatically be achieved. This is enabled by supporting the language extensions of several other vendors and the shared memory programming environment. The second question, *scalability*, has two aspects; scalability of memory size and scalability of performance. The user gets the benefit of scalability of memory size immediately because the ALLCACHE memory system transparently migrates addresses to the local cache processor being referenced. Data which has not been recently accessed is migrated to local caches that have excess capacity.

From the point of view of the application, local caches are treated as one large shared memory with its inherent aggregate storage capacity. This ability for a user to execute large applications on a single cell of the KSR1 sharply distinguishes the system from large scale message passing systems.

Since ALLCACHE handles data allocation and data sharing chores transparently, the KSR1 is ideally suited for incremental improvements of performance by restructuring only the key portions of the code.

Alternative architectures do not lend themselves to incremental optimization, as they must be completely rewritten. Data allocation and data sharing must be explicitly managed by the programmer. Only after the entire application is parallelized can the user run large problems that require the aggregate memory size of several processors.

S. Picano, E. Brooks, and J. Hoag, "Programming Costs of Explicit Memory Localization on a Large Scale Shared Memory Multiprocessor", Albuquerque, NM: Proceedings of Supercomputing '91, November, 1991.

### IMPLEMENTING NEW ALGORITHMS

New algorithm development is easier with the shared memory programming environment. A programmer need not be constrained by having to first master data parallel programming techniques or message passing protocols. New algorithms can be "dropped-in" without rewriting the entire application, or being concerned over global data structures. This is illustrated in the examples at the end of this chapter.

### PARALLEL PROGRAMMING ENVIRONMENT

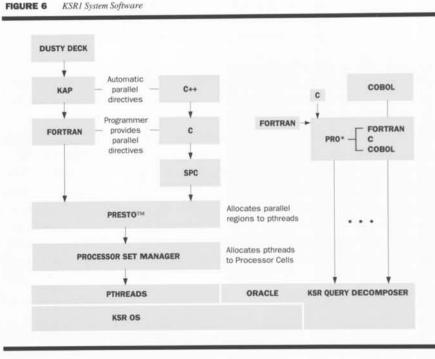

The KSR OS facilitates technical and commercial applications including OLTP, relational database management and decision support.

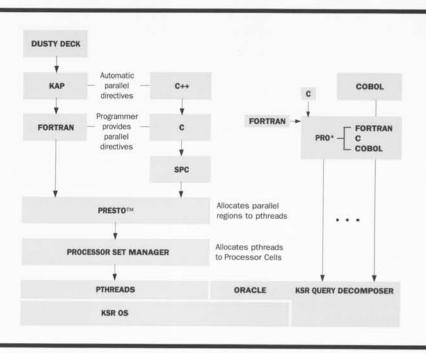

The architecture enables single or multiple applications which mix technical and commercial characteristics to execute efficiently on a single KSR1 system as shown in Figure 6.

The various languages are shown interfacing to lower level software layers. For example, the Fortran compiler, using automatic and programmer generated directives, creates parallel units of work, or ptasks. The number of ptasks created may be set at the time of compilation, or dynamically determined at runtime, based on user directives. The KSR1 runtime environment, PRESTO<sup>TM</sup>, maps ptasks to pthreads. *Pthreads*<sup>1</sup> are POSIX-compliant lightweight processes that are scheduled by the KSR OS on available processors. Pthreads may be accessed by the programmer through the pthreads library calls, or through compiler directives which are replaced with calls to the pthreads library by the compiler. Pthreads provide a low-level interface to the operating system — thereby adding little overhead.

IEEE Technical Committee on Operating Systems, "Threads Extension for Portable Operating Systems", draft P1003.4a/D4, 1990.

The execution of a parallel Fortran program consists of the execution of one or more teams of pthreads. A "team" is a group of pthreads with a team identification number. Its behavior is as follows:

- · A single pthread, called the program master, begins execution at the start of the program.

- When a pthread encounters a begin-parallel-directive, that pthread summons a team. The

pthread that summons the team assumes the role of team leader. The other pthreads are the

team members.

- Each parallel directive can take a team identification number as a parameter. If this

parameter is specified, the designated team will execute the parallel segment. If no team is

specified, the KSR Fortran runtime system, PRESTO, will designate a team to execute the

parallel segment, creating a new team if needed.

- Each pthread in a team executes a portion of the work in the parallel segment. Together, the members execute all of it.

- When all the pthreads in the team reach the end-parallel-directive, the team is usually disbanded, its members are returned to the idle pool, and the team leader continues execution from the statement following the end of the parallel directive. Creation and disbanding of a team does not imply creation and destruction of pthreads: only the grouping of pthreads and the assignment of team identification numbers occur upon creation and disbanding of team operations. Teams that execute within an affinity region are not disbanded, until the end of the affinity region itself. Teams created explicitly by the user are not disbanded until the user explicitly disbands them.

Parallelization of technical applications is achieved by inserting parallelization directives in the source code. A preprocessor, KSR KAP, is available for source code analysis and automatic generation of compiler directives. While the compiler and KSR KAP are capable of automatic parallelization of applications, higher performance can sometimes be obtained with programmer assistance via compiler directives. These directives are described in more detail below. Message passing libraries are also provided as a convenience for some users, primarily for compatibility reasons, but not of necessity to the porting strategies themselves. Users will obtain higher performance by programming the KSR1 as a shared-memory system.

## **COMPILERS AND LANGUAGES**

### **KSR FORTRAN**

KSR Fortran lets programmers develop and port code from other systems quickly and easily. It adheres to the ANSI X3.9-1978 (Fortran 77) standard, and supports several popular extensions of the language present in standard Fortran 77 compilers such as the VAX/VMS, IBM VS, and Cray compilers. In order to maintain portability of the code from the KSR1, Kendall Square has not introduced any language extensions of its own to aid parallelization, rather it delivers the capability of constructs like "PARALLEL REGION" with simple compiler directives.

The KSR Fortran compiler provides optimizations seen in mature compilers<sup>1</sup>, including:

- strength reduction

- loop invariant code motion

- common sub-expression elimination

<sup>1.</sup> M. Wolfe, Optimizing Supercompilers for Supercomputers, Cambridge, MA, the MIT Press, 1989.

- constant folding

- register allocation by graph coloring

- instruction scheduling/branch delay filling

- peephole optimization to minimize register-to-register moves, loads, and stores

- argument-passing in registers

- multi-level loop unrolling

There is ample hardware support to enable aggressive optimization, including a large set of registers, extensive pipelining, multiple instruction launch and chaining of operations.

#### FORTRAN EXTENSIONS

Some of the extensions beyond Fortran 77 that are included in KSR Fortran include: Additional Data Types

INTEGER\*1, INTEGER\*2, INTEGER\*4, INTEGER\*8 LOGICAL\*1, LOGICAL\*2, LOGICAL \* 4, LOGICAL\*8 REAL\*8 COMPLEX\*16, DOUBLE COMPLEX

Bit Operations With Byte Addressability

Bit Field Manipulations Bit Subfields Bit Processing Bit Constants

Dynamic Allocation Of Variables Interlanguage Procedure Calls

#### The C Language

The KSR1 system supports C and offers an efficient C language compiler. The KSR C compiler conforms to the ANSI standard defined in ANSI X3.159-1989 (ANSI C). Parallelization of C codes is accomplished with manual insertion of pthread calls. Simple Parallel C (SPC) comprises higher-level subroutines that provide the same functionality as the Fortran parallelization directives described above.

#### C++ Compiler

C++ is an object-oriented language derived from C. On the KSR1 system, programs written in C++ may be run by compiling them with the C-Front pre-compiler.

C++ is a superset of the C language that provides flexible and efficient facilities for defining new "types." The key concept in C++ is \*class\* which is a user-defined type. Classes provide data hiding, guaranteed initialization of data, implicit type conversion for user-defined types, dynamic typing, user-controlled memory management and mechanisms for overloading operators.

#### PARALLELIZATION CONSTRUCTS

The KSR1 Fortran compiler provides a powerful set of parallel processing capabilities. These include the ability to share variables and common blocks, and procedures for specification of parallel execution of code fragments.

Major parallel constructs include parallel regions, parallel sections and tile families which comprise the KSR1 high-level interface to pthreads. Each of these high-level interface directives is specified with *begin/end-parallel*-directive pairs surrounding the code fragments that may be executed in parallel.

- Parallel region Execute multiple instances of a code fragment in parallel.

- <u>Parallel sections</u> Execute multiple code fragments in parallel. Parallel sections in the text

of a Fortran program are also denoted by a *begin/end-parallel-directive* pair.

- <u>Tiles</u> Loop parallelization in KSR Fortran is achieved by *tiling*, in which the iteration space defined by a Fortran *do* loop nest is decomposed into *tiles*, or groups of loop iterations. The group of tiles that make up a loop nest is called a *tile family*. The tile directive specifies the loop indices over which tiling is to occur. These indices define an iterative space. For example, in Figure 7 the indices i, j and k define the iteration space. A point in this iteration space corresponds to unique values of the loop indices i, j and k.

Rather than have a pthread for each iteration, a tile directive creates groups of iterations that will be executed together. This increases the granularity of the parallel computation and minimizes scheduling overhead.

The tile directive causes the iteration space to be partitioned into rectilinear sub-spaces called tiles, each of which contains enough loop iterations to create a reasonable amount of work for one processor. Each tile is executed by a pthread, and each pthread may execute on a different processor. Numerous processors can execute the same loop nest, with each processor working on a separate tile simultaneously. There may be more tiles than pthreads, so that a given pthread may execute more than one tile.

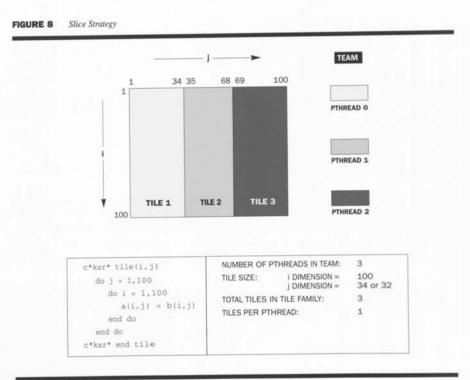

The tile directive can specify parameters giving the user a broad range of control options. In the example presented in Figure 8, the runtime system determines the tile size and how they are allocated to pthreads, but the directives could have included additional tile parameters to control these choices.

## **Major Tiling Strategies**

The four distinct tiling strategies available to the programmer are outlined below. These fall into two major categories: static, as exemplified by *slice*, *mod*, *wave*, and dynamic as exemplified by *grab*. Depending upon the tiling strategy employed, each pthread will execute one or more tiles.

#### slice

The compiler simply slices the iteration space so that iterations are divided equally among the pthreads, where each pthread is to execute one tile. This strategy is the simplest and has the lowest overhead and is the default strategy adopted by the compilation system

#### mod

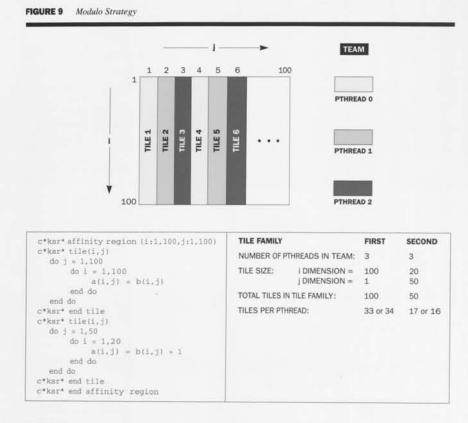

Assigns tiles to pthreads using a modulo mapping: tiles for which the tile number modulo the numbers of pthreads is the same are executed sequentially by the same pthread. There may be more tiles than pthreads, and thus each pthread may execute more than one tile. The compilation system chooses this strategy when data affinity must be maintained across a loop nest (as specified by the directive, *affinity region*) and the bounds of the iteration space vary dynamically.

#### wave

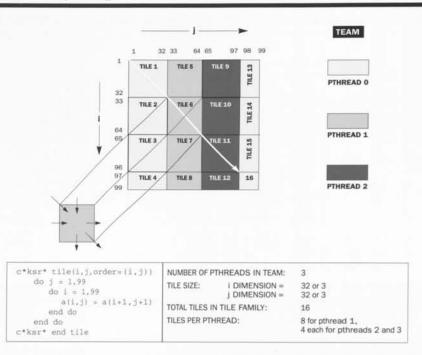

The compilation system chooses this strategy when data dependencies impose ordering requirements. Typically there are more tiles than pthreads, and they will be executed in a wavefront manner, with synchronization that ensures program correctness. Assignment of tiles to their execution pthreads is done as in the modulo strategy.

#### grab

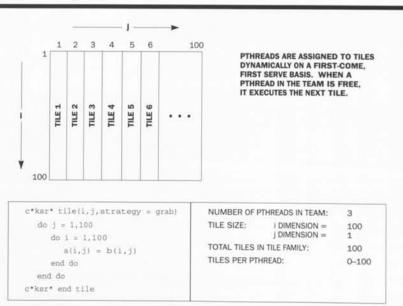

The grab strategy can adjust to an unbalanced load during execution of a tile family. With this strategy pthreads are assigned to tiles on a first come, first serve basis.

FIGURE 11 Grab Strategy

The directives that invoke particular tiling strategies are simple to insert, yet are powerful in their impact. On message passing systems, the equivalent functionality requires dozens of lines of user code.

If the user chooses not to specify a tile strategy, the compilation system and the run-time system do so, as follows:

- · the wave strategy is used for tile families with ordering requirements

- · the mod strategy is used when data affinity must be maintained

- · the slice strategy is the default

### KSR OS

The operating system of the KSR1, known as the KSR OS, is a UNIX operating system based on OSF/1 and is fully compatible with AT&T System V.2 and System V.3 and with Berkeley 4.3BSD and 4.4BSD. The Application Environment Specification (AES) is functionally complete, integrating the specifications of the major standards organizations, including ANSI C, FIPS 15-1, POSIX 1003.1 and XPG3.

The Unix shell, or command interpreter, has a built-in high-level language that allows the user to combine or pipeline programs without the need for compilation or recoding. Several standard shells are offered - including the C shell, tsch, and the Bourne shell.

KSR OS includes the standard set of UNIX text editors (vi, ed, and ex), as well as the GNU-MAKE screen editor. GNUMAKE provides an advanced set of editing capabilities that can be customized and extended by the user, with built-in help facilities that make it easy to use.

KSR OS also provides facilities for software development, including Revision Control System (RCS) and GNUMAKE. RCS supports the management of large development projects, in which many programmers are collaborating and where multiple versions of programs must be maintained. RCS manages the process of revising text files such as source code and documentation. It maintains a complete revision history, automates storage and retrieval of multiple versions of a program, provides release and configuration control, and controls programmer access to the source code.

GNUMAKE, a utility for maintaining consistency between program source and object modules, keeps track of the interdependencies between program elements so that when changes are made, modified source modules are automatically recompiled. A Kendall Square enhancement of GNUMAKE, known as *parallelmake*, automatically spreads compilations over multiple processors, taking a fraction of the time required on a single processor.

The udb debugger, which runs under the X Window System, or in a terminal mode, is a source level debugger designed for multiprocessors. A multiple-window display allows the programmer to track independent pthreads of execution, to set break points with mouse ("point and click") input, and to use pop-up menus for tracing program variables, call structures, or stack frames. The user can call on the integrated, context-sensitive, on-line help facility. Moreover, the command interface of udb is a superset of standard UNIX debuggers, such as dbx, so that minimal retraining is required for its use.

Without changing the standard user interface or file system, KSR OS gives users access to the powerful ALLCACHE shared memory system, the extensive address space, and scalable I/O and the large number of processors that may be configured in a KSR1.

The KSR OS environment also includes support for window-oriented user interfaces, built around industry standards, such as X-Windows and Motif.

-11

Numerous extensions have been added to provide support for high-performance applications and for administrative functions.

A partial list of the KSR OS extensions to UNIX that facilitate operations in a highly parallel system environment is given below:

- KSR OS multi-threads the operating system to allow multiple processors to execute the same operating system code simultaneously.

- The I/O system supports parallel access for all read/write file system operations.

- Disk striping allows the construction of extremely large logical files over large numbers of

physical disks. Data parity helps to maintain data integrity on logical disks. Files of up to

1 Terabyte are supported, and users are allowed to customize their file system for different

types of file access.

- To reduce contention and data movement, the scheduler in KSR OS supports multiple-run queues, with the result that the operating system can sustain a simultaneous mix of jobs from high-performance OLTP to high-performance numerical computations.

- Process management facilities automatically group system resources, as appropriate. Cell and ALLCACHE Engine affinities are used to associate processes with a particular cell or ALLCACHE Engine:0, to maintain a favorable cache footprint.

A batch facility provides capabilities usually lacking in UNIX. Users can submit job requests specifying a minimum and maximum number of processor cells. The batch facility also supports other common batch-scheduling functions, including resource limits, allocation of I/O devices, and job status notification.<sup>1</sup>

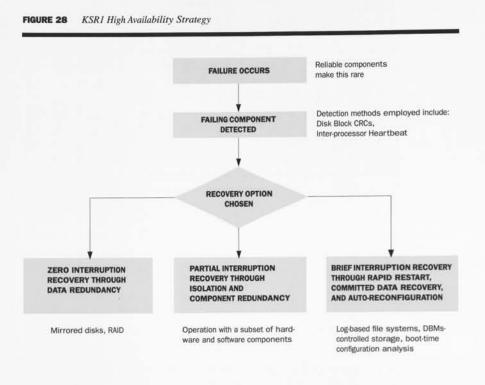

KSR OS includes additional capabilities to ensure data integrity and high system availability:

- · Disk parity, to allow the on-line replacement of components

- A check-point and restart facility for job recovery after unexpected interruptions

- Environment monitoring to help detect unsafe operating conditions

- On-line diagnostic facilities to help identify, report and deconfigure failing hardware components

- On-line maintenance

- Error logging

- Committed data recovery in conjunction with database management software

- Automatic system restart upon condition of a processor interconnect failure, with reduction

of performance limited to the failed component so that operations may continue to the

extent possible. The failed element need not be replaced immediately.

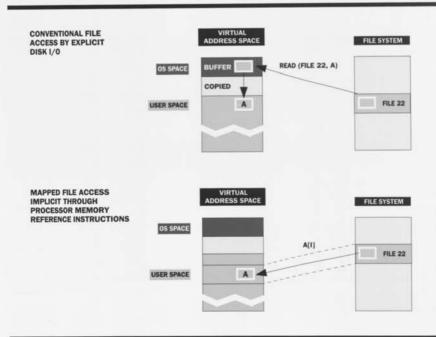

### Single Level Store/Mapped Files

An important technique to increase I/O performance is to complete the operation using main memory and virtual memory hardware. Scalability and performance are significantly increased since the time to access primary (main) memory is 10,000 times faster (microseconds vs. 10s of milliseconds) than the time to access secondary (disk) storage. Other techniques such as software managed file caches are still 100-1000 times slower than main memory. The ALLCACHE memory system and 64 bit addressing of the KSR1 processor are fundamental to enabling operations which

<sup>1.</sup> The batch facility is derived from the Network Queueing System developed by NASA/Ames.

require physical disk I/O on most systems to be satisfied within ALLCACHE through a technique called single level store or mapped files.<sup>1</sup>

On conventional mainframes, virtual address space is used to reference data and programs that have been copied explicitly from disk into a temporary region of virtual memory. The user's program moved the data and programs explicitly into the virtual address space with I/O commands that used a separate addressing scheme for the disk. Single level storage extends the concept of virtual memory to all storage. Files are never copied into virtual storage, as no explicit disk I/O is done by the program. A single address space (rather than one for memory and one for disks) is used to address all storage, both data and files. Thus, processor memory reference instructions are used to access files directly as data. Performance is accelerated, because the standard memory hierarchy is used to cache most recently accessed files.

Single level store requires virtual memory addressability of greater than 32 bits and scalable memory architecture to cache recently accessed portions of files. The KSR1 architecture uniquely meets these requirements in a scalable manner. The KSR1 processor and ALLCACHE meet the first requirement through native 64 bit addressing and meet the second requirement through hard-ware based hierarchical caches. ALLCACHE provides a scalable single level store by efficiently representing the most recently accessed portions of files (a sparse representation of the virtual address space) within a size and performance scalable physical memory.

### FIGURE 12 Mapped Files vs. Conventional File Access

Duby, R.C., J.B. Dennis, "Virtual Memory, Processes, and Sharing in Multics," Communications of the ACM, 11, 5, May 1968, pp. 306-312.

### **Mass Storage**

The KSR OS overlaps computing and I/O operations by means of asynchronous I/O. For example:

- A job can start several I/O operations through asynchronous I/O.

- A process can poll I/O operations or wait for an operating system signal on completion, whichever is more expeditious.

- The file system uses a read-ahead/write-behind feature.

### System Administration

Processors can be divided into processor sets, and a given process can be restricted to one or more particular processor sets. For example, one processor set might be designated for interactive use, a second set for batch queue purposes, and a third set for a particular application. Processor sets can be altered manually or automatically by system administration commands without interrupting operations.

### Scheduler

The KSR OS scheduler is hierarchical in nature and corresponds to the way the system itself is physically constructed. The scheduler is symmetrical and runs on each processor, rather than via a single master. It balances the load between processors and between processes with a single processor. For multi-threaded processes, processors can be added to or removed from an on-going process without disruption of the process' execution.

### RUN-TIME ENVIRONMENT

The KSR1 runtime environment is called PRESTO. As seen in Figure 6 on page 21, the PRESTO environment is available to programs written in Fortran, C and C++. Its primary function is to provide a high-level interface between lightweight pthreads and the user application. The underlying POSIX-compliant pthread library contains primitives for the synchronization and management of pthreads, locks and barriers. PRESTO constructs are executed by teams of pthreads with a master responsible for executing the serial code before and after the parallel construct is encountered. PRESTO dynamically resizes the tile shape based on loop length and the number of operations per loop trip, and the number of pthreads assigned for the job.

It should be noted that PRESTO ensures load balance within a job, namely optimal assignment of tiles to pthreads. Load balance among processes on processors is handled by the OS scheduler.

### **PORTING CODES TO THE KSR1**

Two examples of scientific/engineering applications are described:

### **Example 1: Automatic Parallelization**

The first example is based on a code from "Programming Parallel Processors" by Robert G. Babb, Addison-Wesley (1988). The following code computes an approximation to Pi by using the rectangle rule on an integral representation of Pi. As Babb shows in the text book, even this simple example exposes the "flavor" of parallel programming environments. The critical component of the code is the three-statement DO 100 loop.

-

R

R.

Р.

R

```

c

C - - Pi - Program loops over slices in interval, summing

C - - area of each slice

C

real tt1(2), tt2(2)

integer intrvls, cut

real sumall, width, f, x

C

f(x) = 4. / (1. + x * x)

c

read(*,*) intrvls

t2 = etime(tt1)

C

C - - Compute width of cuts

0

width = 1. / intrvls

sumall = 0.0

С

C - - Loop over interval, summing areas

C

do 100 cut = 1, intrvls

sumal1 = sumal1 + width * f((cut - .5) * width)

100 continue

0

C - - Finish overall timing and write results

C

t1 = etime(tt2)

write(6, *) 'Time in main =', t1 - t2,', sum =', sumall

write(6, *) 'Error =', sumall - 3,14159265358979323846

stop

end

```

On the KSR1, the critical loop is automatically parallelized by KSR KAP. No source code modifications are required. The command line for creating an executable is:

f77 -kap -para -02 -o pi pi.f -lpresto.

The switches -para and -lpresto link parallel libraries, and the switch -O2 tells the compiler to use the highest optimization.

The compilation gives, together with an executable "pi," an intermediate Fortran file, pi.cmp;

```

C

KSR KAP

12.00 k091959 920206polr2 23-Mar-1992 17:52:10

C

C - - Pi - Program loops over slices in interval, summing

C - - area of each slice

C

REAL TT1(2), TT2(2)

integer intrvls, cut

real sumall, width, f, x

SAVE INTRVLS

C

F(X) = 4. / (X * X + 1.)

C

READ (*, *) INTRVLS

t2 = etime(tt1)

C

```

```

Compute width of cuts

C

C

WIDTH = 1. / INTRVLS

SUMALL = 0.

C

C -

- Loop over interval, summing areas

C

C*KSR* TILE (CUT, REDUCTION=(SUMALL))

DO 2 CUT=1, INTRVLS

SUMALL = SUMALL + WIDTH * F((CUT -.5) * WIDTH)

2 CONTINUE

C*KSR* END TILE

- - Finish overall timing and write results

C

C

t1 = etime(tt2)