# Monolithic Concept and the Inventions of Integrated Circuits by Kilby and Noyce\*

Arjun N. Saxena

**Emeritus Professor, Rensselaer**

International Science Company

# 4217 Pomona Avenue, Palo Alto, CA 94306, USA

#### (\* This paper was communicated by Chih-Tang Sah to the conference chairpersons.)

[The paper was presented at the conference based on this revised manuscript. Its earlier version was withdrawn but could not be substituted with this revision. Key changes made: Tables 1 & 2 updated; corresponding modifications made in the text and references; section 7.1 added.]

section 7.1 added.

#### ABSTRACT

Getting history right is an important matter. It is in that spirit that this paper has been written about the invention of integrated circuits (ICs) as an evewitness to, and from the first hand knowledge as a participant in, the development of the materials and technologies of ICs from their inception to the current stage of Ultra Large Scale ICs (ULSICs) and beyond. The invention of ICs has been one of the most important inventions of the 20th century which has revolutionized mankind forever. They are used worldwide in many fields and applications: education, research, computers, medicine, internet, nanotechnology, biotechnology, government and others, and in every commercial, industrial and defense industries. Almost nothing is possible nowadays without using the ICs. Therefore it is important to know who invented them and how. The issues in the inventions of ICs by Kilby, Noyce and the others are intricately entwined technically, chronologically, and legally patent wise. To understand them, it is critical to know what are monolithic-ICs which are the only kind sold from the inception in the IC industry, and how do hybrid-ICs differ from them. A brief account of their key facts including recent communications with USPTO in 2005, which have not been published before, will be given. The debate over who invented what kind of IC will be resolved by the facts presented in this paper. In some respects, Kilby and Noyce have been denied their due recognitions, and in some other respects they have been given more credit in the entire field than they are due. It will become clear that the key concepts for the monolithic-IC were first documented by Noyce, even though the reduction to practice of his invention was done by others, and it depended crucially on Hoerni's and Lehovec's inventions. While Kilby's invention was not for monolithic-IC, he did anticipate some of the monolithic concepts for the devices and their isolation in an IC. But Kilby missed the key concepts of monolithic interconnects and planar technology necessary to fabricate monolithic-IC. The reduction to practice was done by Kilby using Ge mesa technology and wire bonded interconnects dangling above the chip which are not used in monolithic-ICs. Kilby was awarded the Nobel Prize in 2000, and he is generally regarded as the inventor of ICs, implying monolithic-ICs, which is not pedantically accurate. Historians and journalists who have not been in the IC field are apt to glamorize and romanticize its success stories, probably because it is "politically right thing to do". The "law of the famous" is generally upheld, so the famous are given most if not all the credit, and a large number of the others who also made key contributions to the success are ignored. However, for a scientist and an engineer, the documented facts and data are the key criteria to judge who did what? That is the only way history can be set right.

### 1. Introduction

All integrated-circuits (ICs) manufactured and sold from the very beginning around 1960 when they had only a

few transistors per chip to those today having over a billion transistors per chip have been monolithic-ICs made with Si. But what is the monolithic concept which is key for fabricating such ICs and how do these differ from the hybrid-ICs, has not been understood properly in the literature so far and by laymen, non-engineering professionals and even some IC engineers. Jack S. Kilby and Robert N. Noyce have been given the main credit for inventing the ICs, although several others also made crucial contributions. However, even Kilby's and Novce's inventions have not been examined carefully to understand exactly what their inventions were and how they were achieved. For example, Kilby's invention<sup>1,16</sup> as demonstrated in his reduction to practice was only a hybrid-IC consisting of germanium (Ge) mesa transistors and passive devices (resistors, capacitors) on separate chips interconnected by thin metal wires dangling above the chips. Most of the materials and technologies specified by Kilby in his patents <sup>1,16</sup> are not, and have never been used to manufacture monolithic-ICs. Several authors have erroneously credited Kilby to have invented the monolithic-IC. The purpose of this paper is to define the monolithic concept unambiguously, and to give important historical facts of the inventions of ICs primarily by Kilby and Noyce. These facts will also prove that Noyce's invention<sup>2</sup> was that of a monolithic-IC, but it depended crucially on using the other inventions such as those of Lehovec<sup>3</sup>, Hoerni<sup>4</sup> and Kooi<sup>5</sup>. Without these inventions, Noyce's invention would not be feasible. A few authors such as Kilby<sup>1, 11, 12, 13</sup>, Noyce <sup>34</sup>, Rostky

<sup>6</sup>, Riordan & Hoddeson<sup>7</sup>, Berlin<sup>8</sup>, Braun<sup>9</sup>, Brock<sup>10</sup>, Wolff <sup>31</sup> Reid <sup>32</sup>, Lee <sup>33</sup> and Lojek <sup>35</sup> have tried to tell the story of the invention of ICs in their respective ways. While Kilby<sup>1</sup> himself has given a historical account of the invention of the ICs in 1976, however he addressed and discussed the technical aspects of his invention and the patent<sup>16</sup> only recently<sup>12</sup> in 1998, and made some comments also on Novce's invention and his basic IC patent<sup>2</sup>. Novce <sup>34</sup> described the IC as conceived at Fairchild, and referred to the work of Kilby (ibid), Hoerni<sup>4</sup>, Lehovec<sup>3</sup> and others, but did not describe the technical details of the patents. The authors in references 6 - 10 do not address the technical issues of Kilby's and Noyce's IC inventions and their patents, and they have ascribed incorrectly Kilby's invention to be that of a monolithic-IC. Perhaps this may be due to their efforts more as historians without the technical precision of a scientist and engineer, rather than as contributors having first hand experience in solid state devices and IC technologies. Even Kilby's later comments<sup>12</sup> are incomplete at best (see section 6 of this paper). For Wolff's account <sup>31</sup> of the genesis of the ICs, see section 3 below. As a journalist, Reid <sup>32</sup> has done a good job of writing the story of "The Chip", however, it is meant for laypersons. While he does not give the technical details of the invention of ICs, he presents the various key issues quite well. Lee <sup>33</sup> discusses mostly "The (Pre-) History of the ICs", and gives only a capsule of Kilby and Novce's inventions at the end of his paper without analyzing their

technical details. The recent book by Lojek <sup>35</sup> gives an interesting and compelling account of the "History of Semiconductor Engineering", covering several of the areas of semiconductor engineering as it developed from the early years. While it is almost impossible to give the technical details of every issue in its entire field, he has tried to give the essence of a few of them. He has provided incredible amount of documentation, some of which is rather provocative and debatable but to the point. Regarding the invention of ICs, his statement at the outset (p. X. lines 15 - 17) is quite correct: "Historians assigned the invention of integrated circuits to Jack Kilby and Robert N. Noyce. In this book I am arguing that the group of inventors was much bigger."

While investigating the details of Kilby's patents, this author has received some new information about them (see section 5 of this paper) as recently as on September 26 and on November 02, 2005, from the United States Patent and Trademark Office (USPTO)<sup>14, 15</sup>. They have not been reported in the literature previously. Their key purpose was to clarify the issue of the filing date of the original application<sup>16</sup> (OA) claimed repeatedly to be Feb. 6, 1959, by Kilby<sup>1, 11,12</sup>. These official communications from the USPTO documented two conflicting responses <sup>14, 15</sup> showing the OA's filing date to be different than Feb. 6, 1959. The importance of clarifying this filing date of Feb. 6, 1959, lies in the fact that Kilby was incorrect to claim it earlier than what it actually was according to the USPTO records, or that it did not have a filing date at all. If such clarification was available about 40 years ago, it would have had a major impact on the early lawsuits among Kilby (Texas Instruments), Noyce (Fairchild), and Lehovec (Sprague Electric Company). However, they are not the subject of this paper.

#### 2. Summary of the key facts regarding the inventions of the ICs by Kilby and Noyce as documented in the literature

In order to appreciate the significance of understanding the monolithic and hybrid concepts, and distinguish between the inventions of the ICs by Kilby and Noyce from fundamental technology points of view, it is important at the outset to know what they are exactly. The key facts of these inventions as documented in the literature are summarized in Table–1.

### 3. Monolithic vs. hybrid concepts

We shall describe first how the "monolithic" concept has been presented in the literature so far, and then explain the difference between hybrid-ICs and the monolithic-ICs. It is important to understand this, because the "monolithic" concept used to characterize the IC invented by Kilby in the literature has been incorrect.

Riordan and Hoddeson<sup>7</sup> give an excellent historical account of the era from the birth of the transistor to the beginning of integrated circuits. Their last chapter is on "The Monolithic Idea", as they give concluding remarks in their book on the advent of integrated circuits. However, they<sup>7</sup> ascribed erroneously (p. 259; line 32) the accomplishment of Kilby's reduction to practice as "The monolithic idea was finally a reality." It was not a reality completely, but it was a reality only partially and that too in a limited way. Kilby's reduction to practice was a hybrid-IC with mesa devices on two pieces of Ge, and they were interconnected by bonding metallic wires to the chips; they are not used in the monolithic-ICs.

Wolff<sup>31</sup> gives an early account of the genesis of IC including predictions of Dummer<sup>21</sup> in England, efforts of Kilby<sup>16</sup> at Texas Instruments (TI), Noyce<sup>2</sup> at Fairchild, and Lehovec<sup>3</sup> at Sprague. While his descriptions of the work of

Noyce and Lehovec are quite correct, but that of Kilby's requires some clarification. Fig. 1 of Wolff shows "A page from Jack Kilby's notebook of July 24, 1958, where he first recorded how resistors, capacitors, and transistors could be made on a single slice of silicon." This part of making devices is to be aptly credited to Kilby, but only as a part of monolithic fabrication of the chip provided all the devices are made with planar, not mesa, technologies. Nowhere in his patents or papers Kilby neither mentions nor uses planar technology; instead he uses mesa technology. Therefore, while Kilby's enunciation of the concept to fabricate various devices on a single chip is to be recognized, his actual accomplishments were not for the monolithic fabrication of even just the devices. Also, the key role of interconnects to electrically connect these devices is not clarified. Wolff<sup>31</sup> simply quotes from Kilby's notebook as their fabrication with "conductive material evaporated to connect the transistor emitter and base to the circuit, or small wires might be attached by thermal bonding." Kilby prescribes in his patents evaporation of metals through metal masks, and wire bonded interconnects which are not used in monolithic ICs. Until the monolithic interconnects adherent to the insulator layers without shorting to the regions adjacent to the devices and each other are also fabricated, monolithic IC is not complete. These key points will become clearer in section 3.2.

Similar to the erroneous characterization of Kilby's reduction to practice of his invention described above, another research historian, Brock<sup>10</sup>, has made similar characterization more recently on p. 18 of his book in 2006 as, "In the fall of 1958 Texas Instrument's Jack Kilby succeeded in demonstrating that the monolithic concept was a practical possibility, though he did not address the issue of yield." This erroneous characterization was re-stated on p. 26 of his book as "... the new integrated circuits that had been touted in 1959 by Texas Instruments as the first realization of the 'monolithic' circuit ideal." The issue of yield is secondary if not tertiary, in fact almost irrelevant, in Kilby's IC invention; the primary issue is that of demonstrating the monolithic concept, which Kilby did not achieve completely. Fabricating more than one mesa transistor in a single piece of Ge, which was being done routinely at Texas Instruments in 1958 and onwards, is only a part of the monolithic concept. To interconnect these transistors by wire bonding dangling above the Ge piece, as was done by Kilby, negates the very monolithic concept. Monolithic means electrically interconnecting also the devices (transistors, diodes, capacitors, resistors, ...) on a piece of silicon or germanium by conductors which are fabricated monolithically on germanium or silicon, not by manually (or even mechanically) bonding the metal wires to each device. On p. 16 of his book, Brock also writes, "... Many members of the technical community were skeptical of the concept, for it too faced its own tyranny of numbers, a 'tyranny of yield.' " A fundamental tyranny which affects the yield of ICs critically in manufacturing, is the monolithic multilevel interconnection of all the devices needed in the IC. Kilby neither demonstrated nor even specified in his patent such monolithic interconnections, even in a single level, which are mandatory to fabricate the monolithic-ICs.

Another science-technology historian Berlin<sup>8</sup> also writes: "In the fall of 1958, a young Texas Instruments researcher named Jack Kilby set out to build an integrated circuit. By early 1959, he had built a complete circuit on a single germanium substrate. Kilby's circuit was meticulously hand assembled with a network of gold wires connecting the components to each other. The wires precluded the device from being manufacturable in any quantity, a fact of which Kilby was well aware, but his was undoubtedly an integrated circuit of sorts." Not all the "components" of Kilby's

complete circuit were fabricated on a single Ge substrate. However, Berlin does credit Kilby correctly to have "built a complete circuit ... meticulously hand assembled with a network of gold wires connecting the components to each other", and that it "was undoubtedly an integrated circuit of Berlin does not characterize Kilby's invention sorts". specifically to be either hybrid-IC or a monolithic-IC. However, those conversant in the state of the art, and the others after reading this paper, will agree that Kilby's invention as described by Berlin was not a monolithic-IC. Building a "complete circuit ... meticulously hand assembled with a network of gold wires connecting the components to each other ... (which) precluded the device from being manufacturable in any quantity" certainly does not constitute a monolithic-IC.

As it is evidenced from the above discussions that the key concept of what is "monolithic-IC" has not been understood from the early years to even now in 2007.

3.1 Hybrid-Integrated Circuits (Hybrid-ICs): In such circuits, the active devices (e.g., transistors and diodes) are fabricated singly or collectively on or from suitable semiconductors (e.g., Ge or Si). The passive devices (e.g., resistors and capacitors) could be fabricated from the same semiconductors, and/or from different materials. These devices, unpackaged or packaged, may also be mounted on or inserted in substrates having interconnects already formed in them, e. g, Printed Circuit Boards (PCBs), silk-screened ceramic substrates, glass, high- resistivity semiconductors, plastic, etc. Additional wire bonding is done between the various electrical contact regions of the devices and the preformed interconnects of the circuit. Such circuits with wire bonds dangling above the chips are called hybrid-ICs. These wire bonds preclude the chip from being monolithic, i. e., it is not a whole solid integral circuit.

## **3.2 Monolithic-IntegratedCircuit** (Monolithic IC)

The expressions monolithic-ICs and ICs shall be used interchangeably in this paper, except that the former may be used in particular when the monolithic aspect is to be emphasized.

In monolithic-ICs, all the active and passive devices are formed and fabricated in and on the surface of a single piece (chip) of a single crystal semiconductor, e. g., Si, wafer (substrate) using planar technology. But fabrication alone of the active and passive devices in the same chip in one block (monolith idea) is not enough. They must be interconnected contiguous and adherent to the insulating layer over the same body of the semiconductor to produce a solid integral monolithic-IC. If the devices are fabricated within the same body of the semiconductor, but they are interconnected by bonding wires dangling above the chip, such an IC is not a monolithic-IC. This is explained in detail in the previous section 3.1.

Each wafer (now eight inch and 12 inch in diameter) has a large number of chips laid out in arrays. In monolithic-ICs, the devices (transistors, diodes, resistors and capacitors) are fabricated monolithically, i. e., on the same single chip of a single crystal Si, by,

1. PLANAR technology, and

2. ISOLATED [by p-n junction, or LOCOS, or trench isolation, or other appropriate technologies], and

3. INTERCONNECTED [by monolithic interconnections adherent to the insulator (e.g., SiO <sub>2</sub>) layers without shorting to the adjacent areas and each other]. Without these three key criteria, MONOLITHIC ICs cannot be made Arm other more than a more short by the provide state of the state of th

be made. Any other approach gives HYBRID ICs. For a quantitative characterization of adhesion, which was a key issue in Kilby vs. Noyce lawsuit, see Saxena <sup>26</sup>.

The only exception in MONOLITHIC ICs for the passive devices such as resistors and capacitors is that some of them may not need to be fabricated by planar technology; they could be fabricated by thin film technologies as well. However the criteria 2 and 3 above still must be met. Further, each fabrication step is done on the wafer as a whole, i. e., simultaneously on every chip on the wafer. More important in monolithic-ICs, each respective fabrication process step of depositions and/or growth of the various films/layers are done contiguously to the entire surface of the wafers, and the respective photolithographic masking and etching processes are used to delineate the patterns of the ICs in these films/layers simultaneously over the entire array of chips on each wafer. (The materials for contacts and interconnects are not evaporated through masks in monolithic-ICs, which were specified by Kilby<sup>1,16</sup> in his invention.) All the devices in each chip of the monolithic-ICs are interconnected by suitable multilevel metallization (e.g., Al) as needed by the circuit design, contiguous and adherent to the insulating layers over the entire surface of the wafer, without shorting to the regions adjacent to the devices and between various interconnect levels. This necessitates that all the metal interconnections must go over the insulating layers (e.g., SiO 2) from one device to another, as well as from one interconnect level to another in each chip. The p-n junction edges must be covered in situ during their fabrication by the insulating layers, so that the interconnections do not short the junctions with the adjacent regions. This is the fundamental invention of planar technology (Hoerni<sup>4</sup>). Another key contribution used in Hoerni's invention was by Sah<sup>17</sup>. He had given the experiments-based theoretical design curves for SiO<sub>2</sub> layer thicknesses needed to mask against the dopant impurity for selective thermal diffusions in order to make planar junctions of desired geometries. This was a critical step in fabricating Hoerni's planar transistors, not recognized by the others earlier. Appropriate isolation techniques (Lehovec<sup>3</sup>; Kooi<sup>5</sup>) were also used for the electrical isolation of devices and circuit elements within each chip. The entire surface of a completed monolithic-IC chip is contiguous to the surface of the single crystal semiconductor substrate. The monolithic-IC chip is one solid body, and it does not have any dangling wires bonded to different devices and regions, as it does in Kilby's hybrid-ICs.

To do all of the above in order to manufacture monolithic-ICs, the use of planar technology (Hoerni<sup>4</sup>) for fabricating various devices, such as transistors and diodes, is mandatory. Also, the semiconductor necessary for the planar technology is Si because of the high quality SiO<sub>2</sub> insulator film which is grown in situ on its surface. Ge is not suitable for this purpose because germanium oxide is not stable, so it cannot lend itself to give planar technology. Ge mesa technology and wire-bonding (used by Kilby<sup>1.16</sup>) for fabricating and interconnecting the devices will be extremely difficult if not impossible to use for manufacturing monolithic-ICs, especially at the billion-transistor integration levels of today, or even tens of transistors of 45 years ago in early 1960's.

The above discussions explain why Kilby's invention of the integrated circuit was a hybrid-IC, not a monolithic-IC. This will be further augmented by the discussions in the following sections 6 and 7 to prove this conclusion unequivocally. Kilby demonstrated his invention by using Ge mesa transistors glued to a glass slide, and the devices were wire-bonded to interconnect them. These are not used in manufacturing the ICs. Noyce's invention of the integrated circuit was a monolithic-IC, not a hybrid-IC. Noyce did not reduce to practice his invention, which was written but unwitnessed in his lab notebook. However, he had specified Si planar technology, Al interconnects adherent to and going over SiO<sub>2</sub> layers without shorting p-n junctions to the adjacent regions, photolithography and etching techniques which are all used in manufacturing the ICs. Turning Noyce's invention into reality was done by several of his colleagues (e.g., Norman, Last and Haas<sup>36</sup>, and others) working with him during 1959-1960. The fact that Kilby did not receive any patent on IC technologies after receiving his original patents<sup>1,16</sup> suggests that he made no contributions to the Si planar technologies even after it was well established that they were mandatory for the manufacturing of the ICs. Also as discussed in section 6, Kilby refers only to his original patent<sup>16</sup> in his recent discussions<sup>12</sup> and to no other patents or papers by him or others. Kilby's specifications of the interconnect materials and processes in his patent<sup>16</sup> are also unusable in the manufacturing of the ICs.

The solar cells are not characterized as miniature ICs, because their p-n junctions and interconnections are huge in size as compared to those fabricated in transistors or even hybrid-ICs. The early workers in this field did use Si for solar cells inter-connected monolithically with Al, although their technology relatively speaking was crude. Some of them may feel entitled to be credited with the invention of the integrated circuit (e. g, see Queisser<sup>19</sup>). Therefore, they could also be considered as the inventors of the IC. But this is like claiming that a sledgehammer can be used to shape a diamond rather than the precision miniature tools of the diamond experts. Thus they will be ignored.

#### 4. Sequence of relevant patents filing and issue dates

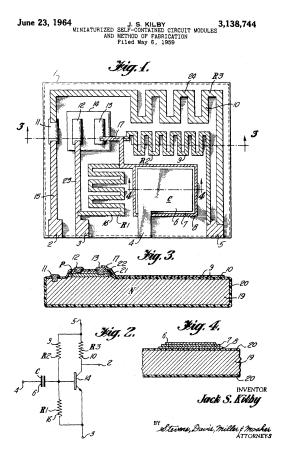

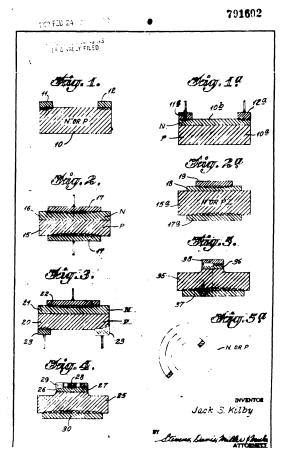

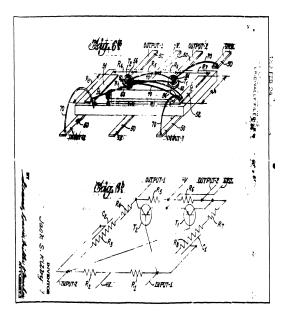

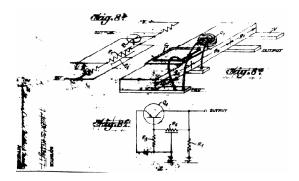

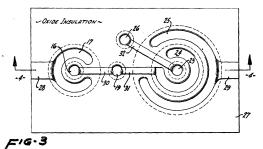

In order to understand the facts about the invention of the ICs, it is important for us to know the most relevant documents of these inventions. They are the original patents (Figs. 1, 2 and 3) of Kilby<sup>1, 16</sup> and Noyce<sup>2</sup> (Fig. 4) which have been used primarily in the literature, and by Texas Instruments and Fairchild corporations to claim the basic invention of ICs, as well as the original patent application of Kilby<sup>16</sup> and his papers<sup>11,12</sup> published in 1976 and 1998 respectively. Kilby's paper<sup>13</sup> published in 2000 before he was awarded the Nobel Prize was not a research publication, but it was a brief re-statement of the early history of the ICs already published<sup>11</sup> by him in 1976. Therefore it has not been listed below. The filing and the issue dates of a few relevant patents in addition to those of Kilby and Noyce are also listed in Table-2. (They are listed chronologically with patent filing dates and public disclosures. As it is well known, listing patent filing dates and public disclosures chronologically documents the origin and sequence of conception of an invention, which is not reflected by the issue dates of the patents. The process in between the filing and the issue dates of the patent, as well as what each inventor did beyond his respective invention to advance its technology to what it is today, are also important to acknowledge and critique each contribution.)

# Key features of Saxena's patent # 3,687,722 on interconnects<sup>20</sup>

The key invention of this patent was to form the welldefined patterns of interconnects and contacts selectively without doing any etching of the metal films. This patent dealt with the adhesion and its selective modification of metal films on insulator layers. (For a quantitative characterization of adhesion, which was a key issue in Kilby vs. Noyce lawsuit, see Saxena <sup>26</sup>. It is amazing that the industry still uses qualitative techniques like "Scotch tape", "Scratch resistance", and related tests.) The main purpose of listing this patent here is to give an example of the continuity of Saxena's work on interconnects and ICs from the early years to the present. It should be noted that this patent of Saxena<sup>20</sup> was filed on March 10, 1971, which was after Kooi's<sup>5</sup> patents on Local Oxidation of Silicon (LOCOS) were filed on Oct. 3, 1966, and Jun. 4, 1970. But it was granted on Aug. 29, 1972, which was well before Kooi's both patents were granted (Jul. 20, 1976; Aug. 14, 1973, respectively). Prior to Kooi's patents<sup>5</sup> on LOCOS process, which is used for the isolation of devices in ICs, Lehovec<sup>3</sup> had been awarded the patent for the p-n junction isolation of devices in ICs. Both Lehovec's and Kooi's patents were important and crucial to isolate the devices in manufacturing the monolithic-ICs.

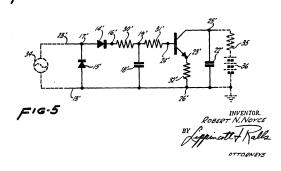

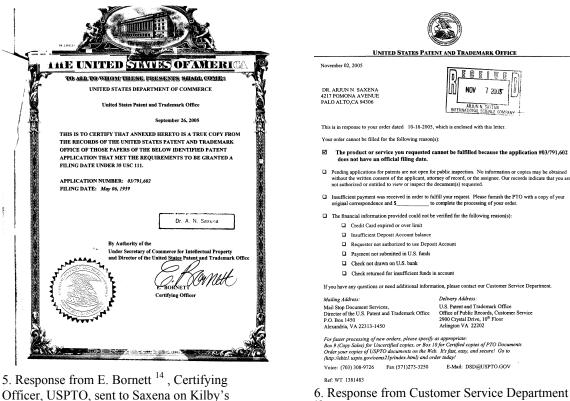

# 5. Controversy over public disclosures and patent filing dates

There is no controversy over public disclosures and the patent filing dates of all of the authors listed in Table – 2, except in the case of Kilby<sup>1, 16</sup>. In his patent no. 3,138,744, Kilby writes (cf: column 1, lines 55 - 57), "To that end, I have proposed in my pending application for patent, Serial No. 791,602, filed February 6, 1959, …" Saxena, while obtaining a copy of Kilby's<sup>16</sup> Application Serial No. 791,602, "Miniaturized Electronic Circuits and Method of Making" from the United States Patent and Trademark Office (USPTO), received the following two official responses recently:

5.1 E. Bornett<sup>14</sup>, Certifying Officer, USPTO, to Dr. Arjun N. Saxena, "This is to certify that annexed hereto is a true copy from the records of the United States Patent and Trademark Office of those papers of the below identified patent application that met the requirements to be granted a filing date under 35USC111. Application: No. 03/791,602; Filing date: May 06, 1959." Sent by USPTO to Saxena on September 26, 2005. (See Fig. 5)

5.2 Customer Service Department<sup>15</sup>, USPTO, to Dr. Arjun N. Saxena, "The product or service you requested cannot be fulfilled because the application #03/791,602 does not have an official filing date." Sent by USPTO to Saxena on November 02, 2005. (See Fig. 6)

The above seemingly contradictory responses from the USPTO cannot be explained. No matter what may be the problem of keeping records accurately and consistently at the USPTO, one fact is clear from the above responses: the official filing date of Kilby's Application No. 03/791,602 was not February 6, 1959, as claimed by Kilby<sup>1.16</sup>. Either it was May 06, 1959, which was also the filing date of Kilby's other patents listed in Table-2, or it did not have an official filing date at all (see also section 7.1).

Table-2 shows that on Kilby's Application<sup>16</sup> No. 03/791,602, two patents 3,138,743 and 3,261,081 were issued, although the revised filing serial no. and date of the latter were 352,380 and Mar. 16, 1964. It is important to note that all the figures in OA 791,602, patents 3,138,743 and 3,261,081 were exactly the same, and their entire texts were also similar except for very small additions in these patents. But the three sets of claims were different and they were not entirely supported by their respective specifications (texts and figures). The fact that Kilby chose to refer only to his patent 3,138,743 in his 1998 paper <sup>12</sup>, and to no other subsequent patent of his, suggests that no significant patents relevant to ICs beyond 3,138,744 and 3,261,081 were issued to him later.

Several technology related matters in Kilby's Application<sup>16</sup> No. 03/791,602, such as "shaping" or "mesa" techniques prescribed in it for the fabrication and isolation of transistors and other devices, gold for interconnects, gold and aluminum evaporated through masks for ohmic contacts, etc, shall not be reviewed in detail in this paper. As it is well known to those conversant in the state of the art, these

technologies are not used and will not work in manufacturing the monolithic-ICs.

## 6. Award of the pre-planar technology IC patents

The planar technology patents were issued to Hoerni<sup>4</sup> in 1962. Even though Kilby's patents<sup>1, 16</sup> were issued in 1964, they are reviewed in this pre-planar section because they were filed earlier in 1959. Noyce's patent<sup>2</sup> was both filed and issued earlier than 1962, so it is also discussed in this section.

Kilby<sup>1</sup> was awarded the IC patent no. 3,138,744 (Fig.1) because of which he earned the recognition of being an inventor of ICs. Kilby's fundamental concept of his invention was stated in this patent only in part correctly (italicized here to focus on it) to suggest monolithic-ICs. For example, in his patent<sup>1</sup>, he writes in Column 1; Lines 55–62: "... To that end, I have proposed in my pending application for patent, Serial No. 791,602, filed February 6, 1959, that various circuit elements including diodes, transistors, and resistors all be formed within a single block of semiconductor material, thereby eliminating the necessity for separate fabrication of the semiconductor devices and the interconnections as mentioned above. ..." (See Table – 1 also).

The basic concept stated above was only partly consistent, but in a limited way, with the concept of monolithic-ICs. Kilby did not specify how these devices formed within a single block of semiconductor were to be fabricated and interconnected within the same block of semiconductor for a given IC, and to maintain the necessary electrical isolations of the devices and the interconnects. Also regarding the fabrication of the devices within a single block of semiconductor, Kilby did not even suggest the correct procedures in his issued patent<sup>1</sup> to accomplish what he had stated. The reduction to practice, and the materials and technologies specified by Kilby in his patent<sup>1</sup> and in the original application<sup>16</sup> to fabricate the devices and the interconnects were not consistent with those required for monolithic-ICs.

To explain further and re-emphasize, Kilby's specifications (text and the claims) in his original patent application no. 791,602 and the issued patent no. 3,138,744, were inconsistent with the purported invention of monolithic-ICs stated above (cf: Column 1; Lines 55 - 62). He had specified several materials and technologies which are not used, and will not work, to fabricate monolithic-ICs. The filing date of Kilby's Application Serial No. 791,602 appears to have never been resolved, but two patents 3,138,743 and 3,261,081 were awarded on this patent application. Further, he did not even specify in his patent no. 3,138,744 the planar technology which is mandatory to fabricate the monolithic-ICs. Even in his later critiques in "Origins of the Integrated Circuit", Kilby<sup>12</sup> while referring to his patent no. 3,138,743 left this question ambiguous and unanswered by concluding that "Despite these introductions, the monolithic concept remained controversial." In monolithic ICs, as described in section 3.2 above, planar technology, depositions and growth of the various interconnect and insulating films/layers are contiguous and adherent to the entire surface of the wafers, and the respective photolithographic and etching techniques are used to delineate the patterns of the ICs simultaneously over the entire array of chips on each wafer. In monolithic-ICs, mesa technology for devices is not used and the materials for contacts and interconnects are not evaporated through masks. As discussed above in sections 2 - 4, several materials and technologies specified in Kilby's patents 3,138,743 and 3,138,744 are not used to fabricate monolithic-ICs.

Without going into further details in Kilby's patents, the bottom line is that his specifications for the integrated circuit consisted of a mesa transistor, whose emitter, base and collector regions were connected to passive components such

as resistors and capacitors by interconnects of copper (Cu), gold (Au) and aluminum (Al) evaporated through masks over an insulating layer such as silicon monoxide. In monolithic-ICs, silicon monoxide and mesa transistors are not used, Cu, Au and Al interconnects are not evaporated through masks, and Cu and Au by themselves are not used because they do not adhere to the insulating layers. So at best, Kilby's invention claimed in his patent was an integrated circuit having mesa transistors, and the materials chosen for interconnects (except for Al for contact only to base regions) would be non-adherent and non-functional when used for a monolithic-IC structure. In the famous slide<sup>6</sup> showing Kilby's reduction to practice of his first integrated circuit, the transistor and passive components in two separate pieces of Ge (i. e., not fabricated in a single block of Ge - monolith idea) are glued to a glass slide, and the different regions of the transistor, capacitor and resistor are shown interconnected by dangling wires bonded to them. Thus, Kilby's invention specified in his issued patents<sup>1, 16</sup> and the first integrated circuit constructed by him were that of a hybrid-IC, not a monolithic-IC.

Noyce was awarded the IC patent no. 2,981,877, (Fig.4) based on his concepts for ICs, written but unwitnessed in his lab notebook, and he had not reduced them to practice by himself. However, he did specify Si planar technology and Al interconnects adherent to SiO<sub>2</sub> which are crucial and used in the monolithic-ICs. Such Al interconnects were not evaporated through masks to make contacts to and between various regions. In Noyce's invention, Al was deposited over the entire surface of the wafer, and photolithographic and etching techniques were used to delineate the interconnects over the entire array of the chips on the wafer simultaneously. The task of turning Noyce's IC concepts into reality was done by several of his colleagues (see brief discussions in Rostky<sup>6</sup>, Berlin<sup>8</sup> and Lojek<sup>35</sup>). This had caused bitter feelings and animosities among the key contributors, especially because Noyce was given the sole credit of being the "Co-inventor of ICs" with Kilby.

[Note: Saxena's role in the award of IC patent to Bob Noyce ahead of Jack Kilby is documented in two papers<sup>24</sup>, therefore it is not discussed here. Kilby's lawsuit lost only partially to Noyce in contesting the award of the IC patent earlier by about 3 years and 2 months to Noyce than to him. Essentially, Noyce's specifications, consistent with monolithic-ICs of using Si planar technology and Al interconnects adherent to  $SiO_2$  layers, prevailed (see Reid <sup>32</sup>). It was surprising, however, that Kilby's<sup>1</sup> description of his concept of ICs (cf: Column 1; Lines 55 - 62) was accepted by the USPTO. In addition, Kilby's actual specifications of the materials and technologies in the text of the patent, and more important in its claims, were also accepted by USPTO. Most of them were inconsistent with monolithic-ICs; nevertheless the USPTO awarded the patents for the invention of ICs to Kilby<sup>1, 16</sup> after reviewing them for over 5 years. Kilby also lost a patent interference suit against Lehovec<sup>18.1, 18.2</sup> in 1966 on the invention of p-n junction isolation of devices in ICs. As listed in Table-2, Lehovec had filed his patent independently only about 14 days earlier than Kilby, but was awarded his patent ahead of Kilby by about 26.5 months.]

7. Award of the post-planar technology IC patents and contributions to ULSICs and beyond: After Kilby<sup>1</sup> was awarded the IC patent no. 3,138,744, only one patent 3,261,081 was awarded, but no further patents relevant to IC technology were awarded to him, even after it was well known that the planar technology, Si and Al interconnects adherent to SiO<sub>2</sub> were mandatory for fabricating monolithic ICs. As evidenced from the published literature and patents, Kilby did not contribute even later to the planar and other

technologies which were, and are, essential to manufacture conventional and advanced monolithic-ICs such as ULSICs. However, he did obtain subsequent patents on miniature electronic calculators and in other fields, which were important contributions in their own right, but not to the invention and further development of ICs. Nevertheless, to repeat, Kilby was given the recognition of being the inventor of ICs based solely on two patents 3,138,743 and 3,138,744. As mentioned also in section 6, even Kilby<sup>12</sup> refers only to his patent<sup>16</sup> no. 3,138,743 in his paper in 1998 on "Origins of the Integrated Circuit", and not to any other patent of his, when critically reviewing his and Noyce's fundamental inventions of the integrated circuit.

After Noyce<sup>2</sup> was awarded the IC patent no. 2,981,877, a few more patents were awarded to him on other process and design related issues of ICs. But no further patents were awarded to him that went beyond the present 2-Dimensional-ICs, for which Moore's Law holds<sup>24</sup>. Noyce did not publish any papers nor receive any patents for the interconnect technologies beyond Al, which are used today in many of the advanced 2D-ICs such as ULSICs. Examples of these are the use of Cu interconnects with appropriate barrier and cap layers, W (tungsten) for contact and via filling, planarization of dielectric and metal films, etc. The limitations of Moore's Law for the 2D-ICs can be removed by invoking the 3D-ICs and Ultra Performance ICs (UPICs). This is discussed in two memos of Saxena<sup>27</sup> given to Gordon Moore at Intel. See also two recent patents of Saxena<sup>22, 23</sup>, and a recent paper<sup>24</sup>.

**7.1 Discussion:** Key observations on the patents relevant to the invention of ICs are summarized below. Some important information has been repeated to facilitate in following their intricate issues entwined technically and chronologically.

(A) Noyce's patent - Noyce patent  $\frac{1}{2}$  2,981,877 (filed on Jul. 30, 1959; issued on Apr. 25, 1961).

(B) Kilby's original application (OA) and patents – Two patents 3,138,743 and 3,261,081 were awarded to Kilby <sup>16</sup> based on his OA 03/791,602. A third patent 3,138,744 was also awarded to Kilby <sup>1</sup> which refers to OA 03/791,602, but its serial no. was 811,486. [According to Lehovec <sup>3</sup> in his ref. 6, "Application 811,476 filed on May 6, 1959; refiled as US Application 218,206 on Aug. 16, 1962"; it is not clear if this refers to Kilby's 811,486.] It is important to note that all the figures in OA 791,602, patents 3,138,743 and 3,261,081 were exactly the same, and their entire texts were also similar except for very small additions in these patents. But the three sets of claims were different and they were not entirely supported by the specifications (texts and figures).

B.1 If the claims of the OA were supported by the specifications (i. e., texts and figures), and USPTO was satisfied, a patent with those claims would have been issued reasonably promptly instead of having to review it for over 5 years and then award 3,138,743 with the new set of claims on June 23, 1964.

B.2 Next, if the claims of 3,138,743 were sufficient to get the patent on the OA filed on Feb. 6, 1959, why 3,261,081, which also originated from the same OA and specifications on the same filing date, was re-filed and new set of claims were necessary? See section D for its revised filing date Mar. 16, 1964 and serial no. 352,380; it was awarded on July 19, 1966. Obviously its issue date was after that of 3,138,743 on April 23, 1964. In addition, the fact that it did not provide any new information, this may have been the reason also why Kilby did not refer to 3,261,081 also in his 1998 paper (see section C below).

(C) Reference to patent by Kilby in his latest paper in 1998 and comments on monolithic concept - Kilby<sup>12</sup> refers only to 3,138,743 with serial no 791,602 and the filing date Feb. 6, 1959 in his 1998 paper. Kilby<sup>12</sup> does not refer to

his second patent 3,261,081 nor to 3,138,744 (filing date May 6, 1959; serial no. 811,486) in his 1998 paper. Kilby also writes in this paper, "Despite these introductions, the monolithic concept remained controversial." In author's opinion, Kilby's patent no. 3,138,744 was his KEY PATENT because it was the ONLY patent of Kilby in which he had at least stated the monolithic concept though partly consistent in its text.

(D) Kilby's filing dates and recent communications from USPTO - Kilby's <sup>16</sup> OA 791,602 and corresponding patent <sup>16</sup> 3,138,743 were claimed to have been filed on Feb. 6, 1959. But recent USPTO communications to Saxena <sup>14, 15</sup> in 2005 (see Figs. 5 and 6, and section 5) regarding serial no. 791,602 sent two conflicting responses:

D.1. Its filing date was May 6, 1959.

D.2. It did not have an official filing date.

Why did USPTO still keep the filing date of 3,138,743 to be Feb. 6, 1959 is a mystery? The filing date of the second patent 3,261,081 is written in its Column 1, lines 6-9 as "Original application Feb 6, 1959, Ser. No. 791,602, now Patent No. 3,138,743, dated June 23, 1964. Divided and this application Mar. 16, 1964, Ser. No. 352,380; 21 Claims, (Cl. 29 – 155.5)." The wording in this patent, "Divided and this application Mar. 16, 1964, Ser. No. 352,380" seems strange, but it is clear that revised filing date was Mar. 16, 1964, and its serial no. was 352,380. As written in (B) above, the claims of this patent 3,261,081 were also not supported by its specifications (texts and the figures).

(E) Monolithic concept - Noyce's patent states and claims the monolithic concept clearly using planar technology and monolithic interconnects adherent to the insulator layers, and without shorting to the regions adjacent to the devices (see item F below). Kilby <sup>12</sup> wrote in his 1998 paper, "Despite these introductions, the monolithic concept remained controversial" implying that he did not agree with the monolithic concept described by Noyce. Kilby did not refer in this paper to his patent 3,138,744 which at least stated the monolithic concept though only partly consistent in its text. Instead, he chose to refer only to 3,138,743 which did not even mention the monolithic concept. Kilby had filed a lawsuit against Noyce for earlier award, and claiming priority that monolithic interconnects were already anticipated by him in his OA 791,602. The lawsuit was settled as a compromise that both the patents of Noyce and Kilby were deemed necessary to fabricate monolithic ICs. Except in Kilby's 3,138,744, none of his other patents (especially the patent application OA 791,602, patent 3,138,743, and patent 3,261,081), state the monolithic concept in their specifications or claims.

(F) Monolithic interconnects - None of Kilby's patents, especially the patent application OA 791,602, patent 3,138,743, patent 3,261,081, and 3,138,744 state how to achieve monolithic interconnects adherent and contiguous to the insulator layers, and without shorting to the regions adjacent to the devices.

(G) P-N junction isolation - Lehovec <sup>3</sup> filed on this on Apr. 22, 1959, and was awarded patent no. 3,029,366 on April 10, 1962. Kilby had filed a lawsuit against Lehovec claiming priority that the P-N junction isolation technique was already anticipated by him in his OA 791,602, which was claimed to have been filed earlier on Feb. 6, 1959. Kilby lost the lawsuit because of the decision by the Board of Patent Interference on this priority sought by Kilby over Lehovec's p-n- junction isolation technique <sup>3, 18.2</sup>. Briefly, the Board ruled "We have carefully examined Patent 3,138,743 but nowhere can we find support for the subject matter of the counts ... Since Kilby has no reduction to practice prior to the filing date of Lehovec, ... priority of counts 1 – 5 is awarded to to Kurt Lehovec, the senior party."

(H) Importance of keeping the filing date Feb. 6, 1959 by Kilby - Because of the lawsuits (see items E and G above), it was quite important for Kilby to insist on keeping the filing date Feb. 6, 1959 as valid. See item D above for details regarding Feb. 6, 1959. The communications from USPTO to Saxena<sup>14, 15</sup> in 2005 negate this validity. However it is difficult to explain why this filing date Feb. 6, 1959 was allowed to be kept in Kilby's patent 3,138,743, and its claims to be re-written, which was in the review process for over 5 years by USPTO. During this period, Noyce's patent for monolithic ICs had been issued, i. e., its contents were public knowledge, and Kilby's lawsuits against Noyce and Lehovec were ongoing. The re-written claims of 3,138,743 and 3,261,081 which were quite different from those in OA 791,602, seem to have been influenced by the then public knowledge of Noyce's patent 2,981,877 and Lehovec's patent 3,029,366.

(I) Possible compromise of the laws of US Patent code 35 USC 112 and associated protocols - The fact that the claims of Kilby's OA 791,602, patent 3,138,743, and patent 3,261,081 were not entirely supported by their specifications (which were almost the same in all three), would suggest a possible compromise of the laws of US Patent code 35 USC 112 and associated protocols. The proceedings in the award of patents 3,138,743, and 3,261,081 to Kilby, in particular allowing the filing date to be kept as Feb. 6, 1959 in view of the lawsuits and their outcomes (see items E and G above), appear rather unusual. Additional issues that further beg clarifications are that all the figures, which are the same in three documents of Kilby (OA 791.602, patent 3.138.743, and patent 3,261,081), show mesa structures for the devices and wire bonded interconnects which are never used in monolithic ICs. Also the figures in patent 3,138,744 show mesa structure, and its text specifies materials and technologies most of which are not used in monolithic ICs. The "shaping said wafer to obtain isolation between said components in said wafer" appears to include mesa etching, and selective formation of p-n junction formation. All the figures show the former but not the latter at all. See also G above regarding the decision by the Board of Patent Interference which ruled against Kilby in favor of Lehovec in this matter of p-n junction isolation. It is also interesting to note that the patents 3,138,743 and 3,138,744 differ in number by only 1, and they were awarded to Kilby on the same date June 23, 1964. Grouping more than one patent to be issued on the same day may not be unusual. But for two successive patents with different sets of claims for achieving the same invention, especially with their strange history, extra long review periods for over 5 years, lawsuits, and awarded on the same date, all of them raise some concern regarding the decisions of USPTO to award Kilby's patents.

(J) Were any of Kilby's patents ever used to manufacture ICs? Perhaps some aspects of the patents may be argued to have been usable, but it is debatable. Did they affect the huge sums of royalties earned by TI and Fairchild from the others? Yes.

(K) Unless the devices (transistors, diodes, resistors and capacitors) are fabricated monolithically, i. e., on the same single chip of a single crystal Si, by,

K.1. PLANAR technology, and

K.2. ISOLATED [by p-n junction, or LOCOS, or trench isolation, or other appropriate technologies], and

K.3. INTERCONNECTED [by monolithic interconnections adherent to the insulator (e.g., SiO<sub>2</sub>) layers without shorting to the adjacent areas and each other], MONOLITHIC ICs cannot be made. Any other approach without these three key criteria gives HYBRID ICs. For a quantitative characterization of adhesion, which was a key issue in Kilby vs. Noyce lawsuit, see Saxena<sup>26</sup>.

The only exception in MONOLITHIC ICs for the passive devices such as resistors and capacitors is that some of them may not need to be fabricated by planar technology; they could be fabricated by thin film technologies as well. However the criteria K.2 and K.3 above still must be met.

In principle, monolithic-ICs could be made with mesa devices, grown (for Si devices) or deposited (for Ge or compound semiconductors) films of  $SiO_2$  and monolithic interconnects. However high leakage currents in such devices, and their unpredictable variations in the devices within a chip and from chip-to-chip in the wafers, would make such monolithic-ICs useless. It will be even worse at the higher integration levels of today.

(L) NOYCE's invention covered all the criteria in K-1, 2 & 3. So his invention was for the MONOLITHIC ICs.

KILBY's invention(s) met only the criterion of fabrication of the devices monolithically, i. e., on the same single chip of a single crystal semiconductor. But Kilby did not specify PLANAR technology in any of his patent(s). Kilby used Ge to demonstrate his reduction to practice, and

L.1 used MESA technology (see figs in his patents), and

L.2. specified ISOLATION by "shaping" with MESA etching, or p-n junctions (this was denied by the Board of Patent Interference in favor of Lehovec), and

L.3 INTERCONNECTED by wire bonds dangling above the chip.

Therefore, KILBY's invention did not meet all the criteria in K-1, 2 & 3. Therefore his invention was not for the MONOLITHIC ICs; instead it was for HYBRID ICs.

(M) The issues in the inventions of ICs are intricately entwined technically, chronologically, and legally patent wise. The analyses of the inventions of Kilby, Noyce, Lehovec, Hoerni and Kooi are complicated anyway. But they have been made more difficult by the mind boggling speed with which the rapid advancements and progress were made, and colossal sums of money were generated, in the IC business. Few had the time or the patience to stop and pay attention to the original key facts of the invention of ICs, and worry about who invented what? Many scientists and engineers have made outstanding contributions to bring the IC industry to its current level of multi-hundred billion dollars per year. Its snowballing effect, however, has not led to a destructive avalanche. Instead, it has revolutionized the entire mankind forever with businesses in many fields amounting to trillions of dollars per year.

The author is privileged to have been involved from the very inception of this magnificent phenomenon when the first few snowflakes were beginning to coalesce and form the initial tiny snowball.

# 8. Conclusion

Based on a critical and thorough review of the invention of the integrated circuits presented here, the conclusions to be drawn are as follows.

Noyce's invention was for the monolithic-IC. It depended crucially on Hoerni's and Lehovec's inventions. Its reduction to practice was done by others using Si planar technology and monolithic Al interconnects.

Kilby's invention was not for monolithic-IC. Its concepts included mesa technology, and wire-bonded Au interconnects which were not adherent to  $SiO_2$  layers. The reduction to practice was done by Kilby using Ge mesa technology and wire bonded interconnects dangling above the chip. From Kilby's patents and the decisions of the Board of Patent Interference on his lawsuits, it appears that the processing of his patents (filing and award of patents) possibly deviated from the normal practice. Whether or not the laws of US Patent code 35 USC 112 and associated

protocols were compromised (see section 7.1.I above), needs further investigation by the experts in that field.

The conclusions drawn here are not meant at all to be pejorative and disrespectful to Noyce, Kilby and all other contributors, or to impugn their contributions. The only objective of this author is to put all the available important facts on record. What is credible evidence depends to a certain degree, in a way similar to beauty, on the eyes of the beholder. Nevertheless, these are the records in writing, and in technical English with engineering precision, not just a pleasure to the eyes.

As an example, Kilby's invention was only for the hybrid-IC, not for monolithic-IC. In his reduction to practice, he had used materials and technologies which are not used at all in the monolithic-ICs manufactured and sold from day one to present. Kilby had only stated the concepts for monolithic-ICs in one of his patents which were partially correct, and that too in a limited way. Also, they were strikingly similar to Dummer's concepts published earlier<sup>21</sup>. All the specifications, drawings in Kilby's issued patent including its claims and in the original application, as well as his reduction to practice, did not support his statements and concepts for monolithic-ICs. Nevertheless, the evidence in his case was adjudged to be credible. Kilby was awarded the Nobel Prize in Physics in 2000 "for his part in the invention of the integrated circuit", but what was his part was not defined. Kilby was a co-recipient, though given twice the amount of financial award than to each of the other two co-recipients (Alferov and Kroemer). Noyce's invention was for monolithic-IC, but it was based only on handwritten notes which were not even witnessed, and he did not reduce his concepts to practice. The latter was done by several of his colleagues. The evidence in his case also was adjudged to be credible, and he was credited with being the co-inventor of the monolithic-ICs. These are the facts, well established in the literature and documented by the dated patent claims. Therefore, no debate should be necessary to decide on their credibility

Both Noyce and Kilby had acknowledged that it was a stroke of good luck for them to have invented the ICs. Good luck did play a greater role for them and their respective versions of the invention of ICs, than it did for several others who did work very hard to make the monolithic-ICs a reality in the marketplace from day one. There are many other scientists and engineers all over the world who also deserve the recognition for their respective invaluable contributions to the invention of monolithic-ICs, and for advancing them to the ULSICs and the super-chips of today. This will require a detailed review which is not the subject of this paper.<sup>3</sup> However, to select a few other than Noyce and Kilby for their fundamental contributions to the invention of ICs, and singling out Moore for his contributions to take the entire industry beyond the IC invention to what it is today, the names (listed alphabetically) of Hoerni<sup>4</sup>, Kooi<sup>5</sup>, Lehovec<sup>3</sup> and Moore<sup>28, 29</sup> should also be on top of the list.

The clap of the thunder of invention of ICs may be gone and belong only to a few. However, the thunder usually lasts momentarily or for a short duration only. But the resulting rains, akin to the invaluable contributions of many, bear the fruits and the crops for a long time to come, whether it is in the Silicon Valley and/or in the other global valleys. Certainly the invention of the ICs has borne, and continues to bear, the fruits and crops like the ULSICs to benefit all mankind. It is almost certain that the additional fruits like the 3D-ICs, UPICs, etc will also become realities in the future and benefit everybody, whether it will be in the author's and audience's lifetimes or not is of little or no consequence.

### 9. Acknowledgements

The author is deeply indebted to a large number of scientists and engineers, with whom he has discussed many aspects of ICs, ULSICs and beyond during the past 46 years. They have provided very helpful advice and comments. It is almost impossible to list all of them. A few key persons from the early years are as follows (listed alphabetically), to whom he is immensely grateful: Gordon Moore, (late) Bob Novce, and Sheldon Roberts. The author is thankful to Toshiaki Masuhara for sending a copy of VLSI Systems Design<sup>6</sup> and nice comments on this manuscript. He also wishes to thank Kurt Lehovec, Dan Maydan, W. K. H. Panofsky, Chih-Tang Sah and Simon Sze for their help and key communications. The personal communications of Julius Blank, Jay Last and Bob Norman on the early work at Fairchild are gratefully acknowledged. (Those in the IC field would know that Blank, Grinich, Hoerni, Kleiner, Last, Moore, Noyce, and Roberts had founded Fairchild, and Moore and Novce later founded Intel.) Thanks are also due to Bo Lojek for sending his book. The author also wishes to thank his daughter-in-law Mrs. Karen Saxena for her help in the preparation of the manuscript. A detailed account of the invention of ICs is planned<sup>30</sup>.

#### 10. References

1. Jack S. Kilby, "Miniaturized Self-Contained Circuit Modules and Method of Fabrication", U. S. Patent No. 3,138,744, filed on May 6, 1959, issued on June 23, 1964.

2. R. N. Noyce, "Semiconductor Device-and Lead Structure", U. S. Patent No. 2,981,877, filed on July 30, 1959, issued on April 25, 1961.

3. K. Lehovec, "Multiple Semiconductor Assembly", U. S. Patent No. 3,029,366, filed on April 22, 1959, issued on April 10, 1962.

4. J. A. Hoerni, "Method of Manufacturing Semiconductor Devices", U. S. Patent No. 3,025,589, filed on May 1, 1959, issued on March 20, 1962.

J. A. Hoerni, "Semiconductor Device", U. S. Patent No. 3,064,167, filed on May 1, 1959, issued on Nov. 13, 1962.

5. E. Kooi, U. S. Patent No. 3,970,486, filed on Oct. 3, 1966, issued on July 20, 1976.

E. Kooi, Ú. S. Patent No. 3,752,711, filed on June 4, 1970, issued on Aug. 14, 1973.

6. George Rostky, "The 30<sup>th</sup> Anniversary of the Integrated Circuit", VLSI Systems Design, CMP Publications Inc., Vol. IX, No. 9A, September, 1988.

7. Michael Riordan and Lillian Hoddeson, "Crystal Fire", W. W. Norton & Company, NY, ISBN: 0-393-31851-6, 1998; Michael Riordan, "The Road to Silicon was Paved with Germanium", p. 134 – 142, Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology, Vol. 98-1, Editors: H. R. Huff, H. Tsuya and U. Gösele. The Electrochemical Society, Pennington, NJ 08534-2896; ISBN: 1-56677-195-1, 1998.

8. Leslie Berlin, "The Man Behind the Microchip: Robert Noyce and the Invention of Silicon Valley", p. 97 – 127; p. 141; Oxford University Press, ISBN – 13: 978-0-19-516343-8, 2005.

9. Alex Braun, Senior Editor, Semiconductor International, August 1, 2005.

10. David C. Brock, "Understanding Moore's Law: Four Decades of Innovation", Chemical Heritage Press, Philadelphia, PA, p. 3 – 108, ISBN 0-941901-41-6, 2006.

11. Jack S. Kilby, "Invention of the Integrated Circuit", p. 648-654, IEEE Transactions on Electron Devices, Vol. ED-23, No. 7, July, 1976.

12. Jack S. Kilby, "Origins of the Integrated Circuit", p. 342 – 349, Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology, Vol. 98-1, Editors: H. R. Huff, H. Tsuya and U. Gösele. The Electrochemical Society, Pennington, NJ 08534-2896, ISBN: 1-56677-195-1, 1998.

13. Jack S. Kilby, "The Integrated Circuit's Early History", p. 109 – 111, Proceedings of the IEEE, Vol. 88, No. 1, January, 2000.

14. E. Bornett, Certifying Officer, USPTO, to Dr. Arjun N. Saxena, "This is to certify that annexed hereto is a true copy from the records of the United States Patent and Trademark Office of those papers of the below identified patent application that met the requirements to be granted a filing date under 35USC111. Application: No. 03/791,602; Filing date: May 06, 1959." Sent by USPTO to Dr. Saxena on September 26, 2005; given as Fig. 5 in this paper.

15. Customer Service Department, USPTO, to Dr. Arjun N. Saxena, "The product or service you requested cannot be fulfilled because the application #03/791,602 does not have an official filing date." Sent by USPTO to Dr. Saxena on November 02, 2005; given as Fig. 6 in this paper.

16. Jack S. Kilby, "Miniaturized Electronic Circuits and Method of Making", Application: No. 03/791,602 claimed to have been filed officially with the US Patent Office on Feb. 6, 1959; referred to in Kilby's patent no. 3,138,744 (see refs. 14 & 15). On this application No. 791,602, the patent no. 3,138,743 was issued on the same date as 3,138,744 (See Table – 2; note the difference in no. by only 1 between these two patents).

17. Chih-Tang Sah, et al, "Diffusion of Phosphorus in Silicon Oxide Film", J. Phys. Chem. Solids, Vol. 11, 288-298 (1959)

### 18. K. Lehovec

18.1 Private communication, September 10, 2006.

18.2 K. Lehovec, "Invention of p-n Junction Isolation in Integrated Circuits", p. 495-496, IEEE Transactions on Electron Devices, Vol. ED-25, No. 4, April, 1978.

[Ref. no. 6 in Lehovec's paper: J. S. Kilby, US Application 811-476 filed on May 6, 1959. *This is the key patent no. 3,138,744 of Kilby;* refiled as US Application 218-206 on Aug. 16, 1962. *Nothing happened on this refiling.*]

[Ref. no. 7 in Lehovec's paper: ---- (Kilby), "Miniaturized electronic circuits," US Patent 3,183,743, issued June 23, 1964, filed Feb. 6, 1959. [*This is incorrect; it is NOT Kilby's patent. This US patent no.3,183,743, "Sheet Cutting Machine", was filed by Francis O'Donnell, Francis Hallatt, Arthur Hallatt, and Fritz Doerscheln on July 17, 1962, Ser. No. 210,421, and it was issued on May 18, 1965. This has nothing to do with ICs.*] The correct patent no. should have been 3,138,743.

## 19. Hans J. Queisser:

19.1 "Materials Research in Early Silicon Valley – and Earlier Yet", p. 4 - 25, Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology, Vol. 98-1, Editors: H. R. Huff, H. Tsuya and U.

Gösele. The Electrochemical Society, Pennington, NJ 08534-2896; ISBN: 1-56677-195-1, 1998.

19.2 Private communication at 4217 Pomona Avenue, Palo Alto, CA 94306; November 17, 2001.

19.3 Seminar at Stanford University, Stanford, CA 94305; December 11, 2001

19.4 "Slow Solar Ascent", March meeting of German Physical Society (2004).

20. A. N. Saxena, "Method of Coating Selective Areas of the Surface of a Body", U. S. Patent No. 3,687,722, filed on March 10, 1971, issued on Aug. 29, 1972.

# 21. G. W. A. Dummer:

21.1 "Electronic Components in Great Britain", Proc. Components Symp., Washington, DC, p. 15 - 20, May 6, 1952.

21.2 "Integrated Electronics Development in the United Kingdom and Western Europe", Proc. IEEE, P. 1412 – 1425, December, 1964.

22. Arjun N. Saxena, "Methods for and Products of Growth of Single-Crystal on Arrayed Nucleation Sites (SCANS) Defined in Nucleation Unfriendly Substrates", U. S. Patent No. 6,110,278, filed on Aug. 10, 1998, issued on Aug. 29, 2000.

23. Arjun N. Saxena, "Semiconductor Device with Single Crystal Films Grown on Arrayed Nucleation Sites on Amorphous and/or Non-Single Crystal Surfaces", U. S. Patent No. 6,392,253, filed on Aug. 6, 1999, issued on May 21, 2002.

24. Arjun N. Saxena, "Transistors to ICs to ULSICs and Beyond: Impact on Various Applications to Improve the Quality of Human Life", IETE-Golden Jubilee Compendium, p.23-31, ISBN 81-901477-2-2, 2003.

25. A. N. Saxena, "Roadmap of Future Monolithic ICs", VMIC State-of-the-Art Seminar, p. 8 (1989); A. N. Saxena, K. Ramkumar, S. K. Ghosh & M. A. Bourgeois, "Technology and Reliability Issues of Multilevel Interconnects in Bipolar, BiCMOS and CMOS VLSIC/ULSIC", Proc. IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), p. 12-19 (1993).

26. Arjun N. Saxena, "Current status and future directions of ultra large scale integrated circuits and the crucial role of adhesion science and technology", First International Congress on Adhesion Science and Technology, *Mittal Festschrift*, p.137-146, W. J. Van Ooij and H. R. Anderson, Jr. (Eds.), VSP, ISBN 90-6764-291-6, 1998.

27. Arjun N. Saxena, "Technologies to Extend the Validity of Moore's Law: New Business Opportunities in Microelectronics", p. 1-2, & p. 1-7, June 2 (1998); private communication to Gordon Moore, Intel, June 4 (1998).

28. G. E. Moore, "Progress in Digital Integrated Electronics", IEDM Technical Digest, p. 11 - 13 (1975); G. E. Moore, "Lithography and the Future of Moore's Law", Optical/Laser Microlithography VIII: Proc. SPIE, 2440, p. 2 - 17, Feb. 20 (1995); G. E. Moore, "No exponential is forever - some approaching limits to VLSI technology", Keynote address, VLSI Multilevel Interconnection Conference (VMIC), unpublished (1993).

29. G. E. Moore, "Moore's Law at 40", Chapter 7, p. 67 – 84, "Understanding Moore's Law: Four Decades of Innovation",

Edited by David C. Brock, Chemical Heritage Press, Philadelphia, PA, ISBN 0-941901-41-6, 2006.

30. Arjun Saxena, *Invention of Integrated Circuits: Untold Important Facts and Impact on Future ICs*, World Scientific Publishing Company, 2008.

31. Michael F. Wolff, "The genesis of the integrated circuit", IEEE Spectrum, p. 45 – 53 (1976).

32. T. R. Reid, "The Chip – How Two Americans Invented the Microchip and Launched a Revolution", Random House, New York; ISBN 0-375-7528-3; TK7874.R43 (2001).

33. Thomas H. Lee, "The (Pre-) History of the Integrated Circuit: A Random Walk", IEEE SSCS News, Vol. 12, No. 2, Spring 2007.

34. Robert N. Noyce, "Microelectronics", Scientific American, Vol. 237, p. 63 (1977).

35. Bo Lojek, "History of Semiconductor Engineering", ISBN-10-3-540-34257-5, Springer (2007).

36. R. Norman, J. Last and I. Haas, "Solid-State Micrologic Elements", IRE Solid State Conference, Feb. 12, 1960; cf. Lojek <sup>35</sup>, p. 137, Fig. 4.33.

# About the Author

Dr. Arjun N. Saxena is an Emeritus Professor of the Rensselaer Polytechnic Institute. He has both state of the art industrial experience and advanced academic background. He has been a Director and Professor, and established major R & D programs at Rensselaer, and at several industrial corporations. He is an inventor or co-inventor of major semiconductor technologies which are used currently in manufacturing. He has had over 40 years of experience in the multibillion dollar Si VLSI/ULSIC field, microelectronics technologies and other high-tech areas. He has served as the Consulting Editor of a book series on Microelectronics Manufacturing. He is a Life Senior Member of IEEE. A graduate fellowship has been established at Rensselaer Polytechnic Institute in his and his wife's name for advanced research in microelectronics, because of his teaching and their substantial donation. Prior to 1960, Dr. Saxena has published in and contributed to the fields of Nuclear Shell Structure and High Energy Physics at the Institute of Nuclear Physics, India, and at Stanford University. He earned the PhD degree in Physics from Stanford and is listed in the Who's Who in the World and Who's Who in America.

#### Important Facts

1. What was the basic concept of the invention as written in their key patents: Kilby's 3,138,744; Noyce's 2,981,877 ? Note: Kilby did not refer in his 1998 paper <sup>12</sup> to 3,138,744; instead he chose to refer to 3,138,743 in which the concept of monolithic-ICs was NOT mentioned at all in its text or the claims. Controversy over application no. 791,602 filed on Feb. 6, 1959 for patent no. 3,138,743. (See section 5.)

2. What was actually invented as

described in the issued patent?

3. First public disclosure of

4. Test circuit(s) defined.

5. Reduction to practice of original

6. Proof of the original invention.

invention.

invention.

## Table - 1

#### Kilby

"....various circuit elements including diodes, transistors, and resistors all be formed within a single block of semiconductor material, thereby eliminating the necessity for separate fabrication of the semiconductor devices and the interconnections as mentioned above." (cf: Kilby<sup>1</sup>: column 1, lines 58-62; it is not written in Kilby <sup>16</sup>). *The basic concept stated above* was only partly consistent with the concept of monolithic-ICs, and that too in a limited way. Kilby did not state nor specify how these devices formed within a single block of semiconductor were to be interconnected within the same block of semiconductor for a given IC, and assure that the interconnects and the devices were properly isolated electrically. Also regarding the fabrication of the devices within a single block of semiconductor, Kilby did not even suggest, what to say of giving, the correct procedures in his issued patent<sup>1</sup> to accomplish what he had stated. The reduction to practice, and the materials and technologies specified by Kilby in his patent<sup>1</sup> and in the original application <sup>16</sup> to fabricate the devices and the interconnects were not consistent with the monolithic-ICs.

Hybrid-IC with mesa devices, not planar devices; wire-bonding of devices, not monolithic interconnects (cf: Figs. 3 & 4 of patent<sup>1</sup>; Figs. 4, 5, 6 & 8 of original application <sup>16</sup>).

Application serial no. 811,486 filed on May 6, 1959 for patent no. 3,138,744. (Controversy over application serial no. 791,602 filed on Feb. 6, 1959 for patent no. 3,138,743. See section 5.)

Yes (phase-shift oscillator; multivibrator)

Yes; Phase-shift oscillator - used a single Ge mesa transistor (not used in ICs), glued Ge to glass slide (not used in ICs), wire-bonded (not used in ICs) to 2 resistors and a capacitor; Multivibrator - used 2 Ge mesa transistors, glued Ge to glass slide, wire-bonded to 6 resistors and 2 capacitors. US Patent nos. 3,138,743 and 3,138,744 (note their nos. differ by only one) issued on the same date Jun. 23, 1964; contested in courts for their delayed issue 3 yrs after Noyce's patent; Kilby's suit was lost partially because it was resolved that both Noyce's and Kilby's patents were essential for ICs; Kilby's suit against Lehovec<sup>3, 17, 18</sup> for p-n junction isolation was also lost (see section 6).

No

No

7. Contributions to planar and monolithic-IC technologies?

8. Contributions to other advanced IC technologies, 3D-ICs and UPICs <sup>24-26</sup> ?

### Noyce

"....the present invention utilizes dished junctions extending to the surface of a body of extrinsic semiconductor, an insulating surface layer consisting essentially of oxide of the same semiconductor extending across the junctions, and leads in the form of vacuum-deposited or otherwise formed metal strips extending over and adherent to the insulating oxide layer for making electrical connections to and between various regions of the semiconductor body without shorting the junctions.' (cf: Noyce<sup>2</sup>: column 1, lines 24 32). Noyce says it all in the very first paragraph of this patent. This is essentially how the monolithic-ICs are made.

Monolithic-IC.

US patent filed on Jul. 30, 1959. (Note that this was after Kilby's filed on May 6, 1959.)

No (but done by others).

No (but done by the others using Si planar technology, and Al interconnects adherent and contiguous to SiO<sub>2</sub>, which are used in ICs).

US Patent no. 2,981,877 issued on Apr. 25, 1961. (Note that this was much earlier than Kilby's patent issued on June 23, 1964.)

Yes; 4 US Patents since the above IC patent was issued.

Co-founded Intel Corporation whose engineers are leading the world in inventing and putting into manufacturing practice the new technologies.

# Table – 2

|                                            | Patent #                                                                                                                                                                                                                                                         | Filing date                                                                                                                                                                                                        | Issue date                                |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| _ Kilby <sup>16</sup><br>(ICs)             | 3,138,743<br>Application<br>Serial No.<br>03/791,602.                                                                                                                                                                                                            | Claimed by<br>Kilby to be<br>Feb. 6, 1959.<br>(No official<br>record <sup>15</sup> of this<br>filing date.<br>Official records<br>show only May 6,<br>1959, as the filing<br>date <sup>14</sup> . See Figs. 5, 6.) | June 23, 1964*                            |

| _ Lehovec <sup>3</sup><br>(Isolation)      | 3,029,366                                                                                                                                                                                                                                                        | Apr. 22, 1959                                                                                                                                                                                                      | April 10, 1962                            |

| _ Hoerni <sup>4</sup><br>(Planar Tech.)    | 3,025,589<br>3,064,167                                                                                                                                                                                                                                           | May 1, 1959<br>May 1, 1959                                                                                                                                                                                         | Mar. 20, 1962<br>Nov. 13, 1962            |

| _ Kilby                                    | 3,072,832                                                                                                                                                                                                                                                        | May 6, 1959                                                                                                                                                                                                        | Jan. 8, 1963                              |

| _Kilby                                     | 3.115,581                                                                                                                                                                                                                                                        | May 6, 1959                                                                                                                                                                                                        | Dec. 24, 1963                             |

| - Kilby <sup>1</sup><br>(ICs)              | 3,138,744                                                                                                                                                                                                                                                        | May 6, 1959                                                                                                                                                                                                        | Jun. 23, 1964* (Key patent)               |