D. a. Chesnut <del>103</del> Chem. Bldg. 310

# WILLIAM M. RICE INSTITUTE For the Advancement of Literature, Science, and Art

# **COMPUTER MANUAL**

A MANUAL

FOR

## THE RICE INSTITUTE COMPUTER

September 1, 1958

To the reader of this manual:

In the text which follows references have been made to sections which are not included at this time because they are currently being prepared. Also, we expect to compile from time to time addendum and errata which would render your copy of the manual more useful.

If you would like to receive this material, please fill out the form below and mail to:

> Computer Project The Rice Institute Houston 1, Texas

Please mail material to be included in <u>A Manual</u> for the Rice Institute Computer to:

Name \_\_\_\_\_

Position \_\_\_\_\_

Address \_\_\_\_\_

### TABLE OF CONTENTS

|                                         | F                                                   | age |  |  |  |  |  |  |

|-----------------------------------------|-----------------------------------------------------|-----|--|--|--|--|--|--|

| I.                                      | Computer Organization                               | . 1 |  |  |  |  |  |  |

| II.                                     | Octal Notation                                      | . 6 |  |  |  |  |  |  |

| III.                                    | Numerical Word Structure                            | . 9 |  |  |  |  |  |  |

| IV.                                     | Addressing System                                   | .12 |  |  |  |  |  |  |

| v.                                      | Instruction Word Structure                          | .16 |  |  |  |  |  |  |

|                                         | 1. Field 1                                          | .18 |  |  |  |  |  |  |

|                                         | 2. Field 4                                          | .20 |  |  |  |  |  |  |

|                                         | 3. Field 2                                          | .23 |  |  |  |  |  |  |

|                                         | 4. Field 3                                          | .44 |  |  |  |  |  |  |

| VI.                                     | Examples of Single Instructions                     | 46  |  |  |  |  |  |  |

| VII.                                    | Indicators                                          | 52  |  |  |  |  |  |  |

| VIII.                                   | Tagging, Trapping, and Repeat                       | 57  |  |  |  |  |  |  |

| IX.                                     | Electrostatic Storage or Memory                     | 61  |  |  |  |  |  |  |

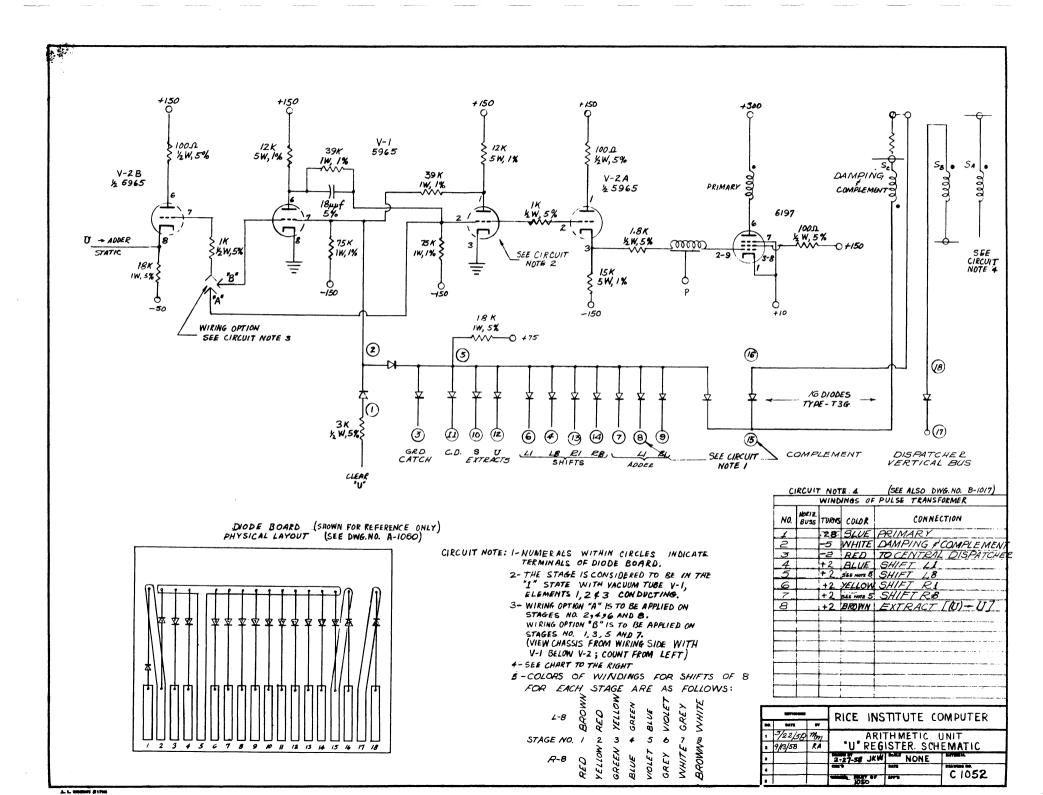

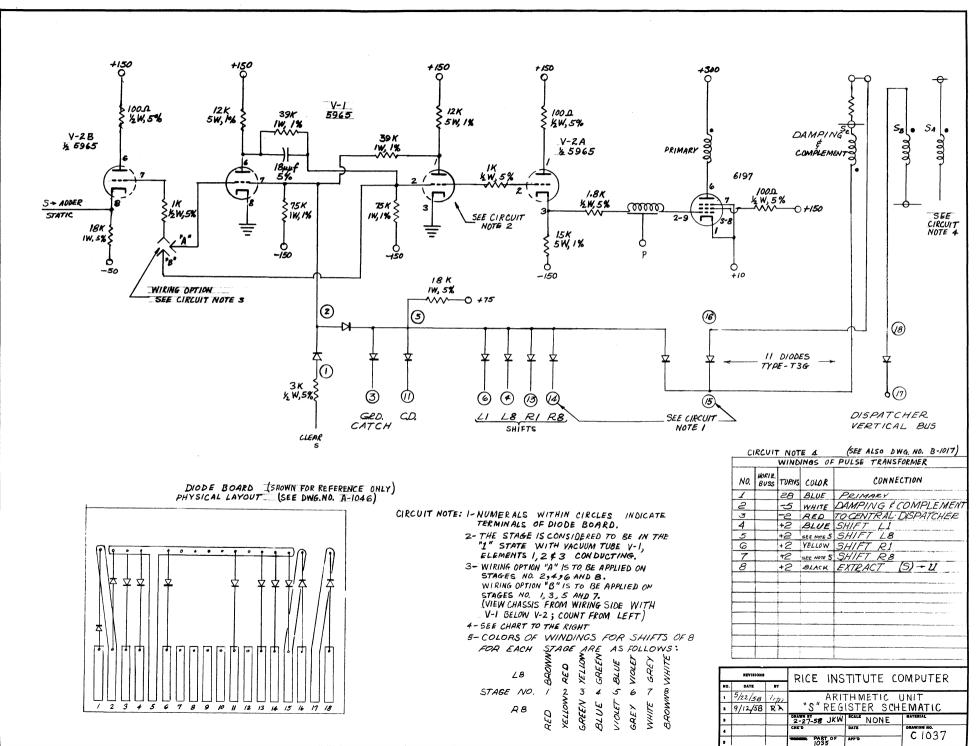

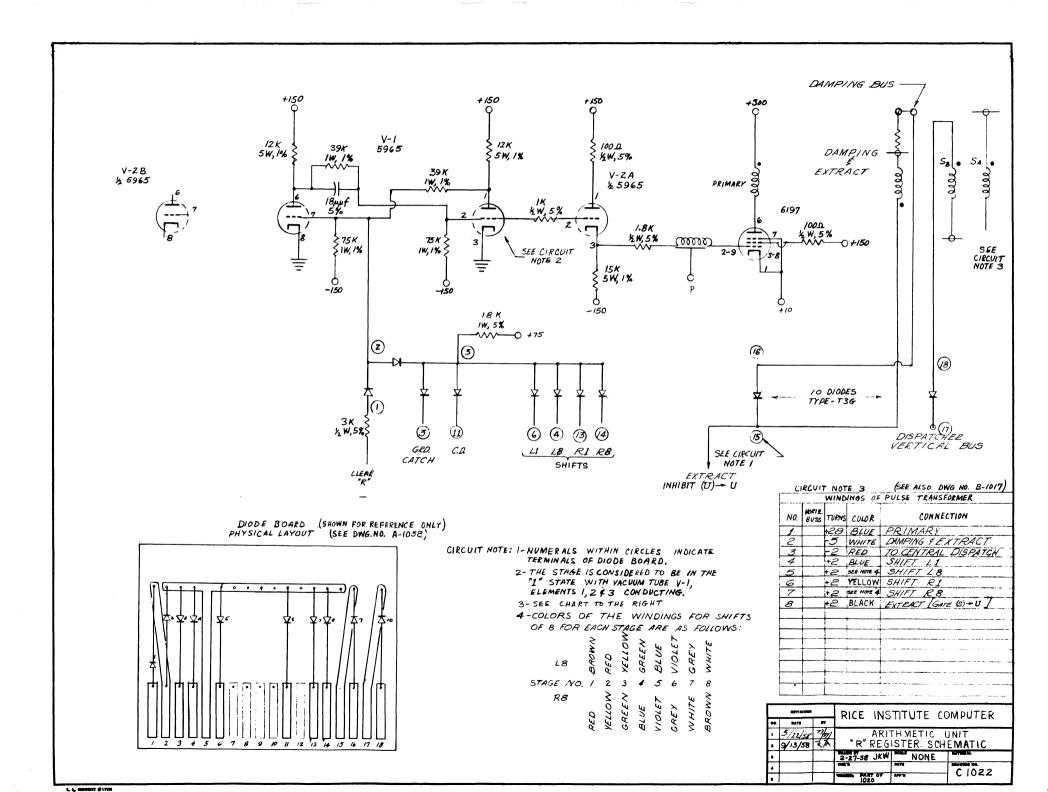

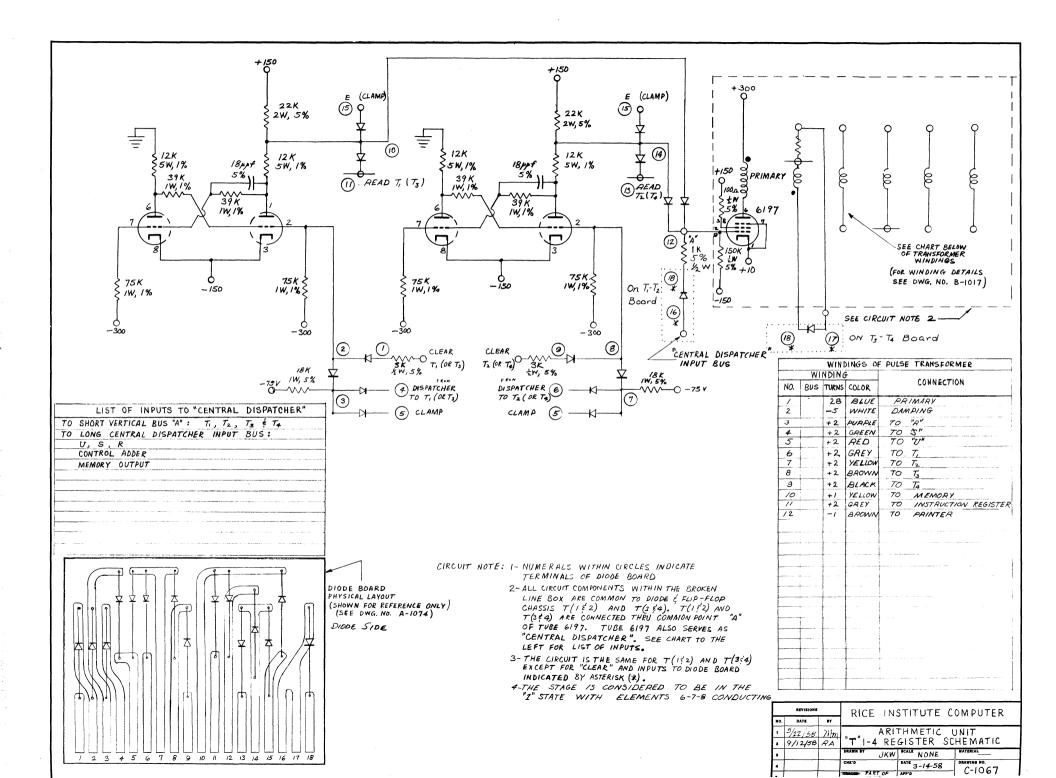

| х.                                      | Arithmetic Unit                                     | 64  |  |  |  |  |  |  |

| XI.                                     | Control Unit                                        | 69  |  |  |  |  |  |  |

| XII.                                    | Complement Arithmetic                               | 76  |  |  |  |  |  |  |

| XIII.                                   | Printer Output                                      | 79  |  |  |  |  |  |  |

| XIV.                                    | Punched Paper Tape                                  | 88  |  |  |  |  |  |  |

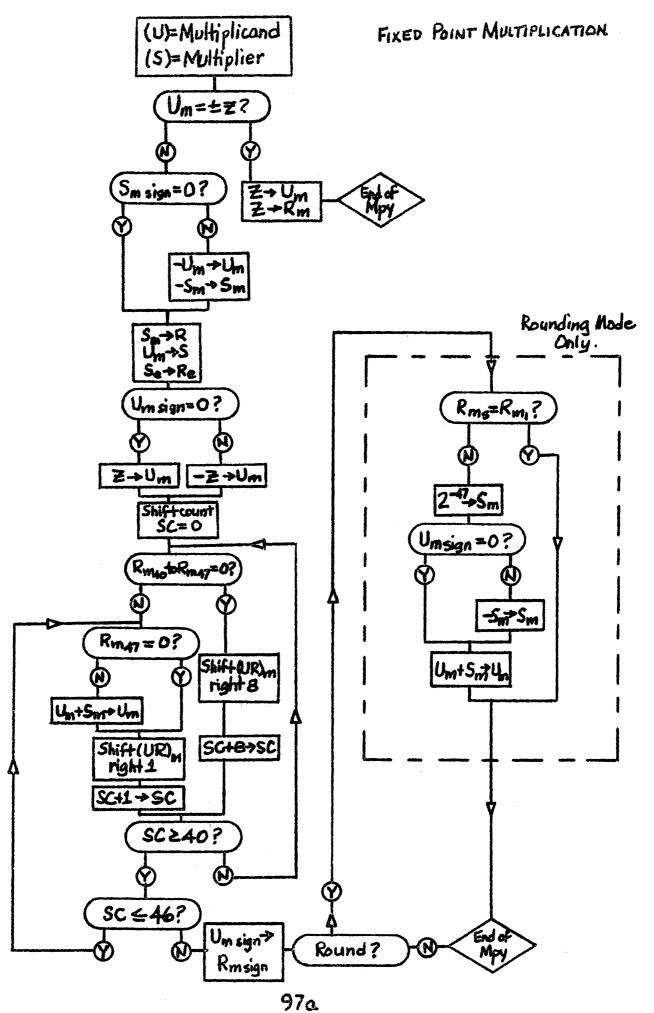

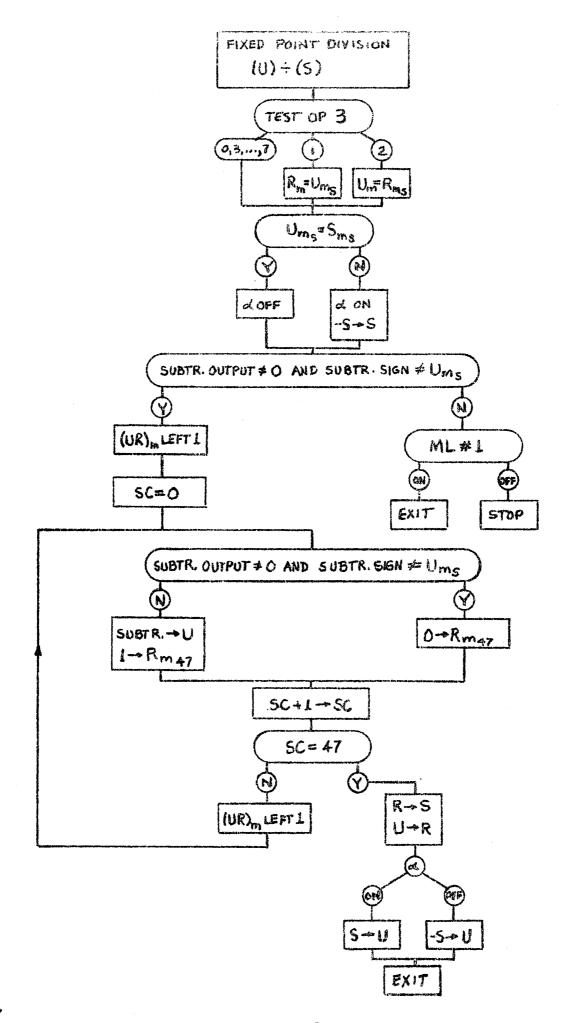

| XV.                                     | Fixed Point Arithmetic                              | 92  |  |  |  |  |  |  |

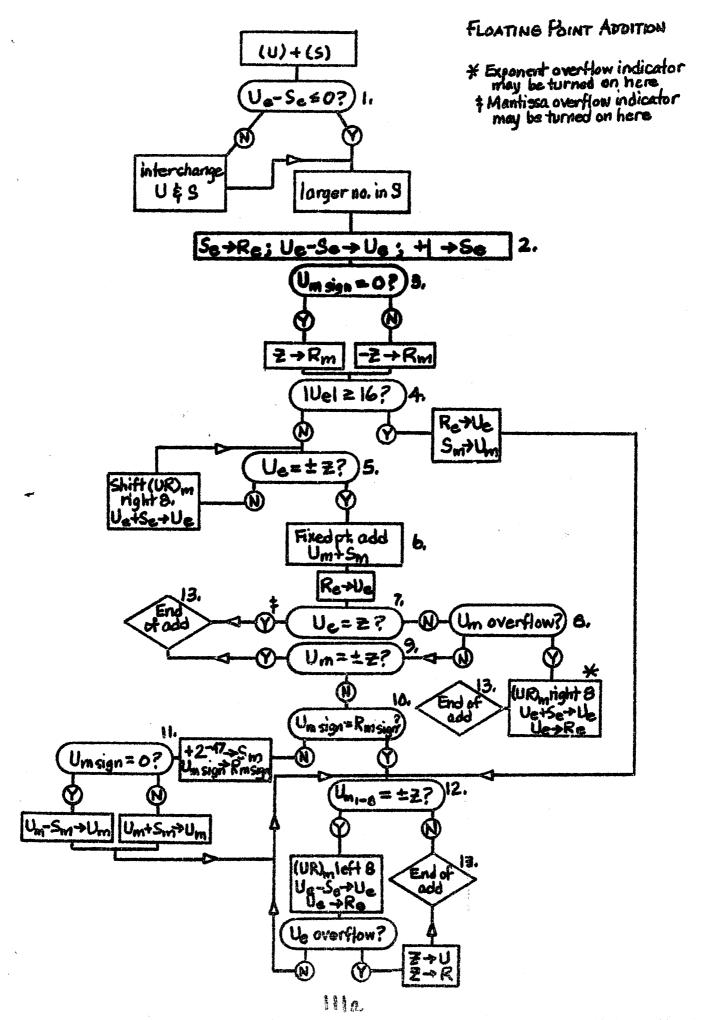

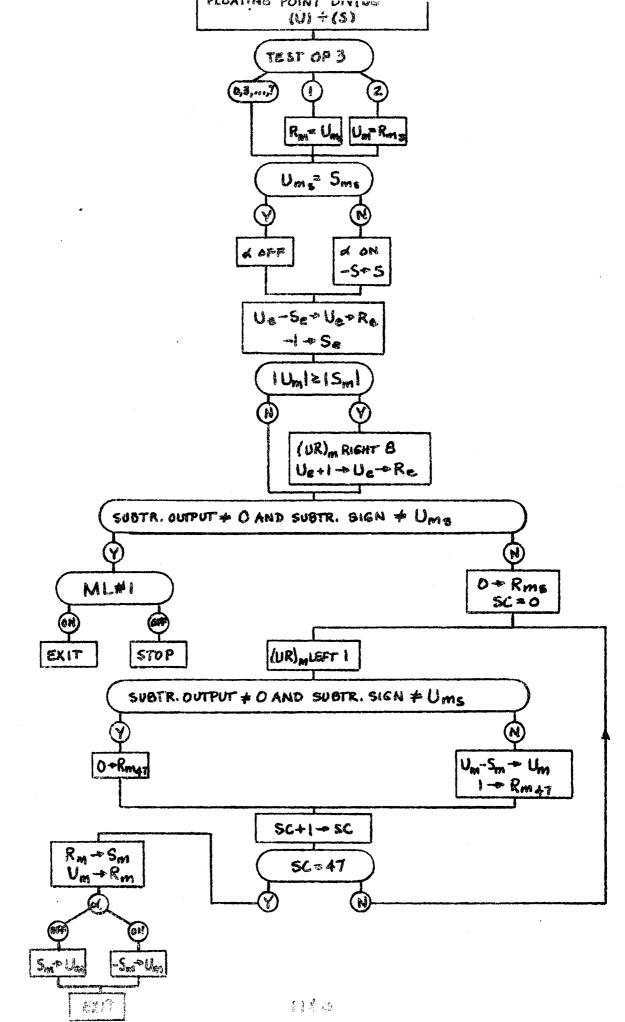

| XVI.                                    | Binary Point Location and Floating Point Arithmetic | 100 |  |  |  |  |  |  |

|                                         | Index                                               | 111 |  |  |  |  |  |  |

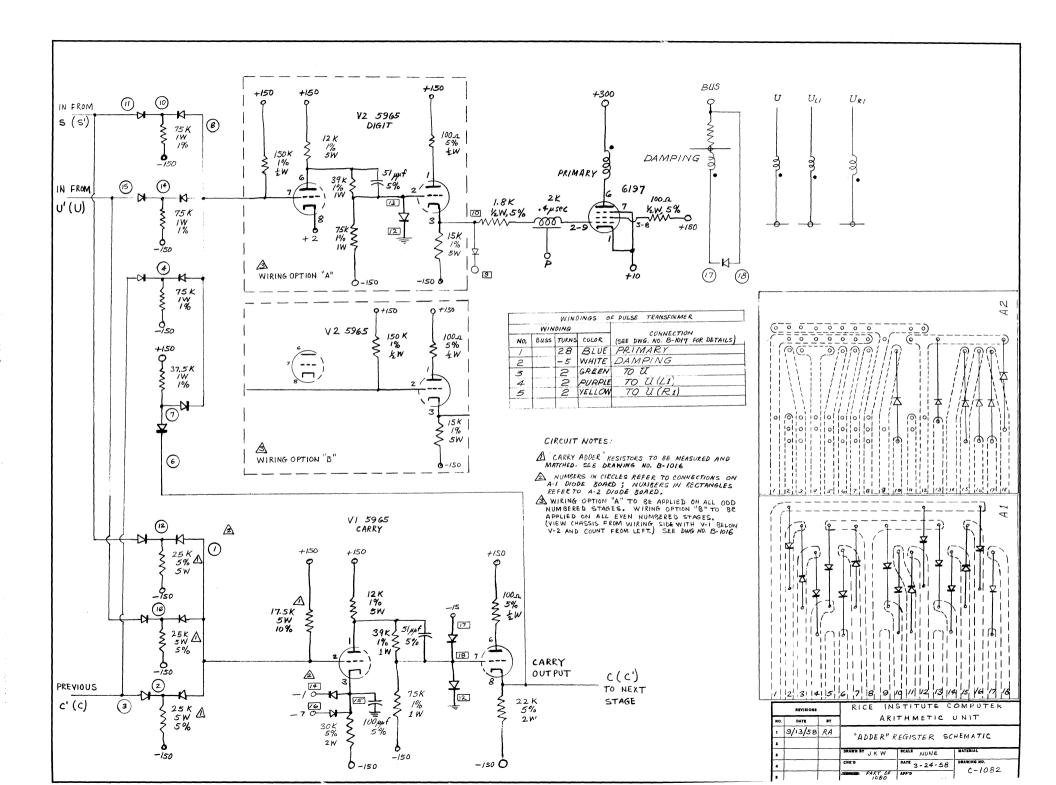

| Append                                  | ix 1: Electronics of the Computer                   |     |  |  |  |  |  |  |

|                                         | I. Arithmetic Unit                                  |     |  |  |  |  |  |  |

| Appendix 2: A Symbolic Assembly Program |                                                     |     |  |  |  |  |  |  |

| Appendix 3: A Sample Routine            |                                                     |     |  |  |  |  |  |  |

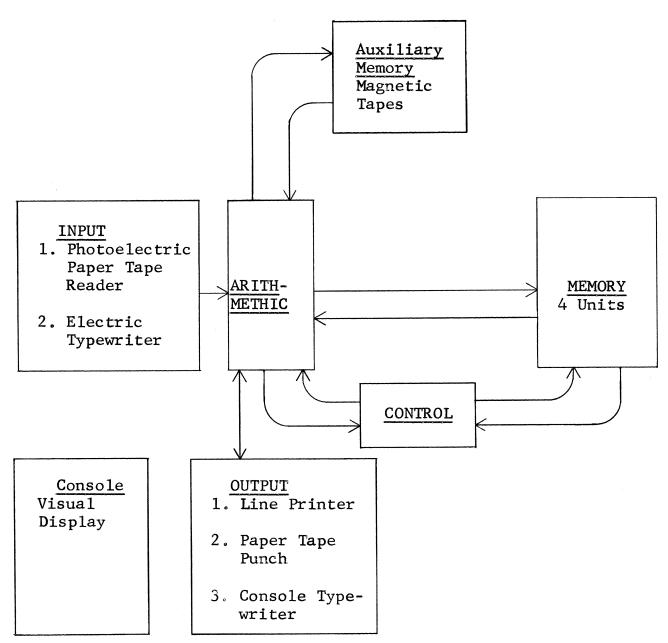

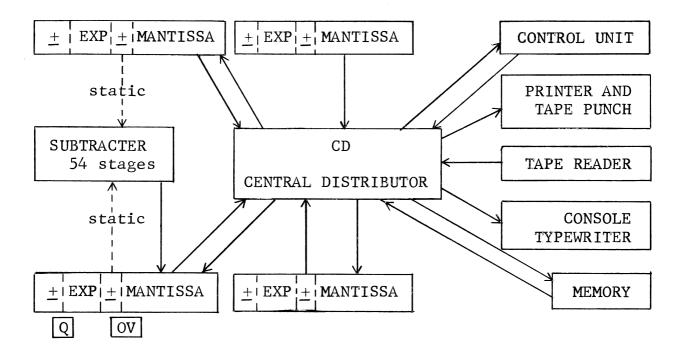

Figure I. Functional parts of the digital computer and their relationships. The arrows represent information flow.

#### COMPUTER ORGANIZATION

The modern digital computer consists of five distinct groups of equipment which perform the following functions:

- (1) input

- (2) memory or storage

- (3) arithmetic

- (4) control

- (5) output

Figure I is a block diagram of these units showing the relationships among them.

The <u>input section</u> consists of a photoelectric reader which takes information from punched paper tape and places it in memory and an electric typewriter which can be used to type information into the arithmetic and control sections. The arithmetic unit is always an intermediate in the flow of input information to memory. The information in question may be anything which can be stored in memory: numbers, instructions, or alphabetical and numerical comments.

The <u>memory</u> is an information-holding device composed of 64 electrostatic storage tubes. One memory contains 55 storage tubes and is subdivided into distinct units called words. The memory is needed to record numbers and hold instructions. Thus, each word may be a number, an instruction, or a coded comment. Each memory unit is capable of recording up to 8,192 words, and the computer in its final form will have 4 memory units.

The memory may be thought of as N little boxes or locations where numbers or instructions can be located. Each of the locations is given an identification number from 8 to N (the numbers 0 to 7 are reserved for a purpose to be explained later). The label of a location is called its address (synonyms: cell, location, box). Note that the address 1371 does not mean that we can find the number 1371 stored there - except by accident; the address is purely a label or identifying number.

A memory location can hold only one word at a time, and placing a word in a location automatically destroys whatever was there previously. It is possible to read a number out of memory without destroying or removing it. A detailed description of the word and the memory unit is given in the section on electrostatic memory.

The <u>arithmetic section</u> does what its name implies. In addition to the basic arithmetic operations, this unit can shift numbers right and left and assist in certain operations which make it possible for the computer to make decisions. If we use the analogy of a desk calculator, this section corresponds to the upper, lower and middle dials plus the wheels and gears that actually do the calculation. A detailed description is given in the section under the heading of arithmetic unit.

Register is a term commonly used in connection with these various units. It denotes a device for temporarily storing a

piece of information while or until it is used. A register corresponds quite closely to the dials on a desk calculator. Not only numbers but also instructions may be stored in a register.

The whole computer is controlled by a certain set of specified permissible operations, and no two such operations can occur simultaneously. The permissible operations may be executed in any desired sequence. It is up to the user to specify the sequence of operations or, as it is commonly called, the program. Each permissible operation can be specified in a concise coded form called an order (synonym: instruction). For a problem to be solved on a computer, it must be broken down into a series of precise steps and this sequence is coded and usually stored in memory as ordinary numbers. The correspondence between the set of permissible operations and the set of numbers which specify them is called the order code and is described in the section on instructions.

The <u>control section</u> of the machine has the function of accepting orders one by one and of interpreting or decoding these instructions and then sending signals to the other units telling them what to do. The control unit is equivalent to the operation buttons which are pushed on a desk calculator. The control section is described in detail in another section.

The <u>output units</u> are an automatic punch for paper tape

and a fast line printer. The printer can print up to 600 lines per minute - each line containing up to 108 characters. Information may also be permanently recorded (or written) on magnetic tape.

#### SUMMARY of MACHINE CHARACTERISTICS:

The Rice Institute Computer is a megacycle computer (i.e., a basic pulse time of about 1 microsecond) with a speed that is appropriate to:

(1) memory access time for reading of 10 microseconds

- (2) memory access time for writing of 20 microseconds

- (3) an addition time of 4 microseconds

(4) an average multiplication time of 120 microseconds. The machine is asynchronous, binary and parallel in operation and will have a random access memory of 32,000 words.

#### OCTAL NOTATION

Binary numbers are very well adapted to representation by electronic circuits. Since each digit can have only two different values, zero or one, the digits of a binary number can be put into one-to-one correspondence with the electrical conditions of off-on, open-closed, non-conducting-conducting, etc. We pay for this simplicity (i.e., small amount of information per digit) by needing more digits to represent a given amount of total information than if we had used a larger number base. For example, a decimal number with N significant figures is equivalent to a binary number with N ln 10/ln 2 = N/0.30103 = 3.321 N digits. For example, the standard numerical word in the Rice Computer will have between 40 and 47 significant binary places. This is equivalent to about 12 to 14 decimal places.

The problem of conversion between base two and base ten is actually simple but need not concern the reader at the moment. The process will be carried out essentially automatically by the computer by means of subroutines, so that the average machine user will supply decimal input data and the computer will deliver decimal final results.

In order to discuss the instruction word and numerical word structure of the computer, we must use the full 54 bit binary machine words. It is very inconvenient to write out

II.

such words in full and it is equally inconvenient to type them into a typewriter-tape punch. As a shorthand, we shall introduce "octal" notation. The binary number is divided into triads (groups of three bits). Instead of writing each triad in full, we shall write instead an integer between zero and seven inclusive:

| <u>binary</u> | <u>octal</u> |

|---------------|--------------|

| 000           | 0            |

| 001           | 1            |

| 010           | 2            |

| 011           | 3            |

| 100           | 4            |

| 101           | 5            |

| 110           | 6            |

| 111           | 7            |

| and and a set |              |

Each triad is thought of as an octal integer, and the digit written is the usual symbol for this integer. The reader is advised to memorize as soon as possible this conversion table. This conversion is of course very easy in either direction. The resulting shorthand number is actually the equivalent of the binary number written to base eight, i.e., an octal number. A 54 bit machine word becomes an 18 octal digit number, much more manageable in length. We shall use expressions such as "the second octal figure" and "the second triad" essentially synonymously. In the computer we shall have triads; on paper or at the typewriter punch we shall use octal figures.

As an example, 00010101001010100111 is equivalent to 000, 101, 011, 001, 010, 100, 111 is equivalent to 0531247.

The octal form is obviously much easier to write and to absorb at a glance.

In referring to an octal or binary number we read it from left to right. For example, "the first octal figure" refers to the figure furthest to the left (0 in the above example); "the second octal figure" or "the second triad" in the number above is 5.

#### NUMBER REPRESENTATION

A number  $x = m \cdot (256)^e$  is represented by the number pair (m,e) where m and e are referred to as the mantissa and exponent, respectively. The actual computer representation of m and e depends upon the location of x. There are two cases one must consider, (a) the representation in storage; and (b) the representation in the arithmetic registers U and S.

(a) Representation in storage.

In all storage locations (electrostatic memory, R and T registers) the number is a sequence of 54 binary bits, 6 exponent bits and 48 mantissa bits, numbered as follows:

|    |                | 1              |                | 2              |                | 1              | 3              |                |                | 4              |                |                | 5              |                |                 |                     |                 |                 | 18              | 1               | į      |

|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|---------------------|-----------------|-----------------|-----------------|-----------------|--------|

| <  |                | 4              | <u> </u>       |                |                | <-             |                |                | /              |                |                | - m            |                |                | 1               |                     | 1               | Γ               |                 | >               | r<br>1 |

|    |                |                |                |                |                |                |                |                |                |                |                |                |                |                |                 |                     |                 | 1               |                 |                 | Ī      |

| es | <sup>e</sup> 1 | <sup>e</sup> 2 | <sup>e</sup> 3 | <sup>e</sup> 4 | <sup>e</sup> 5 | <sup>m</sup> s | <sup>m</sup> 1 | <sup>m</sup> 2 | <sup>m</sup> 3 | <sup>m</sup> 4 | <sup>m</sup> 5 | <sup>m</sup> 6 | <sup>m</sup> 7 | <sup>m</sup> 8 | <sup>m</sup> 9* | ••• <sup>m</sup> 43 | <sup>m</sup> 44 | <sup>m</sup> 45 | <sup>m</sup> 46 | <sup>m</sup> 47 |        |

Each bit is a 0 or \* 1.  $m_s$  is termed the sign bit of m and  $e_s$  the sign bit of e (0 means +, 1 means - ). The number representation is what is usually called the 1's complement system and can be explained as follows. For simplicity and convenience in explanation we will regard the binary point as being located between  $m_s$  and  $m_1$ . In floating point operations this is the only interpretation possible, while in fixed point work the location of the binary point can be chosen by the coder.

mantissa

$$m_{s} = 0; m = m_{1} \cdot 2^{-1} + m_{2} \cdot 2^{-2} + \dots + m_{47} \cdot 2^{-47}$$

$$m_{s} = 1; m = -(\bar{m}_{1} \cdot 2^{-1} + \bar{m}_{2} \cdot 2^{-2} + \dots + \bar{m}_{47} \cdot 2^{-47})$$

III

9a

where  $\bar{m}_i$  is the bit-complement of  $m_i$ : that is, if  $m_i = 0$ ,  $\bar{m}_i = 1$  and if  $m_i = 1$ ,  $\bar{m}_i = 0$ . To clarify this system consider as an example a 4-bit mantissa:

| <sup>m</sup> s | <sup>m</sup> 1 | <sup>m</sup> 2 | <sup>m</sup> 3 |   |                                                              |

|----------------|----------------|----------------|----------------|---|--------------------------------------------------------------|

| 0              | 1              | 0              | 0              | - | $1 \cdot 2^{-1} = 1/2$                                       |

| 0              | 0              | 1              | 1              | = | $1 \cdot 2^{-2} + 1 \cdot 2^{-3} = 3/8$                      |

| 1              | 0              | 1              | 1              | = | $-(1^2 2^{-1}) = -3/2$                                       |

| 1              | 1              | 0              | 0              | = | $-(0 \cdot 2^{-1} + 1 \cdot 2^{-2} + 1 \cdot 2^{-3}) = -3/8$ |

exponent

$e_s = 0; e = e_1 \cdot 2^5 + e_2 \cdot 2^4 + \dots + e_6 \cdot 2^0$  $e_s = 1; e = -(\bar{e}_1 \cdot 2^5 + \bar{e}_2 \cdot 2^4 + \dots + \bar{e}_6 \cdot 2^0)$

As an example consider the following exponents

<sup>e</sup>s <sup>e</sup>1 <sup>e</sup>2 <sup>e</sup>3 <sup>e</sup>4 <sup>e</sup>5

$0 \ 0 \ 0 \ 1 \ 1 = + 3$

$1 \quad 1 \quad 1 \quad 1 \quad 0 \quad 1 = -(1 \cdot 2^{1} + 0 \cdot 2^{0}) = -2.$

The zero is a special case that must be given careful consideration. A sequence of all zeros in m is called a logical zero (sometimes a + zero) while a sequence of all ones in m is called an arithmetic zero (sometimes a -0). The word "zero" by itself will refer to either +0 or -0.

In the exponent e, all ones represent the arithmetic zero and all zeroes, by convention, represent an exponent  $\leq$  -32. The reason for this will become clear when floating point operations are discussed.

Since the octal notation is often useful, the reader is advised to study the following examples.

10a

| <u>Octal Machine</u> | Number                 | Value                                                                                                   |

|----------------------|------------------------|---------------------------------------------------------------------------------------------------------|

| 00000 \              |                        | (zero (or "plus zero")                                                                                  |

| 00200                | Fixed point numbers    | ) 1/2                                                                                                   |

| 00777                | rixed point numbers    | zero (or "minus zero")                                                                                  |

| 00577)               |                        | - 1/2                                                                                                   |

| 77000 )              |                        | $(256)^{0} \times 0.0$ $(256)^{-2} \times 0.5$ $(256)^{2} \times (-0.5)$ $(256)^{-31} \times (0.03125)$ |

| 75200                |                        | (256) <sup>-2</sup> × 0.5                                                                               |

| 02577 }              | Floating point numbers | 5 (256) <sup>2</sup> $	imes$ (-0.5)                                                                     |

| 40020 )              |                        | $(256)^{-31} \times (0.03125)$                                                                          |

In fixed point numbers the choice of the exponent is left to the coder, who will, however, find it advantageous to use a "plus zero" exponent. A nonzero floating point number will never have 00 for an exponent.

(b) Representation in U and S.

In the arithmetic registers the number is a sequence of 56 binary bits, 7 exponent bits and 49 mantissa bits, numbered as follows:

| : e                                                           | >  <                                         | <        |                                                             | <b>m</b>                                          | >                                                  |

|---------------------------------------------------------------|----------------------------------------------|----------|-------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

| e <sub>s</sub> e <sub>0</sub> e <sub>1</sub> e <sub>2</sub> e | 3 <sup>e</sup> 4 <sup>e</sup> 5 <sup>m</sup> | ns mo m1 | <sup>m</sup> 2 <sup>m</sup> 3 <sup>m</sup> 4 <sup>m</sup> 5 | <sup>m</sup> 6 ••• <sup>m</sup> 43 <sup>m</sup> 4 | 44 <sup>m</sup> 45 <sup>m</sup> 46 <sup>m</sup> 47 |

The two bits  $e_0$  and  $m_0$ , called the exponent overflow and the mantissa overflow respectively, have no representation in storage. In S,  $e_0$  is always equal to  $e_s$  and  $m_0$  is always equal to  $m_s$ . Thus the  $e_0$  and  $m_0$  bits in S as described below are only virtual concepts. However in U the  $e_0$  and  $m_0$  bits are actual stages in the register. Whenever a number is transferred to U from some other register, the computer automatically sets  $e_0 = e_s$  and  $m_0 = m_s$ . We note, however, that these two bits ( $e_0$  and  $m_0$ ) in U are unaffected when (U) -> U as described later in the interpretation of Field 1.

The bits  $(e_0, m_0)$  are only altered upon arithmetic operations and arithmetic shifts as explained in the section describing overflow and underflow. Whenever a number is stored, all bits except  $e_0$  and  $m_0$  are transferred to their corresponding positions in storage. It is convenient to consider the binary point in the mantissa (to be located to the right of the  $m_0$  bit. In this manner we can give the following interpretation to the numbers in U: mantissa

U is capable of working with mantissae in the range -2 to +2, using the following convention:

m<sub>g</sub> m<sub>0</sub> range

| (1         | 0 | $-2 < m \leq -1$    | $ \mathbf{m}  - 1 = \bar{\mathbf{m}}_1 \cdot 2^{-1} + \bar{\mathbf{m}}_2 \cdot 2^{-2} + \dots + \bar{\mathbf{m}}_{47} \cdot 2^{-47}$ |

|------------|---|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| <b>(</b> 1 | 1 | $-1 < m \leq 0$     | $ \mathbf{m}  = \bar{\mathbf{m}}_1 \cdot 2^{-1} + \bar{\mathbf{m}}_2 \cdot 2^{-2} + \dots + \bar{\mathbf{m}}_{47} \cdot 2^{-47}$     |

| 0          | 0 | $0 \leq m < 1$      | $m = m_1 \cdot 2^{-1} + m_2 \cdot 2^{-2} + \dots + m_{47} \cdot 2^{-47}$                                                             |

| 0          | 1 | 1 <u>&lt; m</u> < 2 | $m - 1 = m_1 \cdot 2^{-1} + m_2 \cdot 2^{-2} + \dots + m_{47} \cdot 2^{-47}$                                                         |

Whenever, as a result of an operation, m falls in the range -2 to -1 or 1 to 2, it has overflowed the range of the storage locations and an overflow indicator will be turned on when appropriate (see section entitled "overflow").

#### exponent

In U the exponent has an extended range in which  $-63 \le e \le +63$ .

12a

| e<br>s | e <sub>0</sub> |                     |

|--------|----------------|---------------------|

| 1      | 0              | -63 ≤ e ≤ -32       |

| 1      | 1              | -31 ≤ e ≤ 0         |

| 0      | 0              | $0 \leq e \leq +31$ |

| 0      | 1              | +32 <u>≤</u> e ≤ 63 |

Exponents in range +32 to +63 are said to have overflowed and an appropriate overflow indicator will be turned on if this occurs. Exponents in the range -63 to -32 are said to have underflowed the storage range. By convention a zero exponent is represented by all 1's, and all zeros will indicate an exponent smaller than -31.

The question probably occurs to the reader: Why do we use the large base 256 rather than the more obvious value of 2? The choice of base depends upon consideration of a number of factors ( the number range desired, the minimum and maximum mantissa accuracy desired, the details of the shifting technique used in standardisation of numbers, the proportion of arithmetical combinations that may be expected to require a final standardization, etc.). Our choice appears to be about optimum. We lose very little as compared with base two; we gain a great deal, particularly in that floating point operations will be carried out (on the average) very nearly as fast as fixed point operations.

13a

#### ADDRESSING SYSTEM

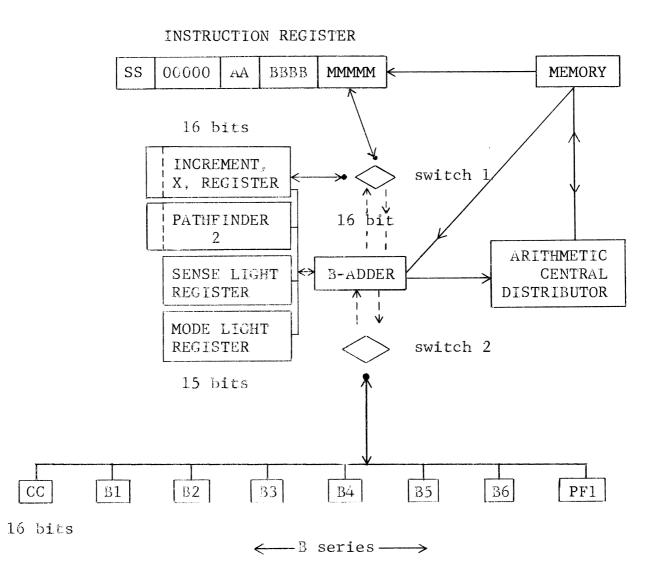

The Rice Computer will have eight full length (54 bit or 18 triad) registers (the A series), eight address or index-/5 ing (15 bit or 5 triad plus one sign bit) registers (the B series), eight special purpose (15 or 16 bit) registers, and an electrostatic memory of 2<sup>15</sup> -16 or 32,752 full length words. The A and B series are jointly known as F registers. The special purpose and F reigsters are fast registers, having an access time of the order of one microsecond. The electrostatic memory addresses have an access time of about ten microseconds. The A series and the special purpose registers, together with the electrostatic series are known as M addresses.

The execution of every instruction by the computer involves (1) procuring two operands, one from an F address and one from an M address, (2) some arithmetical or logical work on these two operands, and (3) the storage of some result at an F address or a modification of the contents of some B register.

IV.

A SERIES

| address | abbreviation   | <u>full name</u>      |

|---------|----------------|-----------------------|

| 0       | 0              | zero or null register |

| 1       | U*             | universal*            |

| 2       | R              | remainder             |

| 3       | S              | storage               |

| 4       | T <sub>4</sub> | temporary store 4     |

| 5       | T <sub>5</sub> | temporary store 5     |

| 6       | T <sub>6</sub> | temporary store 6     |

| 7       | т <sub>7</sub> | temporary store 7     |

\*Note: The U register plays a special role in arithmetic operations and has 55 bits - the extra bit is called an overflow bit and its use will be explained in the detailed description of arithmetic operations. This overflow bit is always set, when a number is sent to U. equal + a the sign bit

B SERIES

| address | abbreviation    | full name       |

|---------|-----------------|-----------------|

| 0       | CC              | control counter |

| 1       | <sup>.B</sup> 1 | B register 1    |

| 2       | B <sub>2</sub>  | " 2             |

| 3       | <sup>B</sup> 3  | " 3             |

| 4       | B <sub>4</sub>  | <b>"</b> 4      |

| 5       | <sup>B</sup> 5  | " 5             |

| 6       | <sup>B</sup> 6  | " 6             |

| 7       | PF1             | pathfinder      |

M addresses range from 0 to 77777 (octal) (i.e., 0 to 32767 decimally), with 0 to 7 being from the A series and 10 to 77767 being true electrostatic memory addresses and 77770 to 77777 being the addresses of a class of special registers.

Register 0 does not actually exist. By definition it always contains zeros. The uses of address 0 will appear later. U and S (and sometimes R) are used to hold the operands of arithmetical or logical operations. After an operation, U and R hold the result.  $T_4$  through  $T_7$  are used to temporarily store words.

CC holds the address of the next instruction word to be fetched to the instruction register (see discussion of instruction register in section on control unit). B<sub>1</sub> through B<sub>6</sub> contain address increments to be used in certain logical manipulations of instructions. PF1 is set to the current an unconditional classo reading of CC immediately before a transfer or skip is executed.

### SPECIAL PURPOSE REGISTERS

| address                          | abbreviation         | name                                                                    | description<br>CC<br>description<br>on all modifications<br>of CC other<br>than the normal |

|----------------------------------|----------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 77770                            | PF2                  | pathfinder 2                                                            | CC<br>→PF2 before trans-<br>fer or skip executed                                           |

| 77771                            | SL                   | sense light<br>register                                                 | holds sense light<br>information                                                           |

| 77772                            | Х                    | increment or<br>index register                                          | adds special purpose<br>increments to B series<br>registers                                |

| 77773                            | ML                   | mode light<br>register                                                  | holds mode light in-<br>formation                                                          |

| 77774<br>77775<br>77776<br>77777 | TR<br>IR<br>reserved | <i>trapping</i> register<br><i>indicator</i> register<br>for future use | holds trapping information<br>holds indicator information                                  |

PF2 and X are 16 bit registers (5 triads plus sign); the use of the X register is described in the discussion of field 3 operations. SL and ML are 15 bit registers and are described fully in the section on indicators. INSTRUCTION WORD STRUCTURE

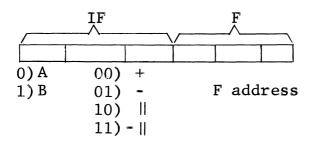

All instruction words are divided into four major fields. These fields are further subdivided as follows:

| field | triad    | name       | use                  |

|-------|----------|------------|----------------------|

| 1     | $\int$ 1 | IF         | inflection on F      |

| T     | 2        | F          | F address            |

|       | 5        | С          | class                |

|       | 4        | 0p1        |                      |

| 0     | 5        | Op2        |                      |

| 2     | 6        | 0p3        | 4 operation triads   |

|       | 7        | Op4        |                      |

| 2     | 5 8      | ISt        | inflection on store  |

| 3     | 9 ک      | St         | store address        |

|       | ✓ 10     | IM         | inflection on M      |

|       | 11       | IA: 1 bit  | indirect address bit |

|       |          | BM: 8 bits | B modification of M  |

|       | 13       |            |                      |

| 4     |          |            |                      |

|       | 15       |            |                      |

|       | 16 >     | М          | memory address       |

|       | 17       |            |                      |

|       |          |            |                      |

V.

An instruction word is decoded and interpreted by the computer in the I register. We shall first take an overall View of the results of this decoding, then return later to a detailed view of each section.

5

- (1) The computer consults CC and fetches the contents of the indicated address to the I register. CC is advanced by 1.

- (2) Field 1 (2 triads, IF and F) is decoded. Consequence: a word in an F address (generally a numerical word) is sent to U.

- (3) Field 4 (9 triads, IM, IA, BM, M) is decoded. Consequence: a word is sent to S and an address (possibly new) is left in position M of I.

- (4) Field 2 (5 triads, C, Opl, Op2, Op3, Op4) is decoded. Consequence: in general, arithmetical or logical work is done using the contents of U and S and/or the final address M (which have been set up by the two preceeding steps). If the operation is arithmetical, the primary answer will be found in U and the secondary answer (if there is one) in R.

- (5) Field 3 (2 triads, ISt, St) is decoded. Consequence: the contents of either U or R is sent to an F address or certain changes may be made in the contents of one of the B registers.

- (6) Return to step (1).

We shall use from now on the convention that an address symbol in parentheses means the contents of that address location; the address symbol alone means the numerical value of that address. For example:

(M) represents the 54 bit word located at M

M represents a 15 bit numerical address

(B<sub>4</sub>) represents a 15 bit number and sign stored in  $\rm B_4$  SUMMARY:

The common features of every instruction, <u>without</u> exception, are:

- (1) a number  $\rightarrow U$

- (2) an address  $\rightarrow$  M in I

- (3) a number  $\rightarrow$  S

The instruction may then operate with any or all of these three results.

#### 1. Field 1

The two triads of field 1 (IF,F) determine the F address of a word which is brought to U and the modification of its sign. F is a fast address. Bit 1 of IF determines whether we mean an A or a B address, a zero for A and a 1 for B. The contents of this address are fetched to U. Bits 2 and 3 of IF determine a sign modification according to the scheme: 00 means + (no sign change)

01 " - (change sign)

- 10 " || (absolute value)

- 11 " || (negative of absolute value)

For convenient reference we quote again a table of F addresses:

|    |      | <u>A</u>       | <u> </u>       |

|----|------|----------------|----------------|

| 0  | 000  | 0              | CC             |

| 1  | 001  | U              | <sup>B</sup> 1 |

| 2  | 010  | R              | <sup>B</sup> 2 |

| 3  | 011  | S              | <sup>B</sup> 3 |

| 4  | 100  | T <sub>4</sub> | B <sub>4</sub> |

| .5 | 10 p | т5             | <sup>B</sup> 5 |

| 6  | 110  | <sup>T</sup> 6 | <sup>B</sup> 6 |

| 7  | []]  | T <sub>7</sub> | PF1            |

Examples of field 1:

| 037 ROOM     |    | means      | $zero \longrightarrow U$   | clear     |

|--------------|----|------------|----------------------------|-----------|

| 000 con      | 01 | \$1        | (U) $\longrightarrow$ U    | no change |

| ornande fait | 40 | ŧĭ         | (CC) $\longrightarrow$ U   |           |

| bbe Tor      | 05 | <b>9</b> 8 | $(T_5) \longrightarrow U$  |           |

| DOI 107      | 15 |            | $-(T_5) \longrightarrow U$ |           |

Examples of field 1 (continued):

| 010 10             | 25 | means | $ (T_5)  \longrightarrow U$  |

|--------------------|----|-------|------------------------------|

| 311 10°<br>311 10° | 35 | • 1   | $- (T_5)  \longrightarrow U$ |

| 130 101            | 45 | **    | $(B_5) \longrightarrow U$    |

Whenever an integer from any B register is sent to a 54 or 56 bits of the B register are bit register (for example, U), the 15 <del>bit magnitude is</del> written

in the right hand end of the register and the sign bit of the

B register is sent to the sign bit of the long register. All mantissa, including the overflow bit, are set equal to the value of the first bit (that on the left and) of the B register are eleared to zero. When using operations of this sort it is convenient to regard this number as an integer (either positive or negative).

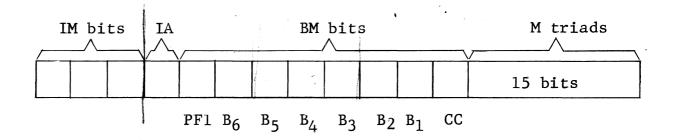

#### 2. Field 4

The nine triads of field 4 (IM, IA, BM, M) determine what word is brought to the S register and the final address residing in the I register. <u>M</u> is a 5 triad octal address. 00000 through 00007 refer to A addresses; 00010 through 77767 refer to electrostatic memory addresses; and 77770 through 77777 refer to the special purpose registers. BM consists of 8 bits. Counting from right to left, they refer to the 8 B addresses: CC,  $B_1$  through  $B_6$ , and PF1. The M address as written will be modified by the sum of the contents of the B registers referred to. A zero means ignore, a 1 means use. For example:

ΒM

001

000

01

10

|     | meaning                          |  |  |

|-----|----------------------------------|--|--|

| 010 | add $(B_1) + (B_3) + (B_6)$ to M |  |  |

| 000 | add (PF1) to M                   |  |  |

00001add (CC) to M00000101add (CC) +  $(B_2)$  to M

Field 4 is decoded according to the following sequence.

Field 4 is decoded according to the following sequence:

- (1) If bit 4, 5, or 6 of trapping register is 1 and control tag register = 1, 2, or 3 respectively, transfer to 41, 49, or 57, respectively.

- (2) BM is decoded and a new M is formed in I

$M + \Sigma(B_i) \rightarrow M$

(M is incremented by the contents of all of the B registers referred to in BM.)

(3) Test IA bit

if 0, go to step 4

if i, form new IA, BM, M in I (last 24 bits of (M) -> I), then return to step 1.

(4) Test bit 1 if IM

if 0,  $(M) \rightarrow S$

if 1,  $M \rightarrow S$  (last 15 bits of S, all others cleared to zero)

(5) Test bits 2, 3 of IM and modify the sign of (S) as follows:

00 means + (no sign change)

Ol means - (sign change)

10 means || (absolute value)

11 means - || (negative absolute value)

(6) If bit 1, 2, or 3 of the trapping register is 1 and the arithmetic tag register = 1, 2, or 3 transfer to 9, 17, or 25 respectively.

At the end of this sequence some word will have been sent to S, with or without sign modification. This word may have come from the original M address (no 1's in BM). It may have come from M incremented by any or all of the B registers

101

(note the possibilities and flexibility in the fact that the B series includes CC, PF1, and the regular B indexing registers, singly or in combination). It may have come from an address (with B modification) looked up in memory (IA bit 1). This procedure may be repeated indefinitely. Finally, we have a choice of obtaining either the contents of the final M address or the address itself, with or without sign modification in either case.

Most operations will work with the contents of U (set up by field 1) and the contents of S. Some operations, however, ignore (S) and use the final M. Examples: shifts of U and/or R, set or increment B from address, and transfers. In these cases, a 10 microsecond memory fetch time can be saved by writing a 1 in bit 1 of IM. These operations can be controlled by M. They can also be controlled by the M portion of (M) by use of the IA bit.

#### 3. Field 2

The five triads of field 2 determine what arithmetical or logical operation takes place. C is decoded first and determines the class of the operation:

| <u>C</u> | class                              |

|----------|------------------------------------|

| 0        | control: compare, skip,or transfer |

| 1        | arithmetic                         |

| 2        | store, substitute, set tag         |

<u>class</u>

$\underline{\mathbf{C}}$

| 3 | not used - reserved for future use  |

|---|-------------------------------------|

| 4 | B register modify, set sense, shift |

| 5 | logical arithmetic                  |

| 6 | input-output                        |

| 7 | special functions                   |

Class 0 - Control: Compare, Skip, or Transfer

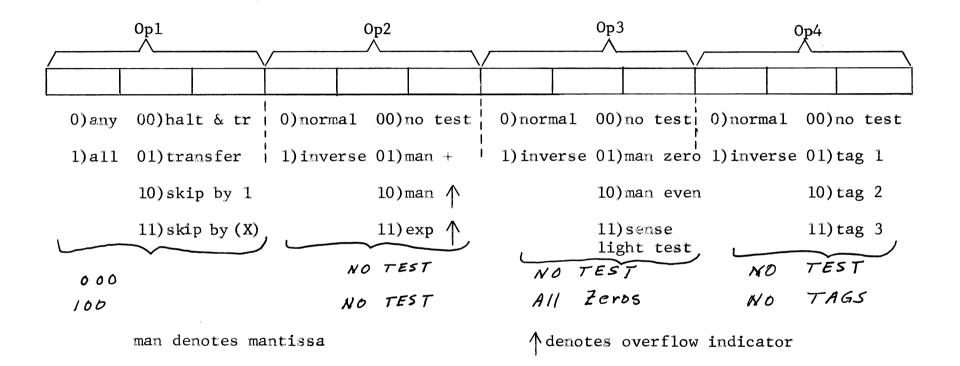

This is a very flexible family of conditional transfers. Op2, Op3, and Op4 are used to specify a set of zero, one, two, or three tests. The inverse of every test is possible. Bit 1 of Op1 specifies whether we mean a favorable outcome for the whole test to be (0) a favorable outcome from any one test, (1) a favorable outcome from all tests. Bits 2 and 3 of Op1 give the action to be taken on favorable outcome, i.e., some special adjustment of CC.

### class 0 operations

The first bit of Op2, Op3, and Op4 indicates whether we mean the normal form or the inverse form of the indicated test.

The various tests are applied to:

- (1) special indicators (e.g., overflow, tag, etc.)

- (2) (U) (S) (floating point subtraction)

- (3) sense register

In case (2), the exponents of (U) and (S) are tested. If they are both zero, effectively a fixed point subtraction is carried the result of the subtraction goes to U, and S is cleared to zero. out; and both (U) and (S) are left unchanged. If both exponents are not zero, a floating point subtraction is carried out, and (U) and (S) are possibly changed by shifting and normalizing procedures. In either case, the quantity (U) - (S) is not available in U after the test.

In a transfer order M denotes the address to which one is transferring; thus the number in S is not used. If Op1 = 0, 1, 4, or 5, zero—>S before the test and we test (U) - 0 = (U). In view of this, one can also say that the computer has two classes of control orders:

- (1) test (U) and/or indicators and then transfer to M

- (2) compare (U) with (S), test indicators and then skip by 1 or (X)

If no tests are specified (i.e., an ignore test in Op2, 3, and 4), the function specified in Op1 will be executed unconditionally. Op1:

- 0) on any test successful, halt; transfer to M when start button is pressed

- 1) on any test successful,  $M \rightarrow (CC)$  (transfer)

- 2) " " " , (CC) +  $1 \rightarrow$  (CC) (skip)

on any test successful, (CC) + (X)  $\rightarrow$  (CC) (relative 3) transfer) on all tests successful, halt; transfer to M when start 4) button is pressed \*\* 11 ŧī 11 5) ,  $M \rightarrow (CC)$ 11 11 11 11 6) , (CC) + 1 $\rightarrow$ (CC) 11 #1 11 11 , (CC) + (X)  $\rightarrow$  (CC) 7)

Op2:

0) ignore Op2

1) mantissa positive?

2) mantissa overflow?

3) exponent overflow?

4) ignore Op2

5) mantissa negative?

6) no mantissa overflow?

7) no exponent overflow?

Op3:

- 0) ignore Op3

- 1) mantissa 2 + 0 or 0?

- 2) mantissa lower bit zero? (equivalent to "mantissa even"?)

- 3) sense lights designated by 1's in M on?

- 4) ignore Op? is revery bit in U zero?

5) mantissa nonzero?

6) manitssa lower bit one? (equivalent to "mantissa odd"?)

7) sense lights designated by 1's in M off?

**Op4**:

0) ignore Op4

1) tag indicator 1 on?

2) tag indicator 2 on?

3) tag indicator 3 on?

4) tag indicators all off?

5) tag indicator 1 off?

6) tag indicator 2 off?

7) tag indicator 3 off?

(4 is not the true inverse of 0 but appears to be too useful to leave out.)

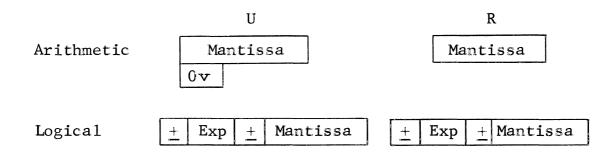

Class 1 - Arithmetic

At the present, only Op2 is used. Op1, Op3, and Op4 As denoted by OP2 will be ignored and may be written as zeros.  $\sqrt{(U)}$  and (S) are combined as follows:

Op2operation0)fixed point addition1)fixed point subtraction2)fixed point multiplication

3)

5)

6)

7)

fixed point division

4) floating addition

floating subtraction

floating multiplication

floating division

With OPI = 30r7 (division order), OP3 may be Used as follows:

OP 3 :

- 0) Leave (U) and (R) unchanged (double length dividend)

- 1) Clear (Rm) to sign of (Um) before division (single length dividend)

- 2) Clear (Um) to sign of (Rm) before division (integer division)

That is, bit 1 determines fixed or floating arithmetic while 2 and 3 determine +, -, x,  $\ddagger$ . In addition and subtraction, (U)  $\pm$ (S) $\rightarrow$ U. In multiplication, the most significant 47 bits of the mantissa of (U) x (S) go to U, with the remaining 47 bits going to R. The exponent and sign of mantissa of R are set to agree with U. The manitssa of R is merely the continuation of the mantissa of U. Division is exactly the reverse of multiplication. (U), with the mantissa of R being understood as the continuation of the mantissa of U, is divided by (S). The exponent and sign of (R) is ignored. The quotient appears in U and the remainder in R.

In fixed point addition, the exponent part of S is simply transferred to U, replacing the previous exponent. Thus, a fixed point addition with field 1 = 0, 0 is a load (or fetch)command. However, a logical "or" with field 1=0,0 is the usual load order. NSERT

<u>Class 2</u> - Store or Substitute, Set Tag

Op1:

- 0) store  $(U) \rightarrow M$

- 1) substitute part of  $(U) \rightarrow M$ ; in detail, part of  $(u) \rightarrow 5$ ,

- 2) add to memory: (U) + (S)  $\rightarrow M$

- 3) substitute to memory: part of (U) + (

3) substitute to memory: part of [(U) + (S)] → M (unless a 1 has been used in bit 1 of IM, (S) will have come from M) Not used

(1), 5), (), 7) tag location M (no. in M is not affected)

Op2: not used

Op3: this triad is interpreted only for substitute orders (1 or

- 3 in Op1)

- 0) substitute the M triads of (U), i.e., last 5 triads into S and store (S)→M; note that the former contents of M are in S if correct IM is used.

- 1) substitute right half (27 bits) of (U) $\rightarrow M$

- 2) substitute left half (27 bits) of  $(U) \rightarrow M$

Op4: this triad may adjust the tag at address M

- 0) set tag to no tag

- 1) set tag to tag 1

- 2) set tag to tag 2

3) set tag to tag 3

4) Sond contents of arithmetic tag register to tag bits at M

5), 6), 7) ignore tag (do not change tag) on M)

We can store (U), substitute from (U), or add (U) to memory and at the same time clear, adjust, or ignore the tag condition at M. One note of caution about the substitute order is needed. The order actually substitutes part of U into S and then stores (S) at M. In order to be a true substitute in memory order, one must be sure that bit 1 of IM is zero (i.e., (M) must first come to S).

We also note that the overflow bit in U cannot be transferred to memory since it exists only in U. Class 3 - Not Used

Class 4 - B Register Arithmetic, Shift, Set Sense and Mode Lights

The operations of this class are all controlled by the final 15 bit integer M in I. The original M is used as a number or control symbol unless IA = 1. The particular operation is specified by the triad in Opl as follows: Opl:

- 0) increment  $(B_i)$  by M, i.e.,  $(B_i) + M \rightarrow B_i$

- 1) arithmetic shift of U/R by M places

- /urn on

2) -set sense lights designated by 1's in M

- 3) logical bit count of (R) for M places

- 4) set  $(B_i)$  to M, i.e.,  $M \rightarrow B_i$

- 5) logical shift of U/R by M places *furn off*6) set mode lights designated by 1's in M

- 7) not used

With Op1 = 0 or 4, Op2 designates which B register is to be set to M or incremented by M, as follows: Op2:

- $\begin{array}{ccc} \text{O} & \text{B}_{0} \equiv \text{CC} & \text{A} & \text{B}_{4} \\ \text{A} & \text{B}_{1} & \text{C} & \text{C} \end{array}$

- 1) B<sub>1</sub> 5) B<sub>5</sub>

- 2) B<sub>2</sub> 6) B<sub>6</sub>

- 3)  $B_3$  7)  $B_7 = PF1$

# INSERT :

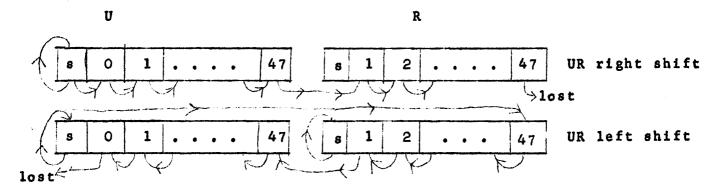

In an arithmetic shift of U or R to the right the sign is propogated to the right as many places as the contents of the register are shifted. In an arithmetic shift of U or R to the left, the sign fills in those places on the right into which nothing is being shifted. <u>Shifting</u>: a short discussion of shifting in the Rice Computer will help clarify this set of instructions.

Consider a shifting register (e.g., U or R). This register may be considered to have a "donor" and an "acceptor" stage for bits. For example, when U shifts right,  $\longrightarrow$ , the right hand stage is the "donor" and the left hand stage is the "acceptor".

The shifts fall into two major classifications: (1) arithmetic and (2) logical. In the arithmetic class, the left hand bit of U is the overflow bit just to the left of the mantissa and the right hand bit is bit number 54; the left hand bit of R is bit number 8 (the highest order bit in the mantissa) and IN SERT the right hand bit of R is again number 54. In the logical shifts, the entire word for both U and R is used, that is, the exponent sign, exponent, sign, and mantissa (the overflow bit in U being ignored). Thus for the logical shifts, the left hand bit is bit number 54.

Each register (U or R) may be shifted right or left M  $(mod 2^7)$  times, taking into its "acceptor" stage either zeros or the spill from the "donor" of the other register. The

number of bits entering the acceptor stage is equal to  $M(\mod 2^7)$ , that is, the number of positions shifted.

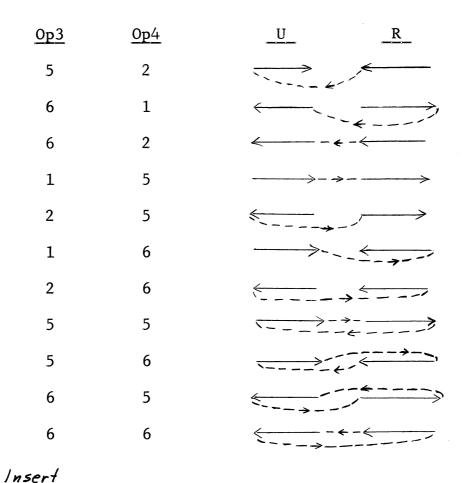

The pattern of shifts is specified by the triads Op3 and  $\widehat{Op4}$ , with Op3 determining the behavior of the U register and Op4 that of the R register in the following manner:

|                      | Op3     |         |    |                  | 0p4          |         |        |

|----------------------|---------|---------|----|------------------|--------------|---------|--------|

| Bit 1                | Bit 2   | Bit 3   | В  | sit 1            | Bit 2        | Bit 3   |        |

| into U<br>"acceptor" | U left  | U right |    | ato R<br>accepto | R left<br>r" | R right | )<br>} |

| 0)zeros              | 0 times | 0 times | 0) | zeros            | 0 times      | 0 times | 4      |

| 1)spill<br>from R    | M times | M times |    | spill<br>rom U   | M times      | M times |        |

The pattern of shifts can also be pictured in the following way:

| <u>Op3</u> | <u>Op4</u> | <u> </u> | R                 |

|------------|------------|----------|-------------------|

| 1          | 0          | >        |                   |

| 2          | 0          | <        |                   |

| 0          | 1          |          | $\longrightarrow$ |

| 0          | 2          |          | ←                 |

| 1          | 1          | >        | $\longrightarrow$ |

| 2          | 1          | <b>{</b> | >                 |

| 1          | 2          | >        | ←                 |

| 2          | 2          | <b>~</b> | ←                 |

| 5          | 1          | <u> </u> | × A               |

The only connections that are meaningful for the arithmetic shifts are  $U_{54}$  to the left end of R and the left end of R to  $U_{54}$ , i.e.

In other words, any spill from the extreme ends of U or R are lost, and only ones or zeros will be accepted at these places. Hence, the full range of shifting possibilities is available in logical shifts only.

All shifts are controlled by the 15 bit integer M in the instruction register, modulo 128.

The procedure for logical bit count is as follows:

- (1) U and S are cleared to zero.

- (2) The shift pattern specified by Op3 and Op4 is executed with the spill out of the low end of R going to the lowest order stage of the adder. Thus the bits are added one at a time (with each shift) to U. By convention we use 0, 1 for the Op3, Op4 code in the bit count.

The-set sense lights and set mode lights instructions

With Op 1 = 2 or 6 the lights turned on or off respectively are as follows: 0) sense lights 1) mode lights 2) trapping lights 3), 4), 5), 6), 7) not used

Lights corresponding to zeros in M are not affected.

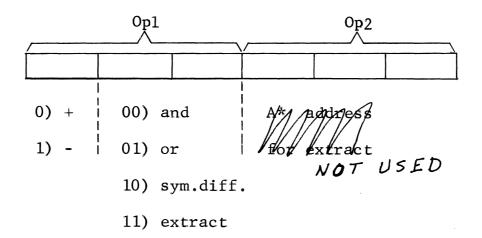

<u>Class 5</u> - Logical

Only Opl and 0p2 are used. (U) and (S) are combined by a logical operation.

These operations will work on all 54 bits. The first bit enables us to negate (one's complement) the final result. In "and", "or", and "symmetric difference" corresponding bits in U and S are compared and the usual logical result placed in U. Extract is more complicated and involves three words. Below we give the combination tables for "and", "or", and sym. diff. and their negations:

Op 1:

The

| 0)     | and     |   | 0               | 1                                | 4) | neg and               | 0      | 1    |

|--------|---------|---|-----------------|----------------------------------|----|-----------------------|--------|------|

|        |         | 0 | 0               | 0                                |    | 0                     | 1      | 1    |

|        |         | 1 | 0               | 1                                |    | 1                     | 1      | 0    |

| 1)     | or      |   | 0               | 1                                | 5) | neg or                | 0      | 1    |

|        | (       | 0 | 0               | 1                                |    | 0                     | 1<br>0 | 0    |

|        |         | 1 | 1               | 1                                |    | 1                     | 0      | 0    |

| 2)     | sym dif | f | 0               | 1                                | 6) | sym sum               | 0      | 1    |

| ·      |         | 0 | 0               | 1                                |    | 0                     | 1      | 0    |

|        |         | 1 | 1               | 0                                |    | 1                     | 0      | 1    |

| 3)     | extract |   |                 |                                  | 7) | neg extra             | ct     |      |

| The    | (M)     |   | $(\mathcal{R})$ | is outlined<br>)<br>) into (F)—— |    |                       |        |      |

| conten | 2       |   |                 | <del>) 1.100 (1)</del>           |    | <del>-Op2)</del> is e | xtra   | cted |

|        |         |   |                 | ?<br>?                           |    | 1-7                   |        |      |

through the contents of **B** as a mask (this word is set up by

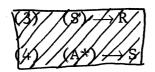

memory address M and inflections) into (F), set up as usual by field 1. The sequence of operations is as follows:

- (1)  $(F) \rightarrow U$  (from field 1)

- (2) (M) or  $M \rightarrow S$  (from field 4)

(3) The bits of (S) corresponding to 1's in (R) are substituted into U; the remaining bits of U are unchanged.

The operation neg extract merely forms the 1's complement of this final result in U.

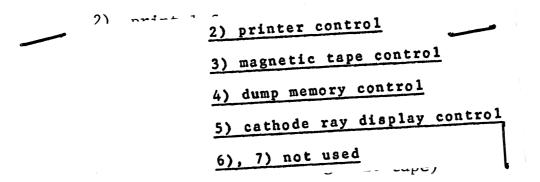

Class 6 - Input-Output

The Rice Computer will have the following auxiliary input-output equipment:

- (1) one optical paper tape reader

- (2) one fast line printer

- (3) one console typewriter

- (4) one paper tape punch

- (5) several magnetic tape units (Provision will be made in the vocabulary to be able to add an arbitrary number of units in the future. Initially there will be two units.)

Of these five pieces of equipment, the magnetic tape units will have the most complicated and versatile order code. For a complete understanding, the reader should read the sections in this manual devoted to the detailed description of each unit. However, for the purpose of following the description of this class of orders the following brief outline will suffice.

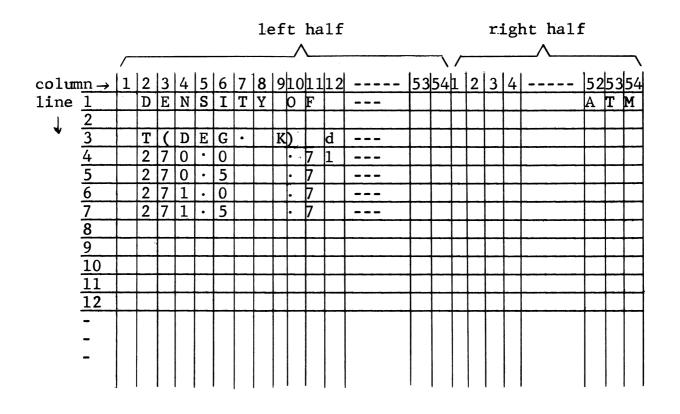

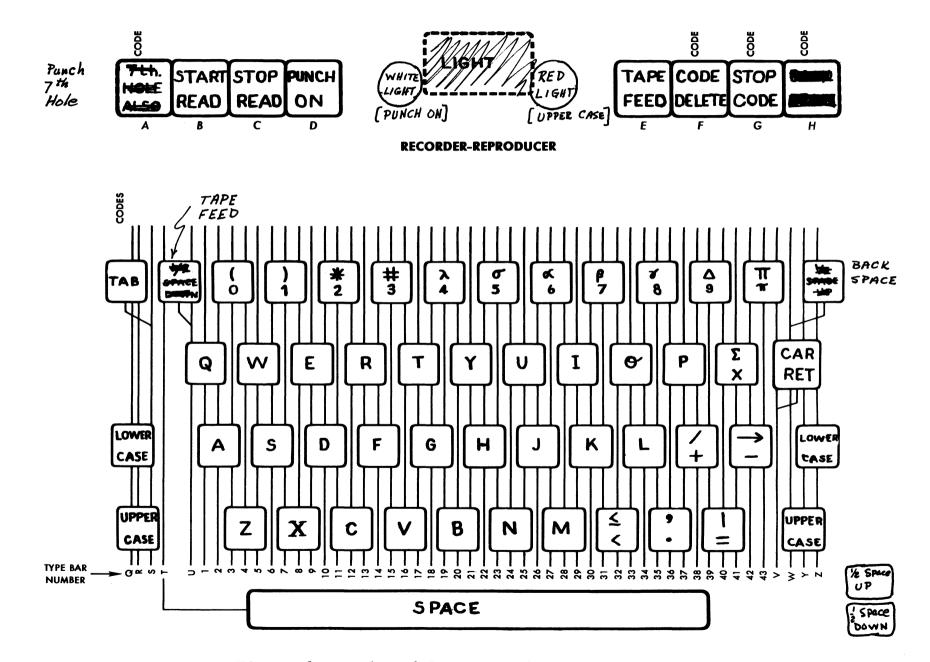

The paper tape used is seven hole tape (i.e., the optical reader may read seven bits at a time). The information in six positions (a hexad) is transferred to and from the machine. The seventh position is used for the purpose of control and is not read into the memory. A punch in the seventh position means that the corresponding hexad is not to be read into the machine but is to be interpreted as a control on reading ( $e_{\circ}g_{\circ}$ , delete or ignore, end of word, end of tape).

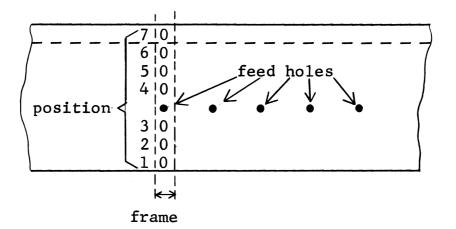

Paper tape will be prepared on an electric typewriter punch which will punch one hexad at a time.

The <u>optical reader</u> may be used to read (1) a whole tape at a time (terminated by an "end-of-tape" control punch) or (2) one to nine hexads at a time (as specified by the coder). The first choice may also be initiated by a load switch on the control console.

The <u>line printer</u> will have 64 characters. These will include the numbers from 0 through 9, mathematical symbols, lower case letters a through f, upper case letters A through Z, and special symbols. In addition, there will be provisions for format control by means of a control tape on the printer itself.

The <u>console typewriter</u> can be used to type octal (i.e., binary) information into the instruction register and into the S register. In addition, the console typewriter can be used to obtain the octal contents of any of the F registers (both A series and B series). This can be accomplished by means of a stored instruction or keys on the typewriter. There will be one key for each register. When a given key is struck, the contents of the corresponding register will be typed in octal.

The <u>paper tape punch</u> can be ordered to punch one to nine hexads at a time or special control punches.

The contents of the memory can be recorded (i.e., written) on <u>magnetic tapes</u> in blocks of arbitrary length. These blocks can be grouped in files.

The triad, Opl, will be used to designate the unit or units selected and their functions. The remaining triads, Op2-Op4, then are used to designate various inflections and details. Op1:

0) paper tape control (either read er punch)

1) type  $[(M) \rightarrow \text{console typewriter in octal}]$

# MARY REPERT CHARGES HOLDER

The detailed description of each function is as follows. Op2:

This triad specifies the various options on the "read paper tape" and "punch paper tape" order.

| 0 | _ | ົ |

|---|---|---|

| U | р | ۷ |

|    | Bit 1 | Bit 2                      | Bit 3      |

|----|-------|----------------------------|------------|

| 0) | read  | punch hexads               | hexad mode |

| 1) | punch | punch hexads<br>+ 7th hole | octal mode |

Description of read and punch paper tape orders:

In the read {hexad mode the following sequence is executed:

$\begin{array}{c} (F) \longrightarrow U \\ (M) \text{ or } M \longrightarrow S \end{array} \right\} \text{ usual decoding of fields 1 and 4}$

No 0V (1) shift U left  $\left\{ \begin{array}{c} 6\\ 3 \end{array} \right\}$  places [logical shift] (2)  $\left\{ \begin{array}{c} hexad\\ triad \end{array} \right\}$  under optical reader  $\rightarrow$  U (triads 17-18) (3) test exponent overflow 0V (4) store (U); (U)  $\rightarrow$  M

> (5) decode field 3, then proceed to next instruction

In the punch { hexad } mode, the following sequence is executed:

$\begin{array}{c} (F) \longrightarrow U \\ (M) \text{ or } M \longrightarrow S \end{array} \right\} \quad \text{from fields 1 and 4}$

(1)  $S \longrightarrow R$ (2) shift UR left  $\begin{cases} 6 \\ 3 \end{cases}$  places [long logical shift] (3)  $\begin{cases} hexad \\ triad \end{cases}$  in lower order part of U $\longrightarrow$  punch +  $\begin{cases} 0 \longrightarrow 7th hole \\ 1 \longrightarrow 7th hole \end{cases}$ (4) test exponent overflow

»(5)

proceed

Bit 2 of Op2 refers only to the punch orders.

Op3:

This triad controls the various output formats of the line printer on the print order.

#### Loading of paper tape

A. Automatic starting of the machine is accomplished by loading the paper tape reader and pressing the load button on the control console. Pressing the load button does the following:

- 1) Sets CC = 1

- 2) Turns on the repeat mode light

- 3) Sets I to the load instruction (see below)

- 4) Starts paper tape feed

The load instruction consists of the following, in the order of decoding:

Field 1

$\frac{1F}{100} \xrightarrow{F} (CC) \rightarrow U, \text{ placing a 1 in the lowest-order}$ bit of U.

Field 4

BM

When Field 4 is decoded the first time  $(I_M)$  is the first true memory address 000 000 000 001 000. Each time the order is repeated,  $(I_M)$  is increased by (CC) = 1.

Note: If it is desired to start loading at an address other than 10, the desired read instruction must be manually typed into the I register and the start button must be used.

Field 2

This field indicates that the order is an input-output order and specifically denotes a read hexad paper tape function.

#### Field 3

Not used.

The overall operation of the load procedure is the following: The paper tape reader is loaded with the desired tape and the load button is depressed. Field 1 is decoded and places a 1 in the lowest order bit of U. This is accomplished by sending  $(CC) \rightarrow U$ . The machine begins reading hexads and shifting them into .the U register. This is continued until the 1 which was previously placed in the lowest order bit of U reaches exponent overflow. Then  $(U) \rightarrow M$ which initially is 10...

41a

Since the repeat mode light is on the order is repeated until the end of the tape punch turns off the repeat mode light. The last word is then read from tape into U and  $(U) \rightarrow M$ , leaving the last word in U. The instruction register then consults CC for the address of the next instruction. (CC) = 1. Therefore the next instruction is (U) which is the last word from paper tape. Thus the memory is loaded and the first instruction is in the I register.

B. For manual starting or alteration of the normal loading process dure, the control console also has a selector switch and a start buttorn. The selector switch (15 push buttons) selects registers for manually typing in instructions and the start button serves to remove halt conditions (Field 2, Class 0) as well as manually starting the machine from a typed instruction. Op 3:

- 0) no space.

- 1) space ½ line

- 2) space 1 line

- 3) space 2 lines

- 4) format #1 on printer (usually restore half page)

- 5) format #2 on printer (usually restore full page)

- 6) format #3 on printer

- 7) format #4 on printer

The coder has the option of preparing up to four of his own formats for spacing control on the printer.

The orders pertaining to magnetic tape should be ignored at this time. The principal reason for this is that a simple buffer and checking system is now being prepared for the computer. A new description of magnetic tape input and output will be written as soon as possible.

Class 7 - Special Functions.

We plan initially to have the square root (  $\sqrt{(U)} \rightarrow U$ ) and eventually a number of other special functions, depending upon the need for such functions and the feasibility of building the necessary circuits.

eight The soon manipulations which may be performed are as follows : D contente of U -> an A address 000 1, " R -> an A address  $Z: (Bi) + 1 \longrightarrow Bi$ 010 3. (Bi) + (X) [increment register] -> Bi 100 \$ @ address portion of u -> Bi  $'' "R \rightarrow B;$ 101 5 1106 (Bil-1 -> B: 1117 address Fortion of instruction register -> B: Note that if I St = 0 121, St is an A address 11 = 2 - 7 11 " a B 11 the neckstary with current 1. use Masy 't ... proceeding ( the second parase ( a)

# 4. Field 3

The two triads of field 3 (ISt, St) offer an additional flexibility to each instruction by allowing the coder to obtain "free" (i.e., without an additional order or access time) one of for convenient manipulations. The decoding of this field is independent of the operation code and all for choices are available with all possible orders. St is a fast address (see discussion of addresses). Bit 1 of ISt determines whether we mean an A or a B address. Bits 2 and 3 of ISt specify one of the four permissible manipulations, namely, store (U) in a fast register, store (R) in a fast register, advance  $B_i$  by 1, or advance  $B_i$  by the contents of X, the increment register.

ISt St ISt St ISt: 0)  $(U) \rightarrow A_i$  4)  $(U) \rightarrow B_i$ 1)  $(R) \rightarrow A_i$  5)  $(R) \rightarrow B_i$ 2)  $(B_i) + 1 \rightarrow B_i$  6)  $(B_i) - 1 \rightarrow B_i$ 3)  $(B_i) + (X) \rightarrow B_i$  7)  $(I)_{40-54} \rightarrow B_i$ where  $A_i$  is an A-series register and  $B_i$  is a B-series register. St: i = 0, 1, ..., 7, the address of the desired register

in the A- or B-series.

field 3 is left blank (all zeros), this section will be ignored and the computer will then fetch the next instruction.

Examples of field 3:

| <u>octal code</u>                     | meaning                                                                        |

|---------------------------------------|--------------------------------------------------------------------------------|

| 00<br>62<br>3                         | ignore<br>B <sub>2</sub> -1 - B <sub>2</sub><br>meaningless - do not-use       |

| 03<br>B                               | ( <del>11)==s</del> (u) → S                                                    |

| 14<br><b>24</b> -                     | $(R) \longrightarrow T_4$                                                      |

| <u>33</u>                             | $(B_4) + 1 \longrightarrow B_4$                                                |

| A A A A A A A A A A A A A A A A A A A | $(B_3) + (X) \longrightarrow B_3$                                              |

| 40                                    | (U) $\rightarrow CC$ (an effective transfer)                                   |

| 75                                    | $(I)_{40-54} - B_{5}$                                                          |

|                                       | 5 bits of a long register (e.g., U)<br>they are transferred without any change |

|                                       | he mantissa sign of the 54 bit regis-                                          |

| ter is also examined. If              | the sign is plus, the 15-bits are                                              |

transferred without any change. If the sign is negative, the

-2's complement of the 15 bits is placed in the B register (i.e.,

the number in U plus the sign is transferred to B).

Examples should be disregarded as printed in view of changes in machine language.

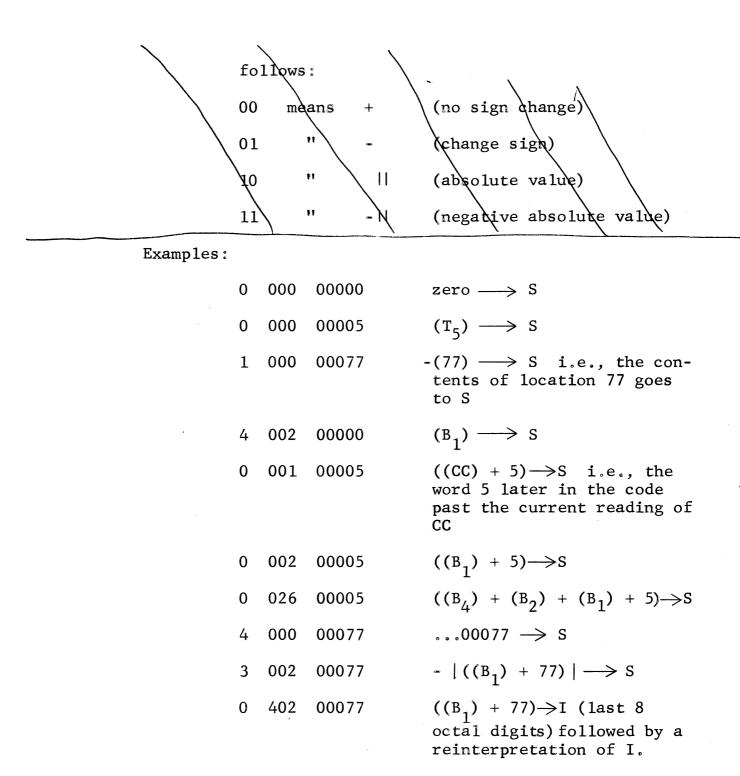

#### VI.

# EXAMPLES OF SINGLE INSTRUCTIONS

In order to illustrate the procedure of microprogramming instructions (that is, composing a single instruction) in machine language, the following arbitrary list of instructions is presented.

The instructions are grouped according to class. The numerical code in octal is first given for each order. The octal digits are arranged according to the following pattern:

| field 1 | field 2       | field 3 | fie    | eld 4 |

|---------|---------------|---------|--------|-------|

| XX      | XXXXX         | XX      | xxxx   | xxxxx |

| IF, F   | class &<br>Op |         | IM, BM | М     |

Below each numerical pattern is a symbolic description of what the order will accomplish. The reader is strongly advised to check the numbers against the previous outline of the order code and to try to compose a few instructions. After a few attempts, one will realize how easy it is to memorize the various field codes to compose orders.

#### Class 0

# 00 00000 00 0000 00000

Stop. A class 0 (control) order, halt and transfer variety which is unconditional; S and U are cleared, CC is set to zero.

#### 01 01200 06 4000 06122

Transfer to location 6122 if mantissa overflow indicator is on; U is unchanged and  $(U) \rightarrow T_6$ ; 6122 $\rightarrow$  S.

# 01 01000 00 4001 00015

Jump forward 15 instructions. U is unchanged and the address (CC) +  $15 \longrightarrow S$ , thus saving a memory access time.

51 06150 00 5000 00007

Skip CC by 1 when  $-(B_1) + 7 \ge 0$  (positive, non-zero)

42 03120 61 4002 00007

Skip CC by (X) when  $+ (B_2) - 7 - (B_1)$  is positive or even. In any case, advance  $B_1$  by 1.

# 04 07105 61 0002 00555

This order can be used to search consecutive memory locations starting at 555 until a number larger algebraically than the one in  $T_4$  is found or tag 1 is reached (the end of the table). This is accomplished by assuming that X contains -1 (i.e., the two's complement of 1). As a note of caution we recommend that such an order be in the T registers or that the repeat mode be used. Otherwise the chance of a read-around error may become appreciable.

Class 1

00 10000 00 0000 12345

$0 \longrightarrow U$  and  $(12345) \longrightarrow S$ ; fixed point  $(U) + (S) \longrightarrow (U)$  with exponent of  $(S) \longrightarrow$  exponent of (U). Hence,  $(12345) \longrightarrow U$ .

04 10600 04 0002 12345

$(T_{\underline{A}}) \times (12345 + (B_{\underline{1}})) \longrightarrow U$  (floating point) then  $(U) \longrightarrow T_{\underline{4}}$

41 10200 53 4004 00000

$(B_1) \times [(B_2) + 0] \longrightarrow U, R \quad (fixed point)$   $(R)_{14-18} \xrightarrow{\rightarrow} B_3 \quad i.e., [(B_1) \times (B_3)] \pmod{2^{15}} \xrightarrow{\rightarrow} B_3$

Note that since we consider the numbers in B registers as integers, they are sent to the lower bits of U and S and the product is formed in the lower order 30 bits of R.

Class 2

$01 \ 20000 \ 00 \ 0000 \ 12345$ (U)  $\rightarrow 12345$  (clearing tag to zero)

07 21023 00 0002 12345

Bits 28-54 of  $(T_7) \rightarrow bits$  28-54 in location [12345 + (B<sub>1</sub>)] with a tag 3.

03 20000 61 0002 12345 (S)  $\rightarrow U$ (12345 + (B<sub>1</sub>)) $\rightarrow$ S then (U)  $\rightarrow$  12345 + (B<sub>1</sub>) and (B<sub>1</sub>) + 1  $\rightarrow$  B<sub>1</sub>

Together with the repeat mode, this can be used to shift a block of numbers in storage.

Class 4

44 44400 07 4002 12345  $(B_4) \longrightarrow U \longrightarrow T_7$  (i.e.,  $(B_4)$  is saved in  $T_7$ ) 12345 +  $(B_1) \longrightarrow B_4$

In the same instruction 12345 + (B<sub>1</sub>) $\longrightarrow$ S, thus the new number in B<sub>4</sub> is also available in S.

We assume that location 12345 only contains a non-zero number in the M section (triads 14-18), that is, with no modifications. This is a means of incrementing B with a number in memory.

# 01 45056 00 4000 00066

This instruction inverts the order of the bits in U and sends the results to R and at the same time inverts the order of the bits in R, sending the result to U.

22 46010 73 4000 50000

$-(R) \longrightarrow U$

Turn on sense lights 1 and 3

then increment  $B_3$  by (X), i.e.,  $(B_3) + (X) \rightarrow B_3$

Class 5

01 55000 00 0002 12345

(U) "or"  $(12345 + (B_1))$ , then complement result.

06 53700 00 0000 12345 (T<sub>7</sub>) through (12345) into (T<sub>6</sub>), result $\rightarrow$ U For example, consider the initial bits:

| T <sub>7</sub> | 1 | 1 | 0 | 0 | 1 | - | - |             | - |

|----------------|---|---|---|---|---|---|---|-------------|---|

| 12345          | 0 | 1 | 1 | 0 | 0 | - | - | -           | - |

| T <sub>6</sub> | 0 | 0 | 1 | 1 | 1 | æ | - |             | - |

| result         | 1 | 1 | 0 | 1 | 1 |   |   | 3 <b>80</b> | - |

## <u>Class</u> 6

#### 10 60000 61 4002 01000

Read one hexad from paper tape to location  $1000 + (B_1)$ . The hexad is located in the lower order 6 bits; all other bits are zero except the exponent sign which is negative. In addition,  $(B_1) + 1 \longrightarrow B_1$ . If the repeat mode is used in conjunction with this order, a series of hexads can be read into a block of storage. The repeat mode light is turned off by a special control punch.

#### 02 60100 61 4002 01000

We assume that R contains a one in bit 54 and zeros elsewhere. This order then reads 18 triads or a word from tape into memory location 1000 + ( $B_1$ ). Then ( $B_1$ ) + 1 $\longrightarrow$  $B_1$ .

10 60600 00 0002 12345

1

Punch the exponent plus sign of location  $12345 + (B_1)$  onto paper tape and punch control hole.

Special purpose register (77775)<sub>8</sub> is known as the indicator register. The bits of this register are themselves indicators which describe certain conditions of the computer. If the bit is 1, the indicator is said to be "on" or the corresponding condition has been recorded.

| bit  | condition                     |

|------|-------------------------------|

| 1    | arithmetic tag indicator #1   |

| 2    | arithmetic tag indicator $#2$ |

| 3    | arithmetic tag indicator $#3$ |

| 4    | U mantissa overflow indicator |

| 5    | U exponent overflow indicator |

| 6-15 | not used                      |

#### INDICATORS

The Rice Computer will have available a number of indicators useful in determining the logical control of the problems.

Overflow and Tag Indicators

These indicators are either on or off and can be tested by means of a class 0 test instruction. Transfer of control can be effected by such instructions on either the "on" or the "off" status of the indicator. Whenever an indicator is turned on, it remains on until it is tested. When it is tested, it is turned off regardless of its prior condition. The reader is advised to study the numerical word structure before reading this section.

| abbreviation   | <u>full</u> name             |

|----------------|------------------------------|

| MAN 🛧 or MANOV | U register mantissa overflow |

| EXP 1 or EXPOV | U register exponent overflow |

| tag 1          | tag indicator # 1            |

| tag 2          | " # 2                        |

| tag 3          | ™ <b>#</b> 3                 |

The status of these indicators is displayed on the console in the form of small neon lights.

VII

#### Mantissa Overflow Indicator

This indicator is turned on when <u>the word in U has a</u> <u>positive sign on its mantissa and</u> a 1 is carried past the binary point into the overflow position <u>or when the word in</u> <u>U has a negative sign on its mantissa and a 0 is carried</u> past the binary point into the overflow position. This **ema**

can be the result of the execution of a fixed point arithmetic or an arithmetic shift command. An example is a carry resulting from an algebraic addition. The indicator can be turned off by testing it. [See also the section on floating point arithmetic.]

# Exponent Overflow Indicator

This indicator is turned on when a l is carried past the Sign and a l is carried past the first bit of the exponent of the U register (i.e., bit 2 in U) or when the exponent of U is negative and a O is carried past the First bit. This can be the result of the execution of a floating point

arithmetic order or a logical shift left. [See also the section on floating point arithmetic.]

## Tag Indicators

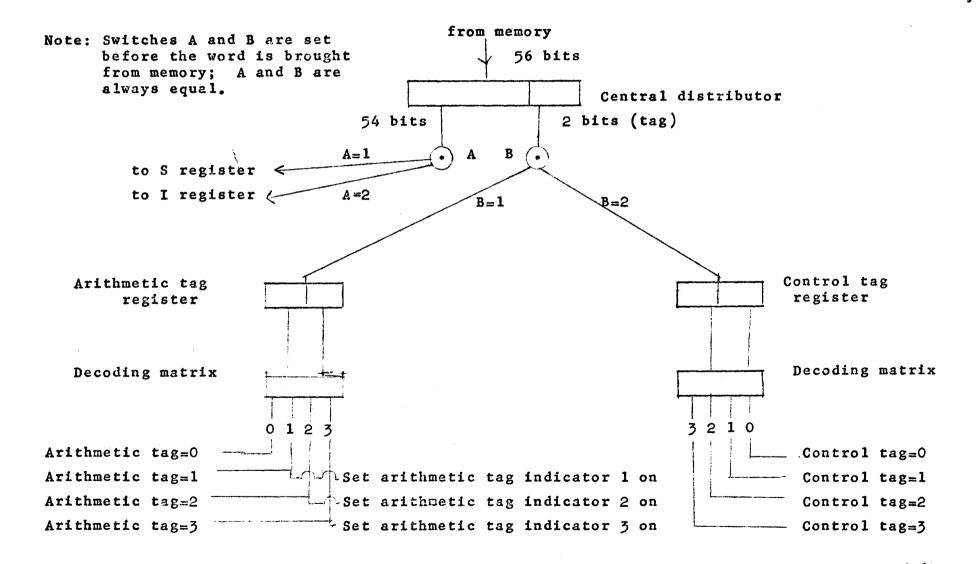

When a word from memory enters the arithmetic unit through the central distributor, the two tag bits are noted according to the following code:

| 00 | no tag |

|----|--------|

| 01 | tag 1  |

| 10 | tag 2  |

| 11 | tag 3  |

If the number in memory is tagged, the corresponding tag indicator is turned on. Note that the two tag bits exist

tag register in the arithmetic unit. For a discussion of the uses of tags the reader should refer to the section entitled, "Tagging and Trapping."

# Sense Light Register

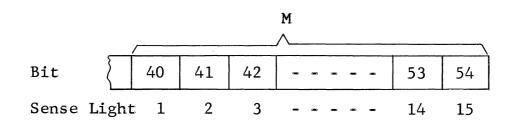

The sense lights are numbered 1 through 15 and are available to the coder for general use, e.g., control of printing, sequencing of orders, transfers of control, visual indication of certain phases of a calculation, and so forth.

The lights are located on the console with a switch below each light. The lights themselves correspond to the bits in the sense light register (location 77771). When a given bit position has a one in it, the corresponding light is on. The switch below each light may be (1) in a neutral position (the sense indicator is then under internal control); (2) depressed momentarily to turn on the given sense light; (3) locked in the down position which sets the sense indicator to "one" as long as the switch is down; or (4) locked in an "off" position. When a switch is in the neutral position, the sense light may be turned on or off by a set sense instruction. The status of any sense light or group of sense lights may be tested at any time. The test does not affect the status of these indicators.

# Mode Light Register

The mode lights are numbered one through 15 and correspond with machine operation modes one through fifteen. Modes one through six have been assigned as noted below; the remainder are reserved for assignment to be made at a later time as need dictates.

Mode lights are essentially sense lights which control and indicate the status (in use or not in use) of their corresponding machine modes of operation. The lights are located on the console with a switch below each light. The lights themselves correspond to the bits in the mode light register (location 77773). When a given bit position has a 1 in it, the corresponding light is on, indicating that the mode is in use. The switches associated with the lights are used in exactly the same manner as those associated with the sense lights (see the previous section).

| mode light o | control specification          |

|--------------|--------------------------------|

| 1 5          | gnore error stop mode          |

| 2 1          | cepeat mode                    |

| 3 t          | rapping mode                   |

| 4 s          | significance mode              |

| 5 1          | cound mode                     |

| 6-15         | reserved for future assignment |

When mode light one is on, the machine ignores all automatic error stops (e.g., improper division). When mode light 2 is on, the "fetch and advance CC" operation is omitted and the computer will repeat the current order. When mode light 3 is on, the machine will operate in the trapping mode (see the section on tagging and trapping). When mode light 4 is on, the machine will perform floating point arithmetic in the significance mode (see section on floating point arithmetic). When mode light 5 is on, the high order bit of R is added into the low order end of U after floating point additions and subtractions and after all multiplications.

#### VIII.

#### TAGGING, TRAPPING, AND REPEAT

The numerical word and instruction word in the Rice Computer is 54 bits in length. However, in memory each word has two additional bits called tag bits which allow the coder to tag a word with one of three possible labels. This concept offers many novel features and possibilities in coding.

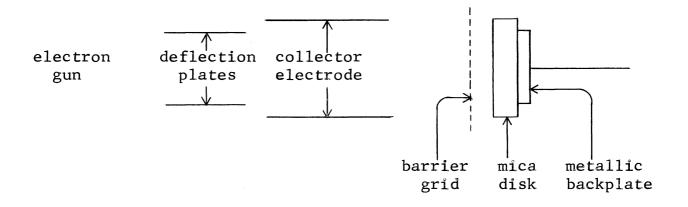

#### Tag Registers